## **Physical Random Functions**

by

#### Blaise L. P. Gassend

Diplôme d'Ingénieur École Polytechnique, France, 2001

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 2003

© Massachusetts Institute of Technology 2003. All rights reserved.

| Author       |                                                                                                   |

|--------------|---------------------------------------------------------------------------------------------------|

|              | Department of Electrical Engineering and Computer Science<br>January 17, 2003                     |

|              |                                                                                                   |

| Certified by |                                                                                                   |

|              | Srinivas Devadas<br>Professor of Electrical Engineering and Computer Science<br>Thesis Supervisor |

|              |                                                                                                   |

Professor of Electrical Engineering and Computer Science Chairman, Department Committee on Graduate Students

## **Physical Random Functions**

by Blaise L. P. Gassend

Submitted to the Department of Electrical Engineering and Computer Science on January 17, 2003, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering and Computer Science

#### **Abstract**

In general, secure protocols assume that participants are able to maintain secret key information. In practice, this assumption is often incorrect as an increasing number of devices are vulnerable to physical attacks. Typical examples of vulnerable devices are smartcards and Automated Teller Machines.

To address this issue, Physical Random Functions are introduced. These are Random Functions that are physically tied to a particular device. To show that Physical Random Functions solve the initial problem, it must be shown that they can be made, and that it is possible to use them to provide secret keys for higher level protocols. Experiments with Field Programmable Gate Arrays are used to evaluate the feasibility of Physical Random Functions in silicon.

Thesis Supervisor: Srinivas Devadas

Title: Professor of Electrical Engineering and Computer Science

## Acknowledgments

This work was funded by Acer Inc., Delta Electronics Inc., HP Corp., NTT Inc., Nokia Research Center, and Philips Research under the MIT Project Oxygen partnership.

There are also many people who have contributed to this project in big or little ways. I will mention a few of them, and certainly forget even more.

First of all, I would like to thank my advisor, Srinivas Devadas, for his boundless energy and incessant stream of ideas, which were essential in getting Physical Random Functions off the ground. I also warmly thank the other key players in the development of Physical Random Functions: Marten van Dijk, who is always full of enthusiasm when I come to talk to him; and Dwaine Clarke, who always makes me "spell it out" for him – often quite a fruitful exercise.

I also greatly appreciated the help of Tara Sainath and Ajay Sudan, who decided to spend their summer hacking away at FPGA test-boards, instead of going somewhere sunny as they rightly should have. My office-mates, Prabhat Jain, Tom Kotwal and Daihyun Lim, deserve special credit for putting up with me, despite my tendency to chat with them while they are trying to work, and write on my white-board with toxic smelling markers. My girl-friend, Valérie Leblanc, and my apartment-mate, Nate Carstens, have been very good at not pointing out that I haven't been doing my share of kitchen work lately, as I devoted myself to writing. My gratitude also extends to all the people on my end of the second floor, who contribute to making it a warm and lively place. And finally, I thank my parents, and all my past professors, without whom I would never have ended up at MIT in the first place.

Last, but not least, I must state that this work would never have been possible but for Ben & Jerry's ice-cream. Without it, surviving the lengthly meetings in which all these ideas first surfaced would have been impossible.

## Contents

| C             | Contents |         |                             |    |

|---------------|----------|---------|-----------------------------|----|

| $\mathbf{Li}$ | st of    | Figure  | es                          | 11 |

| 1             | Intr     | oducti  | on                          | 13 |

|               | 1.1      | Storing | g Secrets                   | 13 |

|               | 1.2      | Relate  | d Work                      | 14 |

|               | 1.3      | Organi  | ization                     | 15 |

| 2             | Phy      | sical R | Random Functions            | 17 |

|               | 2.1      | Definit | zions                       | 17 |

|               |          | 2.1.1   | Physical Random Functions   | 17 |

|               |          | 2.1.2   | Controlled PUFs             | 18 |

|               |          | 2.1.3   | Manufacturer Resistant PUFs | 18 |

|               | 2.2      | Simple  | e Keycard Application       | 19 |

|               | 2.3      | Threat  | Model                       | 20 |

|               |          | 2.3.1   | Attack Models               | 20 |

|               |          | 2.3.2   | Attacker Success            | 21 |

|               |          | 2.3.3   | Typical Attack Scenarios    | 22 |

|               | 2.4      | PUF A   | Architecture                | 24 |

|               |          | 2.4.1   | Digital PUFs                | 24 |

|               |          | 2.4.2   | Physically Obfuscated Keys  | 24 |

|               |          | 2.4.3   | Analog PUFs                 | 24 |

| 3             | Ana      | dog Ph  | nysical Random Functions    | 27 |

|               | 3.1      | Optica  | d Approaches                | 27 |

|               |          | 3.1.1   | Physical One-Way Functions  | 27 |

|               |          | 3.1.2   | Analog or Digital Interface | 28 |

|               |          | 3.1.3   | Optical CPUF                | 28 |

|               | 3.2      | Silicon | Approaches                  | 29 |

|               |          | 3.2.1   | Overclocking                | 30 |

|               |          | 3.2.2   | Genetic Algorithm           | 32 |

|               |          | 3.2.3   | Delay Measurement           | 32 |

|               |          | 3.2.4   | Measuring a Delay           | 33 |

|               |          | 3.2.5   | Designing a Delay Circuit   | 35 |

|   |            | 3.2.6 Intertwining                          | 39         |

|---|------------|---------------------------------------------|------------|

|   | 3.3        | Experiments                                 | 40         |

|   |            | 3.3.1 Quantifying Inter-Chip Variability    | 41         |

|   |            | 3.3.2 Additive Delay Model Validity         | 44         |

|   | 3.4        | Possibly Secure Delay Circuit               | 46         |

|   |            | 3.4.1 Circuit Details                       | 46         |

|   |            | 3.4.2 Robustness to Environmental Variation | 47         |

|   |            | 3.4.3 Identification Abilities              | 49         |

|   | <b>~</b> . |                                             |            |

| 4 |            |                                             | 53         |

|   | 4.1        |                                             | 53         |

|   | 4.2        |                                             | 55         |

|   | 4.3        | 1                                           | 55         |

|   | 4.4        |                                             | 56         |

|   | 4.5        |                                             | 56         |

|   |            | 4.5.1 Discretizing                          | 57         |

|   |            | 4.5.2 Correcting                            | 57         |

|   |            | 4.5.3 Orders of Magnitude                   | 59         |

|   |            | 4.5.4 Optimizations                         | 60         |

|   | 4.6        | Multiple Rounds                             | 60         |

| 5 | CP.        | P Infrastructures                           | 63         |

| J | 5.1        |                                             | 63         |

|   | 5.1        |                                             | 63         |

|   |            | - 3                                         |            |

|   |            | 0                                           | 64         |

|   | F 0        |                                             | 66         |

|   | 5.2        |                                             | 67         |

|   |            |                                             | 67         |

|   |            | 9                                           | 68         |

|   |            | 0 1                                         | 71         |

|   |            | S S S S S S S S S S S S S S S S S S S       | 72         |

|   |            | 5.2.5 Protocols in the Open-Once Model      | 76         |

|   | 5.3        | Applications                                | 76         |

|   |            | 5.3.1 Smartcard Authentication              | 76         |

|   |            | 5.3.2 Certified execution                   | 77         |

| 6 | Phy        | vsically Obfuscated Keys                    | 79         |

| • | 6.1        | ·                                           | <b>7</b> 9 |

|   | 6.2        |                                             | 80         |

|   | 6.2        |                                             | 81         |

|   | 0.5        | Elements of I Oix Security                  | 01         |

| 7 | Con        | nclusion                                    | 83         |

|   | 7.1        | Future Work                                 | 83         |

|   | 7.2        | Final Comments                              | 84         |

| Glossary     | 85 |

|--------------|----|

| Bibliography | 87 |

# List of Figures

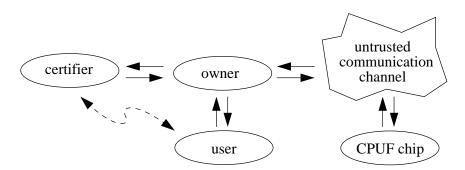

| 2-1  | Control logic must be protected from tampering                         |

|------|------------------------------------------------------------------------|

| 2-2  | Architecture of a digital PUF                                          |

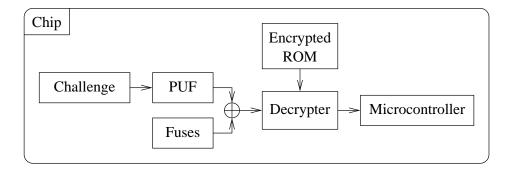

| 2-3  | Architecture of a physically obfuscated PUF                            |

| 2-4  | Architecture of an analog PUF                                          |

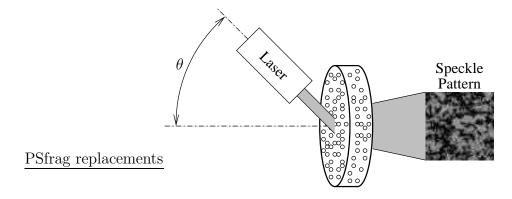

| 3-1  | An optical PUF                                                         |

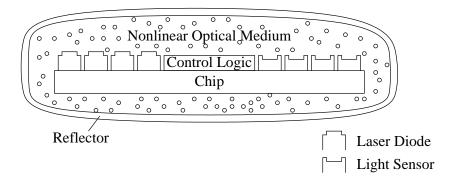

| 3-2  | An optical CPUF                                                        |

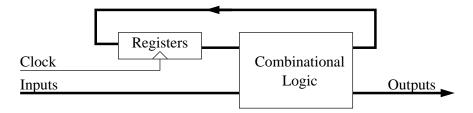

| 3-3  | A general synchronous logic circuit                                    |

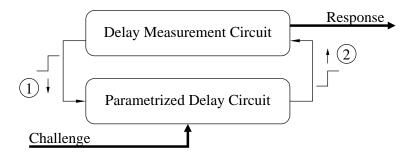

| 3-4  | Measuring delays to get a PUF                                          |

| 3-5  | A self-oscillating loop to measure a delay                             |

| 3-6  | An arbiter-based PUF                                                   |

| 3-7  | The switch block                                                       |

| 3-8  | The simple delay circuit                                               |

| 3-9  | Variable delay buffers                                                 |

| 3-10 | Variable delay buffers in a delay circuit                              |

|      | Delay circuit with max operator                                        |

| 3-12 | Adding internal variables with an arbiter                              |

| 3-13 | Control logic, protected by overlying delay wires                      |

| 3-14 | Interference between self-oscillating loops                            |

| 3-15 | Voltage dependency of delays                                           |

| 3-16 | Response histograms with and without compensation                      |

| 3-17 | Temperature dependence with and without compensation                   |

| 3-18 | The demultiplexer circuit                                              |

| 3-19 | Response vs. challenge for two different FPGAs                         |

| 3-20 | Self-oscillating loop delay measurement                                |

| 3-21 | Locking of nearly synchronized loops                                   |

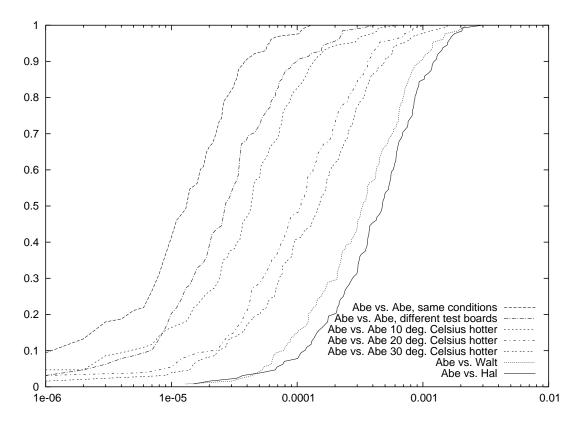

| 3-22 | Variation for different FPGAs or different environmental conditions 50 |

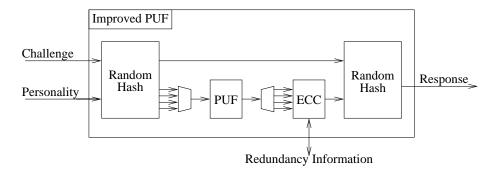

| 4-1  | Improving a weak PUF                                                   |

| 4-2  | Parameters for the Error Correcting Code                               |

| 5-1  | Model for Applications                                                 |

| 5-2  | Model for Bootstrapping                                                |

| 5-3  | Model for Renewal                                                      |

| 5-4  | Model for Introduction 65                                              |

| 5 - 5 | Model for Anonymous Introduction                             | 66 |

|-------|--------------------------------------------------------------|----|

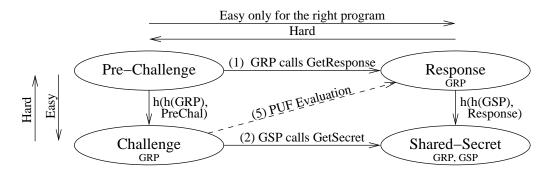

| 5-6   | Navigating pre-challenges, challenges, responses and secrets | 69 |

| 5-7   | The anonymous introduction program                           | 75 |

| 6-1   | Using a PUF to generate a key                                | 80 |

## Chapter 1

## Introduction

## 1.1 Storing Secrets

One of the central assumptions in cryptographic protocols is that participants are able to store secret keys. Protocol participants are able to protect themselves from adversaries because they know something that the adversary does not know. Encrypted messages work because their intended recipient knows a decryption key that eavesdroppers do not know. Digital signatures work because the signer knows some information that nobody else knows, so a potential impostor is unable to forge a signature.

In these examples, we can see that knowing secret information allows someone to perform a certain action (read a message, produce a signature, etc.). In a way the secret keys that are involved identify their bearer as being authorized to perform a certain action.

In many cases, unfortunately, keeping a secret is extremely hard to do. Many devices are placed in environments in which they are vulnerable to physical attack. Automated Teller Machines can be dismantled to try to extract keys that are used for PIN calculation or to communicate with the central bank. In the cable television industry, users can open their set-top boxes to try to extract decoding keys, so that others can get free access to premium rate channels. The EPROM on smartcards can be examined to extract the bits of their signing keys. Many examples and details of exploits can be found in [2, 4].

The state of the art method for protecting against key extraction through invasive physical attack is to enclose the key information in a tamper sensing device. A typical example of this is the IBM 4758 [23]. A battery operated circuit constantly monitors the device, using a mesh of wires that completely envelops it. If any of the wires are cut, the circuit immediately clears the memory that contains critical secrets. This type of protection is relatively expensive as the circuit must be enclosed in tamper sensing mesh and the tamper sensing circuitry must be continuously powered. Despite this, the circuit remains vulnerable to sophisticated attacks. For example, shaped charges could be used to separate the tamper sensing circuit from the memory it is supposed to erase, faster than the memory can be cleared.

The goal of this thesis is to explore a different way of managing secrets in tamper prone physical devices. It is based on the concept of Controlled Physical Random Functions (CPUF).<sup>1</sup> A Physical Random Function (PUF) is essentially a random function, which is

<sup>&</sup>lt;sup>1</sup>Footnote 1 on page 17 explains the CPUF acronym.

bound to a physical device in such a way that it is computationally and physically infeasible to predict the output of the function without actually evaluating it on the original device. That is, taking the device apart, or trying to find patterns in the function's output won't help you predict the function's output on new inputs. A CPUF is a PUF that can only be evaluated only from within a specific algorithm.

Our hope is that with PUFs, a greater level of physical security will be attainable, at a lower cost than with the classical approach of storing a digital secret. Indeed, an attacker can easily read a digital secret by opening a device. To protect the secret, attackers must be prevented from opening the device, or the device must be able to detect invasive attacks and forget its secrets if an attack is detected. Our approach is different; we extract the secret from a complex physical system in such a way that the secret is hard to get by any other means. We can do this because we accept not to choose the secret, and we accept to do more work to reliably reconstruct the secret. In exchange, we can do away with most of the expensive protection mechanisms that were needed to protect the digital secret.

## 1.2 Related Work

The idea of PUFs is not new. It was first studied in [21] under the name of Physical One-Way Functions. In that work, a wafer of bubble filled transparent epoxy is used. When a laser beam is shone through the wafer and projected onto a light sensor, a speckle pattern is created. This pattern is a complicated function of the direction from which the laser beam is incident, and the configuration of the bubbles in the epoxy. For suitable bubble sizes and densities, it is hypothesized that such a wafer is unclonable and that the speckle pattern for a given illumination is hard to predict from the patterns for other illuminations.

What makes this approach work is that a sufficiently complex physical system can be hard to clone, and can be made to exhibit a hard to predict but repeatable behavior. Thus, we have a way of extracting some secret information that we do not choose from a physical system. It appears that not being able to choose the secret information that is extracted makes physical protection much cheaper to implement. This key observation explains why PUFs are easier to implement than secure digital key storage.

The major advantage of CPUFs over the work described in [21] resides in the control. Without control, the only possible application is the one-time pad identification system that is presented in Section 2.2. The output of the PUF cannot be used as a secret for higher level protocols because of the possibility of a man-in-the-middle attack: an adversary can monitor outputs from the PUF to get the device's secret for a specific instance of the protocol. He can then use that secret to run the higher level protocol himself, pretending to be the device.

In our implementation of CPUFs, we use a silicon Integrated Circuit (IC) as the complex physical system from which we seek to extract PUF data. During IC fabrication, a number of process variations contribute to making each integrated circuit unique [6, 8]. These process variations have previously been used to identify ICs. For example, [17] uses random fluctuations in drain currents to assign an identifier to ICs. However, the identification system that results is not resistant to adversarial presence. An adversary can easily find out the identification string for an IC and then masquerade as that IC, since he has all the available identification information.

Unlike the system we propose, these IC identification circuits attempt to extract information from the manufacturing variations in an extremely controlled way, for reliability reasons. In contrast, we use a complex physical circuit for which it is hard to predict the output from direct physical measurements. Moreover, we produce a function instead of a single value, so revealing one output of the function does not give away all the IC's identification information. The parameter that we measure in our circuit is the delay of a complex path through a circuit.

## 1.3 Organization

This thesis is structured as follows. Chapter 2 gives a general overview of PUFs. It includes definitions, a simple application, threat models and general remarks on PUF implementation.

Chapters 3 and 4 go further into the details of PUF implementation. First a weak PUF has to be made that is directly based on a complex physical system. Chapter 3 shows how optical and physical systems can be used to make a weak CPUF. Experimental results for silicon PUFs implemented on Field Programmable Gate Arrays (FPGA) show that the systems we suggest can actually be built, and give an idea of the orders of magnitude that are involved. The following chapter takes the weak CPUF and shows how to make it into a CPUF that is more secure and reliable. This improvement is made by surrounding the weak CPUF with some digital pre- and post-processing.

Now that we know how to build CPUFs, we look at how they can be used. Our main interest is to use PUFs in a network context; machines on the network could use their PUF to prove their physical identity and integrity, even if they are located in hostile environments. Ideally, we would like to build a PUF infrastructure to exchange credentials that has a comparable flexibility to public key infrastructures. Chapter 5 shows how such an infrastructure can be built. Attaching an unique identity to a device raises serious privacy concerns, which our infrastructure is able to address. The chapter is concluded with an example of use for distributed computation.

The network context is not the only context in which PUF ideas can be put to use. In Chapter 6 we show how the physical systems that we have used to make PUFs can instead be used to store keys on a device, in a way that is more secure than simply storing keys digitally.

This research has opened up many opportunities for future work. They are presented in Chapter 7 along with some concluding remarks.

Many terms are defined in this thesis and later assumed to be known to the reader. A glossary is provided at the end of the document to help the reader who has missed one of the definitions.

## Chapter 2

## **Physical Random Functions**

#### 2.1 Definitions

First we give a few definitions related to Physical Random Functions. Because it is difficult to quantify the physical abilities of an adversary, these definitions will remain somewhat informal.

### 2.1.1 Physical Random Functions

**Definition 1** A Physical Random Function  $(PUF)^1$  is a function that maps challenges to responses, that is embodied by a physical device, and that has the following properties:

- 1. Easy to evaluate: The physical device is capable of evaluating the function in a short amount of time.

- 2. Hard to characterize: From a limited number of plausible physical measurements or queries of chosen Challenge-Response Pairs (CRP), an attacker who no longer has the device, and who can only use a limited amount of resources (time, money, raw material, etc...) can only extract a negligible amount of information about the response to a randomly chosen challenge.

In the above definition, the terms short and limited are relative to the size of the device, which is the security parameter. In particular, short can be read as linear or low degree polynomial, and limited can be read as polynomial. The term plausible is relative to the current state of the art in measurement techniques and is likely to change as improved methods are devised.

In previous literature [21], PUFs were referred to as Physical One Way Functions. We believe this terminology to be confusing because PUFs do not match the standard meaning of one way functions [19].

In the rest of this thesis we will often compare PUF methods with methods that involve storing and protecting a digital secret. We will generally refer to the latter methods as classical methods.

<sup>&</sup>lt;sup>1</sup>PUF actually stands for Physical Unclonable Function. It has the advantage of being easier to pronounce, and avoids confusion with Pseudo-Random Functions.

#### 2.1.2 Controlled PUFs

**Definition 2** A PUF is said to be Controlled if it can only be accessed via an algorithm that is physically linked to the PUF in an inseparable way (i.e., any attempt to circumvent the algorithm will lead to the destruction of the PUF). It is then called a Controlled PUF (CPUF). In particular the control algorithm can restrict the challenges that are presented to the PUF, limit the information about responses that is given to the outside world, and/or implement some functionality that is to be authenticated by the PUF.

The definition of control is quite strong. In practice, linking the PUF to the algorithm in an inseparable way is not trivial. However, we believe that it is easier to do than to link a conventional secret key to an algorithm in an inseparable way, which is what classical devices such as smartcards attempt.

Control is the fundamental idea that allows PUFs to go beyond simple identification applications such as the one presented in Section 2.2. Control plays two major parts. In Chapter 4 we will see that control can protect a weak PUF from the outside world, making it into a strong PUF. Moreover, in the assumptions of the control definition, the control logic is resistant to physical tampering, which means that we can embed useful functionality that needs to be protected into the control logic.

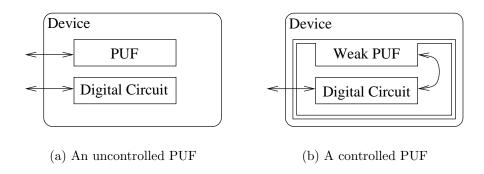

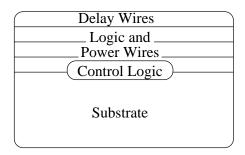

In practice the PUF device will be designed so that the control logic is protected by the fragile physical system that the PUF is based on. Any attempt to tamper with the former will damage the latter. Figure 2-1 illustrates how the PUF is intertwined with its control logic in a CPUF.

Figure 2-1: Control logic must be protected from tampering

#### 2.1.3 Manufacturer Resistant PUFs

**Definition 3** A type of PUF is said to be Manufacturer Resistant if it is technically infeasible to produce two identical PUFs of this type given only a polynomial amount of resources.

Manufacturer resistance is an interesting property; it implies unclonability and greatly reduces the level of trust that must be placed in the manufacturer of the device. Our way of making PUFs manufacturer resistant is to measure parameters of a physical system that are the result of process variation beyond the control of the manufacturer.

## 2.2 Simple Keycard Application

The simplest application for PUFs is to make unclonable key cards. This application was first described in [21]. These keycards would be as hard to clone as the silicon PUFs that we present in Section 3.2. Without unclonability, a keycard that has been lost or lent should be assumed to be compromised, even if it is later retrieved.

We describe a protocol for keycards that allows secure identification, in which some person with access to the card can use it to gain access to a protected resource. The typical scenario is that of a person with a key card presenting it to a reader at a locked door. The reader can connect via a secure channel to a remote, trusted server. The server has previously established a private list of randomly chosen CRPs with the card. When the person presents the card to the reader, it contacts the server using the secure channel, and the server replies with the challenge of a randomly chosen CRP in its list. The reader forwards the challenge to the card, which returns the corresponding response. The reader forwards the response back to the server via the secure channel. The server checks that the response matches what it expected, and, if it does, sends an acknowledgment to the reader. The reader then unlocks the door, allowing the user to pass.

The protocol works because, to clone a keycard, the adversary would have to either guess which CRPs are in the database, or build a database of his own that covers a large enough portion of the CRPs that he has a significant chance of knowing the CRP that the reader will ask. For a big enough PUF, both tasks are infeasible.

Because the server's database contains a small number of CRPs, the method only works if each challenge is be used only once. Otherwise, a replay attack is possible. An attacker harvests some challenges from the reader by trying to get access with a fake card. At a later time he gets access to the real card, and asks it for the responses to the challenges that he has harvested. Finally, he goes back to the reader, and keeps trying to get access until he is asked one of the challenges for which he knows the response. Since the reader only contains a small number of CRPs, the adversary has a significant chance that one of the ones he harvested will get reused. The protocol worked only as long as an attacker was unable to guess which of the unmanageable multitude of challenges would be used. As soon as the attacker was able to find out that some challenges were more likely, he could make himself a partial clone of the keycard, and get unauthorized access. Because each CRP can only be used once, some people like calling this protocol a one-time-pad protocol.

The fact that CRPs can only be used once leads to the possibility of denial of service attacks in which an adversary tries to gain access until the server has run out of CRPs. One way of mitigating these attacks would be to use a classical challenge-response protocol to authenticate that the card knows some digital secret, and only then using the PUF authentication. That way, the denial of service attack is as hard as breaking the classical keycard, while gaining unauthorized access additionally requires breaking the PUF authentication protocol.

There remains the problem of storing a large number of CRPs for each keycard or renewing CRPs once the database runs low. There doesn't seem to be a cheap way of doing either task, which shows how limited this protocol is. The protocol is interesting nevertheless as it is the only PUF protocol that doesn't require control. We shall explain this limitation of

uncontrolled PUFs in Section 5.2.1.

The keycard only solves part of the problem of getting a door to open only for authorized users. Other aspects include making the door sturdy enough to prevent forcible entry, making the server and reader secure, and finding ways such as biometrics or Personal Identification Numbers (PIN) for the user to identify herself to her keycard. Indeed, the goal is usually to give access to a person, and not to any bearer of a token such as a keycard.

### 2.3 Threat Model

The reason for using PUFs rather than classical methods is to try to improve physical security. In this section, we try to quantify the improvement by considering a variety of threat models. First we will consider the abilities the attacker might have, then the goal he is trying to achieve. Finally we will consider a few typical attack scenarios.

#### 2.3.1 Attack Models

There is a wide range of different attack models to choose from:

#### Passive vs. Active

An attacker can simply observe a device (passive), or he can intercept, modify or create signals of his own (active). For any reasonable level of security, an active attacker must be assumed.

#### Remote vs. Physical Access

Classical methods are perfectly suited to defeating attackers that only have remote access to a device. To be useful, PUFs must do just as well against remote attackers.

The real potential that PUFs have for improvement is against attackers with physical access. There is a whole range of physical attackers to consider. Non-invasive ones will simply observe information leaking from the device without opening it. Invasive attacks will actually open the device. Destructive attacks will damage the device. Non-destructive ones won't leave any trace of the attacker's work, allowing him to return the device to its owner without arousing suspicion.

With physical attacks, a level of technology has to be assumed: there doesn't seem to be much we can do against an adversary who can take the device apart an atom at a time, and then put it back together again. Consequently we won't be able to make any absolute statements about PUF security against physical attacks. Both financial resources and state of the art technology must be considered to determine an attacker's physical ability.

#### Openness of Design

Detailed information about the design of the PUF device can be available to the attacker or not. Kerckhoffs' [14] principle says that full knowledge of the design by the attacker should be assumed and only key information should be assumed private.

In the case of PUFs, the key information is typically the process variation that was present during device fabrication. For manufacturer resistant PUFs, that variation can't be controlled and/or known by the manufacturer. For PUFs that aren't manufacturer resistant, the Manufacturer might have some knowledge of or control over that information.

#### Computational Ability

The attacker can have bounded (e.g., polynomial) or unbounded computation at his disposal. Nevertheless, even an attacker with unbounded computation will be limited in the number of queries he can make from the PUF as each query must be run through the single instance of that PUF in existence.

#### Online or Offline

If the attacker can attempt an attack while the PUF is in use, we call him an online attacker. If has access to the device only when it is idle, he is an offline attacker.

An online attacker might be the owner of a PUF equipped set-top box. An offline attacker would be trying to clone the PUF equipped credit card that you left on your desk during a lunch break.

#### 2.3.2 Attacker Success

Possible goals the attacker may have are listed in approximate order of decreasing difficulty:

#### Attacker Clones the PUF

The attacker produces a device that is indistinguishable from the original. The word indistinguishable can take on a range of meanings. For example, in copying a smartcard, the attacker might need to produce a card that looks just like the owner's original card, and that passes for the original in the card reader. When cloning a phone card, however, the clone only has to look like the original to the card reader.

#### Attacker Produces a Partial Clone of the PUF

In this case, the clone isn't perfect, but is good enough for the clone to have a non-negligible probability of passing for the original.

#### Attacker Gets the Response to a Chosen Challenge

Given any challenge, the attacker is able to get the corresponding response. This attack, like those that follow, is only useful in the context of CPUFs, as uncontrolled PUFs are willing to give the response to any challenge to whoever asks.

#### Attacker Tampers with an Operation

Without being detected, the attacker is able to make a CPUF device perform an operation incorrectly. The tampering can be more or less deliberate (i.e., the attacker chooses how exactly the operation is carried out), which leads to a whole range of degrees of success.

#### Attacker Eavesdrops on an Operation

Without being detected, the attacker is able to read information that should have been withheld from him.

#### Attacker Gets the Response to Some Challenge

The attacker manages to find out any CRP. This attack is actually not very interesting for us except in Chapter 6. Indeed, we would like anybody to be able establish trusted relations with a CPUF device, and this will involve knowing CRPs.

#### Manufacturer Produces two Identical Devices

This would violate the manufacturer resistance assumption. We can also imagine that the manufacturer would be able to produce two nearly identical devices that could pass for one another with non-negligible probability.

This security breach only applies for manufacturer resistant PUFs, it is independent in strength from all the attacker goals except cloning.

## 2.3.3 Typical Attack Scenarios

We now describe some typical attack scenarios that we will be trying to prevent in the rest of this thesis.

#### **Brute-Force Attacks**

Naturally, there are a number of brute force attacks that attempt to clone a PUF. An adversary can attempt to produce so many PUFs that two will be identical. This is implausible, as the number of PUFs to produce would be exponential in the number of physical parameters that contribute to the PUF. Moreover it is not clear how to check if two PUFs are identical.

Alternatively, an adversary can attempt to get all the CRPs by querying the PUF. This also fails as the number of CRPs to get is exponential in the PUF input size. The limitation is more severe than in the previous case because all the CRPs must be extracted from a single device that has a limited speed.

#### Model Building

An attacker could produce a generic model of a given class of PUF devices, and then use a relatively small number of CRPs to find the parameters in his model for a specific instance of the device. We can hope to make this attack difficult for a computationally bounded attacker.

#### Direct Measurement

An adversary could open the PUF device and attempt to measure physical parameters of the PUF. Those parameters could then be used to manufacture a clone (not for manufacturer resistant PUFs) of the device, or could be used as parameters for a model of the device. We will often assume that this attack is infeasible as the attacker has to open the device without damaging the parameters that he wishes to measure.

#### Information Leakage

Most protocols that a CPUF could be involved in require that some information being processed in the device remain private. Unfortunately devices tend to leak information in many ways. Power analysis, in particular, has attracted considerable attention in recent years [15], but it is not alone [18, 2]. Therefore CPUFs must be designed with the possibility of information leaks in mind if they involve any manipulation of private data.

#### Causing a CPUF to Misbehave

In the case of a CPUF, the adversary can attack the control logic that surrounds the PUF. He could do so to extract information that should have remained hidden, or generally make the device operate in an unexpected way without arousing suspicion.

This type of attack is present with classical methods [3]. Clock glitches, voltage glitches, temperature extremes or radiation can all be used to cause misbehavior. The classical response is to equip the device with sensors that detect these conditions, or regulate parameters internally. These attacks and defenses still apply in the case of CPUFs.

PUFs can be used advantageously in the case of invasive attacks that try to cause the device to misbehave by tampering with its internal circuitry. Indeed, if the PUF is intertwined with the critical circuitry, attempts to modify the circuitry are likely to damage the PUF causing the tampering to be detected. This intertwining is to be compared with classical methods [25, 23] that surround the device with a mesh of intrusion sensors causing the device to clear its memory when an intrusion is detected. These intrusion sensors must be turned on permanently to prevent an attacker from opening the device while it is off and doctoring the tamper detection circuitry. With PUFs, there is no need for constant active monitoring; the adversary will damage the PUF — which is the device's secret information — whether it is on or off.

#### Open-Once Attacks

A final interesting model that we will consider is the *open once* model. In this model, the attacker cannot exploit information leakage, and he destroys the PUF as soon as he opens the device. However, it is assumed that the attacker can open the device at any time and get full access to the digital state of the device (he can read and tamper at will) at any single time. In doing so, though, he destroys the PUF. Essentially we have a black box containing a PUF and some other circuitry. The PUF works as long as the box is closed, and once the box has been opened so that we can play with the internal mechanisms, it can't be re-closed.

This model might appear contrived. Nevertheless, it leads to interesting results and is plausible if information leakage can be prevented, and the PUF can be caused to break as soon as the device is opened.

## 2.4 PUF Architecture

The definition that was given of a PUF is concerned mainly with functionality. We shall now see an overview of different ways of implementing a PUF.

### 2.4.1 Digital PUFs

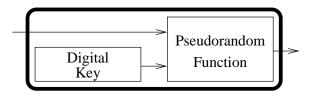

We can contemplate making a PUF by building a circuit that combines its input with a secret using a pseudorandom function, and placing it in an impenetrable vault as in Figure 2-2. This is an extreme case of the PUF as it is built with classical digital primitives. A digital PUF has all the vulnerabilities of any digital circuit, as well as the complications of using PUF protocols. Clearly, there is no point in using digital PUFs.

Figure 2-2: Architecture of a digital PUF

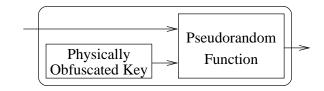

## 2.4.2 Physically Obfuscated Keys

If we eliminate the vault from the digital PUF, then the digital key that is inside can be revealed to an adversary that performs an invasive attack. Therefore, we can try extract the key from a complex physical system that is harder for an invasive adversary to comprehend as in Figure 2-3. By using the complex physical system as a shield for the digital part of this device (to prevent an attacker from opening it and inserting probes to get the key), it might be possible to make a PUF. We will consider this type of idea in Chapter 6. Nevertheless, it would be nice not to have a single digital value that, if probed, reveals all the device's secrets.

## 2.4.3 Analog PUFs

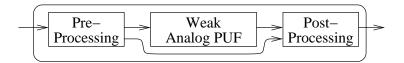

In analog PUFs, we try to put as much functionality as possible into a complex physical system. That system takes a challenge and directly produces a response.

In practice, it is hard to find a physical system that has the characteristics we desire. The output won't be completely unpredictable, and because of measurement noise, the output for a given challenge is likely not to be completely reliable. We can say that we have a weak

Figure 2-3: Architecture of a physically obfuscated PUF

Figure 2-4: Architecture of an analog PUF

PUF. To solve these problems, some digital pre- and post-processing has to be added to the physical system as is shown in Figure 2-4.

The upcoming chapter will look at candidate physical systems for an weak analog PUF. Then in Chapter 4 we will look at the digital processing that is needed to strengthen the PUF.

## Chapter 3

## **Analog Physical Random Functions**

In this chapter, we will discuss ways to produce a weak analog PUF. This is the basic building block that we strengthen into a full-fledged PUF in Chapter 4. The weaknesses that we are willing to tolerate in this chapter have to do with PUFs that have noisy output and for which modeling attacks might be possible.

We will briefly consider PUFs based on optical systems, then move on to the silicon systems, which have been our main focus. This is in no means an exhaustive presentation of ways to make weak analog PUFs.

## 3.1 Optical Approaches

## 3.1.1 Physical One-Way Functions

Physical One-Way Functions [21] are a simple example of analog PUFs (see Figure 3-1). The physical system is a wafer of bubble-filled transparent epoxy. The PUF behavior is obtained by shining a laser beam through the wafer from a location that is precisely defined by the challenge. The laser beam interacts in a complex way with the bubbles in the wafer, and a speckle pattern is observed on the other side of the wafer. This speckle pattern is a function of the exact position of the bubbles and of the laser, and is the PUF's response.

Figure 3-1: An optical PUF

In [21], particular emphasis is put on the fact that the wafer that is being measured is a 3-dimensional system. This is very good because compared with a 2-dimensional system, it increases the amount of information in the system, and makes direct measurement harder. This is a significant advantage over the silicon PUFs that we will consider in Section 3.2 that are essentially 2-dimensional.

### 3.1.2 Analog or Digital Interface

Unlike all the other PUFs that we will consider, the Physical One-Way Function is made to be used with an analog interface: the wafer is embedded in a plastic card and all the expensive optical equipment (laser, speckle detector) is part of the reader. This is interesting because an adversary who wants to clone a wafer by using a model building method has a much harder task. Indeed, not only does he have to be able to predict the speckle pattern for a given laser position, he also has to determine the laser position, and simulate the speckle pattern on the speckle detector in the time interval that is expected by the reader.

We have decided not to pursue analog interfaces as we are more interested in applications where PUF devices are used remotely. That implies that the measurement equipment is just as vulnerable to physical attack as the physical system it is measuring, and the advantages of having an analog interface disappear. Therefore, we prefer to include the measurement equipment into the PUF, and provide a digital interface (i.e., you digitally input the laser's position, and read out a digital representation of the speckle pattern).

A major advantage of incorporating the measurement equipment in the PUF is that there is a reduced need for calibration. If many sensors in many readers have to be able to measure a physical system, then they must all be identically calibrated, whereas if the system is always measured with the same sensor, calibration is unnecessary.

Finally, full fledged CPUFs are only possible if the measurement equipment is part of the PUF. Indeed, a CPUF should be able to restrict challenges and responses it receives, which is not the case if it does not incorporate the measurement equipment.

Of course, for the digital interface method to be cost effective, the sensor equipment must be cheap. That is certainly not the case for Physical One-Way Functions where precision mechanisms are necessary to position the laser source correctly.

## 3.1.3 Optical CPUF

The Physical One-Way Function described above can, in principle, be made into a potentially cost effective CPUF. The key idea is to integrate the light source and light sensors on a chip that is embedded in an irregular transparent medium like the epoxy wafer that we have been considering, and surrounded by reflecting material. The setup is depicted in Figure 3-2.

Instead of mechanically moving a laser source in accordance with the challenge, many laser diodes are present on the chip, and depending on the challenge, a combination of them is be turned on. Since the different laser diodes are not coherent with each other, a speckle pattern with reduced contrast results. To avoid excessive loss of contrast, only a few sources should be turned on at any given time.<sup>1</sup> Moreover, a non-linear optical medium should be

<sup>&</sup>lt;sup>1</sup>If the different sources could be made coherent with each other, this constraint would no longer hold. The

Figure 3-2: An optical CPUF

used so that the speckle pattern isn't simply the sum of the patterns that would result from each source being turned on individually.

With this setup, a control algorithm could be embedded on the chip. The algorithm would be protected from tampering by the optical medium, which would get damaged by any invasive physical attack. Of course information leaks and non-invasive tampering still have to be dealt with.

For now we have not seriously considered implementing this optical CPUF, but it bears some resemblance to preexisting intrusion detection systems [1]. It is interesting for many reasons: it is based on a 3-dimensional physical system, the control logic is clearly intertwined with the PUF, it is manufacturer resistant, and there is hope that there will be better temperature stability than with purely silicon PUFs. On the downside, the bubble-filled epoxy might be a problem for heat dissipation and the processes that enable optical components to be present on-chip are still costly.

## 3.2 Silicon Approaches

Instead of combining optics and microelectronics to produce a PUF, we have focused on ways to produce PUFs that only use cheap and extensively studied silicon technology. This section describes the approaches that we have considered to make a PUF out of an integrated circuit (IC).

Silicon PUFs try to harness the variations that are present when chips are fabricated. These variations and their sources are under constant research [6] as they determine the minimum feature size on ICs. In each new process, chip manufacturers do their utmost to reduce variation. Yet, with each generation, the relative variation increases (Chapter 14 of [8]). This observation shows us that the process variation in ICs might be an excellent starting point for manufacturer resistant PUFs since this variation exists despite the manufacturing world's best effort.

Using process variation to provide chips with a unique identifier has already been done [17] by measuring drain currents in transistors. However, this method reduces the variation to

number of challenges would then grow exponentially with the number of sources, rather than polynomially.

a vector of bits, that is easy to clone by embedding those bits same bits into a device that only pretends to measure physical parameters. The major question that we must answer is how to go beyond simple identification, and use process variation to produce a PUF.

## 3.2.1 Overclocking

For the most part, circuits on ICs are designed in the synchronous logic model: a huge combinational circuit maps a vector of inputs to a vector of outputs, and a bank of registers connects a subset of the outputs to a subset of the inputs (see Figure 3-3). The whole circuit is synchronized on a clock that ticks at regular intervals. Each time the clock ticks the registers instantly copy their input to their output. The combinational logic sees its new input, and propagates it through its logic gates, to compute the new output. While the logic is computing, the output can go through some glitching as signals propagate through the logic at different speeds. Eventually the output settles and the circuit is ready for the next clock tick.

Figure 3-3: A general synchronous logic circuit

As long as the clock frequency is low enough, the output always has time to settle, and the circuit behaves as expected.<sup>2</sup> Fabrication variation only shows up in the details of how signals propagate through the combinational logic. Once the clock signal arrives, all functional chips will have stabilized at the same output value.

This simple picture has been a key contributor to the successful scaling of electronic devices from thousand transistor circuits to hundred-million transistor circuits. Simply by selecting a clock frequency that is low enough, the effects of all the manufacturing variations can be wiped out. However, if the clock frequency is increased, the clock might tick when the output of the combinational logic is still settling, and the results become chip dependent.

This discussion inspires a very simple type of PUF implementation. A challenge is a whole vector of inputs to the combinational logic and a delay. To query the PUF, the circuit is brought into a state in which it will, at the next clock cycle, have the challenge input going into the combinational logic. At the clock tick, that signal starts propagating through the combinational logic. Instead of being sent after the normal clock period, the next tick is sent after the delay that is contained in the challenge. The vector that is captured by the registers during that tick is taken to be the PUF's response. Essentially, the idea is to tell chips apart by looking at their response to momentary overclocking.

<sup>&</sup>lt;sup>2</sup>Of course, there are extra constraints in real circuits because registers have more elaborate timing problems, which are irrelevant here.

In principle, this method could be combined with the methods from Chapter 4 to produce a PUF. In practice, there are many difficulties:

• There is a huge number of challenges for which the response will not depend on the chip at all, or will depend very little on the chip (for example, all challenges for which the delay is greater than the normal clock period). For simple circuits, most challenges will be in this case. That means that a method for finding significant challenges must be found, or else the chip must be queried a huge number of times to get enough identifying information out of it (see Section 4.2).

One way of selecting good challenges would be, to take an arbitrary input vector for the challenge, and look at how the output depends on the delay that we put in the challenge. We pick a delay that is close to a transition of the output. Such challenges would be more likely to vary across chips.

- For complex circuits such as a multiplier, the output vector might vary very rapidly while settling. In order to capture the response consistently, the output vector must be stable for a small period of time around the clock tick called the hold time. If that minimum time is rarely met in the output vector's settling, then few challenges will consistently output the same response. Instead of measuring the device, we would be measuring noise.

- Depending on environmental parameters such as temperature, the settling of the output vector might not occur in the same way. It is not clear how this PUF scheme would be able to recognize a chip that was characterized at a different ambient temperature than the one at which it is used.

- The clock is an extremely sensitive part in a circuit, especially as the circuit size and speed increase. Inserting a precisely timed glitch in its normal operation as this PUF implementation requires is a difficult task.

- The way the combinational logic settles might depend on the previous input as well as the current one, so the previous input would also have to be included in the challenge.

- For complex sequential circuits (in which many outputs of the combinational logic are fed through registers), it is not always possible to bring the circuit into an arbitrary state. Even when it is possible, determining how to do so is very difficult. Therefore, instead of defining the input vector in the challenge, one would need to give a sequence of steps that would bring the circuit into the appropriate state for the PUF measurement to be made.

Clearly, there are a number of problems that arise from this simple PUF implementation. None of them are insurmountable, but so far this doesn't seem like a practical way to make a PUF, though it would have been nice to have a method to make a PUF from an arbitrary synchronous circuit.

## 3.2.2 Genetic Algorithm

Some interesting work [26] involving FPGAs and genetic algorithms shows that it is possible to evolve a circuit to distinguish between an input that oscillates at 1kHz and an input that oscillates at 10kHz. The interesting part for us, is that the evolved circuit, when loaded into a different FPGA, no longer works. Moreover, when we look at the evolved circuit, it is not at all apparent how exactly it works.

This experiment confirms once again that process variation does make chips measurably different, and also shows a way of producing circuits that are hard to understand, and that tell chips apart. We can in theory base a PUF on this observation. A challenge is an FPGA circuit, and the response is the output of that circuit when it is loaded into the FPGA.

As with the overclocking method, many challenges will produce responses that do not depend on the chip, while others will produce erratic responses. A genetic algorithm can be used to find challenges that meet our needs.

Environmental parameters are also likely to change the responses as is observed in [26], though it might be possible to vary environmental parameters during training to find challenges that are sufficiently robust to environmental parameters such as temperature [27].

Overall this method is neat, and shows that PUFs can be made. Unfortunately, it is impractical because the genetic algorithm takes a prohibitive time to run.

### 3.2.3 Delay Measurement

So far we have considered two ways of making a Silicon PUF. Both methods were very general, but both had similar problems: it is hard to find challenge-response pairs that actually differ from chip to chip, and it is hard to get reliable operation, particularly in presence of environmental variation (such as changes in temperature). We will now turn to a method that is less general but that we have better control over. The basic idea is to measure delays in a specially designed circuit to produce a PUF.

Figure 3-4: Measuring delays to get a PUF

The general architecture of a delay-based silicon PUF is shown in Figure 3-4. The main element is a parametrized delay circuit. When a rising edge is applied to the input of the delay circuit (1), it propagates through the delay circuit. After some amount of time that is a function of the challenge that is applied to the circuit, the rising edge arrives at the circuit's output (2). In the PUF, the delay circuit is coupled to a delay measurement circuit

that generates the rising edge, and measures the time until it emerges from the delay circuit. It outputs the delay as the response. As long as the delay circuit is complex enough, we have a good PUF candidate.

Many of the drawbacks that existed with previous circuits have now been solved. Any challenge now gives a response that changes from chip to chip, so we no longer need to look for challenges that stimulate some chip dependent behavior. Since the delay circuit is designed so that one rising edge at the input leads to a single rising edge at the output, the quantity that we are measuring is well defined; as long as the delay circuit is designed so that its delay is the same each time it is stimulated, we will be able to get consistent measurements.

#### **Environmental Parameter Compensation**

The problem that remains is robustness to environmental variations. Fortunately, it turns out (sections 3.3 and 3.4) that when temperature changes, delays of similar design vary proportionally to each other. Therefore, by measuring two different delays and dividing them by one another it is possible to get a value that is a lot less dependent on environmental parameters such as power supply voltage and temperature than the values that are being divided. We call ratios of two delays *compensated measurements*, and the operation of dividing delays by each other *compensation*.

We now have a viable silicon PUF candidate. In the next sections we go into the details of the delay measurement circuit and the delay circuit so that we have a complete story on how to build delay-based silicon PUFs.

## 3.2.4 Measuring a Delay

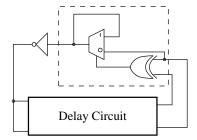

#### Self-Oscillating Loops

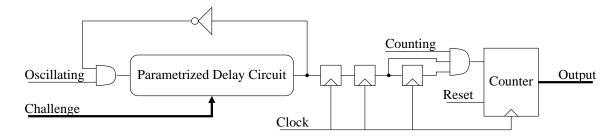

The main method that we have used to measure delays is to use the delay circuit to build a self-oscillating loop. We do this by inverting the output of the delay circuit and feeding it back into the delay circuit's input. This circuit spontaneously oscillates with a period approximately two times greater than the delay to be measured.<sup>3</sup> The period of the loop can easily be determined by counting the number of oscillations in a given amount of time as measured by some reference clock. Because of compensation, the reference clock doesn't even need to be calibrated, it need only be stable over short time-scales.

Figure 3-5 shows the details of the self-oscillating loop circuit. The Oscillating signal is used to turn the loop on or off. The output of the loop is synchronized to the reference clock by using two registers. Another register and an and gate are used to detect rising edges. The rising edges are then counted, as long as the Counting signal is high. To perform the measurement, the loop is turned on, the counter is reset using the Reset signal, Counting is put high for a predefined amount of time, and finally a frequency is read from the output

<sup>&</sup>lt;sup>3</sup>Since all we care about is getting a consistent measurement out of the chip, the fact that the loop period is only approximately twice the delay of the delay circuit doesn't bother us.

Figure 3-5: A self-oscillating loop to measure a delay

of the counter. Of course the clock must be at least two times faster than the loop for this circuit to function.

A few constraints on the delay circuit must be maintained for self-oscillating loops to work. Indeed, the edge that enters the delay circuit might get split into many competing edges inside the circuit. One of those edges will eventually cause the output of the delay circuit to change, which will almost immediately cause an opposite polarity edge to be applied to the input of the delay circuit. If some edges from the previous time through the loop are still present in the delay element, they could change the delay that is seen by the new edge. With a badly designed delay circuit, this could lead to chaotic variations in the delay, and unreliable responses.

This method leads to very precise measurements. Unfortunately, to get measurements with precisions of tens parts per million, hundreds of thousands of clock cycles must elapse during the measurement. Measuring delays is consequently a slow affair, which gets even longer when we start using vectorization (see Section 4.2).

#### Arbiters

To make delay measurement faster, we are trying to do direct delay measurements, which only run a single edge through the delay circuit. This is not a trivial task given that in our experiments, we have to measure the delays with precisions on the order of tens of picoseconds. An added advantage of not using an oscillating circuit, is that stable frequencies are particularly easy for an adversary to look for when he is trying to probe a circuit. This weakness could allow an adversary to bypass a CPUF's post-processing steps, such as the output random function (see Section 4.3).

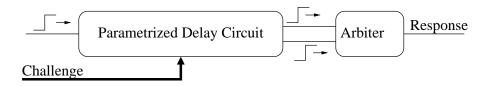

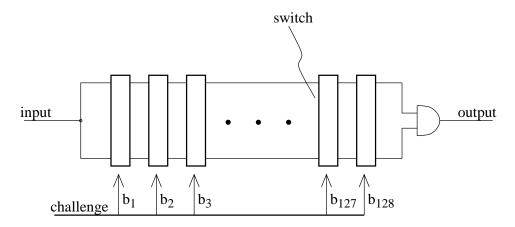

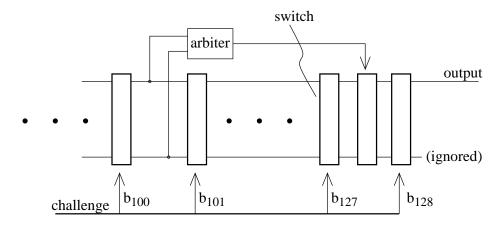

Daihyun Lim is currently running experiments in which, instead of measuring two delays and taking their ratio, two delays are simply compared. Two (possibly intermingled) delay circuits are excited simultaneously. An arbiter circuit at the output determines which rising edge arrived first and sets its output to 0 or 1 depending on the winner. Figure 3-6 shows an arbiter-based circuit.

Preliminary results show that the method works. The disadvantage of the method is that if for some challenge, one delay is consistently greater than another across chips, then

<sup>&</sup>lt;sup>4</sup>In fact, because the reference clock period must be less than half the loop period, it is better, for maximum precision, to count the number of clock ticks in a predefined number of oscillations of the loop rather than the number of oscillations of the loop in a certain number of clock ticks.

Figure 3-6: An arbiter-based PUF

the response will always be the same for that challenge. Fortunately, each measurement can be performed extremely fast, so it is possible to try many challenges in the time it would take to measure a single delay with a self-oscillating loop. In one experiment we have run, around 2 % of challenges have a response that changes between chips. This figure would be sufficient to make the arbiter circuit faster than the self-oscillating loop circuit despite having to try more challenges. With more control over delay circuit layout, we hope to get much more than 2 % of useful challenges.

### 3.2.5 Designing a Delay Circuit

Choosing the right delay circuit is the key to making silicon PUFs work. The delay circuit must be designed to have a consistent delay and be resistant to model building attacks.

To make model building difficult, it is tempting to try to reproduce the types of structures that appear in digital pseudo-random functions such as SHA1 [20] or MD5 [22], to make the relation between individual physical parameters and global delay hard to invert. Unfortunately, those functions are designed to have a cascade effect: if a single bit is changed at the input, one can expect half the output bits to change as a result. This chaotic behavior is contradictory with what we need to get reliable delay operation. With a chaotic analog circuit, any small fluctuation in the physical parameters would completely change the circuit output, making it useless for identification purposes (it might be usable as a random number generator, though).

Therefore, we will use the opposite approach. We will start from a circuit that gives reliable outputs, study it, and propose ways of making it harder to model.

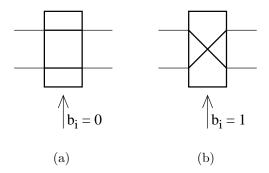

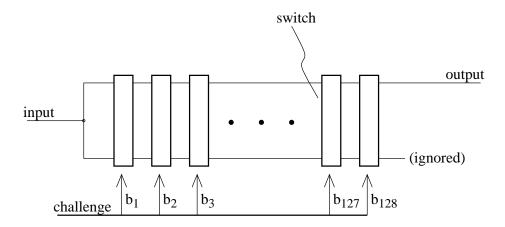

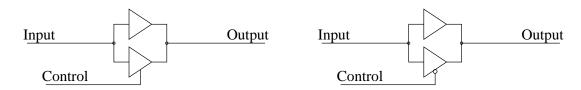

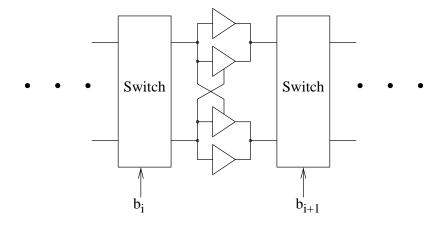

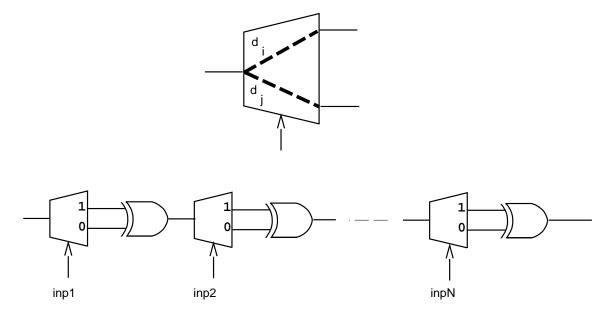

Our basic delay circuit is made up of a string of switch blocks. A switch block has two inputs, two outputs and a control bit. The value of the control bit determines if the inputs go straight through to the outputs, or if they are exchanged, as in Figure 3-7. The input of the delay circuit goes to both inputs of the first switch block. One of the outputs of the last switch block is used as the output of the delay circuit, the other is ignored (or possibly used as the other input to the arbiter circuit if we are doing direct measurement). Figure 3-8 shows the full circuit.

This circuit is interesting because each challenge selects a different path through the circuit, leading to an exponential number of paths. Of course, these paths are far from being independent of each other. In fact, for a k stage circuit, if we assume an additive delay model — the total delay of a path is the sum of the delays of the elements that make it up — then knowing 4k independent paths is sufficient to set up a linear system of equations, which, when inverted, would give all the elementary delays in this circuit.

Figure 3-7: When  $b_i = 0$  the paths go straight through, when  $b_i = 1$ , the paths are crossed.

Figure 3-8: The simple delay circuit

Combined with the methods discussed in Chapter 4, this circuit would actually be sufficient for any remote attacker. Nevertheless, just as we choose to use analog PUFs rather than physically obfuscated keys in Section 2.4, it would be nice to make the physical system that the PUF is based on intrinsically harder to model. We shall therefore present a number of tricks that make model building harder.

To date we do not know how much difficulty is added by these tricks if an additive delay model is assumed. What is certain is that, deviations from the additive delay model, and the input pseudorandom function that we introduce in Section 4.1, makes attacks even more difficult.

#### Variable delay buffers

Variable delay buffers can be used to make additive delay modeling much more difficult. Essentially they are delay elements that have a delay which depends on an auxiliary input. The subtlety is that no glitches must be introduced if the auxiliary input changes while an edge is propagating through the delay element, or else measurement reliability would decrease.

Figure 3-9: Variable delay buffers can be made with a buffer and a tristate buffer. The tristate buffer can be active-high as on the left, or active-low as on the right. Depending on the polarity of the edges and whether the variable delay buffer is active-high or active-low, competing edges will be brought closer together or farther apart.

Variable delay buffers can easily be made by combining a slow buffer (essentially a yes logic block) and a fast tristate buffer (a buffer that can have its output turned off) as in Figure 3-9. If the tristate buffer is off, the delay is long. If the tristate buffer is on, the delay is short. If the tristate buffer changes state while an edge is propagating through the buffer some intermediate delay results.

Since our basic circuit has two edges propagating through it simultaneously, we can use one of the edges as the auxiliary input to a variable delay buffer, and have the other path go through the buffer as is shown in Figure 3-10.

Figure 3-10: Variable delay buffers in a delay circuit

The presence of variable delay buffers makes additive delay modeling much harder as the delays of individual circuit elements are no longer constant. The adversary must make guesses about which state the variable delay buffer is in. In fact the variable delay buffers have a delay that can vary continuously in a certain range which makes the adversary's life even harder. It is interesting to note that variable delay buffers can be used to create non-monotonic behavior: a component in the circuit that becomes faster can make the overall circuit slower.

Great care must be taken when designing a circuit with variable delay buffers. They lead to circuits with complicated behaviors. If misused, a number of things can go wrong. The circuit can become chaotic, and therefore useless. If the variable delay buffers tend to make

the leading path get even further ahead than it already is, then the two competing paths will get well separated after just a few circuit stages and the remaining variable delay buffers will be in predictable states.

Overall, variable delay buffers seem like a powerful but potentially dangerous tool. A lot more research could be devoted to exploring delay circuits based on them.

#### Minimum and Maximum

A somewhat more controlled way of preventing a model building adversary from setting up linear systems of equations is to put max and min operators in the model he is building. For direct delay measurement, this can be done using an and-gate or an or-gate respectively. For self-oscillating loop circuits the task is a little harder as there are both rising and falling edges to take into account, we will see how to handle that case in Section 3.4.1.

Figure 3-11: Delay circuit with max operator

One way of using these operators to make model building harder is shown in Figure 3-11. A model building attacker doesn't know which path was selected by the and-gate, which forces him to produce two equations for each CRP he knows. An exponential number of possible systems of equations results when many CRPs are combined, unless some pruning strategy is found. For a while [9], our hope was that as long as our delay circuit was laid out in a way that preserved the symmetry between the two paths, and an input random function was used on the challenge, this circuit would be hard to break in the additive delay model. Recent unpublished work by Marten van Dijk shows that such a circuit is vulnerable to statistical attacks, even with an input random function. Perhaps incorporating more max and/or min operators in the circuit would thwart these attacks.

#### Arbiters

Yet another way of making modeling attacks harder is to have some of the switches be controlled by signals that are generated earlier on in the delay circuit. For example, Figure 3-12 shows how an arbiter can decide, part way through the circuit, which path is fastest so far, and set a switch further down the circuit based on that decision.

Figure 3-12: Adding internal variables with an arbiter. Note that for simplicity, this figure does not include the logic needed to reset the arbiter between edges.

The attacker's job is harder because he has no way of knowing what the arbiter's decision was. The drawback is that there are borderline cases where the edges arrive at the arbiter almost simultaneously. Those cases will lead to erratic responses. Therefore, the number of arbiters that can be placed in the circuit this way must remain limited.

### 3.2.6 Intertwining

In a CPUF, an invasive adversary must be prevented from tampering with the control algorithm. Our way of addressing this problem is to design the CPUF so that the control logic is protected by the physical system that the PUF is based on. That way, the adversary is forced to damage the physical system if he tries to tamper. In the case of silicon PUFs, we suggest that the top layer of wires above the control logic be devoted to delay wires, as shown in Figure 3-13. Those delay wires would then act as a shield for the underlying logic.

Figure 3-13: Control logic, protected by overlying delay wires

At this time, we do not have the means to test the difficulty of tampering with the control logic while leaving the PUF sufficiently intact. Attacks through the top of the chip are greatly hindered because the adversary must gain access to lower layers of the chip without damaging PUF wires. Unlike attacks against classical circuits that surround the

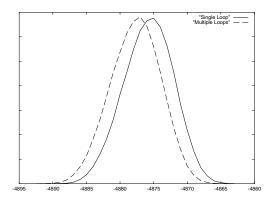

Figure 3-14: In this plot we show how multiple self-oscillating loops on the same IC interfere. The histograms show the frequency of the loop oscillating alone or with the seven other loops on the IC turned on. The frequency shift between these two situations is tiny compared with measurement noise.

chip with meshes, the adversary is detected as soon as the wire delay starts changing; he does not need to cut the wire completely to change the PUF.

Attacks through the bottom of the chip are not taken into account with this approach, but to date, invasive attacks on chips have concentrated on entering through the top. Entering through the bottom of the chip without destroying it seems much more difficult.

If the adversary opens the chip, but does not attempt to penetrate the PUF wires, he can try to make measurements of the signals flowing in the delay wires. Those measurements could help him build a model of the circuit. His task is particularly easy in the case of self-oscillating loop measurements. He simply needs to determine the frequency of the oscillation to know the output of the PUF before any post-processing (see Chapter 4). A possible solutions is to design the chip's packaging so that its removal will sufficiently change the delays of the PUF wires (preferably in an inhomogeneous way to make sure that compensated measurements won't cancel out the change). In the case of direct delay measurement, arranging to have a large number of delay elements in lower levels of the chip, so that the adversary can only get a limited amount of information for his model by direct measurement, is another possibility.

# 3.3 Experiments

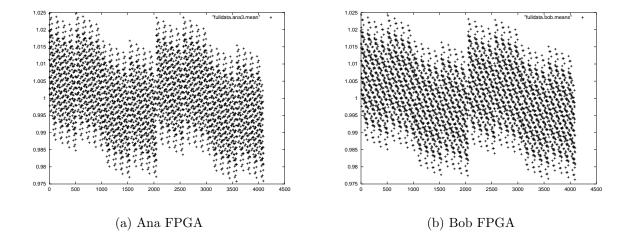

The rest of this chapter describes experiments that were performed using XC2S200 Field Programmable Gate Arrays (FPGAs)<sup>5</sup> on various delay circuits. FPGAs are an example of a high-volume part where the manufacturing process is tuned to produce ICs that are as identical as possible in order to maximize yield and performance. Our experiments indicate that even a highly-optimized manufacturing process designed for predictability has enough variability to enable reliable identification.

<sup>&</sup>lt;sup>5</sup>The exact components that were used were the XC2S200PQ208-5.

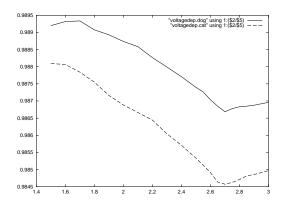

Figure 3-15: This plot shows compensated measurement dependency on power supply voltage. The dependency for 1% changes in supply voltage is small enough for our purposes. Interestingly, by running the FPGAs near the 2.7V extremum, it might be possible to further reduce the voltage dependency.

In all our experiments, we compare delays across two or more FPGAs with each FPGA being programmed by exactly the same personality matrix. This means that each FPGA has exactly the same logic circuit, and moreover the circuit is laid out in the exact same locations on each FPGA. Therefore, these FPGAs can be viewed as copies of the same IC.

First we consider a non-parametrized delay circuit, just to see how much variability is present, in Section 3.3.1. Then, in Section 3.3.2 we try to evaluate how valid the additive delay model is, using the simplified circuit in Figure 3-18. Finally, a circuit that might actually provide enough security for a real application is presented in Section 3.4.

# 3.3.1 Quantifying Inter-Chip Variability

In our first experiment, each FPGA is equipped with 8 self-oscillating loops, the circuit for which is shown in Figure 3-5. Each loop is made up of 32 buffers<sup>6</sup> and an inverter. We determine the frequencies of the loops by measuring the number of oscillations they make during a certain period of time (typically  $2^{20}$  cycles of an external 50 MHz oscillator). The period of the loops is on the order of 60ns.

We ran various experiments to quantify measurement errors, inter-FPGA variation, variation due to ambient temperature and variation due to power supply voltage variations. To summarize our findings, the following standard deviations are given in parts per million (ppm). A deviation of n ppm around a frequency  $f_0$  corresponds to a deviation of  $\frac{nf_0}{10^6}$ . These deviations correspond to measurement across several FPGAs.

Here are the main results:

1. Consecutive measurements of the same delay produce slightly different results because

<sup>&</sup>lt;sup>6</sup>In this context, a buffer is simply a logic gate that copies its input to its output with a short delay. They are usually used to amplify signals.

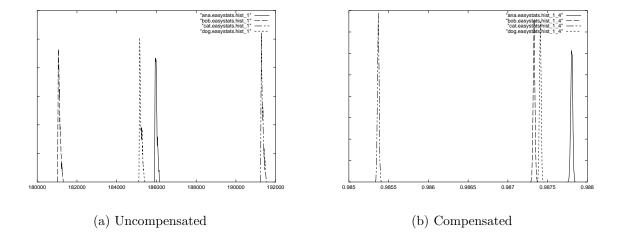

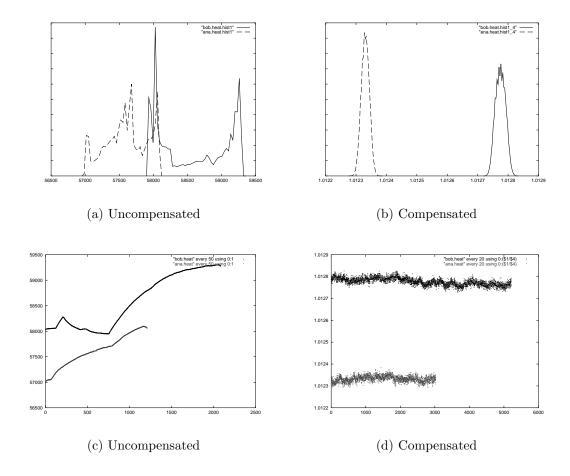

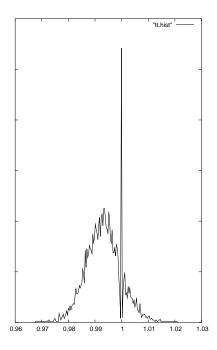

Figure 3-16: These histograms show the relation between measurement error (width of a peak) and inter-FPGA variation (each peak is for a different FPGA), with and without compensation. Clearly information about the FPGA's identity can be extracted from these measurements.

of measurement inaccuracy inherent in the loop circuit. The standard deviation of this measurement error with compensated measurement is 30 ppm.