## A High Performance Interface for a 40-bit Machine on the NuBus

by

David C. Douglas

Submitted to the

DEPARTMENT OF ELECTRICAL ENGINEERING AND COMPUTER SCIENCE

in partial fulfillment of the requirements

for the degrees of

BACHELOR OF SCIENCE

and

MASTER OF SCIENCE

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

May 1986

© David C. Douglas 1986

The author hereby grants to MIT permission to reproduce and to distribute copies of this thesis Moccument in whole or in part.

| Signature of Author | r                                                                        |

|---------------------|--------------------------------------------------------------------------|

|                     | Department of Electrical Engineering and Computer Science<br>May 9, 1986 |

| Certified by _      | · · · · · · · · · · · · · · · · · · ·                                    |

|                     | Thesis Supervisor: Professor Stephen A. Ward                             |

| Certified by _      | Company Supervisor: Steve Krueger                                        |

| Accepted by $\_$    |                                                                          |

|                     | Arthur C. Smith, Chairman                                                |

Committee on Graduate Students

MASS. INST. TECH.

JUL 2 3 1986

LIBRARIES

**Archives**

A High Performance Interface for a 40-bit Machine on the NuBus

bv

David C. Douglas

Submitted to the Department of Electrical Engineering and Computer Science on May 9, 1986, in partial fulfillment for the degrees of Master of Science and Bachelor of Science in Electrical Engineering.

Abstract

In order to achieve full 32-bit capability, a processor based on a tagged architecture must support word sizes greater than 32 bits. While it is desirable to maintain compatibility with existing 32- and 16-bit devices, problems arise in transferring data from the smaller word size of these devices to the larger word size of the tagged processor. Many of these problems are avoided if the tagged processor can be efficiently interfaced to an existing standardized bus. A high speed memory interface allowing efficient use of a 40-bit processor on the 32-bit NuBus is examined. Two functional designs are presented and evaluated through simulation and numerical analysis.

Thesis Supervisor: Stephen A. Ward

Title: Associate Professor, Computer Science

Company Supervisor: Steve Krueger

Senior Member of Technical Staff, Texas Instruments

## Acknowledgements

I would like to thank my thesis advisor, Prof. Steve Ward, who taught me that working with computers and having fun didn't have to be mutually exclusive activities, and also for his attention, advice, and help on this work. Also at MIT, I'd like to thank Sharon Thomas for her help and encouragement. I would like to thank all of the many people I worked with at Texas Instruments, where the work for this thesis was conducted. In particular, Steve Krueger, Mike Amundsen, and Pat Bosshart for being my technical mentors, and Gene Matthews for all of his support and guidance.

I would like to thank my parents, grandparents, and my brother Pete for their constant love and encouragement. I would like to thank Pam, who makes all of this fun, and also all of my great friends and fellow students at MIT who've helped me keep my sanity here.

I would like to dedicate my thesis to the memory of my grandfather, Charles Wilken, who taught me the value of hard work, and to the memory of Eric Ritland, Harvard '86, a close friend who passed away while I was completing the work for this paper.

## Contents

| Int | roduction                            |                                                                                                                                                                                                                                                                                                                                                                                     |

|-----|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1 |                                      |                                                                                                                                                                                                                                                                                                                                                                                     |

|     | Notation                             | 10                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.2 | Overview of Div3 Method              | 11                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.3 | The Separate Tag Method              | 12                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.4 |                                      | 12<br>13                                                                                                                                                                                                                                                                                                                                                                            |

| Ra  |                                      | 17                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1 | Compatibility with Existing Hardware |                                                                                                                                                                                                                                                                                                                                                                                     |

| 2.2 |                                      | 17                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                      | 18                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                      | 18                                                                                                                                                                                                                                                                                                                                                                                  |

|     | Diode Hendleis                       | 18                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                      | 19                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.3 | Local Cache Memory                   | 19                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.4 | Summary                              | 20                                                                                                                                                                                                                                                                                                                                                                                  |

| The | Div3 Method                          | 21                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.1 |                                      | 21                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.2 |                                      | 21<br>25                                                                                                                                                                                                                                                                                                                                                                            |

|     |                                      | 25<br>25                                                                                                                                                                                                                                                                                                                                                                            |

|     |                                      | 30                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.3 |                                      | 33                                                                                                                                                                                                                                                                                                                                                                                  |

|     |                                      | 34                                                                                                                                                                                                                                                                                                                                                                                  |

|     | 1.4 Ran 2.1 2.2 2.3 2.4 The 3.1 3.2  | 1.4 Performance Evaluation  Range of Applications  2.1 Compatibility with Existing Hardware  2.2 Virtual Memory Systems  2.2.1 Address Mapping  2.2.2 Block Transfers  2.2.3 Unmapped Accesses  2.3 Local Cache Memory  2.4 Summary  The Div3 Method  3.1 Bword Organization  3.2 Virtual Memory Management  3.2.1 Address Pages  3.2.2 Transfer Pages  3.3.1 Div3 Cache Addressing |

|   |            | 3.3.2   | Update Policies                             | 37 |

|---|------------|---------|---------------------------------------------|----|

|   |            | 3.3.3   | Small Caches and Buffers                    |    |

|   | 3.4        | Perfo   | nance of the Div3 Method                    | 41 |

|   | 3.5        |         | nary of Div3                                |    |

| 4 | Th         |         | rate Tag Method                             |    |

|   | 4.1        |         | d Organization                              | 45 |

|   | 4.2        |         | ory Management                              | 45 |

|   |            | 4.2.1   |                                             | 48 |

|   |            | 4.2.2   | Virtual Memory Requests                     | 50 |

|   | 4.3        |         | Unmapped Memory Requests                    | 54 |

|   | 4.4        | Perfor  | mg with the Separate Tag Method             | 55 |

|   | 4.5        |         | mance of the Separate Tag Method            | 57 |

|   | 2.0        | ~ umm   | nary of the Separate Tag Method             | 59 |

| 5 | Exa        | ample l | Implementations of the Two Methods          | 61 |

|   | 5.1        | The T   | I Explorer                                  | 61 |

|   |            | 5.1.1   | The Explorer Virtual Machine Implementation | 62 |

|   |            | 5.1.2   | The Explorer Virtual Machine Model          | 63 |

|   |            | 5.1.3   | The 40-bit Explorer Virtual Machine Model   | 64 |

|   | <b>5.2</b> | Simula  | tion Techniques                             | 64 |

|   |            | 5.2.1   | The Simulator                               | 65 |

|   |            | 5.2.2   | Access Time Computation                     | 65 |

|   | 5.3        | Results | s from the 32-bit Explorer                  | 70 |

|   | 5.4        |         | s from the Div3 Method                      | 70 |

|   | 5.5        |         | s from the Separate Tag Method              | 71 |

| 6 | Sun        | nmary   |                                             | 90 |

|   | 6.1        | Hardwa  | are                                         | 80 |

|   |            |         | The Div3 Hardware                           | 80 |

|   |            |         | The Separate Tag Method                     | 80 |

|   | 6.2        |         | nance                                       | 82 |

|   |            |         | The Explorer                                | 83 |

|   |            |         |                                             |    |

| ,     |       |                              |    |

|-------|-------|------------------------------|----|

| , ,   | 6.2.2 | The Div3 Method              | 84 |

|       | 6.2.3 | The Separate Tag Method      |    |

| 6.3   | Concl | usion                        | 87 |

|       | 6.3.1 | Why 40 Bits on a 32-bit Bus? | 87 |

|       | 6.3.2 | Cost/Perfomance Analysis     |    |

| A App | endix | A: Raw Results               | 90 |

# List of Figures

| 1.1  | Computing the Average Memory Access Time of a General Architec- |           |

|------|-----------------------------------------------------------------|-----------|

|      | ture                                                            | 14        |

| 1.2  | General Organization of the Virtual Memory Hardware             | 15        |

| 3.1  | Bword Alignment in a 4-Word Transfer Block                      | 22        |

| 3.2  | Physical Address Formats for Bword Addressing                   | 23        |

| 3.3  | Realignment Buffer                                              | 24        |

| 3.4  | Calculating the NuBus Block Address and Block Offset            | 28        |

| 3.5  | Example Address Translation for 3 Different Block Sizes         | 29        |

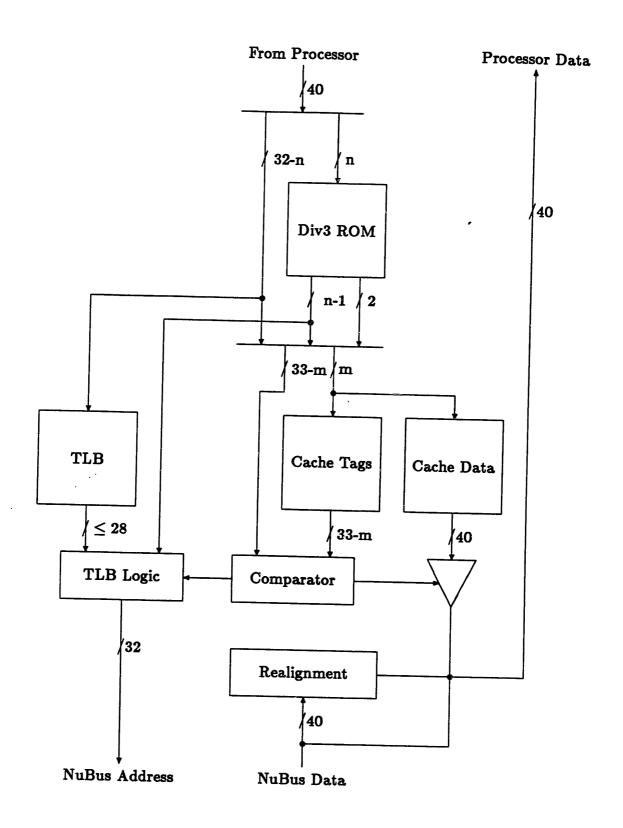

| 3.6  | Organization of the TLB and Div3 ROM                            | 31        |

| 3.7  | Two Cache Addressing Schemes                                    | 35        |

| 3.8  | Caching Realignment Buffer                                      | 40        |

| 3.9  | Computing the Average Access Time of the Div3 Method            | 42        |

| 3.10 | Functional Diagram of a General Div3 System                     | 43        |

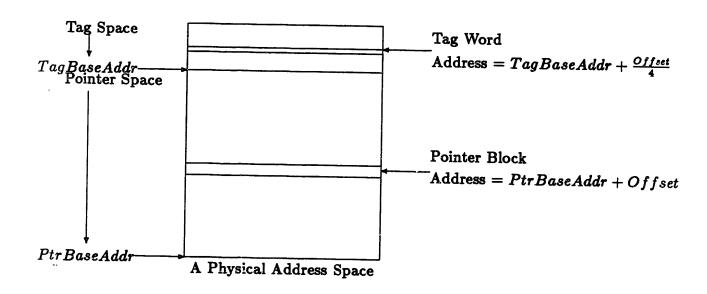

| 4.1  | Arrangement of the Pointer and Tag Space                        | 46        |

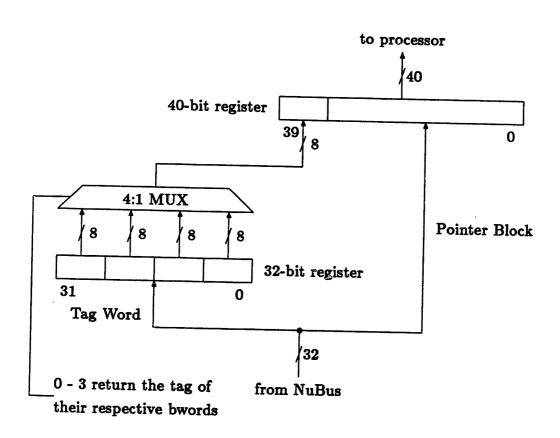

| 4.2  | Realignment Buffer                                              | 47        |

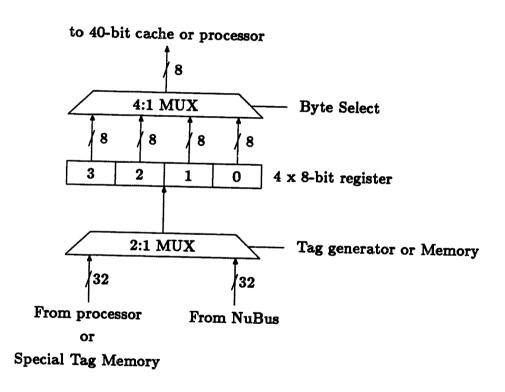

| 4.3  | An Example of Automatic Tag Generation Hardware                 | 49        |

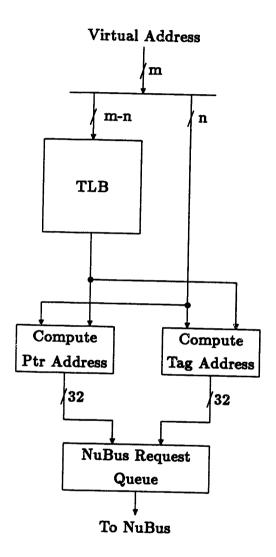

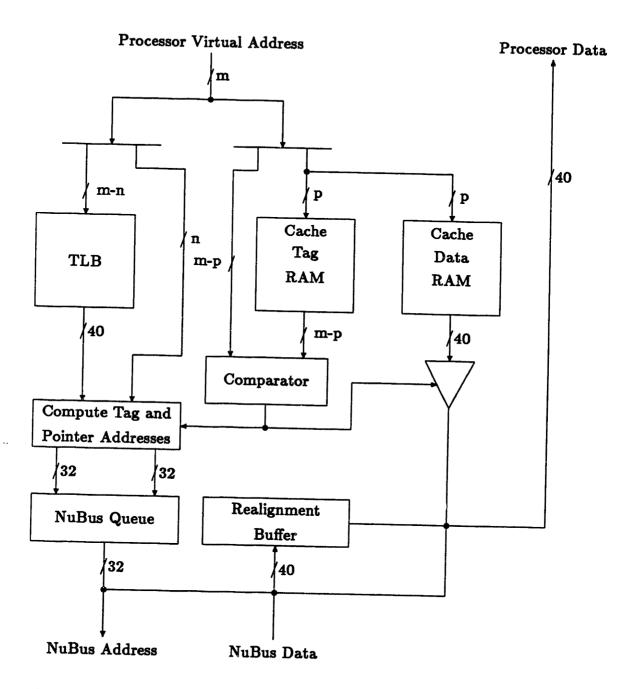

| 4.4  | General Virtual Memory System of the Separate Tag Method        | 51        |

| 4.5  | Format of a Translation Lookaside Buffer Entry                  | <b>52</b> |

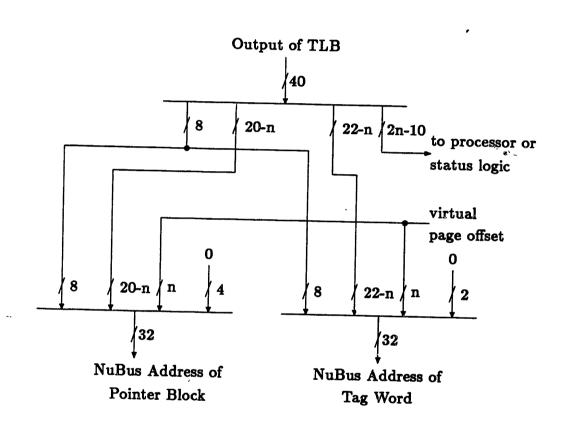

| 4.6  | Physical Page Generation Using the Output of the TLB            | 53        |

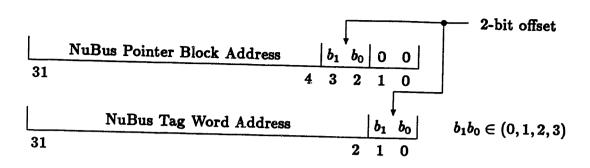

| 4.7  | Method of Addressing Single Bwords                              | 54        |

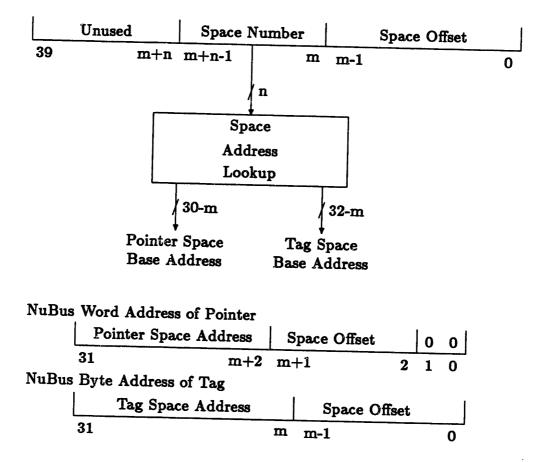

| 4.8  | Unmapped Bword Address Generation Using Space Lookup            | 56        |

| 4.9 | Computing the Average Memory Access Time of a the Separate Tag |    |

|-----|----------------------------------------------------------------|----|

|     | Method                                                         | 58 |

|     | Organization of the Separate Tag Virtual Memory Hardware       |    |

| 5.1 | Average Access Time (ns) of the Store-In Policy                | 68 |

## List of Tables

| 3.1         | Page Sizes in Words and Bwords                                        | 25  |

|-------------|-----------------------------------------------------------------------|-----|

| 3.2         |                                                                       | 28  |

| 3.3         |                                                                       | 33  |

| 5.1         | Memory Access Times over the NuBus                                    | 67  |

| 5.2         |                                                                       | 72  |

| 5.3         | Average Access Time of Explorer using Write Through                   | 73  |

| <b>5.4</b>  | Average Access Time (ns) of the Div3 Method using Store-In            | 74  |

| 5.5         | Average Access Time (ns) of the Div3 Method using Write-Through       | 75  |

| 5.6         | Average Access Time (ns) of the Separate Tag Method: Store-In         | 76  |

| 5.7         | Average Access Time (ns) of the Separate Tag Method: Store-In         | 77  |

| 5.8         | Average Access Time (ns) of the Separate Tag Method: Write-Through 78 | * * |

| 5.9         | Average Access Time (ns) of the Separate Tag Method: Write-Through 79 |     |

| A.1         | Read Miss Ratios for the Explorer                                     | 91  |

| <b>A.2</b>  | Write Miss Ratios for the Explorer                                    | 92  |

| <b>A.3</b>  | Fetch Miss Ratios for the Explorer                                    |     |

| A.4         | Read Miss Ratios for the Div3 Cache                                   | 93  |

| A.5         | Write Miss Ratios for the Div3 Cache                                  | 94  |

| <b>A.</b> 6 | Fetch Miss Ratios for the Div3 Cache                                  | 95  |

|             | The second for the Diag Cache                                         | 96  |

### Chapter 1

### Introduction

This paper describes and analyzes the virtual machine changes necessary to implement a 40-bit processor on the NuBus<sup>1</sup>. The goals of the designs in this paper are to minimize the average access time of virtual memory requests from the 40-bit processor to existing NuBus devices. Two approaches will be presented and an example implementation of them on an existing machine will be described. The first approach is based on storing 3 40-bit words per 4 word block. The second is based on the storage of 4 40-bit words in a 4 word block and one extra word. The rest of this chapter will discuss the notation used in this paper, give an overview of the two approaches, and discuss how their performance will be evaluated. The next chapter will discuss the range of machine architectures to which these approaches are applicable. The next two chapters will describe the two approaches in detail, the following chapter will present an example of the necessary changes and subsequent performance of an existing 32-bit machine (the Texas Instruments Explorer Lisp Machine<sup>2</sup>) following a hypothetical upgrade to 40 bits. The final chapter will summarize the results.

<sup>&</sup>lt;sup>1</sup>Nubus is a trademark of Texas Instruments, Inc.

<sup>&</sup>lt;sup>2</sup>Explorer is a trademark of Texas Instruments, Inc.

#### 1.1 Notation

This paper will use the following notations which are consistent with those described in the NuBus Specification. Byte will refer to a group of 8 bits, half-word to 16 bits, and word to 32 bits. In this paper, bword will refer to groups of 40 bits, this being short for "big word". The least significant bit (LSB) of a group will always refer to bit 0, while the most significant bit (MSB) will refer to bit n-1 of a group n bits long. Bit strings will always be listed from the MSB to the LSB, left to right. The hardware which occupies a NuBus slot will be referred to as a NuBus module.

In reference to bwords, pointer will designate the lower 4 bytes or 32 bits. The upper byte will be called the tag. These terms are usually used in reference to a tagged architecture, and are used throughout this paper in anticipation of the tagged architecture example in Chapter 5.

In the cache sections, the word block is used for what is referred to as either a block or a line in cache literature. References to caches as local mean that the cache is in the same NuBus module as the processor, i.e. a NuBus access is not necessary in order to obtain data from the cache. The write-back update policy will be referred to as store-in. All other cache terms try to comply with common usage (see [Smit82]). Cache performance statistics will be represented as probabilities, allowing more formal representation and usage. The following conventions will be used: P(A) will stand for the probability of event A,  $P(A \mid B)$  will signify the probability of event A given event B, and  $P(A \cdot B)$  will signify the probability of both event A and event B.

This paper frequently makes references such as the necessary changes or the only unit which will change without specifying what the object is changing from (or sometimes to). It should be assumed that such phrases are referring to the changes necessary in converting a 32-bit processor to a functionally equivalent 40-bit architecture.

Variables in equations will often use the *prime* mark (') to indicate that the value of the variable differs from that of its original use in describing the Explorer

performance.

### 1.2 Overview of Div3 Method

The Div3 Method is based on a transfer unit of 4 words containing three bwords and an extra byte which can be used to serve a variety of useful purposes. The name is derived from the fact that a factor of 3 is introduced into the addressing scheme, causing a divide-by-3 to be done implicitly or explicitly at some point in the virtual address translation process. The performance of an implementation of this method will depend heavily on how efficiently this translation is done.

The pertinent design variables in this method include the following: the organization of the bwords within the 4 word block, the size of the addressable page, the size of the transfer page, the cache organization, and the method of address translation. These variables are not independent, with the actual number of efficient, feasible combinations being quite small. The effects of different designs on performance are reflected in trade-offs between cache access speed, map access speed, hardware complexity, and transfer efficiency. These effects will be discussed in the chapter describing the general Div3 Method and will be quantified in the example in a later chapter.

### 1.3 The Separate Tag Method

The Separate Tag Method is based on the storage of 4-bword pointer fields in a 4-word block, and their corresponding tag fields together in 1 word. Physical and disk address spaces are divided into two subspaces – pointer space and tag space. These are identified by pointer and tag space base addresses. The offsets of a pointer block (four pointer words) and its corresponding tag word (four tags) into their respective address spaces are related by a simple binary operation.

An implementation of this method on a 40-bit machine will be very similar to the memory interface of a 32-bit version of the same processor. The only major change requires the virtual memory system to perform two complementary operations, one each in pointer and tag space, for each virtual memory request. Similar performance estimates will also be made for this method.

Besides the necessary virtual machine changes and their performance effects, implementations of the two methods differ in their ability to share memory with non-40-bit devices. The Separate Tag Method can communicate easily with 8-, 16-, and 32-bit processors by using pointer space as shared memory. However, in the Div3 Method, the non-40-bit device would have to be given some knowledge of how bwords are arranged within the virtual and physical address spaces. This may or may not be an design consideration, depending on the proposed use of the 40-bit processor. This topic will be reintroduced later in more detail.

### 1.4 Performance Evaluation

In using a 40-bit processor on a 32-bit bus, one must pay an unavoidable performance penalty when accessing data over the bus. This is reflected in an increase in both the time to access memory from the processor, and in the time to process a page fault in a virtual memory implementation. If a cache block size other than a power of 2 is used, as in the Div3 Method, the hit ratio of a local cache may also be effected by the change from 32- to 40-bit words. In an attempt to capture all of these effects in one measurable value, this paper will use the average access time of virtual memory requests as a basis for evaluating performance.

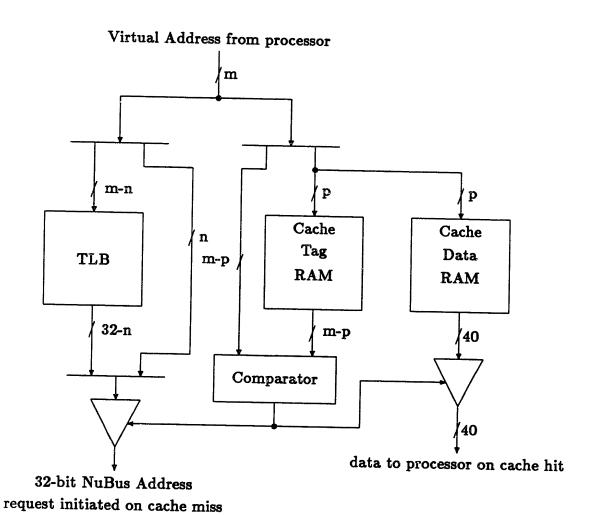

The average access time of a virtual memory request on a general architecture can be expressed by the definitions and resulting equation shown in figure 1.1. These equations are based on the general virtual memory system shown in figure 1.2. Note that it is assumed that the cache and TLB are accessed in parallel, and that this is reflected in equation 1.1. Other cache/TLB arrangements can easily be represented by this equation by choosing appropriate values for  $t_c$  and  $t_{tlb}$ . Note also that the processing time  $t_{pgf}$  overlaps  $t_c$  and  $t_{tlb}$  in equation 1.1. The delay  $t_{tlb}$  will be considered to have a second order effect on the value of  $t_{pgf}$  so it has been

$$P(h_c) = probability \ of \ a \ cache \ hit \ on \ a \ local \ cache$$

$P(m_c) = probability \ of \ a \ miss \ on \ a \ local \ cache = 1 - P(h_c)$

$t_c = access \ time \ of \ a \ local \ cache$

$P(h_{tlb} \mid m_c) = probability \ of \ a \ hit \ on \ the \ translation \ lookaside \ buffer \ given \ a \ local \ cache \ miss$

$P(m_{tlb} \mid m_c) = 1 - P(h_{tlb} \mid m_c)$

$t_{tlb} = access \ time \ of \ the \ translation \ lookaside \ buffer$

$t_{mem} = access \ time \ of \ block \ from \ main \ memory$

$t_{pgf} = time \ to \ process \ a \ page \ fault \ on \ a \ tlb \ miss$

$t_{avg} = average \ access \ time \ of \ a \ virtual \ memory \ request$

$t_{avg} = P(h_c) * t_c + P(m_c) * [P(h_{tlb} \mid m_c) * (t_{mem} + t_{tlb}) + P(m_{tlb} \mid m_c) * t_{pgf}] \ (1.1)$

Figure 1.1: Computing the Average Memory Access Time of a General Architecture included implicitly in that value instead of explicitly.

Each of these terms can be expanded as necessary to reflect a particular architecture. Such cases would include architectures with a heirarchy of local caches, multiple actions resulting from a TLB miss, a cache using various update policies, or a cache which handles instructions separate from data. Other cases involve the expansion of the  $t_{pgf}$  and  $m_{tlb}$  terms.

The terms  $P(h_{tlb} \mid m_c)$  and  $P(m_{tlb} \mid m_c)$  can be simplified in the following manner:

$$\mathbf{P}(h_{tlb} \mid m_c) = 1 - \mathbf{P}(m_{tlb} \mid m_c) \tag{1.2}$$

$$P(m_{tlb} \mid m_c) = \frac{P(m_{tlb} \cdot m_c)}{P(m_c)}$$

(1.3)

This paper will assume that the main memory is sufficiently large compared to the cache that:

$$\mathbf{P}(m_{tlb} \cdot m_c) = \mathbf{P}(m_{tlb}). \tag{1.4}$$

Certainly, for any system a sequence of events can be invented in which a data object is in the cache but the physical page on which it resides has been flushed from main

Figure 1.2: General Organization of the Virtual Memory Hardware

memory. It will be assumed that such occurrences are infrequent enough to have no statistical impact on the outcome of these equations. paper which justifies this. Combining equations 1.2, 1.3, and 1.4, it is found that:

$$\mathbf{P}(m_{tlb} \mid m_c) = \frac{\mathbf{P}(m_{tlb})}{\mathbf{P}(m_c)},\tag{1.5}$$

and

$$\mathbf{P}(h_{tlb} \mid m_c) = 1 - \frac{\mathbf{P}(m_{tlb})}{\mathbf{P}(m_c)}. \tag{1.6}$$

Similar substitutions will be used throughout this paper.

Performance comparisons will be made between the two 40-bit methods and a 32-bit processor on the NuBus. The 32-bit machine is included as a basis for comparisons, assuming that its perfomance is equivalent to that of a 40-bit machine on a 40-bit bus, both running identical access sequences. Specific changes to equation 1.1 will be discussed at the end of the chapters which describe the methods.

### Chapter 2

## Range of Applications

This chapter discusses the range of 40-bit virtual architectures which are supported by the designs in this paper. By supporting these architectures, these designs should have applications to a wide range of 40-bit machines. If a given application does not require the support of some or any of the features described in this chapter, aspects of the designs may be simplified of left out altogether.

### 2.1 Compatibility with Existing Hardware

Except in some multiprocessor applications, the designs in this paper require no changes to any existing NuBus devices except the 40-bit processor. Unaffected devices include the NuBus itself, NuBus memory boards, and any other NuBus based peripheral devices. No changes will be required of other processors unless they are intended to share memory with the 40-bit processor. The extent of these changes will depend on the 40-bit method used. All 40-bit processor changes will be noted in the designs, and some notes on the complexity of these changes will be added. All changes can be implemented using commercially available parts, and are easily implemented with semi-custom or custom IC's.

### 2.2 Virtual Memory Systems

All designs in this paper support a general virtual memory system through the following operations. First, the designs support the dynamic, consistent mapping of virtual addresses onto locations in physical memory. This occurs at the word or bword level. Second, the designs support the transfer of sections of memory between different physical locations or devices, in particular page and disk block transfers. Finally, the designs support unmapped accesses of any memory location. The following sections will discuss each of these operations separately.

#### 2.2.1 Address Mapping

The designs all support the dynamic, consistent mapping of virtual addresses to physical bwords. This means that, even though the physical address of a data object may change over time, it must always be accessible by its virtual address. This operation is among the hardest to meet in implementing a 40-bit machine on a 32-bit bus. The following points about this operation should be noted. First, because of the size difference, a virtual address cannot translate into a single physical address, and a physical address cannot alone represent a virtual address. Second, a physical word may contain parts of one or many virtual bwords, or may never contain any at all. Finally, contiguous, sequential physical words do not necessarily have to represent sequential virtual addresses, even within a page. The address mapping operation supported by these designs guarantees that a set of virtual addresses will always return the same data objects.

#### 2.2.2 Block Transfers

The designs also allow the mapping and transfer of blocks or groups of bwords. The basic operation of this type is virtual memory paging, although I/O transfer blocks, and disk block or sector transfers are also supported by this type of operation. The designs are all compatible with page mapping support such as TLB's and the information necessary to maintain page and block mapping. This includes

the possibility that some portions of these data structures are also stored in virtual memory due to their size. Again, the incompatibility in word sizes presents some anomalies. First, an integral number of bwords does not necessarily occupy a convenient number of words. For this reason, designs may sometimes transfer words which are never used, but are transfered to simplify the management of blocks of bwords. Second, because of the problems described in the last section, knowing the address of a block of bwords does not give one the addresses of the elements of the block. These problems are dealt with differently by the two methods.

#### 2.2.3 Unmapped Accesses

These designs allow the processor to bypass the TLB and access NuBus locations, including memory, with physical addresses. These will be called unmapped accesses throughout this paper. This is necessary in order to support boot strapping operations, I/O, and DMA type operations. Other operations which fall below the top level of the virtual architecture also may require unmapped accesses. These include page fault and interrupt handling. Support of this operation requires the ability to access, without hardware support, a single bword using its virtual address. The designs guarantee the ability to obtain the physical addresses of the bword parts from the data in the TLB, and to obtain the bword in a maximum of two NuBus transactions. By obtaining the exact byte and word addresses of the parts of a bword, the unmapped write of a single bword can be done without doing a read to maintain the integrity of neighboring bwords. This is also an important factor in handling mapped writes in most cache organizations.

### 2.3 Local Cache Memory

Being a crucial part of their efficiency, the designs of this paper fully support local cache memories. For speed purposes, the caches in these designs are addressable with virtual addresses, or in the worst case, virtual addresses which have undergone a single level of translation. All general cache design parameters are supported, including address blocks, multiple set sizes, replacement policies, and update policies. The following paragraphs will discuss a couple of these in detail.

In order to reduce the size of the memory used to store cache tags, it is common to store a tag for every n words, where n is the block size or number of words transfered into the cache at a time. Notice that in no case is every value of n possible, but is instead a member of the set of values represented by equation 2.1.

$$n = c * 2^{i}, i \in \{0, 1, 2...\}$$

(2.1)

In most designs, c has a value of 1. For the designs in this paper, however, bword storage formats further restrict the possible values of n. For the Div3 Method, c has a value of 3, and for the Separate Tag Method a value of 4.

In implementing update policies, the problem of updating single bwords appears again. If a write-through or store-and-invalidate update policy is used, then on every write the corresponding bword in physical memory has to be updated. If a store-in policy is used, then the dirty words or transfer block must be written out to physical memory when that block is flushed. In either case, it is undesirable to have to write out an entire block in order to update one bword in primary memory. On the other hand, one would want to write to memory without complex hardware support. The tradeoffs between these two approaches will be more apparent as the designs are presented.

#### 2.4 Summary

This chapter has shown the architectural features which are supported by the designs of this paper. They also represent the areas in which many designs fail as potential solutions to the problem of a 40-bit machine on the NuBus. As the two methods are presented, the ways in which these methods handle these problem areas will be highlighted. At those times, it will be apparent which portions of the methods have been included to implement these features. These portions of the methods can then be removed if the feature is not required.

### Chapter 3

### The Div3 Method

The Div3 Method is based on the NuBus block transfer of 4-word blocks containing 3 bwords. The following sections will describe a series of implementations of this method which retain the speed advantages of fetching 4-word blocks, while overcoming the difficulties of operating a virtual memory system in this environment. The first section will discuss an organization of bwords within the 4-word block, and will also introduce the hardware necessary for realigning bwords once they are obtained over the NuBus. The next section will discuss the changes which will be necessary to a virtual memory system in order to support the odd block sized introduced by the factor of 3. Cache organizations in the Div3 Method will then be discussed followed by a description of the changes which are necessary to equation 1.1 in order to quantify the performance of the Div3 Method.

### 3.1 Bword Organization

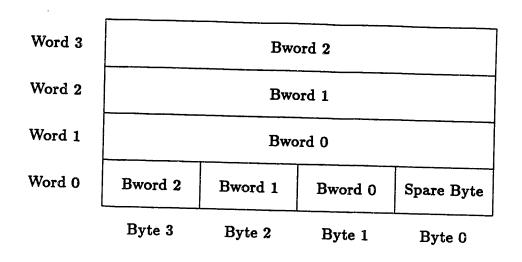

Figure 3.1 shows the alignment of 3 bwords within the 4-word transfer block which will be used by the Div3 Method. This arrangement has been selected due to its logic and time saving effects. The extra byte and a byte from each of the three bwords occupy the first word. These are followed by the remaining parts of the 3 bwords, each occupying a word. The byte from each bword which is placed in the first word of the transfer block can be either the first or last byte of the bword

Figure 3.1: Bword Alignment in a 4-Word Transfer Block

without loss of simplicity. Use of any other byte complicates the realignment buffer – the hardware which reorganizes bwords from their parts. The rest of this paper will use the case where the high order byte (the tag field) is stored separate from the low word (pointer field).

When a transfer block is read into the processor from the NuBus, it is desirable to obtain a bword on every cycle after the first one. In this way data can be read out of the realignment buffer in parallel with the last words being read in. For many potential uses of the extra byte in the transfer block it would also be desirable for it to be read in first. Such uses include error correction, caching information, and multiprocessing data consistency information. For these reasons, the extra byte and a byte from each bword have been placed in the first word of the transfer block.

This bword organization also simplifies the addressing of single bwords within the transfer block. No matter what organization is used, at least two memory accesses are required to access a single bword from the block. Physical bword addresses are easily changed to forms which allow them to access the bword through a word access and a byte access, or the whole transfer block through a single block address. Figure 3.2 shows how this is accomplished. The next section will describe how virtual addresses are translated into physical addresses of this form.

Figure 3.2: Physical Address Formats for Bword Addressing

If memory must be shared with 16- or 32-bit NuBus processor, then the page should be marked as non-lisp and the tag fields of the three bwords will be left empty. Optionally, automatic tag generation hardware similar to that described with the Separate Tag Method could be used in support of this type of page. It should be noted, however, that the other processor must be given knowledge of this format.

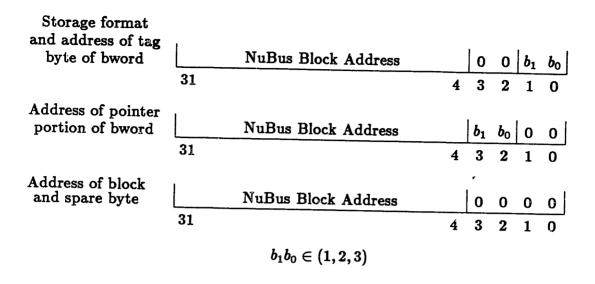

The realignment buffer is designed to allow both single bword and 4-word block transfers to occur without complex control logic. The functional diagram in figure 3.3 gives an example implementation.

It will be assumed that the cache will be responsible for organizing the bwords into the transfer block when they are being written over the NuBus. Since the cache must then have access to the tags all at once, then it will also be advantageous to also give the processor access to this tag word. This requires little hardware and may be especially useful for activities such as garbage collection.

Figure 3.3: Realignment Buffer

| Number of bits    | Number of bwords | Number of words       |

|-------------------|------------------|-----------------------|

| in offset address | addressed        | necessary for storage |

| 7                 | 128              | 171                   |

| 8                 | 256              | 372                   |

| 9                 | 512              | 683                   |

| 10                | 1K               | 1366                  |

| 11                | 2K               | 2731                  |

Table 3.1: Page Sizes in Words and Bwords

### 3.2 Virtual Memory Management

This section describes how the Div3 Method translates virtual bword addresses into physical addresses of the storage format shown in figure 3.2. By storing 3 bwords per transfer block, a factor of 3 has been introduced into the mapping of addresses into physical memory locations. The level of complexity and efficiency of the Div3 Method is dependent on how this awkward factor is handled by the mapping scheme of the virtual memory system. Mapping schemes for address translation at both the bword and page levels will be examined.

#### 3.2.1 Address Pages

Similar to other virtual memory systems, the Div3 Method uses the low n bits of the virtual address as the word offset into the page, and the remaining virtual address bits as the virtual page number. Since the bword offset into the page does not also represent a physical offset into the page, the offset must also be translated to reference the correct physical locations. This extra translation is not necessary with most standard virtual memory systems. Table 3.1 shows the correlation between the number of offset bits in the virtual address (n), the number of bwords which can be addressed  $(2^n)$ , and the number of 32-bit words required to hold them  $(\frac{4}{3}*2^n)$ . Pages of these sizes will be called address pages, and will not necessarily be the

same size as the pages which are stored in primary and secondary memory, which will be called *transfer pages*. These differences, along with the translation of the page number will be discussed in the next section.

Notice that the Div3 Method uses virtual page sizes which are a power of 2 number of bwords, as opposed to using page sizes which are a power of 2 words large. If the latter page size were adopted, then the number of bwords in a page would be an odd number, approximately  $\frac{3}{4}$  the number of words. In this case, the virtual page number and virtual page offset address fields overlap by 2 bits, causing the following problems: the virtual page offset is now a function of the virtual page number, and the virtual page number depends on the two overlap bits. The first problem exists for the Div3 Method also, but in this case the entire virtual address is needed to obtain the offset. Since this operation lies in the critical path of the cache, this added complication will have adverse effects on the access time of the cache. The second problem causes great difficulty in TLB addressing. It was found that these difficulties cannot be overcome without substantial hardware support.

Given n bits specifying the bword offset into the address page, and given an address which specifies the origin of the physical page, the bword offset must be translated into an offset which points to the correct 4-word transfer block within the physical page. Equation 3.1 shows the mathematical relationship between the virtual bword offset and the physical transfer block offset.

$$TransferBlockOffset = Integer(VirtualBwordOffset*\frac{1}{3*I})*4*I, \quad I \in \{1, 2, 4\}$$

$$(3.1)$$

This equation holds for 4- (I=1), 8- (I=2), or 16-word (I=4) NuBus block transfer sizes. Notice that the *Integer* function simply returns the integer portion of its argument.

The following shows how this addressing scheme is implemented for a 4-word, 3-bword transfer block (I=1).

It is clear from equation 3.1 that a divide by three operation cannot be avoided. Assuming that n, the number of bits in the virtual bword offset is not excessive, then the operation can be done by 1 or 2 PALs or ROMs. These would use the

virtual bword offset as an address and return an (n-1)-bit quotient and a 2-bit remainder, these being the results of dividing the address by 3. The multiply by 4 is done by shifting the quotient left 2 places. The result of this operation represents the transfer block offset into the physical page.

Another method of doing the divide-by-3 is to notice that the Taylor series expansion of  $\frac{1}{3}$  is  $\frac{1}{2} - \frac{1}{4} + \frac{1}{8}$ ..... This operation can be done by a series of shifts, adds, and subtracts. Unfortunately, using current technologies, this elegant method will have a propagation delay at least twice that of a fast ROM or PAL.

Since a transfer block offset represents three virtual bwords, the remainder of the divide-by-3 operation is used to identify one of the 3 bwords in the transfer block. A remainder of a divide-by-3 normally returns values of 0, 1, or 2. Upon examining the alignment of bwords within the transfer block, however, it is clear that the values of 1, 2, and 3 (remainder+1) would be more useful. If the remainder is just a PAL or ROM location accessed by the bword address offset, then it is a trivial change to have the PAL or ROM return remainder + 1 instead of remainder. If the Taylor expansion method is being used, then the remainder will have to be incremented following the divide-by-3 operation. This must be done at the end so that only the remainder is affected by this change. This value then represents the byte offset into word 0 and the word offset into the transfer block which correspond to the 5 bytes the addressed bword.

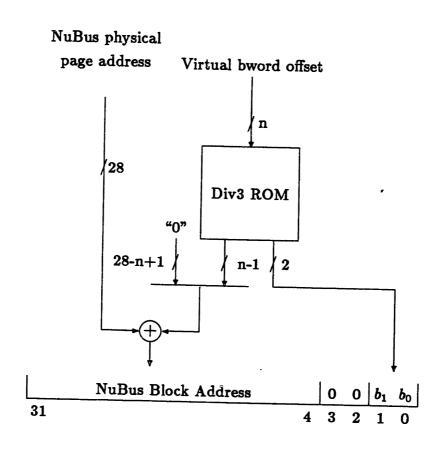

Figure 3.4 gives a functional representation of the translation process which was described in the last two paragraphs. For simplicity the remainder of the paper will refer to the hardware which does the divide-by-3 operation as the Div3 ROM.

This scheme can be easily adapted for block sizes of 8 or 16 words. As equation 3.1 indicates, the divide-by-3 is replaced a divide-by-6 for a block size of 8, and a divide-by-12 for a block size of 16. The multiplication is done by shifting left 3 or 4 bits respectively. Similar arguments about the value of the remainder also apply to these cases. Table 3.2 shows the remainders which should be output instead of the actual values, and figure 3.5 shows an example translation of the same addess for each of the 3 block sizes.

Figure 3.4: Calculating the NuBus Block Address and Block Offset

| Real      | Div6      | Div12     | Real      | Div12     |

|-----------|-----------|-----------|-----------|-----------|

| Remainder | Remainder | Remainder | Remainder | Remainder |

| 0         | 1         | 1         | 6         | 9         |

| 1         | 2         | 2         | 7         | 10        |

| 2         | 3         | 3         | 8         | 11        |

| 3         | 5         | 5         | 9         | 13        |

| 4         | 6         | 6         | 10        | 14        |

| 5         | 7         | 7         | 11        | 15        |

Table 3.2: Remainders Stored in the Div6 and Div12 ROMs

### Physical Page Address = F30FF000 (hex) Virtual Offset = 142 (dec) = 8E (hex)

#### Output of ROM:

| ROM   | Block | Number | Of    | fset  | Physical Block Address |

|-------|-------|--------|-------|-------|------------------------|

|       | (dec) | (hex)  | (dec) | (hex) | (hex)                  |

| Div3  | 47    | 2F     | 1     | 1     | F30FF2F0               |

| Div6  | 23    | 17     | 4     | 4     | F30FF2E0               |

| Div12 | 11    | В      | 10    | A     | F30FF2C0               |

|          | Div12  | Div6  | Div3  |

|----------|--------|-------|-------|

|          |        | DIVO  | DIV3  |

|          | 12     | 6     | 3     |

|          | 11     | 5     | 2     |

|          | * 10 * | * 4 * | * 1 * |

| F30FF2F0 | *      | *     | *     |

|          | 9      | 3     |       |

|          | 8      | 2     |       |

|          | 7      | 1     |       |

| F30FF2E0 |        |       |       |

|          | 6      |       |       |

|          | 5      |       |       |

|          | 4      |       |       |

| F30FF2D0 |        |       |       |

|          | 3      |       |       |

| Ì        | 2      |       |       |

|          | 1      |       |       |

| F30FF2C0 |        |       |       |

Figure 3.5: Example Address Translation for 3 Different Block Sizes

#### 3.2.2 Transfer Pages

This section describes the translation process of virtual page numbers to physical page addresses, and how the virtual memory system maintains physical pages. The ideas of this section can easily be generalized to apply to the transfer of blocks of data between any devices, not just primary and secondary memory. Due to the odd number of 32-bit words in an address page (recall table 3.1), physical pages in the Div3 Method are often not of a convenient size for systems which normally handle blocks of data whose size is a power of 2. This odd page size can complicate both the physical page number to physical page address translation process, and the derivation of the physical address from the physical page address and the physical page offset. Depending on how the virtual memory system is implemented, some tradeoffs can be made between speed, complexity, and the transfer page size.

As previously mentioned, the transfer page is defined which is transfered between primary and secondary storage. In most existing machines this is the same size as the address page, which is obviously optimal as far as memory usage and transfer efficiency are concerned. If this is not an efficient size for some other reason, it is possible to use a transfer page size which is larger than the address page. The bytes past the end of the address page will never be accessed, but will be transfered between primary and secondary memory.

The difference between the address page size and the transfer page size is accepted as wasted physical storage space. This waste is tolerated if the transfer page boundaries fall on addresses which simplify the virtual memory system, especially if much of it needs to be implemented in hardware. This waste will also be tolerated if the transfer page size is fixed due to block size requirements of secondary storage devices, or the use of NuBus block transfers for paging.

If transfer pages are of a size which is not a power of 2, then the physical page address cannot be easily obtained from the physical page number. This is a problem since many systems use physical page numbers instead of physical page addresses in managing the pages of physical memory. To resolve this problem, physical page addresses must be regenerated from physical page numbers on each

Figure 3.6: Organization of the TLB and Div3 ROM

page fault, or the additional information must be maintained when physical pages become available (virtual pages are flushed), or somewhere in the virtual memory management tables. In addition, there must be a way to generate physical page addresses to initialize the virtual memory system.

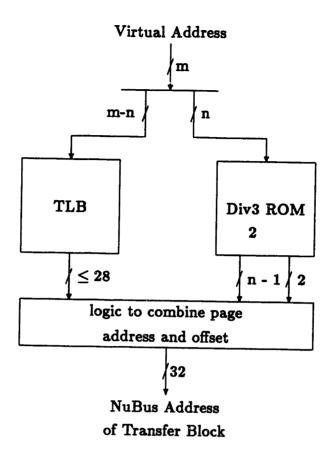

Figure 3.6 shows the general organization of the TLB and the logic to generate a physical address of the form shown in figure 3.2. The next few paragraphs will examine the cases where the transfer page is the same(or nearly the same) size as the address page, where the transfer page size is fixed to a power of 2 larger than the address page size, and where the transfer page size is an integral multiple to a power of 2 which is less than the address page size. The differences between these implementations are in the initial values of the physical page addresses and the logic

which follows the TLB.

In the first case the transfer page size is the same or nearly the same size as the address page size. This implies that the physical page address is an odd size and must be maintained separate of the physical page number, since it would be complicated to generated on every page fault. The output of the TLB will be a full 28 bits (the bottom 4 bits are 0's for a 4-word block transfer), and the logic which follows the TLB in figure 3.6 will consist of a 28-bit full adder. By maintaining the full physical page address any size of transfer page could be used, but a size very close to the address page size would be the most efficient in physical memory usage. Therefore, a transfer page size equal to the address page size or the next higher multiple of 8 or 16 words would most likely be used.

The second case fixes the transfer page size to a power of 2 that is greater than the address page size. Assuming a page size of  $2^m$ , the advantage of this case is that the physical page address ends in m bits of 0. Since the transfer page size is larger than the address page size, the output of the Div3 ROM will be m bits or less. The logic following the TLB then needs to append the physical page address to the physical page offset. This requires no additional hardware and results in no additional delay. It also means that the physical page address and page number are simply related as in most systems. Consequently, the physical page address need not be maintained seperate of the physical page number.

While simplifying physical page management and address generation, the second case is very inefficient in memory usage. If the transfer page size is  $2^m$  words, the address page size is at most  $2^{m-1}$  bwords or  $\frac{2^{m+1}}{3}$  words. This results in  $\frac{1}{3}$  of physical memory being left unused by the virtual memory system.

The final case is a hybrid version of the other two. It has the efficiency of memory usage of the first case and the simplicity of physical page management of the second case. This is achieved by picking a transfer page size which is easy to multiply the physical page number by. For example, with 256 bwords per page, the address page size is 342 words. If a transfer page size of 384 words is chosen, then the physical page address is found by appending the NuBus slot address to the

| Case | Transfer Page Size  | Wasted Memory | Remarks                                |

|------|---------------------|---------------|----------------------------------------|

|      | (words)             | (words/%)     |                                        |

| 1    | 342                 | 0/0%          | Address page size = transfer page size |

| 1    | 352                 | 10/2.84%      | Nearest multiple of 16                 |

| 2    | 512                 | 170/33.2%     | Nearest power of 2                     |

| 3    | 384 (256 + 128)     | 42/10.9%      | Minimum block size of 128, 3 additions |

| 3    | 352 (256 + 64 + 32) | 10/2.84%      | Minimum block size of 32, 4 additions  |

Table 3.3: Consequences of the Different Transfer Page Handling Schemes

physical page size multiplied by 384, which can also be more conveniently expressed as (256 + 128). The physical address is then obtained by the following formula:

$$NuBusBlockAddr = shl24(NuBusSlotNo) + shl10(PhysPageNo) + shl9(PhysPageNo) + shl4(PhysPageOffset).(3.2)$$

Here, shin(value) indicates that value is shifted left n bits. Note that this generates a NuBus byte address, so multiplying by 256 words is the same as multiplying by 1K bytes. This is easily done in hardware by using a series of adders for the logic following the TLB in figure 3.6. If the adders are pipelined, the delay of 3 or 4 adders will not be much greater than the delay of one.

This final case can be modified in many ways to minimize wasted physical memory, delay through the adder circuitry, or be made to fit the minimum block size requirements of the memory system. Table 3.3 shows a few implementations listed by their case (1, 2, or 3) as presented in the preceding discussion. They all assume an address page size of 256 bwords or 342 words.

#### 3.3 The Div3 Cache

Along with the address translation, the local cache is the feature upon which the performance of the Div3 Method depends. Without memory local to the proces-

sor, every memory access would require a 4 word transfer to take place. If processor slot space is critical, then a small cache or buffer should be implemented, hopefully taking some advantage of the extra bwords which have already been fetched. If space or cost restrictions of this degree do not exist, then a large cache should be implemented. The next sections will discuss cache addressing in the Div3 Method, cache update policies, and small caches and buffers.

#### 3.3.1 Div3 Cache Addressing

This section discusses some of the issues which apply to addressing any cache used with the Div3 Method. Many of these issues are a result of the fact that while memory lies in the 32-bit world and the processor in the 40-bit world, the cache must operate between the two. The bwords are now being stored in 40-bit locations, but the factor of 3 is still present in the block size, and must be dealt with accordingly.

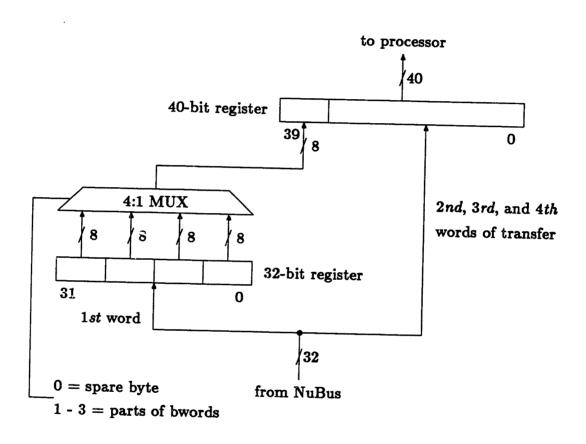

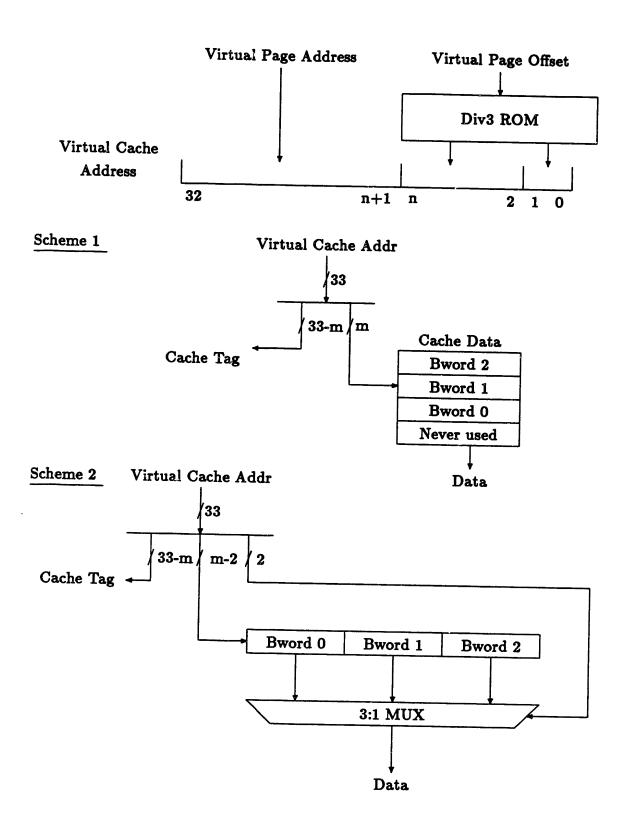

Since 3, 6, or 12 bwords at a time are transfered between memory and the processor, it would seem natural for any cache to have a line or block size equal to the NuBus transfer block size being used. This reduces the cache addressing complexity, allows the cache to store only one tag per block, and uses the minimum number of locations in storing the fetched block. In order to address words in groups of three, however, a divide-by-3 scheme must again be used. This is easily accomplished by using the Div3 ROM. Figure 3.7 shows 2 general cache addressing schemes which support base-3 block sizes using this ROM or PAL.

In discussing cache addressing schemes, it may not always be possible address every cache memory location. These discussions will refer to effective cache size, the size of cache counting only those locations which are used.

The first scheme stores bwords in 40-bit locations. Unfortunately, due to the fact that the remainder only takes on 3 different values, the effective cache size will only be  $\frac{3}{4}$  of the cache capacity. Any cache data location whose address ends in two 0's will never be used. Note that this problem does not apply to the cache tag memory since only one entry per block is stored there.

Figure 3.7: Two Cache Addressing Schemes

The second scheme stores bwords in 120-bit locations, 3 per location. In this scheme no memory is wasted, but 120-bit locations must be constructed. The correct bword of the 3 is then selected by the 2 remainder bits. The feasibility of this scheme depends on the implementation technology. Building this cache out of 8-bit SRAMS would not be practicle, especially if a set size larger than 1 was desired. On the other hand, a semicustom integrated circuit implementation of this cache could be practical.

As can be seen in figure 3.7, there is a cutoff point above which the accessing characteristics of the cache change. This is due to the incongruity introduced in the caching system by joining a base-3 address with a base-2 one. The following equations will be used to define three classes of cache size:

$$AddressPageSize < NumberOfSets * BlockSize$$

(3.3)

$$AddressPageSize > NumberOfSets * BlockSize$$

(3.4)

$$AddressPageSize = NumberOfSets * BlockSize$$

(3.5)

Caches which correspond to equation 3.3 will be known as large caches. Likewise, caches which correspond to equation 3.4 will be known as small caches. The final case, corresponding to equation 3.5 constitute a special case and will be considered separately.

Large caches operate as shown in figure 3.7 without any additional logic. Unfortunately, the high 2 bits of the output of the Div3 ROM will only assume values of 0, 1, and 2. This means that  $\frac{1}{4}$  of the usable cache memory will never by used and the effective cache size is further reduced by a factor of  $\frac{1}{4}$ . For a large cache, this may result in a considerable amount of wasted cache memory. Furthermore, this memory cannot be easily reclaimed since it is scattered throughout the cache in chunks of  $2^{n-2}$

Small caches do not have the memory waste problem of large caches. This is due to the fact that, except in one specific case, the high 2 bits of the Div3 ROM are not used in addressing the cache memory, but instead form part of the cache tag. The exception occurs when the second highest bit of the output of the Div3 ROM

is being used to address the cache, but the highest one is not. In this configuration,  $\frac{2}{3}$  of the address space maps into one half of the cache and the other  $\frac{1}{3}$  maps into the other half. This will clearly have a negative effect on cache performance when compared to a cache of comparable size.

The final case is the special case where the address page size is equal to the size of each cache bank, n banks making up an n-way set associative cache. Like the large caches, this size has an effective cache size of  $\frac{3}{4}$  of the usable cache memory since the high 2 bits of the Div3 ROM output are not being used. However, unlike the large caches, the unused memory is not scattered about in chunks, but is located all together in the top  $\frac{1}{4}$  of the cache memory. This offers the opportunity for it to be used by the processor for some other purpose.

If space allows, an extra Div3 ROM can be used for cache addressing. This ROM would be used for the cache only and would use the correct number of bits so that the output is used to address the cache and the rest of the virtual address is used as the tag. This is identical to the case where equation 3.5 was true, but allows more freedom in picking cache parameters.

### 3.3.2 Update Policies

The choice of update policy is particularly important to the Div3 Method since it will determine how many single bword memory accesses will be required. The choices are either store-and-invalidate, write-through, or store-in (otherwise known as write-back). There is also the side issue of whether to write single bwords or whole transfer blocks on writes in the write-through policy and with dirty flushes in the store-in policy.

### Write-Through Update Policy

The write-through policy is often chosen over the faster store-in policy for two main reasons. First, the cache consistency issues of multiprocessing environments is avoided since primary memory is constantly up to date. Second, the logic necessary to implement write-through is small since the additional information of dirty blocks

and the logic needed to do dirty flushes is not needed. Unfortunately, the writethrough cache used with the Div3 Method must pay the penalty of two NuBus accesses on every write.

### Store-and-Invalidate Update Policy

While saving some logic compared to write-through, the store-and-invalidate policy becomes less efficient as the block size grows. This is due to the fact that the chance that something else in the block will be accessed while the block is in the cache is proportional to the block size. Since the Div3 Method cache is based on transfer blocks of 3, 6, or 12 bwords, the store-and-invalidate cache will not be very efficient. Instead, the write-through policy, requiring comparable hardware support, should be used instead.

### Store-In Update Policy

Store-in has two big advantages over the other two update policies. First, the average access time is lower since the processor does not need to do the write to memory over the NuBus on write misses. Second, bus traffic is reduced for the same reason. The major disadvantage of this policy is the cache consistency problem. Whether this problem will prevent the store-in policy from being used will depend on the environment that the 40-bit machine is to be used in. Another disadvantage is the additional logic needed to maintain dirty bits for, and potentially flush each bword or block.

If cache consistency does present a problem, then either a method to cure the problem must be implemented, or store-in is abandoned as a potential update policy. There are many proposed solutions to the cache consistency problem, and those will not be covered here. Many of these solutions, however, rely on status information about the block in memory. The extra byte in the transfer block could be used as a location with which to pass status information about the block from processor to processor.

### Bword or Transfer Block Writes?

In using the any of these policies, the choice of whether to write the whole block or just the dirty bword should depend on how single bword accesses are being handled. If the logic for single bword accesses already exists for unmapped memory accesses and the write-through or store-and-invalidate policy is used, then single bword writes should be used. If this logic does not exist or store-in is being used it may be far less complex to write the entire block back to memory. This has the advantage of having to initiate only one NuBus transaction, while the single bword write will require a word access and a byte access. Additionally, using store-in, more than one bword per block may be dirty and need to be written back anyway.

### 3.3.3 Small Caches and Buffers

This section will discuss small caches or buffers which can be used when a larger cache is not practicle. For small caches, such as one that would be implemented on a processor chip, a fully-associative cache organization yields the best performance results (this is true for all size caches, but large fully associative caches are usually not practicle to implement). Fortunately, VLSI design supports fast, parallel search over many elements making an efficient fully-associative organization possible. If the Div3 ROM is included on the processor chip along with the cache, then one tag can be stored per 3 bword block, and the parallel search will be  $\frac{1}{3}$  as extensive. If the Div3 ROM is off-chip, then a tag will have to be stored for each bword.

A small cache such as this could also be used with a larger off-chip cache. Access times on-chip will be better than those off-chip, especially since the offset ROM is avoided, and a small cache is easy an easy thing to implement in any spare silicon. Unlike other cache organizations, it is not important for the fully-associative organization to have a size which is a power of two, making its size very flexible. Also, if used to complement a larger, off-chip cache, a very small cache operates best as an instruction-only cache since instructions tend to demonstrate better locality of reference (see Appendix B for results which show this). In this

Figure 3.8: Caching Realignment Buffer

way the logic associated with update policies can be ommitted, assuming that the executing instruction set is not self-modifying.

Caches of this type will be very small, and the cost of bringing something into the cache is compounded by the fact that you must flush something that you will probably need later. Since the cache is small due to size or logic restrictions, write-through should be used since it avoids the extra logic of dirty bits and writing back to memory when that block is finally cached.

Finally, if it is impossible to implement a local cache, then the bword realignment logic should be turned into a buffer which stores the last transfer block which was accessed. An example of this is shown in figure 3.8. At least some advantage could be gotten from having transfered the extra words, but this method should only be used when no other arrangement is possible.

## 3.4 Performance of the Div3 Method

The performance a 40-bit processor which implements the Div3 Method can be compared to that of a functionally equivalent 32-bit processor by noting that a 4-, 8-, or 16-word NuBus block transfer is necessary to fill the block of either cache. For example, the Div3 cache has a block size of 3 bwords which are filled by a 4-word block transfer, while the corresponding 32-bit cache with a block size of 4 words also requires a 4-word block transfer. In a similar manner, the 6-bword block cache and the 8-word block cache both use 8-word block transfers, while the 12-bword block cache and the 16-word block cache both use 16-word block transfers. The differences in their performance will be reflected in the respective hit ratios which will differ due to the number of elements per block.

Some additions to equation 1.1 must also be made in order to accurately predict the performance of the Div3 Method. These are the addition of the access time of the Div3 ROM to the cache access time and the addition of the logic following the TLB to the main memory access time.

The average access time for a general Div3 Method implementation can be represented by the equation 3.6. It is assumed that the page fault occurrence  $(P(m_{tib} \mid m_c))$  will be identical for the two systems, and that the access times associated with disk (reflected in  $t_{pgf}$ ) will be similar, although this will may not be true depending on the size of primary memory and the manner in which page faults are resolved.

### 3.5 Summary of Div3

Figure 3.10 shows the layout of a generalized Div3 Method system. The only hardware additions which have been made are the Div3 ROM and the appropriate logic following the TLB. The Div3 ROM will divide by 3, 6, or 12, depending on the desired NuBus transfer and cache block size. This is implemented with 1 or 2 8-bit PALs or ROMs, or shift and add hardware to implement the Taylor series expansion of  $\frac{1}{3}$ . The delay which this logic introduces in cache addressing will depend on the

$$P(h_c)! = probability of a cache hit on a local cache$$

$$P(m_c)! = probability of a miss on a local cache = 1 - P(h_c)!$$

$$t_{div3} = access time of Div3 ROM$$

$$t_c! = access time of a local cache = t_c + t_{div3}$$

$$P(h_{llb} \mid m_c)! = probability of a hit on the translation lookaside buffer given a local cache miss$$

$$P(m_{llb} \mid m_c)! = 1 - P(h_{llb} \mid h_c)!$$

$$t_{log} = access time of logic after the TLB$$

$$t_{llb}! = access time of the TLB = t_{llb} + t_{log}$$

$$t_{mem} = access time of block from main memory$$

$$t_{pgf} = time to process a page fault on a tlb miss$$

$$t_{avg}! = average access time of a virtual memory request$$

$$t_{avg}! = P(h_c)! * t_c!$$

$$+ P(m_c) * [P(h_{llb} \mid m_c)! * (t_{mem} + t_{llb}!) + P(m_{llb} \mid m_c)! * t_{pgf}] (3.6)$$

Figure 3.9: Computing the Average Access Time of the Div3 Method

Figure 3.10: Functional Diagram of a General Div3 System

implementation, but could be made as low as 15 ns with currently available devices. The logic following the TLB will consist of either nothing, a single full adder, or multiple full adders. These can be implemented with a variety of commercially available parts with delays as small as 31 ns. The speed of these parts is not as critical as the Div3 ROM which lies in the critical path far more frequently.

With the exception of unmapped memory accesses, the management of bwords is totally transparent to the processor. The Div3 Method has been designed to allow the processor to initiate unmapped accesses with minimal knowledge of the organization of bwords in memory. This is done by offering a format for storing NuBus addresses from which the addresses for both parts of the bword are easily derived.

The Div3 Method is also attractive because of range of ways in which it can be implemented. Most notably it has a transfer page size can be selected which is compatible with the other NuBus devices of the system. An efficient cache design can also be selected. All cache organizations correspond to a NuBus block transfer size so that the NuBus is utilized in its most efficient manner and bus traffic is kept to a minimum.

## Chapter 4

# The Separate Tag Method

The Separate Tag Method is based on the storage of 4 bwords in 5 words. In this method, as in the Div3 Method, bwords are divided into two parts. The pointer portion is stored one per word in 4-word blocks, and the tag portion is stored four per word. All types of physical memory spaces are then divided into two parts, a pointer space and a tag space. As the names suggest, tags are stored in tag space and pointers in pointer space. The exact locations of a pointer-tag pair are related to their respective space base addresses by a simple binary operation. The following sections will discuss the organization of bwords in physical memory, the handling of virtual and unmapped memory requests, and the effects of the method on local caches. The final section will discuss performance evaluation of the Separate Tag Method.

### 4.1 Bword Organization

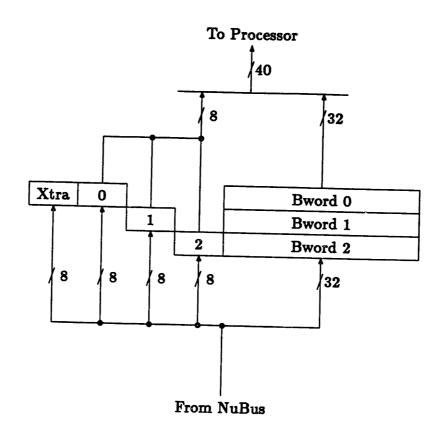

Bwords are organized in the two spaces as shown in figure 4.1. As in the Div3 Method, it is desirable to transfer the tag word first, allowing a bword to be obtained on each additional NuBus transfer. A realignment buffer similar to the one used in the Div3 Method is necessary to reorganize the 5 words into their appropriate bwords. This is shown in figure 4.2.

It will be again assumed that the cache will be responsible for reorganizing

Figure 4.1: Arrangement of the Pointer and Tag Space

Figure 4.2: Realignment Buffer

blocks going to the NuBus, and it will again be advantageous for the processor to have access to the tag word without the associated pointers (see section 3.1).

One advantage of the Separate Tag Method over the Div3 Method is that it allows memory to be easily shared with 8-, 16-, and 32-bit processors without changes to those processors. This can be accomplished in the Separate Tag Method using either of two ways. First, some or all of the pointer space can be used as shared memory, requiring only that the base address and range of this space be made known to the non-40-bit processors. The words in the tag space should be marked appropriately to indicate that their pointers are in shared memory. This is necessary because the tag words will not be updated by a non-40-bit processor which accesses the shared pointer space.

The other way involves setting aside a portion of physical memory as shared memory, and not maintaining tags for that part of memory. These physical pages must be marked appropriately in the physical and virtual page information of the 40-bit processor. When a memory request to one of these areas is made, the tag fetch of the memory access is not done since there is no tag space associated with the physical address. In its place, a word of tags must be read in from the processor or from somewhere in the processor's memory management hardware. Figure 4.3 shows an example implementation of this idea.

## 4.2 Memory Management