# MIT Open Access Articles

# Characterizing and Improving Resilience of Accelerators to Memory Errors in Autonomous Robots

The MIT Faculty has made this article openly available. *Please share* how this access benefits you. Your story matters.

**Citation:** Shah, Deval, Xue, Zi Yu, Pattabiraman, Karthik and Aamodt, Tor. "Characterizing and Improving Resilience of Accelerators to Memory Errors in Autonomous Robots." ACM Transactions on Cyber-Physical Systems.

As Published: http://dx.doi.org/10.1145/3627828

Publisher: ACM

Persistent URL: https://hdl.handle.net/1721.1/152618

**Version:** Final published version: final published article, as it appeared in a journal, conference proceedings, or other formally published context

**Terms of Use:** Article is made available in accordance with the publisher's policy and may be subject to US copyright law. Please refer to the publisher's site for terms of use.

# Characterizing and Improving Resilience of Accelerators to Memory Errors in Autonomous Robots

DEVAL SHAH, University of British Columbia, Canada ZI YU XUE<sup>\*</sup>, Massachusetts Institute of Technology, USA KARTHIK PATTABIRAMAN, University of British Columbia, Canada TOR M. AAMODT, University of British Columbia, Canada

Motion planning is a computationally intensive and well-studied problem in autonomous robots. However, motion planning hardware accelerators (MPA) must be soft-error resilient for deployment in safety-critical applications, and blanket application of traditional mitigation techniques is ill-suited due to cost, power, and performance overheads. We propose Collision Exposure Factor (CEF), a *novel metric* to assess the failure vulnerability of circuits processing spatial relationships, including motion planning. CEF is based on the insight that the safety violation probability increases with the surface area of the physical space exposed by a bit-flip. We evaluate CEF on four MPAs. We demonstrate empirically that CEF is correlated with safety violation probability, and that CEF-aware selective error mitigation provides  $12.3 \times$ ,  $9.6 \times$ , and  $4.2 \times$  lower dangerous Failures-In-Time rate on average for the same amount of protected memory compared to uniform, bit-position, and access-frequency-aware selection of critical data. Furthermore, we show how to employ CEF to enable fault characterization using  $23,000 \times$  fewer fault injection (FI) experiments than exhaustive FI, and evaluate our FI approach on different robots and MPAs. We demonstrate that CEF-aware FI can provide insights on vulnerable bits in an MPA while taking the same amount of time as uniform statistical FI. Finally, we use the CEF to formulate guidelines for designing soft-error resilient MPAs.

$CCS \ Concepts: \bullet \ Computer \ systems \ organization \rightarrow Reliability; \ Robotics.$

Additional Key Words and Phrases: Reliability, Autonomous robots, Motion planning, Collision detection.

#### **1 INTRODUCTION**

Autonomous robots are increasingly used for real-time and safety-critical tasks, including medical care [26, 42], autonomous driving [122, 126], and home assistance [67, 136]. The size of autonomous robots market is expected to grow by  $4 \times$  from 2022 to 2030 [14, 58]. As autonomous robots are becoming an integral part of our lives, it is crucial to ensure that an autonomous robot does not collide with other objects, and thereby harm the safety of its surroundings.

Motion planning allows an autonomous robot to navigate and reach its end goal safely without collisions. Therefore, motion planning is key to the many tasks performed by autonomous robots, including navigation, object manipulation, footstep planning, and full-body movement. It has been an area of study since the 1970s [66, 71],

\*Work performed while at UBC

This research has been funded in part by the National Sciences and Engineering Research Council of Canada (NSERC) through a NSERC Strategic Project Grant.

Authors' addresses: Deval Shah, University of British Columbia, Canada, devalshah@ece.ubc.ca; Zi Yu Xue, Massachusetts Institute of Technology, USA, fzyxue@mit.edu; Karthik Pattabiraman, University of British Columbia, Canada, karthikp@ece.ubc.ca; Tor M. Aamodt, University of British Columbia, Canada, aamodt@ece.ubc.ca.

© 2023 Copyright held by the owner/author(s). Publication rights licensed to ACM. 2378-962X/2023/10-ART \$15.00 https://doi.org/10.1145/3627828

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

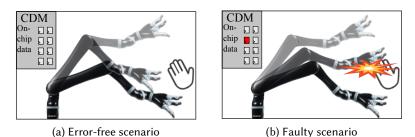

Fig. 1. The effect of soft errors on safety in autonomous robots.

and is today one of the key research topics in robotics. For example, motion planning constitutes about ~10% of the total publications in top robotics conferences [2, 3] (ICRA-2022 had 931 papers, 115 of which were in motion planning). Motion planning has also received significant attention from industry, with an increasing number of patents. For example, the number of patents granted every year by the United States Patent Office (USPTO) on collision detection and motion planning has increased by  $8 \times$  from 2015 to 2022 [39, 127].

The computational and real-time demands of motion planning exceed those provided by typical CPUs. Recently, several approaches have been proposed to accelerate motion planning on different hardware platforms, including GPUs [12, 35], FPGAs [7, 90, 113], and ASICs [10, 77, 89, 112, 114, 139]. Motion Planning Accelerators (MPAs) have achieved impressive performance gains and are being adopted in industry [28, 102, 106]. However, the use of MPAs in robotics applications has significant safety implications. For example, the IEC 61508 [57] provides functional safety standards for electronic systems used in applications such as robotics in terms of allowable dangerous failure rate per hour (Section 2.3). In modern systems, errors induced by particle strikes and radiation, or soft errors, make up the majority of SRAM and register-level faults [84, 115]. Hence, soft errors are a major threat to safety standards compliance in MPAs used in robotics. Furthermore, due to their transient nature, soft errors cannot be eliminated during the design and test phases of a chip, and hence need runtime mitigation.

There have been many studies on the effects of soft errors on CPUs, GPUs, and FPGAs [31, 32, 38, 47, 49, 64, 75, 76, 88, 94, 96–98, 110, 123, 124, 128, 131], deep learning accelerators [53, 54, 74, 78, 101, 108, 125, 134], and autonomous vehicle systems [11, 56, 61–63, 135]. However, their impact on accelerators for robotics has not been studied. Application-agnostic blanket error mitigation techniques such as error-correcting codes (ECC) and dual/triple modular redundancy (DMR/TMR) can increase the area, cost, and power by 12%-125% (Table 5), and degrade the performance of these hardware accelerators. With consumer applications driving growth of robotics, the electronics controlling these systems will become increasingly cost-sensitive [23, 37, 93]. Furthermore, any increase in the MPA's power consumption significantly reduces a mobile robot's operation time as MPAs suitable for real-time motion planning can contribute to 15%-50% of its total power consumption [69, 79, 90]. While there has been work on sensor and actuator faults in robotics [22], there has been no study of the reliability of MPAs in the presence of soft errors. *To the best of our knowledge, we are the first paper on characterizing and improving the reliability of MPAs*.

In this paper, we study soft errors in the collision detection module (CDM), which is the largest, most energyconsuming, and safety-critical component in MPAs [7, 77, 89, 114]. We find that CDMs in these accelerators consist of on-chip storage elements to store the information about space that the robot passes through for possible motions. These storage elements account for more than 97% of the sequential elements (based on our RTL synthesis experiments), and so we focus on it in this paper. Figure 1 shows the effect of soft errors in the CDM. In the error-free scenario (Figure 1a), the robot navigates safely to the end goal. However, in Figure 1b, a soft error causes the MPA to misidentify a path taken by the robot as safe, thereby resulting in a collision. This mis-identification is due to an error modifying the geometric representation of the space that the robot passes through. Prior work has explored memory and register file designs that allow flexible partition into protected and nonprotected regions for incorporating selective error mitigation in systems using CPUs and GPUs [16, 86, 133, 140, 141]. These techniques protect only the most vulnerable data and do so by placing it in protected memory. A challenge with applying such an approach to error mitigation is that it requires accurate and fast identification of the most critical data. One approach is to use exhaustive fault injection (FI) to identify storage bits that exhibit the highest resilience improvement when protected from soft errors. Unfortunately, exhaustive FI can take up to 24,000 CPU hours for a typical MPA (Section 6.1.1). Such high FI time overhead for error mitigation each time the MPA is reconfigured for a different task or robot introduces practical deployment challenges. For fully autonomous robots, the MPA's storage data can be generated or modified at runtime [34, 52, 60], requiring runtime characterization of vulnerable data for selective error mitigation. Also, as noted in earlier work [88] exhaustive FI is an inefficient way to gain insight during architecture design.

Prior work on FI techniques for CPUs and GPUs [31, 32, 49, 76, 92, 124, 131] has obtained significant reductions in the FI time. These FI tools and techniques are targeted towards specific languages, Instruction Set Architectures (ISA), or CPU/GPU system simulators and often exploit the microarchitecture or ISA to reduce the FI time and estimate the failure probability (Section 8). However, these techniques cannot be directly applied to robotic accelerators that use specialized microarchitectures and instruction sets. Thus, there is a need for techniques that efficiently characterize the effect of soft errors in robotics applications. Architectural Vulnerability Factor (AVF) has been widely used to define the vulnerability of a structure and can be measured using an analytical method such as Architecturally Correct Execution (ACE) analysis [88] or FI [73]. Directly applying AVF methodology such as ACE analysis to MPAs requires considering the positions of obstacles in the environment, thus leading to the need to run a large number of simulations to accurately estimate the fraction of time a hardware storage element contains an ACE bit.

To overcome these challenges, we introduce a novel heuristic, *Collision Exposure Factor (CEF)* that depends only upon the accelerator and robot, not on the environment. Other heuristics, such as bit position [74] and accessfrequency [68, 83] have been proposed to find critical bits for deep learning accelerators and embedded applications, respectively. However, our analysis shows that considerable variation exists in the failure probabilities of bits with the same access-frequency or bit position in MPAs. In contrast, our approach provides a higher reduction in the overall failure probability as our proposed heuristic is more accurate at finding critical bits in the MPAs (Section 6.2).

The CEF estimates the vulnerability factor of memory bits storing spatial information. The 3D model data of the swept spaces of a robot's possible motions play a key role in real-time collision detection and motion planning, and is stored in the on-chip memory. Each bit in the on-chip storage helps specify the bounds of some motion's swept space. We define a bit's *critical space* as the region excluded from the swept space if that bit changes value due to a fault. A bit-error can lead to erroneous collision detection and safety violations if an obstacle overlaps with this bit's critical space. To account for this violation, CEF of a bit is defined as the surface area of that bit's critical space exposed to obstacles due to a soft error. The CEF is defined for a memory bit, and the probability of a fault in a bit resulting in a safety violation monotonically increases with its CEF value. Thus CEF values of memory bits can be used to estimate their relative vulnerability factors. In contrast, AVF estimates the failure probability due to soft error for a structure, and not in individual bits.

The probability of a fault in a bit resulting in a safety violation depends upon the environmental characteristics (e.g., average size and number of obstacles). By considering the entire swept space of the robot's motion, the CEF decouples the effects of the robot model and the environment on safety violations, and the safety violation probability of a bit monotonically increases with its CEF value. CEF can be calculated once for a given MPA and robot *without* needing to consider obstacles in the environment (which might be highly dynamic). The underlying reason this separation is possible is that, in the most widely used approaches for real-time motion planning, a robot has a fixed set of possible short motions that are precomputed independently of obstacle positions [72]. During

operation a subset of these motions is selected to navigate to a given goal depending upon obstacle positions. For purposes of fault analysis we decouple these steps by assuming a conservative distribution (e.g., uniform) on where objects will appear. We show empirically that the CEF computed this way *independent of the environment* is positively correlated with the average failure probability.

Further, we propose a CEF-aware error mitigation technique to selectively protect values with higher CEF in an MPA's on-chip storage. Finally, we propose a two-phase FI methodology: Phase 1 FI to find the CEF of all the bits (for a given robot and MPA), and Phase 2 FI to find the relation between the CEF and failure probability with fault site pruning. Uniform statistical FI-based characterization of the CDM provides similar speedup over exhaustive FI as CEF-aware FI (Section 6.1.1). However, it does not find the safety-violation probability of an individual bit nor does it find relative vulnerability of different bits, which is needed for error mitigation. In CEF-aware FI, on the other hand, decoupling the two FI phases allows efficient calculation of the safety-violation probability for every bit in the CDM. In summary, we make the following contributions in this paper:

- Establish the necessary conditions for safety violations (i.e., collisions), and propose Collision Exposure Factor (CEF), a reliability metric for CDM storage elements.

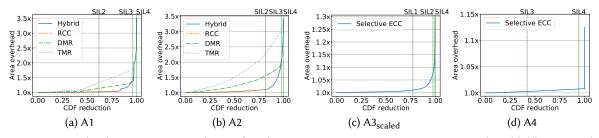

- Propose an efficient *CEF-aware error mitigation* technique that selectively protects values with higher CEF, and compare it to uniform, exhaustive FI, bit position-aware, and access-frequency-aware application of DMR, TMR, and ECC techniques for four CDM designs.

- Propose a two-phase FI methodology using the CEF of storage elements for fault site pruning to reduce FI time by orders of magnitude.

Our results show that CEF-aware selective error mitigation results in  $12.3 \times, 9.6 \times$ , and  $4.2 \times$  lower failure rate for the same amount of protected memory compared to uniform, bit position, and access-frequency-aware selection of critical data. Further, CEF-aware FI reduces the FI time by  $23,000 \times$  with minimal loss of accuracy, and finds the failure rate of the MPA and individual bits. Finally, we study the impact of architectural design parameters on resilience and error mitigation overheads, and demonstrate the potential for designing resilient MPAs architectures using the CEF.

# 2 BACKGROUND AND MOTIVATION

This section briefly summarizes relevant background information on motion planning, general CDM architecture, and safety in robotics. Then, we summarize the limitations of current FI methodologies, and discuss the need for application-specific reliability metric and FI methodology for MPAs.

# 2.1 Motion Planning

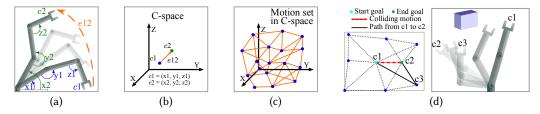

The objective of motion planning is to compute a collision-free path for a robot. Motion planning is performed in the robot's configuration space (C-space), which has the same number of dimensions as the robot's degrees of freedom (DOFs). Figure 2a shows a planar robot with three DOFs, while Figure 2b represents its C-space. Each dimension of the C-space represents the range of angles of a joint of the robot. The point c1 with coordinates (x1, y1, z1) in the C-space corresponds to the pose c1 in Figure 2a. Similarly, edge e12 represents the robot's motion from c1 to c2. The complexity of motion planning increases exponentially with the robot's DOFs [109]. Thus, approximate methods such as probabilistic roadmaps [65] are widely used [70, 109] over the last 20 years. Many hardware accelerators [7, 77, 89, 91, 113, 139] have been proposed for these algorithms.

2.1.1 Probabilistic roadmaps. Probabilistic motion planning consists of two phases. In the preprocessing stage, a graph, called a *motion set*, is constructed in the robot's C-space. Figure 2c and Figure 2d give examples of motion sets for a robot with three and two DOFs, respectively. The nodes in the graph correspond to the robot's spatial poses, and an edge between close-by nodes represent motion generated by a local planner (e.g., linear interpolation between two poses) from one pose to another. Motion set consists of collision-free poses and motions of the robot

Fig. 2. (a) shows the spatial poses and motion of a 2D robot with three degrees of freedom (x, y, z) (figure reproduced from [112]), (b) represents these poses and motion in the robot's C-space, and (c) shows a motion set in the C-space. (d) shows a motion set for a robot with two DOFs. The figure highlights a path between c1 and c2 in the presence of an obstacle in c-space (left) and physical space (right).

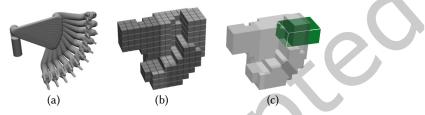

Fig. 3. (a) shows the swept space of a robot motion, (b) represents the voxelization of the swept space (explained in Section 2.2), and (c) shows an obstacle that overlaps with the swept space of this motion.

for given environment. In the query phase, a path search algorithm (e.g., Dijkstra's algorithm) is used to find a path between given start and end poses using the precomputed motion set. A path consists of one or more motions from the motion set. The probabilistic roadmap is a multi-query method, i.e., the same motion set is used to perform motion planning for multiple start and goal poses.

Leven and Hutchinson [72] proposed a real-time motion planning approach based on probabilistic roadmaps for a dynamic environment and is also used by MPAs [46, 77, 89, 91, 113, 139]. In this approach, the motion set is generated for an obstacle-free environment. At runtime, collision detection is performed to find collision-free motions in this set for a given placement of obstacles. The path search module considers collision-free motions to find a feasible path between the start and end pose in the resulting *collision-free* motion set graph. For example, in Figure 2d, an obstacle in the robot's environment makes some of the motions in the motion set flagged as "colliding motion", which are avoided by the path search module to find a path between c1 and c2.

The information about the swept space of each motion in the motion set is stored in the memory to facilitate real-time collision detection. Swept space of a motion is the space occupied by a robot as the given motion is followed. For example, as shown in Figure 3a and Figure 3b, a motion's swept space is discretized, and its 3D model is stored. As shown in Figure 3c, the motion's swept space is checked for overlap with obstacles for collision detection at runtime. Several motion planning approaches propose to modify this motion set at runtime [34, 52, 60]. For these approaches, the swept spaces of new motions are generated at runtime outside of the critical path.

#### 2.2 Collision Detection Module (CDM)

The collision detection step is the most time- and energy-consuming in motion planning and takes up to 99% of the total runtime on a CPU [12]. As collision detection must be performed in real-time with low latency to ensure safety in an environment with dynamic obstacles, MPAs typically dedicate more than 85% of their total area to accelerate collision detection [77, 89, 91], making the CDM the most vulnerable component in an MPA. An erroneous collision detection can potentially lead to a collision between the robot and an obstacle in its surroundings, making collision detection safety-critical. Many approaches have been proposed to accelerate

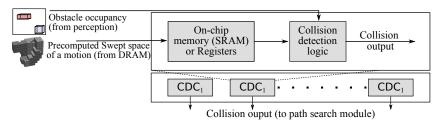

Fig. 4. Architecture of a Collision Detection Module (CDM).

collision detection on different hardware platforms. The architecture proposed by Murray et al. [90] uses specialized combinational circuits for a given motion set, but it is not reconfigurable to different motion sets at runtime. In contrast, GPU-based collision detection acceleration [12, 35] provides high flexibility, but it is not energy-efficient. Configurable collision detection hardware accelerators [7, 10, 77, 89, 91, 113, 139] provide a balance between flexibility and performance/energy-efficiency. We focus on the fault characterization of such reconfigurable CDMs of four MPAs, which we refer to as A1 [90], A2 [89], A3 [77], and A4 [139] (Section 5.2) throughout this paper.

Figure 4 illustrates the architecture of a generic configurable CDM. The CDM consists of multiple collision detection circuits (CDCs) to check multiple motions for collision in parallel. Each CDC consists of on-chip memory/registers to store a motion's swept space, and exploits inter- and intra-query data reuse. The on-chip storage can be configured for different motions at runtime. Based on our synthesis experiments, the on-chip memory to store swept spaces constitutes more than 97% of the sequential elements and  $\sim$  50% of the total area in CDMs. Earlier work on FPGA-based accelerators [89] uses combinational logic to encode swept-space data. However, most programmable CDMs have a high fraction of sequential elements dedicated to on-chip storage for spatial data [77, 89, 91, 139]. We also verify this using RTL synthesis of these programmable CDMs (architecture explained in Section 5.2). Therefore, we focus on the on-chip memory for fault characterization, and do not consider the effect of soft errors in combinational logic in this work.

The key design consideration of CDMs is the geometric representation used to store swept spaces in the memory. Several representations for storing the 3D model have been proposed for motion planning, including polygonal meshes [5], bounding box hierarchies [40, 130], voxels [114], and octrees [59]. These approaches differ in storage requirements, representation accuracy, and computational complexity. All CDM hardware accelerators studied in this work use either grid-based or octree-based representations (explained in Section 3.1) as these representations are less compute- and memory-intensive. For both representations, the swept space of a motion is discretized into fixed-size cubes known as *voxels*. Voxelized swept space is then stored using a set of structures specific to the representation used. At runtime, a perception sensor module senses obstacle occupancy information, converts it to voxels, and sends it to the CDCs. The CDCs perform collision detection for stored motions and send the output to the path search module. Note that the proposed metric CEF is applicable regardless of the geometric representation used.

#### 2.3 Functional Safety in Robotics

Safety is a crucial consideration in robotics. Hence, the failure rate of circuits used in robotics applications, including MPAs, is an important factor. The FIT rate of a circuit (where 1 FIT is one failure/billion hours) consisting of multiple components can be computed using Equation (1) [74, 88].

$$FIT = \sum_{i \in components} S_i \times SDC_i \times FIT_{Raw}$$

(1)

Table 1. Comparison of complete and selective ECC. The die cost calculation is based on the equation provided in [55] (Chapter 1.6). The wafer cost, yield, and impurity factors are for 16nm technology node [18, 25, 119].

| ,                             |        |          |                       | • •                   |

|-------------------------------|--------|----------|-----------------------|-----------------------|

|                               | No ECC | Full ECC | Selective ECC (SIL 2) | Selective ECC (SIL 3) |

| Total area (mm <sup>2</sup> ) | 450    | 502.5    | 454.5                 | 469.8                 |

| Cost/die (\$)                 | 59.9   | 70.0     | 60.8                  | 63.6                  |

$FIT_{Raw}$  is the raw FIT rate defined in FIT/Mb and depends upon multiple factors including technology node, ambient conditions, and elevation [105]. S<sub>i</sub> is the number (in Mb) of sequential elements/latches in component *i*. SDC<sub>i</sub> is the probability of a fault in component *i* affecting the application output.

IEC 61508 [57] defines an international safety standard for safety-critical electronic systems. This standard is based on the risks of failure and defines four Safety Integrity Levels (SIL). Each SIL expresses the upper bound on the average frequency of dangerous failures per hour (PFH) [82]. SIL 1 is the least stringent, while SIL 4 is the most stringent. The maximum allowable PFH rate decreases by three orders of magnitude from SIL 1 ( $10^{-5}$ ) to SIL 4 ( $10^{-8}$ ). Note that the IEC 61508 standard considers the entire electronic system, not only the MPA.

One approach to make circuits soft error-resilient for certifiable safety is to use hardware error mitigation techniques on storage, which incurs high cost/power/performance overheads. Autonomous vehicles and robotics industries typically have shallow profit margins. For example, the profit margin per unit is under \$1000 for several automobile industries [137]. Electronic systems contribute up to 40% to the total cost of a car [24, 100] (at the time of writing). Hence cost-effective solutions to make MPAs more reliable are imperative [23]. The overheads for complete protection of storage structures increase with their size. In such a case, the protection may be sacrificed entirely if the area/power overheads are over budget. In comparison, selective protection is flexible and provides safety with less overhead than complete protection of storage structures by protecting only the most vulnerable data. Table 1 compares the die area and cost for complete and selective ECC for the A3 [77]. As shown in Table 1, selective ECC can reduce the cost by 10% for SIL 3 ( $\sim$  1% increase in the profit margin). While the table compares only the die cost, an increase in the die area has a cumulative effect on the total cost of an electronic system, amplifying the need for selective error mitigation.

#### 2.4 Fault Injection (FI)

In a circuit, a soft error can occur at any location and time. Assuming a single-bit error model, where only one bit is affected by a soft error in the component, exhaustive fault characterization typically requires  $A \times B$  FI runs. In this equation, A is the number of fault sites in space, and B is the number of fault sites in time. A is determined by the number of bits, and B is determined by the application's total execution cycles and the number of possible inputs to the application. Unfortunately, this requires very high numbers of FI runs. In MPAs, different combinations of obstacle positions (input to collision detection) add to the number of FI runs, making the space even larger.

Accelerators' fault characterization is typically carried out by statistical FI experiments [19, 33, 48, 49, 73, 74]. Statistical FI performs random sampling in the fault space and allows to tune the number of FI experiments as per the required confidence of the estimated failure rate for a system [73]. Often, statistical FI is performed per component to find the safety-critical components in a circuit. However, the CDM component occupies more than 85% of the area in an MPA and mainly consists of sizable on-chip storage structures to store swept spaces. Hence, selective error mitigation of CDM requires a strategic approach to determine the safety-critical data in the on-chip storage. Further, the number of FI runs needed for statistical FI increases with a decrease in the probability of a bit error resulting in an output error, i.e., the failure probability of a component [73]. Typical CDMs have a low overall failure probability ( $\sim 0.3\%$ ) which increases the number of FI runs required when using uniform random statistical FI (Section 6.1.1). Therefore, it would be beneficial to develop an application-aware FI strategy in which the sites for FI are strategically selected.

Table 2. Summary of frequently used acronyms

|       | , , , , , , , , , , , , , , , , , , , ,                                          |

|-------|----------------------------------------------------------------------------------|

| CEF   | Collision Exposure Factor                                                        |

| MPA   | Motion Planning Accelerator                                                      |

| CDM   | Collision Detection Module                                                       |

| CDC   | Collision Detection Circuits- A CDM consists of multiple CDCs                    |

| SIL   | Safety Integrity Level (Section 2.3)                                             |

| SDC-C | Silent Data Corruption leading to False-negative collision detection (Section 3) |

| CDF   | Collision Detection Failure rate per billion hours (Section 4.3)                 |

| A1-A4 | CDMs studied in this work                                                        |

|       |                                                                                  |

#### 3 RELIABILITY METRIC FOR MOTION PLANNING

In this section we explain how erroneous collision-detection outcomes can lead to safety-critical events, then describe *Collision Exposure Factor* (CEF) in detail, and finally discuss how to apply CEF to building resilient MPAs. Table 2 summarizes the frequently used acronyms in this work.

Specialized accelerators, such as a CDM, obtain efficiency by replacing long sequences of software instructions with specialized hardware. Such accelerators may perform computations under the supervision of a command processor via an ISA interface (e.g., Google's TPU [29]), and/or may start computation triggered by an event such as the arrival of a new frame of data in a buffer [21]. While an error originating in the accelerator could potentially propagate to the command processor and thereby result in erroneous operation (e.g., hang or system software crash) this paper focuses on Silent Data Corruption (SDC) within the CDM that can result in the robot colliding with an object.

Given a motion set and the current positions of obstacles, collision detection finds motions that may lead to collisions. A bit-flip can lead to erroneous collision detection. A false-positive outcome can lead to a poor (longer) path or the motion planner's inability to find a path, in which case the robot may get stuck. We perform fault injection experiments to measure the probability of a soft error resulting in a false-positive outcome; this gives an upper bound on the probability of the motion planner's inability to find a path due to soft errors. We find that the motion planning failure rate increases by up to 0.001% for 1 second/motion planning query [99] and 45nm technology node due to soft error induced false positive outcomes, which is significantly lower than the failure rate of probabilistic motion planning algorithms (5 – 10% [99]). Further, a simple mechanism such as using a watchdog timer to refresh the corrupted on-chip data can be employed to avoid such cases. We do not focus on false-positive outcomes in this work, as their impact on the motion planning failure rate is very low, and safety standards do not consider false-positives but only safety violations.

We define an SDC-C as an event involving a false-negative result when performing collision detection for a proposed motion and an object (i.e., a colliding motion is misidentified to be collision-free even though sensors detected an object the proposed motion would collide with if chosen during path search). Similar to AVF, SDC-C probability gives a probability of raw error in a memory bit becoming an error in motion planning (i.e., false-negative collision detection). Since, in general, an obstacle might appear anywhere in the environment, a naive (but expensive) approach to estimate SDC-C probability is to simulate many sample environments, each with randomly placed obstacles. Below we consider a more efficient approach suitable, for example, during CDM architecture design.

#### 3.1 Collision Exposure Factor (CEF)

To analyze the errors that can occur in a CDM circuit and their effect on SDC-C probability, we focus on bit changes that can lead to false-negative collision detection. Specifically, we consider the impact of a change in a single bit used to represent a portion of a motion's swept space. As mentioned in Section 2.2, swept spaces of the motions are stored in CDM memory or registers and used to find possible collisions with the obstacles. Each bit in the on-chip storage helps specify the bounds of some motion's swept space. We define the *critical space* of a bit

Characterizing and Improving Resilience of Accelerators to Memory Errors in Autonomous Robots • 9

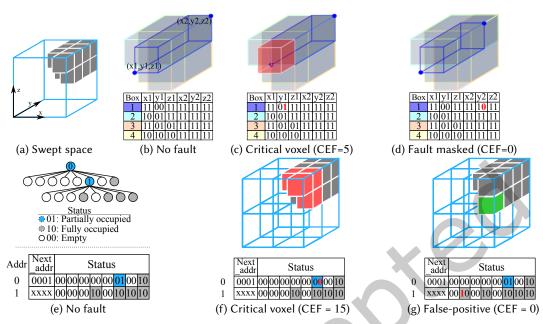

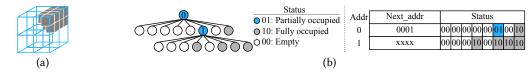

Fig. 5. Analyzing impact of bit flips in a CDM. (a) represents the swept space of a motion stored in CDM, (b)-(d) represent box-based CDM (A2), and (e)-(g) represent octree-based CDM (A3). CEF values are normalized to the surface area of one face of a voxel.

as the region excluded from the swept space if that bit changes value due to a fault. This region represents a part of the swept space that can potentially lead to false-negative collision detection if an obstacle overlaps with the critical space and does not overlap with the remaining swept space. We then define the *collision exposure factor* (CEF) of a bit as the surface area of that bit's critical space exposed to obstacles. If the geometric representation uses voxelized space, the CEF can be normalized to the surface area of one face of a voxel. In our evaluation (Section 6.1), reported CEF values are unitless. The CEF values for different accelerators (A1-A4) are on the same scale as the same normalization factor is used.

Figure 5 illustrates the critical space of specific bits due to single-bit errors for different geometric representations. Figure 5a represents the swept space of a motion. Geometric representation methods convert the swept space to a set of *structures*, such as voxels (used in A1 described in Section 5.2), boxes (used in A2), or octree nodes (used in A3 and A4). Each of these structures is encoded into bits and stored in the on-chip storage of the CDM. For example, a voxel structure is stored using its coordinates, a box structure is stored using the coordinates of the diagonal voxels, and an octree node structure is stored using a custom data structure described below. A bit flip caused by a soft error would modify the space represented by the structure in different ways depending on the location of the bit in the structure and the geometric representation.

Figure 5b shows a box-based representation of the swept space, where four boxes are required to cover the swept space. Since space is divided into four voxels in x, y, and z directions, a total of six  $(\log_2 4 \times 3)$  bits are used to store a coordinate. The highlighted box is represented with coordinates x1, y1, z1 and x2, y2, z2 of the diagonal voxels, before any error is introduced. In Figure 5c, flipping a specific bit causes the value of y1 to increase by one voxel. As the voxel highlighted in red is now excluded from the box, and no other box covers the voxel, it becomes part of the bit's critical space. A soft error in this bit results in the exclusion of the critical space from swept space; hence the collision detection circuit fails to detect a collision if an obstacle occupies this critical space, leading to an

SDC-C. In contrast, in Figure 5d, a bit flip causes *y*2 to decrease, but this bit flip is masked and does not impact the CDM's output as other boxes cover the voxels exposed.

Figure 5e shows the octree representation of the same swept space. In this representation, the root node and all partially occupied nodes are stored in memory using a tree data structure. Each node in the tree contains two fields: "status" and "next\_addr". The status field contains an entry for each octant within the node indicating whether that octant is empty, partially or fully occupied. Only partially occupied octants are further divided. The next\_addr field contains the start address of an array holding the resulting children nodes. For example, in Figure 5e, the node stored in memory at address 0 contains only one partially occupied octant, and the node containing information about it is stored at address 1. In Figure 5f, a bit flip in the node at address 0 modifies the status of a particular octant to be "fully empty", thereby adding all the voxels in that octant to the critical space. In Figure 5g, a bit flip in the node at address 1 modifies the status of an octant to "fully occupied", resulting in a false-positive rather than a false-negative. In this case, motions that would not lead to a collision may be disallowed. However, this false-positive outcome does not result in potential for a collision (an SDC-C). Therefore, this voxel (highlighted in green) is not a part of the critical space.

For a given erroneous bit, it is more likely that an obstacle occupies its critical space and results in an SDC-C as the exposed surface area of this critical space increases. Hence, intuitively, the SDC-C probability of a bit increases with its CEF value (Section 6.1.2). Note that the CEF of a bit is *independent of the position of the obstacles in the environment*. The CEF captures the probability of obstacles appearing in critical space and decouples the effect of a soft-error and exact position of obstacles on SDC-C probability. While the CEF definition assumes a uniform distribution of obstacles, it can also be extended to nonuniform distributions. For example, the CEF value can be scaled by the estimated probability of obstacles occupying the critical space for a nonuniform distribution of obstacles in the environment.

One approach is to use the volume of the critical space (CS\_volume) as a reliability metric. However, the exposed surface area gives a measure of the area of critical space through which obstacles can overlap only with the critical space and not the rest of the swept space, leading to an SDC-C. In contrast, CS\_volume does not differentiate between the surface area exposed to obstacles and the surface area touching the remaining swept space. Hence CEF performs better than CS\_volume as a reliability metric (Section 6.2). For a given motion set

| Algorithm 1 CEF measurement (Phase 1 FI)                         |  |

|------------------------------------------------------------------|--|

| Input: Motion_set, Swept_data, Swept_voxels, CDM;                |  |

| <b>Output:</b> bit_info = {bitID: (CEF, Critical_space)};        |  |

| 1: for Motion $\in$ Motion_set do                                |  |

| 2: bits = Swept_data(Motion)                                     |  |

| 3: voxels = Swept_voxels(Motion)                                 |  |

| 4: for $b \in bits$ do                                           |  |

| 5: Critical_space =                                              |  |

| 6: Collision_vector = FI(CDM, bits, voxels, b)                   |  |

| 7: <b>for</b> $(v, collision) \in (voxels, Collision_vector) do$ |  |

| 8: if $\neg$ collision then                                      |  |

| 9: Critical_space = Critical_space $\cup$ v                      |  |

| 10: end if                                                       |  |

| 11: end for                                                      |  |

| 12: CEF = Calculate <sub>CEF</sub> (Critical_space, voxels)      |  |

| 13: bit_info[b]= (CEF, Critical_space)                           |  |

| 14: end for                                                      |  |

| 15: end for                                                      |  |

of the robot and accelerator, the CEF of all the bits can be calculated using Algorithm 1. The algorithm works by considering each possible motion in turn (Line 1). For a given motion, Swept\_data returns the storage bits used to represent its swept space (Line 2), and Swept\_voxel returns the voxels in the swept space of that motion (Line 3). The loop between Line 4 and 14 considers each bit in the Swept\_data. The CDM takes precomputed

swept space (i.e., bits) and obstacle occupancy voxels as inputs and performs collision detection (Figure 4). The storage elements of the CDM are initialized with bits. To find the critical space an FI run is performed setting voxels as the obstacle occupancy voxels input to the CDM (Line 6). Specifically, a fault is injected into a low-level (e.g., RTL model or microarchitectural simulator) model of the CDM at bit b (Line 6). The CDM outputs a Collision\_vector containing collision detection output for each voxel in voxels. To find the critical space, each bit of the Collision\_vector is checked (Lines 7-11). For an error-free run, the CDM detects collision for all the voxels in the swept space (i.e., voxels). However, for an FI run, a voxel v is added to the Critical\_space if the CDM does not detect a collision (Line 8 and 9). CEF is then calculated by measuring the exposed surface area of the Critical\_space (Line 12). Note that the CEF is obtained without the need to consider a potentially unbounded set object placements. Thus the number of FI runs to measure CEF using Algorithm 1 is orders of magnitude lower than exhaustive FI in which for each bit, multiple FI runs need to be performed with a large number of environment scenarios.

As presented above, Algorithm 1 assumes an RTL or architecture model for the CDM. We note that the resulting reliance upon fault injection to determine CEF could be avoided provided an analytical model is available to compute the critical space on Lines 5 to 12. Such a model could be used to analyze CEF without performing FI prior to the development of RTL model or architecture simulators. However, we use FI to measure CEF, so the proposed Algorithm 1 can be used across different accelerators. Algorithm 1 is proposed for CDMs that use a voxelized representation of spatial data and output collision decisions (A1-A4). The majority of the collision detection acceleration approaches for robotics use voxelized representation [27]. However, the concept behind CEF is applicable regardless of the underlying design parameters, and Algorithm 1 to measure the CEF needs can be modified for a different CDM. For example, for a triangle meshes-based representation of swept space, Line 5-12 can be replaced by a geometry-based calculation of the exposed surface.

MPA is a part of complex systems such as autonomous vehicles. Fault Tree Analysis (FTA) is often used to analyze the failure probability of the overall system by constructing a logic tree of the failure events of subsystems [107]. The proposed metric CEF, being close to the application domain, can easily be integrated with the FTA of the overall system. CEF is useful for CDMs that dedicate a significant area to storage structures for spatial data. Earlier work on FPGA-based accelerators [89] uses combinational logic to encode spatial data. Combinational logic is known to be less prone to soft errors compared to sequential elements [36]. However, the definition of CEF applies to erroneous combinational logic gates if needed.

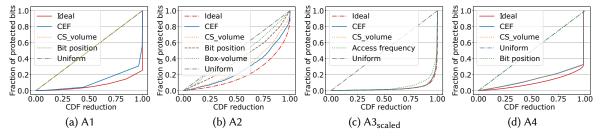

# 3.2 CEF-aware Error Mitigation

For a fixed budget of area/power overhead, selective protection of the most vulnerable bits provides the optimal reduction in the failure rate. Selective error mitigation in storage structures can be implemented by reliability-aware data placement to partially protected memory. However, this requires efficient ways to identify vulnerable data as the data can be generated/modified at runtime. We find that the CEF of a bit gives a measure of its impact on the SDC-C probability of the CDM (Section 6.1.2). Therefore, we can use information about the CEF of each bit in an input design to selectively apply error mitigation techniques such as ECC, DMR/TMR, and strike suppression. This reduces the cost of providing resilience compared to blanket protection of all the bits.

Different structures such as voxel (A1), box (A2), and octree node (A3 and A4) are stored in the on-chip storage of the CDM depending upon the geometric representation method used. CEF-aware error mitigation is performed by placing structures with higher CEF in the protected storage regions. In our evaluation, the sum of CEFs over all the bits in a structure is used as its CEF. Because CEF of a bit gives a measure of its SDC-C probability, CEF-aware data placement results in a higher reduction of the overall failure rate for a given fraction of protected storage

compared to other heuristics (Section 6.2). The CEF measurement is done offline or outside of the critical path using Algorithm 1 after motion set generation.

Selective error mitigation can also be used to guide the accelerator design process. At the accelerator design stage, the designer can perform CEF-aware FI (Section 4.2) for a set of target robots, motion sets, and the expected number of obstacles in the environment to find the distribution of CEF, SDC-C probability of bits, and the failure rate of the system without any error mitigation. Based on this information, a designer can determine the required fraction of protected memory for a given failure rate requirement or achievable failure rate for a given area/power budget for error mitigation.

# 4 CEF-AWARE RELIABILITY CHARACTERIZATION

SDC-C probability and the failure rate measurements are important to find the error mitigation requirements for certifiable safety. Exhaustive FI to find the SDC-C probability of all the bits takes a long time (Section 2.4). In this section, we first explain the fault model and demonstrate how to use the CEF to enable a hierarchical fault analysis methodology that reduces the number of FI runs.

### 4.1 Fault Model

In the CDMs studied in this work, on-chip SRAM/latches that store the swept space of motions account for 97% of the on-chip sequential elements (based on our synthesis results). Our fault model assumes transient single-bit faults in this SRAM/latches. The faults are uniformly distributed in time and space. Only 3% of on-chip sequential elements are used for meta-data (e.g., counters, address register, and finite state machine). These microarchitecture-specific registers are not subjected to CEF in our experiments as they can be characterized and protected with low overheads using latch hardening techniques such as strike suppression or redundant node [111].

# 4.2 CEF-aware FI

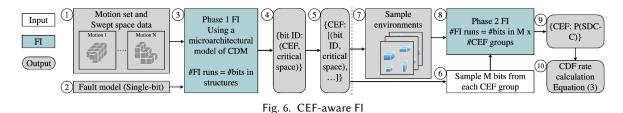

We propose a two-phase CEF-aware FI (shown in Figure 6), a technique to speed up FI for MPAs.

*Phase 1: CEF measurement (Environment independent).* For a given motion set (1) and fault model (2), Phase 1 performs microarchitecture- or RTL-level FI (3) to find the CEF and critical space of each bit in the swept space data. Algorithm 1 is used for this phase. The number of FI runs for this phase is limited to the number of bits in swept space data of all the motions in the robot's motion set. The CEF and critical space of all bits are stored to be used in the next phase (4). Note that environmental information, such as the position of obstacles or the robot, is not needed for this phase, as CEF does not depend upon the environment.

*Phase 2: SDC-C probability measurement.* A bit flip might lead to an SDC-C depending upon the position of obstacles as shown in Section 3. Since for a dynamic environment, obstacles can appear anywhere in the space, a large number of FI runs with random environmental scenarios are required to measure the SDC-C probability of a bit with statistical significance. In our experiments, the representative environment scenarios are generated using apriori information about the environment, such as the distribution and average number/size of the obstacles. In Phase 2, we use the CEF information gathered in Phase 1 to speed up the fault analysis. As mentioned, there is

a strong (positive) correlation between the CEF and SDC-C probability (Section 6.1.2). Thus, we can speed up the FI experiments many-fold by performing FI for only a subset of bits with a given CEF value to measure the approximate SDC-C probability for all bits with the same CEF. The CEF information gathered in Phase 1 is used to group bits with equal CEF values together (5). Then, for each CEF value, *M* bits are selected at random (6). Finally, using multiple sample environment scenarios (7) and FI simulations (8), the SDC-C probability for each CEF value is measured (9). Note that *M* is a tunable parameter in the above heuristic. We use the analytical model in Leveugle et al. [73] to determine the value of *M* to measure SDC-C probability with the required confidence level and error margin. The CEF-aware sampling, while being faster than exhaustive FI, may introduce inaccuracies due to the approximations it makes. However, the accuracy can be increased by increasing the value of *M* - we evaluate this trade-off in Section 6.1.1.

To speed up the FI simulation, we further exploit the fault propagation in the studied CDMs. All the accelerators studied in this work use a geometric representation that divides the space into voxels. For a given motion and environment scenario, a non-empty subset of swept space and obstacle occupancy voxels signify potential collision. Thus the effect of a bit flip can be captured by storing the erroneous swept space voxels of the corresponding motion, instead of performing slow microarchitectural and RTL simulations for multiple environmental scenarios. Simple set operations can be used to find the SDC-C probability. For a given bit flip, an FI simulation is used to find the erroneous swept space (i.e., set of voxels) using Algorithm 1. Line 3 of the Algorithm 1 is modified to use the set of all environment voxels as voxels. Similarly, Lines 8 and 9 are modified to measure the erroneous swept space (i.e., colliding voxels). For each environment scenario, the subsets of obstacle occupancy voxels and erron-free swept space are measured. If the erroneous subset is empty, but the error-free subset is non-empty, the bit flip will result in an SDC-C. The same strategy is used for exhaustive, statistical, and CEF-aware FI. While we focus on FI to measure CEF and SDC-C probability, we believe that an analytical model can be used to replace the multiple runs and find the relation between critical space and SDC-C probability. We defer this to future work.

Equation 2 is used to calculate the SDC-C probability of a CDM. Here  $bits_{CDM}$  is the set of all bits stored in the CDM's on-chip memory. CEF(x) is the CEF value of bit *x*, and  $P(SDC-C_{CEFx})$  is the SDC-C probability for the CEF value CEF*x*.

$$PSDC-C_{CDM} \approx \frac{1}{|bits_{CDM}|} \times \left[ PSDC-C_{CEFx} \right]$$

(2)

Table 3 compares the different phases of CEF-aware FI with exhaustive and uniform random statistical FI approaches for CDM fault characterization and error mitigation. We also use CEF and CEF-aware FI to analyze and compare the effects of microarchitectural design parameters of the CDM, and to derive the principles of *resilience-aware* MPA design (Section 7).

#### 4.3 Collision Detection Failure (CDF) Rate Calculation

As mentioned in Section 2.3, safety standards provide an upper bound on the frequency of dangerous failures (e.g., collision in motion planning). We combine Equation (1) and Equation (2) to measure the Collision Detection Failure rate per billion hours (CDF) for CDMs as below:

$$CDF_{CDM} = |bits_{CDM}| \times PSDC - C_{CDM} \times FIT_{Raw} \times \alpha$$

(3)

Here, the parameter  $\alpha$  is set to N2 for CDMs with inter-query data reuse, else it is set to 1, as explained below. In the MPAs we study, the on-chip data is typically reused across multiple executions of the same application [45, 89, 114, 139] to reduce the DRAM-bandwidth requirement and data movement. In such a case, a bit-flip due to a soft error will persist in the buffer and affect multiple executions, until the buffers are reloaded, and the overall CDF rate of the system increases due to data reuse. This is similar to bit-flips in configuration memory of FPGA [94],

|                                                      | Exhaustive FI                                                              | Uniform random                                                                      | CEF-a                                                                                  | ware FI                                                                                                       |

|------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

|                                                      | Exhausuve Pi                                                               | statistical FI                                                                      | Phase 1                                                                                | Phase 1 + Phase 2 (SDC-C                                                                                      |

|                                                      |                                                                            |                                                                                     | (CEF measurement)                                                                      | measurement)                                                                                                  |

| Description                                          | Performs FI on all<br>combinations of bits<br>and environment<br>scenarios | Samples a few<br>combinations of bits<br>and environment<br>scenarios to perform FI | Performs<br>environment-agnostic FI<br>to measure CEF of all the<br>bits (Algorithm 1) | Samples a few<br>combinations of<br>environmental scenarios<br>and bits for each CEF<br>group and performs FI |

| Number of FI runs                                    | 10 <sup>10</sup>                                                           | $7 \times 10^{6}$                                                                   | 10 <sup>6</sup>                                                                        | $7 \times 10^{6}$                                                                                             |

| FI time                                              | 24,000 hours                                                               | 2-4 hours                                                                           | 1-2 hours                                                                              | 2-4 hours                                                                                                     |

| Measures overall failure rate                        | Y                                                                          | Y                                                                                   | N                                                                                      | Y(2.5% error)                                                                                                 |

| Finds vulnerable bits for selective error mitigation | Y                                                                          | N                                                                                   | Y(Approx.)                                                                             | Y(Approx.)                                                                                                    |

| Measures SDC probability of<br>different bits        | Y                                                                          | N                                                                                   | Ν                                                                                      | Y(Approx.)                                                                                                    |

| Table 3. | Comparison | of different | fault injection | (FI) approaches. |

|----------|------------|--------------|-----------------|------------------|

|          |            |              |                 |                  |

where a bit-flip due to single-event upset persists and affects the application output until the configuration memory is refreshed. A1, A2, A3<sub>scaled</sub>, and A4 accelerators reuse on-chip data across N (where N >> 1) collision detection queries. A soft error can occur in any cycle during a collision detection query; however, the bit will remain erroneous from the start (i.e., cycle 0) for subsequent collision detection queries until the on-chip data is refreshed. Thus the average value of the number of collision detection queries for which a bit will be erroneous from starting is approximately N2, assuming all collision queries take the same time. Hence, to measure the CDF rate for such CDMs, faults are injected at cycle 0 in Phase 2, and the measured failure rate is scaled by  $\alpha = N2$  to account for data reuse. Whereas in A3, the on-chip data is refreshed for every collision detection query. For CDMs without inter-query data reuse,  $\alpha$  is set to 1, and the fault sites are uniformly distributed in time in Phase 2.

### 5 EXPERIMENTAL METHODOLOGY

#### 5.1 Experimental Setup

Table 4 summarizes the robots used in our experiments. These robotic arms are representative of widely used industrial robots [87, 104], and are also included in larger humanoid robots [4]. Because we did not have access to the real robots, we use the Klampt [51] software simulator to simulate the robot's movements and the environment-this has also been used in prior work [50, 90, 114].

The environment size for a robot is determined by its reach, and the environment is discretized into a grid of  $32 \times 32 \times 32$  voxels. For each robot, we generate a motion set with 16,384 poses and 32,768 motions, using Leven and Hutchinson's strategy [72], similar to prior work [90]. We use uniform motion sets in all our experiments, i.e., poses are distributed uniformly in the C-space. The uniform distribution of poses is assumed in the absence of any prior information about the robot's task and fixed obstacles in the environment. However, this information can be used to build a motion set with a nonuniform distribution of poses, where more poses are concentrated in the region of interest [129]. We also evaluate CEF on a nonuniform motion set in Section 6.1.2.

To measure the SDC-C probability, we perform FI with a set of 10,000 random environment scenarios. Each sample environment contains 3 - 12 cuboid-shaped randomly placed obstacles, and the length/height/width of each obstacle is 5 - 20cm, which is consistent with other work on motion planning and collision detection [77, 90]. We generate four sets of environments to study the effect of the number of obstacles on the SDC-C probability

| Robot                                                        | Degrees of<br>freedom | Reach in one direction | Mechanical power<br>(W) |

|--------------------------------------------------------------|-----------------------|------------------------|-------------------------|

| Kinova Jaco2 [69]                                            | 7                     | 90 cm                  | 25                      |

| Programmable Universal Machine for Assembly (PUMA) 761 [138] | 6                     | 150 cm                 | 30                      |

| AL5D [79]                                                    | 4                     | 27 cm                  | 12                      |

Table 4. Robots used for fault characterization.

Table 5. Accelerators studied. We list power and area for each accelerator from the paper and report suitable error mitigation and accelerator area overhead to protect on-chip memory. We use information gathered from our synthesis of RTL models about the fraction of CDM area and power consumed by the on-chip memory to calculate the overall CDM area and power overheads. ECC overheads do not include the area /power of decoder and encoder circuits.

| Accelerator               | Representation   | Data<br>reuse | #CDCs  | Power<br>(W) | Area<br>(mm <sup>2</sup> ) | Storage elements | ECC area/power overhead | TMR area/power<br>overhead |

|---------------------------|------------------|---------------|--------|--------------|----------------------------|------------------|-------------------------|----------------------------|

| A1 [89, 114]              | Voxel            | Yes           | 32,768 | N/A          | N/A                        | Registers        | 20/16%                  | 125/100%                   |

| A2 [89, 114]              | Box              | Yes           | 32,768 | 35           | 400                        | Registers        | 20/16%                  | 125/100%                   |

| A3 [77]                   | Octree           | No            | 128    | 0.47         | 1.7                        | SRAM             | 12/9%                   | 100/75%                    |

| A3 <sub>scaled</sub> [77] | Octree           | Yes           | 32,768 | 121          | 450                        | SRAM             | 12/9%                   | 100/75%                    |

| A4 [139]                  | Flattened Octree | Yes           | 32,768 | 20           | -                          | SRAM/DRAM        | 12/12%                  | 200/200%                   |

(Section 6.1.2). We use the label Dx ( $x \in (1,2,3,4)$ ) to represent a set of 10,000 environment scenarios, where obstacles occupy an average x% volume of the environment. The average number of obstacles increases with the value x.

#### 5.2 Collision Detection Modules (CDM)

Table 5 summarizes the four accelerators studied in this work and overall CDM area/power overheads for complete protection of on-chip storage using ECC and TMR error mitigation techniques. *These constitute the only published work on ASIC-based programmable, real-time accelerators for probabilistic roadmaps-based motion planning and collision detection, to the best of our knowledge.*

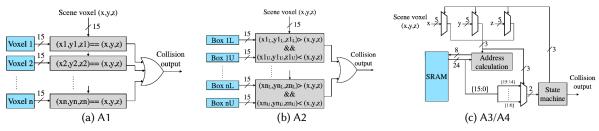

We built microarchitectural simulators and RTL models of these CDMs ourselves as there was no existing simulator. We use Verilog to build the RTL models and implement the combinational logic, control logic, and on-chip memory as described in the prior work on the accelerators we studied in this work [77, 89, 114, 139]. CDMs studied in this work consist of multiple (128-32768) CDUs. Hence, though the overall area of a CDM is high, the design of the basic building block, CDU, is simple and can be implemented accurately (100 - 200 lines of Verilog code). Each CDU consists of storage elements for the swept space data and a collision detection circuit (CDC). Figure 7 represents the architecture of CDCs for different accelerators studied in this work. Further, we implement testbenches to verify the functionality and timing of the RTL models. We use a sample motion set, and perform collision detection for 10,000 environmental scenarios for functional verification. We further measure the timing of collision detection operation in terms of the number of cycles and validate with the reported data in the prior work [77, 89, 114, 139].

We synthesized our RTL models using the Synopsys Design Compiler [1] and the OpenRAM Memory Compiler [44] to estimate the area and power of storage elements in CDMs at 45nm technology (FreePDK45 design library [118]). Because we are interested in the relative area and power consumption of different storage elements and combinational circuits, the technology node's choice should not significantly impact the results. We build the microarchitectural simulators with Python. We model all sequential elements accurately in our microarchitectural model, and verify the collision detection output of these models for 10,000 environmental scenarios.

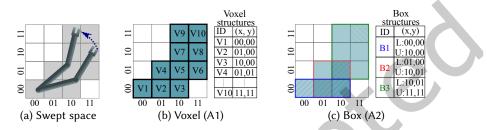

A1 (Base accelerator): This architecture was proposed by Murray et al. [89], and is based on the earlier proposed accelerator for FPGAs [90]. A motion's swept space is stored in registers using the 3D Cartesian coordinates of each voxel in the swept space. Figure 8a and 8b show how a swept space is converted to voxels. The collision detection circuit compares the obstacle occupancy voxels with each voxel in the swept space to find if the motion is in collision with obstacles (Figure 7a).

A2 (Spatial locality-aware accelerator): This architecture, proposed by Murray et al. [89] and Sorin et al. [114], is an optimization of A1. There is a significant degree of spatial locality in the voxels in a swept space; hence, contiguous voxels are merged into a larger box. A box can be represented by the coordinates of two diagonal

Fig. 7. CDU architecture block diagram for different CDMs.

Fig. 8. Voxelization and voxel/box based representation example in 2D. (a) Represents a robot and its motion in 2D. Shaded voxels represent the voxelized swept space. (b) Swept space is stored using coordinates (x,y) of individual voxels. (c) Contiguous voxels are combined into boxes and stored using diagonal voxels' coordinates (striped voxels). L and U represent lower and upper diagonal voxels; darker regions represent overlapping of multiple boxes.

voxels. Figure 8c gives an example. The CDC checks if an obstacle occupancy voxel is inside any of these boxes for collision detection (Figure 7b).

In A1 and A2, all on-chip registers are read in parallel by the collision detection logic instead of using a memory array with limited read ports. This design choice provides significant speedup. Thus all storage elements in A1 and A2 are treated as individual registers that can be protected using a latch protection technique (e.g., DMR or TMR).

A3 (Octree-based accelerator): This architecture was proposed by Lian et al. (2018) [77], and uses the octree structure to store the motion's swept space (shown in Figure 9 and explained in Section 3). Collision detection is performed by traversing the tree to find if obstacle occupancy voxels overlap with the swept space. Figure 7c represents the architecture of CDC for A3.

The proposed design of A3 uses 128 CDCs, where motions in the motion set are processed for collision detection in batches. Hence, there is no inter-query on-chip data reuse, which results in significant DRAM bandwidth requirement [139]. For comparison, we also study a scaled-up version of A3, called  $A3_{scaled}$ , where the number of CDCs is equal to A1 and A2 (32,768), and on-chip data is reused across multiple collision queries, reducing DRAM memory traffic. While the SDC-C probabilities for both A3 and  $A3_{scaled}$  are equal, their failure rates (CDF) are different due to differences in the sizes of their components and the value of *N* (Equation 3).

A4 (Flattened octree-based accelerator): This architecture was proposed by Yang et al. [139], and proposes processing-in-memory for collision detection with a flattened octree-based representation of the swept space. In the flattened octree-based representation, multiple levels of the trees can be flattened in a single level. For example, if all the levels of a 5-level tree are flattened, the resultant tree consists of a single root node with 32,768 children nodes, where each child node is 1 or 0 specifying occupancy of a single node. Such representation consumes more storage but facilitates efficient processing-in-memory, reducing data-movement overhead significantly.

5.3 Fault Injection (FI)

Fig. 9. Octree representation (figure reproduced from [77]). (a) represents the spatial division of the swept space, and (b) represents the corresponding Octree structure (A3).

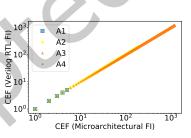

We use microarchitectural simulators for FI, as RTL-level FI was very slow. We use Dell EMC R440 CPU nodes. However, to validate the FI accuracy of our microarchitectural simulators, we perform 10,000 FI runs (uniformly distributed in space and time) on the microarchitectural and RTL models. For RTL-level FI, we use Cadence Incisive Functional Safety Simulator [15]. For microarchitectural FI, a fault is injected, and collision detection is performed. Figure 10 shows that the CEF values measured with microarchitectural FI and RTL-level FI have a 100% correlation accelerators A1-A4.

For CEF-aware FI, we determine the value of M (number of samples) per CEF group required to measure the SDC-C probability with 95% confidence level and 2.5% error margin [73]. The SDC-C probability and population size of the highest CEF group are used to determine the value of M, as these bits contribute the most to the overall SDC-C probability. In our experiments, the value of M is  $2 \times 10^6$ ,  $2 \times 10^5$ ,  $15 \times 10^3$ , and  $2 \times 10^6$  for A1, A2, A3 and A4 respectively. We represent soft errors as single-bit flips in hardware registers, which is consistent with most other papers studying the effects of soft errors [8, 20, 32, 132]. While we focus on single-bit flips, Equation (2) can be extended to accommodate a multi-bit fault model. We defer this to future work.

Fig. 10. CEF values measured by microarchitectural FI and Verilog RTLlevel FI for different CDMs.

#### 5.4 CDF Rate Calculation

To calculate the CDF rate of the accelerators, we use Equation (3), where *N* is the expected number of executions of the application before the bits are reloaded in on-chip storage, and its value depends on the accelerator's architecture and deployment. Reloading of data can be overlapped with collision detection to hide the DRAM accesses latency. We set the value of N = 3600 for the accelerators with inter-query data reuse (A1, A2, A3<sub>scaled</sub>, and A4), as the power overhead of DRAM accesses for refreshing data after 3600 collision detection queries is within 1%. We use FIT<sub>Raw</sub> = 177 FIT/Mb (for 45nm CMOS [6]) in Equation (3). Note that while the choice of N and FIT<sub>Raw</sub> affect the absolute values of the CDF rate, they affect neither our fault characterization nor CEF-aware error mitigation.

# 6 EVALUATION

In this section we present our results for fault characterization (Section 6.1) and error mitigation (Section 6.2) using CEF.

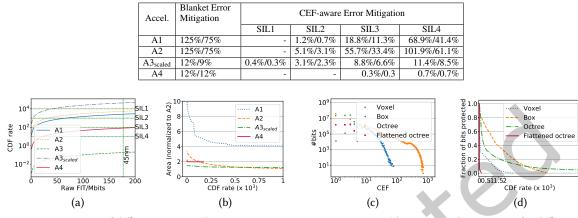

#### 6.1 Fault Characterization

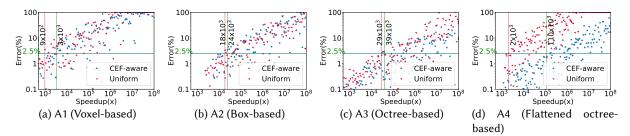

6.1.1 *CEF-aware FI*. In Section 4, we propose two-phase CEF-aware FI to reduce the number of FI runs. In CEF-aware FI, instead of performing FI for all the bits for multiple environment scenarios, we sample a subset from a group of bits with the same CEF value. This sampling introduces inaccuracies in the measured SDC-C probability and CDF rates compared to exhaustive FI. Figure 11 shows the speedup versus error of the calculated CDF rate for CEF-aware FI and uniform statistical FI. The speedup is the ratio of the number of exhaustive FI runs to that of CEF-aware FI or uniform FI.

Fig. 11. Error versus speedup for different FI approaches.

As can be seen from the figure, on average, CEF-aware FI achieves  $23,000 \times$  speedup over exhaustive FI (geometric mean) with 2.5% error margin. The vertical line represents the speedup for error less than 2.5%. The error margin can be reduced further at the cost of more FI trials (Section 4). Uniform statistical FI exhibits a similar speedup as CEF-aware FI over exhaustive FI. Note however that uniform statistical FI cannot be used to find vulnerable bits for selective error mitigation (Table 3). The speedup of CEF-aware FI over exhaustive FI is due to two reasons: (1) a significant fraction of bits have CEF equal to 0, and hence have very low or 0 SDC-C probability. CEF-aware FI ignores these bits for FI, (2) Only a few bits have high CEF and SDC-C probability, and hence contribute the most to overall SDC-C probability. CEF-aware FI segregates such bits and requires fewer samples to measure SDC-C. Phase 1 of CEF-aware FI consumes 1, 1, 2, and 1 CPU hours for A1, A2, A3, and A4, respectively. Phase 2 of CEF-aware FI consumes less than 2 CPU hours for A1, A2, A3, and A4, respectively.

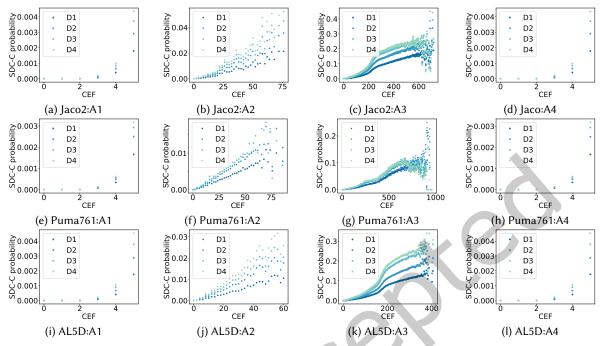

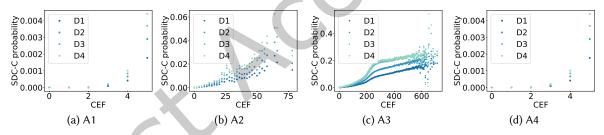

6.1.2 Evaluation of reliability metric. As discussed in Section 4, we propose the CEF as a reliability metric for the MPA's bits. We study the relationship between the CEF and the SDC-C probability of different bits to demonstrate the validity of CEF metric. The SDC-C probability of entire CDM is calculated using SDC-C probability of different CEF groups in Equation (2). We use the benchmarks [D1-D4] (Section 5.1). Figure 12 shows the SDC-C probability of bits with different CEF values for different accelerators, robots, and benchmarks. The CEF values are on the same scale for different accelerators for a given robot. A3 has a higher range of CEF values than other accelerators, which is also reflected in higher SDC-C values. Note that for A3, there is dispersion in SDC-C probability for bits with high CEF values. This occurs as a fault in a bit in the next\_addr field adds a large number of voxels in the represented swept space (green voxels in Figure 5g), which leads to positive collision detection between obstacles and erroneous expanded swept space, and reduces SDC-C probability for some bits with high CEF value. For all the benchmarks, the SDC-C probability of a bit increases as its CEF increases, except for a few bits in A3. Note that as the obstacle occupancy density increases, the SDC-C probability also increases, as there are higher chances that the soft error in a CDM will result in a collision. Thus, even though the relation between SDC-C probability and CEF is not linear, a monotonically non-decreasing relation demonstrates the validity of the CEF as a reliability factor. The SDC-C probability of bits is thus strongly positively correlated with their CEF values across benchmarks, which signifies that the CEF can be used as a reliability metric for MPAs.

*Nonuniform motion set.* We also validate the use of CEF as a reliability metric for a nonuniform motion set. In such a motion set, the motions are nonuniformly sampled in space. Figure 13 shows SDC-C probability versus CEF of bits for nonuniform motion sets. As shown in the figure, there is strong correlation between the SDC-C probability and CEF of bits, showing the validity of CEF for nonuniform motion sets.

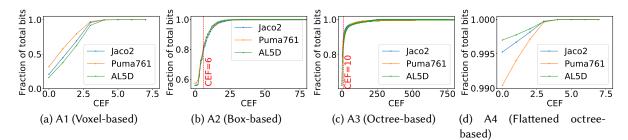

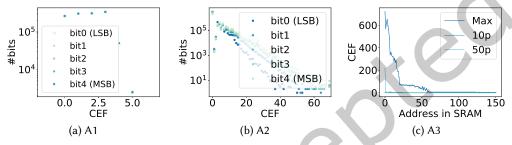

*6.1.3 Characterization of CEF.* To further understand the contribution of individual bits to the overall SDC-C probability, we group the bits according to their CEFs, and plot the cumulative distribution of bits in the CDM. Figure 14 shows that for all four CDMs, there is a high degree of asymmetry in the distribution of bits according to

Fig. 12. SDC-C probability versus CEF of accelerator A1-A4 for Jaco2, AL5D, and Puma761 robot on benchmarks D1-D4. Note that different plots have significantly varying ranges for the vertical axes.

Fig. 13. SDC-C probability versus CEF of accelerator A1, A2, A3, and A4 for Jaco2 for a nonuniform motion set. Note that different plots have significantly differing ranges for the vertical axes.

the CEF. For A1 and A4, 20% and 99% of the total bits have CEF equal to 0, respectively, and do not need to be protected. On the other hand, for A2, only 20% of the total bits have CEF greater than 6 and significantly contribute to the overall SDC-C probability. Thus, protecting only 20% bits can reduce the CDF rate by 60%, as we show in Section 6.2. Similarly, in A3, only 15% of the total bits have a CEF greater than 10. We further examine the CEF distribution asymmetry for each accelerator.

A1: In A1, each structure/variable stores a voxel using its coordinates to represent a part of the swept space. A soft error in any bit of the coordinate will result in misrepresentation of that voxel, and so bit position does not affect CEF range (Figure 15a).

A2: The effect of faults in different bits of coordinates is shown in Figure 15b. The CEF range of bits decreases from the most significant bit (MSB) to the least significant bit (LSB), as a fault in the MSB is likely to result in a higher change in the box size represented by a pair of coordinates than LSB. Thus, the number of bits with

Fig. 14. Cumulative distribution of CEF of all bits. The vertical axis starts from 0.99 for A4 as more than 99% of the bits have CEF equal to 0.

Fig. 15. CEF characterization of bit position/SRAM address.

high CEF values increases from LSB to MSB. For example, the ratio between the number of MSBs (*bit*4) and the number of LSBs (*bit*0) with CEF = 20 is 1000.