## Modeling, Analysis, and Design of Switched-Capacitor Battery Cell Balancers

by

Mario A. Lopez

S.B. Electrical Science and Engineering Massachusetts Institute of Technology, 2021 Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of Master of Engineering in Electrical Engineering and Computer Science at the MASSACHUSETTS INSTITUTE OF TECHNOLOGY September 2023 © 2023 Mario A. Lopez. All rights reserved. The author hereby grants to MIT a nonexclusive, worldwide, irrevocable, royalty-free license to exercise any and all rights under copyright, including to reproduce, preserve, distribute and publicly display copies of the thesis, or release the thesis under an open-access

license.

| Authored by:  | Mario A. Lopez<br>Dept. of Electrical Engineering and Computer Science<br>August 28, 2023 |

|---------------|-------------------------------------------------------------------------------------------|

| Certified by: | James L. Kirtley Jr.<br>Professor of Electrical Engineering<br>Thesis Supervisor          |

| Certified by: | William A. Lynch<br>Research Specialist<br>Thesis Supervisor                              |

| Accepted by:  | Katrina LaCurts<br>Chair, Master of Engineering Thesis Committee                          |

### Modeling, Analysis, and Design of Switched-Capacitor Battery Cell Balancers

by

Mario A. Lopez

Submitted to the Department of Electrical Engineering and Computer Science on August 28, 2023, in partial fulfillment of the requirements for the degree of Master of Engineering in Electrical Engineering and Computer Science

#### Abstract

Battery systems have become crucial components in many modern technological solutions. Battery balancers are among the most important parts of these systems because they play a significant role in the battery's lifespan and performance. A novel capacitive-based balancer was designed and tested for two cell and four cell batteries. The key parameters that were optimized are efficiency, balancing time, volume, and cost. A theoretical model of the circuit was derived to guide design optimization. Additionally, simulations were created to predict performance. Custom printed circuit boards were developed and tested.

Thesis Supervisor: James L. Kirtley Jr. Title: Professor of Electrical Engineering

Thesis Supervisor: William A. Lynch Title: Research Specialist

### Acknowledgments

I have been very fortunate to have Prof. James Kirtley and Dr. William Lynch as advisors. I am thankful for the opportunity to work in their lab group and the creative freedom they've allowed me in pursuing this research.

I would like to thank Navy Capt (RET) Lynn J. Peterson and the Office of Naval Research (ONR) for funding our research enterprise.

I am grateful for my lab mates, Ahmad Negm, Rolando Gonzalez, and Aklilu Aron. Their friendship was instrumental in pushing me through tough times.

I want to extend my thanks to Elaine Ng for her help with LaTeX formatting and the final push towards my thesis.

Finally, and most importantly, I would like to thank my family for their love and support. This work wouldn't have happened without my parents, Mario and Patricia, and brother, Alex.

Thank you all.

# Contents

| 1 Introduction |                                   | 17                                                         |    |  |

|----------------|-----------------------------------|------------------------------------------------------------|----|--|

|                | 1.1                               | 1 Background                                               |    |  |

|                |                                   | 1.1.1 Batteries                                            | 18 |  |

|                |                                   | 1.1.2 Battery Balancing                                    | 20 |  |

|                |                                   | 1.1.3 Switched-Capacitor Converters (SCC)                  | 21 |  |

|                | 1.2                               | Current Gaps in Literature                                 | 22 |  |

|                | 1.3                               | Thesis Contributions                                       | 22 |  |

|                | 1.4                               | Thesis Outline                                             | 23 |  |

| 2              | Mo                                | eling and Analysis of Switched-Capacitor Battery Balancers | 25 |  |

|                | 2.1 Canonical 2-Cell SCC Balancer |                                                            |    |  |

|                |                                   | 2.1.1 Static Analysis                                      | 27 |  |

|                |                                   | 2.1.2 Equivalent Impedance                                 | 29 |  |

|                |                                   | 2.1.3 Dynamic Analysis                                     | 31 |  |

|                | 2.2                               | 2 Canonical Balancer Generalization                        |    |  |

|                |                                   | 2.2.1 Multi-Tier Topology                                  | 33 |  |

|                |                                   | 2.2.2 3S Multi-Tier Analysis                               | 36 |  |

|                |                                   | 2.2.3 4S Multi-Tier Analysis                               | 38 |  |

|                |                                   | 2.2.4 NS Multi-Tier Analysis                               | 42 |  |

| 3              | Cor                               | paring Switched Capacitor Balancing Topologies             | 43 |  |

|                | 3.1                               | Topologies                                                 |    |  |

|                | 3.2                               | Balance Speed Comparison                                   | 45 |  |

| Imp | olemen                                                                                                                          | tation of SCC Balancer                                                                                                                                                                                                                                                                              | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1 | 2S NO                                                                                                                           | CH Design                                                                                                                                                                                                                                                                                           | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.1.1                                                                                                                           | LC Tank                                                                                                                                                                                                                                                                                             | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

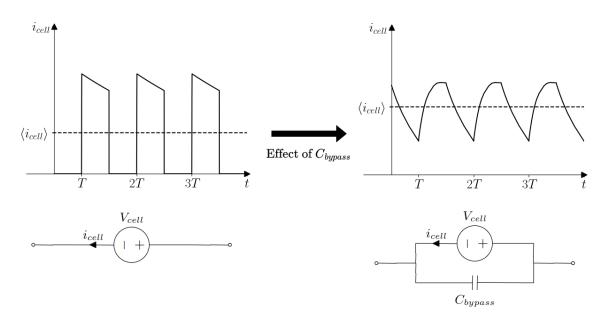

|     | 4.1.2                                                                                                                           | Input Bypass Capacitors                                                                                                                                                                                                                                                                             | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

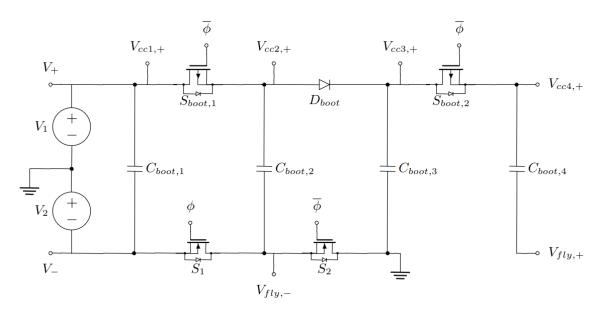

|     | 4.1.3                                                                                                                           | Switches and Bootstrap                                                                                                                                                                                                                                                                              | 51                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.1.4                                                                                                                           | Gate Drive                                                                                                                                                                                                                                                                                          | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

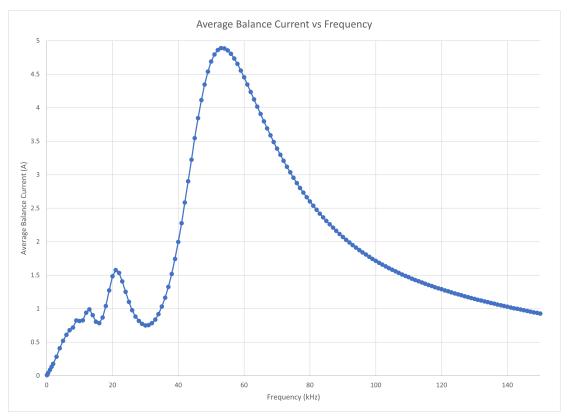

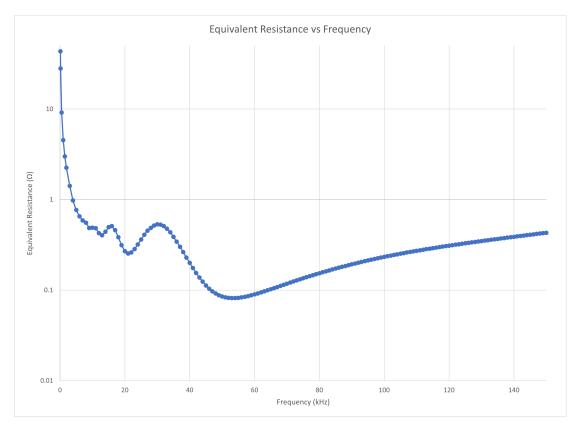

|     | 4.1.5                                                                                                                           | Testing                                                                                                                                                                                                                                                                                             | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.2 | 2S NO                                                                                                                           | CH+PCH Design                                                                                                                                                                                                                                                                                       | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.2.1                                                                                                                           | LC Tank                                                                                                                                                                                                                                                                                             | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.2.2                                                                                                                           | Input Bypass Capacitors                                                                                                                                                                                                                                                                             | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.2.3                                                                                                                           | Switches and Bootstrap                                                                                                                                                                                                                                                                              | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.2.4                                                                                                                           | Gate Drive                                                                                                                                                                                                                                                                                          | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.2.5                                                                                                                           | Testing                                                                                                                                                                                                                                                                                             | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.3 | Comp                                                                                                                            | aring Practical 2S Designs                                                                                                                                                                                                                                                                          | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.3.1                                                                                                                           | Balance Time                                                                                                                                                                                                                                                                                        | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.3.2                                                                                                                           | Volume and Cost                                                                                                                                                                                                                                                                                     | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.4 | 4S De                                                                                                                           | $\operatorname{sign}$                                                                                                                                                                                                                                                                               | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.4.1                                                                                                                           | LC Tank                                                                                                                                                                                                                                                                                             | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.4.2                                                                                                                           | Input Bypass Capacitors                                                                                                                                                                                                                                                                             | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.4.3                                                                                                                           | Switches and Bootstrap                                                                                                                                                                                                                                                                              | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.4.4                                                                                                                           | Gate Drive                                                                                                                                                                                                                                                                                          | 63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | 4.4.5                                                                                                                           | Testing                                                                                                                                                                                                                                                                                             | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Cor | iclusio                                                                                                                         | ns                                                                                                                                                                                                                                                                                                  | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.1 | Mode                                                                                                                            | ling and Analysis                                                                                                                                                                                                                                                                                   | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.2 | Desig                                                                                                                           | n                                                                                                                                                                                                                                                                                                   | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 5.3 | Future                                                                                                                          | e Work                                                                                                                                                                                                                                                                                              | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Tab | les                                                                                                                             |                                                                                                                                                                                                                                                                                                     | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Fig | ures                                                                                                                            |                                                                                                                                                                                                                                                                                                     | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|     | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.4</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> <li>Tab</li> </ul> | 4.1 2S NG<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>4.1.3<br>4.1.4<br>4.1.5<br>4.2 2S NG<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.3<br>4.2.4<br>4.2.5<br>4.3 Comp<br>4.3.1<br>4.3.2<br>4.4<br>4.5<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>4.4.5<br>Conclusio<br>5.1 Model<br>5.2 Design<br>5.3 Future | 4.1.1       LC Tank         4.1.2       Input Bypass Capacitors         4.1.3       Switches and Bootstrap         4.1.4       Gate Drive         4.1.5       Testing         4.1.6       Gate Drive         4.1.7       Testing         4.1.4       Gate Drive         4.1.5       Testing         4.2       2S NCH+PCH Design         4.2.1       LC Tank         4.2.2       Input Bypass Capacitors         4.2.3       Switches and Bootstrap         4.2.4       Gate Drive         4.2.5       Testing         4.2.6       Gate Drive         4.2.7       Testing         4.3       Comparing Practical 2S Designs         4.3.1       Balance Time         4.3.2       Volume and Cost         4.4       4S Design         4.4.1       LC Tank         4.4.2       Input Bypass Capacitors         4.4.3       Switches and Bootstrap         4.4.4       Gate Drive         4.4.3       Switches and Bootstrap         4.4.4       Gate Drive         4.4.5       Testing         5.1       Modeling and Analysis         5.3 </td |

| $\mathbf{C}$ | Equations               |        |                        |     | 99  |

|--------------|-------------------------|--------|------------------------|-----|-----|

|              | C.1                     | Princi | ple of Virtual Work    | •   | 99  |

|              | C.2 Equations of Motion |        | •                      | 100 |     |

|              |                         | C.2.1  | 3S Equations of Motion |     | 100 |

|              |                         | C.2.2  | 4S Equations of Motion |     | 100 |

# List of Figures

| 1-1  | Alessandro Volta with two of his inventions: the electric battery (left) |    |

|------|--------------------------------------------------------------------------|----|

|      | and the electrophorus [22]                                               | 18 |

| 1-2  | Battery Cell Diagram [23]                                                | 19 |

| 1-3  | Lithium iron phosphate cell (LiFePO4 battery)                            | 19 |

| 1-4  | Battery state of charge in various balancing modes [25]                  | 20 |

| 2-1  | Canonical Switching Cell                                                 | 25 |

| 2-2  | SCC Balancer Abstraction                                                 | 26 |

| 2-3  | Canonical 2S SCC Battery Balancer                                        | 26 |

| 2-4  | Switching State of 2S SCC Balancer                                       | 27 |

| 2-5  | Square Wave Input to Flying Capacitor                                    | 27 |

| 2-6  | Equivalent Circuit Model of 2S SCC Balancer                              | 28 |

| 2-7  | Ideal Equivalent Impedance vs Frequency                                  | 30 |

| 2-8  | Practical Equivalent Impedance vs Frequency                              | 30 |

| 2-9  | Equivalent Circuit Model of Dynamic 2S SCC Balancer                      | 31 |

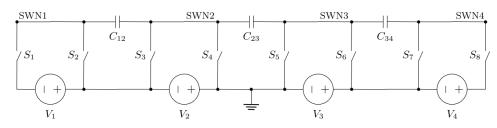

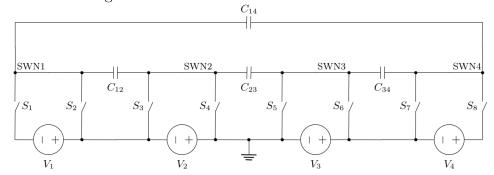

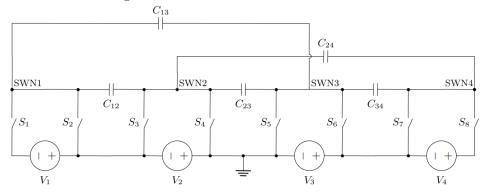

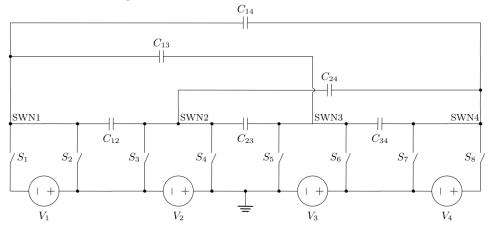

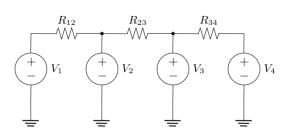

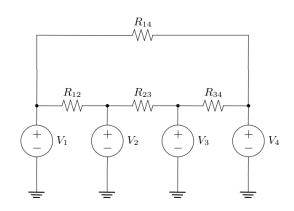

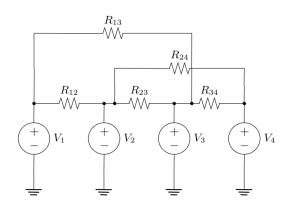

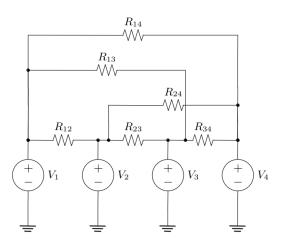

| 2-10 | Conventional or Flat 4S Balancer                                         | 34 |

| 2-11 | Double-Tier 1 4S Balancer                                                | 34 |

| 2-12 | Double-Tier 2 4S Balancer                                                | 34 |

| 2-13 | Multi-Tier 4S Balancer                                                   | 34 |

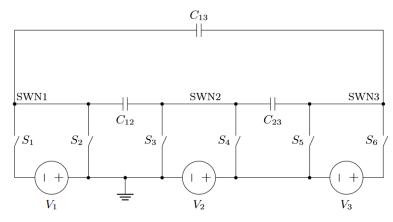

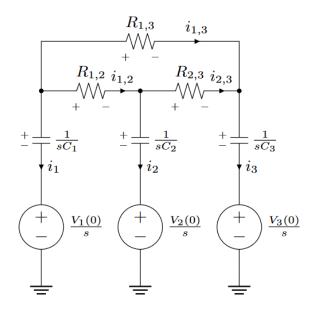

| 2-14 | 38 Multi-Tier Balancer                                                   | 37 |

| 2-15 | Average Model for 3S Multi-Tier                                          | 37 |

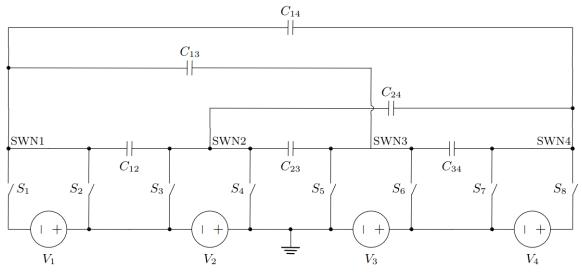

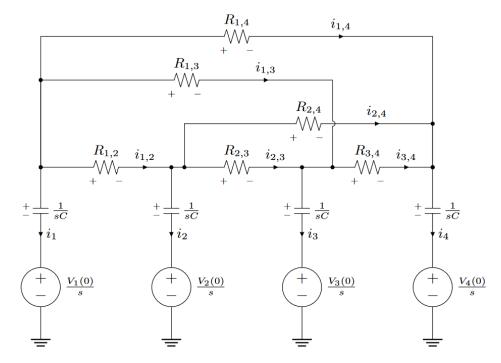

| 2-16 | 4S Multi-Tier Balancer                                                   | 39 |

| 2-17 | Average Model for 4S Multi-Tier                                          | 39 |

| 3-1        | 4S Flat Average Model                            | 44 |

|------------|--------------------------------------------------|----|

| 3-2        | 4S Double-Tier 1 Average Model                   | 44 |

| 3-3        | 4S Double-Tier 2 Average Model                   | 44 |

| 3-4        | 4S Multi-Tier Average Model                      | 44 |

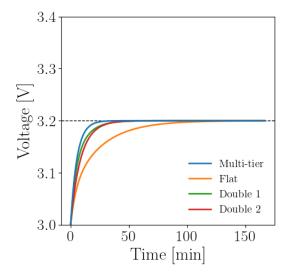

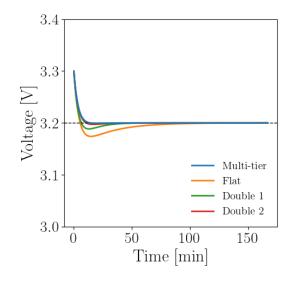

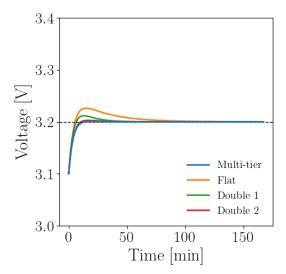

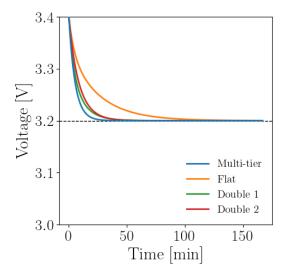

| 3-5        | $V_1$ Simulated Waveform for Initial Condition 5 | 46 |

| 3-6        | $V_2$ Simulated Waveform for Initial Condition 5 | 46 |

| 3-7        | $V_3$ Simulated Waveform for Initial Condition 5 | 46 |

| 3-8        | $V_4$ Simulated Waveform for Initial Condition 5 | 46 |

| 4-1        | Effect of Bypass Capacitors on Cell Current      | 51 |

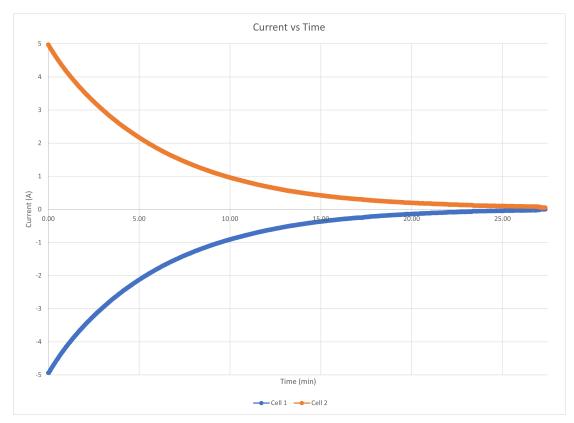

| 4-2        | Bootstrap Circuit for 2S NCH Balancer            | 52 |

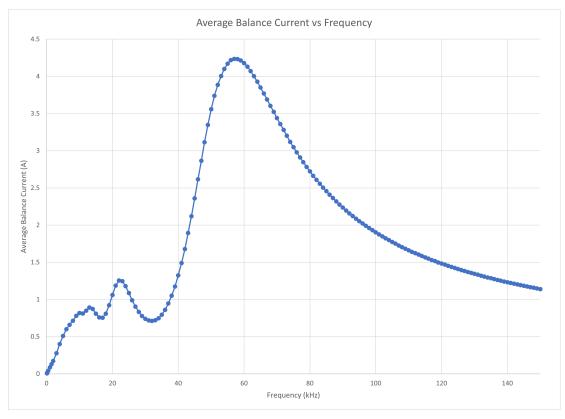

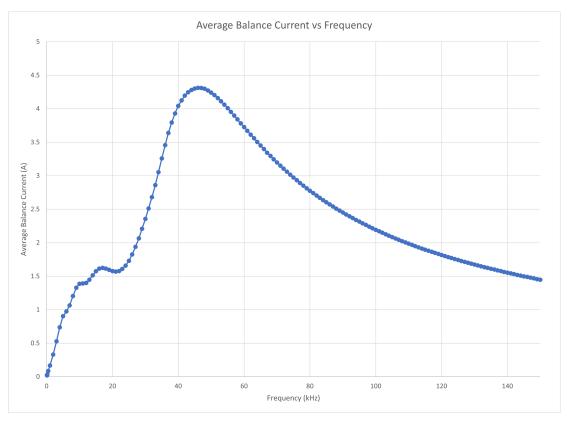

| 4-3        | 2S NCH Average Balance Current vs Frequency      | 55 |

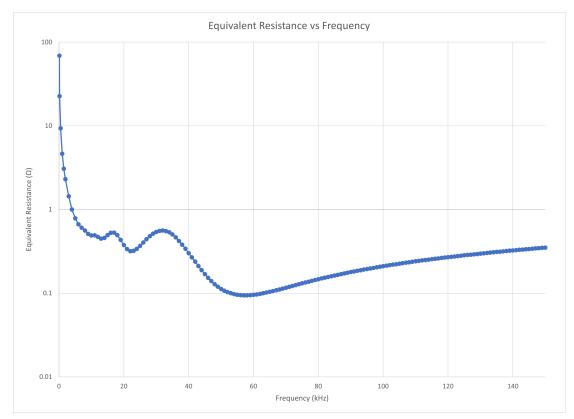

| 4-4        | 2S NCH $R_{eq}$                                  | 55 |

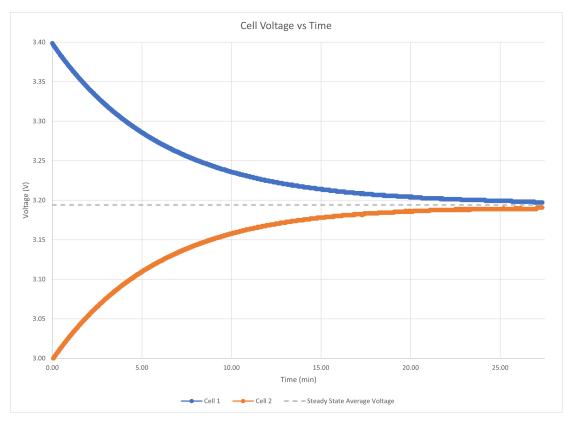

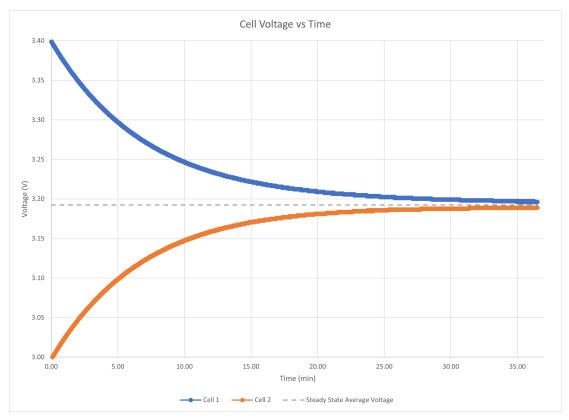

| 4-5        | 2S NCH Dynamic Cell Voltages                     | 56 |

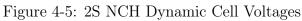

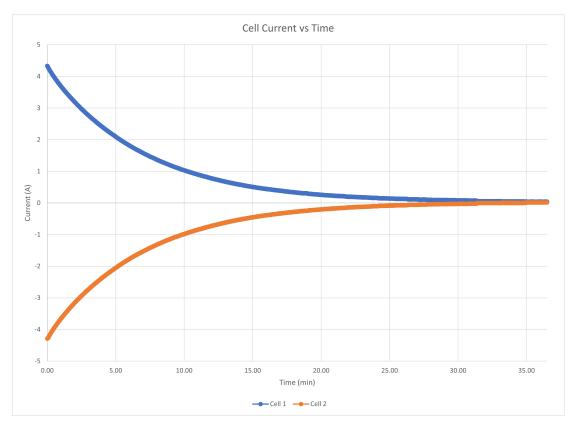

| 4-6        | 2S NCH Dynamic Cell Currents                     | 56 |

| 4-7        | Bootstrap Circuit for 2S NCH+PCH Balancer        | 58 |

| 4-8        | 2S NCH+PCH Average Balance Current vs Frequency  | 60 |

| 4-9        | 2S NCH+PCH $R_{eq}$                              | 60 |

| 4-10       | 2S NCH+PCH Dynamic Cell Voltages                 | 61 |

| 4-11       | 2S NCH+PCH Dynamic Cell Currents                 | 61 |

| 4-12       | 4S Average Balance Current vs Frequency          | 65 |

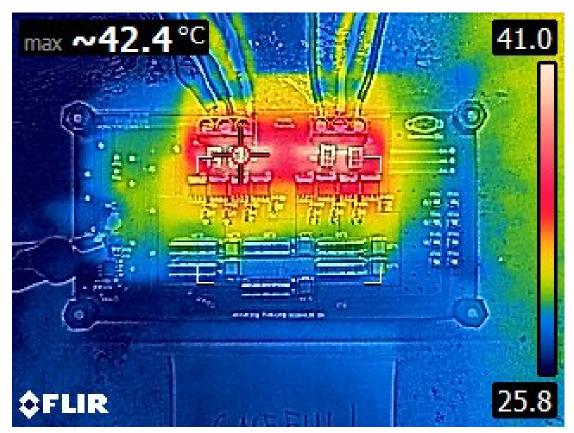

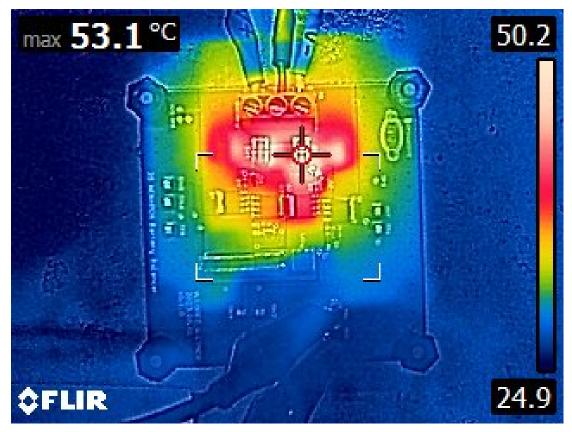

| 4-13       | 4S Thermal Test                                  | 65 |

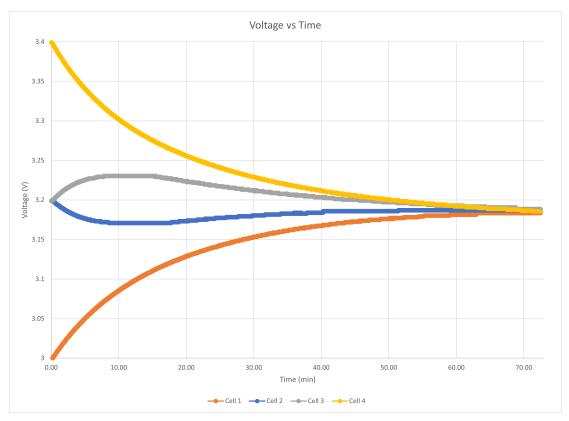

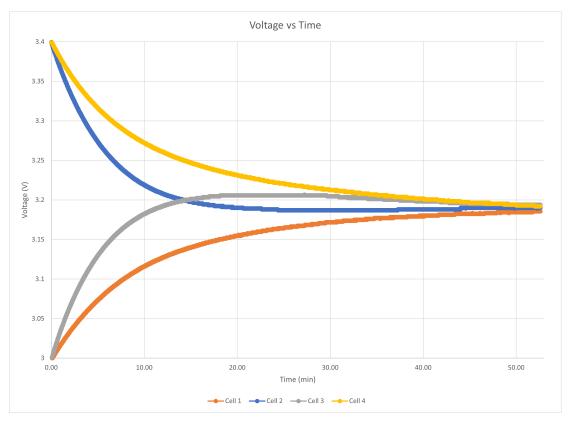

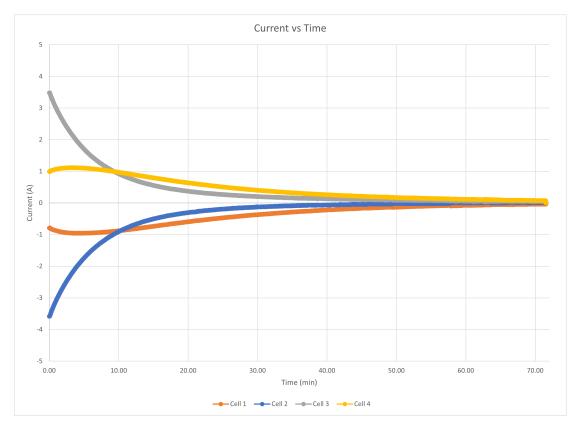

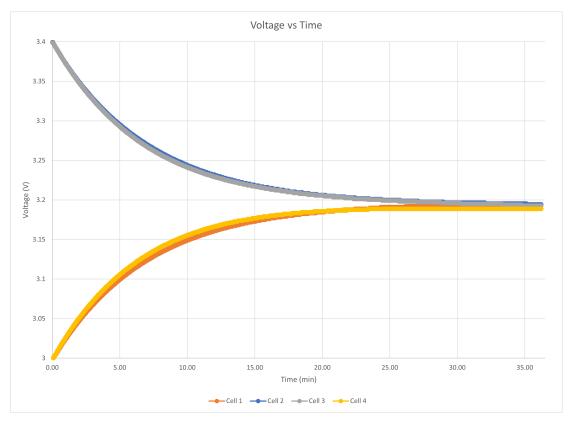

| 4-14       | 4S Dynamic Balance Test 3 Cell Voltages          | 66 |

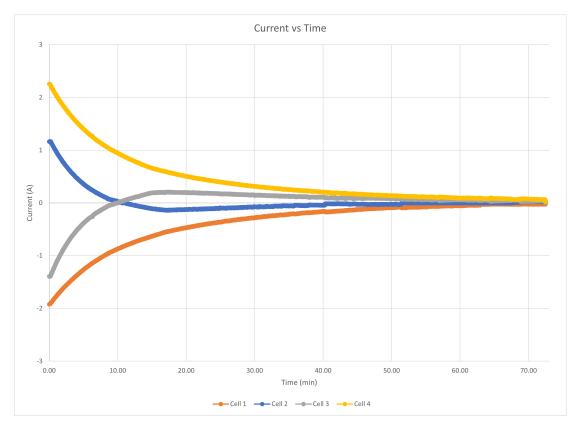

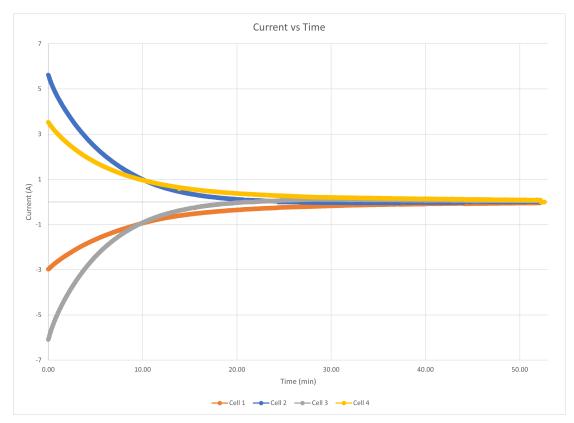

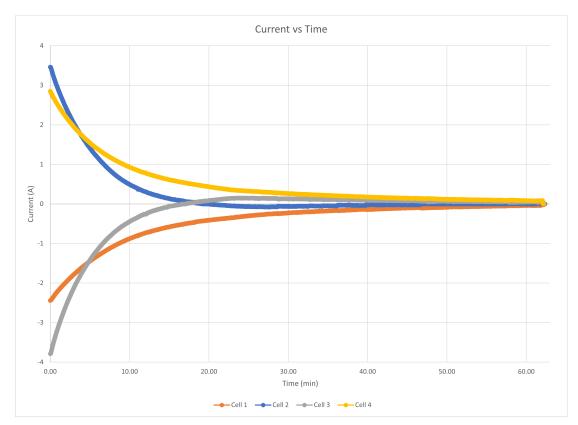

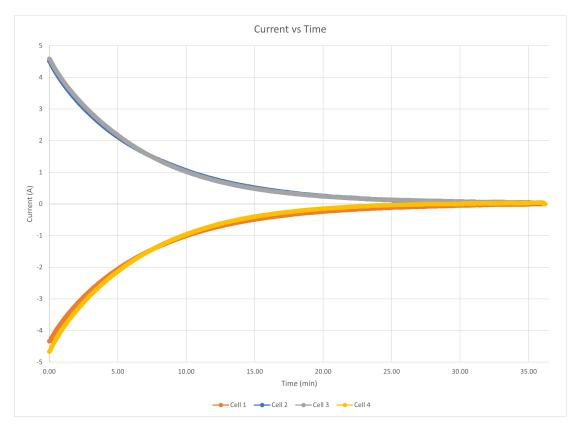

| 4-15       | 4S Dynamic Balance Test 3 Cell Currents          | 66 |

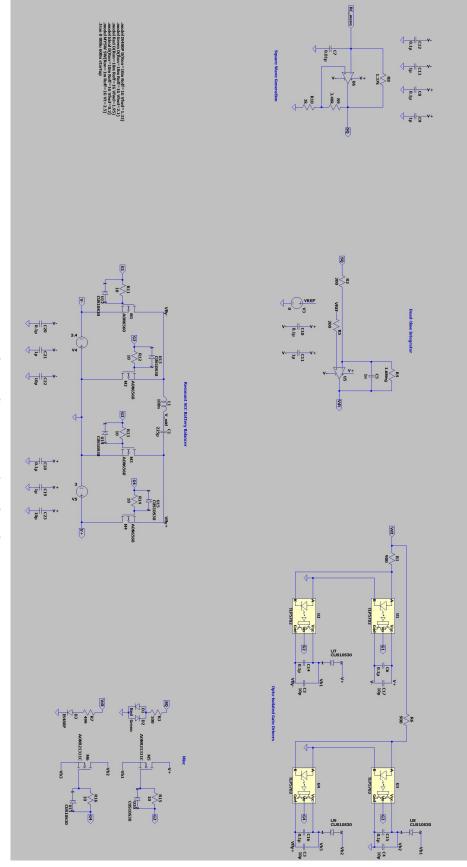

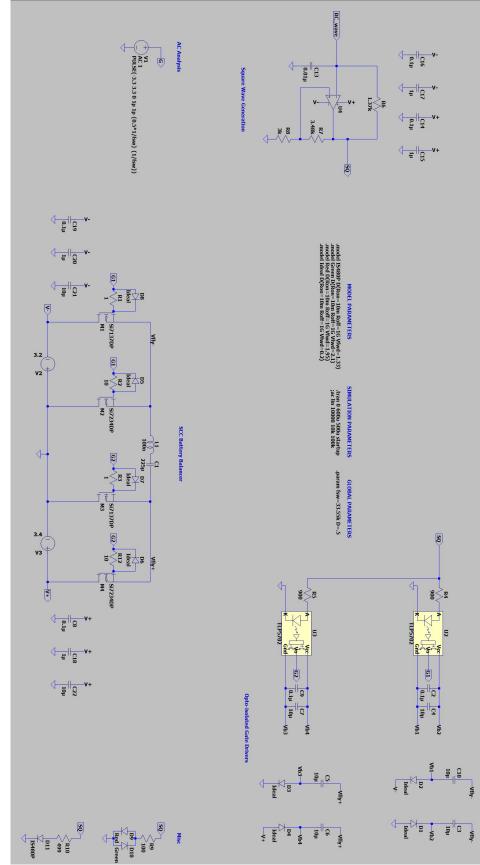

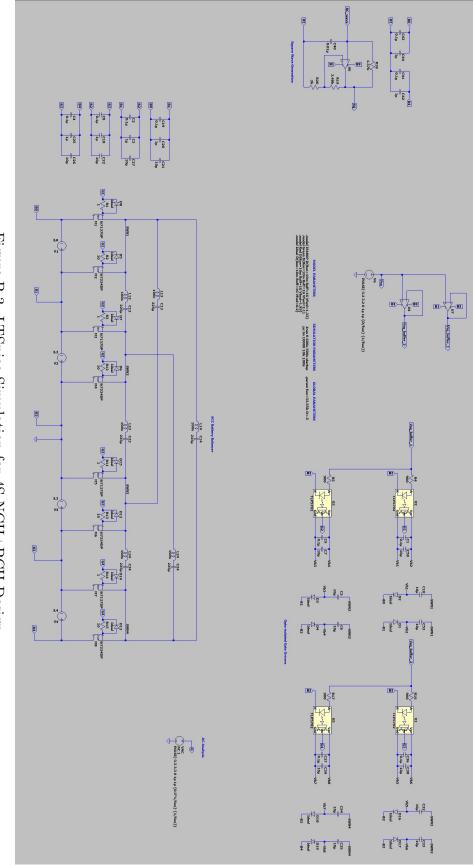

| B-1        | LTSpice Simulation for 2S NCH Design             | 76 |

| B-2        | LTSpice Simulation for 2S NCH+PCH Design         | 77 |

| B-3        | LTSpice Simulation for 4S NCH+PCH Design         | 78 |

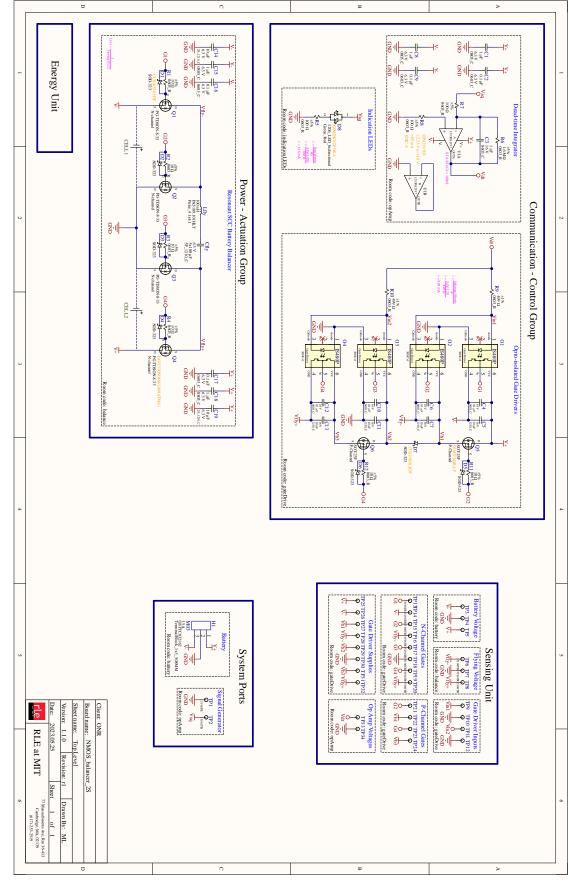

| B-4        | 2S NCH Balancer Schematic                        | 79 |

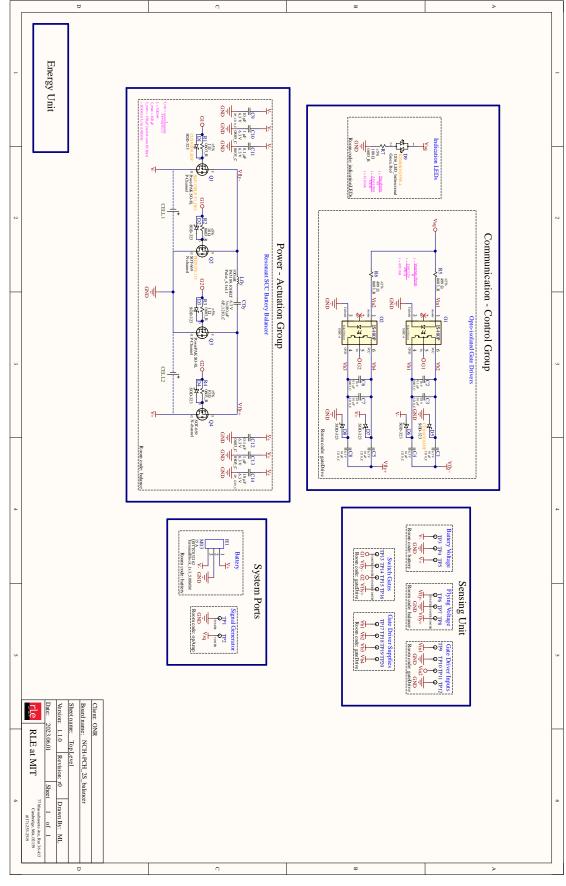

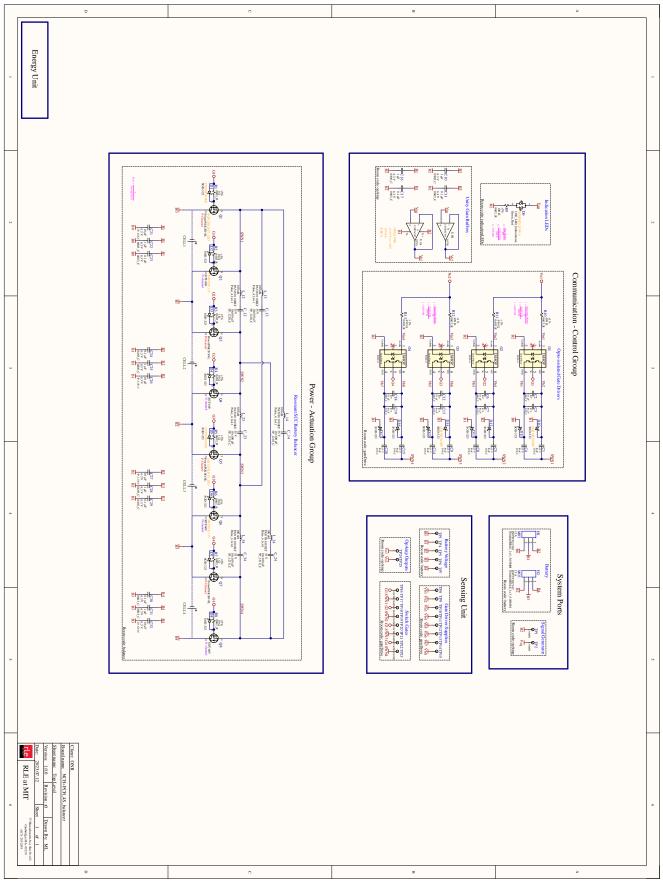

| B-5        | 2S NCH+PCH Balancer Schematic                    | 80 |

| <b>B-6</b> | 4S NCH+PCH Balancer Schematic                    | 81 |

| B-8 2S NCH Balancer Bottom Layout                                                                                           |

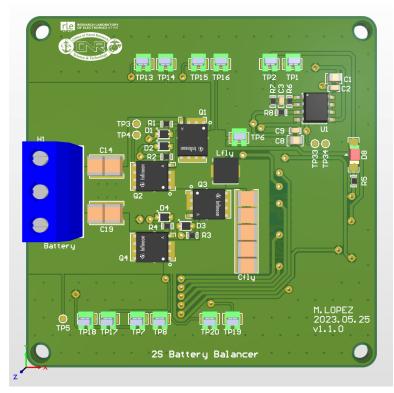

|-----------------------------------------------------------------------------------------------------------------------------|

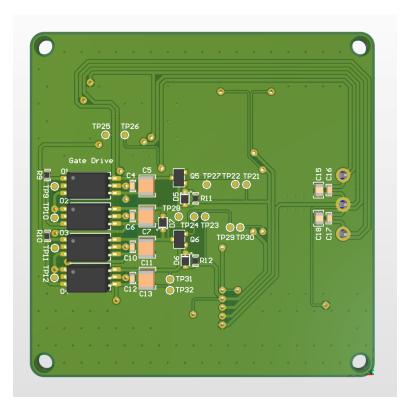

| B-9 2S NCH Balancer PCB Top View                                                                                            |

| B-10 2S NCH Balancer PCB Bottom View                                                                                        |

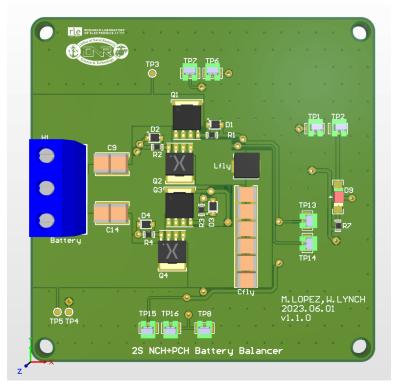

| B-11 2S NCH+PCH Balancer Top Layout                                                                                         |

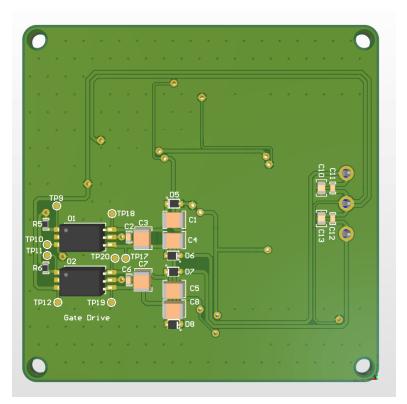

| B-12 2S NCH+PCH Balancer Bottom Layout                                                                                      |

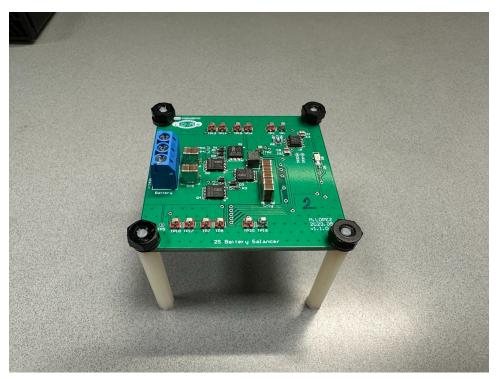

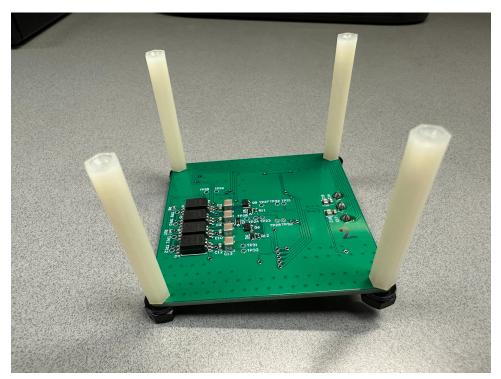

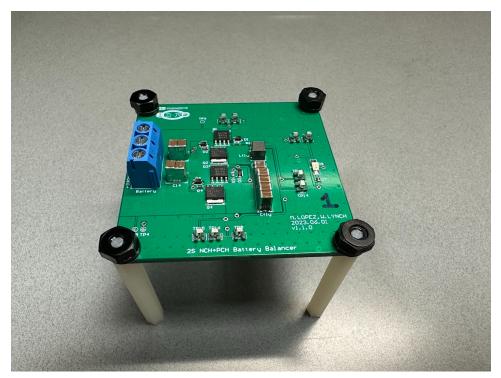

| B-13 2S NCH+PCH Balancer PCB Top View                                                                                       |

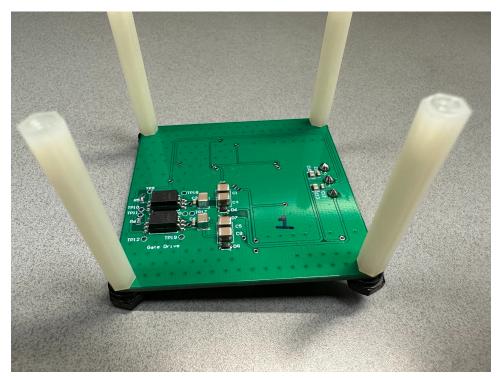

| B-14 2S NCH+PCH Balancer PCB Bottom View                                                                                    |

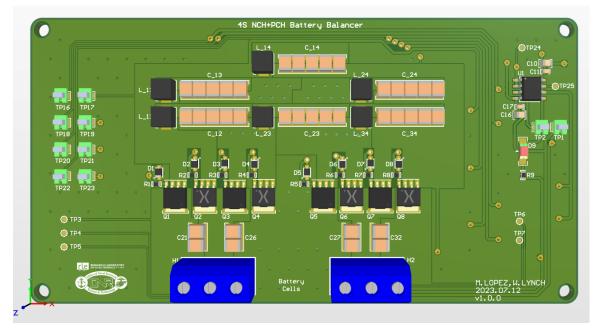

| B-15 4S NCH+PCH Balancer Top Layout                                                                                         |

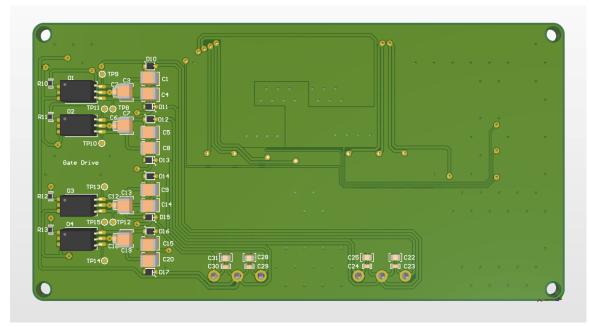

| B-16 4S NCH+PCH Balancer Bottom Layout                                                                                      |

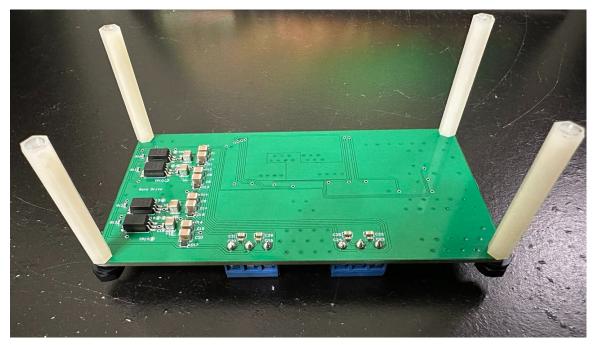

| B-17 4S NCH+PCH Balancer PCB Top View                                                                                       |

| B-18 4S NCH+PCH Balancer PCB Bottom View                                                                                    |

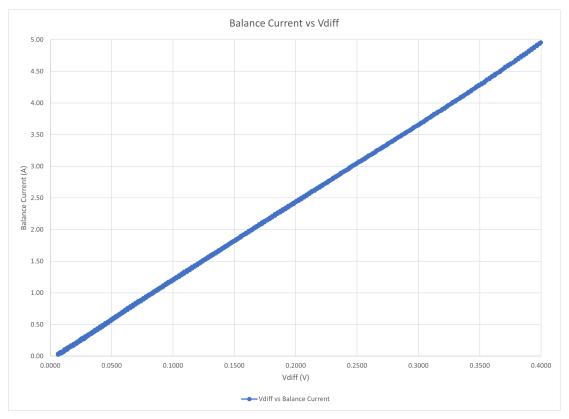

| B-19 2S NCH Dynamic Balance Current vs $\Delta V$                                                                           |

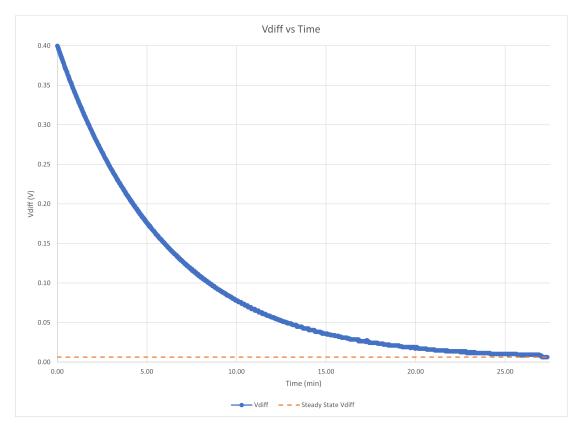

| B-20 2S NCH Dynamic $\Delta V$                                                                                              |

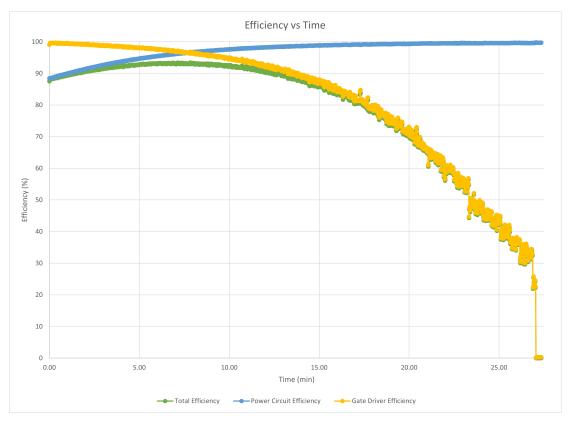

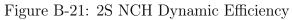

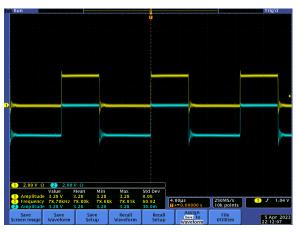

| B-21 2S NCH Dynamic Efficiency                                                                                              |

| B-22 2S NCH Efficiency vs $\Delta V$                                                                                        |

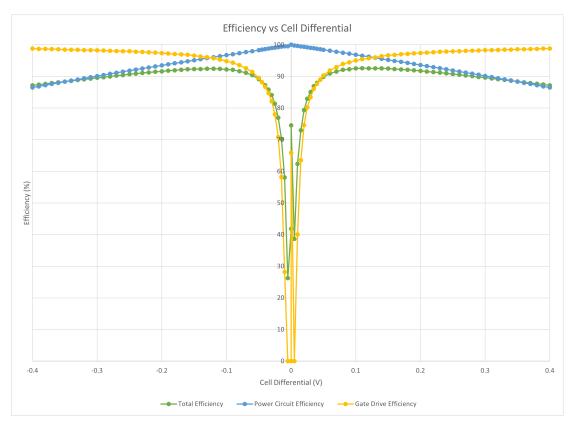

| B-23 2S NCH Balancer Deadtime Verification                                                                                  |

| B-24 2S NCH Balancer Quasi-Synchronous Bootstrap Verification ( $V_{GS}$ shown                                              |

| for each switch)                                                                                                            |

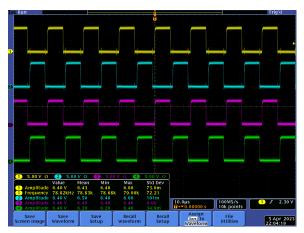

| B-25 2S NCH Balancer Switching Node Voltages                                                                                |

| B-26 2S N+P Dynamic Balance Current vs $\Delta V$                                                                           |

| B-27 2S N+P Dynamic $\Delta V$                                                                                              |

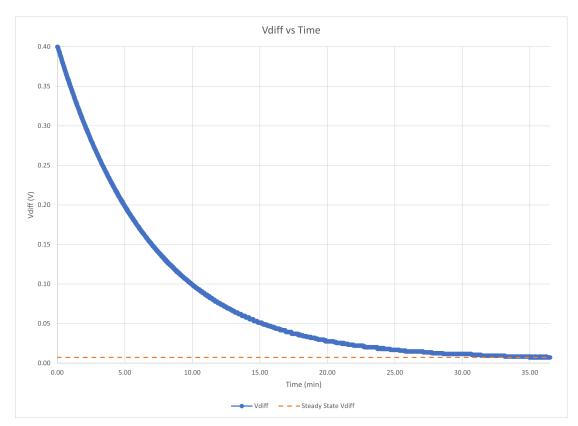

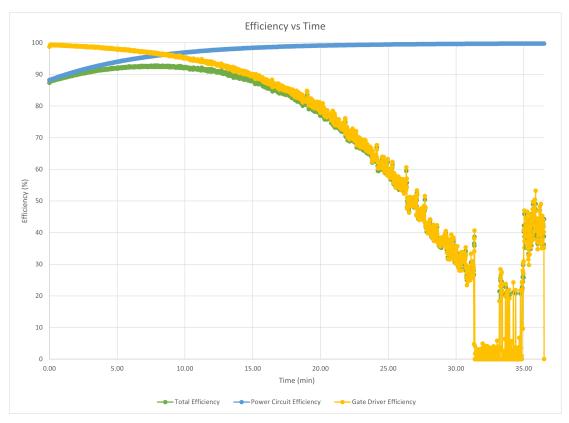

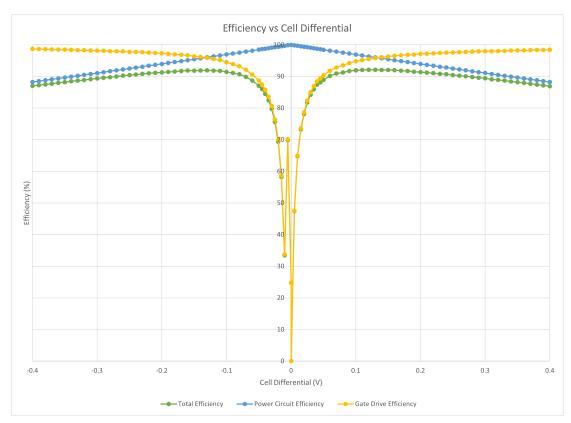

| B-28 2S N+P Dynamic Efficiency                                                                                              |

| B-29 2S N+P Efficiency vs $\Delta V$                                                                                        |

| B-30 2S N+P Thermal Test at $\Delta V = 0.6$ V $\dots \dots 93$ |

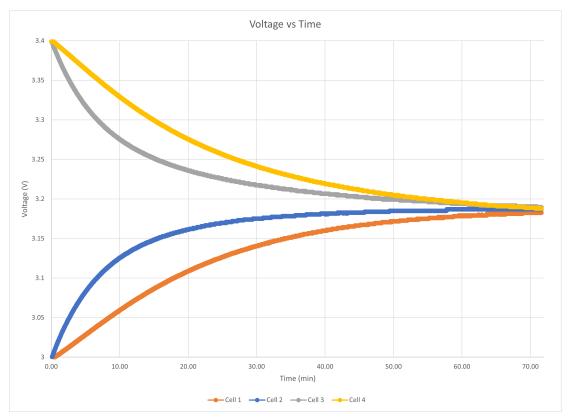

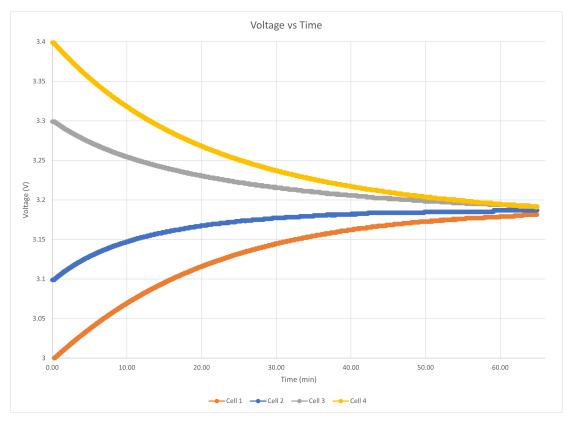

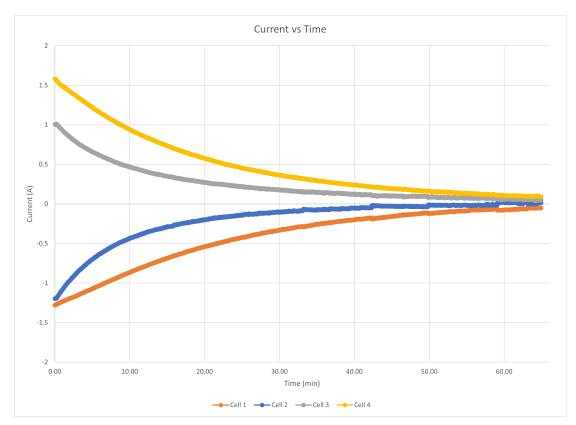

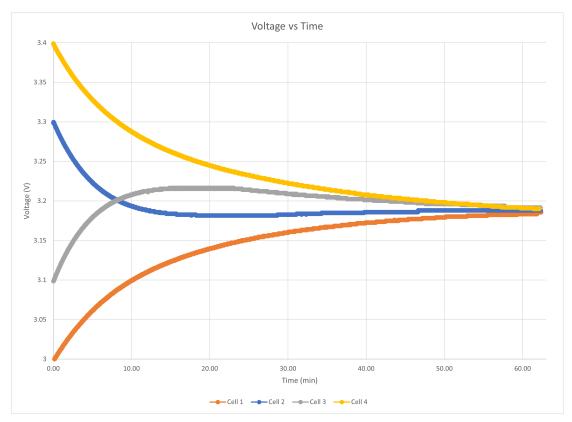

| B-31 4S Dynamic Balance Test 1 Cell Voltages                                                                                |

| B-32 4S Dynamic Balance Test 1 Cell Currents                                                                                |

| B-33 4S Dynamic Balance Test 2 Cell Voltages                                                                                |

| B-34 4S Dynamic Balance Test 2 Cell Currents                                                                                |

|                                                                                                                             |

| B-36 4S Dynamic Balance Test 4 Cell Currents | 96 |

|----------------------------------------------|----|

| B-37 4S Dynamic Balance Test 5 Cell Voltages | 97 |

| B-38 4S Dynamic Balance Test 5 Cell Currents | 97 |

| B-39 4S Dynamic Balance Test 6 Cell Voltages | 98 |

| B-40 4S Dynamic Balance Test 6 Cell Currents | 98 |

# List of Tables

| 3.1 | Comparison on Capacitor Number, Switch Number, and Capacitor Stress  | 43 |

|-----|----------------------------------------------------------------------|----|

| 3.2 | Balance Time Comparison Simulation Parameters                        | 45 |

| 3.3 | Battery Cell Voltages for Different Initial Conditions               | 45 |

| 3.4 | Comparison of Balance Times for Different Initial Conditions (ICs) . | 45 |

| 3.5 | Battery Cell Voltages for Different Initial Conditions               | 47 |

| 4 1 |                                                                      | 00 |

| 4.1 | Measured Balance Times for 2S Balancers                              | 62 |

| 4.2 | Measured Balance Times for 4S Balancer                               | 64 |

| A.1 | Components of 2S NCH Balancer v1.1.0                                 | 70 |

| A.2 | Components of 2S NCH+PCH Balancer v1.1.0                             | 71 |

| A.3 | Components of 4S NCH+PCH Balancer v1.0.0                             | 72 |

| A.4 | Lab Equipment                                                        | 72 |

| A.5 | Battery Cell Emulation Parameters                                    | 72 |

| A.6 | Balance Time Comparison Between Commercial Balancer and 4S NCH+P     | СН |

|     | Multi-Tier Balancer                                                  | 73 |

# Chapter 1

# Introduction

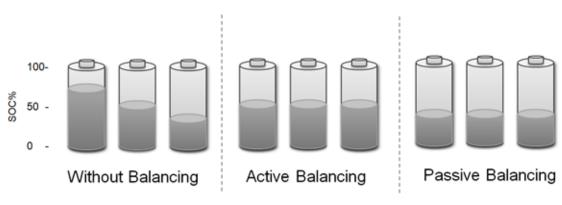

With the latest trends towards electric vehicles and renewable energy storage, battery systems have continued to play an important role in the modern technological land-scape. Many batteries are made up of multiple small cells in series (a battery with N cells is referred to as an NS battery) whose charge is nominally identical. However, due to manufacturing tolerances and temperature differences, when a battery pack is placed into operation, different cells in the system can discharge at different rates. This causes the state of charge (SOC) in the cells to differ, which can reduce the lifespan of the battery since some cells can overcharge or undercharge. Thus, battery balancing circuits are needed for batteries with greater longevity [2].

There are two primary ways of balancing: passive and active. Passive balancing involves removing excess charge from cells by using resistors. This means dissipating energy away as heat until the charge of higher SOC cells matches the charge of lower SOC cells in the battery pack. These balancers are simple and cheap, but are extremely inefficient as they bring high energy losses. Active balancing is much better in this regard since it involves moving charge from higher energy cells into lower energy cells. The main trade-off with active balancers is usually complex control circuitry. There are many topologies for active balancing including capacitive, inductive, and transformer based. This thesis will work primarily with capacitive-based balancing topologies [3].

### 1.1 Background

#### 1.1.1 Batteries

Batteries are electrochemical devices that store and provide electrical energy for various applications. They are used in a wide range of devices, from small electronics like cell phones and laptops to larger applications like electric cars and power grids. The invention of the modern battery is often attributed to Alessandro Volta, who created the first true battery in 1800 [24].

Figure 1-1: Alessandro Volta with two of his inventions: the electric battery (left) and the electrophorus [22].

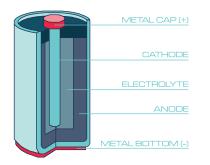

Batteries consist of one or more cells, which are units that convert chemical energy into electrical energy. Each cell contains an anode, a cathode, and an electrolyte. The anode is the negative electrode, and the cathode is the positive electrode. The electrolyte is the medium that allows the flow of ions between the anode and cathode. When a battery is connected to a circuit, a chemical reaction occurs in the cell that creates a flow of electrons, which generates an electrical current in the circuit [24].

Figure 1-2: Battery Cell Diagram [23]

Figure 1-3: Lithium iron phosphate cell (LiFePO4 battery)

There are many different types of batteries, including alkaline, lead-acid, nickelcadmium, and lithium-ion. Each type has its own unique characteristics, such as energy density, voltage, and lifespan [28]. Rechargeable batteries, also known as secondary cells, can be recharged and used multiple times, while non-rechargeable batteries, also known as primary cells, can only be used once and must be disposed of afterwards.

Figure 1-4: Battery state of charge in various balancing modes [25]

Passive and active battery balancing are two different techniques used to balance the state of charge (SOC) of individual cells in a battery pack. The main differences between passive and active battery balancing are [2, 3]:

Passive Battery Balancing:

- Dissipates excess charge from higher SOC cells through a bleed resistor or bypass route

- Simple and cost-effective to implement

- May result in energy losses and heat generation due to the dissipation of excess charge

- Does not redistribute charge between cells during the charging and discharging cycle

Active Battery Balancing:

- Redistributes charge between cells during the charging and discharging cycle

- Utilizes inductive or capacitive charge shuttling to transfer charge between cells

- More complex and expensive to implement compared to passive balancing

• Increases system run-time and charging efficiency by utilizing excess charge from higher SOC cells

Both passive and active battery balancing techniques have their advantages and disadvantages [2, 3]. The choice of balancing technique depends on factors such as the battery chemistry, desired balancing accuracy, power handling capability, and cost considerations. The remainder of the thesis will focus on a subset of active balancing techniques, namely capacitive based balancing in the form of switchedcapacitor converters.

#### 1.1.3 Switched-Capacitor Converters (SCC)

Switched capacitor converters are a fundamental building block of analog integrated circuit design [16]. They are electronic circuits that use capacitors to transfer charge when electronic switches are turned on and off. These circuits are used for a variety of applications, including voltage conversion and energy transfer. SCC have several trade-offs when compared to magnetic-based converters including:

Advantages of switched capacitor converters [8, 13]:

- Smaller size and lower weight due to the absence of magnetic components

- Higher efficiency at low power levels

- Easier to integrate into a chip due to their simple structure and lower output power requirements

Disadvantages of switched capacitor converters [8, 10]:

- Lower efficiency at high power levels

- Limited output power because of the limited charge transfer capability of capacitors

- Higher output voltage ripple due to the discrete nature of the capacitor charge transfer

• Limited frequency range due to component parasitics

Overall, switched capacitor converters are ideal for low-power applications, where size and weight are critical, and efficiency is more important than output power. However, for high-power applications, magnetic-based converters are preferred due to their higher efficiency and power handling capabilities.

#### **1.2** Current Gaps in Literature

There is extensive analysis and study dedicated to 2S SCC balancers [7, 10, 11, 20, 21]. However, improvements can be made in low-entropy modeling of and theoretical insight into the behavior of higher order SCC balancers [18, 27, 30, 32, 33]. The author envisions an impedance-based approach to modeling of higher order balancers to yield balance time constants for every battery cell and gain intuition on how each cell voltage waveform evolves over time. The author believes that this can be achieved through the application of clever circuit techniques [6, 17, 19]. Lastly, there also seems to be some SCC balancer topologies that remain undiscovered.

### **1.3** Thesis Contributions

The shortcomings in the current state of SCC battery balancing as outlined in Section 1.2 presents opportunities for theoretical insights and improvement of practical circuit design. This thesis aims to address some of these gaps through the following contributions:

- 1. Insights into modeling and analysis of higher order balancers. A potential pathway to an analytical solution is shown.

- 2. Presentation of a new SCC balancing topology

- 3. Practical implementation of the latter.

### 1.4 Thesis Outline

The goal of this thesis is to address some of the gaps in SCC battery balancing circuits. In Chapter 2, we describe the modeling and analysis of these circuits starting from their fundamental building block: the canonical 2S SCC battery balancer. We perform a static and dynamic analysis on this balancer, deriving an average model of circuit behavior to gain intuition into its operation and to drive practical design methodology. This model is then generalized for higher order balancers. Additionally, a pathway for theoretical insights and meaningful analytical solutions are discussed. The chapter will also introduce a new balancing topology. Chapter 3 applies the derived models on various SCC topologies to compare their balancing times. In Chapter 4, we build three practical SCC battery balancers, the final one being our proposed balancer topology. Experimental results, practical design considerations, and part selection are also provided. Chapter 5 closes this thesis with conclusions on the modeling, analysis, and design of SCC battery balancers. We also present opportunities for future investigations.

# Chapter 2

# Modeling and Analysis of Switched-Capacitor Battery Balancers

### 2.1 Canonical 2-Cell SCC Balancer

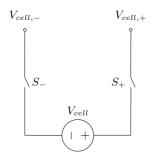

The fundamental building block for all SCC balancer topologies is the canonical switching cell. It is comprised of two switches: one connected to the negative terminal of the battery cell, and the other connected to the positive terminal. This canonical switching cell connects to an energy tank (usually comprised of capacitors and/or inductors), which transfers charge efficiently from higher energy cells to lower energy cells.

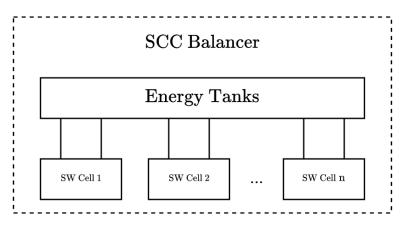

Figure 2-1: Canonical Switching Cell

All SCC battery balancers are essentially energy tanks interfacing with each switching cell such that the average voltage of the cells in aggregate is imparted as a steady state voltage constraint on all N cells:  $\lim_{t\to\infty} V_{cell,n}(t) = \frac{V_{battery}}{N}$  (see Fig. 2-2) where  $V_{cell,n}$  is the voltage of the *n*th cell and  $V_{battery}$  is the battery voltage. One way to prove this equilibrium condition is through the principle of virtual work, as shown in Appendix C.1 [31].

Figure 2-2: SCC Balancer Abstraction

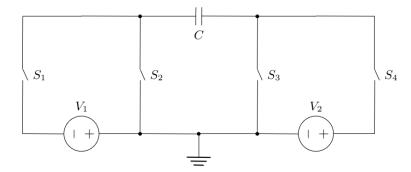

We can use 2 canonical switching cells connected together by a capacitive energy tank to construct the simplest possible 2S SCC battery balancer (see Fig. 2-3). The

Figure 2-3: Canonical 2S SCC Battery Balancer

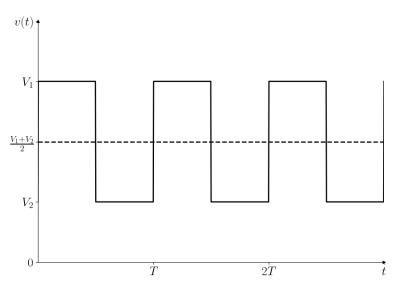

odd numbered switches share the same state and are complementary to the even numbered switches. This means that in a given switching state, one of the cells ( $V_1$ or  $V_2$ ) will be connected in parallel with the flying capacitor energy tank C (see Fig. 2-4). The resistor R is the combination of capacitor series resistance (ESR) and the resistance of the switches. The switches are controlled via pulse width modulation (PWM) with duty cycle D and switching frequency  $f_s$ . From the point of view of the

Figure 2-4: Switching State of 2S SCC Balancer

flying capacitor, it will see a pulse wave input oscillating between  $V_1$  and  $V_2$  with a DC average of  $DV_1 + (1 - D)V_2$  and AC peak-to-peak amplitude<sup>1</sup> of  $\Delta V = V_1 - V_2$ . These SCC circuits typically operate with D = 0.5 to minimize impedance [15]. Thus, the average flying capacitor voltage  $\langle V_c \rangle = \frac{V_1 + V_2}{2}$  (refer to Fig. 2-5). We also know from periodic steady state (PSS) analysis that  $\langle i_c \rangle = 0$  [4].

Figure 2-5: Square Wave Input to Flying Capacitor

#### 2.1.1 Static Analysis

We can initially model the battery cells as ideal voltage sources to gain intuition on the static operation of the circuit and then relax this constraint later to perform a dynamic analysis. We can model the average behavior of the circuit by defining an

<sup>&</sup>lt;sup>1</sup>This assumes that  $V_1 > V_2$ .

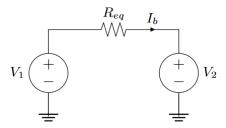

equivalent impedance  $R_{eq}$  that connects the unbalanced battery cells and carries out the charge transfer (see Fig. 2-6) [5, 10]. The cell voltage differential and equivalent

Figure 2-6: Equivalent Circuit Model of 2S SCC Balancer

impedance determine the balance current  $I_b = \frac{\Delta V}{R_{eq}}$ . By inspection of Fig. 2-6, one can see that  $\langle i_1 \rangle = -\langle i_2 \rangle = -I_b$ , where  $i_1$  and  $i_2$  are the battery cell currents. It is worth noting that in most practical designs, there will be some difference in the magnitude of  $\langle i_1 \rangle$  and  $\langle i_2 \rangle$  due to resistive mismatches in the circuit. It is thus better to define the balance current as

$$I_b = \frac{|\langle i_1 \rangle| + |\langle i_2 \rangle|}{2} \tag{2.1}$$

The power loss through the flying capacitor will be determined by its root mean square (RMS) current, which can be expressed as  $i_{RMS} = \sqrt{i_{DC}^2 + i_{RMS,AC}^2}$ . Since  $i_{DC} = \langle i_c \rangle = 0$ , then  $i_{RMS} = i_{RMS,AC}$ . From Fourier analysis, it can be shown that  $i_{RMS,total} = \sqrt{\sum_{k=1}^{N} i_{k,RMS}^2}$  if the set of  $i_k$  form an orthogonal basis [4]. With this in mind, we can express the capacitor RMS current as

$$i_{c,RMS} = \sqrt{i_{1,RMS}^2 + i_{2,RMS}^2} \tag{2.2}$$

Assuming resistive symmetry,  $i_{1,RMS} \approx i_{2,RMS}$  and therefore  $i_{c,RMS} \approx \sqrt{2} \cdot i_{1,RMS}$ . The average power loss in the flying capacitor is thus

$$\langle P_{c,loss} \rangle = i_{c,RMS} \cdot V_{c,RMS} \approx \sqrt{2} \cdot i_{1,RMS} \cdot \frac{V_1 + V_2}{2}$$

(2.3)

Note that  $V_{c,RMS} \approx \frac{V_1+V_2}{2}$  if the capacitor voltage ripple is sufficiently small, as is in the case if the equivalent impedance is dominated by the circuit series resistances. It is crucial to understand why and how  $R_{eq}$  changes as a function of both switching frequency and duty cycle [15, 16].

#### 2.1.2 Equivalent Impedance

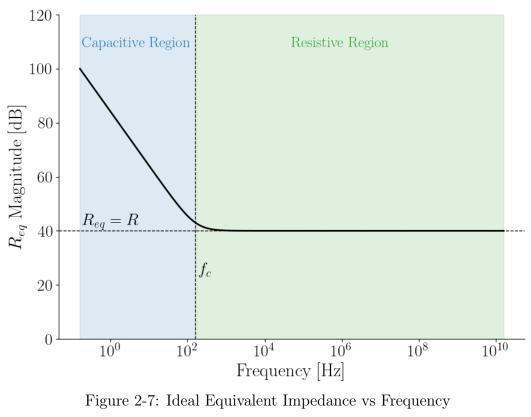

We can define the circuit time constant  $\tau = RC$  (see Fig. 2-4) and compare its magnitude to the switching period  $T_s$ . From here, we can distinguish between 3 different regions for  $R_{eq}$  as the switching frequency is varied. If  $\tau \ll T_s$ , then the capacitor fully charges and discharges within each switch period. This implies that  $R_{eq}$  will behave as a capacitive impedance (see leftmost region of Fig. 2-7). If  $\tau \gg T_s$ , the capacitor voltage ripple is approximately linear since the charge interchange is very small. This causes  $R_{eq}$  to behave as a resistive impedance (see rightmost region of Fig. 2-7). Finally, if  $\tau \approx T_s$ , there is partial charge interchange from the capacitor to the cells. This will cause  $R_{eq}$  to behave as an intermediate impedance between the two main regions (refer to the curved section of impedance curve in Fig. 2-7). This characterizes the transition from the capacitive region to the resistive region. The total impedance formula is commonly approximated as

$$R_{eq,total} \approx \sqrt{R_{SSL}^2 + R_{FSL}^2} \tag{2.4}$$

where  $R_{SSL}$  is the impedance in the capacitive region (slow switching limit) and  $R_{FSL}$ is the impedance in the resistive region (fast switching limit) [15]. The 2S canonical SCC balancer has  $R_{SSL} = \frac{1}{f_sC}$  and  $R_{FSL} = \frac{R}{D(1-D)}$ . However, it is worth noting that in practice, there is an additional region to  $R_{eq}$ .

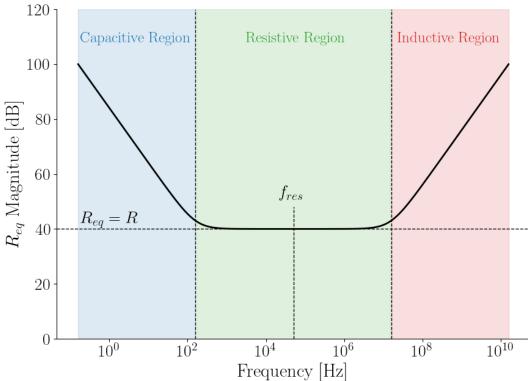

A practical  $R_{eq}$  curve is shown in Fig. 2-8. There will always be some stray (or intentional) inductance present in any practical circuit and as such will affect the equivalent impedance. This third region is commonly referred to as the inductive switching limit (ISL) [12]. The transition to ISL will depend upon the circuit's quality factor Q. For an *RLC* circuit whose impedances depend on duty cycle, the quality

Figure 2-8: Practical Equivalent Impedance vs Frequency

factor is

$$Q = \frac{2\pi f_{res}L}{R} \tag{2.5}$$

where  $f_{res} = \frac{D}{\pi\sqrt{LC}}$ . The Q factor will approach zero as L becomes smaller. This will cause the transition from the resistive region to the inductive region to occur at an arbitrarily large frequency and the practical RLC impedance curve will look more like the ideal RC impedance curve. It is recommended to operate the circuit near resonance for high Q factors, which can also occur if R or D is low with L fixed. Additionally, variations in duty cycle will change the magnitude and frequency cutoffs of  $R_{eq}$  throughout the various regions in Fig. 2-7 and 2-8. For a detailed discussion on the trade-offs involved with intentionally augmenting the flying capacitor's impedance with a series inductor, please refer to [12, 34].

#### 2.1.3 Dynamic Analysis

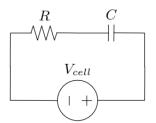

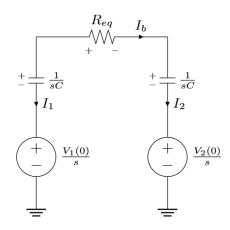

To approximate the 2S canonical SCC balancer's dynamic behavior, we can replace the ideal voltage sources with a simple battery cell model in the form of a very large capacitor. This will approximate a real battery cell's behavior in its linear region of operation. This opens up the opportunity for meaningful analytical solutions and thus provides a reasonable estimate on balancer performance. One can utilize more complicated cell models to predict battery cell performance beyond the linear region, but we will utilize this large capacitor model for the remainder of this thesis [28].

Figure 2-9: Equivalent Circuit Model of Dynamic 2S SCC Balancer

We will begin by replacing  $V_1$  and  $V_2$  with capacitors  $C_1$  and  $C_2$  (see Fig. 2-9). Each capacitor is initialized to the respective voltage of its original ideal voltage source. Furthermore, let  $C_1 = C_2 = C$ . We now can take the Laplace transform of each circuit element to construct its *s*-domain analog. The equations of motion for this circuit (KVL and KCL) are

$$V_1(s) - I_b R_{eq} - V_2(s) = 0 (2.6)$$

$$V_1(s) - \frac{V_1(0)}{s} - \frac{I_1}{sC} = 0$$

(2.7)

$$V_2(s) - \frac{V_2(0)}{s} - \frac{I_2}{sC} = 0$$

(2.8)

$$I_1 + I_2 = 0 (2.9)$$

$$I_b - I_2 = 0 (2.10)$$

This is just a first-order linear system of ordinary differential equations (ODEs). Solving this system yields the following voltage equations

$$V_1(t) = \left\{ t \ge 0 : \frac{V_{batt}}{2} + \frac{\Delta V_{12}}{2} e^{\frac{-2t}{RC}} \right\}$$

(2.11)

$$V_2(t) = \left\{ t \ge 0 : \frac{V_{batt}}{2} - \frac{\Delta V_{12}}{2} e^{\frac{-2t}{RC}} \right\}$$

(2.12)

where  $V_{batt}(t) = V_1(0) + V_2(0) = V_1(t) + V_2(t)$  since we shall assume that  $\frac{d}{dt}V_{batt} = 0$ . Additionally, we express the initial voltage differential as  $\Delta V_{12} = V_1(0) - V_2(0)$ . This system is comprised of two poles (or eigenvalues) at locations  $\lambda_k = [0, -\frac{2}{RC}]$ , which characterize system stability and settling time. Since  $\Re(\lambda_k) \leq 0$ , the system is stable [26]. The balance time  $\tau_b$  can be expressed as

$$\tau_b = \frac{RC}{2} \ln \left( \frac{|\Delta V_{12}|}{\Delta v_b} \right) \tag{2.13}$$

The balanced voltage differential  $\Delta v_b$  is chosen arbitrarily by the circuit designer. We will use  $\Delta v_b = 10$  mV for numerical characterization of the balance time in later sections of this thesis. The average efficiency of the balance process is

$$\eta_b(t) = \frac{P_{out}}{P_{in}} = \frac{\min\left(|i_1V_1|, |i_2V_2|\right)}{\max\left(|i_1V_1|, |i_2V_2|\right)}$$

(2.14)

If we assume that  $V_1 \ge V_2$  and utilize Eq. (2.9), then  $\eta_b(t) = \frac{V_2(t)}{V_1(t)}$ . Thus, the average balance process efficiency is purely determined by the distance between battery cell voltages. If the linear region of the cell voltages is constrained to be within the range [3.0, 3.4], as is generally the case with LiFePO4 battery cells, then the minimum average balance efficiency is  $\eta_{min} = \frac{3}{3.4} = 0.882$  [14].

### 2.2 Canonical Balancer Generalization