### Efficient Algorithms, Hardware Architectures and Circuits for Deep Learning Accelerators

by

Miaorong Wang

B.S., Shanghai Jiao Tong University (2016) S.M., Massachusetts Institute of Technology (2018)

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 2023

© Miaorong Wang 2023. All rights reserved.

The author hereby grants to MIT a nonexclusive, worldwide, irrevocable, royalty-free license to exercise any and all rights under copyright, including to reproduce, preserve, distribute and publicly display copies of the thesis, or release the thesis under an open-access license.

| Authored by:  | Miaorong Wang<br>Department of Electrical Engineering and Computer Science<br>August 18, 2023                                                             |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Certified by: | Anantha P. Chandrakasan<br>Vannevar Bush Professor of Electrical Engineering and Computer Science<br>Dean, MIT School of Engineering<br>Thesis Supervisor |

| Accepted by:  | Leslie A. Kolodziejski                                                                                                                                    |

Accepted by: Leslie A. Kolodziejski Professor of Electrical Engineering and Computer Science Chair, Department Committee on Graduate Students

### Efficient Algorithms, Hardware Architectures and Circuits for Deep Learning Accelerators

by

Miaorong Wang

Submitted to the Department of Electrical Engineering and Computer Science on August 18, 2023, in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

#### Abstract

Deep learning has permeated many industries due to its state-of-the-art ability to process complex data and uncover intricate patterns. However, it is computationally expensive. Researchers have shown in theory and practice that the progress of deep learning in many applications is heavily reliant on increases in computing power, and thus leads to increasing energy demand. That may impede further advancement in the field. To tackle that challenge, this thesis presents several techniques to improve the energy efficiency of deep learning accelerators while adhering to the accuracy and throughput requirements of the desired application.

First, we develop hybrid dataflows and co-design the memory hierarchy. That enables designers to trade off the reuse between different data types across different storage elements provided by the technology for higher energy efficiency. Second, we propose a weight tuning algorithm and accelerator co-design, which optimizes the bit representation of weights for energy reduction. Last, we present VideoTime<sup>3</sup>, an algorithm and accelerator co-design for efficient real-time video understanding with temporal redundancy reduction and temporal modeling. Our proposed techniques enrich accelerator designers' toolkits, pushing the boundaries of energy efficiency for sustainable advances in deep learning.

Thesis Supervisor: Anantha P. Chandrakasan

Title: Vannevar Bush Professor of Electrical Engineering and Computer Science

Dean, MIT School of Engineering

### Acknowledgments

This thesis would not have been possible without the help of a large group of people. First of all, I would like to express my sincere gratitude to my thesis supervisor, Professor Anantha P. Chandrakasan, for his guidance and support throughout my doctoral journey. I feel very fortunate to have had the opportunity to work under his mentorship. He is always very supportive and provides a great environment for me to learn and grow. Also, I am very fortunate to have a unique perspective into the professional life of an exceptional leader who has achieved remarkable success and global recognition in the field. Having a role model like him has an invaluable impact on my professional life.

I would like to acknowledge Professor Vivienne Sze and Professor Song Han for serving on my thesis committee and providing invaluable advice. I would like to thank Professor Vivienne Sze for providing me with invaluable feedback on paper writing and presentation, and Professor Song Han for the guidance in the VideoTime<sup>3</sup> project (Chapter 4).

I would also like to extend my appreciation to Professor Luca Daniel for serving on my RQE committee and Professor David J. Perreault for being my academic advisor and providing me with great advice every semester.

I would like to express my heartfelt gratitude to Professor Joel Emer. He led me into computer architecture and deep learning accelerator design with two of his courses (with Professor Daniel Sanchez and Professor Vivienne Sze). And his way of understanding and analyzing hardware architectures has greatly influenced my way of thinking.

I am very grateful to my mentor Joyce Wu. She is always there answering my questions and providing guidance about professional and personal life. Many thanks to her unlimited plant support that lights up my living environment.

My internship at the ASIC/VLSI research group of NVIDIA also contributed a lot to my professional development. I would like to thank my manager Dr. Brucek Khailany, my mentor Dr. Rangharajan Venkatesan, my co-mentor Prof. Yakun Sophia Shao, and many other colleagues at NVIDIA for their helpful advice during my internship.

I am very grateful to all past and present members of Anantha Group for creating such a supportive working environment. I would like to thank Utsav Banerjee for providing great support for my first chip tape-out, Michael Price for answering my questions about speech recognition and chip measurement setups even though we did not overlap during MIT, Mehul Tikekar, Priyanka Raina and Phillip Nadeau for helpful advice about tape-out, Preetinder Garcha for being a good friend and cubicle neighbor, our visiting student Xiaopeng Zhong for answering my questions regarding chip measurement and other senior members for helpful discussions. Also, thanks to Alex Ji for being a wonderful peer and Ruicong (Ray) Chen, Rishabh Mittal, Skanda Koppula, Vipasha Mittal, Deniz Umut Yildirim, Zhiye (Zoey) Song, Adam Matthew Gierlach, Eunseok Lee, Kyungmi Lee, Maitreyi Ashok and Saurav Maji for many happy chats.

I would like to thank Margaret Flaherty, Yuvie Cjapi, Jessie-Leigh O Thomas, Katey Provost, and other former lab administrators for their help with appointment scheduling, reimbursement, purchase orders, and lab space maintenance. I would also like to thank MTL Compute Team for their quick response to emails for various IT issues (sometimes even during non-working hours).

My life at MIT would not be so colorful without my friends. I want to thank them for all the fun we had together, such as badminton games, meals, BBQs, movies, etc.

I would like to acknowledge Irwin Mark Jacobs and Joan Klein Jacobs Presidential Fellowship for funding the academic year 2016 – 2017, TSMC for funding the eMRAM evaluation, Foxconn for funding the weight tuning project, and Qualcomm for funding the VideoTime<sup>3</sup> project.

I would like to thank my boyfriend for his support. Thanks for trying his best to feeding me well when I was busy! Many thanks to all the wonderful moments we have together.

Finally, I would like to express my deepest gratitude to my family members. I am very grateful to my parents for being my biggest cheerleaders, and offering words of encouragement when I needed them the most. Their understanding gave me a lot of comfort in the difficult time during the pandemic. I would like to thank my grandmas for all they have done for me!

# Contents

| 1        | Intr | roduction                                                   | 23 |

|----------|------|-------------------------------------------------------------|----|

|          | 1.1  | Motivation                                                  | 23 |

|          | 1.2  | Background                                                  | 24 |

|          | 1.3  | Thesis Overview                                             | 27 |

| <b>2</b> | Hyl  | orid Dataflow and Memory Hierarchy Co-design                | 29 |

|          | 2.1  | Introduction and Motivation                                 | 29 |

|          | 2.2  | Hybrid Dataflow and Memory Hierarchy                        | 31 |

|          | 2.3  | System 1 and its Evaluation                                 | 36 |

|          | 2.4  | System 2 and its Evaluation                                 | 40 |

|          |      | 2.4.1 Technology                                            | 42 |

|          |      | 2.4.2 Overall Architecture                                  | 43 |

|          |      | 2.4.3 Evaluation Setup                                      | 46 |

|          |      | 2.4.4 Evaluation Results                                    | 50 |

|          | 2.5  | Summary and Conclusions                                     | 53 |

| 3        | Wei  | ight Tuning Algorithm and Datapath/SRAM Co-design for Flex- |    |

|          | ible | Fully-Integrated CNN Accelerator                            | 55 |

|          | 3.1  | Introduction and Motivation                                 | 56 |

|          | 3.2  | Weight Tuning Algorithm and Potential SRAM Co-design        | 58 |

|          |      | 3.2.1 Tensor Decomposition with Retraining                  | 58 |

|          |      | 3.2.2 Quantization and the Sign-Magnitude Representation    | 59 |

|          |      | 3.2.3 Weight Scaling and Bit Perturbation with Retraining   | 60 |

|   | 3.3 | Datap  | bath Co-design and Flexible CNN Accelerator Architecture   | 63  |

|---|-----|--------|------------------------------------------------------------|-----|

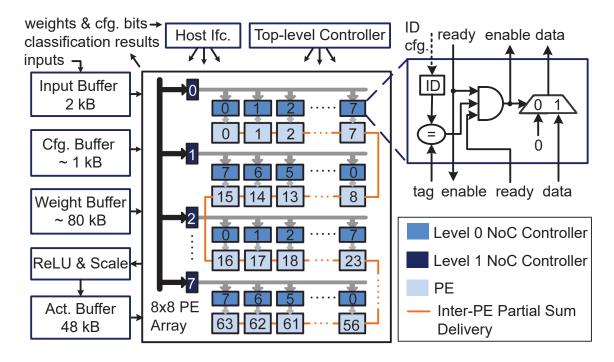

|   |     | 3.3.1  | Overall Architecture                                       | 63  |

|   |     | 3.3.2  | Flexbile Dataflow and NoC                                  | 64  |

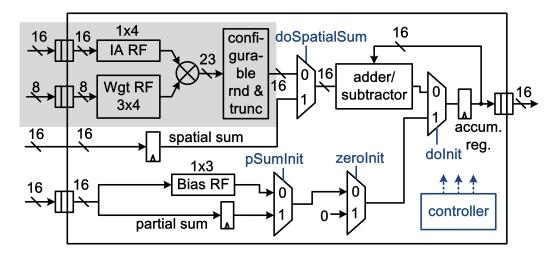

|   |     | 3.3.3  | Mixed-Representation Datapath                              | 66  |

|   | 3.4 | Evalu  | ation and Test Setup                                       | 67  |

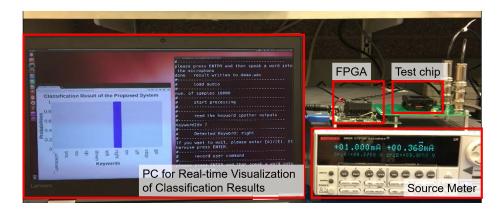

|   |     | 3.4.1  | Algorithm Evaluation Setup                                 | 67  |

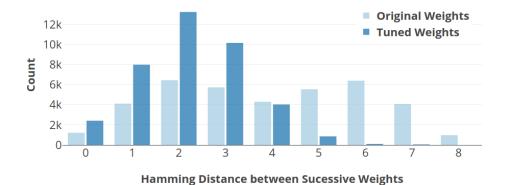

|   |     | 3.4.2  | Chip Measurement Setup                                     | 68  |

|   | 3.5 | Evalu  | ation and Measurements                                     | 69  |

|   |     | 3.5.1  | Weight Tuning Algorithm Evaluation Results                 | 69  |

|   |     | 3.5.2  | FPGA Demonstration Results                                 | 70  |

|   |     | 3.5.3  | Chip Implementation Results                                | 70  |

|   | 3.6 | Summ   | ary and Conclusions                                        | 73  |

| 4 | Ala | orithr | and Architecture Co-design Utilizing Data Features for     | •   |

| т | U   |        | derstanding                                                | 75  |

|   | 4.1 |        | iew of Deep-learning-based Video Understanding and Related | ••• |

|   |     |        | · · · · · · · · · · · · · · · · · · ·                      | 76  |

|   | 4.2 |        | thm and Accelerator Architecture                           | 80  |

|   |     | 4.2.1  | Real-Time DiffFrame Convolution                            | 80  |

|   |     | 4.2.2  | Sparsity Handling                                          | 85  |

|   |     | 4.2.3  | Temporal Modeling                                          | 90  |

|   |     | 4.2.4  | Activation Buffering                                       | 91  |

|   |     | 4.2.5  | Data Layout in DRAM                                        | 94  |

|   |     | 4.2.6  | Other Components and Overall Architecture                  | 95  |

|   | 4.3 | Evalu  | ation and Test Setup                                       | 99  |

|   |     | 4.3.1  | Model Preparation and Algorithm Evaluation Setup           | 99  |

|   |     | 4.3.2  | Architecture Evaluation and Chip Measurement Setup         | 100 |

|   | 4.4 | Evalu  | ation and Measurements                                     | 102 |

|   |     | 4.4.1  | Accuracy                                                   | 103 |

|   |     | 4.4.1  | Accuracy                                                   |     |

|   |     | 4.4.2  | DRAM Access                                                | 104 |

|   |                       | 4.4.3 Energy Breakdown                                 | 106 |

|---|-----------------------|--------------------------------------------------------|-----|

|   |                       | 4.4.4 Chip Measurements and Comparison with Prior Work | 107 |

|   | 4.5                   | Further Discussions on CNN Sparsity Handling           | 107 |

|   | 4.6                   | Summary and Conclusions                                | 112 |

|   |                       |                                                        |     |

| 5 | Con                   | clusions and Future Directions                         | 113 |

|   | 5.1                   | Summary of Contributions                               | 113 |

|   | 5.2                   | Future Directions                                      | 115 |

| Α | $\operatorname{List}$ | of Abbreviations                                       | 117 |

| в | Cus                   | tom NN Model structures                                | 119 |

| С | Dat                   | aflows                                                 | 123 |

## List of Figures

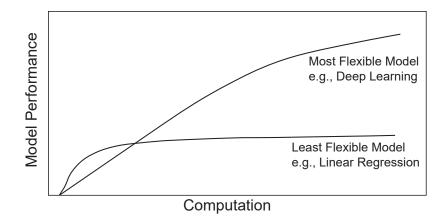

| 1-1 | Implications of model performance versus computation of deep learning    |    |

|-----|--------------------------------------------------------------------------|----|

|     | and linear regression [52].                                              | 24 |

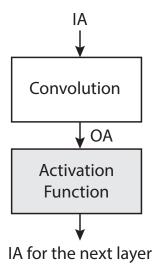

| 1-2 | Illustration of a convolution layer. Some convolution layers do not have |    |

|     | an activation function and thus OA equals IA for the next layer          | 25 |

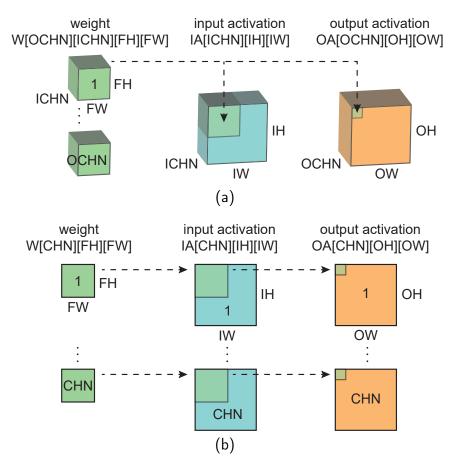

| 1-3 | Illustration of (a) ordinary convolution and (b) depth-wise convolution  |    |

|     | and the annotations used in this thesis                                  | 26 |

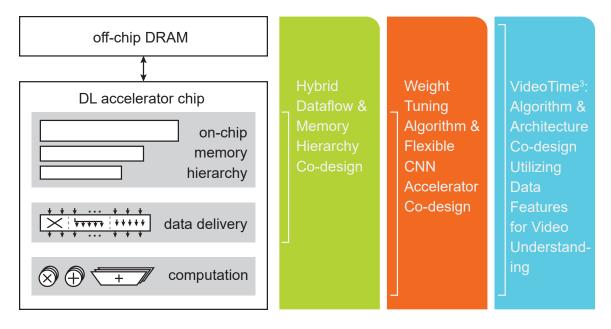

| 1-4 | An overview of a general deep learning system and a summary of the       |    |

|     | thesis.                                                                  | 27 |

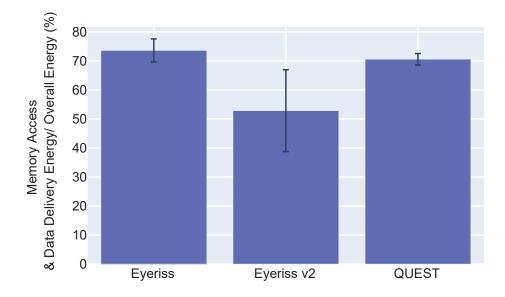

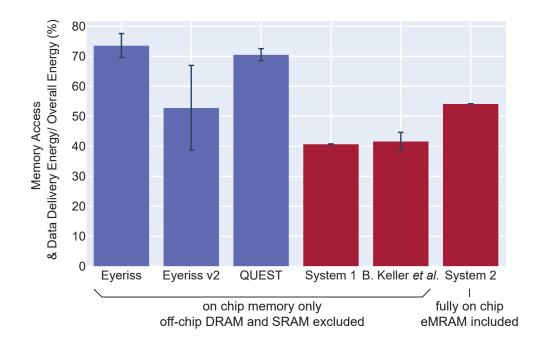

- 2-1 Memory access and data delivery energy is a significant part of the total NN accelerator energy. This figure only includes the reported on-chip energy consumption. Off-chip data access is more energy-consuming than on-chip memory access [23]. The energy ratio is obtained from the energy breakdown graphs/tables of prior NN accelerators running various workloads. We exclude the clock network energy from our analysis for Eyeriss [6] and Eyeriss v2 [7]. All the on-chip energy consumption is included except the "CLK and MISC." part in Fig. 18 of QUEST [53]. 30

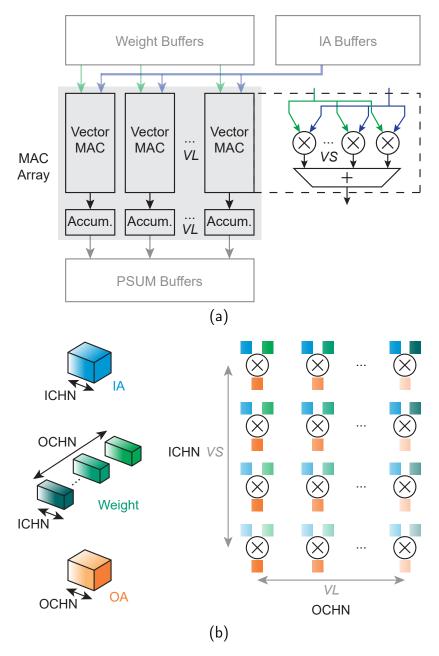

- 2-2 The baseline (a) spatial datapath architecture and (b) spatial mapping (to better illustrate the spatial mapping, we only show the multipliers from the MAC array in this figure). VS: the number of multipliers in a vector MAC; VL: the number of vector MACs and accumulators in the MAC array; accum.: accumulator. The colored squares indicate the mapping of IA, weight, and OA across the channel dimensions. . . 32

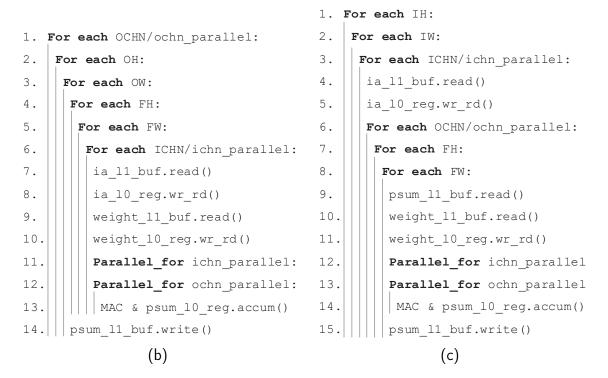

| 2-3  | Examples of (a) WS, (b) OS, and (c) IS data<br>flow with L1 buffers and L0 $$                                                                                     |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | registers. wr_rd: write and bypass read or read. accum: accumulation.                                                                                             | 34 |

| 2-4  | Illustration of WS-LOS (a) dataflow and (b) memory hierarchy. The                                                                                                 |    |

|      | differences between WS data<br>flow are highlighted in red. $\ldots$                                                                                              | 35 |

| 2-5  | Illustration of OS-LWS (a) dataflow and (b) memory hierarchy. The                                                                                                 |    |

|      | differences between the WS data<br>flow are highlighted in red. $\ldots$ .                                                                                        | 37 |

| 2-6  | (a) The overall architecture of system 1. PE: processing element. (b)                                                                                             |    |

|      | The PE architecture. The MAC array is shown in Fig. 2-2a. SC:                                                                                                     |    |

|      | standard cell.                                                                                                                                                    | 39 |

| 2-7  | Overview of MAGNet framework [54]. Its capability to co-design the                                                                                                |    |

|      | DL application is not used in our evaluation and thus is not included                                                                                             |    |

|      | in this figure.                                                                                                                                                   | 40 |

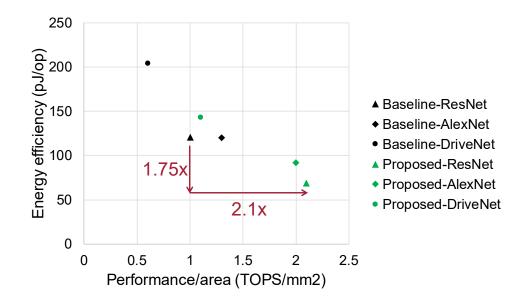

| 2-8  | Comparison of energy efficiency and performance per area of the opti-                                                                                             |    |

|      | mal accelerators with conventional dataflows and the proposed dataflows.                                                                                          |    |

|      | The proposed hybrid dataflows greatly improve energy efficiency and                                                                                               |    |

|      | performance per area.                                                                                                                                             | 41 |

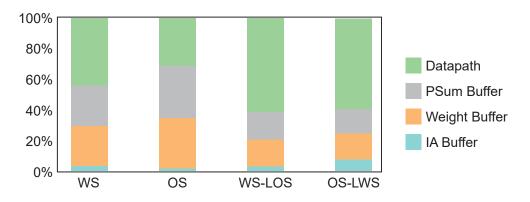

| 2-9  | The energy breakdown of a PE with $VL$ and $VS$ of 16                                                                                                             | 41 |

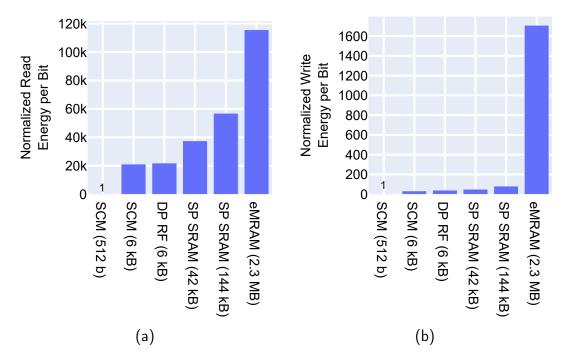

| 2-10 | Normalized (a) read energy per bit, and (b) write energy per bit of                                                                                               |    |

|      | 22-nm eMRAM and 28-nm standard cell memory (SCM) and SRAM                                                                                                         |    |

|      | relative to 512-b SCM. DP RF: the dual-port register file from 28-                                                                                                |    |

|      | nm memory compilers (this thesis refers to it as SRAM). SP SRAM:                                                                                                  |    |

|      | single-port SRAM.                                                                                                                                                 | 42 |

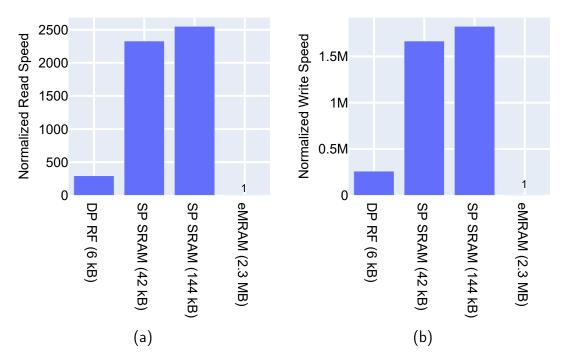

| 2-11 |                                                                                                                                                                   |    |

|      | Normalized (a) read speed, and (b) write speed of 22-nm eMRAM and                                                                                                 |    |

|      | Normalized (a) read speed, and (b) write speed of 22-nm eMRAM and 28-nm SRAM relative to eMRAM. DP RF: the dual-port register file                                |    |

|      |                                                                                                                                                                   |    |

|      | 28-nm SRAM relative to eMRAM. DP RF: the dual-port register file                                                                                                  | 43 |

| 2-12 | 28-nm SRAM relative to eMRAM. DP RF: the dual-port register file<br>from 28-nm memory compilers (this thesis refers to it as SRAM). SP                            | 43 |

| 2-12 | 28-nm SRAM relative to eMRAM. DP RF: the dual-port register file<br>from 28-nm memory compilers (this thesis refers to it as SRAM). SP<br>SRAM: single-port SRAM. | 43 |

| 2-12 | 28-nm SRAM relative to eMRAM. DP RF: the dual-port register file<br>from 28-nm memory compilers (this thesis refers to it as SRAM). SP<br>SRAM: single-port SRAM  | 43 |

| Overall system architecture. The system is fully on-chip with eMRAM.                             | 45                              |

|--------------------------------------------------------------------------------------------------|---------------------------------|

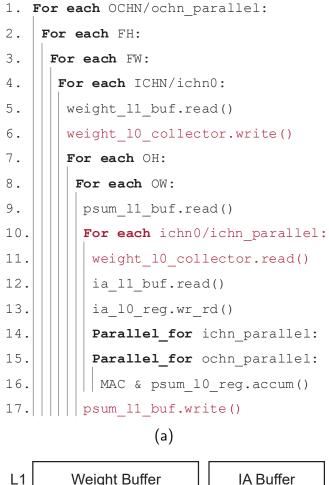

| OS-LWS-a dataflow (inner-level).                                                                 | 47                              |

| OS-LWS-b dataflow (inner-level).                                                                 | 48                              |

| The design space exploration framework for system 2                                              | 49                              |

| Comparison of the best energy efficiency and EDP achieved by conven-                             |                                 |

| tional dataflows and proposed dataflows under different optimization                             |                                 |

| targets—maximizing energy efficiency and minimizing EDP. The leg-                                |                                 |

| end of (a): <design space="">, <optimization target=""></optimization></design>                  | 49                              |

| Comparison of EDP between different dataflows. The optimization                                  |                                 |

| target is minimizing EDP.                                                                        | 50                              |

| The energy breakdown of different dataflows. The results are from an                             |                                 |

| optimization target of minimizing EDP                                                            | 51                              |

| Comparison of overall proportion of on-chip energy used for memory                               |                                 |

| access and data delivery of various NN accelerators, including Eye-                              |                                 |

| riss [6], Eyeriss v2 [7], QUEST [53], B. Keller <i>et al.</i> [30] and the two                   |                                 |

| systems presented in this chapter. System 2 is different from other                              |                                 |

| works as it includes all memory hierarchy on chip. The energy con-                               |                                 |

| sumption of off-chip memory hierarchies in other works is not included                           |                                 |

| in the analysis.                                                                                 | 53                              |

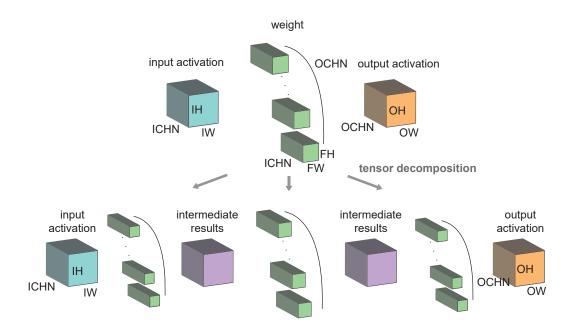

| Illustration of tensor decomposition for CNNs [32]. The original weight                          |                                 |

|                                                                                                  |                                 |

| -                                                                                                | 59                              |

|                                                                                                  |                                 |

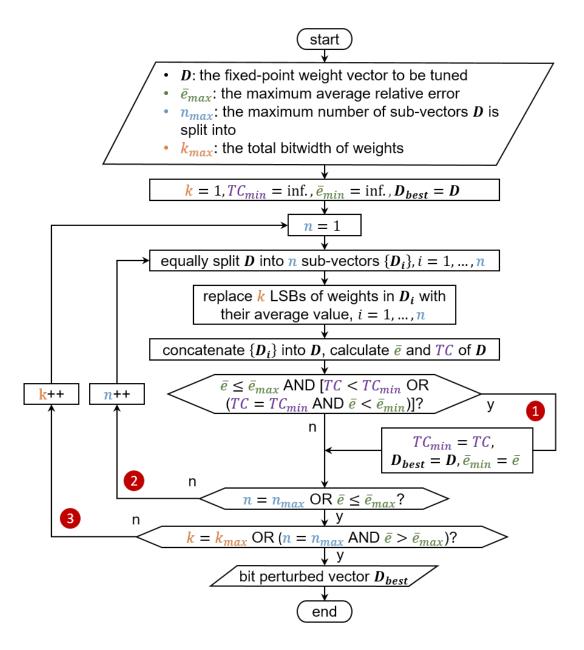

| keep the lowest possible $\bar{e}$ and the corresponding toggle count and the                    |                                 |

| weight vector. The second branch is to find out how many sub-vectors                             |                                 |

| <b>D</b> needs to be split into so that $\bar{e}$ can be lower than $\bar{e}_{max}$ given that k |                                 |

| LSBs are tuned. The third branch is to loop through all possible $k_{\cdot}$ .                   | 62                              |

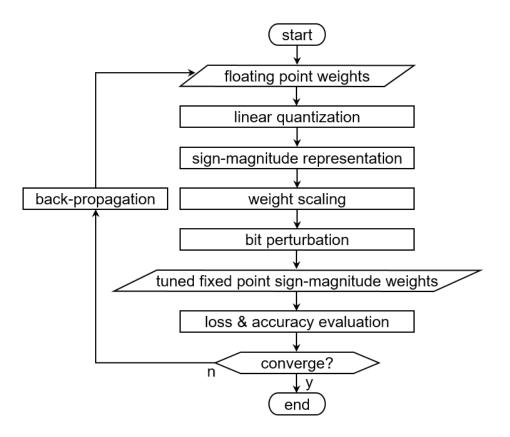

| The flowchart of quantization and sign-magnitude representation and                              |                                 |

| weight scaling and bit perturbation with retraining                                              | 63                              |

|                                                                                                  | OS-LWS-a dataflow (inner-level) |

| 3-4  | System architecture of the NN accelerator and the micro-architecture of the NoC controller.                                                                                                                                                                                                                                                                                                                                                                                                       | 64 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

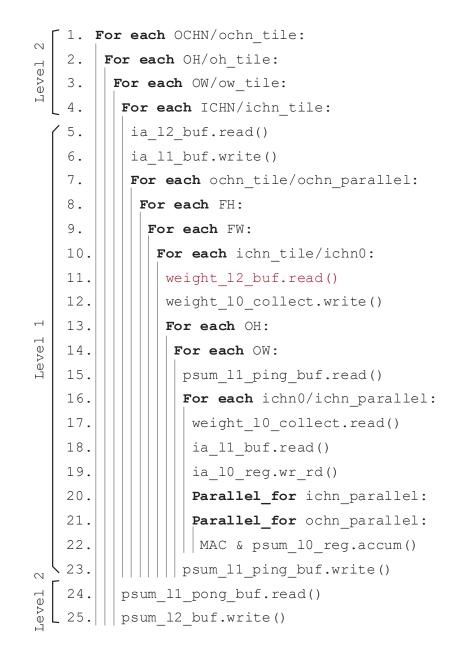

| 3-5  | The dataflow illustrated with loop nests. The tensor dimension parameters are defined in Fig. 3-1. Bias is ignored for simplicity. The batch size is 1 for real-time application. For the first layer, where ICHN $= 1$ , we replace ICHN with FW and remove the original FW loop to increase the PE array utilization. The read, delivery, and computation sequence of weight is as shown. PEs are filled up with weights in sequence. The limits on natively supported NN shapes are annotated. | 65 |

| 3-6  | The PE structure. The shaded part is the sign-magnitude domain.<br>The rest is in the 2's complement domain. Wgt: weight; rnd: round;<br>trunc: truncate; RF: RegFile; accum. reg.: accumulation register                                                                                                                                                                                                                                                                                         | 67 |

| 3-7  | The chip measurement setup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 68 |

| 3-8  | The weight tuning algorithm reshapes the histogram of Hamming distance between successive weights. CNN80 is shown as an example                                                                                                                                                                                                                                                                                                                                                                   | 69 |

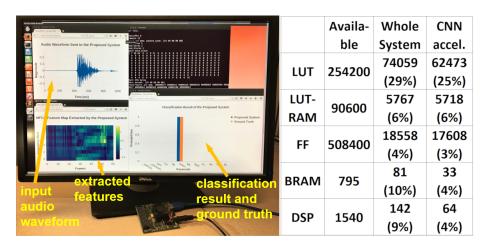

| 3-9  | The FPGA demo of the CNN accelerator with a feature extraction<br>processorv [15] on KWS, and a summary of FPGA post-PnR resource<br>utilization.                                                                                                                                                                                                                                                                                                                                                 | 70 |

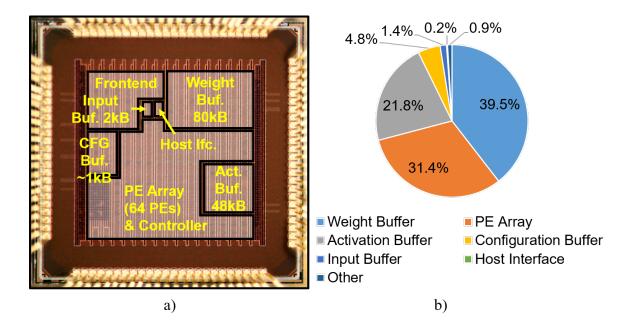

| 3-10 | a) Die micrograph. b) Area breakdown of the CNN accelerator                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71 |

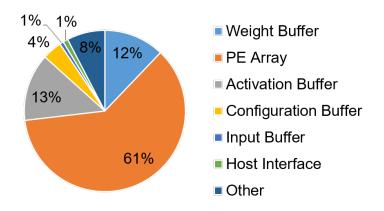

| 3-11 | Power breakdown of the CNN accelerator based on post-P&R simulation.                                                                                                                                                                                                                                                                                                                                                                                                                              | 72 |

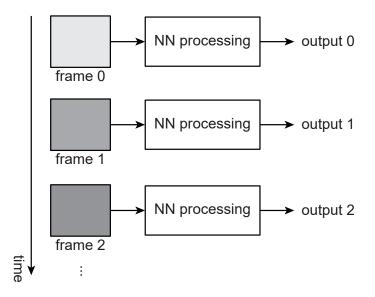

| 4-1  | The NN accelerator that only supports single-frame/image processing fails to capture temporal information across video frames                                                                                                                                                                                                                                                                                                                                                                     | 77 |

| 4-2  | Illustration of the conventional DiffFrame method, which is based on<br>the linearity of convolution, i.e., $\operatorname{conv}(f_t - f_{t-1}) + \operatorname{conv}(f_{t-1}) = \operatorname{conv}(f_t)$ .<br>$f_t - f_{t-1}$ and $\operatorname{conv}(f_{t-1})$ are DiffFrame and RefFrame at time t respec-                                                                                                                                                                                   |    |

|      | tively                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 78 |

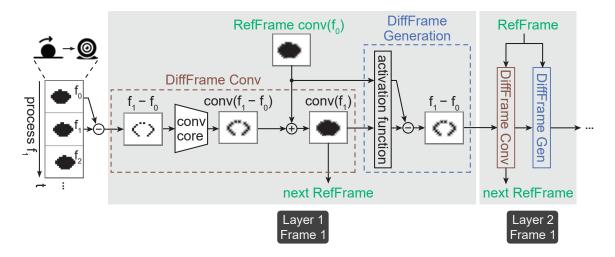

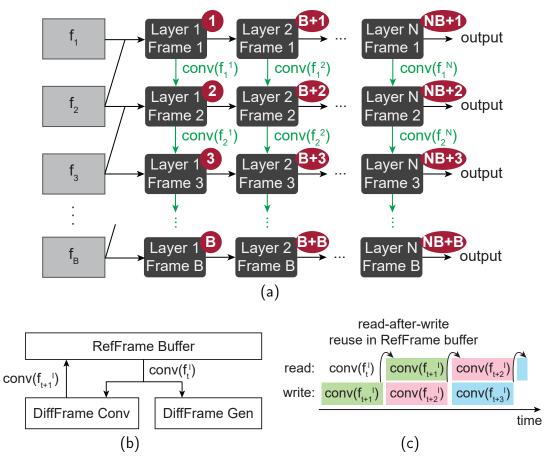

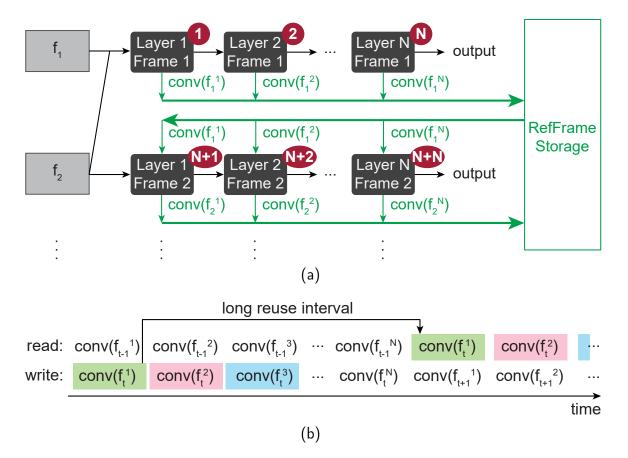

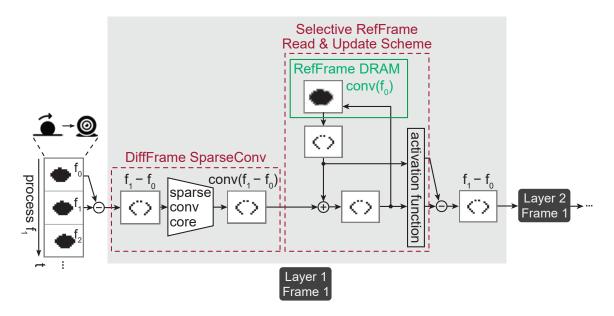

| 4-3  | (a) An illustration of serial batch processing. The processing sequence        |    |

|------|--------------------------------------------------------------------------------|----|

|      | is noted in red. N is the total number of layers and B is the batch            |    |

|      | size. (b) The high-level block diagram of the DiffFrame convolution            |    |

|      | accelerator and an illustration of RefFrame buffer access during the           |    |

|      | process of layer $l$ at frame $t$ . (c) The reuse of RefFrame over time in     |    |

|      | the on-chip buffer.                                                            | 79 |

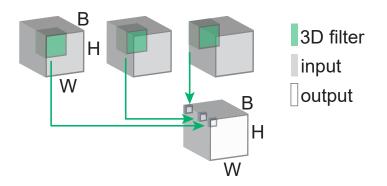

| 4-4  | Illustration of 3D CNN convolving the temporal dimension, which is             |    |

|      | composed of a batch of frames. For simplicity, the channel size is set         |    |

|      | to one in the illustration. W: width. H: height. B: batch                      | 79 |

| 4-5  | (a) An illustration of frame-by-frame processing. The processing se-           |    |

|      | quence is noted in red. N is the number of layers. (b) A long interval         |    |

|      | between the reuse of RefFrame in frame-by-frame processing                     | 81 |

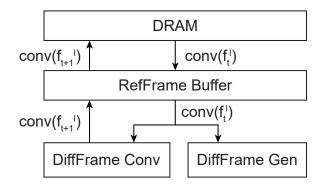

| 4-6  | The block diagram of naive DiffFrame generation and buffering                  | 81 |

| 4-7  | (a) An illustration of naive RefFrame read. (b) An illustration of pro-        |    |

|      | posed selective RefFrame read and update                                       | 82 |

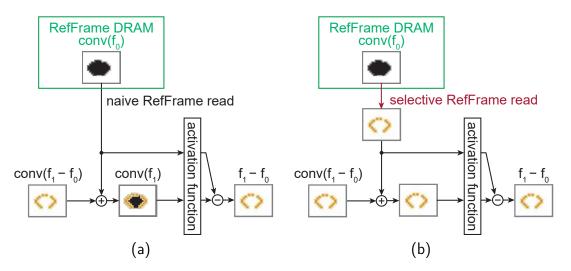

| 4-8  | (a) Fine-grained irregular sparsity in DiffFrame leads to DRAM burst           |    |

|      | length under-utilization for selective RefFrame load and store. (b)            |    |

|      | Channel-wise coarse-grained sparsity in DiffFrame leads to high uti-           |    |

|      | lization of DRAM burst length for selective RefFrame load and store.           | 83 |

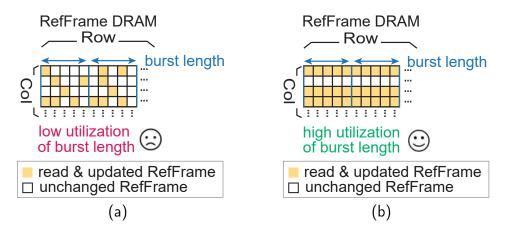

| 4-9  | The rules of input and output coordinates in sub-manifold sparse con-          |    |

|      | volution. (a) For stride $= 1$ layers, the input and output coordinates        |    |

|      | are exactly the same. (b) For stride $= 2$ layers, the valid outputs are       |    |

|      | those with $x\%2 = 0$ and $y\%2 = 0$ , where $(x, y)$ is the output coordinate |    |

|      | of conventional convolution.                                                   | 84 |

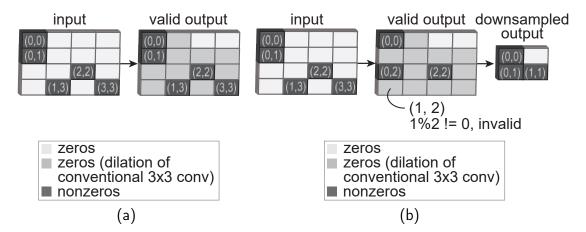

| 4-10 | The proposed real-time DiffFrame method illustrated with stride $= 1$          |    |

|      | layer                                                                          | 84 |

| 4-11 | An illustration of sparse (a) PW convolution and (b) DW convolution.           |    |

|      | Channels are set to 1 for simplicity and clarity of the figure. Colored        |    |

|      | and white boxes present nonzeros and zeros respectively                        | 87 |

|      |                                                                                |    |

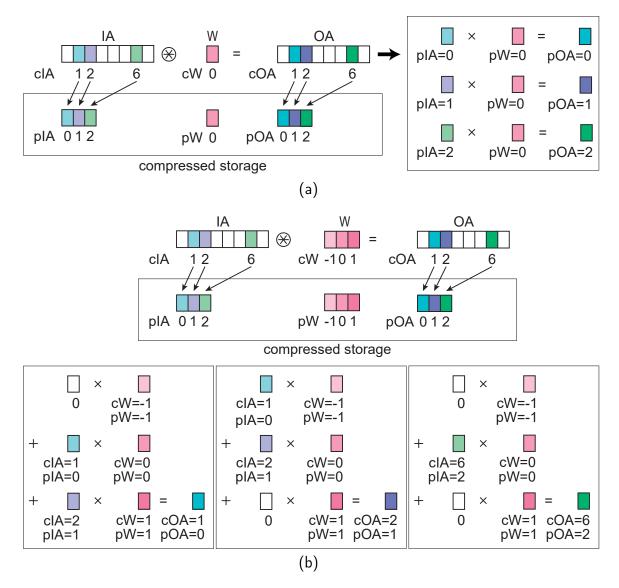

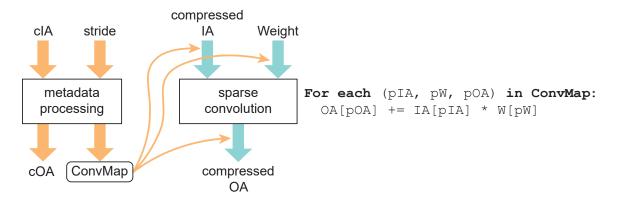

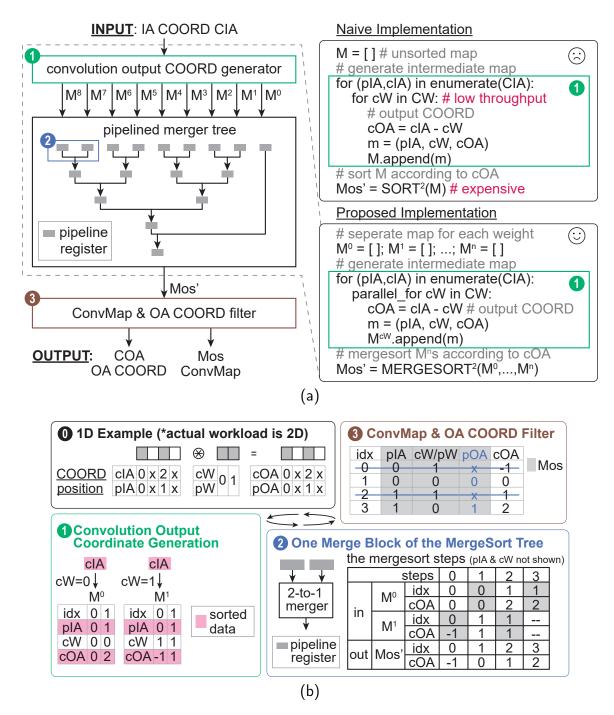

| 4-12 | An illustration of map-guided convolution and decoupled metadata                                                                                                                                                                                                                                                                                                                                                                                                                                       |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | generation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 88  |

| 4-13 | (a) An overview of the proposed sorter-free ConvMap and coordinate<br>generator. $cIA$ , $cOA$ and $cW$ : coordinates of nonzero IA, OA and<br>weight respectively; $pIA$ , $pOA$ and $pW$ : positions of nonzero IA, OA<br>and weight respectively; $M'_{OS}$ ; the intermediate unfiltered map con-<br>taining all possible outputs of conventional convolution; $M_{OS}$ : the final<br>ConvMap satisfying the rules in Fig. 4-9. (b) An example of simple 1D<br>ConvMap and coordinate generation. | 89  |

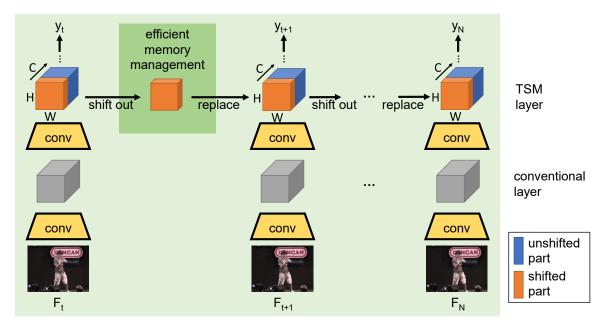

| 4-14 | An illustration of temporal shift module [35]. C: channel                                                                                                                                                                                                                                                                                                                                                                                                                                              | 91  |

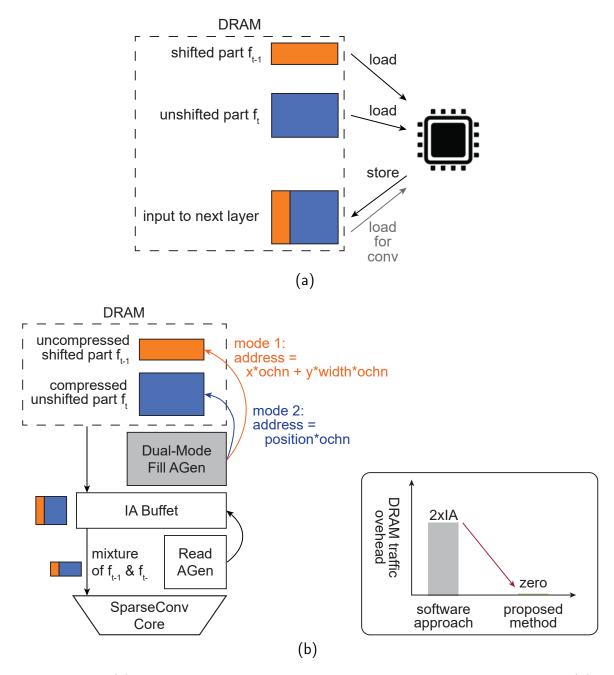

| 4-15 | <ul><li>(a) An illustration of software approach of TSM data handling. (b)</li><li>An illustration of the proposed dual-mode IA Buffet for TSM data</li><li>handling. AGen: address generator</li></ul>                                                                                                                                                                                                                                                                                                | 93  |

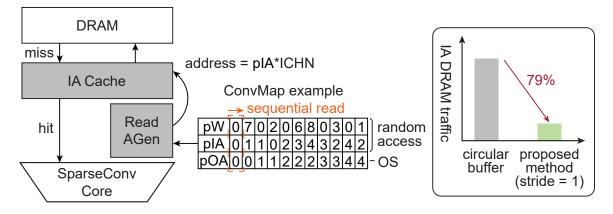

| 4-16 | A cache-based implicit decoupled data orchestration for ConvMap-<br>guided IA load of DW DiffFrame SparseConv.                                                                                                                                                                                                                                                                                                                                                                                         | 94  |

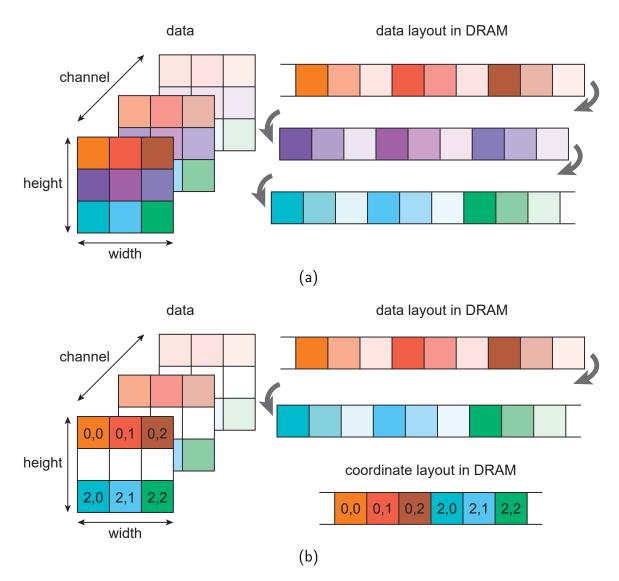

| 4-17 | An illustration of row-major memory order for data and coordinate<br>with a simple $3 \times 3 \times 3$ tensor. (a) Uncompressed storage. (b) Com-<br>pressed storage (zero data are shown in white).                                                                                                                                                                                                                                                                                                 | 95  |

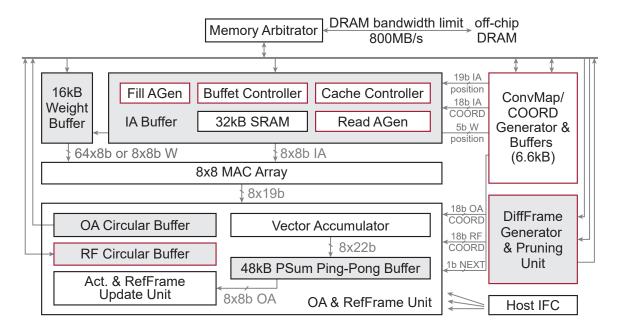

| 4-18 | Overall system architecture. AGen: address generator; gen.: gener-<br>ator; PSum: partial sum; RF: RefFrame; IFC: interface; COORD:                                                                                                                                                                                                                                                                                                                                                                    |     |

|      | coordinate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 96  |

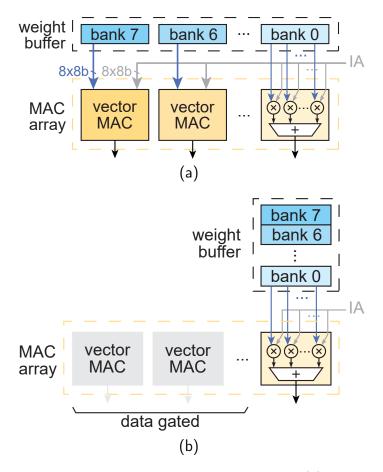

| 4-19 | The dual-mode MAC array and weight buffer. (a) Standard convolu-<br>tion. (b) DW convolution                                                                                                                                                                                                                                                                                                                                                                                                           | 97  |

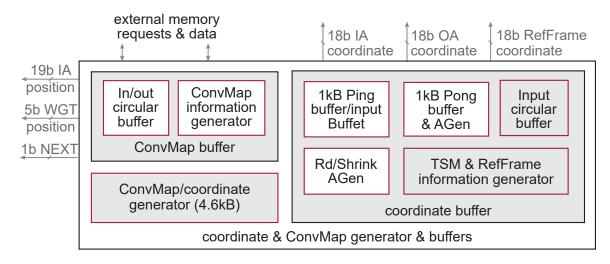

| 4-20 | The block diagram of the ConvMap and coordinate generator and buffers. WGT: weight                                                                                                                                                                                                                                                                                                                                                                                                                     | 98  |

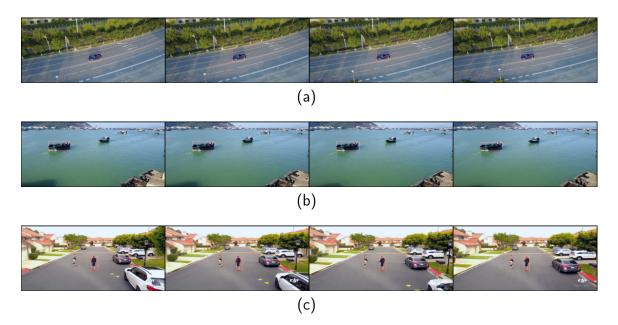

| 4-21 | A few samples of the DAC-SDC dataset [61]                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 100 |

| 4-22 | The setup for architecture exploration and evaluation. LUT: lookup                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

|      | table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 101 |

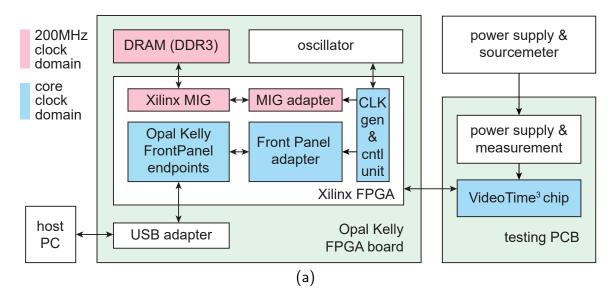

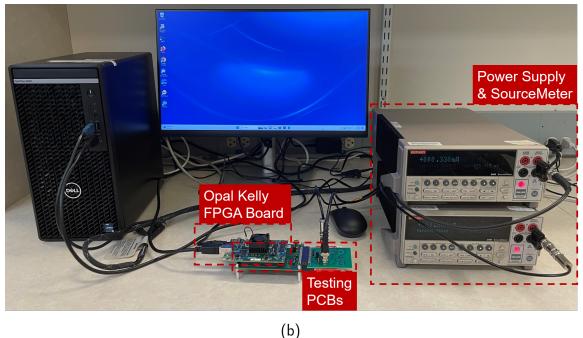

| 4-23 | (a) The block diagram of the chip measurement setup.     | FPGA has two   |     |

|------|----------------------------------------------------------|----------------|-----|

|      | clock domains. One is the highest clock frequency for    | DDR3 and the   |     |

|      | other is for the chip. gen: generator; cntl: controller. | (b) A photo of |     |

|      | the chip measurement setup                               |                | 102 |

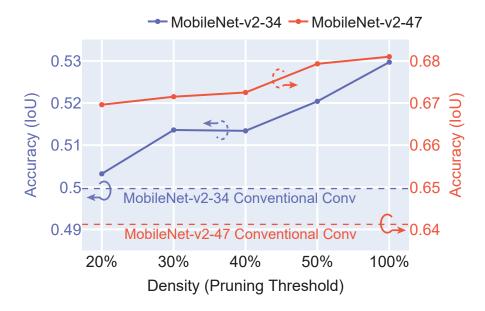

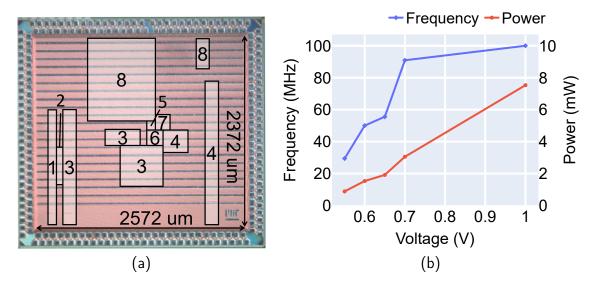

- 4-24 Comparison with conventional convolution and sensitivity of accuracy on the pruning threshold of the proposed real-time DiffFrame SparseC-onv with temporal modeling algorithm. The NN is not quantized. The case with a density of 100% is equivalent to convolution with TSM. The dash lines are plain conventional convolution. . . . . . . . . . . . . . . . 103

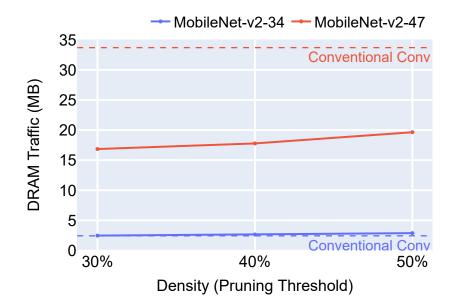

- 4-25 The total DRAM traffic vs. the pruning threshold (input density) of the proposed real-time DiffFrame SparseConv with temporal modeling algorithm and a comparison with conventional convolution. The target of the mapping optimizer is set to be minimizing DRAM traffic. . . . 105

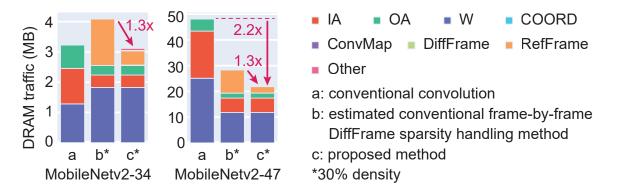

- 4-27 Energy breakdown of the accelerator chip (including IO drivers) running MobileNet-v2-34. DRAM access time and energy are not included.

COORD: coordinate; Gen.: generator; IFC: interface. . . . . . . . . . . . . . . 107

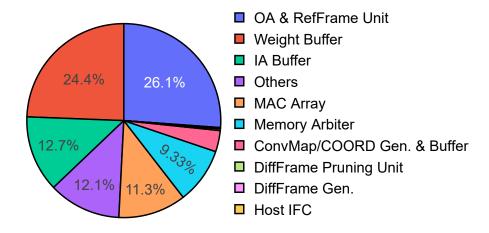

- 4-28 (a) Die micrograph (1: 16 kB Weight buffer; 2: 8 × 8 MAC array; 3: 32 kB IA buffer; 4: 44 kB OA RefFrame unit; 5: DiffFrame generator;

6: DiffFrame pruning; 7: ConvMap buffer; 8: ConvMap generator and coordinate buffer). (b) Frequency and power measurements. . . . . 108

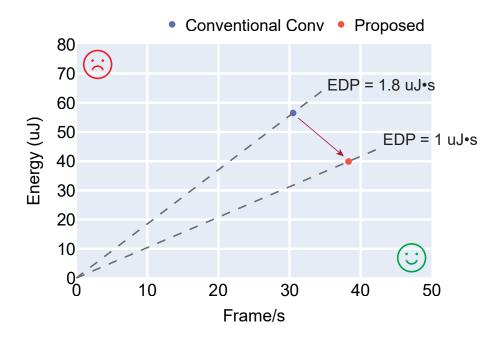

| 4-29 | Comparison of the proposed real-time Diffframe convolution and con-   |     |

|------|-----------------------------------------------------------------------|-----|

|      | ventional convolution in terms of energy, frame rate and energy-delay |     |

|      | product (EDP) on our accelerator chip                                 | 108 |

|      |                                                                       |     |

| C-1  | WS-a data<br>flow (inner-level). No weight L1 buffer is needed        | 124 |

| C-2  | WS-b dataflow (inner-level)                                           | 125 |

| C-3  | OS-a dataflow (inner-level).                                          | 126 |

| C-4  | OS-b dataflow (inner-level).                                          | 127 |

| C-5  | WS-LOS-a dataflow (inner-level). No weight L1 buffer is needed        | 128 |

| C-6  | WS-LOS-b dataflow (inner-level).                                      | 129 |

# List of Tables

| 2.1 | Summary of reuse per read/write of L1 buffers and reuse per write of  |     |

|-----|-----------------------------------------------------------------------|-----|

|     | L0 registers in the WS, OS, and IS dataflows.                         | 33  |

| 2.2 | Summary of reuse per read/write of L1 buffers/L0 collectors and reuse |     |

|     | per write of L0 registers in WS-LOS and OS-LWS data<br>flows          | 38  |

| 2.3 | The design space of system 1 [54]. A conventional design space con-   |     |

|     | tains WS and OS dataflow. The proposed hybrid dataflow expands the    |     |

|     | design space with WS-LOS and OS-LWS data<br>flows                     | 40  |

| 2.4 | The design space of the system                                        | 45  |

| 3.1 | The Effect of the Weight Tuning Algorithm on Accuracy and Energy      |     |

| 0.1 | Consumption Based on Post-P&R Simulation                              | 70  |

| 3.2 | Chip Specifications                                                   | 72  |

|     |                                                                       |     |

| 4.1 | The Summary of Existing Challenges in Prior Work                      | 77  |

| 4.2 | Comparison of Conventional DiffFrame Convolution and Our Proposed     |     |

|     | Real-time DiffFrame Convolution                                       | 80  |

| 4.3 | A Summary of Data Types and Their Layout in DRAM                      | 94  |

| 4.4 | Accuracy Analysis of the Proposed Method on Quantized MobileNet-      |     |

|     | v2 Neural Nets                                                        | 104 |

| 4.5 | Comparison to Prior Work                                              | 109 |

| 4.6 | Computation-Related Sparsity Handling Techniques                      | 110 |

| 4.7 | Memory-Related Sparsity Handling Techniques                           | 110 |

| 4.8 | Comparison to Prior Work in Terms of Sparsity Handling in Activations |     |

|     | and Partial Sums                                                      | 111 |

- B.2 The Structure of MobileNet-v2-47 (The input size is H = 160 and W = 360. The proposed real-time DiffFrame convolution with temporal modeling algorithm is applied to layer 4 and the following layers. Metadata need to be generated for layer 4, 16, 17, 37 and 38. The last layer, which is a fully connected layer, is not included in our evaluation.)120

- B.3 The Structure of MobileNet-v2-34 (The input size is H = 54 and W = 122. The proposed real-time DiffFrame convolution with temporal modeling algorithm is applied to layer 3 and the following layers. Metadata need to be generated for layer 3, 12, 13, 27, and 28. The last layer, which is a fully connected layer, is not included in our evaluation.)121

# Chapter 1

# Introduction

### 1.1 Motivation

Deep learning (DL) is widely used in many applications for its state-of-the-art performance revolutionizing how we process and analyze complex data. Among its many uses, DL has demonstrated impressive results in image and video understanding, speech recognition, and natural language processing. In image and video understanding, DL models have been deployed on drones and autonomous vehicles to detect and track objects, such as pedestrians, roads, obstacles, etc. [13, 11]. In natural language processing, the state-of-the-art DL model, such as the generative pre-trained Transformer (GPT) series [12], enables a natural and interactive way of obtaining knowledge and assistance. With the growth in data and the increasing demand for more intelligent systems, the importance of DL is set to increase in the years to come.

However, DL is computationally expensive. Researchers have shown in theory and practice that the progress of DL in a wide variety of applications is strongly reliant on increases in computing power [52]. As shown in Fig. 1-1, traditional machine learning methods, e.g., linear regression, which use a small number of parameters, have their performance plateau at a low level as available computation (and amount of data) increases. In contrast, deep learning methods, which use an enormous number of parameters, achieve higher performance at the cost of more computation (and data). If we project this dependence into the future, it becomes evident that continuing on

Figure 1-1: Implications of model performance versus computation of deep learning and linear regression [52].

the same path is unsustainable given the current energy cost of computation. This projection is supported by a probabilistic analysis of the emissions from computing onboard a global fleet of autonomous vehicles in the future. The model predicts that the computing power of 1 billion autonomous vehicles with 1-hour drive per day leads to the emission of all data centers on earth [50]. Even in the near term, the computing cost of DL is prohibitive. Quoted OpenAI, the popular DL tool ChatGPT [39] caused "eye-watering" computing cost when it hit 1 million users<sup>1</sup>. The increasing demand for computing power poses significant challenges to the growth of DL applications.

As a result, improving the energy efficiency of DL workloads while preserving their accuracy and meeting application throughput requirements becomes very important. The objectives of this thesis are to propose algorithm, architecture, and circuit codesign techniques to tackle this challenge, and experimentally evaluate them through simulation and/or chip tapeout and measurements.

### 1.2 Background

This section presents a general background and the terminology used in this thesis.

**Convolution**: Fig. 1-2 illustrates a general convolution layer, which convolutes input activation (IA) with weight, generates output activation (OA) and optionally

<sup>&</sup>lt;sup>1</sup>https://analyticsindiamag.com/chatgpt-hits-one-million-users-burns-in-millions/

Figure 1-2: Illustration of a convolution layer. Some convolution layers do not have an activation function and thus OA equals IA for the next layer.

applies an activation function to OA to generate IA for the next layer. OA refers to the direct output of convolution instead of the output of the activation function in this thesis. Partial sum (PSum) refers to the partially computed OA. Feature map (FMap) refers to the activations in a NN, including both IAs and OAs. Illustration of ordinary convolution and depth-wise convolution [24] is shown in Fig. 1-3 along with the annotation of tensors and dimensions used in this thesis. The fully connected layer can be treated as a special case of ordinary convolution with FH, FW, IH, IW, OH and OW equal to 1.

**Dataflow, mapping and loop nest**: Sze *et al.* introduce *dataflow* to represent the ordering of calculations in convolution and which calculations run in parallel [51]. We split the dataflow into two parts, including *spatial mapping* which represents the parallel calculations, and temporal mapping which represents the sequential ordering of calculations. To precisely describe a dataflow, Sze *et al.* introduce *loop nests* [51]. In this thesis, we use the following syntax to represent a loop in temporal mapping,

#### For each dimension:

and the following syntax to represent a loop in spatial mapping.

```

Parallel_for dimension:

```

Figure 1-3: Illustration of (a) ordinary convolution and (b) depth-wise convolution and the annotations used in this thesis.

Although loop nests define how accelerators handle the computation, it does not show how data are buffered. To describe data buffering schemes of NN accelerators, we add read and write annotations of storage elements in the loop nests, such as the following.

Weight\_L1\_buffer.read()

Weight\_L0\_buffer.write()

**Coordinate and position**: *Coordinate* refers to the coordinate of each datum in the tensor. They are used to index the tensor and represent how convolution should be done mathematically. *Position* refers to the position of each datum in the memory relative to the base of this data block. They represent how to access the memory in hardware accelerators. If a data block is sequentially stored in the memory

Figure 1-4: An overview of a general deep learning system and a summary of the thesis.

without compression, the position can be calculated from the coordinate based on the storing sequence and the dimensions of the data block. For 1-D arrays, the position is equal to the coordinate. If a data block is as a compressed form in the memory, the relationship between the position and the coordinate is not straightforward. It can be influenced by many factors, such as the sparsity pattern and the compression algorithm.

#### 1.3 Thesis Overview

In this thesis, we focus on reducing energy consumption and improving energy efficiency across various system components while ensuring that we meet the required levels of accuracy and performance. The major components in a general DL accelerator are on-chip memory hierarchy, data delivery fabrics, and computing units. The DL accelerator may need off-chip storage if the processing data are too large to fit on chip. We take an algorithm, hardware architecture and circuit co-design approach to optimize different system components as summarized in Fig. 1-4.

Hybrid Dataflow and Memory Hierarchy Co-design: In Chapter 2, we

focus on memory hierarchy design and dataflows to reduce the associated energy consumption. We propose hybrid dataflows that provide an option to tradeoff the reuse opportunities of weight and PSum in different memory hierarchies. We evaluate how the proposed hybrid dataflows affect the energy efficiency and other characteristics of two system designs with different technologies. In both systems, our proposed hybrid dataflows improve energy efficiency by around 1.5x - 2x and show significant improvements in performance per area and energy-delay product (EDP).

Weight Tuning Algorithm and Flexible CNN Accelerator Co-design: In Chapter 3, we propose a weight tuning algorithm to reduce the energy consumption of on-chip components—the memory access, data delivery, and computation associated with weights. It focuses on reducing the weight-related switching activity through optimization of the bit representation of weights. In addition, we co-design a standalone deep learning accelerator with a specialized datapath and potentially applicable custom SRAM for the algorithm.

Algorithm and Architecture Co-design Utilizing Data Features for Video Understanding: In Chapter 4, we take the entire system into consideration and co-design the algorithm and architecture for video understanding applications utilizing their data features. Our design features the capability of temporal modeling for higher accuracy, the utilization of temporal redundancy to improve energy efficiency, and achieving single-frame latency for real-time applications, such as autonomous vehicles and AI drones. Our work also provides an extension to the existing sparsity handling taxonomy with the proposed map-guided sparse convolution and decoupled metadata generation.

## Chapter 2

# Hybrid Dataflow and Memory Hierarchy Co-design

As discussed in the previous chapter, it is important to keep improving the energy efficiency of NN accelerators. In this chapter, we focus on reducing the energy consumption of memory access and data delivery through the design of efficient dataflow and memory hierarchy.

The chapter is organized as follows. First, we analyze the energy consumption of memory access and data delivery in existing NN accelerators, point out the importance of energy reduction for memory access and data delivery, and summarize the related prior works. Then, we introduce our proposed hybrid dataflows and their corresponding memory hierarchy. Later, we present the evaluation results of our proposed techniques on several systems with different technologies followed by a summary of this chapter.

### 2.1 Introduction and Motivation

Optimizing memory access and data delivery is an important part of neural network (NN) accelerator design. Fig. 2-1 describes the contribution of memory access and data delivery to the overall power consumption of various NN accelerators. In terms of target workload, Eyeriss [6] and QUEST [53] are optimized for dense NNs, while

Figure 2-1: Memory access and data delivery energy is a significant part of the total NN accelerator energy. This figure only includes the reported on-chip energy consumption. Off-chip data access is more energy-consuming than on-chip memory access [23]. The energy ratio is obtained from the energy breakdown graphs/tables of prior NN accelerators running various workloads. We exclude the clock network energy from our analysis for Eyeriss [6] and Eyeriss v2 [7]. All the on-chip energy consumption is included except the "CLK and MISC." part in Fig. 18 of QUEST [53].

Eyeriss v2 [7] is designed for sparse NNs. In terms of the memory system, Eyeriss [6] and Eyeriss v2 [7] use regular DRAM and SRAM based systems, while QUEST [53] proposes a unique 3D-stacking SRAM with inductive coupling technology. As shown, the energy of memory access and data delivery takes up a significant portion of the total energy consumption of different NN accelerators.

Extensive prior works have proposed many techniques to reduce the energy consumption of memory access and data delivery in NN accelerators, and some works investigated the factors influencing memory access and data delivery. Yu-Hsin *et al.* was pioneered in proposing a dataflow taxonomy and the convolution loop nest representation to systematically analyze the memory access and data delivery in NN accelerators [5, 51]. X. Yang *et al.* distinguished the impact of spatial mapping from that of temporal mapping in the dataflow. They showed that spatial mapping does not lead to much impact on the overall energy consumption as long as the temporal mapping and memory hierarchy are fully optimized [62]. That emphasizes the importance of the choice of memory allocation for each data type along with the loop permutation and temporal unrolling in the convolution loop nest. Prior work proposed weight stationary (WS), input stationary (IS), and output stationary (OS) dataflow corresponding to specific loop permutations that have weight/input/output-related dimensions in the outermost loops respectively. They result in a maximum reuse opportunity of weight/IA/OA respectively at the cost of losing reuse opportunities of other data types.

Based on prior work, we propose hybrid dataflows that offer balanced reuse opportunities for different data types at different levels of memory hierarchies. To demonstrate the impact of our proposed techniques, we evaluate them on several systems with different technologies, including a system with off-chip DRAM using 16nm FinFET technology and a fully-on-chip NN accelerator with embedded magnetoresistive RAM (eMRAM) in 22-nm/28-nm CMOS technology. It is shown that our proposed output stationary with local weight stationary (OS-LWS) dataflow delivers around 1.5x - 2x improvements in the energy efficiency of all systems evaluated and significant improvements in performance per area and EDP. Part of the work was done during the author's internship at the ASIC/VLSI research group at NVIDIA.

### 2.2 Hybrid Dataflow and Memory Hierarchy

This section presents our proposed hybrid dataflows, WS with local OS (WS-LOS) and OS with local WS (OS-LWS), which 1) provide designers the capability to balance the reuse of weight and PSum/OA based on the characteristics of the storage elements in the chosen technology, 2) enrich the design space for the architecture exploration framework to achieve potentially better energy efficiency and performance/area.

The baseline spatial datapath architecture and spatial mapping of the proposed dataflows are shown in Fig. 2-2. The spatial datapath architecture is composed of sev-

Figure 2-2: The baseline (a) spatial datapath architecture and (b) spatial mapping (to better illustrate the spatial mapping, we only show the multipliers from the MAC array in this figure). VS: the number of multipliers in a vector MAC; VL: the number of vector MACs and accumulators in the MAC array; accum.: accumulator. The colored squares indicate the mapping of IA, weight, and OA across the channel dimensions.

eral vector MACs and accumulators. The vector MAC consists of several multipliers to generate the products of weights and IAs, and an adder tree to spatially accumulate the products (PSums). The accumulator is used for the temporal accumulation

| Data Type | Storage Unit | WS    | OS         | IS         |

|-----------|--------------|-------|------------|------------|

| Weight    | L1 buffer    | OH×OW | 0          | 0          |

| weight    | L0 register  | OH×OW | 0          | 0          |

| PSum/OA   | L1 buffer    | 0     | FH×FW×ICHN | 0          |

| FSUIIOA   | L0 register  | 0     | 0          | 0          |

| IA        | L1 buffer    | 0     | 0          | FH×FW×OCHN |

| IA        | L0 register  | 0     | 0          | FH×FW×OCHN |

Table 2.1: Summary of reuse per read/write of L1 buffers and reuse per write of L0 registers in the WS, OS, and IS dataflows.

of PSums locally before storing them in PSum/OA buffers. We spatially map the input and output channels to the MAC array for parallel computing. With high-level architecture modeling, prior work demonstrated that spatial mapping only has a limited impact on overall energy consumption, and channel-wise spatial mapping is good for the utilization of computing units as NNs usually have a large channel size [62]. That justifies our choice of spatial mapping. Moreover, the spatial accumulation of part of the PSums enabled by our vector MACs is shown to be more energy efficient than temporal accumulation as there is no need to access the accumulation register.

With this spatial architecture and spatial mapping, conventional dataflows—WS, IS, and OS—can be implemented as shown in Fig. 2-3 with a memory hierarchy that has one level of buffer for each data type, weight and IA registers at the inputs of MAC array, and PSum accumulation registers in the accumulators. The reuse opportunity for each data access to each buffer is summarized in Table 2.1. For WS, all the weight-related dimensions are in the outer loops and thus each weight buffer read and weight register write gets reused over the OH and OW loops while other data keep being accessed in every loop. Similar analysis can be applied to other conventional dataflows. For OS dataflow, the PSum accumulation register needs to be accessed each cycle for temporal accumulation, although all the PSum-related dimensions are in the outermost loops.

To balance the reuse opportunities across multiple data types, we propose hybrid

```

1. For each OCHN/ochn parallel:

2.

For each FH:

3.

For each FW:

4.

For each ICHN/ichn parallel:

5.

weight l1 buf.read()

6.

weight 10 req.wr rd()

For each OH:

7.

For each OW:

8.

ia l1 buf.read()

9.

10.

ia l0 reg.wr rd()

11.

psum l1 buf.read()

12.

Parallel for ichn parallel:

Parallel for ochn parallel:

13.

14.

MAC & psum 10 reg.accum()

psum l1 buf.write()

15.

```

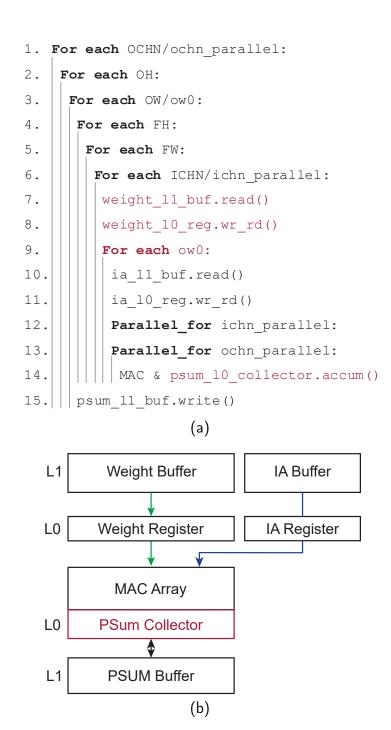

Figure 2-3: Examples of (a) WS, (b) OS, and (c) IS dataflow with L1 buffers and L0 registers. wr\_rd: write and bypass read or read. accum: accumulation.

dataflows—WS-LOS and OS-LWS—and introduce new storage elements.

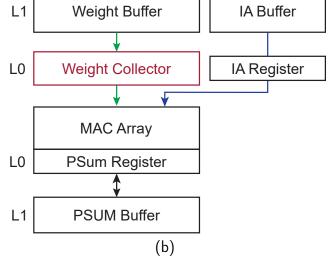

Figure 2-4: Illustration of WS-LOS (a) dataflow and (b) memory hierarchy. The differences between WS dataflow are highlighted in red.

#### Weight Stationary with Local Output Stationary

The weight stationary with local output stationary (WS-LOS) dataflow and its memory hierarchy implementation are shown in Fig. 2-4. Based on WS dataflow, we move part of the input channels to the innermost temporal loop and those input channels are temporally accumulated in the PSum registers without accessing the PSum buffer. Instead of having single-entry L0 weight registers at the input of the MAC array, we expand it to a  $ichn0/ichn\_parallel$ -entry weight collector to temporally hold  $ichn0 \times ochn\_parallel$  weights during the OH, OW and ichn0 loops. In this way, reuse per weight buffer read stays the same as the WS dataflow while reuse per PSum buffer read goes up to ichn0 at the cost of no reuse opportunity for the weight collector. A summary of the reuse opportunity can be found in Table 2.2.

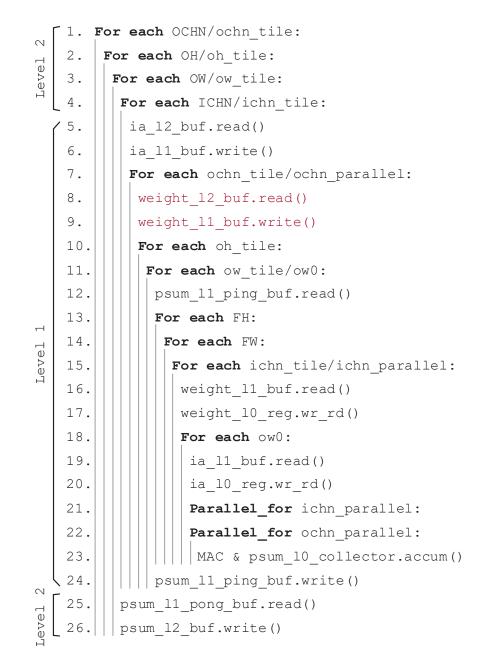

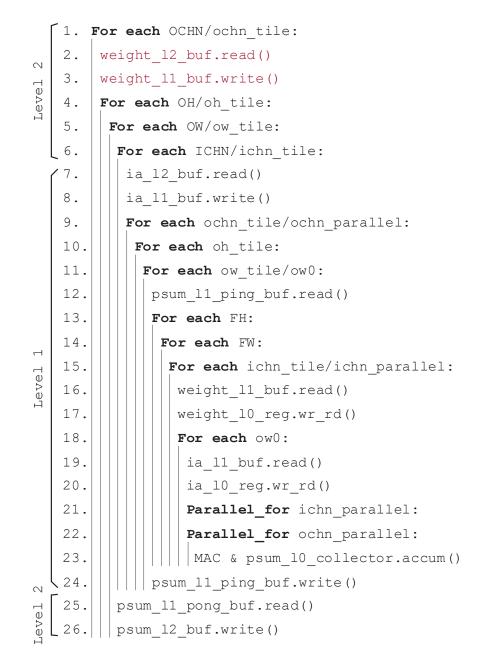

#### Output Stationary with Local Weight Stationary

The output stationary with local weight stationary (OS-LWS) dataflow and its memory hierarchy implementation are shown in Fig. 2-5. Based on OS dataflow, we move part of the input width to the innermost temporal loop, and the same weights are reused across those inputs. Instead of having single-entry L0 PSum registers for temporal accumulation in the MAC array, we expand it to be a *ow*0-entry PSum accumulation collector to temporally hold  $ow0 \times ochn_parallel$  PSums during FW, FW, ICHN and ow0 loops. In this way, reuse per PSum buffer write stays the same as the OS dataflow while reuse per weight buffer read and weight register write goes up to ow0. The overhead is that the multi-entry PSum collector needs muxes and thus the energy consumption of read and write is higher compared to that of the single-entry PSum accumulation register. A summary of the reuse opportunity can be found in Table 2.2.

#### 2.3 System 1 and its Evaluation

The previous section introduces the proposed hybrid dataflows on a MAC-array-based spatial datapath with channel-wise spatial mapping. That expands the design space with options to balance the reuse opportunities between different data types and storage elements. In this section, we briefly present an evaluation of the impact of our proposed techniques on the energy efficiency and performance per area of a DL

Figure 2-5: Illustration of OS-LWS (a) dataflow and (b) memory hierarchy. The differences between the WS dataflow are highlighted in red.

accelerator done in collaboration with Rangharajan Venkatesan, Yakun Sophia Shao, Jason Clemons, Steve Dai, Matthew Fojtik, Ben Keller, Alicia Klinefelter, Nathaniel Pinckney, Priyanka Raina, Yanqing Zhang, Brian Zimmer, William J. Dally, Joel Emer, Stephen W. Keckler, and Brucek Khailany during the author's internship at

Table 2.2: Summary of reuse per read/write of L1 buffers/L0 collectors and reuse per write of L0 registers in WS-LOS and OS-LWS dataflows.

| Data Type | Storage Unit                 | WS-LOS | OS-LWS     |

|-----------|------------------------------|--------|------------|

| Weight    | L1 buffer                    | OH×OW  | ow0        |

|           | L0 collector/<br>L0 register | 0*     | ow0        |

| PSum/OA   | L1 buffer                    | ichn0  | FH×FW×ICHN |

|           | L0 collector/<br>L0 register | 0      | 0*         |

| IA        | L1 buffer                    | 0      | 0          |

|           | L0 register                  | 0      | 0          |

The differences between the baseline WS/OS dataflow are highlighted in red.

\*Collectors has multiple entries and thus muxes are needed per read/write. That increases the energy consumption per read/write compared to registers.

#### NVIDIA.

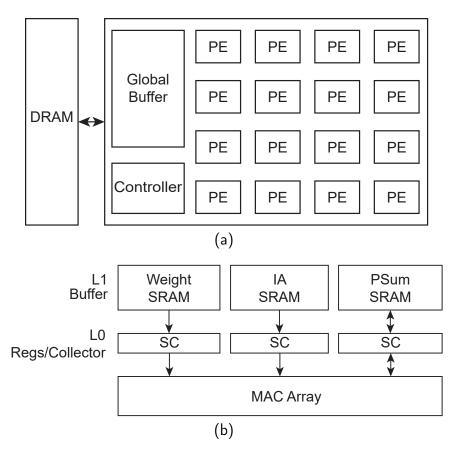

The proposed techniques were evaluated with a DL system shown in Fig. 2-6a. It comprises a processing element (PE) array as the main workhorse, a global buffer for data transfer between DRAM and chip, and a controller. The MAC-array-based spatial datapath is distributed in the PEs with local buffers and local controllers. The PE architecture is shown in Fig. 2-6b. SRAMs are used for L1 buffers and standard cells are used for the L0 registers/collectors.

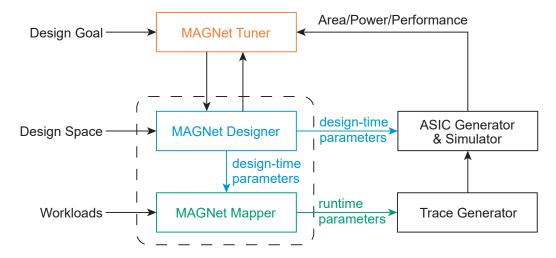

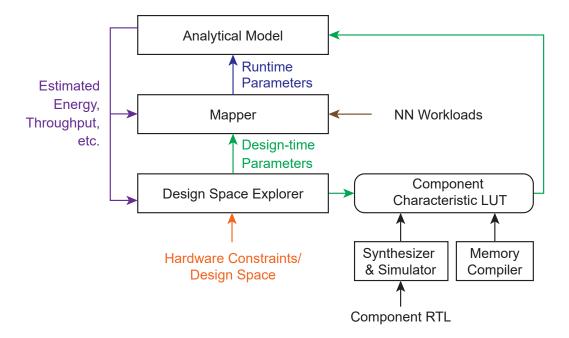

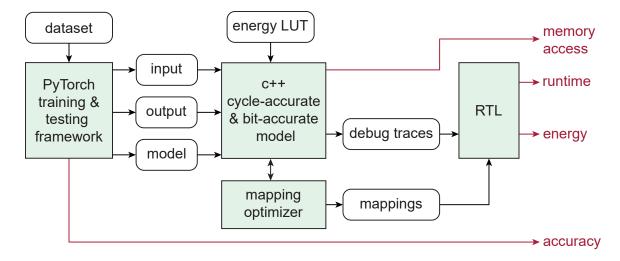

MAGNet [54] shown in Fig. 2-7 is developed to explore the design space of PEs and search for the best design-time and runtime parameters for given workloads. The design space of PEs is shown in Table 2.3. The MAGNet designer takes that as the input and generates a set of design-time parameters. An RTL generator, which consists a systemC-based parameterized architecture template, uses those design-time parameters to generate RTL [31]. The MAGNet mapper takes in the design-time parameters and workloads, and searches for the best runtime parameters, such as the tile size, for the accelerator. Given the runtime parameters, a trace generator produces the configuration bits and data traces for simulation. Traditional RTL synthesis, place-and-route, and simulation tools are used to evaluate the power, performance,

Figure 2-6: (a) The overall architecture of system 1. PE: processing element. (b) The PE architecture. The MAC array is shown in Fig. 2-2a. SC: standard cell.

and area of the generated accelerator. The designer sets the design goal for the MAGNet tuner and uses it to tune the designer and mapper to efficiently explore the design space guided by the power, performance, and area of generated designs.

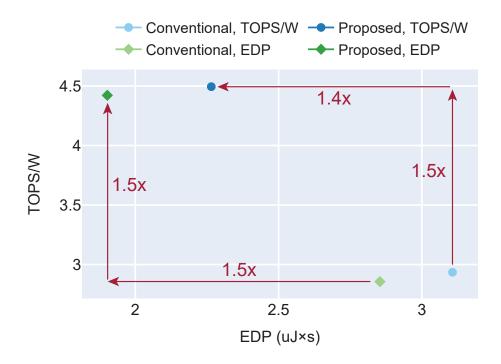

The design is implemented with TSMC 16-nm FinFET technology. It is optimized across a workload of three NNs—AlexNet [33], ResNet [21], and DriveNet [3] weighted by their number of operations. Fig. 2-8 shows the evaluation results of a baseline accelerator optimized with the conventional dataflows, and the most energyefficient accelerator design with the proposed hybrid dataflows. As shown, our proposed hybrid dataflows improve energy efficiency by 1.75x and performance per area by 2.1x running ResNet. Fig. 2-9 shows the energy breakdown of the most energyefficient PE with VL and VS of 16 under different dataflows. As shown, our proposed hybrid dataflows greatly reduce the energy of memory access compared to the baseline WS and OS dataflows.

Figure 2-7: Overview of MAGNet framework [54]. Its capability to co-design the DL application is not used in our evaluation and thus is not included in this figure.

Table 2.3: The design space of system 1 [54]. A conventional design space contains WS and OS dataflow. The proposed hybrid dataflow expands the design space with WS-LOS and OS-LWS dataflows.

| Bit-width             | 8-b weight/activation, 24-b PSum |  |

|-----------------------|----------------------------------|--|

| VL/VS                 | 4, 8, 16                         |  |

| Weight Collector Size | 8 B – 2 KB                       |  |

| PSum Collector Size   | 8 B – 384 B                      |  |

| IA Buffer Size        | 2 KB, 8 KB, 16 KB                |  |

| Weight Buffer Size    | 4 KB – 128 KB                    |  |

| PSum Buffer Size      | 1 KB – 6 KB                      |  |

| Global Buffer Size    | 64 KB                            |  |

| Target Frequencies    | 500 MHz, 1 GHz                   |  |

| Supply Voltage        | 0.6 V                            |  |

| Dataflow              | WS, OS, WS-LOS, OS-LWS           |  |

# 2.4 System 2 and its Evaluation

The last section presents the benefits of hybrid dataflows on energy efficiency and performance per area on a 16-nm accelerator with a memory system composed of off-chip DRAM and on-chip SRAM. As discussed in Section 2.2, the technology and its characteristics of storage units affect the choice of optimal dataflow and temporal mapping. In this section, we expand our analysis to a fully on-chip NN accelerator with emerging eMRAM in 22-nm technology. In the evaluation, we compare

Figure 2-8: Comparison of energy efficiency and performance per area of the optimal accelerators with conventional dataflows and the proposed dataflows. The proposed hybrid dataflows greatly improve energy efficiency and performance per area.

Figure 2-9: The energy breakdown of a PE with VL and VS of 16.

the optimal design achieved by our proposed techniques with the optimal design of conventional dataflow to show the benefits of our hybrid dataflows. The evaluation also serves as an early-stage exploration for their application with emerging embedded non-volatile memory for edge computing applications, such as automotive and Industry 4.0.

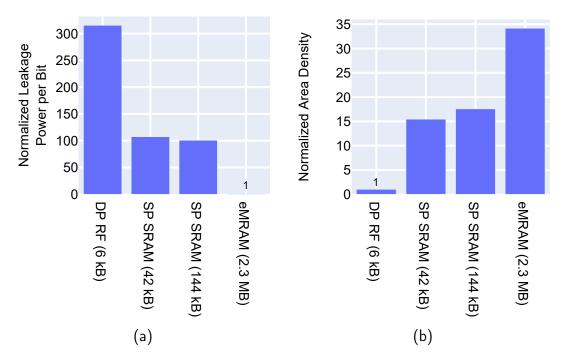

Figure 2-10: Normalized (a) read energy per bit, and (b) write energy per bit of 22nm eMRAM and 28-nm standard cell memory (SCM) and SRAM relative to 512-b SCM. DP RF: the dual-port register file from 28-nm memory compilers (this thesis refers to it as SRAM). SP SRAM: single-port SRAM.

#### 2.4.1 Technology

This system targets TSMC 22-nm technology with eMRAM. But as TSMC 22-nm memory compilers are not available for university access, we use 28-nm technology as an estimate in our evaluation.

#### $\mathbf{eMRAM}$

STT-MRAM is a promising solution for next-generation embedded non-volatile memory. Technology developments have brought us logic-compatible and high-retention eMRAM [14, 44]. It helps keep all data on-chip which eliminates the need for energyconsuming off-chip data access. Moreover, it enables duty cycling to reduce the power consumption of applications that do not need to be always on and maintains NN parameters and boot codes locally avoiding the need for cloud access [25].

Compared to eFlash, which is difficult to scale any further, eMRAM reduces mask

Figure 2-11: Normalized (a) read speed, and (b) write speed of 22-nm eMRAM and 28-nm SRAM relative to eMRAM. DP RF: the dual-port register file from 28-nm memory compilers (this thesis refers to it as SRAM). SP SRAM: single-port SRAM.

adders by over 2x, achieves similar read/write speed and read power, and delivers over 100x higher retention while leading to around 2x higher write power [14]. Compared to off-chip DRAM, MRAM achieves similar bandwidth with 44x less access energy [44]. Fig. 2-10, 2-11, and 2-12 compare eMRAM over 28-nm standard cell memory (SCM) and SRAM. As shown, eMRAM delivers over 2x higher area density and over 100x less leakage power compared to SRAM while having much higher access energy and lower access speed (the inverse of cycle time), especially for writes. Moreover, the minimum macro capacity of eMRAM is over 1000x compared to that of SRAM. The characteristics of eMRAM affect how it can be used in the DL accelerator, which will be discussed in the next section.

#### 2.4.2 Overall Architecture

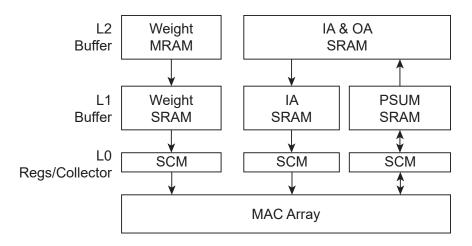

Fig. 2-13 shows the overall architecture of the accelerator chip. A monolithic MAC array is used. More complicated architecture with multiple MAC arrays distributed

Figure 2-12: Normalized (a) leakage power per bit and (b) area density of 22-nm eMRAM and 28-nm SRAM. DP RF: the dual-port register file from 28-nm memory compilers (this thesis refers to it as SRAM). SP SRAM: single-port SRAM.

in a processing element array, like Simba [48], is left as future work. The lowestlevel storage elements are either IA/weight/accumulation registers or a weight/PSum collector for hybrid dataflows. Above that, two levels of buffers are implemented for each data type. eMRAM is used as the last level buffer for weights for the following reasons—1) weights need to be kept in non-volatile memory during power down, 2) the high area density and low leakage of eMRAM make large memory less costly compared to SRAM, 3) the reuse opportunity per access can be high in the last level storage reducing the read bandwidth requirements. The last level buffer for IA and OA is made of SRAM instead of eMRAM, although the above 2) and 3) also hold in this case. The reason is that it is challenging to supply enough write bandwidth with eMRAM for medium/large-scale NN processing as indicated in Fig. 2-11b. Tiny NNs with several thousand parameters or even fewer are not included in the target workload as they cannot fully utilize the capacity of eMRAM available, which is in the MB range. Furthermore, the write energy of eMRAM is much higher than

Figure 2-13: Overall system architecture. The system is fully on-chip with eMRAM.

| Bit-width              | 8-b weight/activation, 24-b PSum                                     |  |

|------------------------|----------------------------------------------------------------------|--|

| VL/VS                  | 16                                                                   |  |

| Weight Collector Depth | 2, 4, 8                                                              |  |

| PSum Collector Depth   | 4, 8, 32                                                             |  |

| L1 IA Buffer Depth     | 128, 256, 512, 1024                                                  |  |

| L1 Weight Buffer Depth | 128, 256, 512, 1024                                                  |  |

| L1 PSum Buffer Depth   | 128, 256, 512, 1024                                                  |  |

| L2 Weight Buffer Size  | 2.3 MB                                                               |  |

| L2 IA/OA Buffer Size   | 0.3 MB                                                               |  |

| Target Frequencies     | 100 MHz                                                              |  |

| Supply Voltage         | 0.8 V/0.9 V                                                          |  |

| Outer Dataflow         | OS                                                                   |  |

| Inner Dataflow         | WS-a, WS-b, OS-a, OS-b,<br>WS-LOS-a, WS-LOS-b,<br>OS-LWS-a, OS-LWS-b |  |

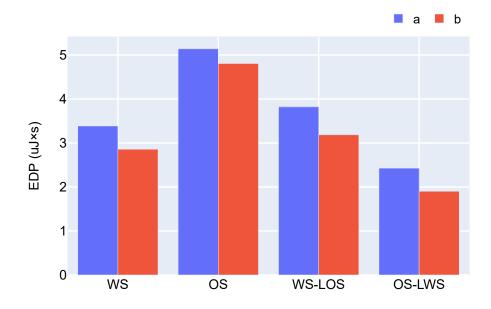

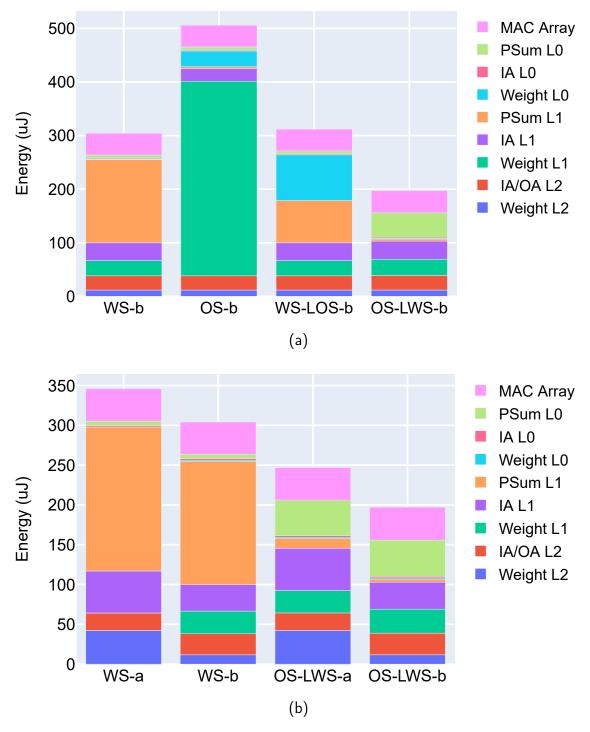

Table 2.4: The design space of the system.