# Model Acceleration for Efficient Deep Learning Computing

by

### Han Cai

B.Eng, Shanghai Jiao Tong University (2016) M.Eng, Shanghai Jiao Tong University (2019)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

May 2024

© 2024 Han Cai. This work is licensed under a CC BY-NC-ND 4.0 license.

The author hereby grants to MIT a nonexclusive, worldwide, irrevocable, royalty-free license to exercise any and all rights under copyright, including to reproduce, preserve, distribute and publicly display copies of the thesis, or release the thesis under an open-access license.

Authored by: Han Cai

Department of Electrical Engineering and Computer Science

May 17, 2024

Certified by: Song Han

Associate Professor in Electrical Engineering and Computer Science

Thesis Supervisor

Accepted by: Leslie A. Kolodziejski

Professor of Electrical Engineering and Computer Science Chair, Department Committee on Graduate Students

## Model Acceleration for Efficient Deep Learning Computing

by

#### Han Cai

Submitted to the Department of Electrical Engineering and Computer Science on May 17, 2024 in partial fulfillment of the requirements for the degree of

#### DOCTOR OF PHILOSOPHY

#### ABSTRACT

Large foundation models play a central role in achieving recent fundamental breakthroughs in artificial intelligence. By simultaneously scaling up the dataset and model size to an unprecedented level, these foundation models demonstrate remarkable performances in many areas such as protein structure prediction, image/video synthesis, code generation, ChatBot, etc. However, their computation and memory costs grow dramatically. It makes deploying these foundation models on real-world applications difficult, especially for resource-constrained edge devices. In addition, their prohibitive training cost also significantly hinders the development of new foundation models and raises concerns about the enormous energy consumption and  $CO_2$  emission. To address these concerns, building effective model acceleration techniques is critical to closing the gap between supply and demand for computing.

This thesis will cover three important aspects of model acceleration. First, we will discuss efficient representation learning, including EfficientViT (a new vision transformer architecture) for high-resolution vision and condition-aware neural networks (a new control module) for conditional image generation. Second, we will present hardware-aware acceleration techniques to create specialized neural networks for different hardware platforms and efficiency constraints. Third, we will introduce TinyTL, a memory-efficient transfer learning technique to enable on-device model customization. Through our design, we can significantly boost deep neural networks' efficiency on hardware without losing accuracy, making them more accessible and reducing their serving cost. For example, our model delivers  $48.9 \times$  higher throughput on A100 GPU while achieving slightly better zero-shot instance segmentation performance than the state-of-the-art model. For conditional image generation, our approach achieves  $52 \times$  computational cost reduction without performance degradation.

Thesis supervisor: Song Han

Title: Associate Professor in Electrical Engineering and Computer Science

# Acknowledgments

First, I want to thank my PhD advisor, Professor Song Han. I have been very fortunate to receive his guidance for the five years of the PhD. He always provides the best support for us and helps us pursue our research interests. His enthusiasm for impactful research greatly motivated me. His deep connection with the industry made his advice insightful beyond the academic context. I also thank my friends and lab mates at MIT: Hanrui Wang, Zhijian Liu, Yujun Lin, Ji Lin, Haotian Tang, Ligeng Zhu, Zhekai Zhang, Guangxuan Xiao, Muyang Li, Shang Yang, Wei-Ming Chen, Wei-Chen Wang, Nicole Stiles, and Tianhao Huang. It was a great pleasure to have you all during my PhD journey.

I also want to thank my advisors during my master's and undergraduate years, Professor Yong Yu and Professor Weinan Zhang. I started to understand what is research and how to do research work, under their supervision. It is my fortune to have them to guide me into the world of research.

I thank my PhD thesis committee members, Professor Vincent Sitzmann and Professor Vijay Janapa Reddi, for their time, help, and advice during my thesis preparation and defense.

I want to thank my mom and dad for their continued support, even though I haven't been home for four years due to various reasons.

Finally, I thank the Qualcomm Innovation Fellowship and Analog Devices Graduate Fellowship for the funding support.

# Contents

| A  | bstra | uct                                                           | 3  |

|----|-------|---------------------------------------------------------------|----|

| A  | ckno  | wledgments                                                    | 5  |

| Li | st of | Figures                                                       | 9  |

| Li | st of | Tables                                                        | 13 |

| 1  | Intr  | roduction                                                     | 15 |

|    | 1.1   | Thesis Outline                                                | 15 |

| 2  | Effi  | cient Representation Learning                                 | 17 |

|    | 2.1   | Efficient Vision Transformer for High-Resolution Vision       | 17 |

|    |       | 2.1.1 Introduction                                            |    |

|    |       | 2.1.2 Related Work                                            |    |

|    |       | 2.1.3 Method                                                  |    |

|    |       | 2.1.4 Experiments                                             |    |

|    |       | 2.1.5 Conclusion                                              | 29 |

|    | 2.2   | Efficient Control Module for Conditional Image Generation     | 30 |

|    |       | 2.2.1 Introduction                                            |    |

|    |       | 2.2.2 Related Work                                            | 31 |

|    |       | 2.2.3 Method                                                  | 33 |

|    |       | 2.2.4 Experiments                                             |    |

|    |       | 2.2.5 Conclusion                                              | 40 |

| 3  | Har   | dware-Aware Acceleration                                      | 43 |

|    | 3.1   | Direct Neural Architecture Search on Target Task and Hardware | 43 |

|    |       | 3.1.1 Introduction                                            |    |

|    |       | 3.1.2 Related Work                                            |    |

|    |       | 3.1.3 Method                                                  |    |

|    |       | 3.1.4 Experiments                                             |    |

|    |       | 3.1.5 Conclusion                                              |    |

|    | 3.2   | Once-for-All Network for Diverse Deployment Scenarios         |    |

|    |       | 3.2.1 Introduction                                            |    |

|    |       | 3.2.2 Related Work                                            |    |

|    |       | 3.2.3 Method                                                  |    |

|    |       | 3.2.4   | Training Once-for-All Network on ImageNet                           | 61 |

|----|-------|---------|---------------------------------------------------------------------|----|

|    |       | 3.2.5   | Once-for-All Network Results for Different Hardware and Constraints | 62 |

|    |       | 3.2.6   | Conclusion                                                          | 66 |

| 4  | Effic | cient N | Model Customization                                                 | 67 |

|    | 4.1   | Introd  | luction                                                             | 67 |

|    | 4.2   | Tiny 7  | Transfer Learning                                                   | 68 |

|    |       | 4.2.1   | Understanding the Memory Footprint of Back-propagation              | 68 |

|    |       | 4.2.2   | Lite Residual Learning                                              | 70 |

|    |       | 4.2.3   | Discussions                                                         | 71 |

|    | 4.3   | Exper   | iments                                                              | 71 |

|    |       | 4.3.1   | Setups                                                              | 71 |

|    |       | 4.3.2   | Main Results                                                        | 73 |

|    |       | 4.3.3   | Ablation Studies and Discussions                                    | 74 |

|    | 4.4   | Concl   | usion                                                               | 76 |

| 5  | Con   | clusio  | ${f n}$                                                             | 79 |

|    | 5.1   |         | et                                                                  | 79 |

| Re | efere | nces    |                                                                     | 81 |

# List of Figures

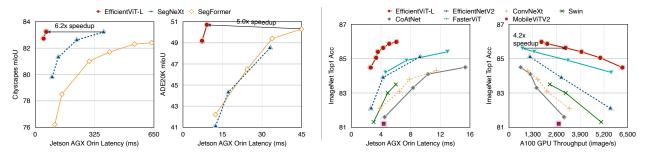

| 2.1 | Latency/Throughput vs. Performance. All performance results are obtained with the single model and single-scale inference. The GPU latency/throughput results are obtained on one edge GPU (Jetson AGX Orin) and |            |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|     | one cloud GPU (A100) using TensorRT and fp16. EfficientViT consistently                                                                                                                                          |            |

|     | achieves a remarkable boost in speed on diverse hardware platforms while pro-                                                                                                                                    |            |

|     | viding the same/higher performances on Cityscapes, ADE20K, and ImageNet                                                                                                                                          |            |

|     | than prior segmentation/classification models                                                                                                                                                                    | 18         |

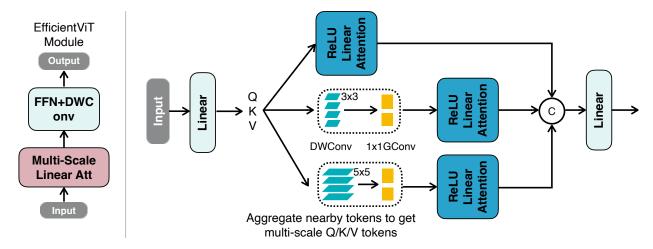

| 2.2 | EfficientViT's Building Block (left) and Multi-Scale Linear Attention                                                                                                                                            |            |

|     | (right). Left: EfficientViT's building block consists of a multi-scale linear                                                                                                                                    |            |

|     | attention module and an FFN with depthwise convolution (FFN+DWConv).                                                                                                                                             |            |

|     | Multi-scale linear attention is responsible for capturing context information,                                                                                                                                   |            |

|     | while FFN+DWConv captures local information. $Right$ : After getting $Q/K/V$                                                                                                                                     |            |

|     | tokens via the linear projection layer, we generate multi-scale tokens by aggre-                                                                                                                                 |            |

|     | gating nearby tokens via lightweight small-kernel convolutions. ReLU linear                                                                                                                                      |            |

|     | attention is applied to multi-scale tokens, and the outputs are concatenated                                                                                                                                     |            |

|     | and fed to the final linear projection layer for feature fusing                                                                                                                                                  | 19         |

| 2.3 | Softmax Attention vs. ReLU Linear Attention. Unlike softmax atten-                                                                                                                                               |            |

|     | tion, ReLU linear attention cannot produce sharp attention distributions due                                                                                                                                     |            |

|     | to a lack of the non-linear similarity function. Thus, its local information                                                                                                                                     | 20         |

| 0.4 | extraction ability is weaker than the softmax attention.                                                                                                                                                         | 20         |

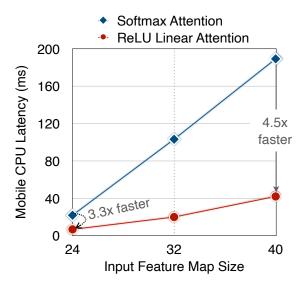

| 2.4 | Latency Comparison Between Softmax Attention and ReLU Linear                                                                                                                                                     |            |

|     | Attention. ReLU linear attention is 3.3-4.5× faster than softmax attention                                                                                                                                       |            |

|     | with similar computation, thanks to removing hardware-unfriendly operations (e.g., softmax). Latency is measured on the Qualcomm Snapdragon 855 CPU                                                              |            |

|     | with TensorFlow-Lite, batch size 1, and fp32                                                                                                                                                                     | 21         |

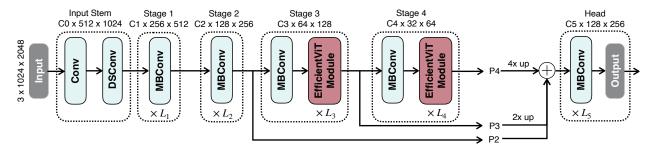

| 2.5 | Macro Architecture of EfficientViT. We adopt the standard backbone-                                                                                                                                              | <b>4</b> 1 |

| 2.0 | head/encoder-decoder design. We insert our EfficientViT modules in Stages 3                                                                                                                                      |            |

|     | and 4 in the backbone. Following the common practice, we feed the features                                                                                                                                       |            |

|     | from the last three stages (P2, P3, and P4) to the head. We use addition to                                                                                                                                      |            |

|     | fuse these features for simplicity and efficiency. We adopt a simple head design                                                                                                                                 |            |

|     | that consists of several MBConv blocks and output layers                                                                                                                                                         | 22         |

| 2.6 | Qualitative results on Cityscapes.                                                                                                                                                                               | 28         |

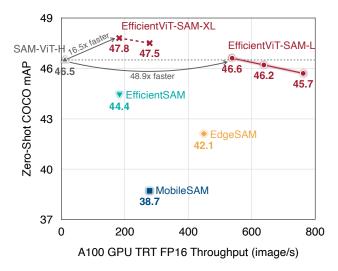

| 2.7  | Throughput vs. COCO Zero-Shot Instance Segmentation mAP. EfficientViT-SAM is the first accelerated SAM model that matches/outper-                                  |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | forms SAM-ViT-H's [4] zero-shot performance, delivering the SOTA performance-                                                                                      |    |

|      | efficiency trade-off                                                                                                                                               | 29 |

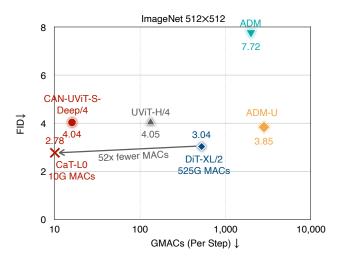

| 2.8  | Comparing CAN Models and Prior Image Generative Models on Im-                                                                                                      | 23 |

| 2.0  | ageNet 512×512. With the new conditional control method, we significantly                                                                                          |    |

|      | improve the performance of controlled image generative models. Combining                                                                                           |    |

|      | CAN and EfficientViT [8], our CaT model provides 52× MACs reduction per                                                                                            |    |

|      | sampling step than DiT-XL/2 [83] without performance loss                                                                                                          | 30 |

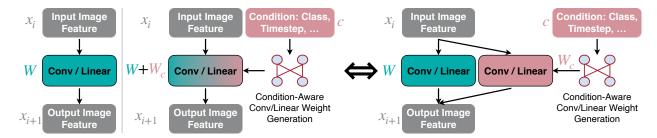

| 2.9  | Illustration of Condition-Aware Neural Network. Left: A regular neural                                                                                             |    |

|      | network with static convolution/linear layers. Right: A condition-aware neural                                                                                     |    |

|      | network and its equivalent form.                                                                                                                                   | 31 |

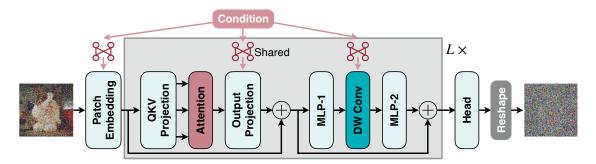

| 2.10 | Overview of Applying CAN to Diffusion Transformer. The patch                                                                                                       |    |

|      | embedding layer, the output projection layers in self-attention, and the depth-                                                                                    |    |

|      | wise convolution (DW Conv) layers are condition-aware. The other layers are                                                                                        |    |

|      | static. All output projection layers share the same conditional weight while                                                                                       |    |

|      | still having their own static weights                                                                                                                              | 32 |

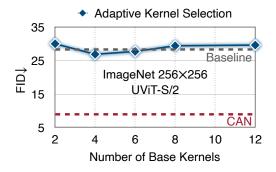

|      | CAN is More Effective than Adaptive Kernel Selection.                                                                                                              | 34 |

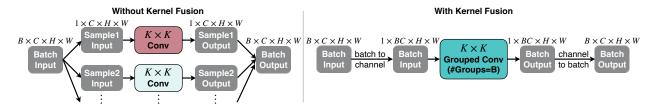

| 2.12 | Practical Implementation of CAN. Left: The condition-aware layers have                                                                                             |    |

|      | different weights for different samples. A naive implementation requires running                                                                                   |    |

|      | the kernel call independently for each sample, which incurs a large overhead for                                                                                   |    |

|      | training and batch inference. <i>Right:</i> An efficient implementation for CAN. We fuse all kernel calls into a grouped convolution. We insert a batch-to-channel |    |

|      | transformation before the kernel call and add a channel-to-batch conversion                                                                                        |    |

|      | after the kernel call to preserve the functionality                                                                                                                | 35 |

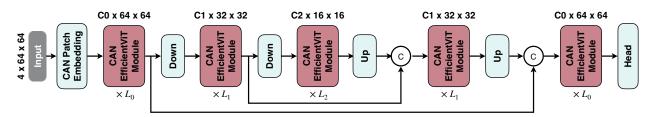

| 2.13 | Macro Architecture of CaT. Benefiting from EfficientViT's linear computa-                                                                                          | 00 |

| 2.10 | tional complexity [8], we can keep the high-resolution stages without efficiency                                                                                   |    |

|      | concerns                                                                                                                                                           | 35 |

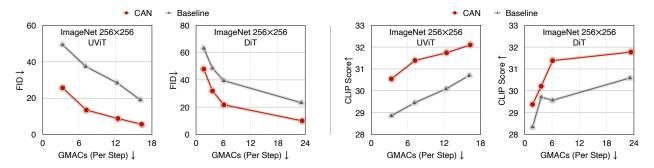

| 2.14 | CAN Results on Different UViT and DiT Variants. CAN consistently                                                                                                   |    |

|      | delivers lower FID and higher CLIP score for UViT and DiT variants                                                                                                 | 36 |

| 2.15 | Training Curve. CAN's improvements are not due to faster convergence.                                                                                              |    |

|      | We observe consistent FID improvements when trained longer                                                                                                         | 37 |

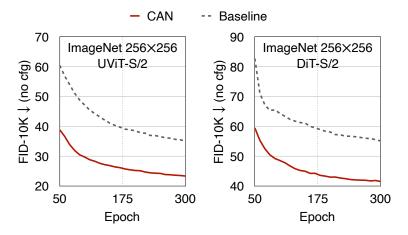

| 2.16 | Samples of Generated Images by CAN Models                                                                                                                          | 41 |

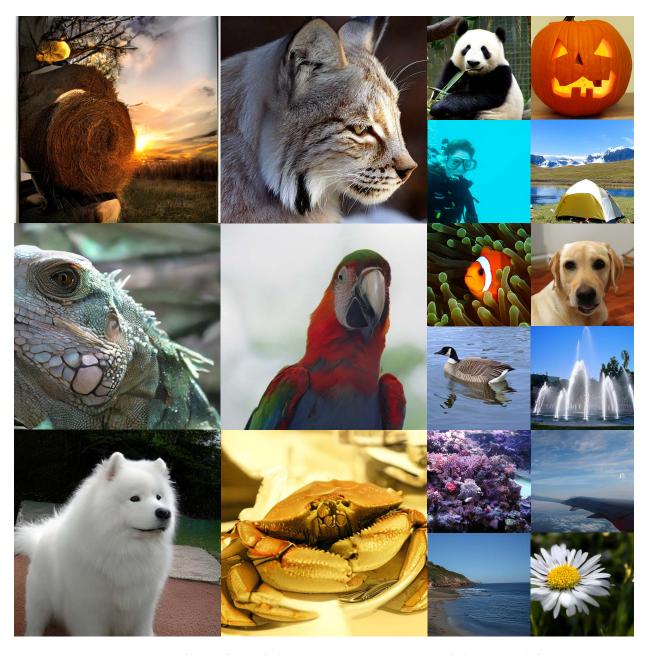

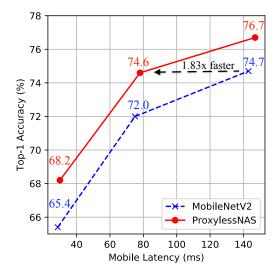

| 3.1  | ProxylessNAS directly optimizes neural network architectures on target task                                                                                        |    |

| 0.1  | and hardware. Benefiting from the directness and specialization, ProxylessNAS                                                                                      |    |

|      | can achieve remarkably better results than previous proxy-based approaches.                                                                                        |    |

|      | On ImageNet, with only 200 GPU hours (200 × fewer than MnasNet [114]),                                                                                             |    |

|      | our searched CNN model for mobile achieves the same level of top-1 accuracy                                                                                        |    |

|      | as MobileNetV2 1.4 while being 1.8× faster                                                                                                                         | 44 |

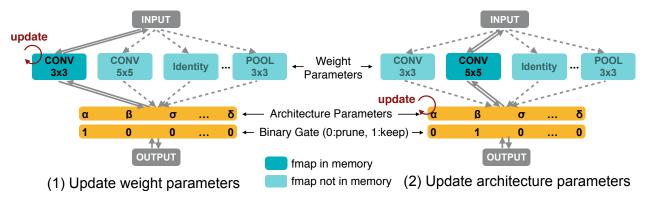

| 3.2  | Learning both weight parameters and binarized architecture parameters                                                                                              | 45 |

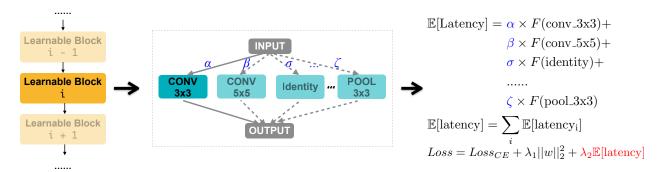

| 3.3  | Making latency differentiable by introducing latency regularization loss                                                                                           | 48 |

| 3.4  | ProxylessNAS consistently outperforms MobileNetV2 under various latency                                                                                            |    |

|      | settings.                                                                                                                                                          | 50 |

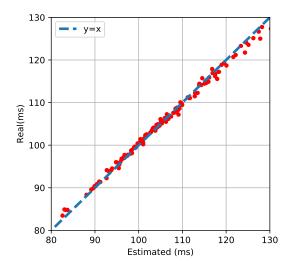

| 3.5  | Our mobile latency model is close to $y = x$ . The latency RMSE is 0.75ms                                                                                          | 50 |

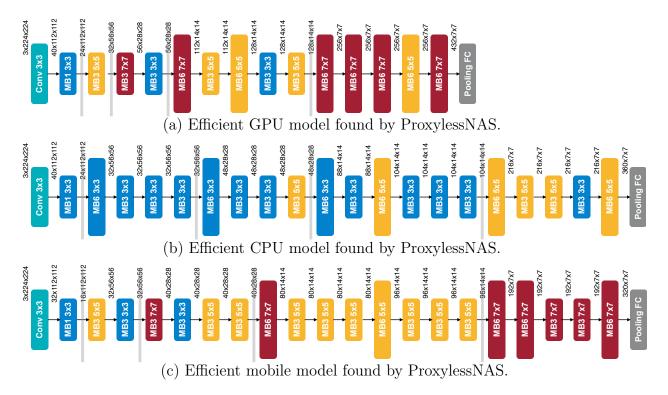

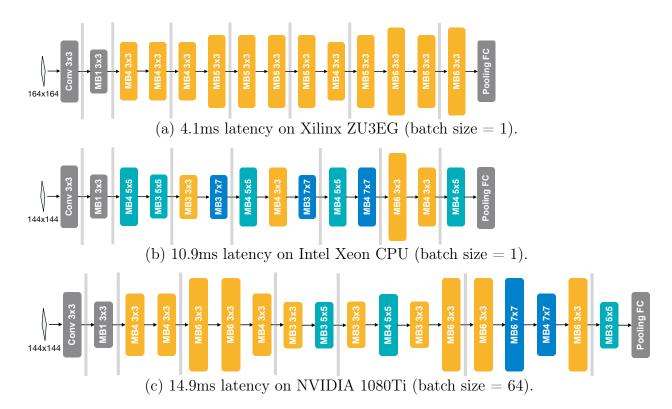

| 3.6  | Efficient models optimized for different hardware. "MBConv3" and "MBConv6" denote mobile inverted bottleneck convolution layer with an expansion ratio of 3 and 6 respectively. Insights: GPU prefers shallow and wide model with early pooling; CPU prefers deep and narrow model with late pooling. Pooling layers prefer large and wide kernel. Early layers prefer small kernel. Late |          |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3.7  | layers prefer large kernel                                                                                                                                                                                                                                                                                                                                                                | 51       |

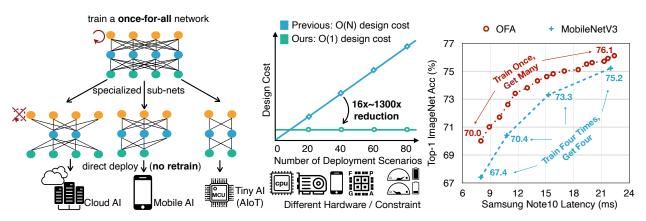

|      | network followed by model selection can derive many accuracy-latency trade-<br>offs by training only once, compared to conventional methods that require<br>repeated training.                                                                                                                                                                                                            | 54       |

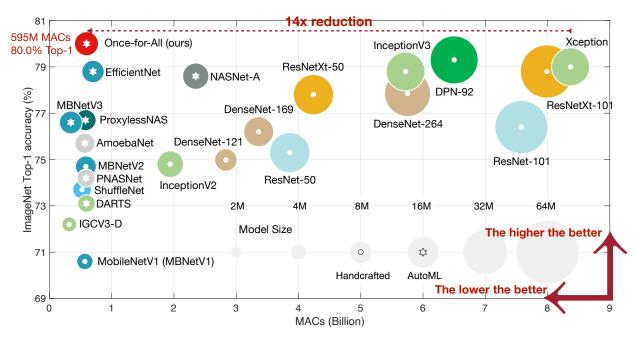

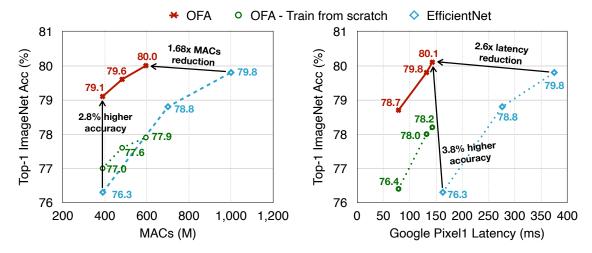

| 3.8  | Comparison between OFA and state-of-the-art CNN models on ImageNet. OFA provides 80.0% ImageNet top1 accuracy under the mobile setting (<                                                                                                                                                                                                                                                 | 55       |

| 3.9  | 600M MACs)                                                                                                                                                                                                                                                                                                                                                                                |          |

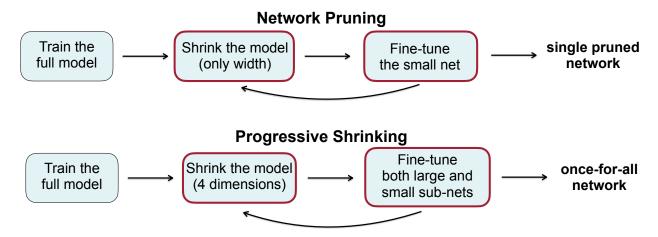

| 3.10 | with much higher flexibility. Compared to network pruning, it shrinks more dimensions (not only width) and provides a much more powerful once-for-all network that can fit different deployment scenarios rather than a single pruned                                                                                                                                                     | 57       |

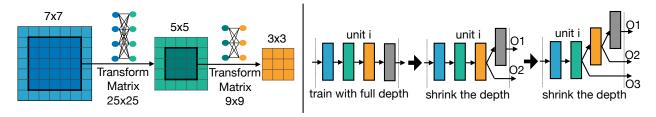

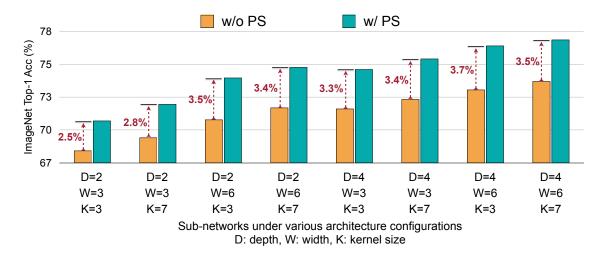

| 3.11 | network                                                                                                                                                                                                                                                                                                                                                                                   | 58       |

| 3.12 | early layers are shared                                                                                                                                                                                                                                                                                                                                                                   | 59<br>59 |

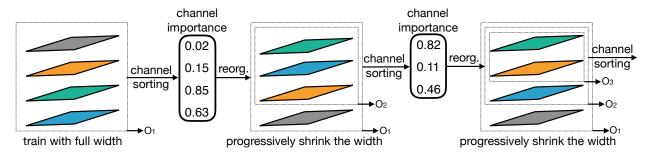

| 3.13 | settings. The important channels' weights are shared                                                                                                                                                                                                                                                                                                                                      | 99       |

|      | each unit, and each layer has an width expansion ratio $w$ and kernel size $k$ .                                                                                                                                                                                                                                                                                                          | 60       |

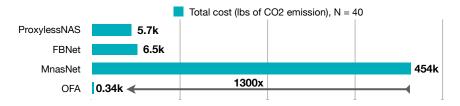

|      | OFA saves orders of magnitude design cost compared to NAS methods                                                                                                                                                                                                                                                                                                                         | 61       |

| 3.15 | OFA achieves 80.0% top1 accuracy with 595M MACs and 80.1% top1 accuracy with 143ms Pixel1 latency, setting a new SOTA ImageNet top1 accuracy on the mebile setting.                                                                                                                                                                                                                       | co       |

| 9.16 | the mobile setting                                                                                                                                                                                                                                                                                                                                                                        | 62       |

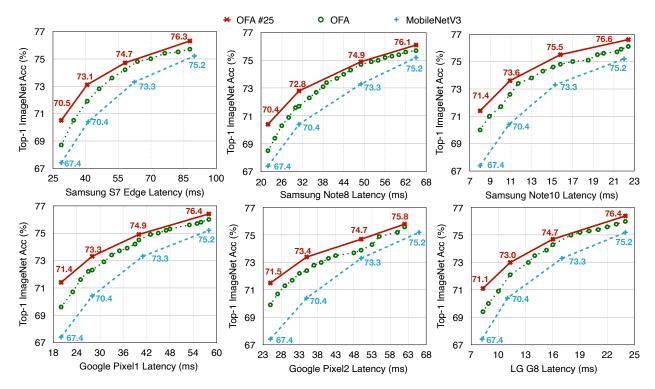

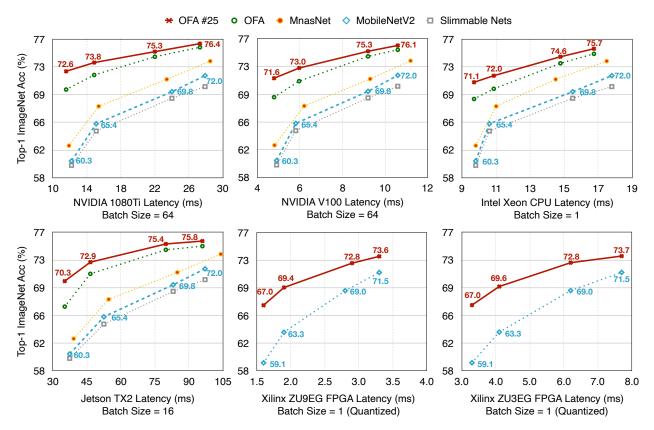

| 3.16 | accuracy with similar latency than non-specialized neural networks on CPU, GPU, mGPU, and FPGA. More remarkably, specializing for a new hardware                                                                                                                                                                                                                                          | 63       |

|      | platform does not add training cost using OFA                                                                                                                                                                                                                                                                                                                                             | 64       |

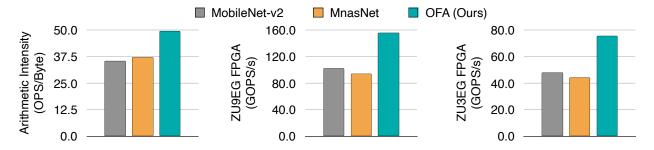

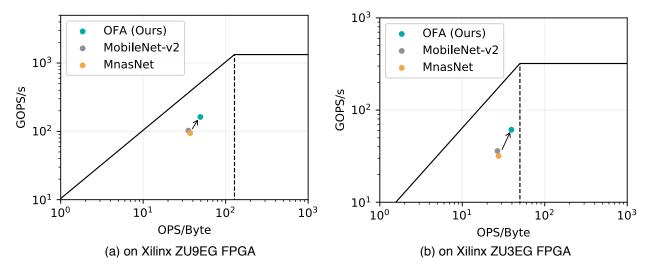

| 3.18 | OFA models improve the arithmetic intensity (OPS/Byte) and utilization                                                                                 |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | (GOPS/s) compared with the MobileNetV2 and MnasNet (measured results                                                                                   |     |

|      | on Xilinx ZU9EG and ZU3EG FPGA).                                                                                                                       | 65  |

| 3.19 | Quantative study of OFA's roofline model on Xilinx ZU9EG and ZU3EG                                                                                     |     |

|      | FPGAs (log scale). OFA model increased the arithmetic intensity by 33%/43%                                                                             |     |

|      | and GOPS/s by $72\%/92\%$ on these two FPGAs compared with MnasNet                                                                                     | 65  |

| 3.20 | OFA can design specialized models for different hardware and different latency                                                                         |     |

|      | constraint. "MB4 3x3" means "mobile block with expansion ratio 4, kernel                                                                               |     |

|      | size 3x3". FPGA and GPU models are wider than CPU model due to larger                                                                                  |     |

|      | parallelism. Different hardware has different cost model, leading to different                                                                         |     |

|      | optimal CNN architectures. OFA provides a unified and efficient design                                                                                 |     |

|      | methodology.                                                                                                                                           | 66  |

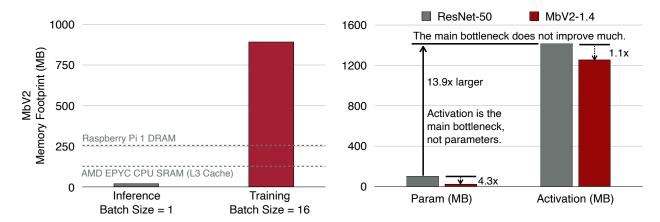

| 4.1  | Left: The memory footprint required by training is much larger than inference.                                                                         |     |

| 1.1  | Right: Memory cost comparison between ResNet-50 and MobileNetV2-1.4                                                                                    |     |

|      | under batch size 16. Recent advances in efficient model design only reduce the                                                                         |     |

|      | size of parameters, but the activation size, which is the main bottleneck for                                                                          |     |

|      | training, does not improve much                                                                                                                        | 68  |

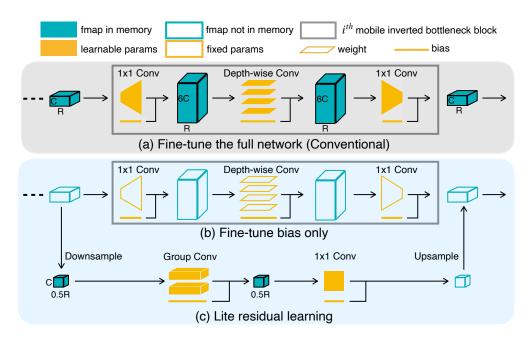

| 4.2  | TinyTL overview ("C" denotes the width and "R" denote the resolution).                                                                                 |     |

|      | Conventional transfer learning relies on fine-tuning the weights to adapt the                                                                          |     |

|      | model (Fig.a), which requires a large amount of activation memory (in blue)                                                                            |     |

|      | for back-propagation. TinyTL reduces the memory usage by fixing the weights                                                                            |     |

|      | (Fig.b) while only fine-tuning the bias. (Fig.c) exploit lite residual learning                                                                        |     |

|      | to compensate for the capacity loss, using group convolution and avoiding                                                                              |     |

|      | inverted bottleneck to achieve high arithmetic intensity and small memory                                                                              | 00  |

| 4.9  | footprint. The skip connection remains unchanged (omitted for simplicity).                                                                             | 69  |

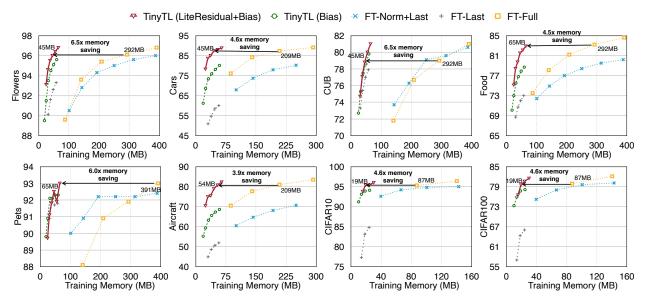

| 4.3  | Top1 accuracy results of different transfer learning methods under varied resolutions using the same pre-trained neural network (ProxylessNAS-Mobile). |     |

|      | With the same level of accuracy, TinyTL achieves 3.9-6.5× memory saving                                                                                |     |

|      | compared to fine-tuning the full network                                                                                                               | 74  |

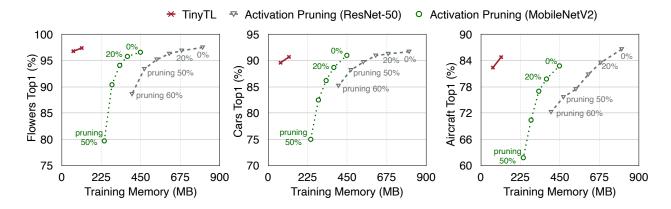

| 4.4  | Compared with the dynamic activation pruning [175], TinyTL saves the                                                                                   | , 1 |

|      | memory more effectively                                                                                                                                | 76  |

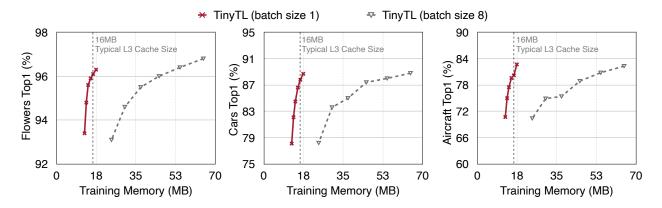

| 4.5  | Results of TinyTL when trained with batch size 1. It further reduces the                                                                               |     |

|      | training memory footprint to around 16MB (typical L3 cache size), making it                                                                            |     |

|      | possible to train on the cache (SRAM) instead of DRAM                                                                                                  | 76  |

# List of Tables

| 2.1  | Ablation Study. The mIoU and MACs are measured on Cityscapes with                        |    |

|------|------------------------------------------------------------------------------------------|----|

|      | 1024x2048 input resolution. We rescale the width of the models so that they              |    |

|      | have the same MACs. Multi-scale learning and the global receptive field are              |    |

|      | essential for obtaining good semantic segmentation performance                           | 24 |

| 2.2  | Backbone Performance on ImageNet Classification. 'r224' means the                        |    |

|      | input resolution is 224x224. 'bs1' represents that the latency is measured with          |    |

|      | batch size 1                                                                             | 25 |

| 2.3  | Comparison with SOTA Semantic Segmentation Models on Cityscapes.                         |    |

|      | The input resolution is 1024x2048 for all models. Models with similar mIoU               |    |

|      | are grouped for efficiency comparison.                                                   | 26 |

| 2.4  | Comparison with SOTA Semantic Segmentation Models on ADE20K.                             |    |

|      | The shorter side of the image is resized to 512, following the common practice.          | 27 |

| 2.5  | Comparison with SOTA super-resolution models.                                            | 27 |

| 2.6  | Zero-Shot Instance Segmentation Results, Prompted with ViTDet                            |    |

|      | Boxes. Throughput is profiled on A100 GPU with TensorRT and fp16,                        |    |

|      | including the image encoder and SAM head                                                 | 28 |

| 2.7  | Zero-Shot Point-Prompted Segmentation Results                                            | 29 |

| 2.8  | Ablation Study on Making Which Modules Condition-Aware                                   | 34 |

| 2.9  | Ablation Study on the Effect of Each Condition for CAN                                   | 37 |

| 2.10 | Comparison with Prior Conditional Control Methods. CAN can work                          |    |

|      | alone without adding other conditional control methods                                   | 38 |

| 2.11 | Class-Conditional Image Generation Results on ImageNet                                   | 39 |

| 2.12 | NVIDIA Jetson AGX Orin Latency vs. FID. Latency is profiled with                         |    |

|      | TensorRT and fp16                                                                        | 39 |

| 2.13 | Text-to-Image Generation Results on COCO 256 $\times$ 256                                | 40 |

| 3.1  | ProxylessNAS achieves state-of-the art accuracy (%) on ImageNet (under                   |    |

|      | mobile latency constraint $\leq 80ms$ ) with $200 \times$ less search cost in GPU hours. |    |

|      | "LL" indicates latency regularization loss                                               | 49 |

| 3.2  | ImageNet Accuracy (%) and GPU latency (Tesla V100) on ImageNet                           | 52 |

| 3.3  | Hardware prefers specialized models. Models optimized for GPU does not                   |    |

|      | run fast on CPU and mobile phone, vice versa. ProxylessNAS provides an                   |    |

|      | efficient solution to search a specialized neural network architecture for a target      |    |

|      | hardware architecture, while cutting down the search cost by $200 \times$ compared       |    |

|      | with state-of-the-arts [43], [114].                                                      | 52 |

|      |                                                                                          |    |

| 3.4 | Comparison with SOTA hardware-aware NAS methods on Pixel1 phone. OFA decouples model training from neural architecture search. The search cost and training cost both stay constant as the number of deployment scenarios grows. "#25" denotes the specialized sub-networks are fine-tuned for 25 epochs after grabbing weights from the once-for-all network. " $CO_2e$ " denotes $CO_2$ emission which is calculated based on [131]. AWS cost is calculated based on the price of on-demand P3.16xlarge instances.                                                      | 61 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1 | Detailed forward and backward processes of non-linear activation layers. $ \mathbf{a}_i $ denotes the number of elements of $\mathbf{a}_i$ . " $\circ$ " denotes the element-wise product. $(1_{\mathbf{a}_i \geq 0})_j = 0$ if $(\mathbf{a}_i)_j < 0$ and $(1_{\mathbf{a}_i \geq 0})_j = 1$ otherwise. ReLU6( $\mathbf{a}_i$ ) =                                                                                                                                                                                                                                         |    |

| 4.2 | min(6, max(0, $\mathbf{a}_i$ ))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 70 |

| 4.3 | same level of accuracy as $FT$ - $Full$ while being $6\times$ memory efficient Comparison with previous transfer learning results under different backbone neural networks. 'I-V3' is Inception-V3; 'N-A' is NASNet-A Mobile; 'M2-1.4' is MobileNetV2-1.4; 'R-50' is ResNet-50; 'PM' is ProxylessNAS-Mobile; 'FA' represents feature extractor adaptation. $^{\dagger}$ indicates the last two layers are updated besides biases and lite residual modules in TinyTL. TinyTL+FA reduces the training memory by <b>7.5-12.9</b> × without sacrificing accuracy compared to | 72 |

| 4.4 | fine-tuning the widely used Inception-V3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75 |

|     | provides competitive results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 75 |

# Chapter 1

# Introduction

Large foundation models have revolutionized many AI areas, including natural language processing [1], [2], computer vision [3]–[5], AI for science [6], etc. By scaling up the model size and training these models on web-scale datasets, these foundation models demonstrate astounding few-shot/zero-shot learning abilities in solving complicated tasks. These remarkable performances have driven a surge of interest in using these foundation models in real-world applications, bringing AI to our work and daily lives.

However, these foundation models have prohibitive training and inference costs due to the increased model size and computation cost. For example, a GPT-3 [7] model has 175B parameters. Storing it alone already exceeds the capacity of the current most powerful GPUs (e.g., NVIDIA H100 GPU). It poses big challenges for serving these models on cloud platforms or deploying them on edge devices. In addition, prohibitive training cost also leads to enormous energy consumption and  $\mathrm{CO}_2$  emission, raising sustainability concerns about these AI foundation models.

In this dissertation, we aim to investigate model acceleration techniques to improve the efficiency of deep neural networks to tackle this challenge. Our approach accelerates deep neural networks from three aspects. First, we will discuss efficient representation learning, targeting to build efficient building blocks / neural network architectures to extract useful information from the raw data. Second, we will discuss hardware-aware acceleration, aiming to get specialized neural networks for different hardware platforms and efficiency constraints to get the best trade-off between accuracy and hardware efficiency. Third, we will discuss efficient model customization that enables memory-efficient on-device learning to offer customized AI services without sacrificing privacy. We summarize the main content of this thesis as follows:

# 1.1 Thesis Outline

• Chapter 2 describes techniques for efficient representation learning. The content is based on [8] and [9]. First, the transformer architecture is the core component of current large foundation models. However, the transformer architecture is bad at handling long sequences since its computational cost grows quadratically as the input sequence length increases. We propose EfficientViT, a new vision transformer architecture for high-resolution vision. It achieves global receptive field and strong capacity with only hardware-efficient operations.

EfficientViT delivers remarkable performance gains over previous models with speedup on diverse hardware platforms. Second, adding control is a critical step to convert image/video generative models to productive tools for humans. We propose condition-aware neural network (CAN), a new method for adding control to image generative models. In parallel to prior conditional control methods, CAN controls the image generation process by dynamically manipulating the weight of the neural network. CAN consistently delivers significant improvements for diffusion transformer models.

- Chapter 3 presents hardware-aware AutoML techniques to efficiently get specialized deep neural networks for different hardware platforms and efficiency constraints. The content is based on [10] and [11]. Different hardware platforms have different properties (e.g., degree of parallelism, cache size, bandwidth, etc.). Given different target hardware platforms and different efficiency constraints, we need specialized neural networks to achieve the best trade-off between performance and efficiency. However, manually customizing neural networks for each case is unscalable. Thus, we propose hardware-aware AutoML techniques to tackle this challenge. Our approach delivers significant speedup on diverse hardware platforms, including mobile phones, CPU, GPU, FPGA, etc. In addition, our approach has won first place in multiple low-power computer vision challenges.

- Chapter 4 presents TinyTL [12] for memory-efficient on-device learning. TinyTL freezes the weights while only learns the memory-efficient bias modules, thus no need to store the intermediate activations. To maintain the adaptation capacity, we introduce a new memory-efficient bias module, the lite residual module, to refine the feature extractor by learning small residual feature maps adding only 3.8% memory overhead. Extensive experiments show that TinyTL significantly saves the memory with little accuracy loss compared to fine-tuning the full network.

# Chapter 2

# Efficient Representation Learning

# 2.1 Efficient Vision Transformer for High-Resolution Vision

### 2.1.1 Introduction

High-resolution dense prediction is a fundamental task in computer vision and has broad applications in the real world, including autonomous driving, medical image processing, computational photography, etc. Therefore, deploying state-of-the-art (SOTA) high-resolution dense prediction models on hardware devices can benefit many use cases.

However, there is a large gap between the computational cost required by SOTA high-resolution dense prediction models and the limited resources of hardware devices. It makes using these models in real-world applications impractical. In particular, high-resolution dense prediction models require high-resolution images and strong context information extraction ability to work well [13]–[18]. Therefore, directly porting efficient model architectures from image classification is unsuitable for high-resolution dense prediction.

This work introduces EfficientViT, a new family of vision transformer models for efficient high-resolution dense prediction. The core of EfficientViT is a new multi-scale linear attention module that enables the global receptive field and multi-scale learning with hardware-efficient operations. Our module is motivated by prior SOTA high-resolution dense prediction models. They demonstrate that the multi-scale learning [15], [16] and global receptive field [19] are critical in improving models' performances. However, they do not consider hardware efficiency when designing their models, which is essential for real-world applications. For example, SegFormer [19] introduces softmax attention [20] into the backbone to have a global receptive field. However, its computational complexity is quadratic to the input resolution, making it unable to handle high-resolution images efficiently. SegNeXt [21] proposes a multi-branch module with large-kernel convolutions (kernel size up to 21) to enable a large receptive field and multi-scale learning. However, large-kernel convolution requires exceptional support on hardware to achieve good efficiency [22], [23], which is usually unavailable on hardware devices.

Hence, the design principle of our module is to enable these two critical features while avoiding hardware-inefficient operations. Specifically, we propose substituting the inefficient

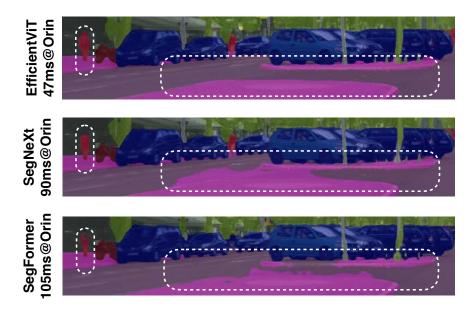

Figure 2.1: Latency/Throughput vs. Performance. All performance results are obtained with the single model and single-scale inference. The GPU latency/throughput results are obtained on one edge GPU (Jetson AGX Orin) and one cloud GPU (A100) using TensorRT and fp16. EfficientViT consistently achieves a remarkable boost in speed on diverse hardware platforms while providing the same/higher performances on Cityscapes, ADE20K, and ImageNet than prior segmentation/classification models.

softmax attention with lightweight ReLU linear attention [24] to have the global receptive field. By leveraging the associative property of matrix multiplication, ReLU linear attention can reduce the computational complexity from quadratic to linear while preserving functionality. In addition, it avoids hardware-inefficient operations like softmax, making it more suitable for hardware deployment (Figure 2.4).

However, ReLU linear attention alone has limited capacity due to the lack of local information extraction and multi-scale learning ability. Therefore, we propose to enhance ReLU linear attention with convolution and introduce the multi-scale linear attention module to address the capacity limitation of ReLU linear attention. Specifically, we aggregate nearby tokens with small-kernel convolutions to generate multi-scale tokens. We perform ReLU linear attention on multi-scale tokens (Figure 2.2) to combine the global receptive field with multi-scale learning. We also insert depthwise convolutions into FFN layers to further improve the local feature extraction capacity.

We extensively evaluate EfficientViT on two popular high-resolution dense prediction tasks: semantic segmentation and super-resolution. EfficientViT provides significant performance boosts over prior SOTA high-resolution dense prediction models. More importantly, EfficientViT does not involve hardware-inefficient operations, so our #FLOPs reduction can easily translate to latency reduction on hardware devices (Figure 2.1).

In addition to these conventional high-resolution dense prediction tasks, we apply EfficientViT to Segment Anything [4], an emerging promptable segmentation task that allows zero-shot transfer to many vision tasks. EfficientViT achieves  $48.9 \times$  acceleration on A100 GPU than SAM-ViT-Huge [4] without performance loss.

### 2.1.2 Related Work

**High-Resolution Dense Prediction.** Dense prediction targets producing predictions for each pixel given the input image. It can be viewed as an extension of image classification from per-image prediction to per-pixel predictions. Extensive studies have been done to improve the performance of CNN-based high-resolution dense prediction models [13]–[18].

Figure 2.2: EfficientViT's Building Block (left) and Multi-Scale Linear Attention (right). Left: EfficientViT's building block consists of a multi-scale linear attention module and an FFN with depthwise convolution (FFN+DWConv). Multi-scale linear attention is responsible for capturing context information, while FFN+DWConv captures local information. Right: After getting Q/K/V tokens via the linear projection layer, we generate multi-scale tokens by aggregating nearby tokens via lightweight small-kernel convolutions. ReLU linear attention is applied to multi-scale tokens, and the outputs are concatenated and fed to the final linear projection layer for feature fusing.

In addition, there are also some works targeting improving the efficiency of high-resolution dense prediction models [25]–[28]. While these models provide good efficiency, their performances are far behind SOTA high-resolution dense prediction models.

Compared to these works, our models provide a better trade-off between performance and efficiency by enabling a global receptive field and multi-scale learning with lightweight operations.

Efficient Vision Transformer. While ViT provides impressive performances in the high-computation region, it is usually inferior to previous efficient CNNs [11], [29]–[31] when targeting the low-computation region. To close the gap, MobileViT [32] proposes to combine the strength of CNN and ViT by replacing local processing in convolutions with global processing using transformers. MobileFormer [33] proposes to parallelize MobileNet and Transformer with a two-way bridge in between for feature fusing. NASViT [34] proposes to leverage neural architecture search to search for efficient ViT architectures.

However, these models mainly focus on image classification and still rely on softmax attention with quadratic computational complexity, thus unsuitable for high-resolution dense prediction.

Efficient Deep Learning. Our work is also related to efficient deep learning, which aims at improving the efficiency of deep neural networks so that we can deploy them on hardware platforms with limited resources, such as mobile phones and IoT devices. Typical technologies in efficient deep learning include network pruning [35]–[37], quantization [38], efficient model

Figure 2.3: **Softmax Attention vs. ReLU Linear Attention.** Unlike softmax attention, ReLU linear attention cannot produce sharp attention distributions due to a lack of the non-linear similarity function. Thus, its local information extraction ability is weaker than the softmax attention.

architecture design [39], [40], and training techniques [12], [41], [42]. In addition to manual designs, many recent works use AutoML techniques [10], [43], [44] to automatically design [11], prune [45] and quantize [46] neural networks.

### 2.1.3 Method

This section first introduces the multi-scale linear attention module. Unlike prior works, our multi-scale linear attention simultaneously achieves the global receptive field and multi-scale learning with only hardware-efficient operations. Then, based on the multi-scale linear attention, we present a new family of vision transformer models named EfficientViT for high-resolution dense prediction.

#### Multi-Scale Linear Attention

Our multi-scale linear attention balances two crucial aspects of efficient high-resolution dense prediction, i.e., performance and efficiency. Specifically, the global receptive field and multi-scale learning are essential from the performance perspective. Previous SOTA high-resolution dense prediction models provide strong performances by enabling these features but fail to provide good efficiency. Our module tackles this issue by trading slight capacity loss for significant efficiency improvements.

An illustration of the proposed multi-scale linear attention module is provided in Figure 2.2 (right). In particular, we propose to use ReLU linear attention [24] to enable the global receptive field instead of the heavy softmax attention [20]. While ReLU linear attention [24] and other linear attention modules [47]–[50] have been explored in other domains, it has never been successfully applied to high-resolution dense prediction. To the best of our knowledge, EfficientViT is the first work demonstrating ReLU linear attention's effectiveness in high-resolution dense prediction. In addition, our work introduces novel designs to address its capacity limitation.

Figure 2.4: Latency Comparison Between Softmax Attention and ReLU Linear Attention. ReLU linear attention is 3.3-4.5× faster than softmax attention with similar computation, thanks to removing hardware-unfriendly operations (e.g., softmax). Latency is measured on the Qualcomm Snapdragon 855 CPU with TensorFlow-Lite, batch size 1, and fp32.

Enable Global Receptive Field with ReLU Linear Attention. Given input  $x \in \mathbb{R}^{N \times f}$ , the generalized form of softmax attention can be written as:

$$O_{i} = \sum_{j=1}^{N} \frac{Sim(Q_{i}, K_{j})}{\sum_{j=1}^{N} Sim(Q_{i}, K_{j})} V_{j},$$

(2.1)

where  $Q = xW_Q$ ,  $K = xW_K$ ,  $V = xW_V$  and  $W_Q/W_K/W_V \in \mathbb{R}^{f \times d}$  is the learnable linear projection matrix.  $O_i$  represents the i-th row of matrix O.  $Sim(\cdot, \cdot)$  is the similarity function. When using the similarity function  $Sim(Q, K) = \exp(\frac{QK^T}{\sqrt{d}})$ , Eq. (2.1) becomes the original softmax attention [20].

Apart from  $\exp(\frac{QK^T}{\sqrt{d}})$ , we can use other similarity functions. In this work, we use ReLU linear attention [24] to achieve both the global receptive field and linear computational complexity. In ReLU linear attention, the similarity function is defined as

$$Sim(Q, K) = ReLU(Q)ReLU(K)^{T}.$$

(2.2)

With  $Sim(Q, K) = ReLU(Q)ReLU(K)^T$ , Eq. (2.1) can be rewritten as:

$$O_i = \sum_{j=1}^N \frac{\text{ReLU}(Q_i) \text{ReLU}(K_j)^T}{\sum_{j=1}^N \text{ReLU}(Q_i) \text{ReLU}(K_j)^T} V_j = \frac{\sum_{j=1}^N (\text{ReLU}(Q_i) \text{ReLU}(K_j)^T) V_j}{\text{ReLU}(Q_i) \sum_{j=1}^N \text{ReLU}(K_j)^T}.$$

Then, we can leverage the associative property of matrix multiplication to reduce the computational complexity and memory footprint from quadratic to linear without changing

Figure 2.5: Macro Architecture of EfficientViT. We adopt the standard backbone-head/encoder-decoder design. We insert our EfficientViT modules in Stages 3 and 4 in the backbone. Following the common practice, we feed the features from the last three stages (P2, P3, and P4) to the head. We use addition to fuse these features for simplicity and efficiency. We adopt a simple head design that consists of several MBConv blocks and output layers.

its functionality:

$$O_{i} = \frac{\sum_{j=1}^{N} \left[ \operatorname{ReLU}(Q_{i}) \operatorname{ReLU}(K_{j})^{T} \right] V_{j}}{\operatorname{ReLU}(Q_{i}) \sum_{j=1}^{N} \operatorname{ReLU}(K_{j})^{T}} = \frac{\sum_{j=1}^{N} \operatorname{ReLU}(Q_{i}) \left[ \left( \operatorname{ReLU}(K_{j})^{T} V_{j} \right) \right]}{\operatorname{ReLU}(Q_{i}) \sum_{j=1}^{N} \operatorname{ReLU}(K_{j})^{T}}$$

$$= \frac{\operatorname{ReLU}(Q_{i}) \left( \sum_{j=1}^{N} \operatorname{ReLU}(K_{j})^{T} V_{j} \right)}{\operatorname{ReLU}(Q_{i}) \left( \sum_{j=1}^{N} \operatorname{ReLU}(K_{j})^{T} \right)}. \tag{2.3}$$

As demonstrated in Eq. (2.3), we only need to compute  $(\sum_{j=1}^{N} \operatorname{ReLU}(K_j)^T V_j) \in \mathbb{R}^{d \times d}$  and  $(\sum_{j=1}^{N} \operatorname{ReLU}(K_j)^T) \in \mathbb{R}^{d \times 1}$  once, then can reuse them for each query, thereby only requires  $\mathcal{O}(N)$  computational cost and  $\mathcal{O}(N)$  memory.

Another key merit of ReLU linear attention is that it does not involve hardware-unfriendly operations like softmax, making it more efficient on hardware. For example, Figure 2.4 shows the latency comparison between softmax attention and ReLU linear attention. With similar computation, ReLU linear attention is significantly faster than softmax attention on the mobile CPU.

Address ReLU Linear Attention's Limitations. Although ReLU linear attention is superior to softmax attention in terms of computational complexity and hardware latency, ReLU linear attention has limitations. Figure 2.3 visualizes the attention maps of softmax attention and ReLU linear attention. Because of the lack of the non-linear similarity function, ReLU linear attention cannot generate concentrated attention maps, making it weak at capturing local information.

To mitigate its limitation, we propose to enhance ReLU linear attention with convolution. Specifically, we insert a depthwise convolution in each FFN layer. An overview of the resulting building block is illustrated in Figure 2.2 (left), where the ReLU linear attention captures context information and the FFN+DWConv captures local information.

Furthermore, we propose to aggregate the information from nearby Q/K/V tokens to get multi-scale tokens to enhance the multi-scale learning ability of ReLU linear attention. This information aggregation process is independent for each Q, K, and V in each head. We

only use small-kernel depthwise-separable convolutions [39] for information aggregation to avoid hurting hardware efficiency. In the practical implementation, independently executing these aggregation operations is inefficient on GPU. Therefore, we take advantage of the group convolution to reduce the number of total operations. Specifically, all DWConvs are fused into a single DWConv while all 1x1 Convs are combined into a single 1x1 group convolution (Figure 2.2 right) where the number of groups is  $3 \times \#$ heads and the number of channels in each group is d. After getting multi-scale tokens, we perform ReLU linear attention upon them to extract multi-scale global features. Finally, we concatenate the features along the head dimension and feed them to the final linear projection layer to fuse the features.

#### EfficientViT Architecture

We build a new family of vision transformer models based on the proposed multi-scale linear attention module. The core building block (denoted as 'EfficientViT Module') is illustrated in Figure 2.2 (left). The macro architecture of EfficientViT is demonstrated in Figure 2.5. We use the standard backbone-head/encoder-decoder architecture design.

- Backbone. The backbone of EfficientViT also follows the standard design, which consists of the input stem and four stages with gradually decreased feature map size and gradually increased channel number. We insert the EfficientViT module in Stages 3 and 4. For downsampling, we use an MBConv with stride 2.

- **Head.** P2, P3, and P4 denote the outputs of Stages 2, 3, and 4, forming a pyramid of feature maps. For simplicity and efficiency, we use 1x1 convolution and standard upsampling operation (e.g., bilinear/bicubic upsampling) to match their spatial and channel size and fuse them via addition. Since our backbone already has a strong context information extraction capacity, we adopt a simple head design that comprises several MBConv blocks and the output layers (i.e., prediction and upsample). In the experiments, we empirically find this simple head design is sufficient for achieving SOTA performances.

In addition to dense prediction, our model can be applied to other vision tasks, such as image classification, by combining the backbone with task-specific heads.

Following the same macro architecture, we design a series of models with different sizes to satisfy various efficiency constraints. We name these models EfficientViT-B0, EfficientViT-B1, EfficientViT-B2, and EfficientViT-B3, respectively. In addition, we designed the EfficientViT-L series for the cloud platforms. Detailed configurations of these models are provided in our official GitHub repository<sup>1</sup>.

## 2.1.4 Experiments

#### Setups

**Datasets.** We evaluate the effectiveness of EfficientViT on three representative high-resolution dense prediction tasks, including semantic segmentation, super-resolution, and Segment Anything.

$<sup>^1</sup>$ https://github.com/mit-han-lab/efficientvit

| Comp         | onents       | mIoU ↑ | Params ↓ | MACs J.         |

|--------------|--------------|--------|----------|-----------------|

| Multi-scale  | Global att.  |        |          | 111100 <b>V</b> |

|              |              | 68.1   | 0.7M     | 4.4G            |

| $\checkmark$ |              | 72.3   | 0.7M     | 4.4G            |

|              | $\checkmark$ | 72.2   | 0.7M     | 4.4G            |

| $\checkmark$ | $\checkmark$ | 74.5   | 0.7M     | 4.4G            |

Table 2.1: **Ablation Study.** The mIoU and MACs are measured on Cityscapes with 1024x2048 input resolution. We rescale the width of the models so that they have the same MACs. Multi-scale learning and the global receptive field are essential for obtaining good semantic segmentation performance.

For semantic segmentation, we use two popular benchmark datasets: Cityscapes [56] and ADE20K [57]. In addition, we evaluate EfficientViT under two settings for super-resolution: lightweight super-resolution (SR) and high-resolution SR. We train models on DIV2K [58] for lightweight SR and test on BSD100 [59]. For high-resolution SR, we train models on the first 3000 training images of FFHQ [60] and test on the first 500 validation images of FFHQ<sup>2</sup>.

Apart from dense prediction, we also study the effectiveness of EfficientViT for image classification using the ImageNet dataset [61].

Latency Measurement. We measure the mobile latency on Qualcomm Snapdragon 8Gen1 CPU with Tensorflow-Lite<sup>3</sup>, batch size 1 and fp32. We use TensorRT<sup>4</sup> and fp16 to measure the latency on edge GPU and cloud GPU. The data transfer time is included in the reported latency/throughput results.

Implementation Details. We implement our models using Pytorch [62] and train them on GPUs. We use the AdamW optimizer with cosine learning rate decay for training our models. For multi-scale linear attention, we use a two-branch design for the best trade-off between performance and efficiency, where 5x5 nearby tokens are aggregated to generate multi-scale tokens.

For semantic segmentation experiments, we use the mean Intersection over Union (mIoU) as our evaluation metric. The backbone is initialized with weights pretrained on ImageNet and the head is initialized randomly, following the common practice.

For super-resolution, we use PSNR and SSIM on the Y channel as the evaluation metrics, same as previous work [63]. The models are trained with random initialization.

#### **Ablation Study**

Effectiveness of EfficientViT Module. We conduct ablation study experiments on Cityscapes to study the effectiveness of two key design components of our EfficientViT

<sup>&</sup>lt;sup>2</sup>https://rb.gy/7je1a

<sup>&</sup>lt;sup>3</sup>https://www.tensorflow.org/lite

<sup>&</sup>lt;sup>4</sup>https://docs.nvidia.com/deeplearning/tensorrt/

| Models                  | Top1 Acc↑ | Top5 Acc↑ | Params ↓ | MACs ↓ | Later<br>Nano(bs1) | 0 ,                | Throughput ↑ A100 (image/s) |

|-------------------------|-----------|-----------|----------|--------|--------------------|--------------------|-----------------------------|

| CoAtNet-0 [51]          | 81.6      |           | 25M      | 4.2G   | 95.8ms             | 4.5ms              | 3011                        |

| ConvNeXt-T [52]         | 82.1      | _         | 29M      | 4.5G   | 87.9ms             | $3.8 \mathrm{ms}$  | 3303                        |

| EfficientViT-B2 (r256)  | 82.7      | 06.1      |          |        |                    |                    |                             |

| Efficient VII-B2 (F250) | 02.1      | 96.1      | 24M      | 2.1G   | $58.5 \mathrm{ms}$ | $2.8 \mathrm{ms}$  | 5325                        |

| Swin-B [53]             | 83.5      | -         | 88M      | 15G    | 240ms              | $6.0 \mathrm{ms}$  | 2236                        |

| CoAtNet-1 [51]          | 83.3      | -         | 42M      | 8.4G   | 171ms              | $8.3 \mathrm{ms}$  | 1512                        |

| ConvNeXt-S [52]         | 83.1      | -         | 50M      | 8.7G   | $146 \mathrm{ms}$  | $6.5 \mathrm{ms}$  | 2081                        |

| EfficientViT-B3 (r224)  | 83.5      | 96.4      | 49M      | 4.0G   | 101ms              | $4.4 \mathrm{ms}$  | 3797                        |

| CoAtNet-2 [51]          | 84.1      | -         | 75M      | 16G    | 254ms              | 10.3ms             | 1174                        |

| ConvNeXt-B [52]         | 83.8      | -         | 89M      | 15G    | 211ms              | $7.8 \mathrm{ms}$  | 1579                        |

| EfficientViT-B3 (r288)  | 84.2      | 96.7      | 49M      | 6.5G   | 141ms              | $5.6 \mathrm{ms}$  | 2372                        |

| CoAtNet-3 [51]          | 84.5      | _         | 168M     | 35G    | _                  | 15.4ms             | 642                         |

| ConvNeXt-L [52]         | 84.3      | -         | 198M     | 34G    | _                  | $11.5 \mathrm{ms}$ | 1032                        |

| EfficientNetV2-S [54]   | 83.9      | -         | 22M      | 8.8G   | _                  | $4.3 \mathrm{ms}$  | 2869                        |

| EfficientViT-L1 (r224)  | 84.5      | 96.9      | 53M      | 5.3G   | -                  | $2.6 \mathrm{ms}$  | 6207                        |

| EfficientNetV2-M [54]   | 85.2      | -         | 54M      | 25G    | _                  | 9.2ms              | 1160                        |

| FasterViT-4 [55]        | 85.4      | 97.3      | 425M     | 37G    | _                  | $13.0 \mathrm{ms}$ | 1382                        |

| EfficientViT-L2 (r288)  | 85.6      | 97.4      | 64M      | 11G    | -                  | $4.3 \mathrm{ms}$  | 3102                        |

| FasterViT-6 [55]        | 85.8      | 97.4      | 1360M    | 142G   | _                  | -                  | 594                         |

| EfficientNetV2-L [54]   | 85.7      | -         | 120M     | 53G    | _                  | -                  | 696                         |

| EfficientViT-L2 (r384)  | 86.0      | 97.5      | 64M      | 20G    | _                  | -                  | 1784                        |

Table 2.2: Backbone Performance on ImageNet Classification. 'r224' means the input resolution is 224x224. 'bs1' represents that the latency is measured with batch size 1.

module, i.e., multi-scale learning and global attention. To eliminate the impact of pretraining, we train all models from random initialization. In addition, we rescale the width of the models so that they have the same #MACs. The results are summarized in Table 2.1. We can see that removing either global attention or multi-scale learning will significantly hurt the performances. It shows that all of them are essential for achieving a better trade-off between performance and efficiency.

Backbone Performance on ImageNet. To understand the effectiveness of EfficientViT's backbone in image classification, we train our models on ImageNet following the standard training strategy. We summarize the results and compare our models with SOTA image classification models in Table 2.2.

Though EfficientViT is designed for high-resolution dense prediction, it achieves highly competitive performances on ImageNet classification. In particular, EfficientViT-L2-r384 obtains 86.0 top1 accuracy on ImageNet, providing +0.3 accuracy gain over EfficientNetV2-L and 2.6x speedup on A100 GPU.

#### Semantic Segmentation

Cityscapes. Table 2.3 reports the comparison between EfficientViT and SOTA semantic segmentation models on Cityscapes. EfficientViT achieves remarkable efficiency improvements over prior SOTA semantic segmentation models without sacrificing performances. Specifically,

| Models                                                           | mIoU ↑                       | Params ↓                 | MACs ↓                        | Later Nano(bs1) | ncy ↓<br>Orin(bs1)                        | Throughput ↑ A100(image/s)   |

|------------------------------------------------------------------|------------------------------|--------------------------|-------------------------------|-----------------|-------------------------------------------|------------------------------|

| DeepLabV3plus-Mbv2 [64]                                          | 75.2                         | 15M                      | 555G                          | 0.28s           | 83.5ms                                    | 102                          |

| EfficientViT-B0                                                  | 75.7                         | 0.7M                     | 4.4G                          |                 | <b>9.9ms</b>                              | <b>263</b>                   |

| SegFormer-B1 [19]                                                | 78.5                         | 14M                      | 244G                          | 5.6s            | 146ms                                     | 49                           |

| SegNeXt-T [21]                                                   | 79.8                         | 4.3M                     | 51G                           | 2.2s            | 93.2ms                                    | 95                           |

| EfficientViT-B1                                                  | 80.5                         | 4.8M                     | 25G                           | <b>0.82s</b>    | <b>24.3ms</b>                             | <b>175</b>                   |

| SegFormer-B3 [19]<br>SegNeXt-S [21]<br>EfficientViT-B2           | 81.7<br>81.3<br>82.1         | 47M<br>14M<br>15M        | 963G<br>125G<br>74G           | 3.4s<br>1.7s    | 407ms<br>127ms<br>46.5ms                  | 18<br>70<br><b>112</b>       |

| SegFormer-B5 [19] SegNeXt-B [21] EfficientViT-B3 EfficientViT-L1 | 82.4<br>82.6<br>83.0<br>82.7 | 85M<br>28M<br>40M<br>40M | 1460G<br>276G<br>179G<br>282G | -<br>-<br>-     | 638ms<br>228ms<br>81.8ms<br><b>45.9ms</b> | 12<br>41<br>70<br><b>122</b> |

| SegNeXt-L [21]                                                   | 83.2                         | 49M                      | 578G                          |                 | 374ms                                     | 26                           |

| EfficientViT-L2                                                  | 83.2                         | 53M                      | 396G                          |                 | <b>60.0ms</b>                             | <b>102</b>                   |

Table 2.3: Comparison with SOTA Semantic Segmentation Models on Cityscapes. The input resolution is 1024x2048 for all models. Models with similar mIoU are grouped for efficiency comparison.

compared with SegFormer, EfficientViT obtains up to 13x #MACs saving and up to 8.8x latency reduction on the edge GPU (Jetson AGX Orin) with higher mIoU. Compared with SegNeXt, EfficientViT provides up to 2.0x MACs reduction and 3.8x speedup on the edge GPU (Jetson AGX Orin) while maintaining higher mIoU. On A100 GPU, EfficientViT delivers up to 3.9x higher throughput than SegNeXt and 10.2x higher throughput than SegFormer while achieving the same or higher mIoU. Having similar computational cost, EfficientViT also yields significant performance gains over previous SOTA models. For example, EfficientViT-B3 delivers +4.5 mIoU gain over SegFormer-B1 with lower MACs.

In addition to the quantitative results, we visualize EfficientViT and the baseline models qualitatively on Cityscapes. The results are shown in Figure 2.6. We can find that EfficientViT can better recognize boundaries and small objects than the baseline models while achieving lower latency on GPU.

**ADE20K.** Table 2.4 summarizes the comparison between EfficientViT and SOTA semantic segmentation models on ADE20K. Like Cityscapes, we can see that EfficientViT also achieves significant efficiency improvements on ADE20K. For example, with +0.6 mIoU gain, EfficientViT-B1 provides 5.2x MACs reduction and up to 3.5x GPU latency reduction than SegFormer-B1. With +1.6 mIoU gain, EfficientViT-B2 requires 1.8x fewer computational costs and runs 2.4x faster on Jetson AGX Orin GPU than SegNeXt-S.