#### PARALLEL COMPUTATION: SYNCHRONIZATION, SCHEDULING, AND SCHEMES

by

#### JEFFREY MARTIN JAFFE

# B.S., Massachusetts Institute of Technology (1976)

# S.M., Massachusetts Institute of Technology (1977)

#### SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

#### DOCTOR OF PHILOSOPHY

#### at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

(AUGUST 1979)

# Signature redacted

Department of Electrical Engineering and Computer Science, August 10, 1979 Signature redacted

Certified by Supervisor e redacted Signat

Accepted by ..... Chairman, Department Committee

Archives MASSACHUSETTS INSTITUTE OF TECHNOLOGY DEC 28 1979

LIBRARIES

1

#### PARALLEL COMPUTATION: SYNCHRONIZATION, SCHEDULING, AND SCHEMES

by

#### JEFFREY MARTIN JAFFE

#### Submitted to the Department of Electrical Engineering and Computer Science on August 10, 1979 in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

#### ABSTRACT

There are two primary means of resource allocation in computer systems. There is the powerful mechanism of using a centralized resource manager that allocates the resources. An apparently weaker mechanism is for the asynchronous processes of the system to allocate resources with some type of message passing between themselves. This thesis provides a unifying treatment of these two methods. It is shown that a managed system may be simulated by the processes. As a corollary, a wide variety of synchronization algorithms may be accomplished without a manager.

The simulation works correctly even in an environment with unreliabilities. Processes may die in an undetectable manner and the memory of the system may be faulty. Thus our general simulation provides the first known algorithm for synchronizing dying processes in a faulty memory environment.

Scheduling jobs on processors of different capabilities is studied. Algorithms are presented for two machine environments that have better performance than previously studied algorithms. These environments are processors of uniformly different speeds with partially ordered tasks and unrelated processors with independent tasks. In addition, the class of all preemptive schedules for uniform processor systems are studied. These schedules are shown to be more effective than previous analyses.

Scheduling jobs on functionally dedicated processors is introduced. Algorithms are presented for scheduling jobs on such processors, both in the case that the processors are equally fast and in the case that they are of different speeds.

The expressive power of the data flow schemes of Dennis is evaluated. It is shown that data flow schemes have the power to express an arbitrary determinate functional. The proof involves a demonstration that "restricted data flow schemes" can simulate Turing Machines. This provides a new, simple basis for computability.

THESIS SUPERVISOR: Albert R. Meyer TITLE: Professor of Electrical Engineering and Computer Science

### Keywords

Chapter 2:

distributed control fair mutual exclusion fault tolerant computing mutual exclusion process systems resource allocation resource manager simulation stable state sychronization unreliable processes

Chapter 3:

independent tasks list schedules maximal usage schedules nonpreemptive scheduling partially ordered tasks preemptive scheduling scheduling task systems typed task systems uniform processor system unrelated processors worst case performance bounds

Chapter 4:

computability data flow schemes effective functionals r.e. program schemes Turing machines

#### Acknowledgements

During my three years as a graduate student the primary source of direction has been provided by my thesis supervisor Albert Meyer. He has suggested exciting research directions to pursue, encouraged me to simplify and clarify my ideas, and provided inspiring technical contributions. Most importantly, he has unselfishly devoted an enormous amount of time to the development of the concepts in this thesis and to the presentation of the results.

My two thesis readers are to be credited for sparking my interest in the general topics covered in this thesis. Ron Rivest deserves primary credit for training me in the techniques of algorithm design and analysis and giving me much feedback on the presentation of the thesis. The data flow machine project of Jack Dennis helped develop my interest in parallel computation.

There are many others that have contributed to my research by providing new insights or working together with me on some of the technical results. While I cannot begin to thank them all for the various levels of help they have provided I would like to single out those who have made the most outstanding contributions: A. Baratz, E. Davis, I. Greif, D. Harel, E. Jaffe, D. Kessler, A. LaFaugh, E. Lloyd, M. Loui, C. Papadimitriou, V. Pratt, M. Rabin, A. Shamir, and G. Stark.

Since no research can be done in a vaccuum, I must thank all of those friends and family whose kinship and support are necessary ingredients of a research effort. Most importantly I must express my eternal gratitude to my wife, Esther for all of her help. It is a rare blessing to be close to someone that provides not only the necessary love and moral support at home, but also a vast reservoir of technical assistance in my work.

This thesis was prepared with the support of a National Science Foundation graduate fellowship, and National Science Foundation grant no. MCS77-19754.

### Table of Contents.

.

.

| Abstract<br>Keywords<br>Acknowledgements<br>Table of Contents<br>Index of Theorems and informal description of content<br>Index of Lemmas<br>Index of Equations<br>Index of Figures and Tables        | 2<br>3<br>4<br>5<br>7<br>9<br>10<br>11 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| <ol> <li>Introduction</li> <li>1.1 Major goals and accomplishments of thesis</li> <li>1.2 Reasons for parallel computation</li> <li>1.3 Some problems associated with parallel computation</li> </ol> | 12<br>12<br>15<br>19                   |

| 2. Synchronization                                                                                                                                                                                    | 26<br>26<br>26                         |

| motivation                                                                                                                                                                                            | 30<br>34                               |

| 2.2.1 Process systems and the definition of simulation                                                                                                                                                | 34                                     |

| 2.2.2 Properties of simulation                                                                                                                                                                        | 41                                     |

| 2.2.3 Process systems with unreliable memory<br>2.2.4 Managed system of processes and the main                                                                                                        | 45                                     |

| results of Chapter 2                                                                                                                                                                                  | 52<br>56                               |

| 2.3 An Example                                                                                                                                                                                        | 50<br>59                               |

| 2.4 Cooperating system of n simulators<br>2.4.1 Overview of the system                                                                                                                                | 59                                     |

| 2.4.2 Memory of the cooperating system                                                                                                                                                                | 64                                     |

| 2.4.3 State transitions of the first $n$ processes<br>2.4.4 Simulation of the RM (state transitions of the                                                                                            | 71                                     |

|                                                                                                                                                                                                       | 74                                     |

| 2.5 Proof of Theorem 2.1                                                                                                                                                                              | 81                                     |

| 2.6 Discussion of unreliability properties                                                                                                                                                            | 104                                    |

| 2.7 Open problems and further work                                                                                                                                                                    | 109                                    |

| 3. Scheduling Theory                                                                                                                                                                                  | 111                                    |

| 3.1 Introduction                                                                                                                                                                                      | 111                                    |

| 3.2 Scheduling tasks on processors of uniformly                                                                                                                                                       |                                        |

| different speeds                                                                                                                                                                                      | 119                                    |

| 3.2.1 Basic definitions and models                                                                                                                                                                    | 119                                    |

| 3.2.2 Nonpreemptive scheduling of tasks on                                                                                                                                                            |                                        |

| uniform processors                                                                                                                                                                                    | 123                                    |

| 3.2.3 Preemptive scheduling of tasks on uniform                                                                                                                                                       | 1 4 7                                  |

| processors                                                                                                                                                                                            | 143<br>159                             |

| 3. 3. Nonpreemptive scheduling of independent tasks on                                                                                                                                                | 133                                    |

| unrelated processors                                                                                                                                                                                  | 162                                    |

| 3.4 Scheduling tasks on processors of different types                                                                                                                                                 | 185                                    |

|     |                     | 3.4.1 Basic definitions and models                                                 | 185 |

|-----|---------------------|------------------------------------------------------------------------------------|-----|

|     |                     | 3.4.2 Nonpreemptive scheduling of tasks on<br>equally fast processors of different |     |

|     |                     | types                                                                              | 188 |

|     |                     | 3.4.3 Nonpreemptive scheduling of tasks on                                         | 100 |

|     |                     | processors of different types and                                                  |     |

|     |                     | different speeds                                                                   | 196 |

|     |                     | 3.4.4 Maximal usage preemptive scheduling of                                       | 150 |

|     |                     | tasks on processors of different types                                             |     |

|     |                     | and different speeds                                                               | 214 |

|     | 3.5                 | Open problems and further work                                                     | 216 |

| 4.  | Schemes             | • • • • • • • • • • • • • • • • • • • •                                            | 219 |

|     | 4.1                 | Introduction                                                                       | 219 |

|     | 4.2                 | Syntax and semantics of schemes                                                    | 222 |

|     |                     | Programming techniques                                                             | 228 |

|     | 4.4                 | Simulating Turing Machine computations with                                        |     |

|     |                     | restricted data flow schemes                                                       | 235 |

|     | 4.5                 | Simulating arbitrary r.e. program schemes with                                     |     |

|     |                     | data flow schemes                                                                  | 243 |

|     | 4,6                 | Conclusion and future work                                                         | 255 |

| Rei | ferences            |                                                                                    | 256 |

|     | ographical          |                                                                                    | 264 |

|     | - 0 - " " " " " " " | · ·····                                                                            | ~~~ |

. .

•

.

## Index of Theorems and informal description of content

| Theorem | 2.1  | Cooperating systems simulate managed systems                                                                         | 54  |

|---------|------|----------------------------------------------------------------------------------------------------------------------|-----|

| Theorem | 2. 2 | Every history for a cooperating system matches<br>some history for the corresponding managed<br>system               | 97  |

| Theorem | 2.3  | Managed systems may be partially simulated by systems with n processes                                               | 101 |

| Theorem | 2.4  | Fair mutual exclusion may be accomplished even with dying processes and unreliable memory                            | 101 |

| Theorem | 2.5  | Cooperating systems without errors simulate<br>managed systems                                                       | 102 |

| Theorem | 3.1  | List schedules on the fastest <i>i</i> processors are at most $1 + 2\sqrt{m}$ times worse than optimal               |     |

|         |      | where m is the number of processors                                                                                  | 130 |

| Theorem | 3.2  | List schedules on the fastest <i>i</i> processors are at<br>most $\sqrt{m} + O(m^{1/4})$ times worse<br>than optimal | 131 |

| Theorem | 3.3  | Any preemptive schedule may be transformed into a maximal usage preemptive schedule in polynomial time               | 152 |

| Theorem | 3.4  | A bound on maximal usage preemptive schedules related to Theorem 3.2                                                 | 153 |

| Theorem | 3.5  | Maximal usage preemptive schedules are at most $\sqrt{m}$ + (1/2) times worse than optimal                           | 157 |

| Theorem | 3.6  | An algorithm for independent tasks on unrelated<br>processors is at most 2.5√m times worse                           |     |

|         |      | than optimal                                                                                                         | 176 |

| Theorem | 3.7  | An algorithm which is similar to the one analyzed                                                                    |     |

|         |      | in Theorem 3.6 is at most 2.41√m times<br>worse than optimal                                                         | 178 |

| Theorem | 3.8  | An algorithm which is similar to but slower than the                                                                 |     |

|         |      | algorithm analyzed in Theorem 3.6 is at most $1.5\sqrt{m}$ times worse than optimal                                  | 180 |

| Theorem 3 | 3.9  | List schedules for typed task systems are at most k+1<br>times worse than optimal where k is the number of<br>types                                                               | 188 |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Theorem 3 | 3.10 | List schedules for typed task systems on processors of<br>different speeds are at most k plus the maximum<br>ratio of speeds of processors of the same type worse<br>than optimal | 200 |

| Theorem 3 | 3.11 | A speed independent bound for list schedules on a subset of processors for typed task systems                                                                                     | 203 |

| Theorem   | 3.12 | A different speed independent bound than that of Theorem 3.11                                                                                                                     | 204 |

| Theorem   | 3.13 | A bound on maximal usage preemptive schedules for<br>processors of different types related to Theorems 3.11<br>and 3.12                                                           | 215 |

| Theorem   | 4.1  | Turing Machines may be simulated by restricted data flow schemes                                                                                                                  | 237 |

| Theorem   | 4.2  | R.e. program schemes are equivalent to data flow schemes                                                                                                                          | 247 |

.

.

.

.

### Index of Lemmas

| Lemma | 2.1  |                     |        | <br> |         | <br> |       |       | <br> |     |

|-------|------|---------------------|--------|------|---------|------|-------|-------|------|-----|

| Lemma | 2.2  |                     |        | <br> |         | <br> |       |       | <br> |     |

| Lemma | 2.3  |                     |        | <br> |         | <br> |       |       | <br> | • • |

| Lemma | 2.4  | (progress lemma)    |        | <br> |         | <br> |       | • • • | <br> |     |

| Lemma | 2.5  |                     |        | <br> |         | <br> |       |       | <br> |     |

| Lemma | 2.6  |                     |        | <br> |         | <br> |       |       | <br> | • • |

| Lemma | 3.1  |                     |        | <br> |         | <br> |       |       | <br> |     |

| Lemma | 3.2  |                     |        | <br> |         | <br> |       |       | <br> | •   |

| Lemma | 3.3  |                     |        | <br> |         | <br> |       | • • • | <br> | •   |

| Lemma | 3.4  |                     |        | <br> |         | <br> |       |       | <br> | •   |

| Lemma | 3.5  |                     |        | <br> |         | <br> |       |       | <br> | •   |

| Lemma | 3.6  |                     |        | <br> |         | <br> |       | • • • | <br> |     |

| Lemma | 3.7  |                     |        | <br> |         | <br> |       |       | <br> | •   |

| Lemma | 3.8  |                     |        | <br> | • • • • | <br> |       |       | <br> |     |

| Lemma | 3.9  |                     |        | <br> |         | <br> |       | • • • | <br> |     |

| Lemna | 3.10 |                     |        | <br> |         | <br> | • • • | • • • | <br> |     |

| Lemma | 3.11 |                     |        | <br> |         | <br> |       |       | <br> | •   |

| Lemma | 3.12 |                     |        | <br> |         | <br> |       | • • • | <br> | •   |

| Lemma | 3.13 |                     |        | <br> |         | <br> |       |       | <br> | •   |

| Lemma | 3.14 |                     |        | <br> |         | <br> |       | • • • | <br> | •   |

| Lemma | 4.1  | (finite translation | lemma) |      |         | <br> |       |       | <br> |     |

:

## Index of Equations

.

. .

| Equation | (1)  |                                         | 127 |

|----------|------|-----------------------------------------|-----|

| Equation | (2)  |                                         | 128 |

| Equation | (3)  |                                         | 128 |

| Equation | (4)  |                                         | 131 |

| Equation | (5)  |                                         | 131 |

| Equation | (6)  | * * * * * * * * * * * * * * * * * * * * | 134 |

| Equation | (7)  |                                         | 135 |

| Equation | (8)  |                                         | 155 |

| Equation | (9)  |                                         | 156 |

| Equation | (10) |                                         | 156 |

| Equation | (11) |                                         | 156 |

| Equation | (12) |                                         | 156 |

| Equation | (13) |                                         | 173 |

| Equation | (14) |                                         | 173 |

| Equation | (15) |                                         | 173 |

| Equation | (16) |                                         | 174 |

| Equation | (17) |                                         | 174 |

| Equation | (18) |                                         | 174 |

| Equation | (19) |                                         | 174 |

| Equation | (20) |                                         | 175 |

| Equation | (21) |                                         | 175 |

| Equation | (22) |                                         | 175 |

| Equation | (23) | • • • • • • • • • • • • • • • • • • • • | 176 |

| Equation | (24) |                                         | 199 |

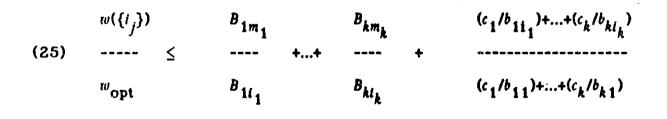

| Equation | (25) |                                         | 199 |

| Equation | (26) |                                         | 200 |

| Equation | (27) |                                         | 201 |

| Equation | (28) |                                         | 201 |

| Equation | (29) |                                         | 202 |

| Equation | (30) |                                         | 202 |

| Equation | (31) |                                         | 202 |

| Equation | (32) |                                         | 204 |

| Equation | (33) |                                         | 204 |

|          |      |                                         |     |

•

# Index of Figures and Tables

.

.

| Table 2 | 2.1      |         |         |       |       |       |     |       | • • |       | •••   | • • | • • • |       |     | • • |     | •••   | ••  | ••  | • • |     |     |   | 66  |

|---------|----------|---------|---------|-------|-------|-------|-----|-------|-----|-------|-------|-----|-------|-------|-----|-----|-----|-------|-----|-----|-----|-----|-----|---|-----|

| Table 2 | 2.2      |         |         |       |       |       | • • |       | • • |       |       |     |       |       | ••  | • • |     | • • • |     |     | • • | • • |     | • | 67  |

| Table 3 | 3.1      |         |         | • . • |       |       | ••  |       |     |       |       | ••• |       |       |     | ••  |     |       | • • |     | ••  |     |     | • | 136 |

| Table 3 | 3.2      | • • •   |         |       | •••   |       | ••  | • • • | ••  | • • • | ••    | ••• | • • • | •••   | ••  | ••  | ••  | •••   | ••  | • • | • • | ••  | ••  | • | 137 |

|         |          |         |         |       |       |       |     |       |     |       |       |     |       |       |     |     |     |       |     |     |     |     |     |   |     |

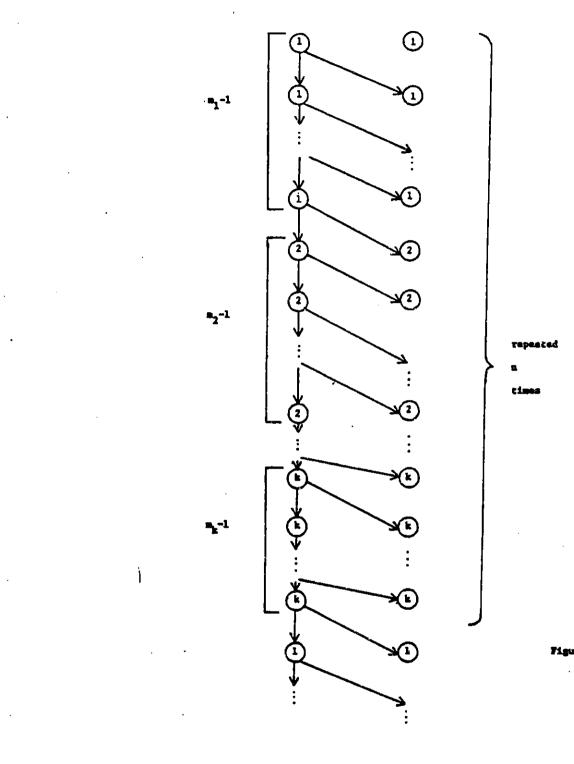

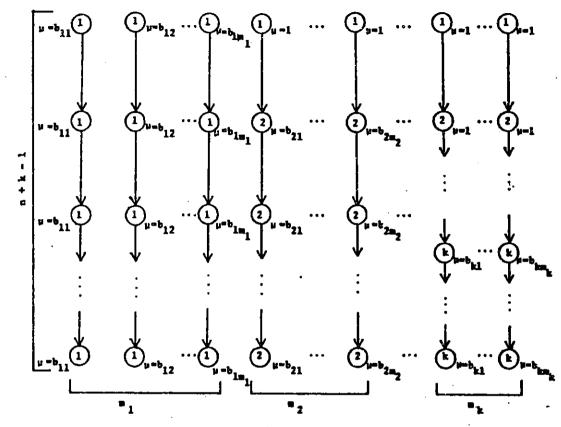

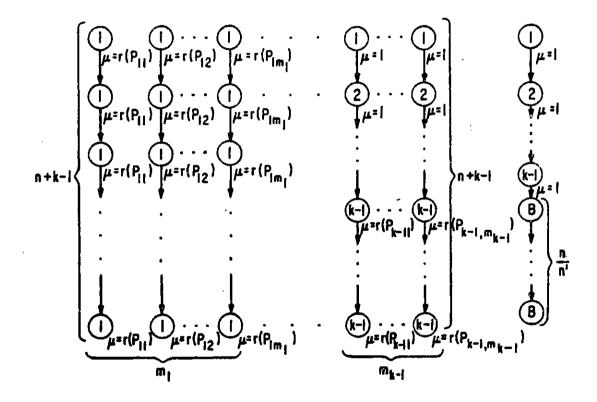

| Figure  |          |         |         |       |       |       | • • | • • • | • • | • • • |       | ••  |       |       |     | • • |     | ••    | • • |     | ••  |     | ••  | • | 140 |

| Figure  | 3.4.1    |         |         |       |       |       | • • | • • • | • • |       |       | • • | • • • |       | ••  | • • | • • |       |     | • • | ••  | • • | • • | • | 192 |

| Figure  | 3.4.2    |         |         |       |       |       | ••  |       | ••  |       |       |     |       |       |     | ••  | ••  | ••    |     | ••  | ••  | ••  |     | • | 207 |

| Figure  | 3.4.3    |         |         |       |       |       |     |       |     |       |       |     |       |       | ••  | • • |     | • • • |     |     |     |     |     |   | 209 |

| Figure  | 3.4.4    |         |         |       |       |       | ••  |       | ••  |       |       |     |       |       |     |     |     |       |     |     |     |     |     |   | 212 |

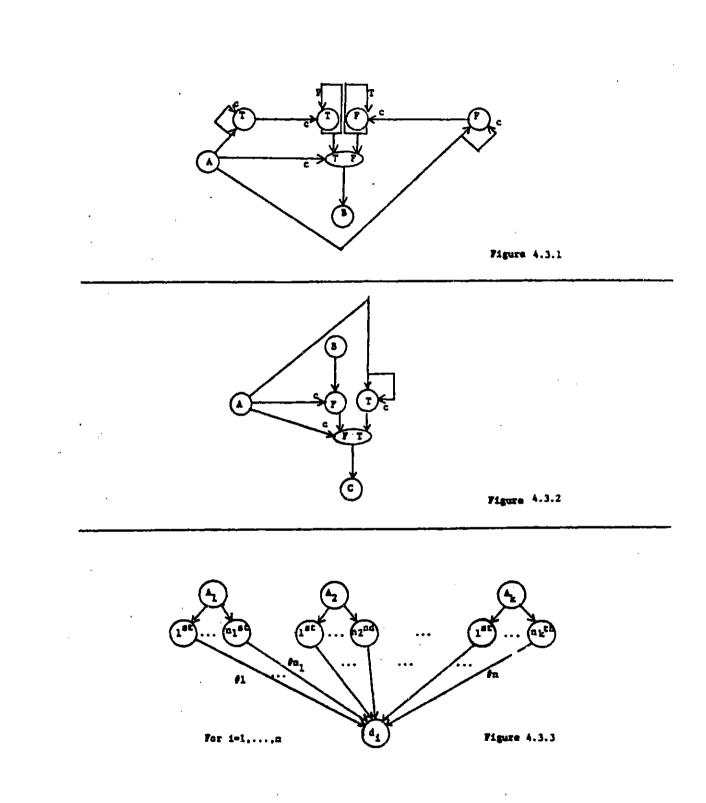

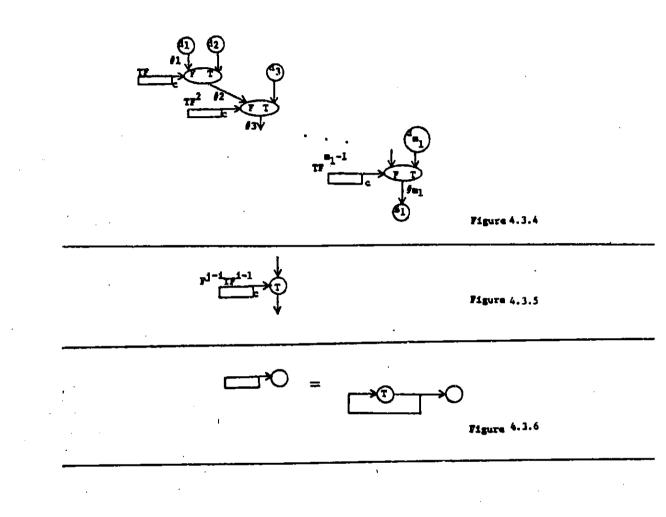

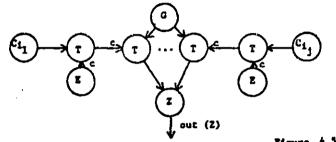

| Figure  | 4.3.1    |         |         |       |       |       |     |       |     |       |       |     |       |       |     |     | ••  |       |     |     |     |     |     |   | 229 |

| Figure  |          |         |         |       |       |       |     |       |     |       |       |     |       |       |     |     |     |       |     |     |     |     |     |   | 229 |

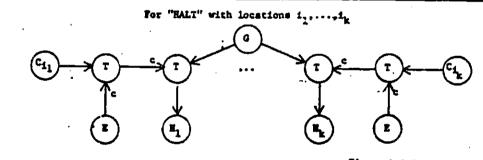

| Figure  |          |         |         |       |       |       |     |       |     |       |       | -   |       |       |     |     |     |       |     |     |     |     |     |   | 231 |

| Figure  |          |         |         |       |       | •     |     |       | • - | • - • |       | • - | • • • |       |     |     |     | • •   | • • |     | • • |     |     | - | 231 |

| Figure  |          |         |         |       |       |       |     |       |     |       |       |     |       |       | -   |     | -   |       |     |     |     | -   |     |   | 231 |

| Figure  |          | •••     |         |       |       |       |     |       |     |       |       |     |       |       |     |     |     |       |     |     |     |     |     |   | 231 |

| Figure  |          |         |         |       |       |       |     |       |     |       |       |     |       |       |     |     |     |       |     |     | -   |     |     | - | 231 |

| •       |          | • • •   |         |       |       | -     | -   |       |     |       | -     | -   |       |       | -   |     |     |       |     |     |     | -   |     |   |     |

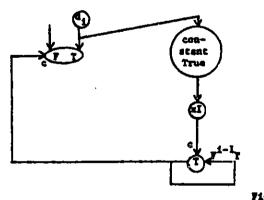

| Figure  |          | • • •   |         |       |       |       |     |       | •   |       |       |     |       |       |     |     |     |       |     |     | • - | •   |     |   | 234 |

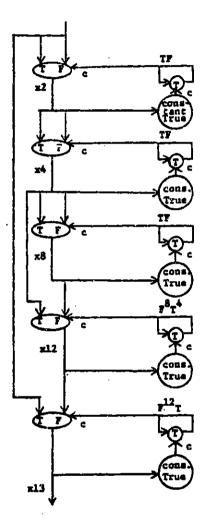

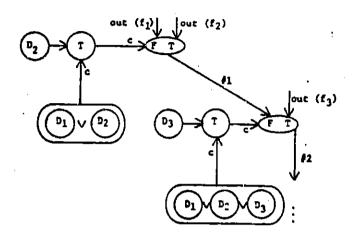

| Figure  |          | •••     |         |       | -     |       |     |       |     |       |       |     |       |       |     |     |     |       |     |     |     |     |     |   | 242 |

| Figure  |          | • • •   |         |       |       |       |     |       |     |       |       |     |       |       |     |     |     |       |     |     |     |     |     |   | 242 |

| Figure  |          | • • •   |         | •••   | • • • | • • • | • • |       | • • | • • • | • • • | • • | • • • | • • • | • • | ••  | • • | ••    | • • | • • | • • | • • | • • | • | 242 |

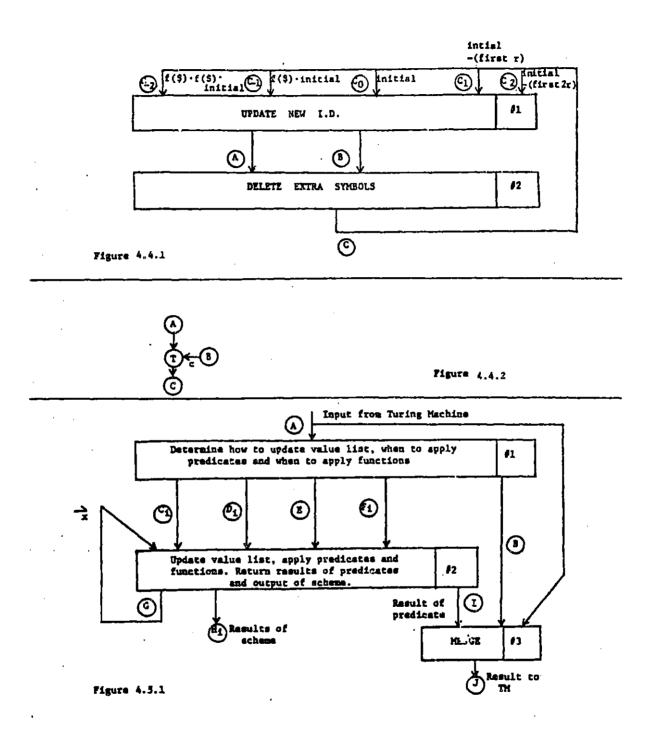

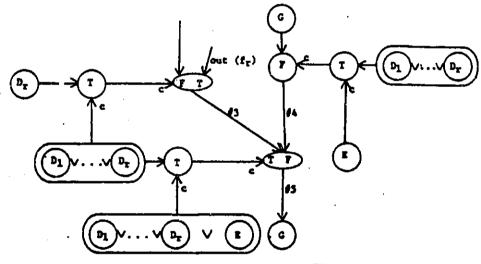

| 0       | 4.5.2a,b |         | • • • • | • • • | ••    | • • • | ••  | • • • | ••  | • • • |       | ••• |       |       | ••  |     | • • | ••    | • • | • • | ••  | • • | • • | • | 250 |

| Figure  | 4.5.2c   |         |         |       |       |       | • • |       | • • |       |       |     | • • • |       | ••  | • • | ••  | ••    | • • | • • |     | ••  | • • | • | 252 |

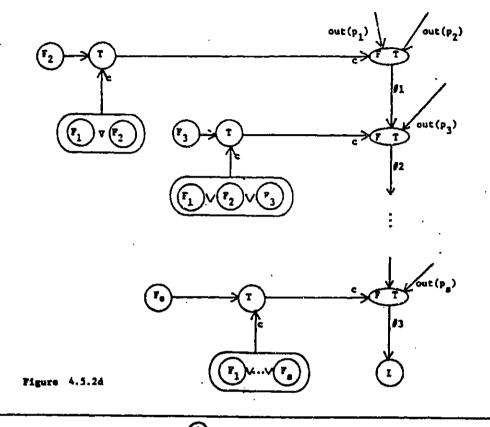

| Figure  | 4.5.2d   |         |         |       |       |       | ••  |       | ••  | • • • |       |     |       |       | ••  |     | • • | ••    |     | • • |     |     | • • | • | 254 |

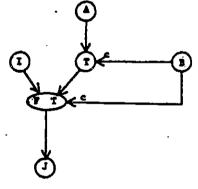

| Figure  | 4.5.3    | • • • • |         |       | • • • |       | ••  | • • • | ••  | • • • | ••    | • • | • • • |       | ••  | • • | • • | • • • |     | ••  | • • | ••  | ••  | • | 254 |

.

.

#### 1. Introduction

#### 1.1. Major goals and accomplishments of thesis

There are three major topics covered in this thesis. They are resource allocation or synchronization of parallel processes, job scheduling, and schemes. In the introduction we give a very brief description of the main contributions of this thesis. We then give an overview of the usages of parallel compution and describe some problems that designers of parallel systems are confronted with. More extensive introductions to the three main topics of the thesis may be found in Section 2.1 (synchronization), Section 3.1 (scheduling), and Section 4.1 (schemes).

#### 1.1.1 Synchronization

There are two primary means of resource allocation in computer systems. There is the powerful mechanism of using a centralized resource manager that allocates the resources. Managed systems are usually easy to design and easy to prove to be correct. An apparently weaker mechanism is for the asynchronous processes of the system to allocate resources with some type of message passing between themselves. This method has the advantage of not needing a manager to "poll" the processes even at times that no resource is needed. This thesis provides a unifying treatment of these two methods. It is shown that a managed system may be simulated by the processes. As a corollary, a wide variety of synchronization algorithms may be easily designed without a manager.

The simulation works correctly even in an environment with unreliabilities. Processes may die in an undetectable manner and the memory of the system may be faulty. Thus our general simulation provides the first known algorithm for synchronizing dying processes in a faulty memory environment.

. -

#### 1.1.2 Scheduling

Scheduling jobs on processors of different speeds is studied. Algorithms are presented for two machine environments that have better performance than previously studied algorithms. These environments are processors of different speeds with partially ordered tasks and unrelated processors with independent tasks. These environments will be defined precisely in Chapter 3. In addition, the class of all preemptive schedules for uniform processor systems are studied. These schedules are shown to be more effective than previous analyses.

Scheduling jobs on functionally dedicated processors is introduced. Algorithms are presented for scheduling jobs on such processors, both in the case that the processors are equally fast and in the case that they are of different speeds.

#### 1.1.3 Schemes

The expressive power of the data flow schemes of Dennis is evaluated. It is shown that data flow schemes have the power to express an arbitrary determinate functional. The proof involves a demonstration that "restricted data flow schemes" can simulate Turing Machines. This provides a new, simple basis for computability.

We proceed with an overview of parallel computation in general. Section 1.2 outlines the basic types of machine environments that we consider under the title of parallel computation. Section 1.3 discusses the three topics of the thesis in somewhat greater detail. We discuss the relevance of these issues in different parallel environments. We also explore the

.

.

.

#### **1.2 Reasons for Parallel Computation**

We identify three different sources of interest in parallel computation: "problem oriented", "machine oriented", and "community oriented" (distributed).

#### **1.2.1** Problem Oriented Parallel Computation

Part of the original interest in parallel computation arose from time-consuming, "number crunching" programs that could not be executed within a reasonable amount of time on a single conventional machine. Many of these programs solve extremely important problems such as partial differential equations and linear programming. In order to solve these important problems one is often willing to buy a large amount of computing resources if this could only help obtain the solution. In certain applications (e.g. FFT) special purpose devices have been built to solve the problem. However, for other less pervasive applications, using more than one general purpose computer is often the cost-effective means of solution. By executing different portions of a program concurrently one substantially reduces the finishing time of a program.

This effort - to understand how to divide programs into different portions capable of being executed concurrently - promises to continue despite further advances in hardware technology. While hardware advances consistently extend the frontier of "which programs may be finished quickly", it seems unlikely that all important problems will ever be solvable quickly. As soon as improved technology and reduced hardware costs permit us to efficiently solve yesterday's intractable problems, a new set of intractable problems invariably appears on the horizon. Indeed, a large class of important decision problems are NP-complete. NP-complete problems are widely believed to require an

•••••

exponential amount of time for their solution [20] in terms of the size of the particular problem instance (i.e., for instances of size n, the time required is  $2^n$ ). In addition, there is a class of somewhat less important problems which provably require exponential time. For these problems, even moderately sized instances are beyond the reach of today's technology, and larger instances which arise in practice, will surely continue to be difficult.

It is interesting to note that the NP-complete problems lend themselves to parallel techniques; they can be solved quickly if one can explore many possible situations in parallel. While this use of parallel computation does not circumvent the apparent exponential growth in the time required for solving the NP-complete problems, it does permit one to solve larger instances than would be otherwise possible.

#### **1.2.2 Machine Oriented Parallel Computation**

Often the motivation for introducing parallelism into a system is the "dual" of problem oriented parallel computation. In a problem oriented environment no individual resource is sufficiently powerful to attack the problem at hand. The "dual" of this is that available resources are overly powerful for any single problem. It is then advantageous to divide the use of the powerful computer among many problems.

This situation has led to a successful series of multiprocessing and multiprogramming computer environments. Many users simultaneously execute different jobs, while a central controller allocates processing time and other machine resources. Typically, some of the users are in an interactive mode; i.e. the inputs to the program are inserted by the users during program execution (e.g., editing programs). This slow input process allows the system

to serve many users at once; each user's program needs only a small amount of CPU time per unit real time. Even programs that are not executed interactively do not utilize all of the machine resources simultaneously. Thus, if one program issues numerous Input/Output instructions, other programs may use the main processor and memory.

There is also some overlap between problem oriented and machine oriented environments. Consider a given problem oriented environment with a large cost overhead due to the purchase of extensive computing resources. It may be useful to amortize that cost by permitting low priority computing to take place in the "background" - to be executed if system resources would otherwise be unused.

#### **1.2.3 Community Oriented Parallel Computation**

Community oriented parallel computation is a relatively new development. In a computer network, a large number of computers are separated by physical distances and linked by communications lines. This interconnection scheme has become practical for a large number of applications due to the astonishing decrease in costs for small computers. A network provides a powerful, flexibile computing system to a large community of users. The dedication of a computer to a small number of local users provides them with computational power free from delays that are inherent with processor sharing in large multiprocessor systems. On the other hand, each user in the system still has access to a wide variety of system resources. In particular, each user has access to any resource located anywhere in the network of computers. Thus (for example), the communications network may enable the user to copy a "mailing list file" from one remote location, process it locally to removed an

undesirable portion of the list, and have the output produced at a different location; perhaps the single network location with a "mailing label" output device.

Another advantage of distribution is that most of the system remains operational if some of the local computers "crash" and have to be withdrawn from the system. This contrasts with the classical computer model that relies heavily on the reliability of the single central processor.

To recapitulate, the three motivating forces for parallel computation that are mentioned here have a number of common high-level goals. The first is to bring more processing power to bear on a particular environment. In a problem oriented environment, this occurs with the use of faster or specialized processors after one completes the programming task of parallelizing the programs. The multiprogrammed environment acquires more *real* computational power by insuring that existing power is not wasted. A distributed environment enables users to use dedicated machines without giving up the capability of a varied resource system.

A common goal of machine and community oriented computation is to attain a wider distribution of computer resources. Multiprocessor systems give each user relatively equal access. Distributed systems provide easier access to users located near the resources.

#### **1.3 Some Problems Associated with Parallel Computation**

#### 1.3.1 Synchronization

One of the more challenging problems in the field of parallel computation is in trying to program moderately difficult algorithms in a distributed manner. That is, trying to establish protocols between different centers of computational power that enable the centers to cooperate on the solution to a particular task. A center of computational power may be a node in a network in a distributed system, or a process in a multiprocessor system. Decentralized algorithms are advantageous as they enable computational tasks to be finished quickly. Specifically, if the distribution is done properly, the completion of the algorithm may not be hampered by a center of computational power which is slow or busy doing other work. The large amount of service work done is one of the inefficient aspects of a central controller.

Chapter 2 of this thesis is devoted to such a "distributed control" program. What is more imortant than the fact that this is a distributed control problem is that it provides a new solution to a practical problem that has been widely studied (e.g., [15,17,37,53]). The problem is to synchronize resource assignment in a multiprocess system. Even in a uniprocessor machine it has long been felt that this should be solved without the central controller [15]. Since the central controller is busy with other time consuming tasks, it is helpful to remove some responsibilities from its domain. There is no reason for the controller to continually poll the users trying to establish if any resource requests have been made.

Some other solutions to this problem in distributed control may be found in [15,16,34,35]. The solution presented here takes hardware reliability into account. The solution works even if there is a failure of any one memory

unit. Also, slow processes do not degrade the efficiency of our solution. A slow process is modelled by a process that stops entirely. The solution continues to work even if some of the processes stop entirely and thus does not wait for a slow process (since a slow process will appear to have stopped entirely). Of course, there is no way of speeding up the system if a slow process is using the resource. In summary, there is a dual fault protection memory may be unreliable, and processes may die (i.e. be slow) without any visible signs of death.

The main result is that we show that in the face of unreliability, the processes may simulate a manager of resources. Since it is a general simulation, it serves as a paradigm for other issues that arise in parallel computation. First, there is a general need to develop techniques of programming in a distributed manner. Our techniques should be generally applicable as they are not *ad hoc* mechanisms that solve only the specific problem of devising a fair synchronization protocol. Rather the techniques are mechanisms which enable the processes to cooperate to simulate the actions of a central controller, even if there is no controller, and memory and processes are unreliable. We note, however, that the solution itself is not quite usable to assign resources in distributed environments as it uses global read/write variables.

There is one final arena in which we believe that our protocols provide an excellent pedagogical model. This is the area of parallel program verification. To prove a complicated parallel program correct is quite difficult, as one must consider all possible interleavings of when which processes executed their instructions. There have been a number of suggested proof techniques in the literature.

The proof that our protocols simulate a central controller uses a "stable state" technique. At certain times, the current states of the processes and values in memory provide a clue as to what the system behavior will be in the immediate future. These times are defined to be the stable states. The constraints on the system at stabilization guarantee that the system will again become stable. Also, these constraints enable us to predict the behavior until the next stabilization.

#### **1.3.2** Scheduling

One of the classical problems in the design of parallel systems is the scheduling of a large number of concurrently executable tasks on a fixed set of processors. The order of execution is an important consideration if one wants the jobs to be completed quickly [24]. A poor scheduling policy squanders the potential benefit of a parallel system. The scheduling problem arises in all three machine environments described in Section 1.1.

This problem has usually been attacked under the assumption that all of the machine's processors are identical [23]. This is a reasonable assumption in certain systems, and it is relatively easy to develop fast, near optimal algorithms in such a system.

In Chapter 3, scheduling algorithms are developed for complex machine environments with processors of different speeds. This problem has been considered in [28,30,43], but the known algorithms are not nearly as effective as in the identical processor case. The assumption that a system has processors of different speeds is widely applicable. For example, in problem oriented parallel computation a computer facility may have different machines with different capabilities. In a multiprocessor system, it is conceivable

(although perhaps not likely) that the computer has processors of different speeds. In a distributed system it is likely that the processors of the system be different. Also, the time required by a specific job on a specific processor (in a distributed system) must include some measure of communication cost. Thus identical processors are viewed as nonidentical from the system's point of view.

Sections 3.2.2 and 3.2.3 analyze the situation where the relative speed of any pair of processors is fixed (uniform) irrespective of the task to be executed. Both preemptive and nonpreemptive algorithms are presented for the scheduling of a partially ordered set of jobs on uniform processors. In both cases, approximation algorithms are developed whose worst case performance is better than known algorithms.

While the machine model with uniform processors is somewhat amenable to analytic, worst case analysis, the non-uniform (unrelated) case is much harder to analyze. The unrelated case models machines of specialized capabilities. In that environment the relative speeds of the processors depend on the task. This type of specialization may be used to model distributed computing, for example, even if the local processors are identical. As mentioned above, the time requirement of a task on a machine, *M*, depends on the relative distance in the network between the source of the task and *M*. Since this environment is more complex, the major results presented treat the situation that there is no partial order on the tasks. In that case, an algorithm is presented whose worst case performance is better than known algorithms.

The limiting case of a processor with specialized capabilities is a processor which is capable of executing certain tasks but not others. These types of processors are incorporated into the design philosophy of machines

such as the data flow machine [14]. This is a general purpose computer that contains many specialized processors. The simplicity of these processors permits one to install many of them at low cost. Scheduling problems on such sets of processors are studied in Section 3.4.

There is no active scheduler in current data flow computer architectures. Nevertheless, the scheduling results of Section 3.4 serve as a useful analysis tool. The scheduling algorithms' analyzed include the passive scheduling that exists in the data flow architecture.

Whether or not a machine architecture permits the use of an active scheduler, one does not want to spend too much time on job scheduling, since the time spent on scheduling may be costly. Some of the results of Chapter 3 are applicable even to systems in which one wants to expend little effort in scheduling. These results suggest that if a processor is sufficiently slow, then a better worst case performance is obtainable if it is *never* used. Furthermore, techniques are provided for deciding which processors are sufficiently slow that they should never be used. This type of scheduling result is actually a machine design consideration - the machine should not be designed with such slow processors. Thus the use of these algorithms presents a one time cost which need not be repeated for every set of tasks.

#### **1.3.3 Schemes**

Synchronization and scheduling may be viewed as special cases of the fundamental question of how to develop and execute programs that are to be run in parallel. A basic issue in parallel program design is to develop a language that naturally exhibits all of the parallelism in a given program. Dennis [12] has proposed a language called data flow schemes. A program is essentially a

directed graph where nodes represent operations and arcs represent the fact that one operation may not be executed until the result of another operation is available. In this manner, a considerable amount of parallelism is expressed.

**14** - 4

A subclass of data flow schemes, called well formed data flow schemes, is equivalent to if-then-while schemes [13]. These are proposed as constructs that are reasonable to program with. A natural extension of this would be to develop a data flow langauge that has more power than if-then-while schemes. It is shown in Chapter 4 that the full class of data flow schemes has as much expressive power as the class of r.e. program schemes. Thus, in particular, recursion is expressible in the language of data flow schemes. To prove this, it is shown that a very restricted version of data flow schemes (without explicit counters) can simulate Turing Machines.

To recapitulate, the three main areas of study are synchronization of parallel processes, scheduling of tasks on processors, and development of expressive parallel languages. In addition, a number of auxiliary issues arise due to the techniques that are used. The synchronization routines involve the following wide variety of issues: fault tolerant techniques, methods to permit parallel processes to cooperate without requiring fast processes to wait for slow ones, parallel program verification, and simulation of a managed system with a decentralized system.

The scheduling portion develops algorithms for scheduling jobs in heterogeneous systems. The results here have an impact on machine design as they indicate situations where the usage of a processor is rarely warranted. In addition, Section 3.2.4 discusses some limitations on scheduling with limited information, such as, without advance knowledge about the actual time requirements of jobs. This is an important practical consideration since one often does not have advance knowledge about the actual time requirements of jobs.

Finally, in the scheme portion a new simple basis for computability is developed. Moreover, the techniques used to simulate r.e. program schemes (in particular the finite translation lemma of Section 4.3.2) quantitatively describe how data flow schemes differ from well formed data flow schemes. This difference suggests that perhaps certain additional constructs should be added to the constructs of well formed data flow schemes to achieve certain programming tasks.

#### 2. Synchronization

#### 2.1. Introduction

#### 2.1.1. Background and motivation

#### 2.1.1.1. Previous Work

The mutual exclusion problem is the problem of arranging for asynchronous parallel processes to take turns using a resource. Each process has a "critical section" during whose execution the resource is used. The critical section may be executed correctly only if no other process is simultaneously in its critical section. The first solution to the mutual exclusion problem, which uses read and write instructions as primitives, was devised by Dijkstra [15].

Often one desires protocols that satisfy additional properties, e.g. "fairness" properties such as "lockout free" and "linear wait". (A "lockout free" protocol ensures that every process that tries to enter its critical section will do so, sooner or later.) In [11,16,35], fairness properties of synchronization protocols are considered.

Recent work provides "robust" solutions to the mutual exclusion problem - solutions that work even if parts of the system are unreliable. For example, a process might "die" and set some special variable to a value "dead" [34,37,52,53].

While early solutions to the mutual exclusion problem use only reads and writes, recent work uses the more powerful test-and-set [4,5,17] (as defined in Section 2.1.1.2). Test-and-set instructions have been used either to obtain memory efficient solutions or to cope with unreliability in the processes. In [5], a test-and-set which operates on a single many-valued variable is used to synchronize reliable processes (i.e., the variable may take

on any of many possible values). Developing such synchronization routines is trivial; the contribution of [5] is in obtaining tight upper and lower bounds on the number of values that the single variable must take on.

Similarly, Burns [4] obtains upper and lower bounds on the number of binary-valued variables needed. Again, obtaining some synchronization protocol is easy, but efficient solutions are hard to find.

Undetectable process death (i.e. no special variable is set at death) is introduced in [17]. In [17], processes which may die are synchronized with a single many-valued variable. Once again difficulties arise only when one tries to obtain tight bounds.

The next generalization of the results of [4,17] is to develop resource allocation algorithms which work in spite of undetectable process death and use only bounded-valued variables. Here, it seems to be difficult to arrive at any solution. We solve this problem as a special case.

#### 2.1.1.2 Focus of the chapter

. . •

In this chapter we present a general method for ensuring cooperation among asynchronous processes. This yields, among other things, a new solution to the mutual exclusion problem. We show that even with undetectable death in processes, a large class of synchronization problems is solvable if one uses a test-and-set on bounded-valued variables. In particular, we describe how asynchronous processes can simulate a powerful, "resource manager". Systems with a resource manager easily provide fairness properties (described in Sections 2.2.4 and 2.3). We have not attempted to be efficient; it appeared challenging to develop *any* protocol which simulates a resource manager in an unreliable environment.

This general simulation would not be interesting if we did not assume undetectable death. With totally reliable processes, one process may be chosen as the manager, spending part of its time as a manager and part as a process. Similarly, in a system in which processes announce their deaths, one process may be appointed as the manager, and if that process dies, a different process is chosen to be manager (note the work of [53] which synchronizes such dying processes even without a test-and-set). Here, no process can be chosen to be the manager, since it may die undetectably. Thus all of the processes must act as managers. They must coordinate their activities as managers, making sure that they do not interfere with each other's managing efforts. Even this problem would be easy to solve with many-valued variables. With one many-valued variable the manager's entire state may be encoded.

A test-and-set instruction in one atomic step reads a multiple-valued memory cell and updates the cell's value based on the value read. The algorithms in this chapter use test-and-sets on four-valued memory cells. An interesting open problem is to use binary variables - since common machine test-and-set instructions operate on binary variables. (We mention in Section 2.4, a technique which uses three-valued cells.)

#### 2.1.1.3 Memory unreliability

Not only does our simulation work if processes die and bounded-valued variables are used, but it also tolerates limited memory failure. If only a single variable is used and this variable is unreliable then the mutual exclusion problem is not solvable. For every k, we may use many memory cells of fixed size to achieve fair synchronization even if any k cells fail.

Memory unreliability may be viewed as a generalization of the attempts of [4,5,17] to get tight bounds on memory requirements. One reason to use a minimum amount of memory is that a system that uses little memory is reliable if it uses reliable hardware. An alternative approach to providing reliability is to use inexpensive unreliable memory and protocols that tolerate memory errors. Other reasons for introducing memory unreliability are discussed in Section 2.1.2.

#### 2.1.1.4 Outline of the chapter

In Section 2.2 we define models for systems of processes and for manager-directed synchronization protocols. Section 2.2 also defines what it means for one system of processes to simulate another system of processes, and shows that this definition preserves important fairness properties. The rest of Chapter 2 shows that a system of processes may simulate an undying manager, even when the simulating system has unreliable memory, processes that die, and no controlling manager. A corollary of this is that fair synchronization in an unreliable environment may be done without a manager.

Section 2.3 presents a sample synchronization protocol where a manager ensures typical fairness properties. Section 2.4 describes our unmanaged simulation of managed systems. Section 2.5 contains a proof of correctness.

#### 2.1.2 Unreliability assumptions and their motivation

#### 2.1.2.1 Process death

In this section we elaborate on our assumption of undetectable death. Real processes often fail without setting a variable to "dead". Thus we assume (as in [17]) that a dead process merely ceases to execute. Our solutions provide fair mutual exclusion as long as at least one process is alive. (Concepts such as fair mutual exclusion require reformulation if processes die undetectably.) We do not consider more extreme modes of failure in which processes deviate from their protocols.

A problem arises when a process dies while executing its critical section, thereby "locking out" all other processes. Our solution will recover from death in the critical section only if processes do announce their death. It is clearly impossible to do better if the system cannot recognize that the process has died.

If a mutual exclusion protocol is tolerant of unannounced death then extremely slow or dead processes cannot cause arbitrary system slowdowns. For example, assume that process *j* will be next to obtain access to a critical resource. In a previous solution [53], process *j* waits for signals from other processes before obtaining access to the resource. Thus, a slow process could unnecessarily hold up process *j*. In any solution tolerant of dying processes, (e.g. our solution) a process must correctly obtain access to the critical resource even if all other processes die. It therefore, cannot wait for acknowledgements from potentially slow or dead processes. This contrasts with solutions which require that other processes will eventually exhibit some activity.

Even if processes die in their critical section, a solution assuming

unannounced death can achieve the k-sharing property [17]. Namely, if there are enough resources for k processes to execute their critical section simultaneously, the deaths of fewer than k processes (even in their critical section) should not deadlock the rest of the system.

Finally unannounced death forces the simulation to be truly decentralized; we can not merely appoint one of the processes as a manager.

#### 2.1.2.2 Memory faults

This section describes the extent to which our simulation methods tolerate memory unreliability. A memory cell is unreliable if after it is set to a specified value, the value may change even if the cell is not rewritten. If all of the memory is unreliable it is impossible for totally reliable coordination to take place. Our solutions are fault tolerant in the sense that they do not depend on the reliability of any single memory cell. Rather, they depend on assumptions about memory failure patterns. Memory is divided into blocks, and the assumptions are of the form "at most e cells in every block of s cells are ever in error." The precise dependence of s on e is described in Section 2.6. For any value of e, there is a value s=f(e) such that the solution works as long as only e cells in each block of s cells fail. To tolerate the failure of any e cells, we make every block of cells tolerant of efailures.

Certain fault tolerant techniques are not applicable. For example, one might utilize primitives that test-and-set three cells at once. If at most one cell is faulty, the three cells still reliably represent a single reliable cell with majority voting. We outlaw this facility on the grounds that three cells that may be accessed at once presumably reside in the same memory "unit". We

desire that our solution tolerate the failure of any such "unit". This also prevents the use of more elaborate coding schemes.

In another fault tolerant technique each process maintains multiple copies of every cell (and each copy is updated at a different step). If at most one cell out of three is unreliable, the true value of a cell could be determined by keeping three copies of every cell and taking the majority. While this technique usually works if each variable is written by only one process, complications arise if different processes may write a variable in a potentially conflicting manner. Since we need to have more than one process write some variables, this multiple copy technique is not immediately usable.

In summary we assume that no single system unit, even a memory unit, is immune to failure. The correctness of the solutions depend on assumptions regarding the number of memory faults. Our protocols handle resource assignment unless all processes die, or as many die in their critical section as there are critical resources.

#### 2.1.2.3 Motivating machine models

This section discusses the interpretation of our model in real systems. In a multiprogrammed environment with several processes running on a single processor, hardware failure would result in the death of all processes. Thus death in our model is best thought of as modeling the effect of an undetected infinite loop. In addition, death models a low priority process which rarely gets processing time. Such slow behavior must not become a system bottleneck.

Our model is also motivated by distributed environments. Here there are usually no global variables, but it is conceivable that some shared memory

might be distributed among the sites of a system. However, even in that case, our solution cannot handle "site death" because site death causes too much memory to be lost. Specifically, if the communication links to a site are unreliable, then all cells at that site are unreliable. If there are *n* sites in the system and one site dies (through unreliable communication links), then 1/n of the cells of the system are not reliably accessible. Our solution does not solve this problem, but does suggest some means of attacking it. As mentioned above, our solutions work if "at most  $\epsilon$  of s cells are unreliable". If such blocks of s cells are partitioned into  $s/\epsilon$  subblocks of size  $\epsilon$ , then the failure of any one subblock is tolerable. For the protocols of this chapter  $s/\epsilon \ge 16n$ . (Section 2.6 contains a variation with a factor of 14n.) If  $s/\epsilon$  can be kept as small as n, then the death of one network site (containing one subblock) is tolerable.

ე ე

#### 2.2. Basic Definitions

Section 2.2.1 defines a process system, and several notions of simulation. Section 2.2.2 explores the properties of simulation and describes how simulation preserves fairness. Section 2.2.3 explains why and how the definitions of simulation must be relaxed to allow one to cope with unreliable memory. Section 2.2.4 introduces a special class of process systems, the managed systems which model resource allocation systems.

U ....

#### 2.2.1 Process systems and the definition of simulation

#### 2.2.1.1 Process systems

A process system captures the notion of a set of asynchronously executing processes each of which represents a program being executed in a computer system. Memory cells are used for message passing between processes. Any memory that is local to a process is incorporated into the process's state. The order in which processes appear in a turns history reflects the order in which they take turns executing instructions.

A process system, P, consists of a finite set of processes, denoted processes(P), a finite set of memory cells, denoted cells(P), and a state transition function  $\delta$ . Process j (for  $1 \le j \le |processes(P)|$ ) is a possibly infinite set, denoted PROC(P,j), of process-states. The j<sup>th</sup> memory cell (for  $1 \le j \le |cells(P)|$ ) is a finite set, denoted CELL(P,j), of memory-states. A designated element of PROC(P,j) is the initial process-state of process j and a designated element of CELL(P,j) is the initial memory-state of cell j.

The set of system-process-states of P, PROCSTATES(P), is the cartesian product  $PROC(P,1) \times PROC(P,2) \times \ldots \times PROC(P,n)$  where n=|processes(P)|. The set of system-memory-states of P, MEMSTATES(P), is the cartesian product CELL(P,1) × CELL(P,2) × ... × CELL(P,m) where m=|cells(P)|. A system-state, s, consists of a system-process-state, procstate(s), and a system-memory-state, memstate(s). The state of process j in a system-state s is the j<sup>th</sup> coordinate of procstate(s). The state of cell j in s is the j<sup>th</sup> coordinate of memstate(s). The set of all system-states is denoted SYSSTATES(P). The initial system-process-state is the system-process-state whose j<sup>th</sup> coordinate is the initial state of process j. The initial system-memory-state and initial system-state are similarly defined.

The state transition function, **b**, is a map

$\delta$ :SYSSTATES(P) × {1,...,n}-SYSSTATES(P) where n=|processes(P)|. The function  $\delta$  satisfies:

(a) For  $k \neq j$ , the state of process k in  $\delta(s,j)$  is the same as that in s.

(b) The state of process j in  $\delta(s,j)$  is not equal to that in s.

(c) If the states of process j in  $s_1$  and  $s_2$  are the same, and if  $memstate(s_1)=memstate(s_2)$ , then the state of process j in  $\delta(s_1,j)$  equals the state of process j in  $\delta(s_2,j)$  and  $memstate(\delta(s_1,j))=memstate(\delta(s_2,j))$ .

If  $\delta(s_1,j)=s_2$  then  $s_2$  follows  $s_1$  after a process j transition.

Condition (a) asserts that at a process *j* transition, the state of no other process changes. Condition (b) insists that at a process *j* transition, the state of process *j* does change, a technical convenience to be explained later. Condition (c) indicates that the changes in the system-state at a process *j* transition depend only on the system-memory-state and the state of process *j*. Note that the processes are deterministic.

A turns history for P is an infinite sequence of integers from the set

υü

$\{1,...,|processes(P)|\}$ . The system-state-history of a turns history  $t_0t_1$ <sup>...</sup> is the unique sequence of system-states  $s_0s_1$ <sup>...</sup> such that  $s_0$  is the initial system-state and  $\delta(s_i,t_i)=s_{i+1}$ . Process *j* dies in a turns history *T* if *j* appears only finitely often in *T*.

#### 2.2.1.2 One definition of simulation

We now discuss one definition of simulation of a process system P by a process system Q. This is a weak definition, involving only the memory.

Let  $1 \le d \le |cells(P)|$ . Let  $s_0 s_1^{\cdots}$  be a system-state-history for P and let  $m_i$  denote the d-tuple of the states of the first d cells in  $s_i$ . The memory-history of the first d cells of  $s_0 s_1^{\cdots}$  is the sequence  $m_0 m_1^{\cdots}$ . We often refer to the memory-history of the first d cells in P, since the others may not be important; they may be used for bookkeeping and not for communication between processes. If all cells of P are important, then the memory history is only of interest for d=|cells(P)|.

The important part of such histories are the changes. Let  $h_0h_1$ ... be an infinite sequence (a "history"). The *i*<sup>th</sup> element of  $h_0h_1$ ... is altered if *i*=0 or if  $h_i \neq h_{i-1}$ . The altered-history is the subsequence consisting of altered sequence elements. For example, the altered-memory-history is the altered history of the memory history.

We define the notion of Q simulating P. Let  $1 \le d \le |cells(P)|$ . A memory-simulator-function, f, for Q into the first d cells of P, consists of dfunctions  $f_1, \dots, f_d$ , where  $f_j$ :MEMSTATES(Q)-CELL( $P_i$ ). The function  $f_j$  is called the memory-simulator-function for cell j of P. If memory-simulatorSQ, then  $f(m)=(f_1(m),\dots, f_d(m))$  is called the simulated-memory-state of m. For any system-state-history,  $s_0s_1^{m}$ , of Q, the simulated-memory-history is the sequence  $f(memstate(s_0))f(memstate(s_1))^{m}$ . The simulated-memory-state and simulated-memory-history depend on d and f, but this dependence is often suppressed when obvious. (The simulated-memory-state is not a system-memory-state of P unless d=|cells(P)|.)

Q simulates the memory of P with respect to a memory-simulator-function,  $f=f_1,...,f_d$  (i.e. with respect to the first d cells) if the set of altered-memory-histories of P obtained from all turns histories for P and the set of altered-simulated-memory-histories of Q obtained from all turns histories for Q are the same.

One considers altered histories so that Q may spend many turns simulating one turn of P. Also, if P spends k turns without changing the first d cells, Q need not waste k turns.

## 2.2.1.3. Faithful simulation

The above notion of simulation does not require any correspondence between the processes of Q and P. When modelling entrance into the critical section, we need a correspondence between the processes of the two systems, e.g., the  $j^{\text{th}}$  process of P and the  $j^{\text{th}}$  process of Q.

Let P and Q be two process systems and let  $1 \le r \le \min(|processes(P)|, |processes(Q)|)$ . A process-simulator-function, g, is a set of r functions  $g_1, \dots, g_r$  where  $g_j$  is a function  $g_j: PROC(Q, j) \rightarrow PROC(P, j)$ , the process-simulator-function for process j. The value  $g_j(q)$  (for  $q \in PROC(Q, j)$ ) is the simulated-process-state of q.

The essential-state of a system-state s with respect to r and d is the r+d-tuple listing the states of the first r processes in s, and the states of

the first d cells in s. The essential-history-with-repetitions of a system-state-history  $s_0s_1^{m}$  is the sequence  $e_0e_1^{m}$  where  $e_i$  is the essential-state of  $s_i$ . The essential-history is the subsequence of the essential-history-with-repetitions consisting of altered sequence elements.

One looks only at the first r processes since it may not be important to simulate the behavior of all of the processes of P. For example, in our simulation of a managed system, it is not important for any process of the simulating system to have its state correspond to the state of the manager.

Let Q and P be two process systems. Let  $s \in SYSSTATES(Q)$ , let  $g=g_1,...,g_r$  be a process-simulator-function, and let  $f=f_1,...,f_d$  be a memory-simulator-function. The essential-simulated-state of s is the r+d-tuple listing the simulated-process-states of the first r processes and the simulated-memory-states of the first d cells. The essential-simulated-history-with-repetitions of a system-state-history for Q,  $s_0s_1$ , is  $e_0e_1$ , where  $e_i$  is the essential-simulated-state of  $s_i$ . The essential-simulated-history is the subsequence of the essential-simulated-history-with-repetitions consisting of altered sequence elements.

Let  $\mathcal{T}$  be a set of turns histories of P and let  $\mathcal{T}'$  be a set of turns histories of Q. Then Q faithfully simulates P with respect to  $\mathcal{T}$  and  $\mathcal{T}'$ , with a memory-simulator-function  $f=f_1,...,f_d$ , and a process-simulator-function  $g=g_1,...,g_r$ , if:

(1) The set of essential-histories of P obtained from turns histories in  $\mathcal{T}$  and the set of essential-simulated-histories of Q obtained from turns histories in  $\mathcal{T}'$  are the same.

(2) Let  $T \in T'$ , and let  $q_0 q_1$  be the sequence of process j states in the

system-state-history generated by T ( $j \le r$ ). If process j does not die in T then infinitely many elements of the sequence of simulated-process-states  $g_j(q_0)g_j(q_1)^{\cdots}$  are altered.

Thus, (2) prevents process j from having infinitely many turns in Q without simulating process j in P. The motivation is that if, in some turns history a process of Q does not die, then the corresponding simulated process of P does not die either. By condition (a) of the definition of the state transition function, the only turns in a turns history for Q at which the simulated-process-state of process j may change are at process j turns.

One reason that process j changes state at a process j transition (condition (b) of the definition of the state transition function), is to permit us to state condition (2). If a process in P could take infinitely many turns without changing state, then it would not make sense to insist that in Q, the corresponding process could not take infinitely many turns without changing its simulated state.

The second reason that process j changes its state is related to (1). If in some history of P process j has a number of turns in which it remains in the same state, there should be some method of noticing this in histories of Q. However, since (as explained in Section 2.2.1.2) it is convenient to define simulation on altered histories, the fact that process j does not change its state is not represented in any essential-history. Thus we force the state to change.

Q faithfully simulates P if it faithfully simulates P with respect to the set of all turns histories of P and the set of all turns histories of Q.

Q faithfully partially simulates P (with respect to T and T') if the set of essential-histories of P (obtained from turns histories in T) contains the set of essential-simulated-histories of Q (obtained from turns histories in T') and (2) above holds (for T').

Intuitively, if Q faithfully partially simulates P, then no history of Q behaves incorrectly, since every history reflects a possible behavior of P. However, Q may not reflect all possible behaviors of P.

The usefulness of a faithful partial simulation depends on which features of P one wants to preserve with Q. For example, if P satisfies properties such as deadlock freedom or bounded waiting (as defined in Section 2.2.2), then so will Q, if Q faithfully partially simulates P. Since these fairness properties motivate this work, faithful partial simulation is important here.

## 2.2.2. Properties of simulation.

For this section suppose Q faithfully simulates P with respect to a memory-simulator-function  $f=f_1,...,f_d$ , and a process-simulator-function  $g=g_1,...,g_r$ . We discuss important properties of simulation which are trivial consequences of the definition.

Lemma 2.1. Q simulates the memory of P.

**Proof.** Obvious.

Lemma 2.2 Let T be a turns history of P, T' a turns history of Q, such that the essential-history of T equals the essential-simulated-history of T'. Let  $j \le r$ . Then process j dies in T iff process j dies in T'. If j does not occur in T', then j does not occur in T.

**Proof.** If process j dies in T, then there are only finitely many alterations in the "process j history" (i.e. the sequence of process j states), by condition (a) of the definition of the state transition function. Thus, the simulated-process-state of process j may change only finitely often in T'. By condition (2) on faithful simulation, if process j does not die in T', the simulated-process-state of process j is altered infinitely often. Thus process j dies in T'.

Conversely, assume that process j dies in T'. Since at most one change in simulated-process-state occurs for each occurrence of j in T', the simulated-process-state of process j changes only finitely often. Thus there are only finitely many changes in the state of process j in the essential-history of T and so by condition (b) on state transition functions joccurs finitely often in T.

If j does not occur in T', then the simulated-process-state of process j never changes and j does not occur in T.  $\Box$

Assume that each process of P has one designated critical state. Then P satisfies mutual exclusion for a set of turns histories, T, if no two processes (i.e. of processes 1,...,r) are ever simultaneously in their designated critical states in any system-state-history that arises from  $T \in T$ . We say that the simulating system, Q, satisfies mutual exclusion for the turns histories, T', if in no system-state which is an element of the system-state-history of a  $T' \in T'$ , are the simulated-process-states of two processes (of processes 1,...,r) simultaneously critical. We think of a process in Q as executing its "critical section" in one of its states whose simulated-process-state is the critical state of P.

Lemma 2.3. If P satisfies mutual exclusion then Q satisfies mutual exclusion.

**Proof.** Assume that Q does not satisfy mutual exclusion. Then in some system-state-history of Q generated by some turns history T' there is a system-state in which the simulated-process-states of two different processes are both critical. Look at the first turn at which this happens. The essential-simulated-state of Q is altered at that turn, and thus appears in the essential-simulated-history of T'. Since the essential-simulated-history of T' equals the essential-history of some turns history T for P, it must be that P violates mutual exclusion.  $\Box$