#### VORTOS

### Versatile Object-oriented Real-Time Operating System

by

Rusty Lee

Submitted to the Department of Electrical Engineering and Computer Science

in Partial Fulfillment of the Requirements for the Degrees of

Bachelor of Science in Electrical Engineering and Computer Science

and Master of Engineering in Electrical Engineering and Computer Science

at the Massachusetts Institute of Technology

May 23, 2001

Copyright 2001 Rusty Lee. All rights reserved.

The author hereby grants to M.I.T. permission to reproduce and distribute publicly paper and electronic copies of this thesis and to grant others the right to do so.

| Author       |                                                           |

|--------------|-----------------------------------------------------------|

|              | Department of Electrical Engineering and Computer Science |

|              | May 23, 2001                                              |

| Certified by |                                                           |

| -            | Sanjay Sarma                                              |

|              | Thesis Supervisor                                         |

| Accepted by  |                                                           |

|              | Arthur C. Smith                                           |

|              | Chairman, Department Committee on Graduate Theses         |

### VORTOS Versatile Object-oriented Real-Time Operating System

by

Rusty Lee

Submitted to the Department of Electrical Engineering and Computer Science on May 23, 2001, in partial fulfillment of the requirements of the Degrees of Bachelor of Science in Electrical Engineering and Computer Science and Master of Engineering in Electrical Engineering and Computer Science

### Abstract

As computer software has become more complex in response to increasing demands and greater levels of abstraction, so have computer operating systems. In order to achieve the desired level of functionality, operating systems have become less flexible and overly complex. The additional complexity and abstraction introduced often leads to less efficient use of hardware and increased hardware requirements. In embedded systems with limited hardware resources, efficient resource use is extremely important to the functionality of the resources. Therefore, operating system functionality not useful for the embedded system's applications is detrimental to the system. Component-based software provides a way to achieve both the efficient application-specific functionality required in embedded systems and the ability to extend this functionality to other applications.

This thesis presents a component-based operating system, VORTOS, the Versatile Object-oriented Real-Time Operating System. VORTOS uses a virtual machine to abstract the hardware, eliminating the need for further portability abstractions within the operating system and application level components. The simple modular component architecture allows both the operating system and user applications to be extremely flexible by allowing them to utilize the particular components required, without sacrificing performance.

Thesis Supervisor: Sanjay Sarma Title: Assistant Professor, Department of Mechanical Engineering

## Acknowledgements

The author would like to thank everyone who gave me support and encouragement while completing this work. Thanks in particular go to Dr. Daniel Engels and Professor Sanjay Sarma for helping me stay on track and reviewing and helping me to revise my work. Thanks also go to Ian Ross and Brett Whittemore for helping me hash out the design.

# **Table Of Contents**

| List of Figures                                            | 9  |

|------------------------------------------------------------|----|

| List of Tables                                             | 11 |

| Chapter 1 – Introduction                                   | 13 |

| Section 1.1 – Historical Background                        | 14 |

| Section 1.2 – Traditional Operating System Characteristics | 16 |

| Section 1.3 – VORTOS Overview                              | 18 |

| Section 1.4 – Thesis Overview and Contributions            | 20 |

| Chapter 2 – Related Work                                   | 23 |

| Section 2.1 – Component-based Software                     | 23 |

| Section 2.2 – Separating Mechanism from Policy             | 24 |

| Section 2.3 – Virtual Machines                             | 25 |

| Section 2.4 – Translation Technologies                     | 26 |

| Chapter 3 – VORTOS Overview                                | 27 |

| Section 3.1 – Components                                   | 27 |

| Section 3.2 – Virtual Machine                              | 31 |

| Section 3.3 – Recompiler Sub-system                        | 32 |

| Chapter 4 – Virtual Machine Architecture                   | 35 |

| Section 4.1 – PVMF-32 Overview                             | 35 |

| Section 4.2 – Instruction Set                              | 39 |

| Section 4.3 – Interrupts                                   | 41 |

| Section 4.4 – Exception Handling                           | 42 |

| Section 4.5 – Threads                                      | 43 |

| Section 4.6 – Debugger                                     | 45 |

| Section 4.7 – Design Analysis                              | 47 |

| Chapter 5 – Component Architecture                         | 51 |

| Section 5.1 – Component Structure                          | 51 |

| Section 5.2 – Component Messaging   | 54 |

|-------------------------------------|----|

| Section 5.3 – Design Analysis       | 56 |

| Chapter 6 – Basic Components        | 59 |

| Section 6.1 – Loader                | 59 |

| Section 6.2 – Task Scheduler        | 62 |

| Section 6.3 – Memory Manager        | 62 |

| Section 6.4 – Design Analysis       | 64 |

| Chapter 7 – Recompiler Architecture | 65 |

| Section 7.1 – Description           | 65 |

| Section 7.2 – Design Analysis       | 70 |

| Chapter 8 – Implementation          | 73 |

| Section 8.1 – Experimental Setup    | 73 |

| Section 8.2 – Difficulties          | 74 |

| Section 8.3 – Performance           | 74 |

| Section 8.4 – Analysis              | 76 |

| Chapter 9 – Conclusions             | 77 |

| References                          | 79 |

| Appendix A – Table of Instructions  | 81 |

| Appendix B – Code Listings          | 85 |

# List of Figures

| Figure 1.3.1 – Logical Layers of VORTOS architecture   | 19 |

|--------------------------------------------------------|----|

| Figure 3.1.3 – Some Example Components                 | 29 |

| Figure 4.1.1 – The Virtual Machine                     | 36 |

| Figure 4.1.2 – The Memory Map Structure                | 37 |

| Figure 4.2.1 – Instruction Formats                     | 40 |

| Figure 4.5.1 – Stack Layout in Memory                  | 44 |

| Figure 4.6.1 – Virtual Machine Register Window         | 45 |

| Figure 4.6.2 – Hexadecimal Dump of Virtual Machine RAM | 46 |

| Figure 4.6.3 – Virtual Machine RAM Disassembly         | 46 |

| Figure 5.1.1 – Component Structure                     | 52 |

| Figure B.1 – Fibonacci C Source Code Listing           | 85 |

| Figure B.2 – Fibonacci Java Source Code Listing        | 86 |

# List of Tables

| Table 3.1.1 – Common Class Codes         | 28 |

|------------------------------------------|----|

| Table 3.1.2 – Common Type Codes          | 28 |

| Table 3.1.4. – Example Codes             | 29 |

| Table 7.1.1 – Meta-Instruction Structure | 67 |

| Table 7.1.2 – Instruction Translation    | 69 |

| Table 8.3.1 – Fibonacci Test Run Times   | 75 |

| Table A.1 – Table of Instructions        | 81 |

## **Chapter 1**

### Introduction

Increased demand for functionality has increased the complexity of modern software systems. To deal with the added complexity, operating systems have provided increased levels of abstraction. While these added layers of abstractions simplify some operations, they can also limit application flexibility. This makes it harder to adjust these systems for use with specialized applications calling for specific functionality and efficiency requirements.

Embedded systems, in particular, have limited memories and processing power available to them. This means that programs and operating systems running on embedded systems must run in an efficient manner, without using unnecessary memory or processing time. Since most embedded systems are targeted towards some very specific application, their specific functionality requirements for efficient operation vary greatly. This means that operating systems must either be large enough to provide all of the necessary functionality that could possibly be required or be customized for each unique system.

The Versatile Object-oriented Real-time Operating System (VORTOS) addresses these problems by providing a platform flexible enough to handle the specialized functional needs of embedded systems without sacrificing efficiency.

This chapter gives an introduction to the problems faced by embedded systems developers and provides an overview of VORTOS. Section 1.1 gives a historical

background of the problems of computer operating systems. Section 1.2 reviews why traditional operating systems are unsuitable for embedded applications. Section 1.3 introduces VORTOS. Section 1.4 covers the findings of this thesis and outlines the rest of the thesis.

#### 1.1 Historical Background

When personal computers were first introduced, specialized programs were written for every task. Writing these programs was a long and difficult task, since the program had to take care of every aspect of interaction with the hardware, including graphical display, user input, and low-level hardware functionality. Since every program had its own needs, similar but unique code was written for the same tasks in many different programs.

As hardware resources became more plentiful within the computer, software programs expanded to take advantage of these additional resources; consequently, the design and functions of computer programs became more complex. Computer operating systems were introduced to simplify the design and construction of software. The purpose of an operating system is to provide services and hardware abstractions for software applications to make writing these applications easier. Examples of these services and abstractions include program loading and scheduling, virtual memory management, and graphical elements like menus and windows. Instead of directly interacting with every aspect of the hardware, software developers can write programs made to run on these operating systems, allowing them to concentrate on the higher level features specific to a single application.

14

The general-purpose abstractions and services for the low-level tasks that developers need eliminate the need for large amounts of redundant code between software programs. This has become even more important as new hardware devices have been introduced. It would be ludicrous for every single program to support every known hardware device. The decreased dependence on hardware enabled by operating systems makes software programs more portable across different hardware platforms.

Unfortunately, the great benefits provided by operating systems come at a price. If a software developer wants to add low-level functionality to the system or take advantage of new hardware, the operating system vendor must add this support before the software developer can take advantage of it. Additionally, since operating systems are designed for general application development, specific policies or algorithms at the operating system level may not be the most efficient or most appropriate for any given task an application may perform, and there is no way for a software developer to modify this behavior. Despite these problems, operating systems over the past 30 years have made possible sophisticated software projects that would have been too complex or timeconsuming to implement without them.

Although operating systems have increased the feasibility and speed of complex software projects, both the software and the computers themselves have also become more complex. The result is that modern software development is still a lengthy and complex process. According to the Standish Group, a quarter of all software projects fail and another 50% fall behind schedule [13]. The services provided by current operating systems are often not flexible enough to accommodate the needs of modern software developers, forcing them to spend time trying to work around these constraints. In

15

addition, code for current operating systems is often poorly organized and inaccessible, and so sometimes software developers cannot understand what the constraints are and even when they do, they cannot change them. This also makes bugs in software hard to track down. Even open-source solutions such as Linux do not alleviate this concern, because the source code itself is so complex that very few people understand it well. Even with a thorough understanding, modifying the operating system code of a system as large and complicated as Linux is a significant undertaking.

As a result, while the power of computer hardware has been increasing exponentially, the power of computer software has only increased linearly. Indeed, as computer software becomes more complex, developers have required higher levels of abstraction using languages such as Java and C++ and markup languages such as XML to make their projects more manageable. However, these multiple layers of abstraction not only add overhead, making software slower but also make adding new features not accounted for by these abstraction layers and tracking down and fixing problems in software extremely difficult. This is particularly important in embedded systems, where hardware resources are minimal and high levels of reliability are required for operation.

### **1.2 Traditional Operating System Characteristics**

Traditional general-purpose operating systems, such as Linux and Microsoft Windows, have several characteristics that make them inappropriate for use with embedded systems. These systems rely on a protected kernel to hide their inner workings from user applications. To meet the functionality needs of user applications, they provide a variety of different interfaces for accessing the kernel. These interfaces must be general enough to cover all the requests an application might make of the kernel, requiring the kernel interfaces to contain a large amount of code simply for making the appropriate requests from the hardware or other parts of the kernel [6]. Allowing applications to dynamically modify these interfaces would provide much needed flexibility, but such functionality cannot be incorporated into traditional kernels that were not designed with such flexibility in mind.

Most traditional kernels, and even microkernels, are fairly large; therefore they are more likely to generate exceptions while executing kernel code. While the kernel typically insulates the operating system from exceptions generated in user programs, most operating systems are not protected from the exceptions generated while in kernel mode. Consequently, kernel exceptions can cause an entire operating system to fail. A very small, simple kernel minimizes the possibility for kernel errors, resulting in a more stable operating system [7].

Additionally, since each user application makes use of the hardware resources differently, the kernel is typically optimized for the most common cases. This results in sub-optimal performance for many applications [7]. Specialized operating systems targeted towards specific narrow tasks can achieve much better performance than operating systems optimized for the average case [8]. Component architectures allow this sort of specialization without sacrificing flexibility, by allowing the appropriate specialized component to be used for a particular task [5] [6].

17

### **1.3 VORTOS Overview**

The Versatile Object-oriented Real-Time Operating System (VORTOS) overcomes the aforementioned limitations of traditional operating systems, by minimizing the kernel code and providing the flexibility to allow specialization of the operating system on a per-process basis. VORTOS is a real-time operating system with a component-based architecture, allowing it to be adaptable to a wide-range of environments and applications. It is highly scalable; it can be used in systems ranging from embedded systems to high-end workstations to a distributed network of machines. The component-based nature of VORTOS allows it to take advantage of whatever power the underlying hardware has to offer. Specialized components can be added for additional functionality or efficiency. It can satisfy real-time constraint requirements for mission-critical operations, making it particularly suited for embedded applications. Its modular structure can adapt to changing conditions to best meet the needs of its users. For embedded applications, unnecessary components can be used to optimize performance. The kernel is extremely small and simple, providing a stable system.

|                        |                                   |                       | Addit | iona |     | omp | onei | nts |

|------------------------|-----------------------------------|-----------------------|-------|------|-----|-----|------|-----|

| Scheduler<br>Component | Memory<br>Management<br>Component | Compiler<br>Component |       |      | _+_ |     |      |     |

| Virtual Machine        |                                   |                       |       |      |     |     |      |     |

| Hardware Platform      |                                   |                       |       |      |     |     |      |     |

Figure 1.3.1: Logical layers of VORTOS architecture

VORTOS consists of a collection of objects running on a simple virtual machine that provides an abstraction layer between the objects and the underlying hardware platform. Figure 1.3.1 graphically illustrates the logical layers of the VORTOS architecture. The operating system functions and user programs running on the virtual machine are made up of a collection of objects called *components* that contain code and data. Components are run-time objects that provide specific services or functionality on a given resource or data. For example, a memory management component allocates and deallocates memory to programs in the address space it corresponds to. Since the operating system functionality is implemented as a set of simple low-level components, applications can choose the components that provide the exact functionality that they need, providing maximum flexibility. User applications can also provide additional custom components to more efficiently take advantage of specific low-level hardware resources, thereby enhancing the functionality of the entire system.

The Portable Virtual Machine Format (PVMF) virtual machine acts as a very simple kernel. The PVMF virtual machine provides a simple abstraction of the hardware and simple services that allow the multiplexing of processor time across any number of

different local or remote components, while satisfying any real-time constraints requested. Using a virtual machine provides binary compatibility for the components across different hardware platforms. Therefore, VORTOS can be ported to new hardware by simply porting the virtual machine. This gives software the flexibility to run on a wide variety of platforms and even allows VORTOS to be embedded into existing operating systems. It also provides maximum stability against errors in both application and operating system components, since individual components can be shut down or replaced without crashing the entire operating system.

### **1.4** Thesis Overview and Contributions

The main contribution of this thesis is VORTOS, a general-purpose system that can provide customized functionality for each application. This custom functionality allows specialized applications to run efficiently, without impeding the efficient operation of other applications that do not require these specialized resources. The key to this flexibility is a new form of dynamic messaging architecture integrated with a component-based architecture running on top of a virtual machine. This thesis describes VORTOS, the various components of its architecture, and how they fit together to produce a flexible, scalable system.

Chapter 2 discusses related work to VORTOS. Chapter 3 gives an overview of the component architecture and virtual machine used to provide a flexible, scalable system. The instruction set architecture used by the virtual machine is detailed in Chapter 4. Chapter 5 introduces a unique dynamic messaging architecture that is responsible for providing the high level of flexibility and customizability of VORTOS. Chapter 6 describes the essential operating system components and how they work together to create a usable system that allows easy substitution of policies and dynamic filtering of programmatic content. Chapter 7 discusses the compiler sub-system and how machine code generated by a commercial off-the-shelf compiler is translated into usable virtual machine code by the system. Chapter 8 describes an implementation of the system and the simplicity benefits in implementation provided by the VORTOS architecture. Chapter 9 presents conclusions and suggests future work.

### Chapter 2

### **Related Work**

Since operating systems cover a broad area of computer science research, there is a large amount of related work in this area, and thus a large amount of overlapping research. This chapter reviews several approaches used to address the problems of embedded systems and operating system software in general. Section 2.1 looks at prior component-based solutions. Section 2.2 reviews customizable software approaches. Section 2.3 explores the abstraction provided by virtual machines. Section 2.4 looks at some translation and recompilation resources for compatibility.

### 2.1 Component-based Software

Component-based operating systems have a long history. UNIX itself was formed based on the idea of modular components, separating out functionality into a kernel, various user-level utility programs, and libraries of code, with all components using a portable source language, C [1]. However, UNIX suffers from the flexibility and efficiency problems of traditional operating systems described earlier in Section 1.2.

In the early 1990's, Taligent created an operating system known as Pink that was based completely around autonomous components generated from C++ classes [2]. Although this provided increased flexibility, the overhead from the run-time manipulation of C++ classes resulted in significant performance degradation [2]. VORTOS takes a similar component-based approach, but with a much more lightweight component architecture.

Scout is another component-based operating system designed to have multiple components communicating over a network while running in parallel [3]. Similarly, CORBA provides a uniform standard for distributed objects to communicate over a network and could be used to provide remote access to local VORTOS components [4]. UIUC's 2K Operating System uses CORBA to provide networked access to its components [5]. However, Scout, CORBA and 2K all implement messaging and componentization at a higher level than VORTOS, and so do not receive as much of a flexibility or efficiency benefit from componentization. The high level messaging also increases system overhead, making implementation on embedded systems difficult.

### 2.2 Separating Mechanism from Policy

More recently, it has become common for operating systems to separate mechanism from policy to maximize flexibility. Harvard's VINO does this to maximize the reusability of code [6]. The Exokernel [7] and Cache Kernel [8] make this separation under the assumption that applications know how to allocate memory and schedule tasks for their specific needs, so can achieve performance better than that of a general-purpose kernel scheduler. The Exokernel attempts to reduce the operating system kernel to a series of basic hardware abstraction calls, much like VORTOS' virtual machine abstracts the hardware through a virtual machine [7]. Stanford's Cache Kernel allows kernels to be implemented as plug-in modules that provide different types of functionality through a kernel multiplexing scheme [8]. However, neither the Exokernel nor the Cache Kernel provides the same level of functionality realized by VORTOS' general-purpose uniform component architecture. Rather than simply allow customization of basic hardware kernels, VORTOS goes a step further by allowing the customization of every aspect of the operating system and applications running on it.

#### 2.3 Virtual Machines

Virtual machine architectures have been around for quite some time, and are quite useful for process migration. FLUX-OS is an operating system that supports applicationspecific and recursive virtual machines. These virtual machines can be customized on a per-application basis to provide specialized functionality [9]. However, having a separate virtual machine for each customized scenario has too large a footprint for many embedded systems. The Spin operating system allows processes to migrate applicationspecific functionality into kernel space, allowing user applications to supplement but not replace kernel functionality [10]. Hope is an operating system that runs on parallel virtual machines and uses optimistic prediction to maximize parallelism, but does not provide any form of customized functionality [11]. Virtual machines such as Sun Microsystem's Java and Synthetix are high-level virtual machines that can generate code at run-time for faster execution [12]. By combining a virtual machine with a component architecture, VORTOS obtains the functionality and efficiency benefits of both approaches.

### 2.4 Translation Technologies

Dynamic recompilation has become a popular approach for overcoming some of the performance limitations of virtual machine architectures such as Java and Synthetix [12]. Dynamic recompilation is common among game console emulators for performance reasons. These systems use dynamic recompilation to speed up execution of virtual machine code by translating it into machine code for the underlying native hardware processor on-the-fly. Apple uses dynamic recompilation on its PowerPC computers to provide compatibility with software written for older Motorola 68000 processors [14]. Digital developed an i386 to Alpha translator for similar compatibility reasons [15]. UQBT is a general-purpose retargetable binary translator for general binary code translation. It performs static binary translation for better optimization and to avoid delays at run-time [16]. VORTOS is built with a similar, but more specific binary translator tailored specifically for the virtual machine architecture used in VORTOS.

### Chapter 3

### **VORTOS Overview**

This chapter provides a general overview of VORTOS by describing its three main parts involved in its operation: the components, the virtual machine, and the recompiler sub-system. Section 3.1 describes the components that provide the operating system functionality to the applications. Section 3.2 explains the virtual machine that these components run on top of. Section 3.3 describes the translation mechanism used to compile the components into compatible virtual machine code.

#### **3.1** Components

VORTOS is a purely component-based operating system. All functionality, including memory management, multitasking, and context switching, which are traditionally included in the kernel, are contained in components. Components contain header information, executable instructions, and data. Component functionality is described in general terms to VORTOS by means of the class code, type code, and implementation code associated with each component. The class code indicates the general functional class of the object, for example, a class code of 'fsys' indicates that a component is a file system and a class code of 'memm' indicates the component is a memory management component. There are five basic class codes defined within VORTOS as shown in Table 3.1.1.

| Component Name         | Class Code |  |  |

|------------------------|------------|--|--|

| Loader                 | 'load'     |  |  |

| Scheduler              | 'sche'     |  |  |

| Memory Manager         | 'memm'     |  |  |

| Disk Driver            | 'ddrv'     |  |  |

| Filesystem             | 'fsys'     |  |  |

| File Storage Component | 'stor'     |  |  |

Table 3.1.1: Common Class Codes

The type code indicates the functional subclass or specific type within the general functional class of a given component. For example, a type code of 'ext2' indicates that a component is an ext2 file system component, and a type code of 'page' indicates a page-based memory management component. There are eight basic type codes defined within VORTOS as shown in Table 3.1.2.

| Component Name                 | Type Code |

|--------------------------------|-----------|

| Loader                         | 'load'    |

| Scheduler                      | 'sche'    |

| Object-oriented Memory Manager | 'oomm'    |

| Page-based Memory Manager      | 'page'    |

| SCSI Driver                    | 'scsi'    |

| IDE Driver                     | 'ide '    |

| Ext2 Filesystem                | 'ext2'    |

| NTFS Filesystem                | 'ntfs'    |

| XFS Filesystem                 | 'xfs '    |

| File Storage Component         | 'stor'    |

Table 3.1.2: Common Type Codes

The implementation code contains a unique identifier for the component. It is similar to the Universal Product Code (UPC) in that it uniquely identifies the author of

the component, and allows every author to have multiple uniquely identified versions of the same component. For shared usage, these codes should be assigned by a central authority or group, similarly to the distribution of IP addresses. All of the components developed as part of this thesis have an implementation code of zero.

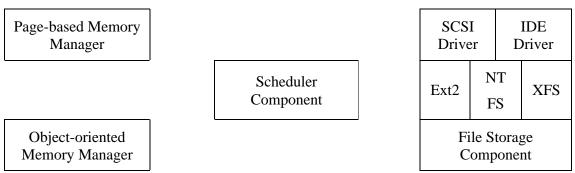

Figure 3.1.3: Some Example Components

Figure 3.1.3 provides some example components and Table 3.1.4 shows their associated class codes, type codes, and implementation codes.

| Table 3.1.4: Example Codes     |            |           |                     |  |  |

|--------------------------------|------------|-----------|---------------------|--|--|

| Component Name                 | Class Code | Type Code | Implementation Code |  |  |

| Page-based Memory Manager      | 'memm'     | 'page'    | 0x0000000           |  |  |

| Object-oriented Memory Manager | 'memm'     | 'oomm'    | 0x0000000           |  |  |

| Scheduler                      | 'sche'     | 'sche'    | 0x0000000           |  |  |

| SCSI Driver                    | 'ddrv'     | 'scsi'    | 0x0000000           |  |  |

| IDE Driver                     | 'ddrv'     | 'ide '    | 0x0000000           |  |  |

| Ext2 Filesystem                | 'fsys'     | 'ext2'    | 0x0000000           |  |  |

| NTFS Filesystem                | 'fsys'     | 'ntfs'    | 0x0000000           |  |  |

| XFS Filesystem                 | 'fsys'     | 'xfs '    | 0x0000000           |  |  |

| File Storage Component         | 'stor'     | 'stor'    | 0x0000000           |  |  |

A component can have any number of entry points to its code, and each entry point has a specific message code associated with it. Message codes are publicly defined codes that allow components to be called by others. Each component with a given class code shares at least a common subset of message codes. Each component with a given class code and type code will generally share most or all of the same message codes. These message codes are discussed in more detail in Chapter 5.

The most central component is the loader component. The loader component loads into memory the components necessary for operation and coordinates and keeps track of all of the components currently available and loaded. Other components can query the loader component for information about the components in the system and can also call on it to load and unload components as needed. The loader component is discussed in more detail in Chapter 6.

Additional commonly required components for useful functionality of VORTOS include a memory management component, a scheduler component, a networking component, and a persistent storage component. A memory management component provides the essential memory allocation and organization functionality. A scheduler component can allow custom scheduling of processor time between processes by assigning and modifying the relative priority levels of running processes and rescheduling them. Networking components can provide both connection-oriented and connectionless transactions over the network. A persistent storage component can load the appropriate file system component to access data saved on a hard disk.

30

All of these components run in their own user-level address-space, so that if one component crashes, it can be killed or reloaded as appropriate without bringing down the rest of the system. This also allows the "hot-swapping" of components when desired. Since the core parts of a traditional kernel are all implemented within components, even these parts of the operating system receive the benefits of this protection. If the memory manager somehow accesses an invalid address and triggers a memory protection fault, the virtual machine will notify the scheduler, which will restart the memory management component.

### **3.2** Virtual Machine

All components run on top of a virtual machine that provides inter-component messaging facilities. The virtual machine can be viewed as a very simple kernel, somewhat similar to the kernel in the Cache Kernel [8] or Exokernel [7] systems. Each task is assigned a dynamic priority level by the operating system. A component may have several corresponding tasks. The virtual machine executes tasks in a round-robin fashion among those tasks with the highest priority. The scheduler component adjusts these priorities as necessary and helps ensure that real-time tasks meet their deadlines. The virtual machine also dispatches messages to components and vectors interrupts and exceptions to the appropriate components. A unique identification number assigned by the loader component when a component is first loaded identifies the target component of a message.

By using a virtual machine, VORTOS components can run on a wide variety of platforms, and even from within other operating systems, without modification. Only the virtual machine implementation itself needs to be ported, and since it is an extremely simple virtual machine with a simple instruction set as described in Chapter 4, it can be easily ported to virtually any hardware or software platform, even those with minimal resources such as embedded systems.

The virtual machine contains a built-in debugger that can be used to pause and step through execution of PVMF instructions. Also it can display and disassemble instructions and data in memory, and display the contents of all of the registers of the virtual machine. The low-level facilities of the debugger make it easier to diagnose and debug even very fundamental components of the operating system.

### 3.3 Recompiler Sub-system

VORTOS includes a recompiler sub-system that translates instructions from foreign instruction set architectures to the PVMF instructions. The recompiler is not part of the operating system itself, but is used for translating code during software development. It allows code to be developed on existing platforms, alleviating the need for a VORTOS-specific compiler. The recompiler reads in the compiled instructions from the code generated by the foreign compiler one by one and replaces each one with the corresponding PVMF instructions. Since the assumptions made by foreign processors are different from those made by the VORTOS virtual machine, several extra control instructions are sometimes necessary for a single foreign instruction. Sometimes it may be necessary to save values stored in registers in foreign code on the stack temporarily in PVMF code if there are not enough registers available. On the flip side, frequently accessed variables currently stored on the stack in the foreign code can be stored in registers in the PVMF code as an optimization when there are extra registers available. Additionally, memory references need to be offset by the proper amounts to contain their proper values in the generated PVMF code. The recompiler sub-system is described in more detail in Chapter 7.

### **Chapter 4**

### **Virtual Machine Architecture**

This chapter details the general architecture of the 32-bit Portable Virtual Machine Format (PVMF-32) virtual machine. Section 4.1 describes the memory address model and architecture of the virtual machine itself. Section 4.2 describes the PVMF-32 instruction set. Section 4.3 explains the interrupt architecture used by the virtual machine. The exception model is detailed in Section 4.4. Section 4.5 describes the multitasking model. Section 4.6 describes the debugger built into the virtual machine. Section 4.7 provides an analysis of the design features of the virtual machine.

#### 4.1 **PVMF-32 Overview**

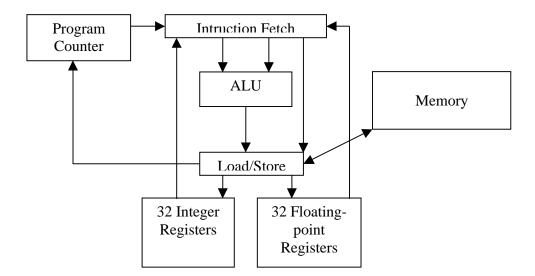

The PVMF-32 virtual machine is a virtual 32-bit processor with a very simple RISC-like instruction set. The PVMF-32 is register-based, with a 32-bit address space. PVMF-32 has 16 primitive operations that operate on some combination of integer registers, floating-point registers, and 16-bit constant values. An architectural diagram of the virtual machine is shown in Figure 4.1.1.

Figure 4.1.1: The Virtual Machine

The virtual machine has 31 general-purpose 32-bit integer registers named r0-r30 and 31 general-purpose 64-bit floating-point registers named fpr0-fpr30. Each of the 64-bit floating-point registers conforms to the IEEE 754 standard for double-precision floating-point numbers. An additional integer register (r31) and an additional floating-point register (fpr31) always contain a value of zero. The current implementation of the virtual machine uses the 32-bit integer register (r30) as a pointer to the base of the current stack. The virtual machine operates solely in big-endian mode.

#### Root node of memory map

|                                   | 0x1000  | Physical memory block start address               |  |  |

|-----------------------------------|---------|---------------------------------------------------|--|--|

| 4096 Physical memory block length |         |                                                   |  |  |

|                                   | r,w     | Permissions on memory block                       |  |  |

|                                   | /0x1000 | Start address of block in component address space |  |  |

| /                                 | 0x2000  | End address of block in component address space   |  |  |

Address map of memory

above 0x2000 in component

Address map of memory below 0x1000 in component address space

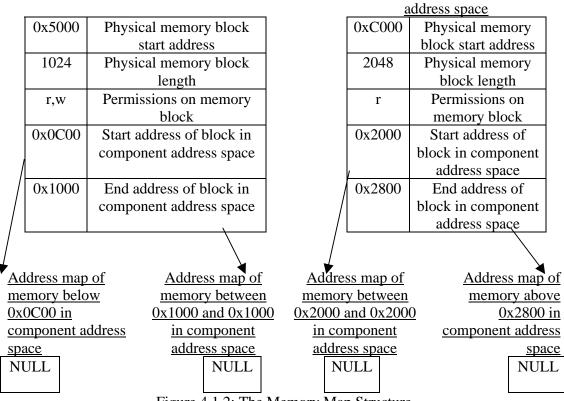

Figure 4.1.2: The Memory Map Structure

The PVMF-32 virtual machine uses a 32-bit object oriented memory addressing model. Each component has its own address space and a memory map structure associated with it. When execution is in a component's address space, its memory map is used for all memory references during execution. The memory map structure is a binary

tree structure used to hierarchically partition an address space as shown in Figure 4.1.2. Figure 4.1.2 shows a memory map that maps data from various discontiguous physical memory blocks of various sizes into one continuous memory block from 0x0C00 to 0x2800 in the component's address space. Each node in the memory map contains the starting and ending addresses in the component's address space that the node corresponds to, the size and location in physical memory of the actual data, and the read, write, and execute permissions on that data block. Each node can have a unique size and permissions. The addresses in the component address space do not have to be continuous.

When a memory address in the component's address space is accessed, this address is compared to the start and end component address space values in the root node of the memory map. If the accessed address is between these start and end values, this node is used to map the address to a physical address. If the accessed address is less than the start address in this node, the same process is repeated on the left child node, and if the access address is greater than the end address in this node, this process is repeated on the right child node. If a NULL node is reached or the permission value on the appropriate node does not allow the attempted form of memory access, a memory access exception is thrown.

Each component has separate memory map structures for code and data references. The code memory map is used for translating address references in branch instructions, while the data memory map is used to translate address references during load and store instructions. The current implementation assumes that the code memory map only contains a single node, for efficiency purposes. Upon startup, the virtual machine starts by clearing all values in all registers to zero and loading a ram image from disk. The ram image contains the initial state of all memory in the virtual machine, including the initial code to run. The virtual machine sets up the interrupt queue and installs a generic timer interrupt handler that generates a rescheduling message. The virtual machine then sets up the stack and memory map structures for the initial thread and starts executing instructions sequentially at the program counter. Since the program counter is zero at initialization time, this means the execution begins with the instruction at memory address zero. In most cases, this will be the code for the loader component described in Section 6.1.

#### 4.2 Instruction Set

The primitive instructions of the PVMF-32 virtual machine include addition, subtraction, multiplication, division, bitwise-AND, bitwise-OR, bitwise-XOR, bitwiserotation, loading a register from memory, storing a register in memory, absolute and relative conditional branching, and comparison instructions. Table A.1 in Appendix A lists all of the PVMF-32 instructions, their assembly mnemonics, and their effects. In The following notation is used to describe the instructions: rX represents an integer register, fprX represents a floating-point register, CONST represents a 16-bit integer constant, and PC is the current address the virtual machine is executing. Note that 16-bit integer constants are used for both floating-point and integer instructions.

| OpCode   | Res-  | Register | Register | Reserved | Register |

|----------|-------|----------|----------|----------|----------|

| (8 bits) | erved | First    | Result   | (6 bits) | Second   |

|          | (3    | Argument | (5 bits) |          | Argument |

|          | bits) | (5 bits) |          |          | (5 bits) |

**Register-based instruction**

#### Immediate Instruction

| OpCode   | Register | Register             | Constant Second Argument |

|----------|----------|----------------------|--------------------------|

| (6 bits) | Result   | First                | (16 bits)                |

|          | (5 bits) | Argument<br>(5 bits) |                          |

Figure 4.2.1: Instruction Formats

Figure 4.2.1 shows the two different formats of instructions. The first argument to an instruction and the result are always registers, while the second argument can either be a register or a 16-bit constant depending on which format the instruction is in. Register-based instructions have an extra two bits in their opcodes, so some of the entries in the hash table of the virtual machine jump to the code to execute the same immediate instructions.

There are two special instructions for message passing. These instructions are called by components to interact with other components. The only ways components interact are through one of these two instructions, Send Message or Fork Message. Each type of component has a number of well-defined message codes that can be passed in a register to the message instruction to indicate to the virtual machine which function of a component to jump to. Another register contains the local identification number of the component to send the message to. The versatility of the message passing instructions is explored in detail in Section 5.

The Send Message instruction calls the message in the object indicated by the values in the registers used as arguments for the Send Message instruction. This instruction transfers control of the processor to the function with the specified message code in the specified object, until a return message is sent to object ID 0. The virtual machine intercepts all return messages to object ID 0 and returns control of execution to the original caller at the instruction just after the Send Message instruction. The result of the message call is placed in the register specified in the Send Message instruction's final argument.

The Fork Message instruction performs the same actions as the Send Message instruction. However, instead of transferring control to the destination object, a new thread is created which begins execution at the function with the specified message code in the destination object. This new thread executes simultaneously at the same priority level as the original thread, while the original thread continues to execute the instructions following the Fork Message instruction without waiting for a result from the called object.

### 4.3 Interrupts

Components can send messages to the loader to register and remove interrupt handlers. The loader maintains a list of all currently registered interrupt handlers. When an interrupt occurs, the virtual machine saves the information passed to its generic interrupt handler in a queue. Adding new entries to the queue is done in such a way to place a very small hard upper bound on the amount of time spent adding entries to the queue, at the expense of possibly losing interrupts if they are not handled quickly enough. Since hardware can only store a fixed number of interrupts at a time, this is a danger in any case, so this is unlikely to be a problem in practice.

Between instructions, when the virtual machine is in a synchronized and welldefined state, the queue is emptied and for each of the entries in the queue, the virtual machine sends a message to each component that has an interrupt handler registered for the interrupt that created that entry. These messages are sent using the same mechanism described for the Fork Message instruction in Section 4.2 so that they can be processed in parallel with each other and other ongoing processes. However, the newly spawned threads for forking these new messages to the appropriate components are given a special high priority value, so that they will get processed before further execution. In most cases, this means that these interrupts will all be handled completely before the rest of the processes resume execution, unless the interrupt handlers block, in which case other processes will continue execution normally as long as there is no higher priority process active.

### 4.4 Exception Handling

The exception handling mechanism for the virtual machine is fairly simple. The virtual machine inserts a special exception handler to be called by the underlying hardware the virtual machine is running on whenever a hardware exception occurs. An exception is also thrown if code running on the virtual machine attempts to execute an illegal instruction or access memory out of bounds. When the exception handler is called, it sets a boolean flag in the virtual machine's global memory space. Setting this flag when it is already set has no effect, so that redundant exceptions are not generated by

the code that generated an exception before the initial exception is handled. The virtual machine periodically checks to see if the flag is set and if it is, it sets another flag and transfers execution to the exception handling message in the component that generated the exception. If the second flag is already set or if that component has no exception handling message, control is transferred to a routine in the loader to forcibly unload the offending component. These checks only occur at safe points in between instructions, so that the virtual machine will not be left in an invalid or unsynchronized state when control is transferred.

### 4.5 Threads

The virtual machine allows multiple threads of execution to run simultaneously. Each thread has a positive numerical priority associated with it. All ready threads with the highest priority level are rotated through in a round-robin fashion. Every tenth of a second, the virtual machine suspends the current thread and register context and loads the thread and context with the highest priority. This interval can be changed as desired by the operating system. If multiple threads have the same priority, and it is the highest priority of any active thread, the thread with the highest priority that has not run for the longest time interval is loaded. The tenth of a second timer is then reset and control of the processor is transferred to the newly loaded thread. When the virtual machine starts, it loads a special thread called the idle thread. The idle thread does nothing but continuously loop. It has a priority of zero, the lowest priority of any thread, so that it will only execute when no other threads are active. Using an idle thread simplifies the scheduling algorithm since it ensures that at least one thread is always ready to run. Each thread has a dynamically resizable stack associated with it. Local data such as stack frames for functions and local variables can be stored on this stack.

|                    | 0xFC  | VAddress   | return | stack pointer |

|--------------------|-------|------------|--------|---------------|

|                    | 0xF8  | VAddress   | return | stack base    |

|                    | 0xF4  | VAddress   | return | code offset   |

|                    | 0xF0  | VAddress   | return | objectID      |

| stack base addr -> | 0xEC  | local stac | k data |               |

|                    | 0xE8  | local stac | k data |               |

| stack pointer ->   | 0xE4  | local stac | k data |               |

| <b>-</b>           | 4 5 1 |            | r      |               |

Figure 4.5.1: Stack Layout in Memory

The layout of the stack is shown in Figure 4.5.1. The current implementation uses register r30 for the stack pointer and register r29 for the stack base address. The base address will always be higher than the stack pointer, because the stack grows downwards. When a message instruction occurs, the virtual machine saves the current stack pointer, stack base address, the address of the following instruction, and the calling object's ID number on the stack. The stack base is set to the address of the current stack pointer after all this information has been stored on the stack. The data address space of the called object is modified to include the new stack, starting from the new stack base. If stack space is running low, this can be used to continue the stack in another portion of memory by storing the stack's information in the new portion of memory rather than right on the current stack, then updating the stack pointer and base and to point to the new portion of

memory, right below the stored information. The new object will normally not have

access to any of the stack information from the calling object.

## 4.6 Debugger

This implementation of the virtual machine includes a built-in debugger for tracing problems during program and operating system development. The virtual machine can display windows showing the current values of every register for each CPU currently executing.

|                  | Registers - CPU           | J#0                |      |

|------------------|---------------------------|--------------------|------|

| PC = 0x0001620C  |                           |                    |      |

| R00 = 0×00000000 | R16 = 0×00000000          | FPR00 = 0×00000000 | FPB1 |

| R01 = 0×00000000 | R17 = 0×00000000          | FPR01 = 0×00000000 | FPR1 |

| R02 = 0×00000000 | R18 = 0×00000000          | FPR02 = 0×00000000 | FPR1 |

| R03 = 0×00000000 | R19 = 0×00000000          | FPR03 = 0×00000000 | FPR1 |

| R04 = 0×00000000 | $R20 = 0 \times 00000000$ | FPR04 = 0×00000000 | FPR2 |

| R05 = 0×00000000 | R21 = 0×00000000          | FPR05 = 0×00000000 | FPR2 |

| R06 = 0×00000000 | $R22 = 0 \times 00000000$ | FPR06 = 0×00000000 | FPR2 |

| R07 = 0×00000000 | $R23 = 0 \times 00000000$ | FPR07 = 0×00000000 | FPR2 |

| R08 = 0×00000000 | $R24 = 0 \times 00000000$ | FPR08 = 0×00000000 | FPR2 |

| R09 = 0×00000000 | $R25 = 0 \times 00000000$ | FPR09 = 0×00000000 | FPR2 |

| R10 = 0×00000000 | $R26 = 0 \times 00000000$ | FPR10 = 0×00000000 | FPR2 |

| R11 = 0×00000000 | R27 = 0×00000000          | FPR11 = 0×00000000 | FPR2 |

| R12 = 0×00000000 | $R28 = 0 \times 00000000$ | FPR12 = 0×00000000 | FPR2 |

| R13 = 0×00000000 | $R29 = 0 \times 00000000$ | FPR13 = 0×00000000 | FPR2 |

| R14 = 0×00000000 | $R30 = 0 \times 00000000$ | FPR14 = 0×00000000 | FPR3 |

| R15 = 0×00000000 | R31 = 0×00000000          | FPR15 = 0×00000000 | FPR3 |

Figure 4.6.1: Virtual Machine Register Window

When the value of a register changes, that register is briefly highlighted in red as shown with the program counter in Figure 4.6.1 to provide visual feedback when registers are modified. The state of the virtual machine's RAM can be examined in a hex dump as seen in Figure 4.6.2.

|            |          | Hex      | C Dump   |          | P          | ]日  |

|------------|----------|----------|----------|----------|------------|-----|

| 0×00000000 | 141F7400 | B4000010 | 60220000 | 60830003 | 00t¥0`"`É0 |     |

| 0×00000010 | 64A26E00 | 00000000 | 00000000 | 00000000 | d¢n        | =   |

| 0×00000020 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×00000030 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×00000040 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×00000050 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×00000060 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×00000070 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×00000080 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×00000090 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×000000A0 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×000000B0 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×000000C0 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×000000D0 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×000000E0 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×000000F0 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×00000100 | 00000000 | 00000000 | 00000000 | 00000000 |            |     |

| 0×00000110 | 00000000 | 00000000 | 00000000 | 00000000 |            | •   |

| 0×00000120 | 00000000 | 00000000 | 00000000 | 00000000 |            | 111 |

Figure 4.6.2: Hexadecimal Dump of Virtual Machine RAM

The user can either execute instructions continuously or halt execution and step through one instruction at a time on command. The currently executing instruction is marked in the disassembly window. This window, shown in Figure 4.6.3, provides a disassembly of the RAM using the assembly mnemonics listed in Appendix A.

| ]        | C    | )isassembly - CPU# | 0        | E    |

|----------|------|--------------------|----------|------|

| 00000000 | adde | r31,0x7400,r0      | 141F7400 |      |

| 00000004 | rote | r0,0x0010,r0       | B4000010 | =    |

| 00000008 | or   | r2,r0,r1           | 60220000 |      |

| 0000000C | or   | r3,r3,r4           | 60830003 | - 11 |

| 00000010 | ore  | r2,0x6E00,r5       | 64A26E00 | - 11 |

| 00000014 | nop  |                    | 00000000 | - 11 |

| 00000018 | nop  |                    | 00000000 | - 11 |

| 0000001C | nop  |                    | 00000000 | - 11 |

| 00000020 | nop  |                    | 00000000 | - 11 |

| 00000024 | nop  |                    | 00000000 | - 11 |

| 00000028 | nop  |                    | 00000000 | - 11 |

| 0000002C | nop  |                    | 00000000 | - 83 |

| 00000030 | nop  |                    | 00000000 | 100  |

| 00000034 | nop  |                    | 00000000 |      |

| 00000038 | nop  |                    | 00000000 |      |

Figure 4.6.3: Virtual Machine RAM Disassembly

#### 4.7 Design Analysis

By using a virtual machine, VORTOS components can run on a wide variety of platforms, and even from within other operating systems, without modification. Only the virtual machine implementation itself needs to be ported, and since it is an extremely simple virtual machine with a simple instruction set, it can easily be ported to virtually any hardware or software platform, even those with minimal resources.

Keeping the virtual machine instruction set small and simple also keeps the footprint of the virtual machine small. The low-level, register-based architecture of the virtual machine avoids the overhead commonly incurred by higher levels of abstraction. The simple RISC-style instruction set provides low-level primitives that can be efficiently implemented on any modern hardware processor. This is particularly important for embedded systems with limited hardware resources available. Furthermore, these low-level primitives do not constrain higher level applications, since they only perform the basic arithmetic functions. Higher level abstractions often limit functionality and performance because they constrain data representations to a given form. Data and programs that do not fit the artificially constructed abstractions well may be awkward to implement and less efficient. The design impact of the special messaging instructions is explored more fully in Chapter 5.

The PVMF-32 virtual machine is a 32-bit processor. Since most modern microprocessors use either 32 or 64 bit registers and addressing, most processors should be able to handle the 32-bit virtual machine quite naturally. At the same time, since most embedded processors currently in use have 32 bit registers and addressing, using a 64-bit virtual machine would unnecessarily increase the size of the system. Since few

embedded systems have more than the four gigabytes of memory addressable by a 32-bit processor anyway, requiring them all to use 64-bit addressing would just be a waste of space or processing power. Furthermore, the architecture of the virtual machine and operating system is portable enough that a 64-bit virtual machine could be implemented if desired. PVMF-32 code could be translated to run on a 64-bit virtual machine with little difficulty using methods similar to those described in Chapter 7.

Using 64-bit floating-point registers that conform to the IEEE 754 doubleprecision standard was a logical choice, since this format is commonly used among modern floating-point processors and can be emulated using multiple 32-bit registers if necessary. 16-bit integer constants are used with both integer and floating-point instructions, since 16-bits is enough space to represent many common integral values but most floating-point numbers that are not integers require more than 16 bits of precision. Immediate instructions and register-based instructions have different formats to accommodate the 16-bit arguments used by immediate instructions. Two of these bits are used by register-based instructions to further differentiate between instructions, allowing additional register-based instructions.

The virtual machine runs in big-endian mode. This means it works well with bigendian processors, but it will also work with little-endian processors. However, littleendian implementations of the virtual machine will need to swap the byte order of words from memory after every load and before every store instruction. This may cause a very small performance overhead to be incurred on little-endian machines. Note however, that little-endian processors face a similar situation when transmitting data over most networks, since TCP/IP stores data in big-endian byte order.

48

Since each component has its own code and data address spaces, the virtual machine can easily enforce per-component memory isolation, to prevent one component from illegally writing to the memory of another. The ability to map memory to a component's address space arbitrarily allows more flexibility in implementing memory allocation schemes, since memory blocks can be discontinuous and scattered throughout memory in any arbitrary fashion. Furthermore, since these addresses are virtual addresses, the memory manager can perform defragmentation of memory blocks transparently to the application. Components can explicitly share portions of their memory space with other components by sending the appropriate messages to the memory management component, which will then map the given memory ranges to the address spaces of the additional components. Using shared memory allows fast data transfer between components, but since memory must be explicitly shared illegal accesses will still be detected. Having separate code and data address spaces allows code addresses to be marked as executable but not writable or readable, increasing stability and security by protecting loaded code from malicious or accidental modification. The assumption that the code address space is continuous both in the address space and in memory was an optimization that improves the performance of the virtual machine without placing undue constraints on the software, since situations requiring arbitrary mapping of the code of simple components are rare since shared objects are accessed entirely through the messaging instructions. It also places an upper-bound on the amount of time necessary to fetch instructions from memory. This is important for systems that require real-time performance. To provide a similar upper-bound on loads and stores to

and from the data address space requires limiting the depth of the data memory map tree, which can be done on a per-component basis by the developer of a component.

The interrupt architecture provides a simple, generic interface for interrupts that does not disrupt the operating of real-time processes with arbitrary interrupt handlers. At the same time, the queuing of messages at interrupt time provides a flexible dispatch mechanism that allows drivers to execute safely and securely in user-mode. Therefore, errors in drivers can be contained from the rest of the system and drivers can be easily dynamically loaded and hot-swapped. Since exception handling uses the same mechanism, these advantages apply to hardware exceptions as well as interrupts.

The threading model employs a simple low-cost scheduling algorithm that can be used to implement more sophisticated scheduling algorithms. Real-time processes can be given a higher priority than other processes to help them meet their timing constraints. The stack architecture isolates stack frames of functions across components, which provides a higher level of stability. Even if a component corrupts its stack space, the stack of the calling object will be unaffected. This also prevents common security problems associated with stack buffer overflows, since the called object cannot access the return address stored on the stack. Furthermore, since the code address space does not include the stack, executable code cannot be stored on the stack. Although this may cause some problems with very machine-specific self-modifying code, it should not impact most applications and provides added security and stability benefits.

The debugger built into the virtual machine provides useful feedback for development and allows step-by-step execution, monitoring, and debugging even of the lowest-level components of the operating system.

# Chapter 5

# **Component Architecture**

This chapter discusses the component architecture of VORTOS and describes the way components interact through messaging. The general nature of the component-oriented messaging system provides a huge amount of flexibility. Section 5.1 describes the structure of components and their characteristics. Section 5.2 describes the messaging architecture. Section 5.3 discusses the ramifications and consequences of the component-oriented messaging approach.

### 5.1 Component Structure

Components are objects containing code and data, just like executable files for any modern architecture. The data organization of each component in memory or storage begins with a header that contains information about how the component is used. The header is followed by a code and data section as shown in Figure 5.1.1.

| Offset     | Field                | Data Type                 |

|------------|----------------------|---------------------------|

| 0x0000     | objected             | 32-bit unsigned integer   |

| 0x0004     | codeOffset           | 32-bit unsigned integer   |

| 0x0008     | dataOffset           | 32-bit unsigned integer   |

| 0x000C     | codeLength           | 32-bit unsigned integer   |

| 0x0010     | dataLength           | 32-bit unsigned integer   |

| 0x0014     | size                 | 32-bit unsigned integer   |

| 0x0018     | classCode            | 32-bit unsigned integer   |

| 0x001C     | typeCode             | 32-bit unsigned integer   |

| 0x0020     | implementationCode   | 32-bit unsigned integer   |

| 0x0024     | attributes           | 32-bit unsigned integer   |

| 0x0028     | instance             | 32-bit unsigned integer   |

| 0x002C     | createdBy            | 32-bit unsigned integer   |

| 0x0030     | instructionMap       | Memory Map Node (See      |

|            |                      | Section 4.1)              |

| 0x0048     | dataMap              | Memory Map Node (See      |

|            |                      | Section 4.1)              |

| 0x0060     | Message Offset Table | Array of [32-bit unsigned |

|            | msgCode1 offset1     | integer, 32-bit unsigned  |

|            | msgCode2 offset2     | integer]                  |

|            | msgCode3 offset3     |                           |

|            | 0x0000000 0x0000000  |                           |

|            |                      |                           |

| codeOffset | instruction list     | Array of 32-bit unsigned  |

|            |                      | integers                  |

|            |                      |                           |

| dataOffset | Arbitrary data block | arbitrary data block      |

|            |                      |                           |

|            |                      |                           |

|            |                      |                           |

| Figure 5.1 | .1: Component | Structure |

|------------|---------------|-----------|

|------------|---------------|-----------|

Each component has an object ID assigned to it when it is loaded into memory. The *objectID* field is updated to contain this value when the component is loaded. The *codeOffset* and *dataOffset* fields indicate the offsets from the beginning of the header to the start of the code and data sections of the component, respectively. Similarly, the *codeLength* and *dataLength* fields indicate the lengths of these sections.

The *size* field indicates the total size of the component, including the header. The *classCode*, *typeCode*, and *implementationCode* fields indicate the class code, type code, and implementation codes of the component, respectively, as defined in Section 3.1. The *attributes* field is reserved for future use and is intended to indicate that a component possesses certain attributes.

The *instance* field is instantiated with the component is loaded into active memory. Its value is the number of other components with the same *typeCode* currently active at the time the component is started. The *createdBy* field contains the object ID of the object that made the call to load this component into active memory. The *instructionMap* and *dataMap* fields contain the code address space and data address space maps, respectively, as described in Section 4.1.

At the end of the component's header is the *message offset table*, which contains an array of paired 32-bit unsigned integers containing a list of message codes and the corresponding offsets in the component to jump to when those messages occur. These message codes are similar to class and type codes in that their values correspond to ASCII strings that indicate their purpose, such as 'open' for the open component message. The end of the *message offset table* is indicated by a pair of zero entries in the table, since

53

a message code of zero is not valid. The code and data themselves occur at the position in the component indicated by the *codeOffset* and *dataOffset* fields, respectively.

### 5.2 Component Messaging

Components interact with each other solely through a simple message passing protocol, using the Send Message and Fork Message instructions described in Section 4.2. When the virtual machine executes a message instruction, it looks through the *message offset table* in the header of the object with the object ID passed as an argument to the message instruction. In the current implementation, the object ID assigned to an object is the address of the beginning of that object's header in memory. The virtual machine sequentially scans each entry in the *message offset table* until it finds the message code passed as an argument to the message instruction, then jumps to the corresponding offset listed in the *message offset table*. If the target object is called instead. This allows components control over what happens when an unknown message code is received. If the target object does not have a 'deft' message, the virtual machine sends a "Not Supported" message with message code 'nots' to the calling object instead. If the calling object does not have a 'nots' message, the virtual machine throws an exception by sending an "Exception" message with message code 'acpt' to the loader.

The same message code can have different meanings for different class codes. This allows the author of a new class to define message codes as desired. The message codes for the components included in the operating system are described along with those components in Chapter 6. New message codes may be added as needed. All messages are dispatched to the correct destination by the virtual machine, allowing messages to be routed to alternate components when desirable. Since messages are the only form of communication between components, this allows a wide range of flexibility in the use of components and application-specific components. For example, a process with a complex memory management scheme can use its own memory management component instead of using the default system memory management policy by sending messages to its custom memory management component instead of the default system component. This allows greater efficiency for applications that wish to do their own memory allocation. However, this places no additional requirements on other applications, since they can always use the system's memory management policy by default. The preferred components for a given function, such as memory management or task scheduling can also be specified on a per-application basis if desired, allowing great flexibility to users and developers alike.

This general message-passing system also allows one or more filters to be applied to components by redirecting the messages for a target component to a filter component by assigning the target object's ID to the filter instead. The filter component can supply a 'deft' message that passes any message not specified in the filter on to the target object while allowing the filter to monitor or modify the arguments or destroy the message as desired. Furthermore, individual message functions in the filter can provide "wrapper" functionality, such as a compression filter that automatically compresses the data sent to it with a "write" message before passing the data to the target object and automatically decompresses data received from the target object with a "read" message before returning it to the caller. This allows the compression filter to be applied to any component that reads and writes data with a "read" and "write" message and automatically provides transparent compression to the target component without any modification. This also allows the implementation of a simple form of inheritance, where the messages defined in the filter "override" those of the component the filter is intercepting messages for.

In addition, components can be swapped in and out of the system at run-time without the need for complex initialization and shutdown procedures by simply routing the messages to the new component. This rerouting is accomplished by simple assigning the new component the object ID of the old component. This is particularly useful for embedded systems, which often require high system availability.

### 5.3 Design Analysis

By isolating code modules into components and adopting a uniform messagepassing model, VORTOS makes it simple to distribute components across processors, both locally and across a network. Since components are simply pieces of PVMF code on the virtual machine, components can even migrate across a heterogeneous network to a remote system of a different architecture. This means that VORTOS can be run as a truly distributed operating system, and will easily scale up to large heterogeneous networks of computer systems. By adding an ORB component to the system, components can be exported quite naturally as CORBA objects, allowing interoperability with a wide range of existing networked systems.

This component architecture also makes it simple to scale downwards to embedded systems and microcontrollers. When space is at a premium, only the essential components, such as memory management and scheduling, need to be loaded or included with the system. An embedded system with no need for a graphic subsystem can leave out all the graphical components. If specific functionality is required, the necessary components can be included in the system. For example, a cell phone's processor may need to send data over a wireless network. The wireless driver component and some networking components could be included to provide this functionality, but since a cell phone has no hard drive, file system components are unnecessary and can be left out, making the total footprint of the system smaller, which is important on a cellular phone with a very limited memory.

The ability to reroute messages to components and to use filter components is a very powerful feature of VORTOS. The "Not Supported" message allows components to provide their own recovery functions rather than being arbitrarily killed for making an invalid external call. The "Default" message provides a way to handle unexpected or unknown messages and allows the easy implementation of filter components that can be applied to a target component without knowing all of the internal details of the target component. This architecture allows the implementation of components that can automatically encrypt or compress data sent to the filtered components. Even messages such as the "Exception" message could be intercepted by a filter component that, for example, logs all exceptions to a file. This also allows hot-swappable components, redundant components that provide insulation against failure, and components that apply only in certain contextual situations, such as only for certain users or only allow a certain amount of data to pass through them before they shutdown for security or bandwidth reasons.

57

# **Chapter 6**

## **Basic Components**

VORTOS itself is a collection of components running on top of the virtual machine. The components in that collection can be customized to fit the needs of the user. However, there is a default set of core components that create a functional system. The Loader component described in Section 6.1 loads and manages the operating system and the components. The Task Scheduler described in Section 6.2 coordinates and provides information about processes. The Memory Manager described in Section 6.3 is responsible for allocating and managing memory for processes.

#### 6.1 Loader

The primary component of VORTOS is the loader component. It has a class code and type code of 'load'. The loader component provides the code necessary to initialize and load the operating system and the key components at boot time. It is also used to load and make queries about components. These queries include obtaining the identification number of a particular component through the 'getc' message code. The loader maintains a list of all current instantiations of components.