#### Monolithic Heteroepitaxial Integration of III-V Semiconductor Lasers on Si Substrates

by Michael Edward Groenert

B.S. with Highest Honors in Physics College of William and Mary, 1996

Submitted to the Department of Materials Science and Engineering in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electronic Materials

at the Massachusetts Institute of Technology

September 2002

© 2002 Massachusetts Institute of Technology All rights reserved.

Signature of Author:

Department of Materials Science and Engineering Aug. 9, 2002

Certified by:

Eugene A. Fitzgerald Professor of Materials Science and Engineering Thesis Supervisor

Accepted by:

Harry L. Tuller Professor of Ceramics and Electronic Materials Chair, Departmental Committee on Graduate Students

#### Monolithic Heteroepitaxial Integration of III-V Semiconductor Lasers on Si Substrates

by

#### Michael Edward Groenert

Submitted to the Department of Materials Science and Engineering on August 9, 2002 in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electronic Materials

#### ABSTRACT

Monolithic optoelectronic integration on silicon-based integrated circuits has to date been limited to date by the large material differences between silicon (Si) and the direct-bandgap GaAs compounds from which optoelectronic components are fabricated. Graded Ge/GeSi buffer layers grown on standard Si substrates have been shown to produce near-lattice matched virtual substrates for GaAs integration on Si. This study investigated the crystal growth conditions and device fabrication techniques necessary for successful GaAs-based laser integration on Ge/GeSi buffer layers on Si substrates.

The nucleation conditions for GaAs on Ge/GeSi/Si substrates have been comprehensively examined. High-temperature ( $\geq$  700 °C) initiation with properly chosen V/III gas flow ratio yields high-quality, stacking fault-free GaAs films on Ge/GeSi/Si substrates, but also encourages the vapor-phase transport of Ge from the substrate into the active regions of integrated GaAs devices. A new two-step GaAs nucleation process was developed that enabled the first demonstration of high-quality Gefree GaAs light-emitting diodes on Ge/GeSi/Si substrates.

The large thermal expansion mismatch between Si, Ge, and GaAs introduces additional strain to integrated device layers on Ge/GeSi/Si substrates grown at high temperatures. This study conclusively demonstrated the link between thermal mismatch strain and increased misfit dislocation formation in  $In_xGa_{(1-x)}As/GaAs$  quantum well structures integrated on Ge/GeSi/Si substrates. The thermal mismatch strain was successfully countered by the introduction of compressive InGaAs graded buffer layers above the Ge/GeSi/Si substrate surface, and strain-free GaAs layers at growth temperatures suitable for laser integration have been demonstrated.

The integration of edge-emitting heterostructure lasers on Ge/GeSi/Si substrates introduces additional waveguide design issues addressed by this study. Low-index  $Al_{0.6}Ga_{0.4}As$  cladding layers, along with a graded-index separate confinement heterostructure, were introduced to reduce photon losses. Interfacial roughness transmitted from the Ge/GeSi/Si substrate was reduced with a pre-growth chemical-mechanical polishing step, and smooth mirror facets on integrated devices were fabricated by cleaving thinned lasers parallel to the substrate offcut direction.

Continuously operating edge-emitting GaAs/AlGaAs quantum well lasers on Ge/GeSi/Si substrates were demonstrated at room temperature with an operating wavelength of 858 nm. Series resistance heating in early devices was reduced by the introduction of a top-contact geometry and optimized cladding layer structure, and

improved laser diodes had a differential quantum efficiency of 40%, a threshold current density of 269 A/cm<sup>2</sup>, and a characteristic temperature of 129 K. Identical devices fabricated on GaAs substrates had similar performance characteristics. Lasers on Ge/GeSi/Si substrates fell below threshold after 4 hours of continuous operation–a dramatic improvement over early measured lifetimes of less than 20 minutes. Electroluminescence images of operating lasers taken before and after failure showed that dark line defects were present in the laser active regions after failure. Room-temperature 60 Å In<sub>0.17</sub>Ga<sub>0.83</sub>As strained quantum well lasers have also been demonstrated on Ge/GeSi/Si with an operating wavelength of 897 nm; these lasers had shorter lifetimes ( < 15 min) under continuous operation due to misfit dislocations in the strained quantum well active region.

While challenges remain for monolithic III/V optoelectronic integration on Si, it is clear that the demonstration of a successfully integrated GaAs-based laser on a Ge/GeSi/Si substrate represents a significant milestone on the path to the final goal of truly integrated high-speed optoelectronic devices and Si integrated circuits.

Thesis Supervisor: Eugene A. Fitzgerald Title: Professor of Materials Science and Engineering

### **Table of Contents**

| Acknowle         | dgements                                                                                      | 10  |

|------------------|-----------------------------------------------------------------------------------------------|-----|

| Chapter 1        | . Introduction                                                                                | 13  |

| 1.1.             | Barriers to Epitaxial III-V/Si integration                                                    | 17  |

| 1.1.1.           | Differences in Lattice Constant                                                               |     |

| 1.1.2.           | Differences in Thermal Expansion Behavior                                                     |     |

| 1.1.3.           | Differences in Crystal Structure                                                              | 27  |

| 1.2.             | Strategies for III-V/Si Integration                                                           |     |

| 1.2.1.           | Dislocation Control Strategies for Monolithic Integration                                     |     |

| 1.3.             | Relaxed Ge <sub>x</sub> Si <sub>(1-x)</sub> Graded Buffers for III-V/Si Integration           |     |

| 1.4.             | GaAs Integration on Ge/Ge <sub>x</sub> Si <sub>(1-x)</sub> Buffers on Si                      |     |

| 1.5.             | Goals and Scope of this Thesis                                                                | 38  |

| Chapter 2        |                                                                                               |     |

| 2.1.             | Introduction                                                                                  |     |

| 2.2.             | Metal-Organic Chemical Vapor Deposition                                                       |     |

| 2.3.             | Thomas Swan MOCVD Research Reactor                                                            |     |

| 2.4.             | Material Characterization                                                                     |     |

| 2.4.1.           | Surface Morphology                                                                            |     |

| 2.4.2.           | Device Structure                                                                              |     |

| 2.4.3.           | Crystallography and Strain                                                                    |     |

| 2.4.4.           | Dislocation Characterization                                                                  |     |

| 2.4.5.           | Optical Characterization                                                                      |     |

| Chapter 3        |                                                                                               |     |

| 3.1.             | Introduction                                                                                  |     |

| 3.2.             | Background: GaAs Nucleation on Ge/GeSi/Si                                                     |     |

| 3.2.1.           | Ge Substrate Surface                                                                          |     |

| 3.2.2.           | GaAs Film Alignment on a Ge Substrate Surface                                                 |     |

| 3.2.3.           | Controlling Anti-phase Boundary Formation at the GaAs/Ge Interface                            |     |

| 3.3.             | Low-Temperature Nucleation Experiments                                                        |     |

| 3.4.             | High Temperature Nucleation Experiments.                                                      |     |

| 3.5.             | Optimizing GaAs Nucleation to Control GaAs/Ge Interdiffusion and Autodoping                   |     |

| 3.6.             | Experiments to Control Autodoping in GaAs/Ge Growth                                           |     |

| 3.6.1.           | Characterizing GaAs/Ge Device Structures with Autodoping Contamination                        |     |

| 3.6.2.           | Reducing Autodoping in GaAs/Ge Device Structures                                              |     |

| 3.6.3.           | Characterizing Autodoping-free GaAs/Ge Device Structures<br>Conclusions                       |     |

| 3.7.             |                                                                                               |     |

| Chapter 4        |                                                                                               |     |

| 4.1.             | Introduction                                                                                  |     |

| 4.2.             | Background: Thermal Expansion Mismatch                                                        | 85  |

| 4.2.1.           | Theory of Critical Thickness                                                                  |     |

| 4.2.2.           | Effect of Thermal Expansion Mismatch on Critical Thickness                                    |     |

| 4.3.             | Thermal Mismatch Experiments                                                                  |     |

| 4.3.1.           | Reduced Critical Thickness on Ge/GeSi/Si Substrates                                           |     |

| 4.3.2.<br>4.3.3. | Uniform In <sub>x</sub> Al <sub>0.55</sub> Ga <sub>(0.45-x)</sub> As Buffer Layer Experiments |     |

| 4.3.3.<br>4.4.   | Graded In <sub>x</sub> Ga <sub>(1-x)</sub> As Buffer Layer Experiments<br>Conclusions         |     |

|                  |                                                                                               |     |

| Chapter 5        |                                                                                               |     |

| 5.1.             | Introduction                                                                                  |     |

| 5.2.             | Background: Laser Rate Equations                                                              |     |

| 5.3.             | Optimizing Optical Confinement                                                                |     |

| 5.3.1.<br>5.3.2. | Introduction<br>Experimental Confinement Calculations                                         |     |

| 5.3.2.<br>5.4.   | 1                                                                                             |     |

| 5.4.             | Minimizing Intrinsic Waveguide Losses                                                         | 122 |

| 5.5.      | Minimizing Mirror Cavity Loss                                   | 127 |

|-----------|-----------------------------------------------------------------|-----|

| 5.6.      | Conclusions                                                     |     |

| Chapter 6 | . Laser Integration on Ge/GeSi/Si Substrates                    | 134 |

| 6.1.      | Introduction                                                    | 135 |

| 6.2.      | Background: Direct Laser Integration on Si                      | 135 |

| 6.3.      | Experimental Procedure: Integrated Laser Growth and Fabrication |     |

| 6.4.      | Results and Discussion                                          |     |

| 6.4.1.    | GaAs Substrate Devices                                          |     |

| 6.4.2.    | Ge/GeSi/Si Substrate Devices                                    | 149 |

| 6.4.3.    | Device Lifetime Measurements                                    |     |

| 6.5.      | Conclusions                                                     | 172 |

| Chapter 7 | '. Conclusions                                                  | 174 |

| 7.1.      | Summary of Experimental Findings                                |     |

| 7.2.      | Suggestions for Future Work                                     |     |

#### References 180

## List of Figures

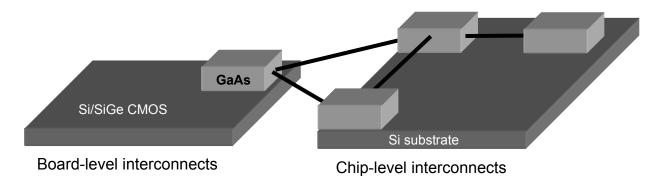

| Figure 1.1:                   | Hypothetical example of an integrated GaAs/Si optoelectronic circuit 1                                                                                                                                                                                                                                                                                             | 5  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

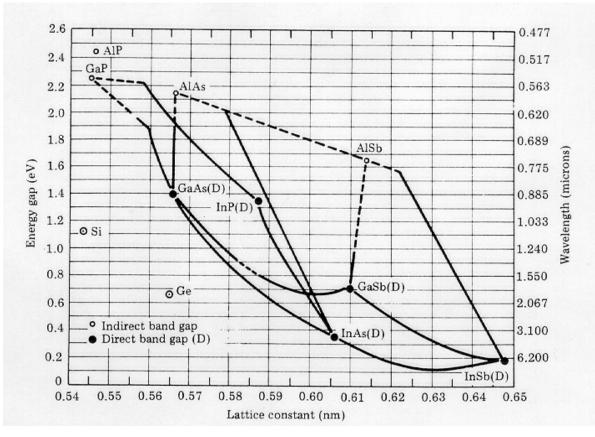

| Figure 1.2:                   | Bandgap energy vs. lattice constant for a variety of common semiconducting materials 1                                                                                                                                                                                                                                                                             | 8  |

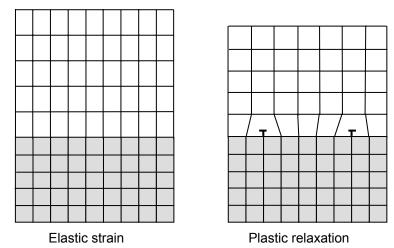

|                               | Elastic strain and plastic relaxation at a mismatched semiconductor interface. Note the two dislocations at the mismatched interface after plastic relaxation.                                                                                                                                                                                                     | 19 |

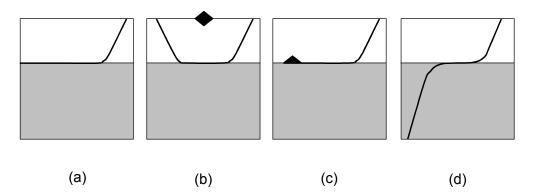

| Figure 1.4:<br>Homo<br>nuclea | Options for dislocation nucleation at a mismatched semiconductor interface. (a.) geneous nucleation, (b.) Heterogeneous nucleation at a surface defect, (c.) Heterogeneous tion at an interface defect, and (d.) Heterogeneous nucleation at a pre-existing thread.                                                                                                |    |

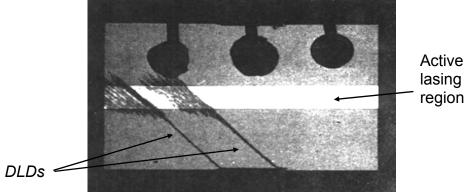

| GaAs/<br>image                | Representative EBIC image of a DLD dislocation cluster propagating from the edge of a AlGaAs laser to the bright active region in the center. The three dark circles at the top of the are metal contacts. (image courtesy of Yellen <sup>18</sup> )                                                                                                               |    |

| Figure 1.6:                   | Antiphase boundary in GaAs formed by a single-atom step on the substrate surface                                                                                                                                                                                                                                                                                   | 28 |

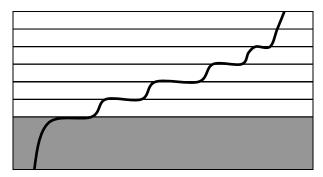

| A thre                        | Cross-sectional schematic of a relaxed graded buffer layer grown on a mismatched substrate.<br>ading dislocation from the substrate is shown moving into the graded buffer and extending its<br>segment length without nucleating additional threads                                                                                                               | 32 |

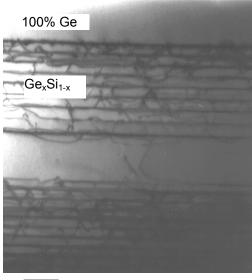

| Figure 1.8:<br>CVD §          | Cross-section TEM micrograph of a Ge/GeSi/Si graded buffer structure grown in the UHV-<br>growth reactor. The thick band in the center of the image is the CMP polished region at 0%.                                                                                                                                                                              |    |

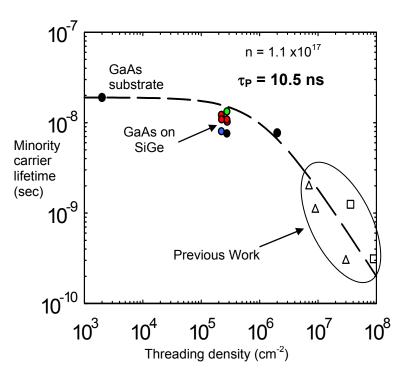

| Figure 1.9:<br>of Ga          | Minority carrier lifetime as a function of measured threading dislocation densities for a variety<br>As heterostructures grown on Si substrates (courtesy of Carlin <sup>54</sup> ). The points labeled "previous<br>reflect reported data in the literature for GaAs growth directly on Si                                                                        | y  |

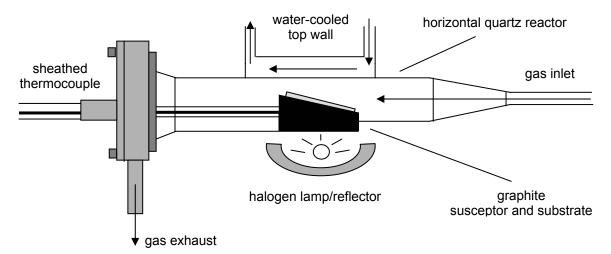

|                               | Schematic diagram of the Thomas Swan MOCVD growth chamber used in this work. The r operates at atmospheric pressure.                                                                                                                                                                                                                                               | 45 |

|                               | Schematic diagram showing single atomic layer steps on a (001) Ge surface. Note the rotation face dimers which occurs at the single steps.                                                                                                                                                                                                                         |    |

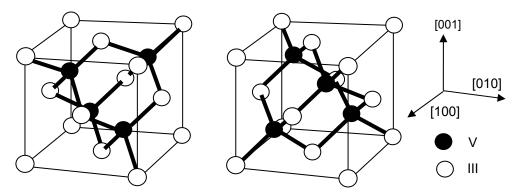

| Figure 3.2:                   | The two possible orientations of the GaAs zincblende unit cell.                                                                                                                                                                                                                                                                                                    | 55 |

|                               | An antiphase boundary in GaAs formed by a single atom step on a Ge surface. Adjacent As-<br>d Ga-Ga bonds will create a charged planar defect propagating upwards from the interface                                                                                                                                                                               | 55 |

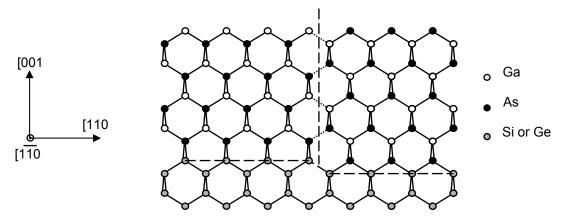

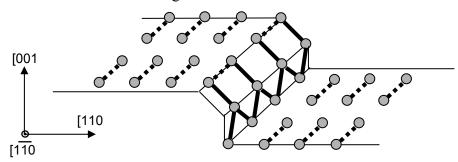

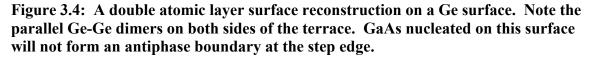

| on bot                        | A double atomic layer surface reconstruction on a Ge surface. Note the parallel Ge-Ge dimers<br>h sides of the terrace. GaAs nucleated on this surface will not form an antiphase boundary at<br>p edge.                                                                                                                                                           |    |

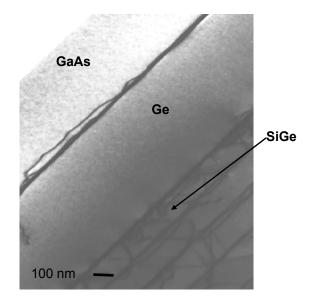

|                               | Cross-sectional TEM image of a GaAs film grown on a Ge/GeSi/Si substrate.                                                                                                                                                                                                                                                                                          |    |

| pyram<br>respec               | Plan-view TEM image of a GaAs film on Ge/GeSi/Si substrate with a high density of idal stacking fault defects. Depending on the orientation of the stacking fault planes with t to the electron beam they will appear as squares or hourglass shapes in the plan-view scope image.                                                                                 | 50 |

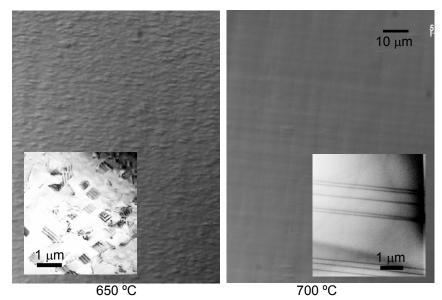

| Figure 3.7:<br>substra        | Optical micrographs and plan-view TEM images (inset) of GaAs films grown on Ge/GeSi/Si ates at 650 and 700 °C. Note the high density of stacking faults correlated with a visibly rough film surface for the film nucleated at 650 °C.                                                                                                                             | er |

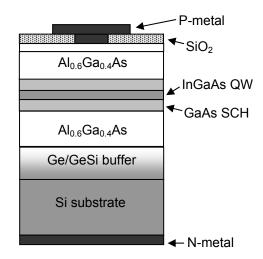

|                               | Schematic cross section of a GaAs/AlGaAs LED device structures grown on a Ge/GeSi/Si ate. Identical devices were fabricated on n-doped GaAs substrates                                                                                                                                                                                                             | 57 |

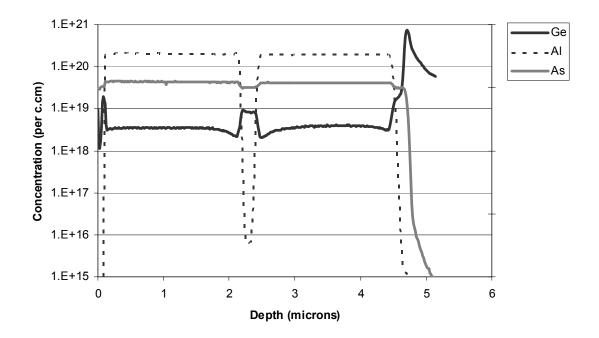

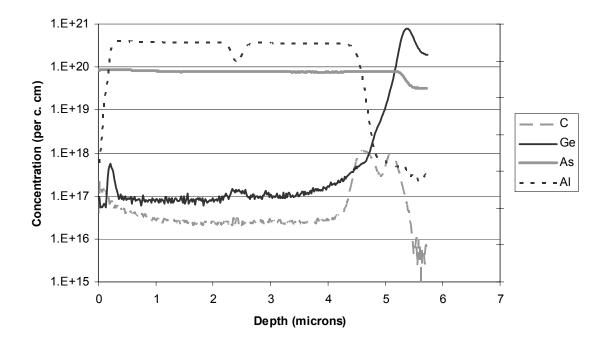

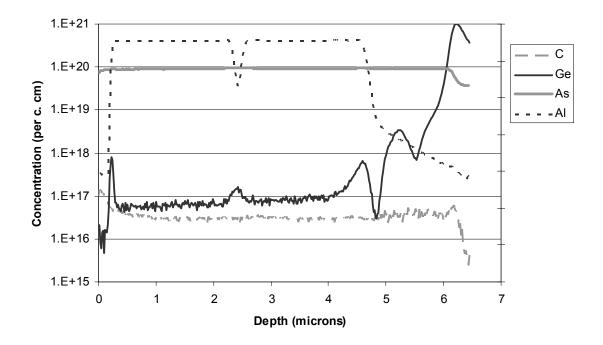

| Note the concert              | SIMS depth profile of InGaAs/GaAs/AlGaAs LED device structure on a Ge/GeSi/Si substrate.<br>he high levels of Ge incorporation throughout all layers of the device. The dip in measured Al<br>ntration in the center of the plot indicates the location of the GaAs device active region where<br>n was slowest. This is also where the Ge incorporation increases |    |

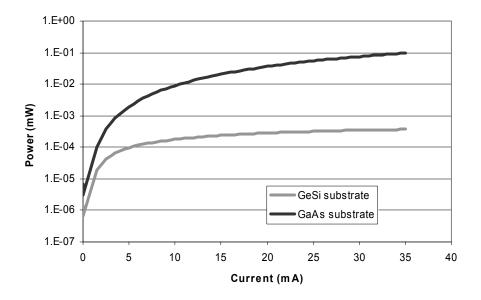

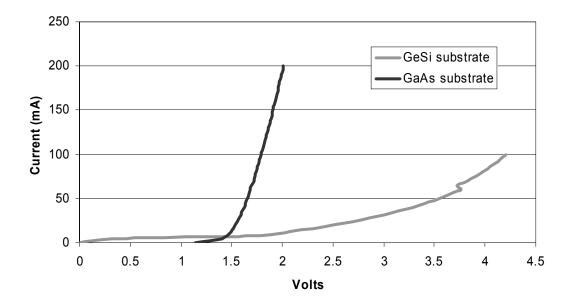

|                               | : Diode current vs. measured optical power for LED structures on Ge/GeSi/Si and GaAs ates. Note the much lower output power for the device on Ge/GeSi/Si                                                                                                                                                                                                           | 70 |

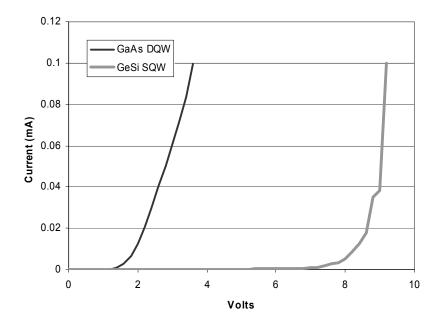

|                               | : Voltage vs. current data for LED structures on Ge/GeSi/Si and GaAs substrates. The turn-or e and series resistance were much higher in the devices grown on Ge/GeSi/Si                                                                                                                                                                                           |    |

| Figure 3.12: SIMS depth profile of GaAs/AlGaAs LED structure grown on a Ge/GeSi/Si substrate using a thick low-temperature GaAs buffer. Note the rapid increase in C contamination in the low-temperature buffer region                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 3.13: SIMS depth profile of GaAs/AlGaAs LED structure grown on a Ge/GeSi/Si substrate after a 15-minute AlAs coating of the susceptor and reactor walls. The overall Ge incorporation is lower, but a Ge spike remains in the central GaAs layer                                                                                          |

| Figure 3.14: SIMS depth profile of a GaAs/AlGaAs LED structure on a Ge/GeSi/Si substrate grown after coating the susceptor and reactor walls and removing the Ge/GeSi back layers of the substrate wafer.                                                                                                                                        |

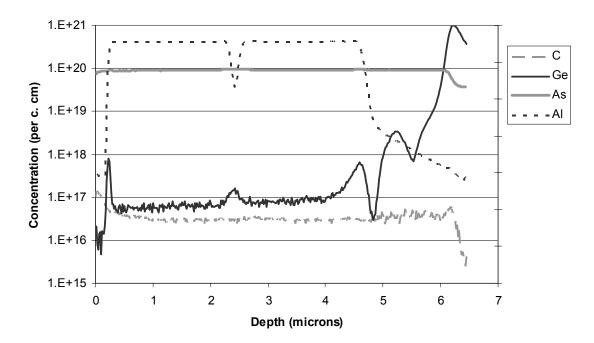

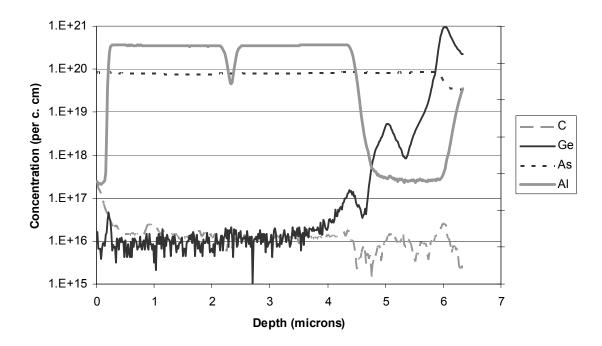

| Figure 3.15: SIMS depth profile of a GaAs/AlGaAs LED structure on a Ge/GeSi/Si substrate grown on a new graphite susceptor in a cleaned reactor tube after mechanically removing the Ge/GeSi back layers. Note the very low Ge and C contamination levels, and the absence of any Ge peak in the GaAs waveguide core in the center of the device |

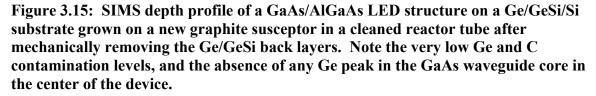

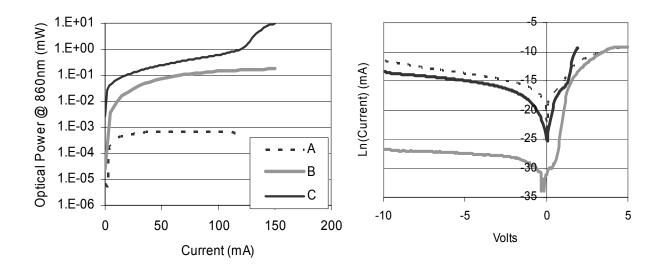

| Figure 3.16: Current vs. optical power and diode voltage vs. current data for improved Ge-free<br>GaAs/AlGaAs LEDs on Ge/GeSi/Si substrates (B) compared with identical devices fabricated on<br>GaAs substrates (C). The original current vs. power and voltage data for the Ge-contaminated LED is<br>also plotted for comparison (A)          |

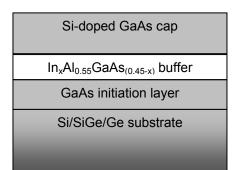

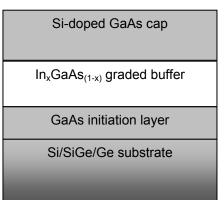

| Figure 4.1: Schematic of the InAlGaAs and InGaAs buffer layers grown on Ge/GeSi/Si substrates. Both samples were n-doped with Si to increase the selectivity of the defect selective etching reaction                                                                                                                                            |

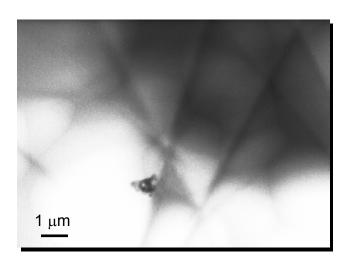

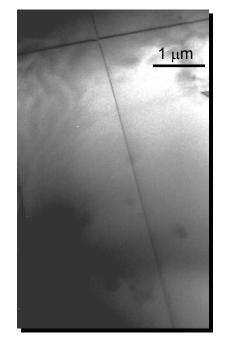

| Figure 4.2: Plan view TEM micrographs of 100 Å InGaAs quantum wells grown on GaAs and Ge/GeSi/Si substrates. Note the presence of orthogonal misfit dislocation lines on the Ge/GeSi/Si substrate that are not present on the GaAs substrate                                                                                                     |

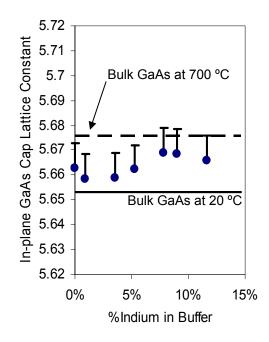

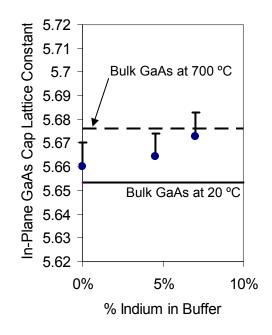

| Figure 4.3: Measured room-temperature in-plane lattice constants of GaAs cap layers grown on InAlGaAs buffer layers on a Ge/GeSi/Si substrate. The plotted error bars indicate predicted in-plane lattice constants at the growth temperature. 95                                                                                                |

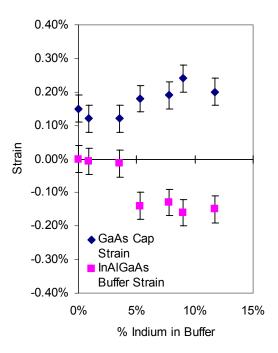

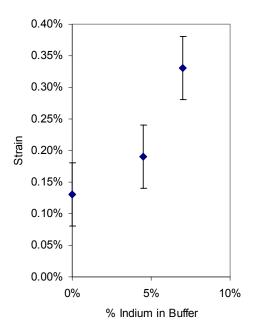

| Figure 4.4: Measured room-temperature strain in an InAlGaAs buffer layer and GaAs cap layer grown on a Ge/GeSi/Si substrate at a variety of In compositions. Note the increase in tensile strain with increasing In for the GaAs buffer, which should result in lower compressive strain at the growth temperature                               |

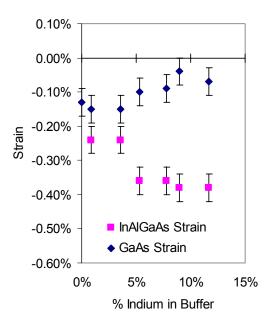

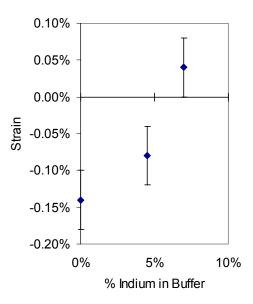

| Figure 4.5: Calculated strain in InAlGaAs buffer layer and GaAs cap layer at the growth temperature on a Ge/GeSi/Si substrate as a function of In composition in the buffer layer. Note the minimized compressive strain in the GaAs cap for $x_{In} = 9\%$                                                                                      |

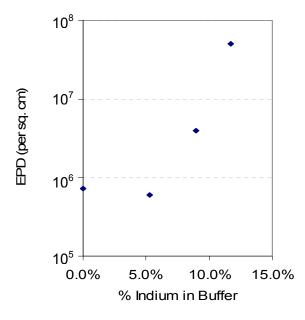

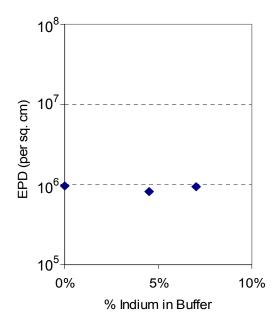

| Figure 4.6: Etch pit density measurements of threading dislocation density in a GaAs cap above an<br>InAlGaAs buffer on Ge/GeSi/Si as a function of In in the buffer. Note the rapid increase in threading<br>density for x <sub>In</sub> > 6%                                                                                                   |

| Figure 4.7: Measured in-plane lattice constant of a GaAs cap above an InGaAs graded buffer on Ge/GeSi/Si as a function of In in the buffer. The plotted error bars indicate the estimated in-plane lattice constant at the growth temperature                                                                                                    |

| Figure 4.8: Measured room-temperature strain of a GaAs cap on an InGaAs buffer on Ge/GeSi/Si as a function of the final In composition of the graded buffer                                                                                                                                                                                      |

| Figure 4.9: Calculated strain in the GaAs cap at the growth temperature on an InGaAs graded buffer on Ge/GeSi/Si. The strain in the cap at the growth temperature should be 0% for a graded buffer terminating at approximately 6% In                                                                                                            |

| Figure 4.10: Measured threading dislocation density in a GaAs film above an InGaAs graded buffer on a Ge/GeSi/Si substrate as a function of In in the buffer layer. Note that the measured threading density does not increase with In fraction as it did for the uniform InAlGaAs buffer in Figure 4.6                                          |

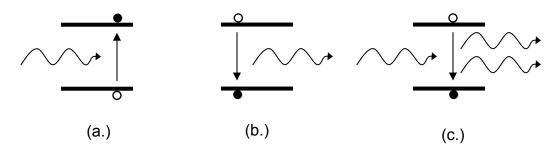

| Figure 5.1: Three possible electron-photon interaction paths in a simple two-level semiconductor system: (a.) absorption, (b.) spontaneous emission, and (c.) stimulated emission                                                                                                                                                                |

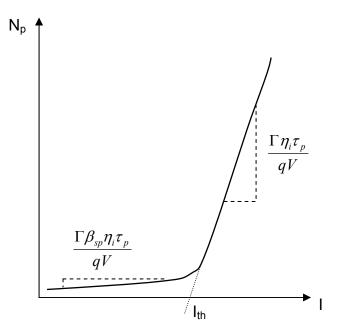

| Figure 5.2: Typical photon-density vs. current graph for a semiconductor laser, showing the kink at the threshold current where stimulated laser emission dominates spontaneous LED emission                                                                                                                                                     |

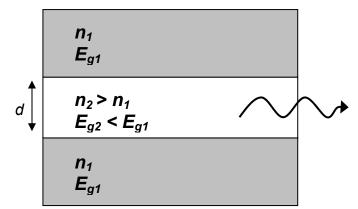

| Figure 5.3: Cross section of a typical double-heterostructure laser. The outer cladding layers have a higher bandgap energy and a lower index of refraction than the inner active layer, thus serving to confine both the injected carriers and the generated photons. 110                                                                       |

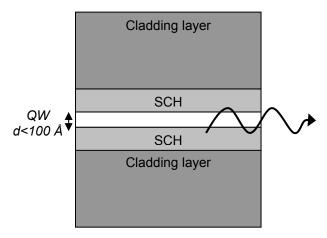

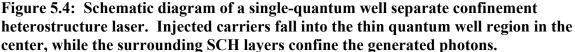

| Figure 5.4: Schematic diagram of a single-quantum well separate confinement heterostructure laser.<br>Injected carriers fall into the thin quantum well region in the center, while the surrounding SCH layers<br>confine the generated photons                                                                                                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

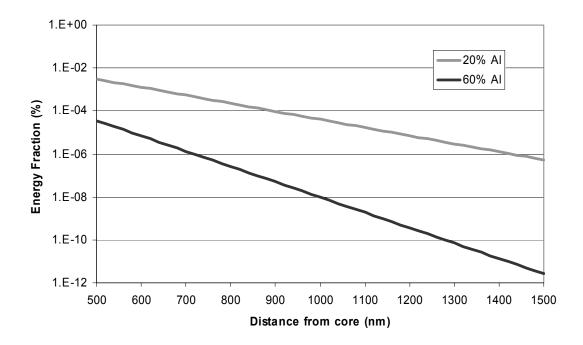

| Figure 5.5: Calculated electromagnetic energy as a function of cladding thickness outside the SCH for xAl = 0.2, 0.6 for an InGaAs/GaAs/AlGaAs quantum well SCH laser structure                                                                                                                                                                                                   |

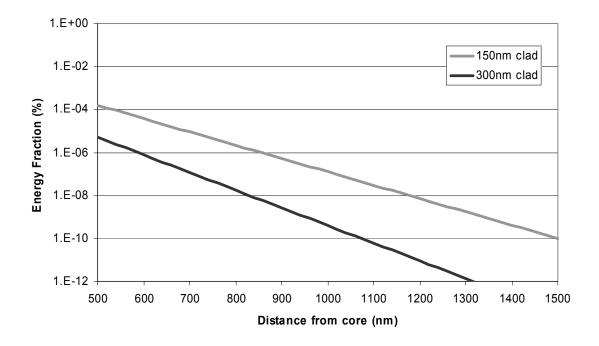

| Figure 5.6: Calculated electromagnetic energy as a function of cladding thickness outside the SCH for a GaAs/AlGaAs quantum well SCH laser with d=150nm, 300nm                                                                                                                                                                                                                    |

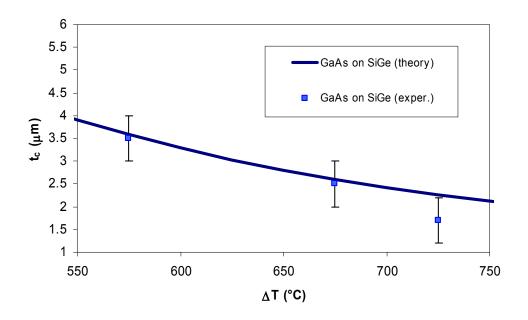

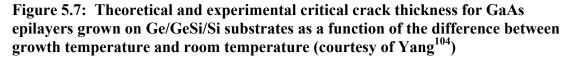

| Figure 5.7: Theoretical and experimental critical crack thickness for GaAs epilayers grown on Ge/GeSi/Si substrates as a function of the difference between growth temperature and room temperature (courtesy of Yang <sup>104</sup> )                                                                                                                                            |

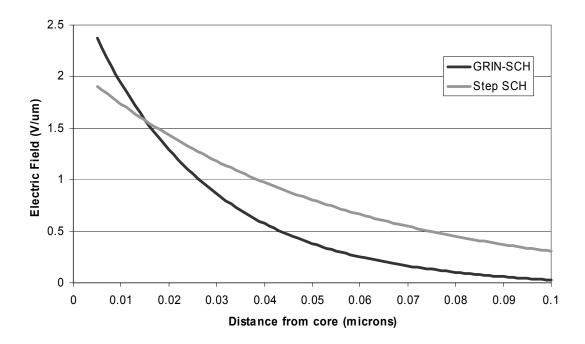

| Figure 5.8: Calculated electromagnetic field strengths as a function of cladding thickness for a GaAs/AlGaAs step-index SCH compared with a GRIN-SCH waveguide structure. The core thickness is fixed for both waveguides at 100nm                                                                                                                                                |

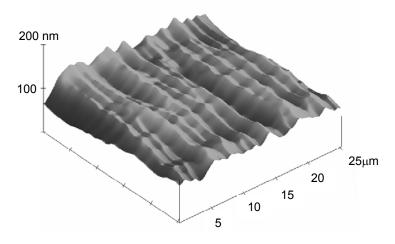

| Figure 5.9: Atomic force micrograph of a Ge/GeSi/Si substrate surface. Note the periodic surface undulations that lead to crosshatch roughness. 124                                                                                                                                                                                                                               |

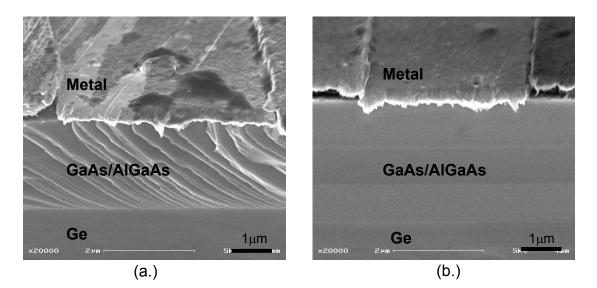

| Figure 5.10: SEM image of GaAs/AlGaAs facet mirrors on a Ge/GeSi/Si substrate cleaved perpendicular (a.), and parallel (b.) to the direction of substrate offcut. Note the increased roughness on the mirror facet cleaved perpendicular to the offcut direction                                                                                                                  |

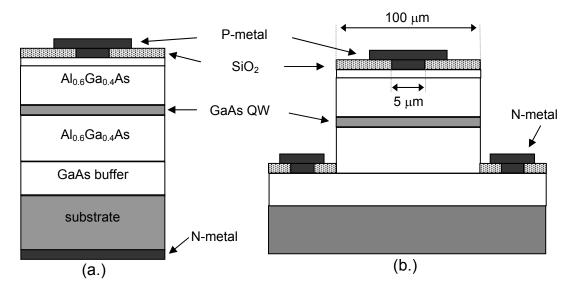

| Figure 6.1: Cross-sectional schematic of a GaAs/AlGaAs quantum well laser processed with (a.) a basic two-level oxide stripe recipe and (b.) the more complex four-level top-contact recipe                                                                                                                                                                                       |

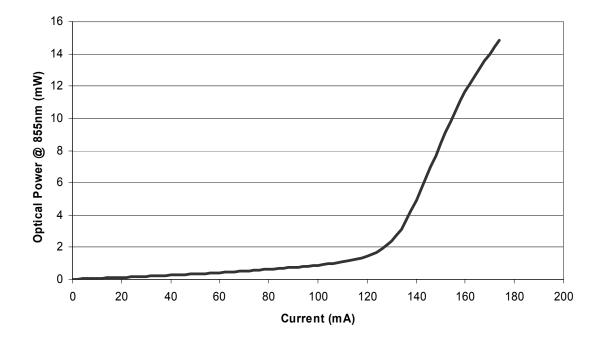

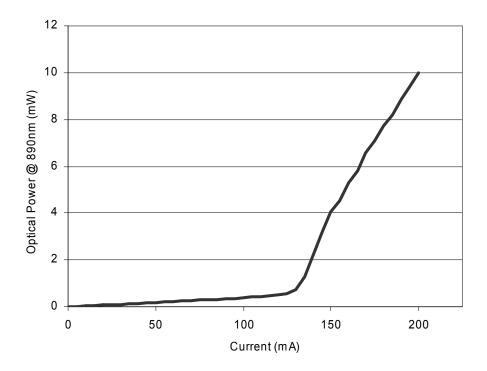

| Figure 6.2: Plot of laser optical power vs. injected current for the initial GaAs/AlGaAs GRIN-SCH quantum-well laser on GaAs. The laser reached threshold at a current of 127mA                                                                                                                                                                                                   |

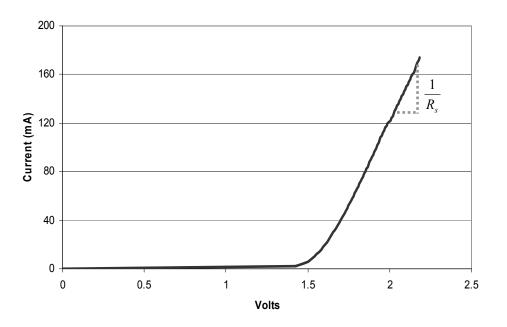

| $\label{eq:GaAs} \begin{array}{l} \mbox{Figure 6.3: Injected current vs. voltage characteristics of initial GaAs/AlGaAs GRIN-SCH laser diode on $$GaAs. The series resistance ($R_S$) in the diode was 3.3 ohms. $$144$ \\ \end{array}$                                                                                                                                           |

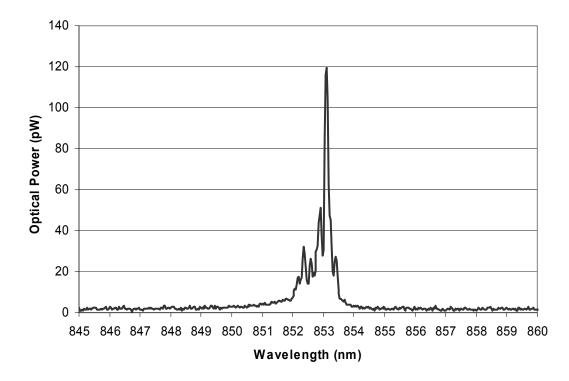

| Figure 6.4: Wavelength spectrum of the initial GaAs/AlGaAs laser diode at an operating current above threshold. The laser emission wavelength shows a peak at 853.2 nm with surrounding low-intensity cavity modes                                                                                                                                                                |

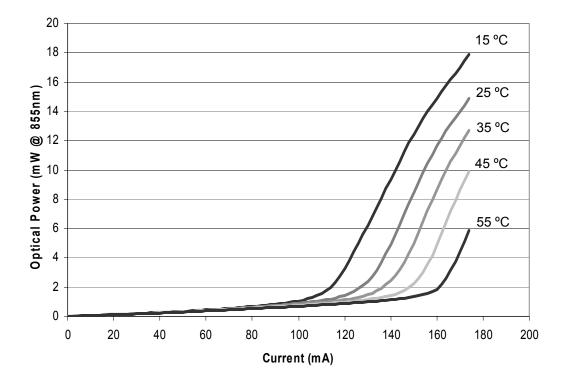

| Figure 6.5: Laser power vs. current as a function of increasing temperature for the initial GaAs/AlGaAs GRIN-SCH quantum well diode on GaAs. Note the increasing threshold current with increasing test stage temperature                                                                                                                                                         |

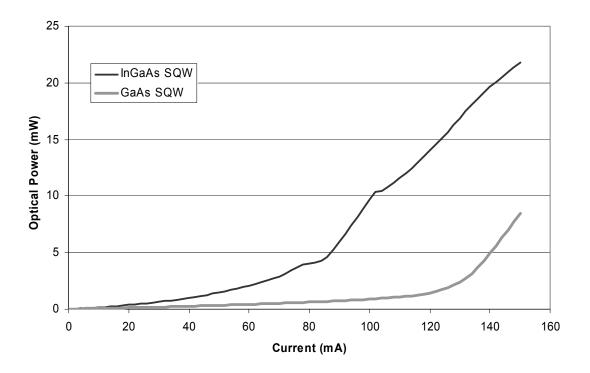

| Figure 6.6: Side-by-side comparison of the optical power vs. current characteristics for GaAs and InGaAs quantum well devices on GaAs substrates. The optical power readings are normalized to take into account the different emission wavelengths. The InGaAs quantum well device shows lower threshold current density and slightly better differential quantum efficiency     |

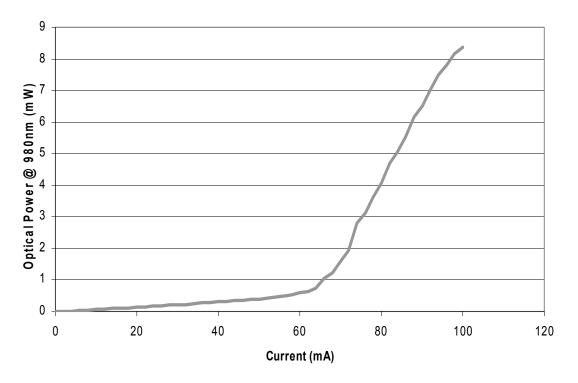

| Figure 6.7: Optical power vs. current for an InGaAs double quantum well laser on a GaAs substrate. This device had the best operating characteristics of all the lasers fabricated on GaAs substrates                                                                                                                                                                             |

| Figure 6.8: Optical power vs. current for the first InGaAs/GaAs/AlGaAs quantum well laser structures integrated on Ge/GeSi/Si substrates. A plot of the power vs. current data for a similar device on GaAs is shown for comparison. The laser structure on Ge/GeSi/Si shows much lower emission efficiency and never turns on                                                    |

| Figure 6.9: Measured diode current vs. voltage for the first InGaAs/GaAs/AlGaAs laser structures integrated on Ge/GeSi/Si. The current-voltage characteristics of a similar device on GaAs are shown for comparison. Note the much higher turn-on voltage for the device on Ge/GeSi/Si                                                                                            |

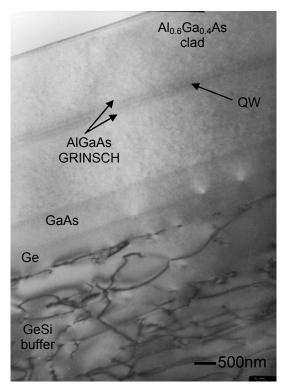

| Figure 6.10: Cross-section TEM image of a GaAs/AlGaAs GRIN-SCH quantum well laser on Ge/GeSi/Si.                                                                                                                                                                                                                                                                                  |

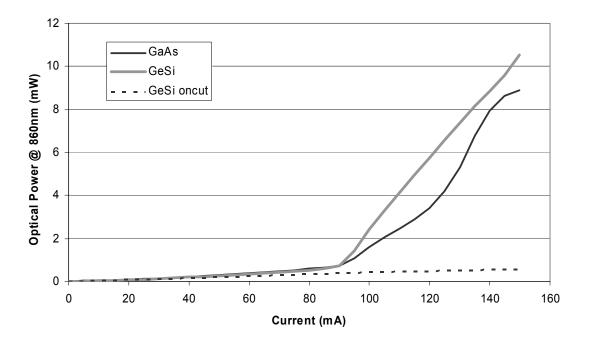

| Figure 6.11: Optical power vs. current for GaAs/AlGaAs GRIN-SCH quantum well lasers integrated on Ge/GeSi/Si substrates with mirror facets cleaved parallel and perpendicular to the substrate offcut direction. Also included for comparison is the optical power vs. current data for an identical laser structure grown on a standard GaAs substrate and processed in parallel |

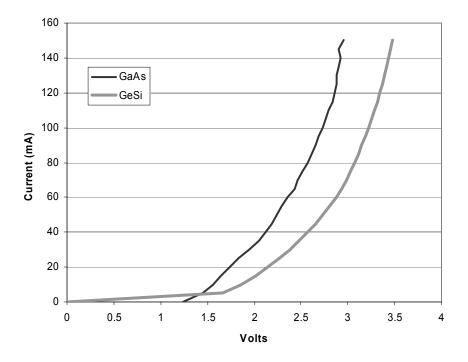

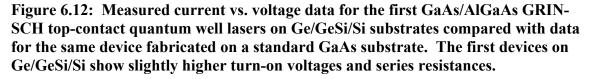

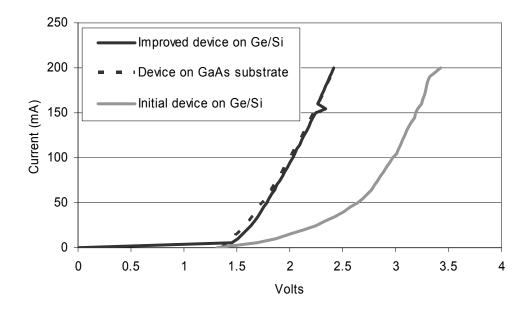

| Figure 6.12: Measured current vs. voltage data for the first GaAs/AlGaAs GRIN-SCH top-contact quantum well lasers on Ge/GeSi/Si substrates compared with data for the same device fabricated on a standard GaAs substrate. The first devices on Ge/GeSi/Si show slightly higher turn-on voltages and series resistances                                                           |

| Figure 6.13: Current-voltage characteristics of GaAs/AlGaAs laser diodes integrated on Ge/GeSi/Si substrates with improved contact metallization layers deposited at the AlGaAs/GaAs waveguide interface (labeled "n-GaAs contact") compared with similar structures contacted at the lower GaAs/Ge interface ("n-Ge contact"). The n-GaAs contacted devices turned on earlier and showed lower series resistance at high current levels |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

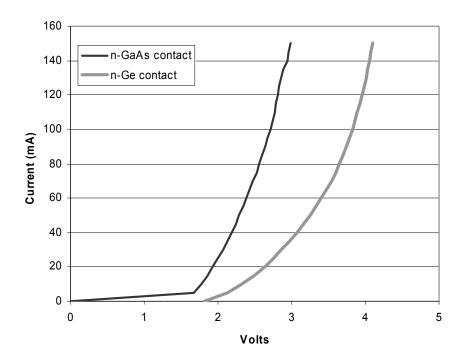

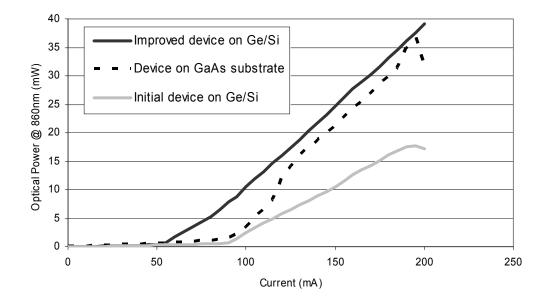

| Figure 6.14: Optical power vs. current data for improved GaAs/AlGaAs laser structures grown on CMP-<br>polished Ge/GeSi/Si substrates. The original optical power vs. current data for the first GaAs/AlGaAs<br>lasers on Ge/GeSi/Si and GaAs substrates are included for comparison                                                                                                                                                     |

| Figure 6.15: Current vs. voltage characteristics of improved GaAs/AlGaAs lasers on Ge/GeSi/Si substrates compared to the current-voltage characteristics of the original GaAs/AlGaAs devices grown on Ge/GeSi/Si and GaAs substrates. Note that the improved devices show identical diode characteristics to the devices grown on GaAs                                                                                                   |

| Figure 6.16: Optical power vs. current data for the first InGaAs/GaAs/AlGaAs laser to be demonstrated on a Ge/GeSi/Si substrate. The laser turned on at 128mA                                                                                                                                                                                                                                                                            |

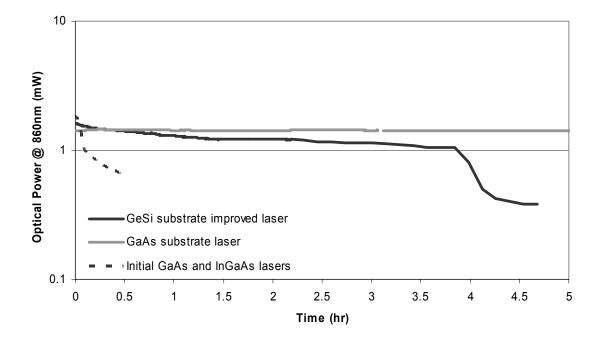

| Figure 6.17: Laser power as a function of time at a fixed current for sample lasers on Ge/GeSi/Si and GaAs substrates. The optical power at threshold was slightly less than 1mW/facet for all devices                                                                                                                                                                                                                                   |

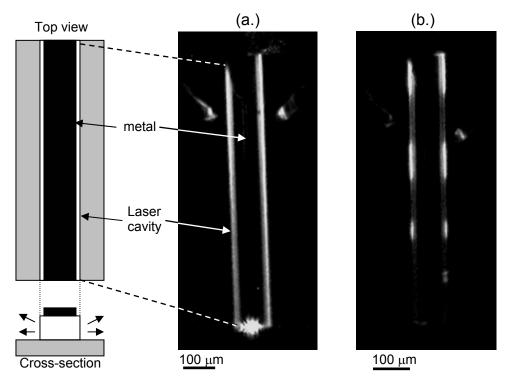

| Figure 6.18: Plan-view electroluminescence image of a GaAs/AlGaAs laser on Ge/GeSi/Si (a.) before and (b.) after laser failure. The active region is obscured by the p-metal layer on the top of the device, but the two bright stripes on either side allow observation of the luminescence pattern inside the cavity, and the appearance of wide, dark bands stretching across the laser cavities in image (b.) after laser failure    |

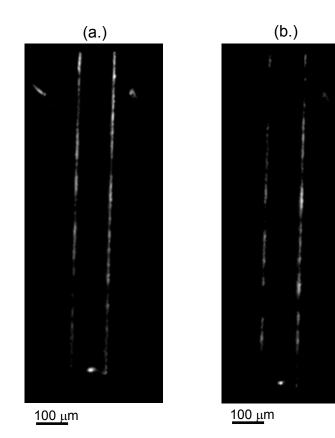

| Figure 6.19: Electroluminescence pattern of an InGaAs laser cavity on Ge/GeSi/Si (a.) before and (b.) after<br>device failure (average lifetime for these devices was < 10 minutes). A pattern of dark areas at the<br>cavity edges is visible in both images                                                                                                                                                                            |

#### Acknowledgements

This is a section that has been composed and re-composed many times in my head over the last six years. I am glad to finally be able to write it down. I will leave MIT grateful to many people for making my experience what it was, but first and foremost I have to thank my thesis advisor Eugene Fitzgerald. Gene has been an inspiring and patient mentor throughout my time in his group and a never-failing source of ideas and enthusiasm when things didn't go as I expected. Though it may have been occasionally frustrating for him to watch, I have appreciated the opportunities he has given me to try and fail (and learn) on my own, and I'm grateful for the confidence he always expressed in my ability to make the lasers work.

Professor Rajeev Ram has been in many ways a second advisor for me since my arrival at MIT, and I don't think I could have pulled off what I did here without his help. All of the resources he made available to me in his lab, along with his advice and wisdom throughout the device design and testing steps was indispensable, and I really appreciate his assistance in reading and revising my thesis.

Professor Gerd Ceder has been a flexible and helpful member of my thesis committee and I am grateful for his input.

The students I worked with in my time here have shaped my experience in ways that are hard to put into words. Needless to say I probably wouldn't have lasted this long without the friendship and humor of everyone who has graced the Fitzgerald group while I've been part of it.

Jeev Makan was one of the first friendly faces I met in the group and his help with equipment training and his thoughtful discussions on group dynamics and post-graduation options were much appreciated.

Mayank Bulsara was a great guy to work with while our paths here overlapped. His patience and his friendliness seemed to know no bounds, even for certain individuals to whom the rest of us were less than charitable. Behind that goofy sense of humor and ever-present tendency to hold animated conversations with himself is a guy who is sincere and honest and a great engineer and scientist.

Andy Kim was a willing and patient mentor in my first years as a grad student, and a helpful and insightful colleague in the years that followed. He was always happy to stop and listen to the problems I was facing, and his mind was usually well ahead of mine with proposed solutions.

Steve Ting was a surprise. A brusque and quiet exterior covered a thoughtful and funny personality, along with an amazing ability and dedication to martial arts and the capacity to converse knowledgeably on topics from antiphase boundaries to firearms to ballroom dancing.

Matt Currie's greatest weapon is his sense of humor. He kept me snickering the whole time I was here, and he definitely has a career in Photoshopery. He's also a master of SiGe and a purveyor of a fine collection of 'urban' music and photocopied election brochures.

Vicky Yang was the best coworker I could have asked for on the III-V reactor. Her patience and friendliness and sly sense of humor, along with a very sharp mind and an amazing collection of gossip made my time here much richer. Ich wünsche ihr viel gluck mit ihrer Hochzeit, den neuen Haus und Stelle, und ihren energischen Katzen. Tom Langdo is gay. Seriously, Tom was one of my best friends here and also the hardest working guy on the UHVCVD. Beyond that, he remains one of the most sincere, unselfish, and genuinely nice guys I've met at MIT or anywhere else. Plus he's a crazy smart scientist and has a mean sense of humor. I hope that more mountain hiking adventures remain in our future.

Chris Leitz was an inspiration. I was constantly impressed by his determination and focus, and am sure he will get where he is headed, probably very quickly in a European sports car.

Arthur Pitera has a good appreciation of the absurdity which surrounds life in the Fitzgerald group and never stops working, even when he's laughing at the rest of us, or downloading illegal television episodes.

Larry Lee is one cool cat. I've appreciated our conversations about the group and life beyond it, and if he doesn't get famous one day for the world's fastest Ge transistors he definitely will for his music.

Gianni Taraschi will someday figure out the stock market and make millions, but in the meantime he's been a fun guy to talk about my "laser" projects with and to ask all of my MATLAB questions.

Lisa McGill is a hard worker with a bright (yellow) future. I don't envy her continuing relationship with the Thomas Swan reactor but I know she will succeed in bending it to her will, and I really appreciate her assistance in editing this thesis.

Nate Quitoriano has a big job in front of him, but he is definitely up to the task. I've been happy to have had a chance to pass what remains of my MOCVD knowledge on to such a smart guy, and to have enjoyed all of the discussions we've had in the process.

I'm pleased to have had a chance to get to know Nava Ariel, and wish her continued success in the group.

Outside the insular world of Gene's research group there have been a number of people I have met at MIT who helped to make my work here possible. Harry Lee in Rajeev Ram's group has been an amazing and patient resource for all of my laser testing questions and requests, while certain individuals in the TRL have been helpful in conquering my frequent processing difficulties, especially Kurt Broderik.

I can't leave MIT without thanking the friends I have made here for all of the support and laughter we've shared. Tim Finegan came up with me from Virginia in a Ryder truck and I'm glad we've stayed friends (and occasional roommates) ever since. Aaron Blanchet made my first two years here much more fun, and Erika Abbas was a great source of MIT wisdom and gossip and above all a dependable friend. Debbie Lightly was one of the reasons I decided to come to MIT, and I'm grateful she's remained here to share the entire experience. Classes and quarter-century crises and lots of qualifier studying all passed much more smoothly with Debbie's friendship and restaurant skills.

Beyond the walls of MIT, Ralph Tsong has remained a great friend, with a sense of humor that always makes perfect sense to me even if it doesn't always impress the Bettys. I'm glad that we've been able to keep up despite frequent moves and the occasional radical career changes, and someday I know I'll be able to boast that I knew Ralph when he was still drawing ants fighting the French Revolution.

My best friend of all while I was here was also the first person to visit me in my furniture-free first-year room on Albany St. Despite the little distractions that followed

(like moving to Africa and spending a year in a marine barracks) we stuck together and I am now immensely proud to call her my wife. None of what I have accomplished here could have happened without Annemarie's love and support. I thank her for her infinite patience during many long nights of research, and for her optimism and humor when I was running out of both. Words can't express the strength of my feelings for her, but above all I'm grateful to be able to look forward to a long life after MIT together.

Finally I would like to thank my family, who have supported me from the first science fair parachutes and telescope birthday parties at the Lawrence Hall of Science. I know I wouldn't have made it to MIT without their unceasing love and support, and I truly appreciate the sacrifices they made along the way to make my experience here possible. I can't thank them enough for what they have taught me about life and learning. I am glad to know that David is receiving his degree along with me this year, and also grateful that I won't be the only science nerd at future family reunions.

I would like to dedicate this thesis to my grandfather, Dr. Raymond Wilson, who sparked my first interest in physics and encouraged me to never stop wondering how things work.

## Chapter 1. Introduction

Silicon has become one of the world's most useful materials for a vast array of electronic applications. Silicon transistors can be found inside thousands of different consumer and manufacturing products where they provide efficient, high-speed calculating power at a fraction of the cost of other technologies. Silicon (Si) is an ideal material for microelectronic circuits for a variety of important reasons. Silicon has a stable, easily processed native oxide (SiO<sub>2</sub>) that can be readily integrated on Si surfaces to form built-in circuit isolation layers and dielectric gate barriers. Silicon also benefits from almost 60 years of material research into the growth of elemental Si crystals. Si transistor manufacturing technology has built on these advances to the point where state-of-the-art fabrication facilities can produce billions of transistors per wafer at a rate of thousands of wafers per day. Considering the intense amount of investment which has gone into Si transistor technology in the last half century and the ubiquity of Si transistors in modern electronic equipment, it seems likely that Si wafers will continue to dominate the microelectronics industry for the foreseeable future.<sup>1</sup>

Despite its many strengths, Si is not a perfect material for large-scale transistor integration, and recent advances with increasing transistor speed and density on Si wafers have begun to expose some of the inherent limitations of traditional Si circuits for ultra-high-speed and high-density microelectronics applications. In particular, relatively low carrier mobility (compared to other inorganic semiconductors like Ge or GaAs) and the inability of Si crystals to form direct-gap optoelectronic devices have both begun to restrict the speed and data rates at which Si-based integrated circuits can operate. Crosstalk between neighboring circuits, coupled with RC signal delays in the metal interconnects that link individual Si transistors are unavoidable in present Si integrated circuit designs.<sup>2,3</sup>

Optical circuit interconnects offer an alternative model for high-speed microelectronics, in which individual Si circuits or devices on a wafer chip are connected by multiplexed optical waveguides, providing crosstalk-free data paths with exponentially higher data rates than current metal wire lines. The performance benefits offered by optoelectronic integration on Si circuits are in essence the same as those

14

offered by the fiber optic technology that replaced much of the traditional metal wiring in the world's telecommunications networks over the last 30 years. Individual fiber optic waveguide cables, capable of carrying trillions of bits of digital information per second through hundreds of discrete frequency channels, now carry nearly all of the long-distance voice and data traffic in the developed world.<sup>4</sup> Optoelectronic interconnects promise similarly revolutionary speed and bandwidth advances for Si integrated circuits if they can be successfully integrated into the mature Si transistor manufacturing infrastructure.

Si is an indirect-bandgap semiconductor and cannot be used to efficiently generate photons for optical communication applications. In contrast to Si, many of the compound semiconductors from groups III and V of the periodic table (such as GaAs or GaN) are direct-bandgap semiconductors. Alloys of GaAs, GaN, and InP have been used to fabricate a wide variety of commercially important light-emitting devices, including the high-speed semiconductor lasers which drive all modern fiber optic telecommunications circuits.<sup>5</sup> Ideally, a Si semiconductor circuit into which a compound semiconductor light-emitting device or detector could be easily and inexpensively integrated would offer the fast calculation speed, high device density, and low cost of modern Si circuit technology together with the high-speed data transfer capabilities of compound semiconductor optoelectronics. New integrated circuit designs may be imagined in which a collection of complimentary metal-oxide-semiconductor (CMOS) logic circuits on a Si wafer are linked to each other and to neighboring wafers by high-speed GaAs laser/detector modules integrated directly on the Si substrate wafer. A hypothetical example of one such circuit design is shown in Figure 1.1.

Figure 1.1: Hypothetical example of an integrated GaAs/Si optoelectronic circuit

The potential benefits of optoelectronic integration on Si integrated circuits have inspired hundreds of investigations into practical methods for achieving this goal by dozens of different research groups during the last three decades. While limited success has been reported for some complex hybrid integration schemes,<sup>6</sup> no group has yet demonstrated a commercially viable epitaxially integrated GaAs-based optoelectronic circuit on a Si CMOS logic platform. Monolithic epitaxial integration of III-V compound semiconductors on Si substrates will remain a key step for the economical production of optoelectronic integrated circuits. Only with compound semiconductor device layers deposited epitaxially at the beginning of the Si circuit fabrication process can manufacturers use the leverage of the mature Si production infrastructure to create truly high-speed and low-cost optoelectronic integrated circuits on Si wafers.

The monolithic epitaxial integration of III-V compound semiconductors on Si substrates is not a straightforward process, due to the significant differences in basic crystal properties that exist between elemental Si and the III-V semiconductor alloys. These differences include variations in the interatomic lattice spacing of the two materials, differences between their thermal expansion properties, and variations in the crystal structures due to the reduced symmetry of compound semiconductor lattices. Early attempts to deposit III-V semiconductor materials directly on Si substrates by a variety of crystal growth mechanisms led to unacceptably high densities of defects in the resulting films, as will be discussed in detail below. Recent work in this research group has suggested a new epitaxial integration procedure that can permit the successful epitaxial integration of III-V optoelectronic circuits on Si substrates via the use of relaxed graded Ge/Ge<sub>x</sub>Si<sub>(1-x)</sub> buffer layers. Simple integrated optoelectronic devices including light-emitting diodes, solar cell structures, and photodetectors have been successfully demonstrated on Si substrates using this new integrated materials platform.

Although basic optoelectronic structures have been integrated on Si substrates via Ge/GeSi buffer layers, semiconductor laser structures remain the ultimate test for the quality of the integrated films because lasers operate at photon and minority carrier population densities that make them very sensitive to epitaxial defects from the integration process. The work presented in this thesis will focus on efforts to use relaxed

16

graded  $Ge/Ge_xSi_{(1-x)}$  buffer layers to demonstrate high-quality III-V semiconductor lasers epitaxially integrated on Si substrates.

#### 1.1. Barriers to Epitaxial III-V/Si integration

As mentioned above, there are a number of fundamental differences between the material characteristics of the III-V optoelectronic semiconductors and Si. A summary of the differences between Si, Ge, and GaAs is presented in Table 1.1.<sup>7</sup>

Table 1.1: Materials constants for Si, Ge, and GaAs

| Semiconductor | Crystal structure | Lattice Constant (Å) | Coefficient of thermal               |

|---------------|-------------------|----------------------|--------------------------------------|

|               |                   |                      | expansion at 300K (K <sup>-1</sup> ) |

| Si            | Diamond cubic     | 5.430                | 2.6 x 10 <sup>-6</sup>               |

| Ge            | Diamond cubic     | 5.657                | 5.8 x 10 <sup>-6</sup>               |

| GaAs          | Zincblende        | 5.653                | 6.8 x 10 <sup>-6</sup>               |

It can be seen from this table that there are significant disparities in the crystal structure, lattice constants, and thermal expansion coefficients for all three semiconducting materials. Data is presented for germanium (Ge) along with Si and GaAs because of the importance of Ge as a natural intermediary material between Si substrates and III-V GaAs alloys, as will be explained below. The various differences between the three materials will be considered separately for each of the properties discussed above.

#### 1.1.1. Differences in Lattice Constant

The lattice constant of bulk Si is 4.1% smaller than GaAs at room temperature. This mismatch in lattice constants means that a GaAs crystal deposited epitaxially on a Si substrate would require the periodic removal of a plane of Ga or As atoms every 25 atomic rows to match up coherently with the atoms of the Si crystal substrate below it. Unfortunately for experimentalists, there are few useful III-V semiconductor alloys with lattice mismatch on Si smaller than that of GaAs. A plot of common semiconductor lattice constants vs. bandgap energies is presented in Figure 1.2. It can be seen from this figure that GaAs is the closest match to Si of the direct-bandgap (light-emitting) binary compound semiconductors.

Figure 1.2: Bandgap energy vs. lattice constant for a variety of common semiconducting materials.

If lattice mismatch is unavoidable for III-V on Si epitaxy, it is important to consider how this mismatch will be accommodated during semiconductor crystal growth. When a semiconductor film with a lattice constant  $a_f$  is deposited on a semiconductor substrate with a lattice constant  $a_s$ , a misfit strain is developed which can be defined as:

$$f = \frac{a_s - a_f}{a_f}$$

For thin films with low amounts of mismatch, this misfit strain will be accommodated by an elastic deformation of the deposited film lattice. Epitaxial films with lattice constants larger than the substrate lattice will be compressively strained, while films with smaller lattice constants will undergo tensile strain. In either case, the film material will remain coherently linked to the substrate, with each substrate atom uniquely bonded to corresponding atoms in the film above it. With higher amounts of mismatch, or thicker epitaxial films, the misfit strain at the interface will increase until it exceeds the elastic strength of the coherent semiconductor-semiconductor bonds. At this point, the film will undergo a plastic deformation resulting in the formation of broken bonds and noncoherent crystal defects at the substrate-film interface. A simplified cross-section showing the elastic and plastic stages of misfit strain accommodation for a compressive semiconductor film on a thick substrate is shown in Figure 1.3.

Figure 1.3: Elastic strain and plastic relaxation at a mismatched semiconductor interface. Note the two misfit dislocations at the mismatched interface after plastic relaxation.

It can be seen from the figure that the deposited semiconductor film will accommodate misfit strain plastically by forming a one-dimensional line of broken atomic bonds at the substrate-film interface. This one- dimensional defect structure is known as a misfit dislocation and will extend linearly along the interface to terminate at a free surface of the crystal. For the (001)-oriented surfaces typically used in semiconductor device epitaxy, the  $\{111\}<110>$  slip system of the mismatched crystal will encourage misfit dislocation lines to align themselves along the low-energy [110] and  $[1 \overline{1} 0]$  directions. Once formed, dislocation lines can propagate by dislocation glide along a mismatched interface.

The formation and propagation of misfit dislocations is thermodynamically governed by a local energy balance between the misfit strain energy relieved by dislocation formation and the energy cost of extending an array of misfit dislocations along a coherent crystal interface. This energy balance can expressed mathematically by equating the misfit strain energy per unit area of a strained film,

$$E_s = \varepsilon^2 Y h$$

with the energy per unit area of an orthogonal array of misfit dislocations:

$$E_{d} = D \frac{b}{b_{eff}} \left( 1 - v \cos^{2} \theta \right) (f - \varepsilon) \left[ \ln \left( \frac{h}{b} \right) + 1 \right]$$

The total strain in the epitaxial film is defined as  $\varepsilon = f \cdot \delta$ , where *f* is the elastic misfit strain and  $\delta$  is the accommodated plastic strain. Physically  $\delta$  represents the strain which has been relieved by existing misfit dislocations. *Y* is the biaxial Young's modulus of the strained film, *h* is the film thickness, v is Poisson's ratio in the epitaxial film, and *b* is the Burgers vector in the strained layer. The angle between the Burgers vector and the interface plane is  $\theta$ , and *D* is the average shear modulus at the interface, defined as:<sup>8</sup>

$$D = \frac{G_f G_s b}{\pi (G_f + G_s)(1 - \nu)}$$

where G<sub>f</sub> and G<sub>s</sub> are the respective shear moduli of the epitaxial film and the substrate.

The energy of misfit strain relaxation and dislocation array formation can be shown to be exactly balanced at a specific critical thickness,  $h_c$ . Mismatched films grown below this critical thickness should remain elastically strained without forming misfit dislocations, while films grown above this critical thickness can relax plastically by generating an array of [110] and [1  $\overline{10}$ ] dislocation lines. Matthews has derived the following expression for critical thickness based on the material terms defined above:<sup>9</sup>

$$h_{c} = \frac{D(1 - v \cos^{2} \theta) \left(\frac{b}{b_{eff}}\right) \left[\ln\left(\frac{h_{c}}{b}\right) + 1\right]}{2Yf}$$

This expression gives the thermodynamic critical thickness for a mismatched film on a semiconductor substrate. As a point of reference, the thermodynamic critical thickness for GaAs grown on bulk Si is about 2 nm.

Kinetic factors also play a role in determining how misfit dislocations form in semiconductors. Kinetic activation barriers can inhibit the formation and glide motion of misfit dislocations, and lead to metastable super-critical strained films on mismatched substrates under certain growth conditions. Models explaining the kinetic factors involved in misfit strain relaxation have been developed but require extensive experimental fitting to be useful for predicting kinetic critical thickness values in real systems.<sup>10</sup> It is therefore reasonable to treat the Matthews equilibrium critical thickness as a firm lower bound for misfit strain relaxation in strained layer systems, and to use this critical thickness relationship to better understand the formation and propagation of misfit dislocations in these systems.

All misfit dislocations must terminate at a free surface at the boundaries of a semiconductor wafer. While some dislocations will form or propagate at the edges of the wafer, most misfit lines will terminate in segments that originate at the semiconductor film surface. The misfit dislocation lines lying in the plane between the substrate and epitaxial film will connect to the surface via threading dislocation segments, which propagate by dislocation climb from the strained misfit interface along {111} planes in diamond-cubic or zincblende materials. Threading dislocations are one-dimensional crystallographic dislocations that do not relieve strain in a semiconductor. Importantly for epitaxial integration experiments, threading dislocations act as non-radiative recombination centers in optoelectronic devices and thus their presence is not welcome for III-V on Si heteroepitaxial structures.

Misfit and threading dislocation segments can be nucleated in a variety of ways in mismatched semiconductor films above the equilibrium critical thickness. At very high misfit strains, misfit dislocation loops can form spontaneously via homogenous nucleation, although this mechanism rarely occurs in practical growth systems. Much more common is heterogeneous nucleation of dislocation loops at surface imperfections or at point defects in the film. Misfit dislocation segments can also nucleate at preexisting threading dislocations climbing upwards from the substrate. A schematic representation of the different ways dislocations can nucleate in a mismatched system is shown in Figure 1.4.

Figure 1.4: Options for dislocation nucleation at a mismatched semiconductor interface. (a.) Homogeneous nucleation, (b.) Heterogeneous nucleation at a surface defect, (c.) Heterogeneous nucleation at an interface defect, and (d.) Heterogeneous nucleation at a pre-existing thread. Heterogeneous mechanisms will dominate in practical growth systems.

Equilibrium thermodynamics can be used to estimate the total density of dislocations that will form for a mismatched semiconductor with a given misfit strain. For any strain state, the average spacing of an array of parallel misfit dislocations, *S*, can be estimated for a given amount of accommodated strain  $\delta$ , as: <sup>11</sup>

$$S = \frac{b}{2\delta}$$

This equation assumes that all strain-relieving dislocations have Burgers vectors 60° from the [110] dislocation directions. For GaAs grown directly on Si, the complete relaxation of the 4.1% lattice mismatch would demand a dislocation spacing S = 100 Å. Equilibrium theory shows that some elastic strain will remain in a mismatched film after relaxation. Work by a number of authors has shown that the relaxation of a mismatched epitaxial film can be limited by kinetic barriers and dislocation-dislocation interactions.<sup>12, 13</sup>

Dislocation-dislocation interactions can play an important role in the relaxation behavior of mismatched epitaxial films. Gliding coplanar misfit dislocation lines can attract or repel each other depending on the sign of their respective Burgers vectors. Threading dislocations can also be attracted or repelled by the strain fields of adjacent dislocations, and research has shown that threading dislocation motion in a growing film can be easily impeded by the tangling of groups of threading dislocations into macroscopic dislocation pileups.<sup>14</sup> If threading dislocations are immobilized, their attached misfit segments cannot continue extending to relieve misfit strain and more dislocations must be nucleated to relieve the remaining strain. Thus the total threading dislocation density in a mismatched epitaxial film will multiply rapidly if dislocations are able to interact and pin each other during growth. Dislocation multiplication is largely responsible for the observed rapid rise in threading dislocation densities with increasing lattice mismatch in real semiconductor systems.

Finding ways to reduce the density of threading dislocations at a given mismatch strain level is an important goal for successful strained-layer heteroepitaxy. As mentioned above, threading dislocations can act as non-radiative recombination centers in optoelectronic devices, because the localized mid-bandgap energy levels in the dislocation cores will act as highly efficient trap states for injected minority carriers. These traps can dramatically reduce the overall minority carrier lifetime in the material.<sup>15</sup> Localized mid-bandgap energy levels in threading dislocations (along with a tendency of these dislocations to getter metal impurity atoms) can lead to short-circuit behavior in active electronic junctions, and scattering from dislocation cores can lead to decreases in effective carrier mobility and transconductance for majority carrier devices.<sup>16</sup>

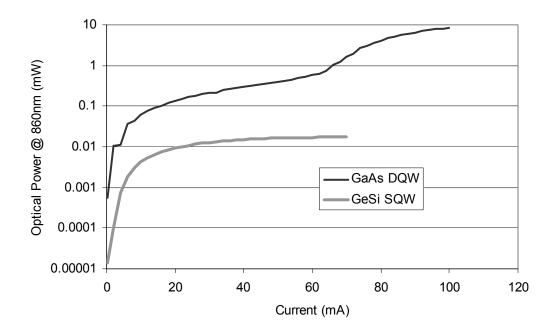

Reductions in minority carrier lifetime are especially detrimental for semiconductor lasers. A semiconductor laser requires a population inversion of minority carriers in the active layers of the laser structure before it can demonstrate a positive gain coefficient and lasing action. No other optoelectronic device requires such a high density of non-equilibrium carriers in its active region. If the minority carrier lifetime is reduced by dislocations in a laser structure, more and more of the injected minority carriers will recombine non-radiatively before they can reach the local densities necessary for population inversion. Early work with GaAs-based semiconductor lasers on GaAs substrates has shown that threading dislocation densities greater than 10<sup>6</sup> cm<sup>-2</sup> can reduce minority carrier lifetimes in these materials enough to completely prohibit laser operation.<sup>17</sup> This requirement is not a problem for today's commercial GaAs substrates, which typically demonstrate total surface dislocation densities less than 100 cm<sup>-2</sup>. However the threading dislocation densities for GaAs epitaxial films deposited directly on Si substrates are typically closer to 10<sup>9</sup> cm<sup>-2</sup>, highlighting one of the chief issues facing any attempt to successfully integrate GaAs-based laser diodes on Si substrates. Another unique issue for integrated laser structures on substrates with high dislocation densities is the potential movement of these dislocations during laser operation to form dark line defects in operating devices. Dark line defects (DLDs) have been reported by a number of authors as one of the chief failure mechanisms in operating GaAs-based semiconductor lasers.<sup>18,19</sup> These defects are composed of clusters of extended dislocation loops that propagate into the active regions of operating devices, where they increase the local rate of non-radiative recombination and thus produce dark lines visible in electroluminescence or electron beam induced current (EBIC) micrographs.<sup>20</sup> An EBIC image of a typical DLD dislocation cluster moving into a bright GaAs/AlGaAs laser active region is shown in Figure 1.5.

Top view EBIC

# Figure 1.5: Representative EBIC image of a DLD dislocation cluster propagating from the edge of a GaAs/AlGaAs laser to the bright active region in the center. The three dark circles at the top of the image are metal contacts. (image courtesy of Yellen<sup>18</sup>)

Two types of dark line defects are commonly found in failed lasers: <100> DLDs perpendicular to the interface planes, which climb from the edges of the cladding layer through the device layer, and <110> DLDs, which lie parallel to the interface planes and move into the active region by gliding from device edges. For both types of defect, the chief mechanism for the initial dislocation propagation and multiplication is believed to be recombination-enhanced defect reactions. As modeled by Weeks,<sup>21</sup> energy liberated by the non-radiative recombination of injected electrons and holes at pre-existing defect sites in an operating laser is converted into localized lattice vibrations. These local lattice vibrations are energetic enough to trigger new defect reactions, such as vacancy-interstitial pair formation and impurity or defect diffusion. Recombination enhanced

defect reactions (REDR) which occur at the newly created defect sites create additional defects in the same manner, and the cycle repeats in a positive feedback reaction as the DLDs climb or glide deeper into the device. At high densities, these dark line defects will lead to rapid increases in the threshold current for laser operation, and irreversible laser failure. Directly correlating the initial threading dislocation density in epitaxial laser structures with the dark-line defect density that develops in operating devices is difficult. While the initial nucleation of new dislocation loops will depend directly on the density of threading dislocation sites in the laser active region, the rapid multiplication of these loops into DLD structures will be controlled mostly by the temperature of the surrounding lattice and the injected carrier density in the operating device. Thus increasing threading dislocation densities in a semiconductor laser structure can be expected to increase the density of nucleated DLDs, but cannot be directly correlated to the final DLD density after failure without factoring in the kinetics of the defect multiplication reactions which follow nucleation.

Controlling DLD failure in operating GaAs lasers epitaxially integrated on Si substrates will place constraints on the maximum allowed threading dislocation densities in these devices, and will demand relatively low laser threshold current densities and low amounts of resistive self-heating in the operating devices fabricated on Si substrates.

Efforts to reduce the threading dislocation density, increase the minority carrier lifetime, and control dark line defect propagation in GaAs devices on Si by a number of different experimental methods will be discussed below.

#### 1.1.2. Differences in Thermal Expansion Behavior

The thermal expansion coefficient of GaAs is almost 60% larger than the Si expansion coefficient at room temperature. This difference narrows only slightly at the elevated temperatures typical for semiconductor heteroepitaxy. The consequences of this thermal expansion mismatch can be significant. When a GaAs film is deposited on a thick Si substrate, it will relax at the growth temperature, forming an array of misfit and threading dislocations as detailed in the previous section. When the substrate is cooled after growth, the difference in thermal expansion coefficients will mean that the GaAs epilayers will shrink much more quickly than the Si substrate lattice below them.

Assuming that the mismatched GaAs film has completely relaxed at the growth temperature, a tensile thermal expansion strain will thus be developed in the cooling film which will be proportional to the total change in temperature of the system:

$$\varepsilon_t = \int_{T_0}^T \left[ \alpha_s(T) - \alpha_f(T) \right] dT$$

where T and  $T_0$  are the final and initial temperatures of the growth system, respectively, and  $\alpha_s$  and  $\alpha_f$  are the temperature-dependent coefficients of thermal expansion for the substrate and film. The actual dependence of the thermal expansion coefficients on temperature for GaAs and Si are small enough that they can be ignored to first order, leading to a simplified expression for the thermal mismatch strain as a function of the total change in reactor temperature  $\Delta T$ :

$$\varepsilon_t = (\alpha_s - \alpha_f) \Delta T$$

For a GaAs film on a Si substrate at a typical reactor growth temperature of 700 °C, the total tensile strain developed on cooldown to room temperature will be 0.26%. This strain is significantly less than the total material mismatch strain for these two materials, but still significant enough to cause some important effects in heteroepitaxial layers. Because this strain develops as the epitaxial layers are cooled from the growth temperature, dislocation relaxation mechanisms are much less efficient at relieving the resulting tension. Dislocation glide velocity decreases exponentially with decreasing temperature, and thus the residual thermal expansion strain that remains in a heteroepitaxial film at room temperature can be as high as 90% of the total thermal mismatch.<sup>22</sup> This trapped tensile strain can lead to the formation of microcracks in the epitaxial film, with microcrack nucleation behavior governed by an effective critical cracking thickness similar to that discussed for misfit dislocation formation previously.<sup>23</sup> Thermal mismatch strain can also act to reduce the critical thickness of strained quantum well laser structures fabricated on Si substrates, as will be discussed in Chapter 4.

Some practical ways to account for thermal mismatch strain in the GaAs/Si materials system have been proposed. Slower cooling rates after growth can encourage additional tensile strain reduction by pre-existing misfit dislocations, although practical considerations limit how slowly temperature can be reduced.<sup>24</sup> Growth or device

fabrication on reduced areas can increase the total thickness of the epitaxial layers that can be grown without crack formation.<sup>25,26</sup> The deliberate inclusion of compressive material strain in an epitaxial layer at the growth temperature can act to balance the tensile thermal strain which develops in this layer during cooldown, resulting in a strainfree room-temperature structure.<sup>27</sup> This process has been demonstrated in the thermally mismatched Ge/Si system, but introduces potential complications for high-temperature post-growth device processing and also for the growth of additional epitaxial layers above the strain-balanced film layers.

#### 1.1.3. Differences in Crystal Structure

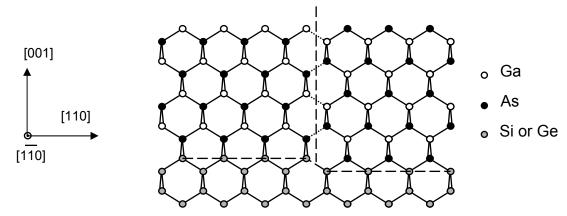

In addition to the fundamental differences in lattice constant and thermal expansion coefficients that separate Si from GaAs-based semiconductor alloys, there is also the issue of the differing crystal structures of these two semiconductor materials. Because of its compound nature, a GaAs crystal unit cell cannot preserve the inherent symmetry of the Si diamond-cubic lattice. The different bonding energies of Ga and As atoms in relation to each other will give the GaAs crystal structure a more ionic character than Si, and will result in an asymmetric polarity that can cause problems when integrated on a non-polar Si substrate lattice. GaAs crystal structures deposited on Ge semiconductor substrates will face the same polarity problems, irrespective of the smaller lattice constant and thermal expansion mismatches that separate these materials. A complete understanding of polar-on-nonpolar epitaxy is a critical challenge for successful compound semiconductor integration.

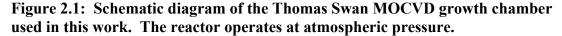

The zincblende unit cell of a GaAs crystal can be imagined as two interpenetrating but chemically distinct face-centered-cubic (fcc) sublattices. This arrangement is different from the diamond-cubic Si or Ge unit cell, which can be simplified into two interpenetrating fcc sub-lattices that are functionally and chemically identical. When a GaAs unit cell is deposited on a Si substrate, the GaAs unit cell can therefore be aligned in one of two distinct and perpendicular orientations. Which orientation is produced will depend on the underlying arrangement of the Si substrate atoms and the growth environment of the GaAs film. A surface variation such as an atomic-level step on the Si substrate can cause the GaAs film above this step to rotate its orientation, and thus lead to the formation of a propagating boundary layer between two distinct GaAs domains. The boundary that separates these adjacent domains will not consist of regular GaAs cation-anion bonds, but instead take the form of an electrically charged 2-dimensional plane of anion-anion or cation-cation bonds. This defective antiphase boundary (APB) plane can serve as a large-scale trapping site to reduce minority carrier lifetime in GaAs device layers,<sup>28</sup> and also act to increase majority-carrier scattering in electronic circuits which include APB defects.<sup>29</sup> A schematic drawing of an APB boundary formed by Ga-Ga bonds above a single-atom substrate step is shown in Figure 1.6.

Figure 1.6: Antiphase boundary in GaAs formed by a single-atom step on the substrate surface.