# THE DETERMINATION OF SEMICONDUCTOR BAND GAP STRUCTURE AND SURFACE STATES USING TUNNELING SPECTROSCOPY

bу

#### STUART MARSHALL SPITZER

- S.B., Massachusetts Institute of Technology (1966)

- S.M., Massachusetts Institute of Technology (1967)

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 1971

| Signature of Author Department of Electrical Engineering, Oct | tober 2, 197 | <b>7</b> 0            |

|---------------------------------------------------------------|--------------|-----------------------|

| Certified by 1 1 1 1                                          |              |                       |

| Accepted by                                                   | •            | Archives  MAR 22 1971 |

## THE DETERMINATION OF SEMICONDUCTOR BAND GAP STRUCTURE AND SURFACE STATES USING TUNNELING SPECTROSCOPY

by

#### STUART MARSHALL SPITZER

Submitted to the Department of Electrical Engineering on October 2, 1970 in partial fulfillment of the requirments for the Degree of Doctor of Philosophy.

#### **ABSTRACT**

The mechanisms of metal-insulator-semiconductor (MIS) tunneling were explored in order to develop a spectroscopic technique. The theory of MIS tunneling was developed through an extension and modification of the theory of metal-insulator-metal (MIM) tunneling.

Special preparation procedures were formulated so that the thin insulator aluminum-silicon dioxide-silicon devices could be fabricated. A low temperature, nitric acid treatment was developed for the growth of a 100A silicon dioxide layer with dielectric breakdown strength exceeding  $5x10^6$  V/cm. Test apparatus was designed to permit automatic low current, phase and frequency sensitive measurements. All measurements were made on the (111) face of non-degenerate silicon at room temperature. Experiment and theory were in good agreement.

A novel effect was discovered in p-type devices, whereby the conduction mechanism was tunneling in the enhancement mode, and Schottky emission in the depletion mode. The device current was found to be relatively temperature insensitive in the enhancement mode, but exhibited a positive temperature dependence in the depletion mode.

Phase measurements of the tunnel current led to a new interpretation of the AC tunnel mechanism. The tunnel transit time was very small, so the surface state recombination-generation time became the factor limiting tunnel charge transfer. At frequencies, however, charge transfer was incomplete and the tunnel current decreased with frequency.

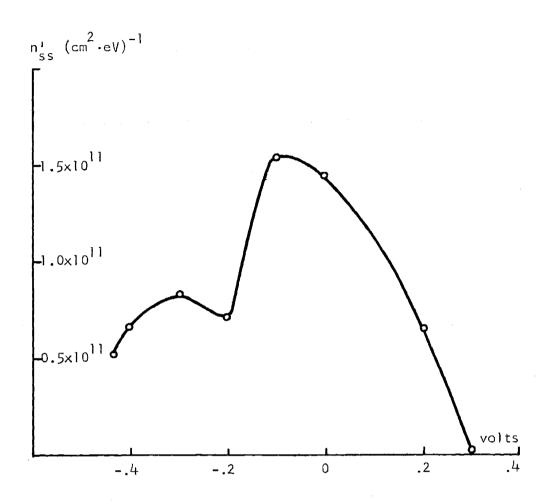

Tunneling spectroscopy was demonstrated to be very valuable in obtaining significant data on silicon surfaces, such as the type of material (n- or p- type), surface potential, surface charge  $(10^{10} - 10^{12}/\text{cm}^2)$ , and surface state distribution  $(10^{11}/\text{cm}^2)$ . These data were shown to be in agreement with the literature. A continuous rather than discrete surface state distribution was observed.

Thesis Supervisor: Harry C. Gatos

Title: Professor of Electrical Engineering

### Table of Contents

| Chapter<br>number |                                                        | Page<br>number |

|-------------------|--------------------------------------------------------|----------------|

|                   | Abstract                                               | 2              |

|                   | Table of Contents                                      | 4              |

| •                 | List of Figures                                        | 6              |

|                   | List of Tables                                         | 11             |

|                   | Acknowledgements                                       | 12             |

| I.                | INTRODUCTION                                           | 13             |

|                   | A. Semiconductor Surfaces                              | 13             |

|                   | B. Techniques for Examining Semiconductor Surfaces     | 15             |

| II.               | THEORETICAL CONSIDERATIONS                             | 16             |

|                   | A. Tunneling Theory                                    | 16             |

|                   | B. Tunneling Spectroscopy                              | 21             |

|                   | Surface Consideration in MIS Tunneling                 | 27             |

|                   | C. Other Conduction Mechanisms in MIS Structures       | 34             |

| III.              | EXPERIMENTAL PROCEDURE                                 | 40             |

|                   | A. Sample Preparation                                  | 40             |

|                   | Oxidation                                              | 40             |

|                   | Electrical Contact                                     | 41             |

|                   | Processing of Silicon Wafers for Tunnel<br>Test Device | 42             |

|                   | B. Measurement Techniques                              | 47             |

| IV.               | RESULTS AND DISCUSSION                                 | 55             |

|                   | A. Results                                             | 55             |

|                   | DC Measurements                                        | 56             |

|                   | AC Measurements                                        | 61             |

| Chapter<br>number |      |             |                      |         | Page<br>number |

|-------------------|------|-------------|----------------------|---------|----------------|

|                   | В.   | Interpreta  | tion of Experimental | Results | 67             |

|                   |      | DC Meas     | surements            |         | 67             |

|                   |      | AC Meas     | surements            |         | 73             |

| ٧.                | SUMI | MARY        |                      |         | 84             |

|                   |      | Suggestion  | ns for Future Work   |         | 88             |

|                   | App  | endices     |                      |         | 90             |

|                   |      | Appendix A  | 1                    |         | 90             |

|                   |      | Appendix B  | 3                    |         | 100            |

|                   |      | Appendix C  | ;                    |         | 101            |

|                   |      | Appendix D  | )                    |         | 107            |

|                   |      | Appendix E  |                      |         | 108            |

|                   |      | Appendix F  |                      |         | 109            |

|                   | Bib  | liography   |                      |         | 158            |

|                   | Biog | graphical N | lote                 |         | 161            |

## List of Figures

| Figure<br>number | Title                                                                                                                                                                                                                                                      | Page<br>number |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 1                | Tunneling Barrier in the MIM Structure                                                                                                                                                                                                                     | 20             |

| 2                | Room Temperature Tunneling Characteristics for the $\mathrm{Al-Al}_2\mathrm{O}_3$ -Al Structure                                                                                                                                                            | 20             |

| 3                | Energy Band Diagram for the MIS Structure                                                                                                                                                                                                                  | 22             |

| 4                | Electron Tunneling in a P-type Semiconductor MIS Structure with Positive and Negative Bias on the Metal Plate                                                                                                                                              | 22             |

| 5                | Electron Tunneling in an N-type Semiconductor MIS Structure with Negative and Positive Bias on the Metal Plate                                                                                                                                             | 24             |

| 6                | Effect of Positive Bias on Metal Plate of N-type MIS Structure                                                                                                                                                                                             | 28             |

| . 7              | Effect of Negative Bias on Field Plate of N-type MIS Structure                                                                                                                                                                                             | 31             |

| 8                | Electric Field Strength in Insulator of MIS<br>Structure as a Function of Allpied Voltage                                                                                                                                                                  | 32             |

| 9                | I-V Tunneling Characteristics Predicted from MIS Structures with Surface States                                                                                                                                                                            | 33             |

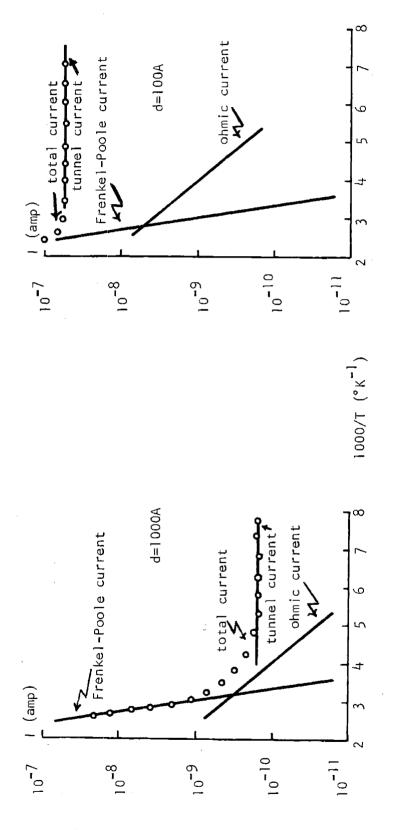

| 10               | Current-Temperature Characteristics of an Au-Si3N4-Si Structure at Applied Field of 5x10 <sup>6</sup> V/cm<br>The Tunnel Current Predominates at Low Tempera-ture; the High Temperature Range can be Extended by Using a Thinner Insulator (Reference 39). |                |

| 11               | Photo-Lithographic Masks for Device Patterns -<br>Mask 1                                                                                                                                                                                                   | 45             |

| 12               | Photo-Lithographic Masks for Device Patterns<br>Mask 2                                                                                                                                                                                                     | 45             |

| 13               | Top View of Processed Wafers                                                                                                                                                                                                                               | 48             |

| 14               | Cross Section View of Processed Wafers                                                                                                                                                                                                                     | 48             |

| 15               | Simple Measurement Circuit for DC I-V Characteristics                                                                                                                                                                                                      | 50             |

| 16               | Bridge Circuit Used for AC and DC Measurements on the Tunnel Test Devices                                                                                                                                                                                  | 50             |

| 17 | Integrator Circuit Used to Provide Slow DC Sweep<br>to Tunnel Test Devices                                   | 52  |

|----|--------------------------------------------------------------------------------------------------------------|-----|

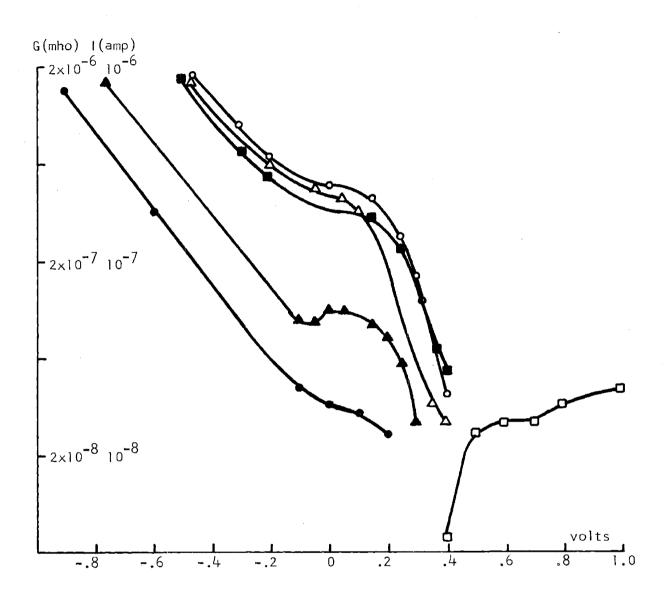

| 18 | I-V Characteristics and Conductance - Wafer N-73                                                             | 57  |

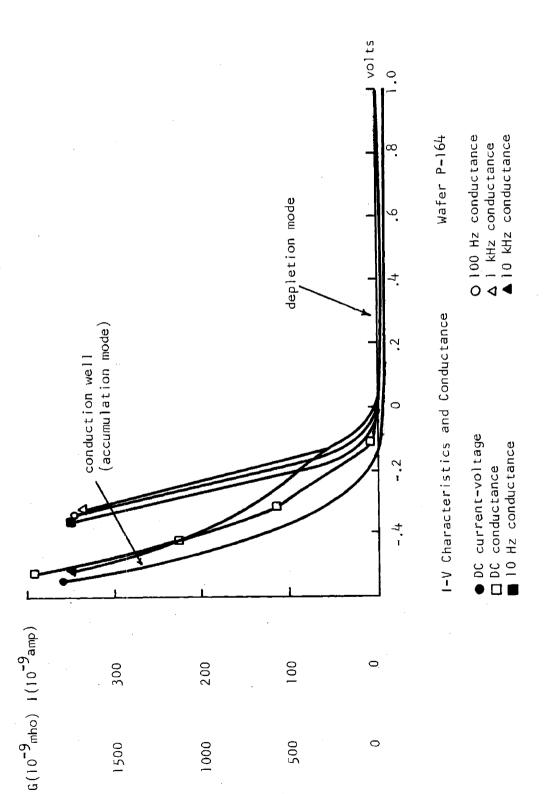

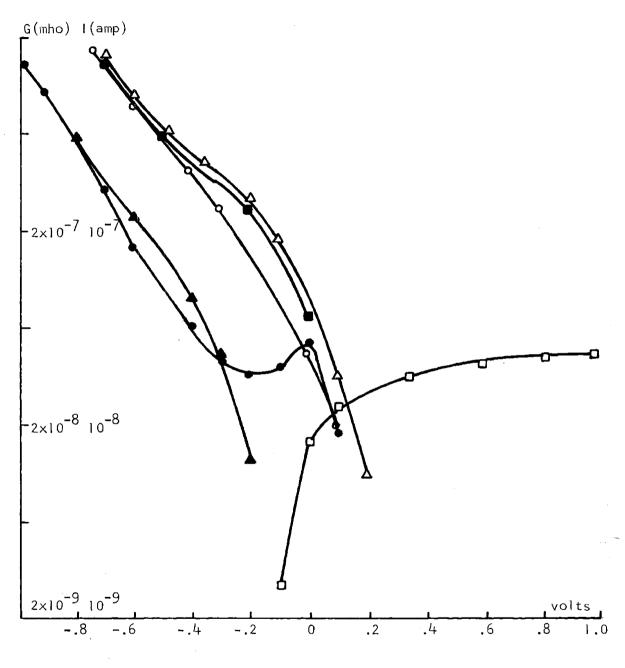

| 19 | I-V Characteristics and Conductance - Wafer P-164                                                            | 59  |

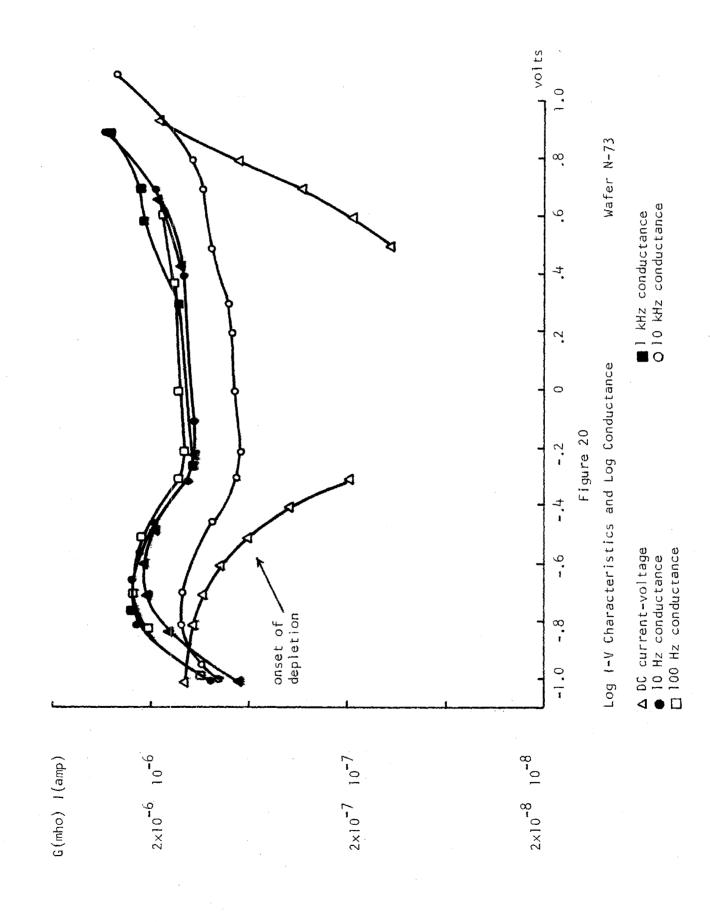

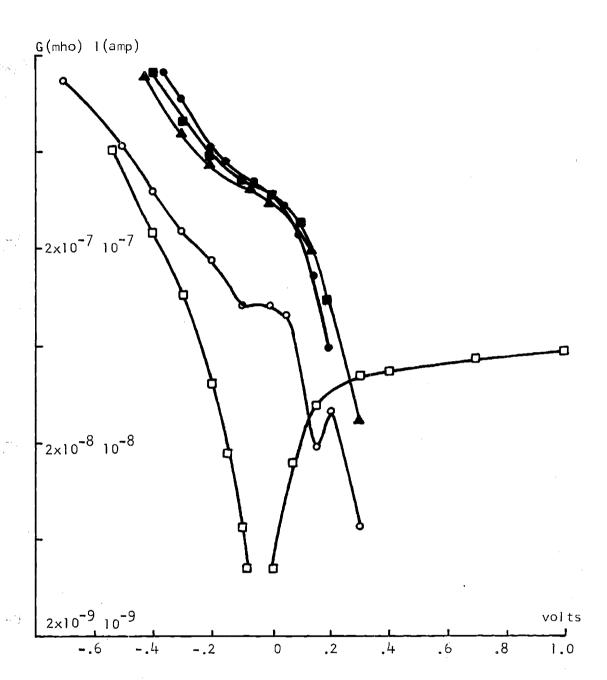

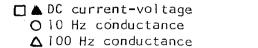

| 20 | Log I-V Characteristics and Log Conductance -<br>Wafer N-73                                                  | 62  |

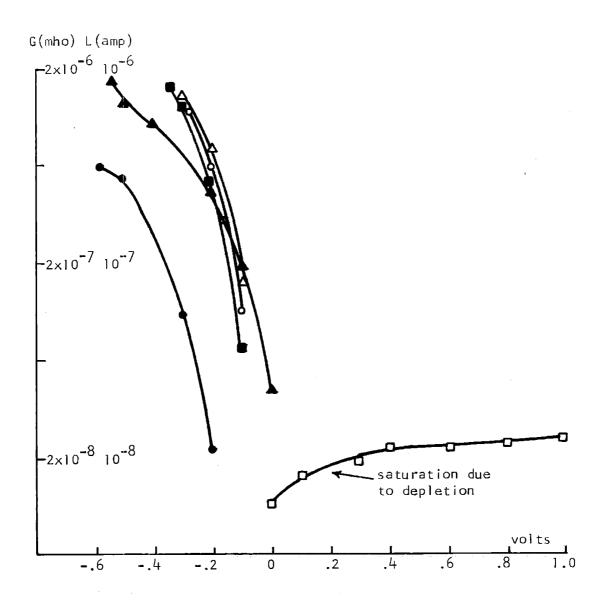

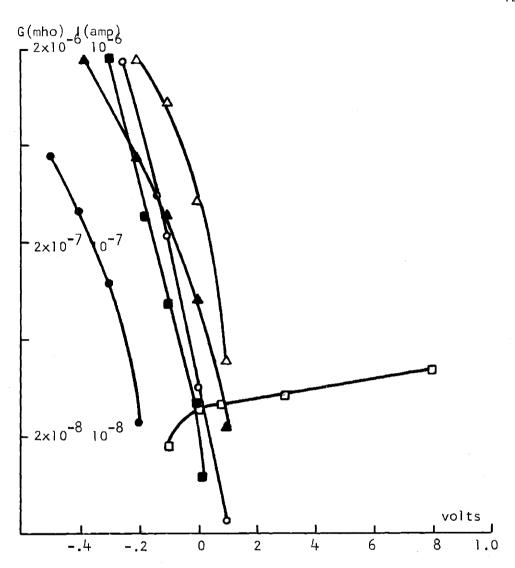

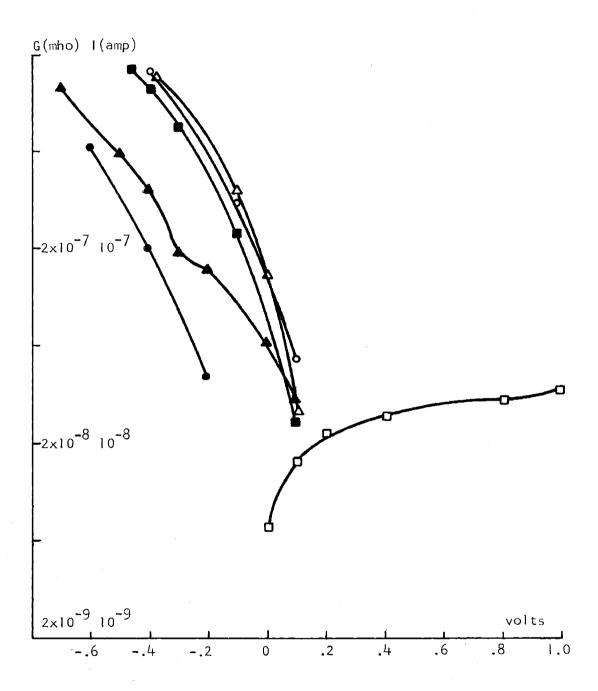

| 21 | Log I-V Characteristics and Log Conductance -<br>Wafer P-164                                                 | 63  |

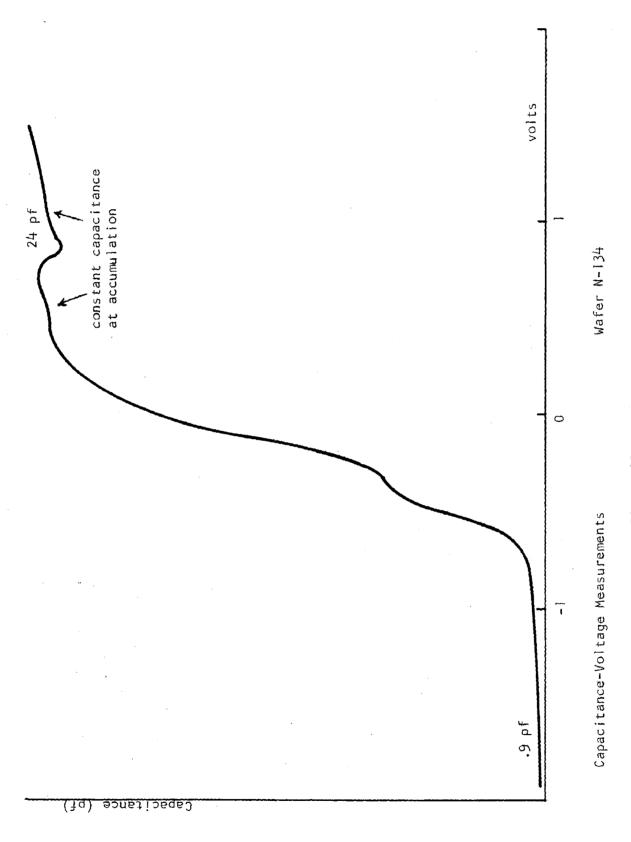

| 22 | Capacitance - Voltage Measurements - Wafer N-134                                                             | 65  |

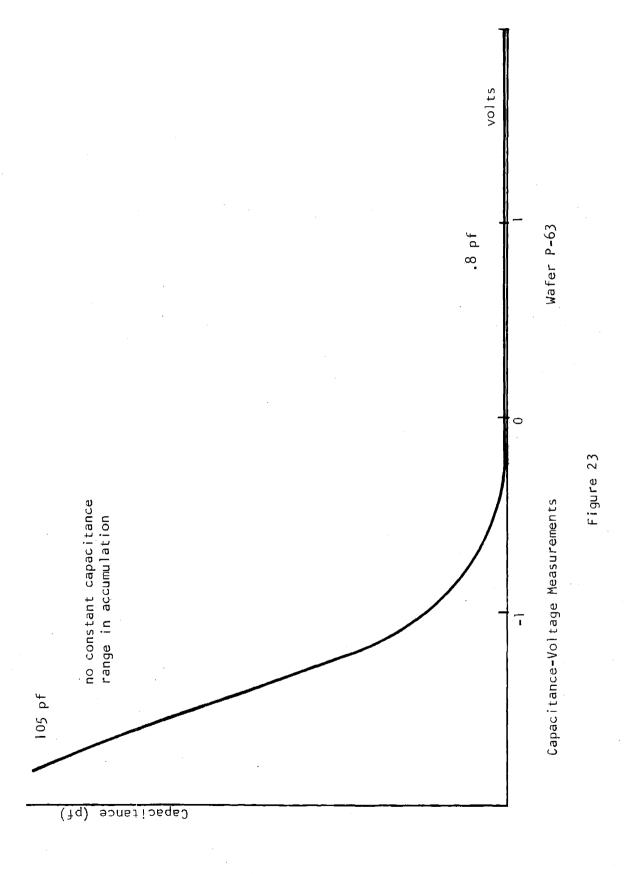

| 23 | Capacitance - Voltage Measurements - Wafer P-63                                                              | 66  |

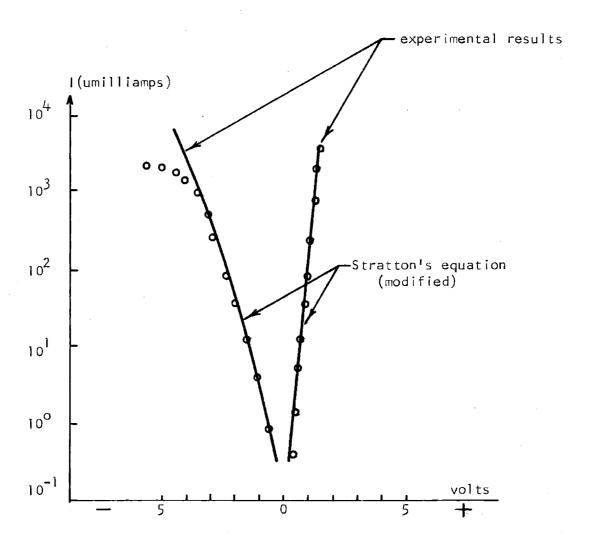

| 24 | Experimental I-V Characteristics of the MIS Structure                                                        | 70  |

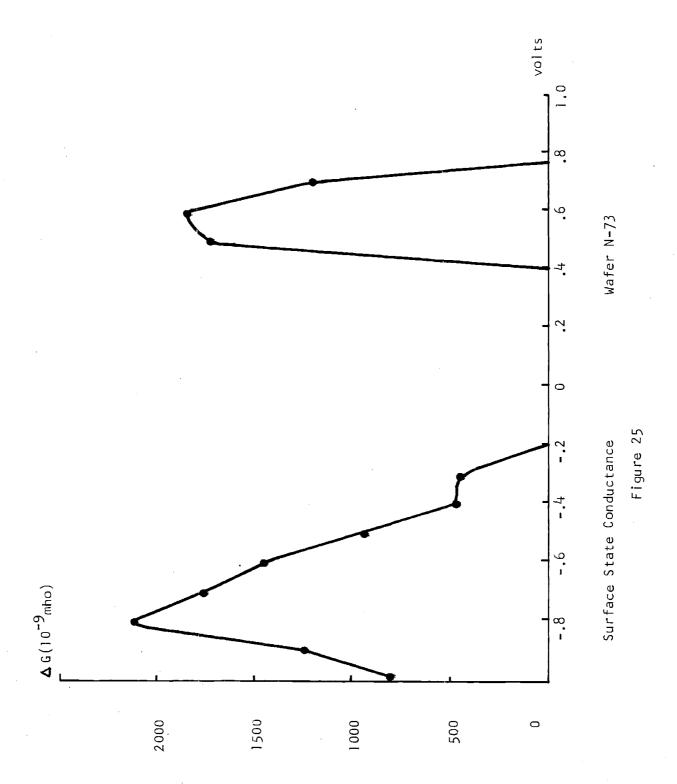

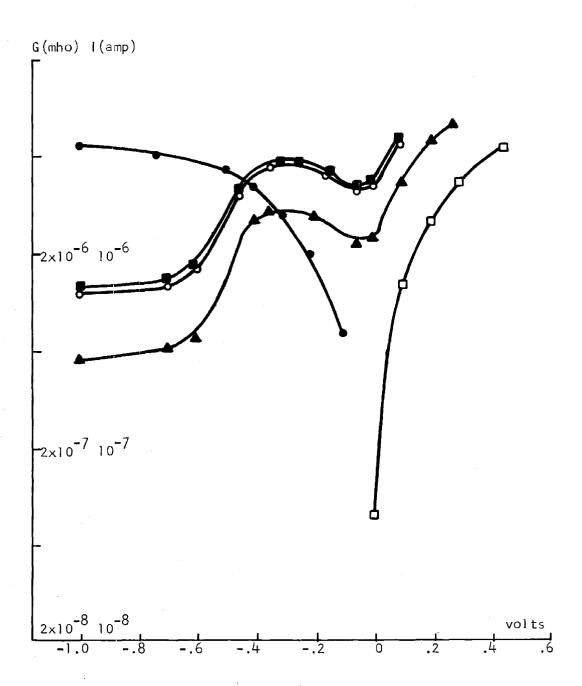

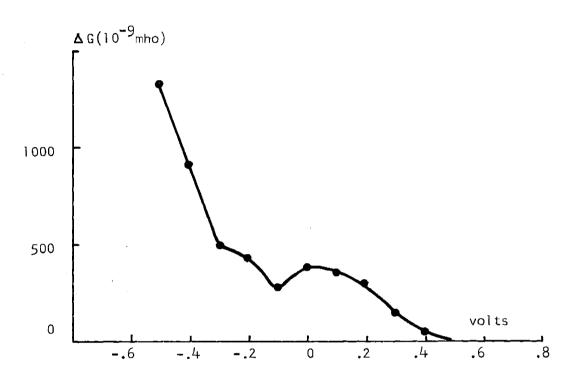

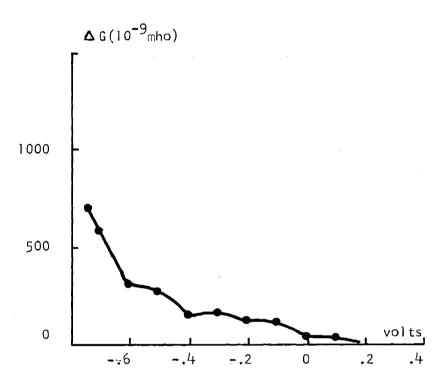

| 25 | Surface State Conductance - Wafer N-73                                                                       | 78  |

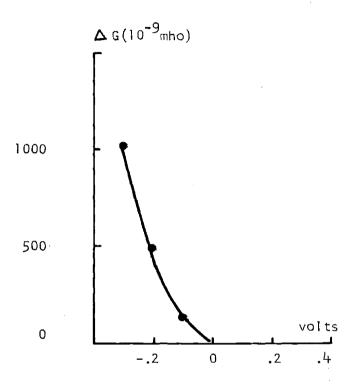

| 26 | Surface State Conductance - Wafer P-164                                                                      | 79  |

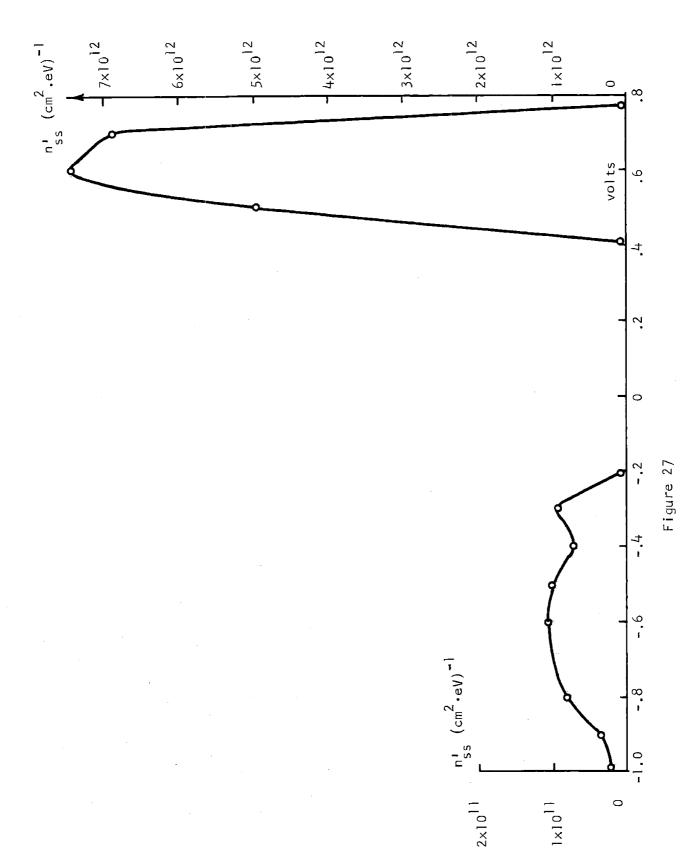

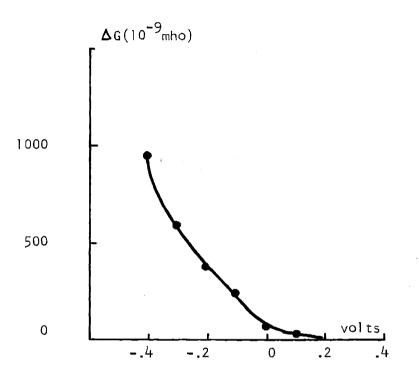

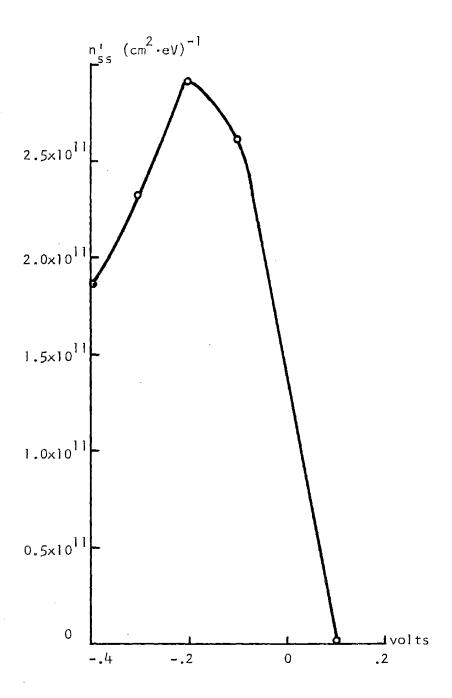

| 27 | Surface State Distribution as Determined from Tunnel Conductance - Wafer N-73                                | 81  |

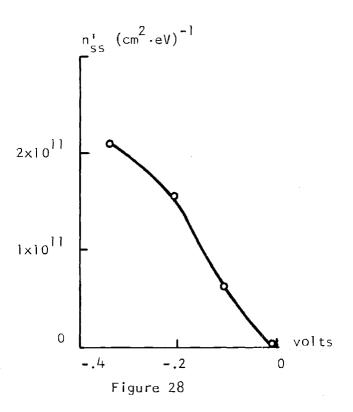

| 28 | Tunnel Conductance - Wafer P-164                                                                             | 82  |

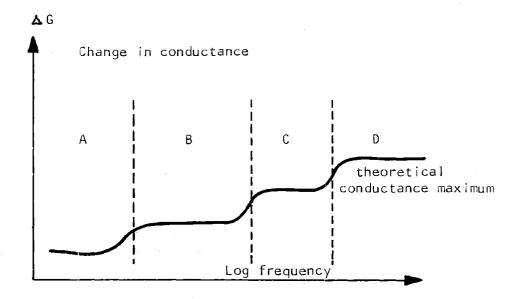

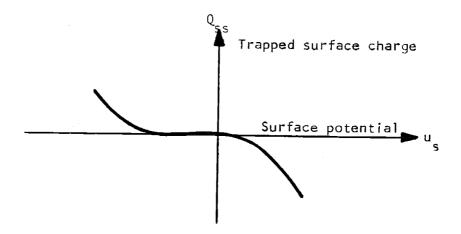

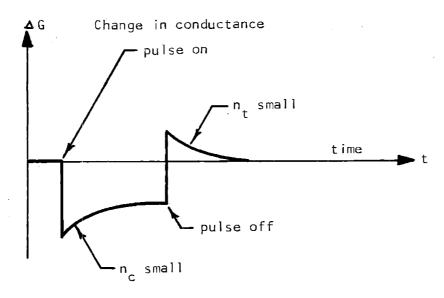

| A1 | Time Dependence of Surface States Shown Through<br>the Frequency Response of the Senusoidal Field<br>Effect  | 91  |

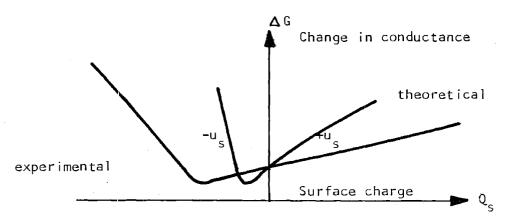

| A2 | Sinusoidal Field Effect to Determine Surface Potential $\mathbf{u}_{s}$ and Trapped Charge $\mathbf{Q}_{ss}$ | 92  |

| A3 | Trapped Surface Charge as a Function of Surface<br>Potential                                                 | 94  |

| A4 | Pulse Field Effect to Determine Density of States                                                            | 95  |

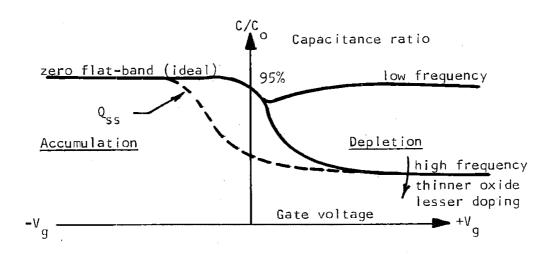

| A5 | Capacitance - Voltage Characteristics                                                                        | 95  |

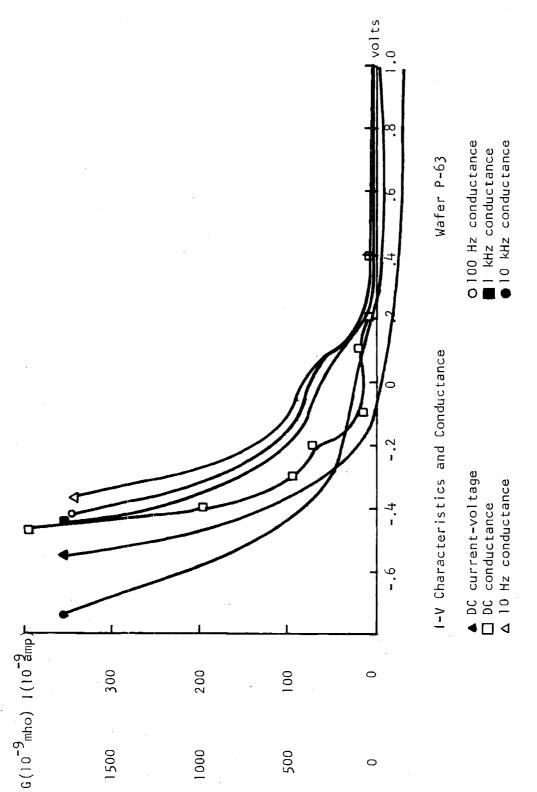

| F1 | I-V Characteristics and Conductance - Wafer P-63                                                             | 110 |

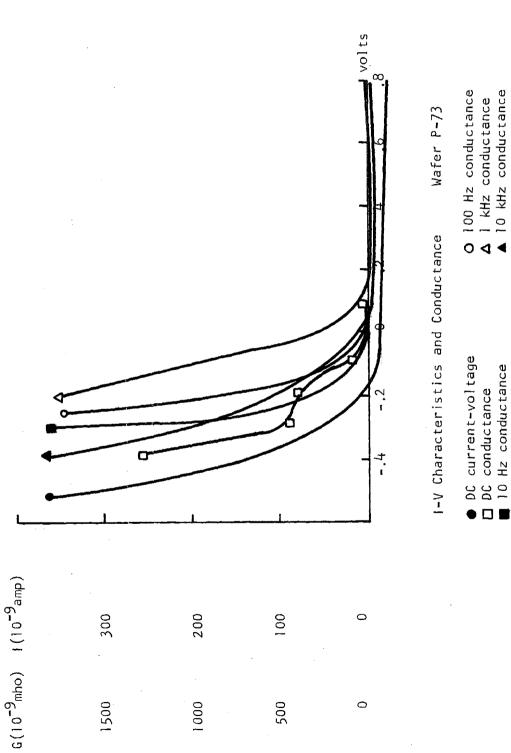

| F2 | I-V Characteristics and Conductance - Wafer P-73                                                             | 111 |

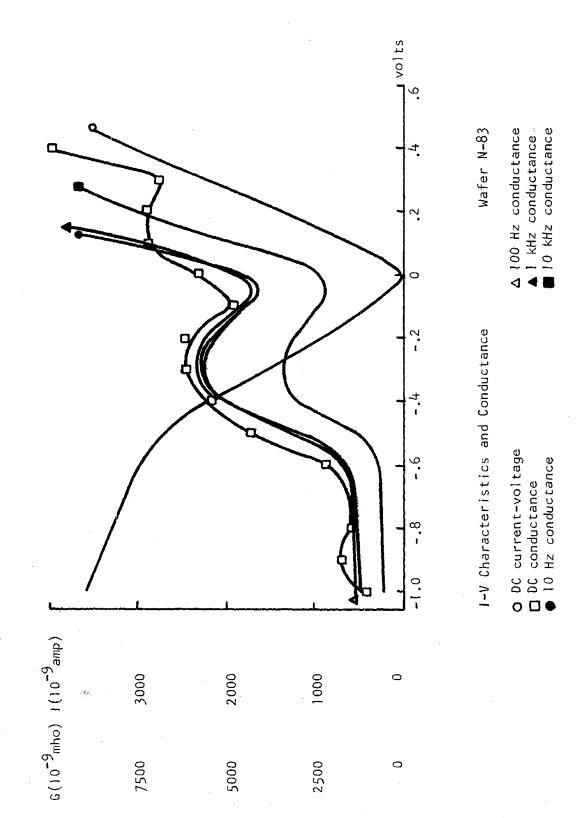

| F3 | I-V Characteristics and Conductance - Wafer N-83                                                             | 112 |

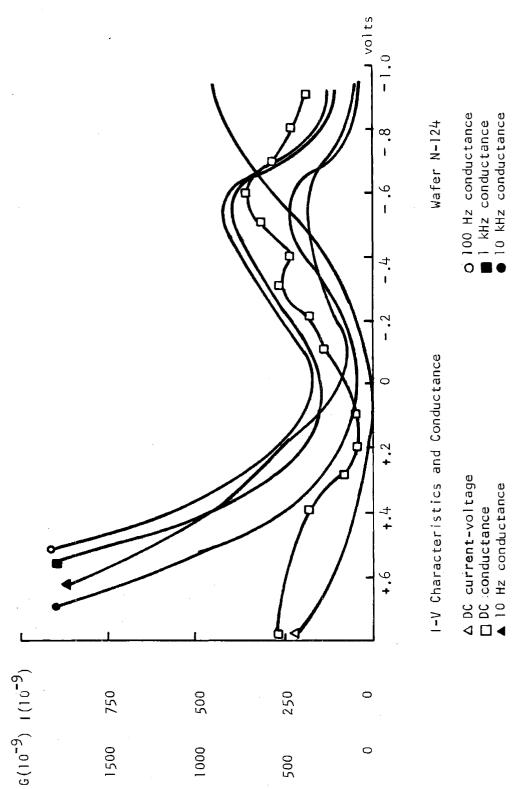

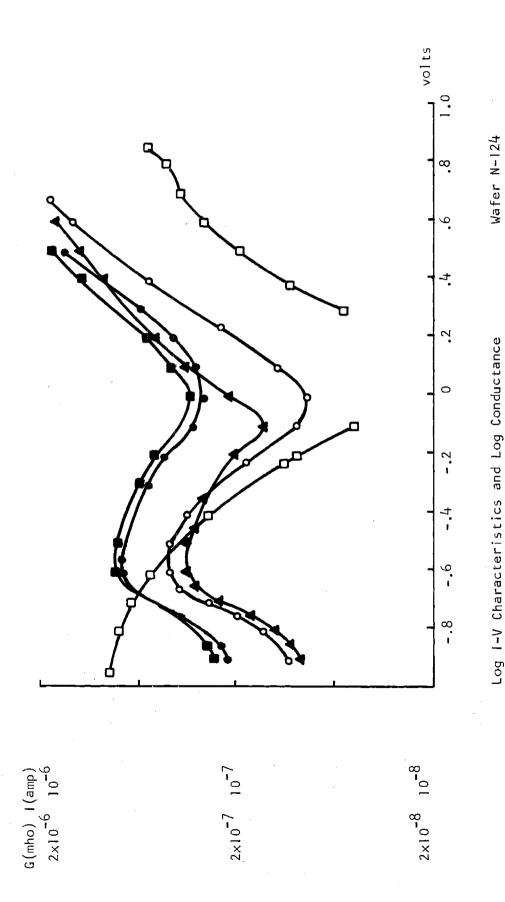

| F4 | I-V Characteristics and Conductance - Wafer N-124                                                            | 113 |

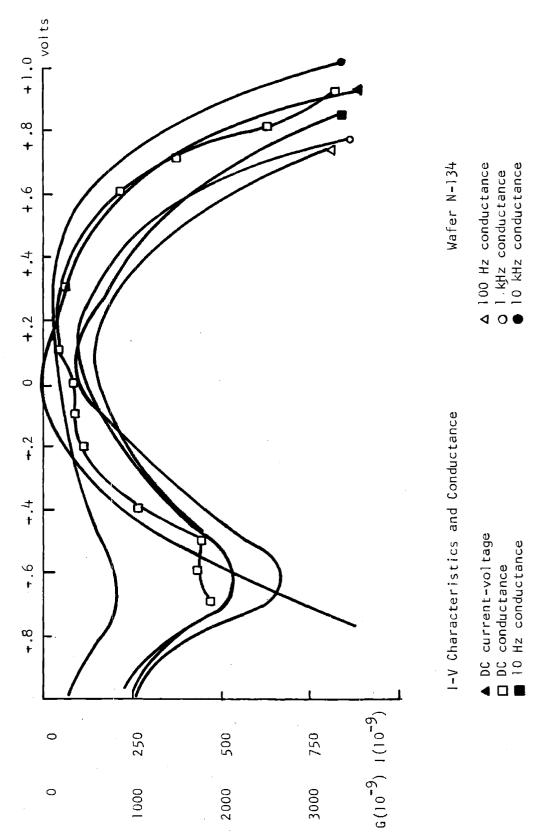

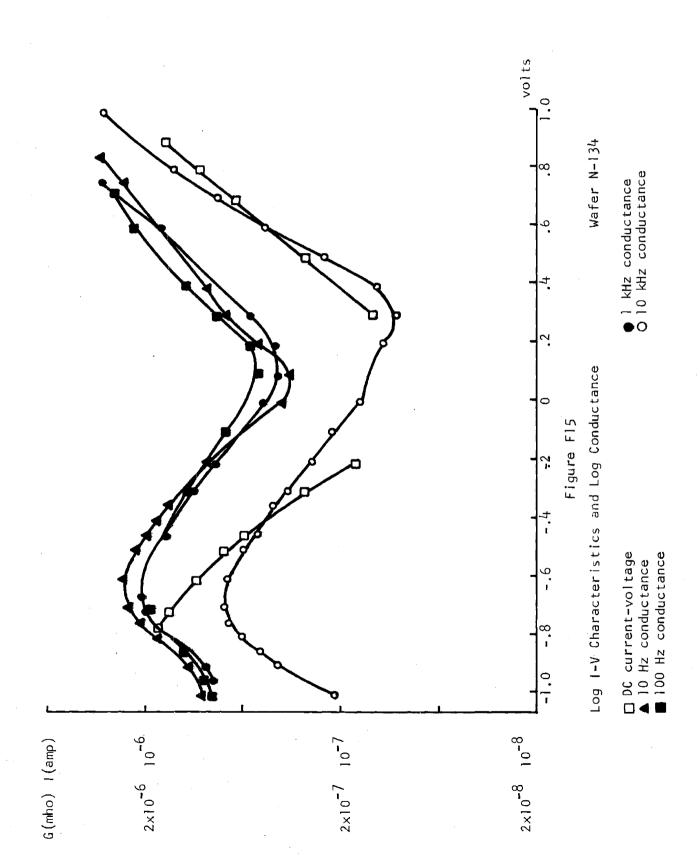

| F5   | I-V Characteristics and Conductance - Wafer N-134            | 114 |

|------|--------------------------------------------------------------|-----|

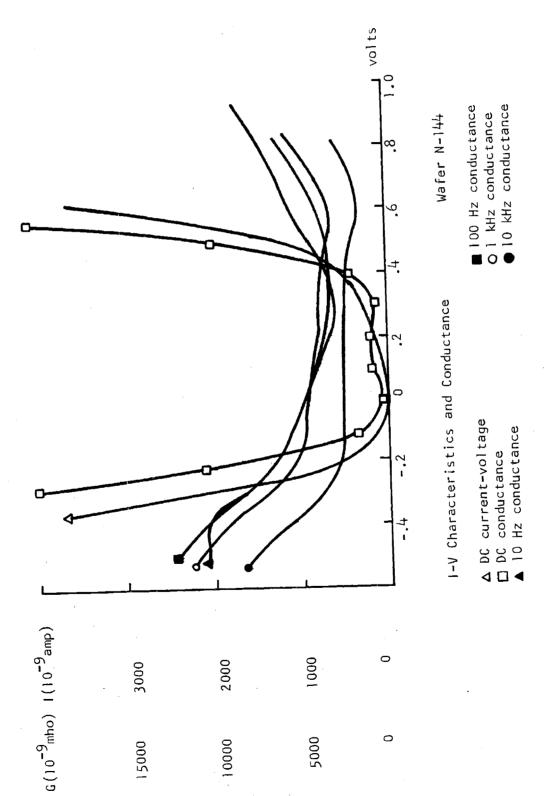

| F6   | I-V Characteristics and Conductance - Wafer N-144            | 115 |

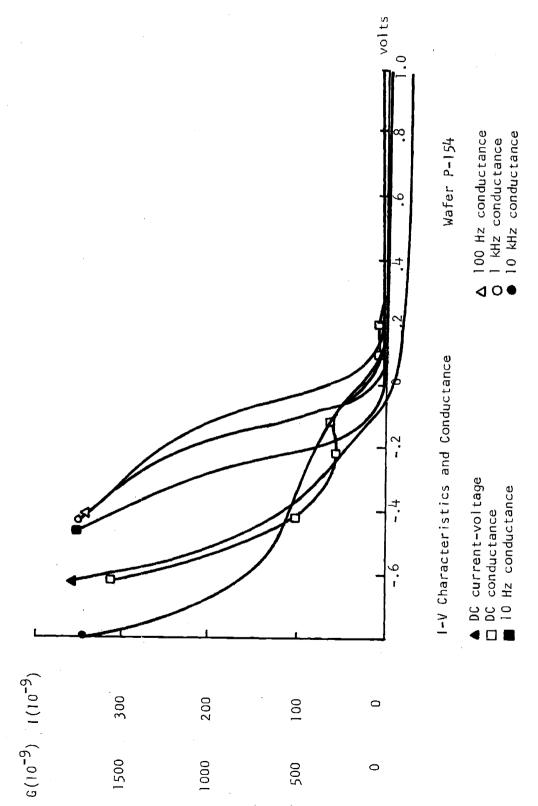

| F7 . | I-V Characteristics and Conductance - Wafer P-154            | 116 |

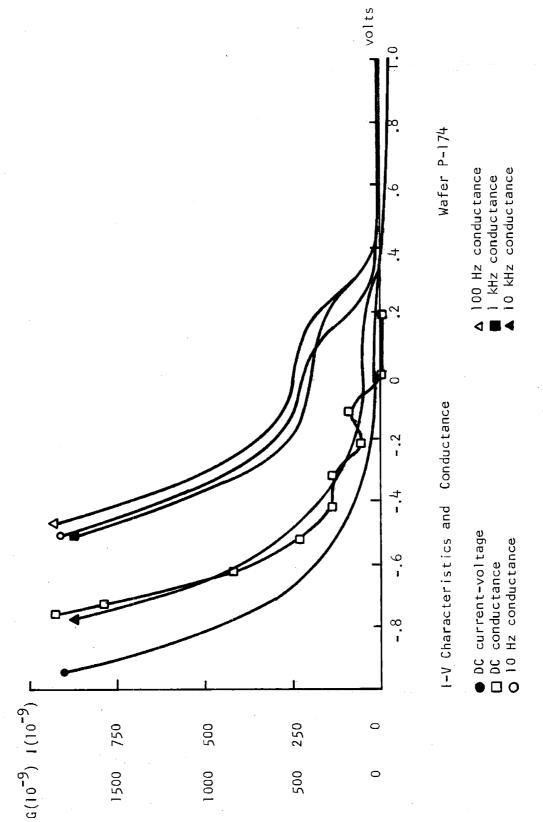

| F8   | I-V Characteristics and Conductance - Wafer P-174            | 117 |

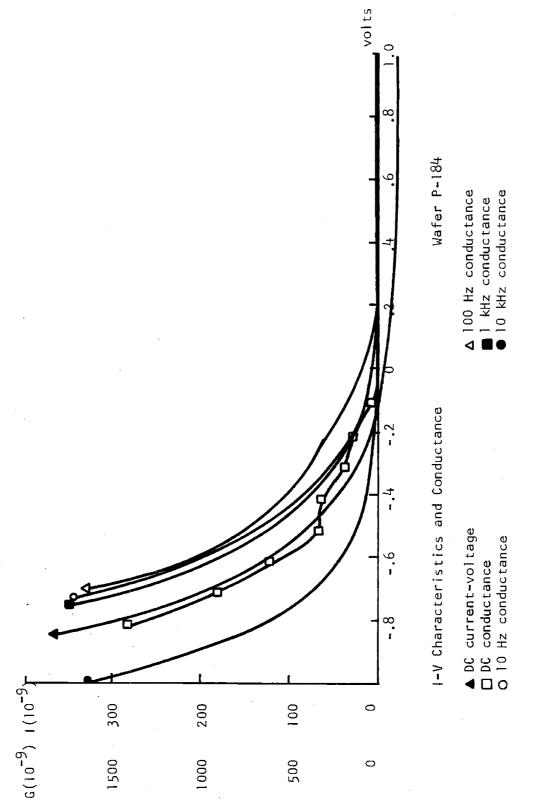

| F9   | I-V Characteristics and Conductance - Wafer P-184            | 118 |

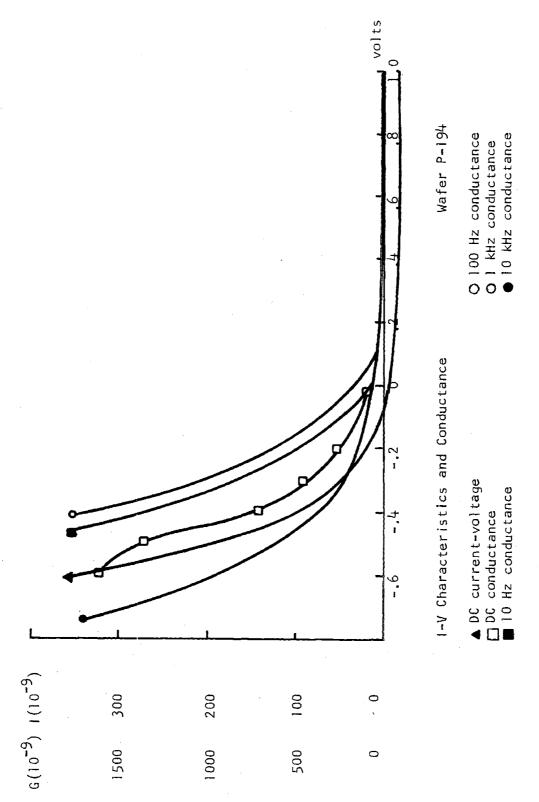

| F10  | I-V Characteristics and Conductance - Wafer P-194            | 119 |

| F11  | Log I-V Characteristics and Log Conductance -<br>Wafer P-63  | 120 |

| F12  | Log I-V Characteristics and Log Conductance -<br>Wafer P-73  | 121 |

| F13  | Log I-V Characteristics and Log Conductance -<br>Wafer N-83  | 122 |

| F14  | Log I-V Characteristics and Log Conductance -<br>Wafer N-124 | 123 |

| F15  | Log I-V Characteristics and Log Conductance -<br>Wafer N-134 | 124 |

| F16  | Log I-V Characteristics and Log Conductance -<br>Wafer N-144 | 125 |

| F17  | Log I-V Characteristics and Log Conductance -<br>Wafer P-154 | 126 |

| F18  | Log I-V Characteristics and Log Conductance -<br>Wafer P-174 | 127 |

| F19  | Log I-V Characteristics and Log Conductance -<br>Wafer P-184 | 128 |

| F20  | Log I-V Characteristics and Log Conductance -<br>Wafer P-194 | 129 |

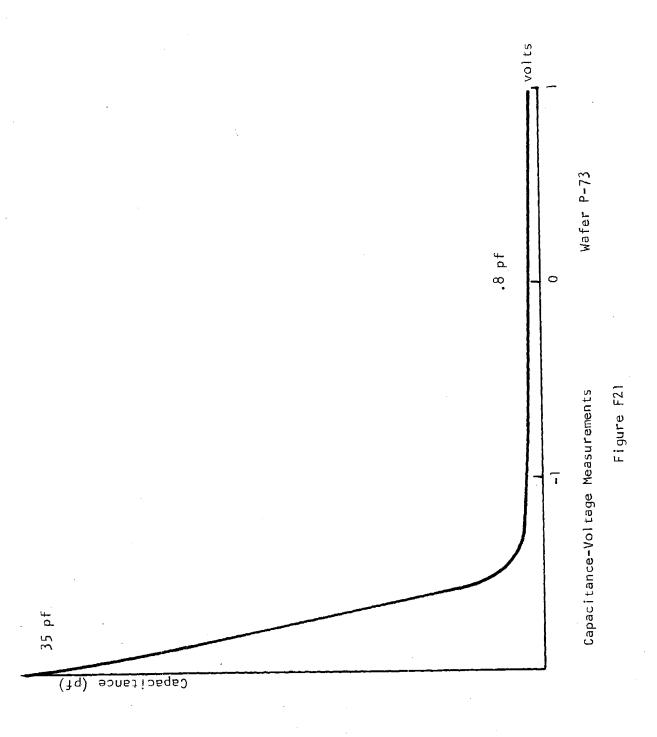

| F21  | Capacitance - Voltage Measurements - Wafer P-73              | 130 |

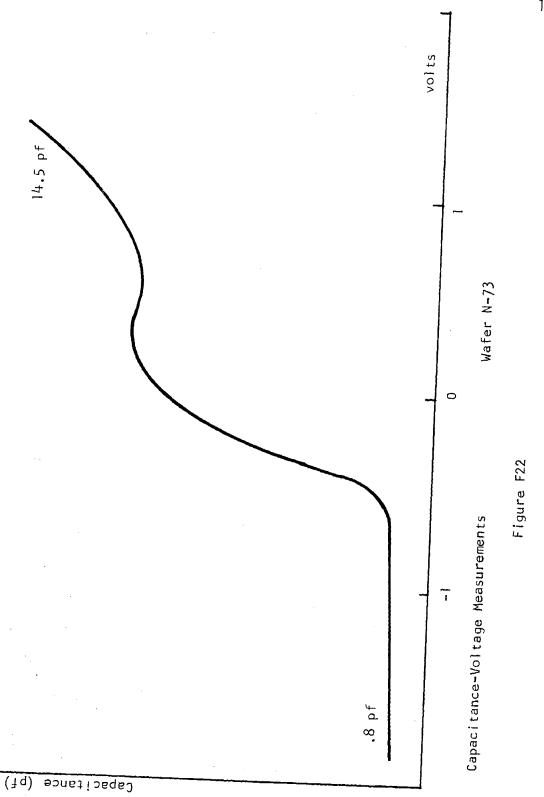

| F22  | Capacitance - Voltage Measurements - Wafer N-73              | 131 |

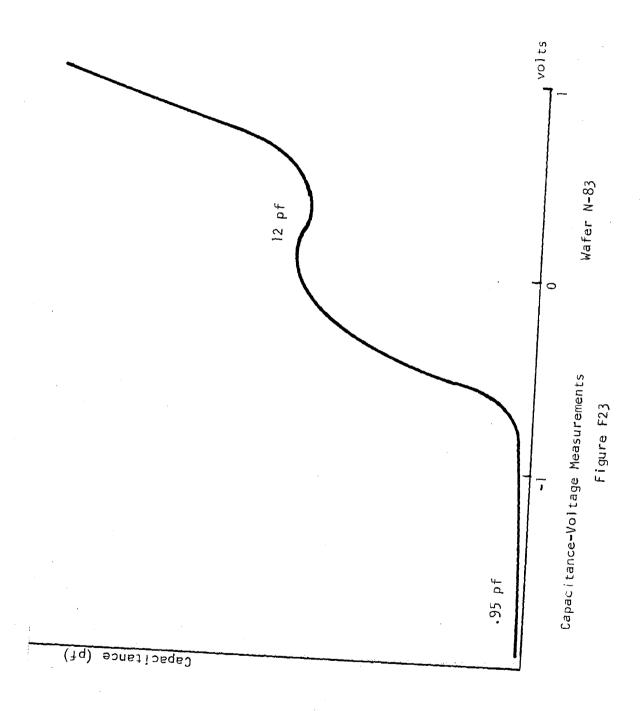

| F23  | Capacitance - Voltage Measurements - Wafer N-83              | 132 |

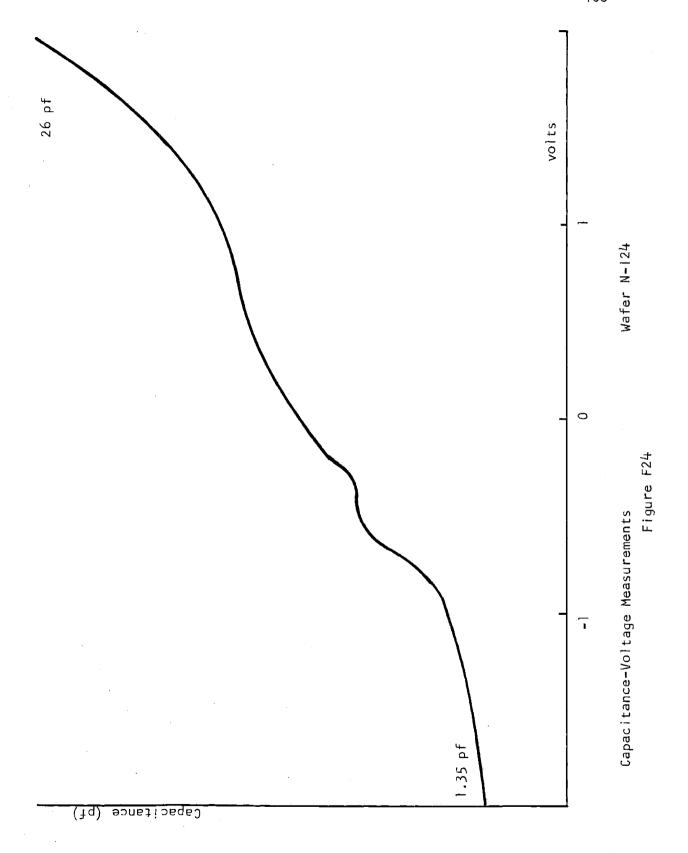

| F24  | Capacitance - Voltage Measurements - Wafer N-124             | 133 |

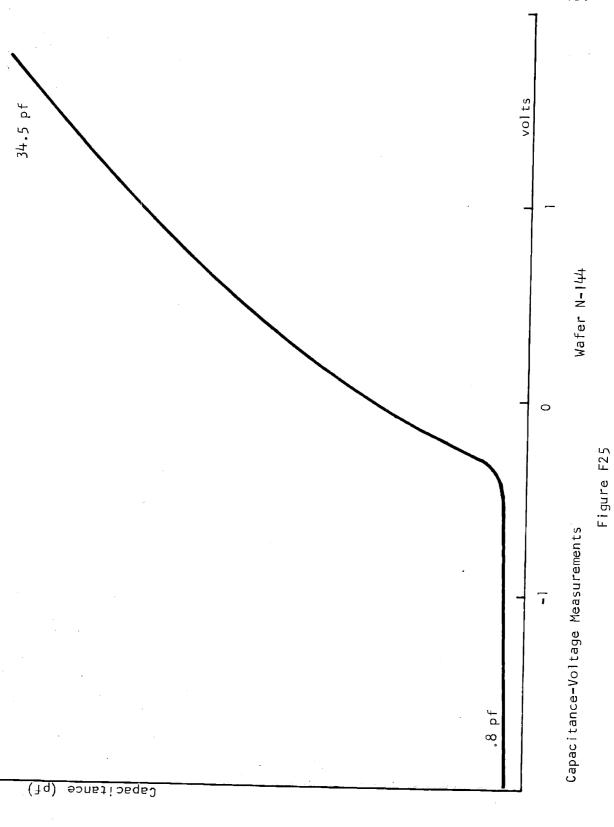

| F25  | Capacitance - Voltage Measurements - Wafer N-144             | 134 |

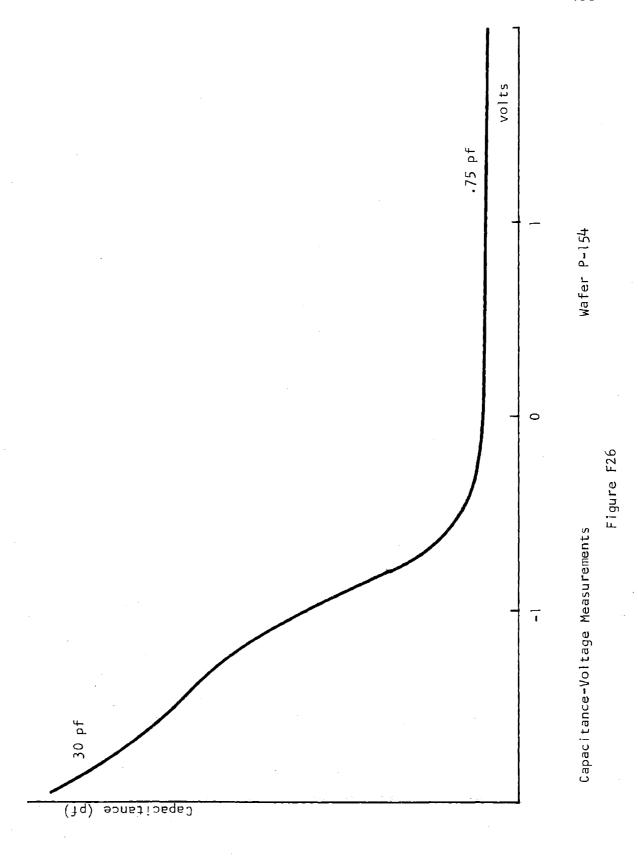

| F26  | Capacitance - Voltage Measurements - Wafer P-154                               | 135 |

|------|--------------------------------------------------------------------------------|-----|

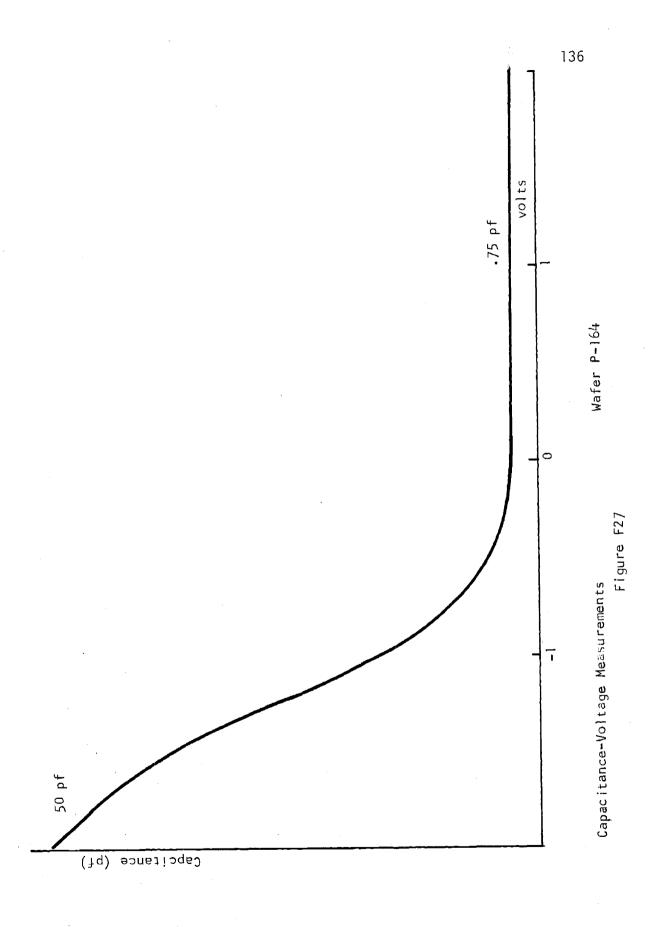

| F27  | Capacitance - Voltage Measurements - Wafer P-164                               | 136 |

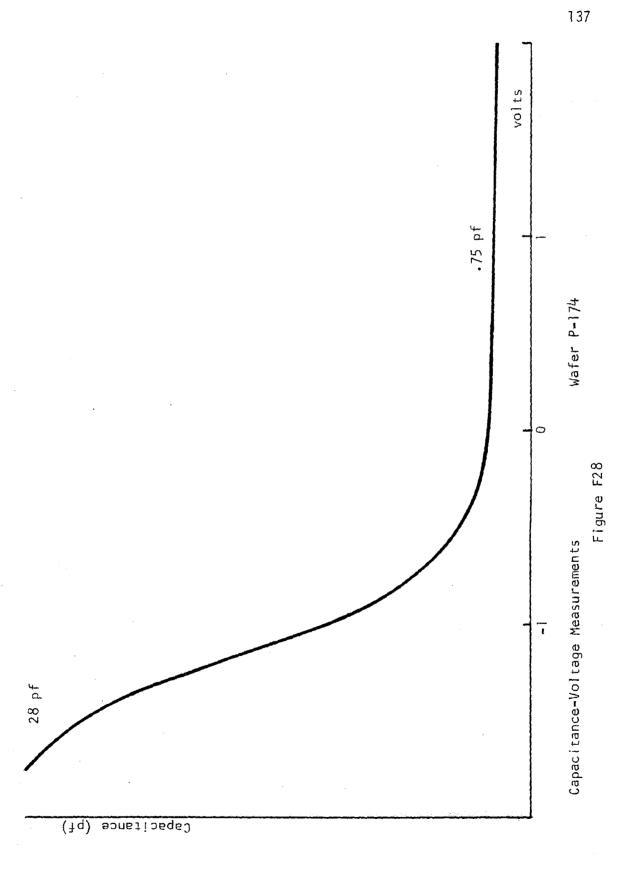

| F28  | Capacitance - Voltage Measurements - Wafer P-174                               | 137 |

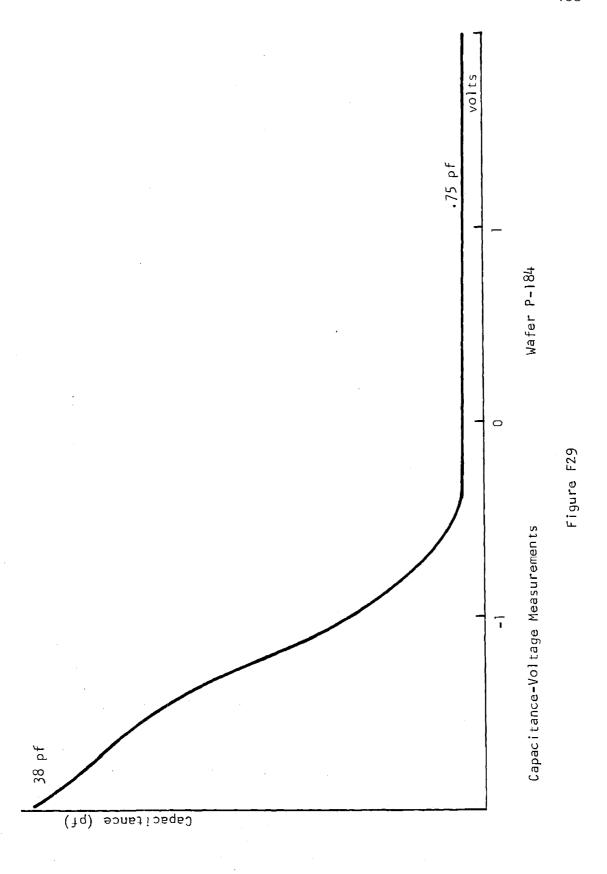

| F29  | Capacitance - Voltage Measurements - Wafer P-184                               | 138 |

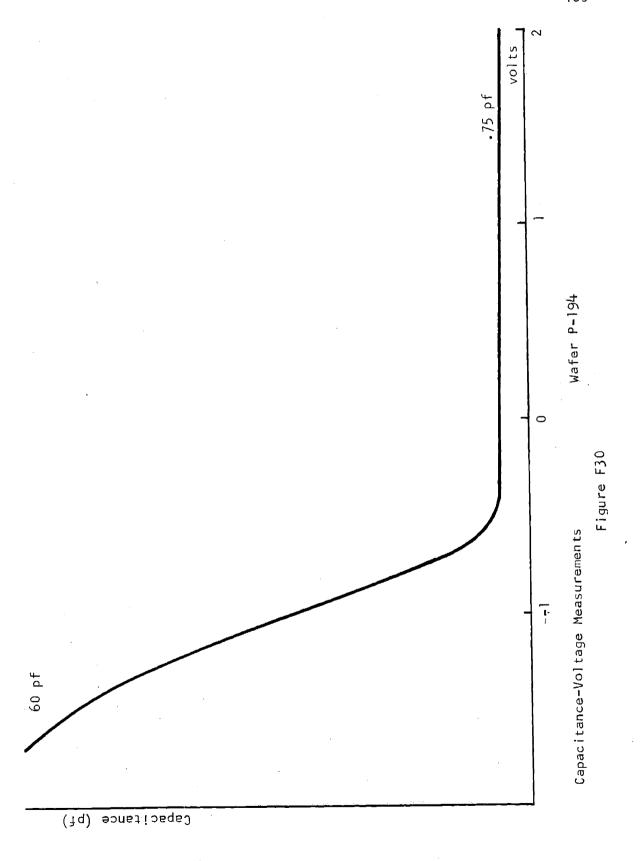

| F30  | Capacitance - Voltage Measurements - Wafer P-194                               | 139 |

| F31  | Surface State Conductance - Wafer P-63                                         | 140 |

| F,32 | Surface State Conductance - Wafer P-73                                         | 141 |

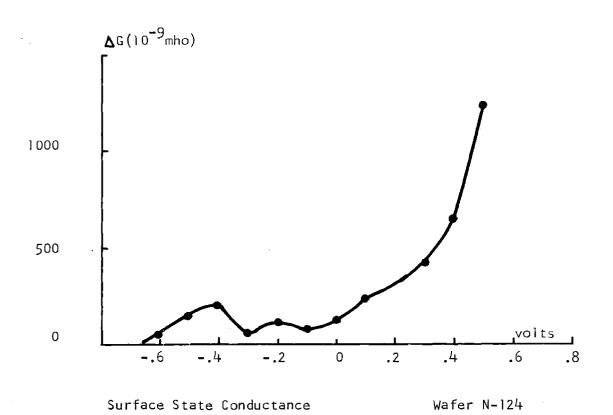

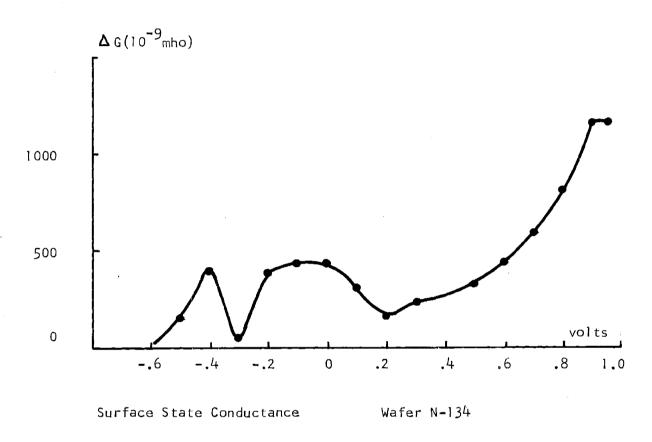

| F33  | Surface State Conductance - Wafer N-124                                        | 142 |

| F34  | Surface State Conductance - Wafer N-134                                        | 143 |

| F35  | Surface State Conductance - Wafer N-144                                        | 144 |

| F36  | Surface State Conductance - Wafer P-154                                        | 145 |

| F37  | Surface State Conductance - Wafer P-174                                        | 146 |

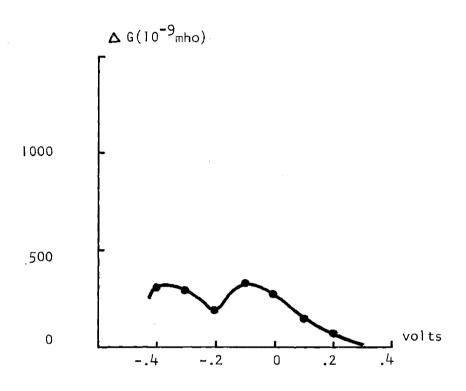

| F38  | Surface State Conductance - Wafer P-184                                        | 147 |

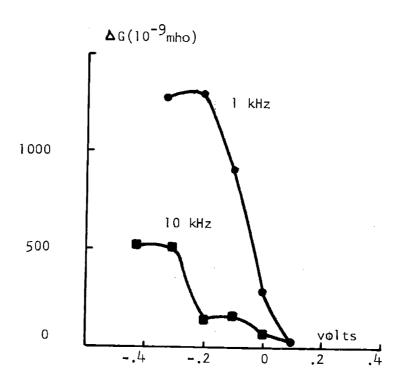

| F39  | Surface State Conductance - Wafer P-194                                        | 148 |

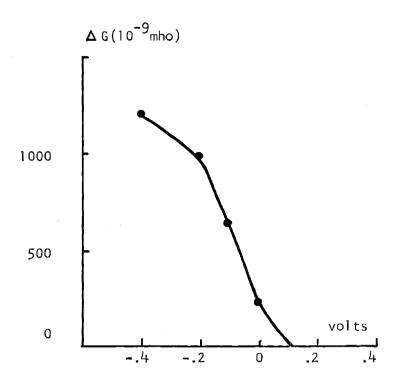

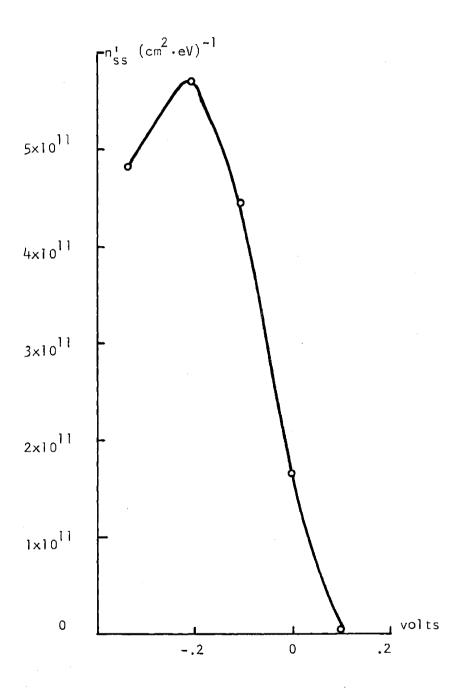

| F40  | Surface State Distribution as Determined from Tunnel Conductance - Wafer P-63  | 149 |

| F41  | Surface State Distribution as Determined from Tunnel Conductance - Wafer P-73  | 150 |

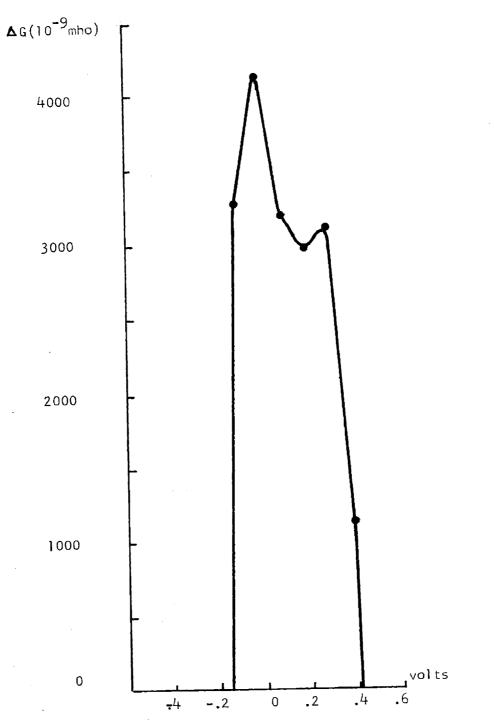

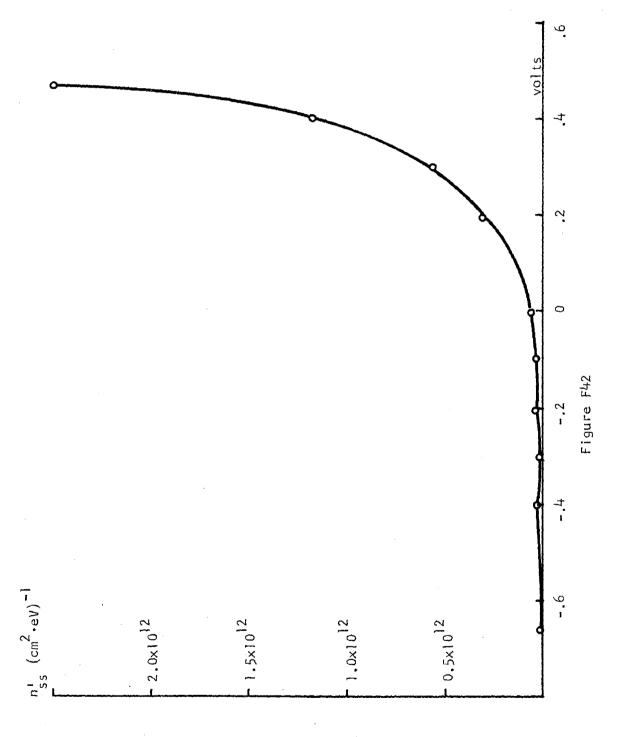

| F42  | Surface State Distribution as Determined from Tunnel Conductance - Wafer N-124 | 151 |

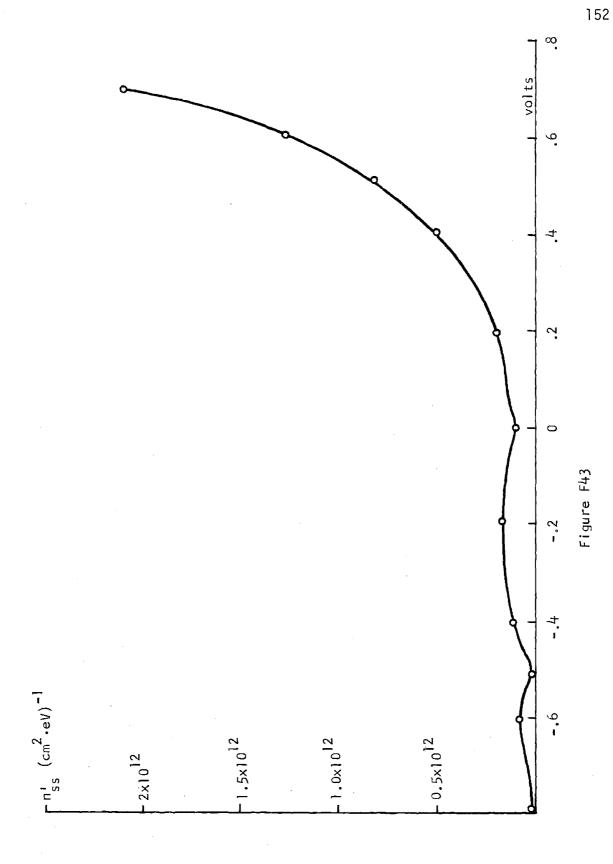

| F43  | Surface State Distribution as Determined from Tunnel Conductance - Wafer N-134 | 152 |

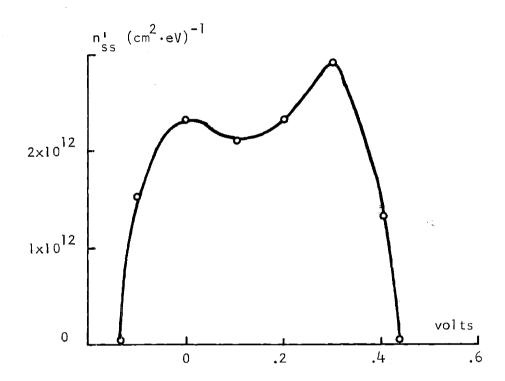

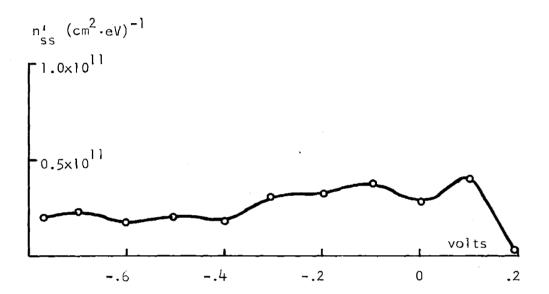

| F44  | Surface State Distribution as Determined from Tunnel Conductance - Wafer N-144 | 153 |

| F45  | Surface State Distribution as Determined from Tunnel Conductance - Wafer P-154 | 154 |

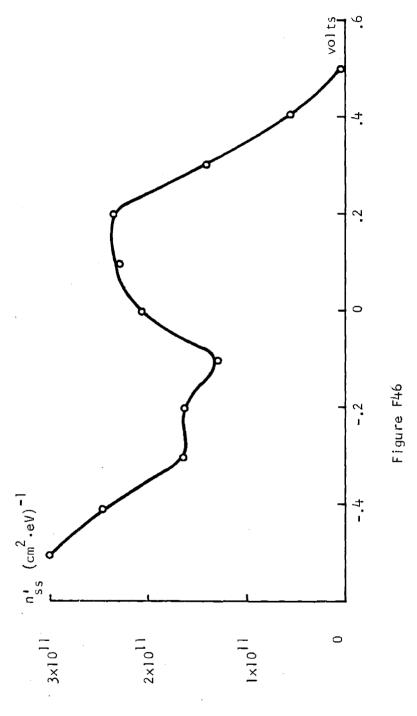

| F46  | Surface State Distribution as Determined from Tunnel Conductance - Wafer P-174 | 155 |

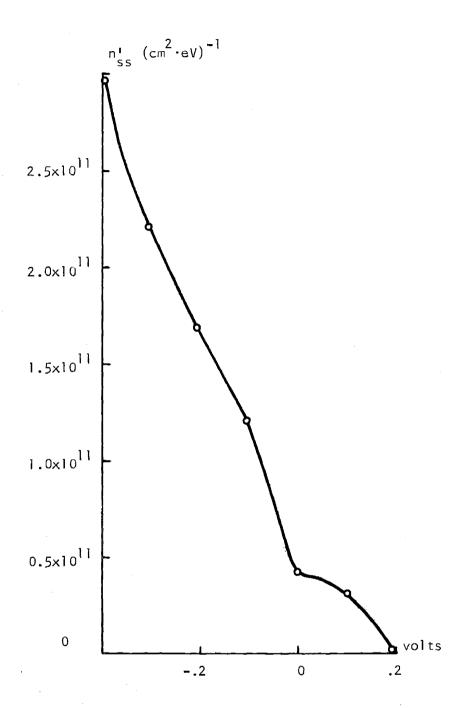

|              | Surface State Distribution<br>Tunnel Conductance - Wafer | from | 156 |

|--------------|----------------------------------------------------------|------|-----|

| F <b>4</b> 8 | Surface State Distribution Tunnel Conductance - Wafer    | from | 157 |

## LIST OF TABLES

| Table<br>number | Title                                                                   | Page<br>number |

|-----------------|-------------------------------------------------------------------------|----------------|

| I               | Tunnel Device Characterization                                          | 55             |

| II              | Semiconductor Surface Data Obtained by DC Tunnel Measurement            | 69             |

| III             | Summary of Fast Surface State<br>Measurements on (111) Silicon Surfaces | 87             |

#### ACKNOWLEDGEMENTS

The author wishes to express his appreciation to Professor H.C. Gatos, his thesis advisor, for encouragement, assistance, and concern with this research.

Special thanks are due to Professor M. S. Dresselhaus for suggestions in choosing the subject of this thesis, and to Dr. L. Chang for his continuous interest and help.

The author gratefully acknowledges the many discussions he had with Professor R. B. Adler, Professor K. H. Johnson, and Mr. C. L. Balestra. He sincerely appreciates the valuable assistance of Mr. C. J. Herman.

The author acknowledges the cooperation of the Failure Mechanisms

Branch of the National Aeronautics and Space Administration, in

Cambridge Massachusetts under Mr. Seymour Schwartz and Dr. J. E. Cline

for use of equipment and facilities, and to Mr. R. Yatsko, Mr. D. Gosselin,

and Mr. A. Spicer for their technical assistance.

Deep gratitude is due to the author's wife, whose companionship and help throughout this period of research served as a constant inspiration, and to his parents who deserve full credit for all his educational achievements.

The help of Mr. D. A. Hayes in preparing the illustrations of this text, and the cooperation of Miss C. Ambler in typing this thesis is gratefully appreciated.

Finally, the author acknowledges the financial support for this work by the National Aeronautics and Space Administration.

#### INTRODUCTION

#### A. Semiconductor Surfaces

In the last twenty years, semiconductor surfaces have been studied in great detail. From the date of development of the first point contact transistor, it was apparent that reliable, reproducible, and stable devices could not be fabricated without an understanding of the semiconductor surface.

Shockley and Pearson<sup>(1)</sup> performed a classical experiment which gave the first understanding of the electrical properties of semiconductor surfaces, i.e. surface states. From a relatively simple field effect capacitor, data were found which gave insight into the density and dynamics of surface states. The early work concentrated on germanium in light of the development of the junction transistor<sup>(2)</sup>; however, the advent of the planar technology<sup>(3)</sup> altered the slant of surface research towards silicon. As a result in the last ten years hundreds of articles have appeared on silicon semiconductor surfaces. Many of the articles are listed in bibliographies prepared by Schlaegel<sup>(4,5)</sup>.

In the study of semiconductor surfaces, researchers distinguish between real and clean surfaces. The real surface is prepared by conventional techniques, i.e. mechanical polish and chemical etch, to remove damaged layers and provide a relatively flat surface. This surface is covered by molecules absorbed from the ambient (innate oxide, for example). Clearly, real surfaces are easily prepared, and are those usually encountered in practical application. Clean surfaces are

free of adsorbed matter to better than a few per cent of a monolayer, and may be prepared under high vacuum by cleavage or by high temperature treatment. There is interest in the clean surface because it most closely represents the actual semiconductor surface. However, in practical application, processing of the semiconductor immediately contaminates the surface, meaning only limited measurements on a clean surface can be made.

Extensive work on surface states has been done along both experimental and theoretical lines.  $T_{amm}^{(6)}$  and  $S_{bockley}^{(7)}$  theoretically developed the idea of localized states existing in the forbidden gap due to dangling bonds. Much experimental work has been done varying physical parameters to fit experiment—to theory, and this work led to considerable understanding of the semiconductor surface. At this time however, experiment and theory do not wholly agree.

Experimentally, surface states are grouped into "slow" and "fast" states. Fast states are those located at the semiconductor-oxide interface, have very short generation-recombination times (less than  $10^{-6}$  seconds), and have densities on the order of  $10^{11}$  to  $10^{12}$  cm $^{-2}$ . The physical characteristics of these fast states such as energy position, density, and capture cross section are fairly well known. The slow states are associated with the oxide of the surface layer and are perhaps the result of absorbed gas atoms and mobile ions within the oxide. Little is known about the slow states except that a typical density is on the order of  $10^{13}$  cm $^{-2}$ .

Probably the most useful theoretical discussions and experimental techniques are described in volumes by Many, Goldstein and  $Grover^{(8)}$ , Frankl<sup>(9)</sup>,  $Gatos^{(10)}$ , and  $Kingston^{(11)}$ .

#### B. Techniques for Examining Semiconductor Surfaces

The large number of investigators looking at semiconductor surfaces is indicative of the many ways in which these surfaces are being examined. The study of semiconductor surfaces includes two areas:

- 1) crystalline and chemical properties of the surface, and

- 2) electronic surface states (or surface states).

First we will define what is meant by a surface state and then we will discuss how these two items interrelate.

A surface state is 1) a location where holes or electrons become trapped, 2) a location where a hole and electron may recombine, or 3) simply a charge center. As the name would imply, these states lie near the semiconductor-oxide interface, either in the insulator or semiconductor. These states may arise from impurities, dislocations, crystalline defects, absorbed gases, moisture, dangling bonds, and anything else disturbing crystalline perfection.

Two of the most important techniques used for the measurement of electronic surface states are the field effect and capacitance voltage methods. The details of these methods are discussed in Appendix A.

The technique of tunneling spectroscopy is the topic of research for this thesis. The theory of tunneling, and experimental techniques will be developed in the next two chapters.

#### II. THEORETICAL CONSIDERATIONS

#### A. <u>Tunneling Theory</u>

Tunneling is the quantum mechanical phenomenon which allows electrons or holes to penetrate an energy barrier. This is a familiar problem, and the solution to Schrödinger's equation in the barrier is:

$$\psi = K \exp[-(2m/\hbar^2)^{1/2}(W - E)^{1/2}x]$$

(1)

where  $X_2 \ge x \ge X_1$ , and  $X_2$ -  $X_1$  = barrier width,

m\* = effective mass in insulator,

W = constant barrier height,

E = energy of particle (W > E),

and the transmission coefficient, which represents the probability of an electron tunneling through the barrier is:

$$T = \exp[-2(2m^*/f_1^2)^{1/2}(W - E)^{1/2}(X_2 - X_1)]$$

(2)

In the case where W is a function of x, the Wentzel-Kramers-Brillouin approximation yields:  $X_2$

rillouin approximation yields:

$$\psi = K(2m^*/h^2)^{1/2}[W(x) - E]^{1/2} \exp\{-(2m^*/h^2)^{1/2} \int_{\chi_1}^{\chi_2} [W(x) - E]^{1/2} dx\}$$

(3)

and the transmission coefficient becomes:

$$T(E) = \exp\{-2(2m^*/\hbar^2)^{1/2}\int_{X_1}^{X_2} [W(x) - E]^{1/2} dx\}$$

(4)

To find the density of current tunneling from one side of the barrier, the number of electrons impinging on the barrier per unit time

is multiplied by the transmission coefficient.

$$dJ_{\chi_1} = ev_{\chi} n \ T(E_{\chi}) \ f(E) \ dK \tag{5}$$

where  $v_X$  = velocity impinging on barrier and  $v_X$  for parabolic bands =  $(1/\hbar)(\partial E/\partial k_X)$

n = number of electrons per unit

volume of k space =  $2/(2\pi)^3$

f(E) = fermi function giving electron occupancy

And so the current density tunneling from one side of the barrier is:

$$J_{X_{\uparrow}} = \frac{e\hbar}{4\pi^{3}m^{*}} \int f(E)T(E_{x})k_{x}dk_{x}dk_{y}dk_{z}$$

(6)

In order to simplify this integral, we note that our real interest is in the  $k_x$  direction, not in  $k_y$  and  $k_z$ . If we write  $K = k_x + K_\perp$  with  $K_\perp \equiv k_y + k_z$ , then  $dk_y dk_z = 2\pi K_\perp dK_\perp$ .

Now since for parabolic bands,

$$k_x dk_x = m^*/\hbar^2 dE_x$$

and  $K_{\perp}dK_{\perp} = m^*/\hbar^2 dE_{\perp}$

we can rewrite equation (6) as

$$J_{\chi_1} = \frac{em^*}{2\pi^2h^3} \int f(E) \ T(E_{\chi}) \ dE_{\chi} dE_{\perp}$$

(7)

Using the Jacobian,  $dE_x dE_y = dE dE_x$ , and equation (7) becomes

$$J_{\chi_1} = \frac{em^*}{2\pi^2h^3} \int f(E) \ T(E_X) \ dE \ dE_X$$

(8)

<sup>\*</sup> See Appendix B.

For the case of two electron or hole sources (metals) separated by a thin insulator, there is tunneling from both sides of the barrier. The net current density is the sum of two terms:

$$J_{x} = \frac{em^{*}}{2\pi^{2}n^{3}} \int_{0}^{\infty} dE[f(E) - f(E + eV)] \int_{0}^{E_{T}} T(E_{x}) dE_{x}$$

(9)

The term eV corresponds to the increase of energy due to the external bias voltage V.

Equation (9) serves as the starting point for the derivation of the tunneling current in a thin metal-insulator-metal (MIM) structure  $^{\left(12-22\right)}$ . The details of the tunneling current differ through the various integrations of the transmission coefficient,  $T(E_\chi)$ . The approximations of both Stratton  $^{\left(12\right)}$  and Simmons  $^{\left(13\right)}$  have been found to describe tunneling through insulating films for limited voltage ranges. More recent approximations  $^{\left(21,22\right)}$  have wider ranges of validity. For the purpose of obtaining an analytical expression describing MIM tunneling, Stratton's approach will be developed. It is hoped that the expression derived will give some understanding to the more complicated problem of tunneling in the metal-insulator-semiconductor (MIS) structure. It must be pointed out that in the theoretical formulation of MIM and MIS tunneling unoccupied states must be available for electrons to tunnel into. This means equation (9) must be modified to

$$J_{x} = \frac{2\pi em^{*}}{n^{3}} \int_{0}^{\infty} dE \rho_{1}(E) \rho_{2}(E + eV)[f(E) - f(E + eV)] \int_{0}^{E} T(E_{x}) dE_{x}$$

(9a)

where  $\rho_{i}(E)$  correspond to the density of states at the energy of the semiconductor and metal respectively.

Stratton measures energy from the top of the valence band and defines  $\phi(x,V)$  to be the barrier energy profile measured from the Fermi level,  $E_f$  (Figure 1). Thus the total energy barrier, W(x) is  $\phi(x,V)$  +  $E_f$ . Now integration by parts of equation (9) yields:

$$J_{x} = \frac{4\pi em^{*}}{4\pi^{3}}kT \int_{0}^{\infty} T(E_{x}) \ln\left[\frac{1 + \exp(E_{f} - E_{x})/kT}{1 + \exp(E_{f} - E_{x} - eV)/kT}\right] dE_{x}$$

(10)

This is a familiar result also found through other derivations as by  $Duke^{(23,24)}$ ,  $Hartman^{(18)}$ , and  $Hartman^{(18)}$ . Stratton assumes that only electrons near the Fermi level dominate the tunneling current, and he thus expands the transmission coefficient in powers of  $E_X'$  where  $E_X' = E_f - E_X$ . The details are presented in Stratton's  $^{(12)}$  and equation (10) becomes

$$J_{x} = J_{0} \frac{\pi a_{1} kT}{\sin(\pi a_{1} kT)} \exp(a_{2} V - a_{3} V^{2}) [1 - \exp(-a_{1} V)]$$

(11)

where

$$J_0 = \frac{4\pi em^*}{a_1^2 h^3} \exp(-a_0)$$

If the barrier is symmetric about  $x = 1/2^*$ , then  $a_2 = a_1/2$ , and equation (11) becomes

$$J_x = J_0 \frac{2\pi a_1 kT}{\sin(\pi a_1 kT)} \exp(-a_3 V^2) \sinh(a_1 V/2)$$

(12)

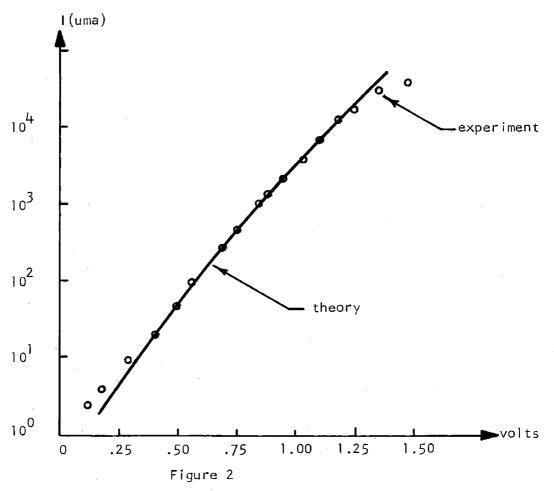

This theoretical equation has been shown to agree with experimental data obtained from MIM structures (12,25). Figure 2 shows the very good fit of data obtained on an Al-Al<sub>2</sub>O<sub>3</sub>-Al sandwich with a 48 Å thick insulator.

<sup>\*</sup> As is generally the case for an MIM structure.

Tunneling Barrier in the MIM Structure Figure 1

Room Temperature Tunneling Characteristics for the Al-Al $_2^0$ \_3-Al Structure

#### B. Tunneling Spectroscopy

Having discussed the theory of MIM tunneling, we wish to make the transition to MIS tunneling. We develop MIS theory by discussing the physical differences between MIM and MIS tunneling, and modifying the MIM equations to fit the MIS system.

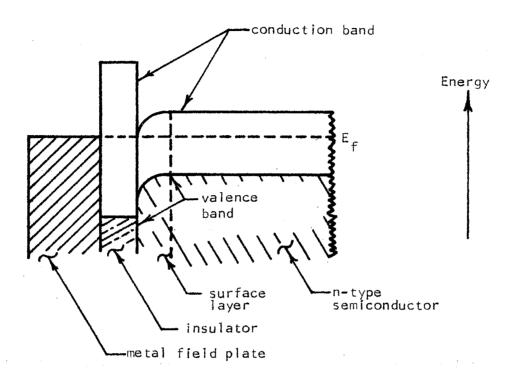

The energy band picture of an MIS structure is shown in Figure 3, with an n-type silicon semiconductor. A chemically etched silicon surface usually has more donor states than the bulk (26). Therefore, the surface is more n-type than the bulk (Figure 3). It is assumed that the energy gap of the insulator is large compared to that of silicon.

The MIS structure differs from the MIM structure in that:

- 1) The semiconductor has a band gap whereas the metal does not.

- 2) The metal is an "infinite" source and sink for electrons, while the semiconductor has only a finite number of states.

- 3) The electrical differences between the metal and semiconductor mean that the tunneling barrier will be nonsymmetric as compared with the Al-Al $_2$ 0 $_3$ -Al structure. It is these differences which must be discussed in order to modify equation (12) to predict MIS tunneling effects.

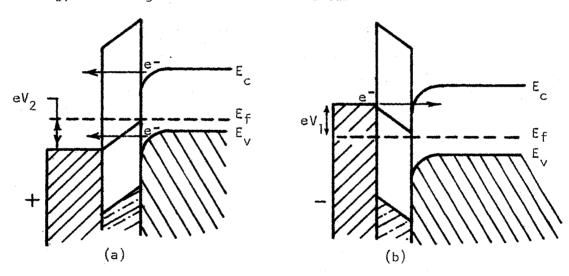

Electrons in the metal or the semiconductor cannot tunnel through the insulator unless they lie opposite to unoccupied states in the other electrode. Therefore, no current can flow in the MIS structure of Figure 4 until the metal is biased  $+V_2$  or  $-V_1$  volts (assuming all the voltage drop is across the insulator, and that the surface states present within the semiconductor's forbidden gap are negligible for now). When  $+V_2$  volts are applied to the metal, electrons in the

Figure 3

Energy Band Diagram for the MIS Structure

Figure 4

Electron Tunneling in a P-type Semiconductor MIS Structure With Positive (a) and Negative (b) Bias on the Metal Plate

valence band of the semiconductor tunnel into unoccupied states of the metal. At  $-V_{\parallel}$  volts, electrons at the Fermi level of the metal tunnel into the conduction band of the semiconductor. For positive bias on the metal, electrons from the conduction band can also tunnel into the metal. Since the semiconductor is p-type, the concentration of conduction band electrons is low (so this effect is small).

When the semiconductor is n-type (Figure 5), tunneling is dominated by metal to semiconductor conduction band transitions. In this case there is only a small gap in tunneling V-I characteristics. The n-type semiconductor would be expected to behave more like a metal than would p-type due to conduction band conductivity.

This tunneling gap,  $V_0 = V_2 - V_1$ , must be overcome for tunneling to occur. If we were to replace the applied voltage V, by  $V - V_0$ , in Stratton's calculation, equation (12) would be corrected to account for this gap. Note that in the p-type semiconductor  $V_0$  is greater than that in the n-type, and in the metal, of course  $V_0 = 0$ .

As discussed in Harrison's paper  $^{(27)}$ , the matrix element for tunneling vanished unless the transverse wave number,  $k_{t}$ , is the same for initial and final states. The Fermi surface of the metal is much larger than the Fermi surface of the semiconductor  $^{(28)}$ , so the "shadow" cast by the semiconductor Fermi surface is always covered by the large shadow of the metal  $^{(29)}$ . Thus, the electrons tunneling from the semiconductor into the metal can easily find an available state, but electrons tunneling from the metal are limited to states within the small area of the shadow cast by the semiconductor.

Electron Tunneling in an N-type Semiconductor MIS Structure with Negative (a) and Positve (b) Bias on the Metal Plate

Figure 5

This restricting of the region of allowed momentum has the effect of reducing the transmission coefficient,  $T(E_\chi)$ . Since we have approximated  $T(E_\chi)$  by a series expansion for the MIM structure, the same approximation should hold for MIS structures with the magnitude of the coefficients reduced.

As seen through equations (4) and (9), the tunneling current between two insulated electrodes depends on the shape and magnitude of the energy barrier of the insulator. If the work function of the two electrodes is unequal, the barrier is asymmetric, causing the MIM tunneling current to differ for forward and reverse bias. Simmons  $^{(30)}$  investigated this barrier asymmetry for different metals, and found that no changes in the tunneling current were evident until the applied voltage exceeded the lower of the two barrier heights. In the structures which Simmons examined, observed changes were on the order of only several per cent for biases up to  $\pm 3$  volts. Thus, even for dissimilar electrode metals, equation (12) is applicable.

The above argument holds true for MIS tunneling with the n-type semiconductor, since the tunneling transitions are with the conduction band for both directions of current (Figure 5). For the p-type semiconductor, however, tunneling transitions occur to the valence band for positive bias (on the metal) and to the conduction band for negative bias (Figure 4). Thus, the tunneling barrier is different for different bias polarity, and a current asymmetry should occur.

This qualitative discussion suggests that the theory explaining MIM tunneling is readily adaptable to MIS tunneling. The energy gap

shifts the tunneling characteristics to higher voltages, and the transition probabilities reduce the magnitude of current. Therefore, when surface effects are not considered, Stratton's results can be modified to

$$J_{x} = J_{0} \frac{2\pi a_{1}^{\prime} kt}{\sin(\pi a_{1}^{\prime} kt)} \exp[-a_{3}^{\prime} (V - V_{0})^{2}] \sinh[a_{1}^{\prime} (V - V_{0})/2]$$

(13)

where  $a_1'$  and  $a_3'$  are smaller than  $a_1$  and  $a_3$  respectively.

The constants  $a_1^i$  and  $a_3^i$  are functions of the physical parameters of the insulator (dielectric constant, thickness, and effective mass) (13,15). Of interest is the fact that  $a_1^i$  varies inversely with insulator thickness and  $a_3^i$  varies with the inverse square of insulator thickness.

The assumption that a transition can be made from MIM to MIS tunneling via equations (12) and (13) is of course dependent on the fact that we indeed know what the tunneling barrier is. One usually considers the large band gap insulator to be intrinsic, and accordingly the net tunneling barrier could be a function of both the conduction and valence bands of the insulator. This model represents two band tunneling, and the above derivation which was carried out for single band tunneling would not be applicable. In fact we could not even define an effective mass (E vs K relation) in the two band model.

In the case at hand, i.e. a very thin insulator, surface charge on the semiconductor induces charge and thus band bending in the insulator. Since the bulk carrier concentration in the insulator is very low (energy gap for  $SiO_2 \simeq 6$  eV), the actual band bending

must be quite large to accomodate the induced charge. If we had a semi-infinite insulator, deep in the bulk the insulator would be intrinsic. But at the surface, near the chage source, the Fermi level would be closer to the conduction band (for  $\mathrm{SiO}_2$  on  $\mathrm{Si}$  on the order of  $\mathrm{2eV}^{(31)}$ ). In the thin insulator, however, we see only this "extrinsic" insulator, and the tunnel barrier corresponds to the conduction band in the insulator indicating that the one band model is applicable. Furthermore, since on a band model we look only at a small segment of this bent band, the segment can be accurately approximated by a straight line. This model permits us to use the single band theory with a trapezoidal barrier.

Surface Considerations in MIS Tunneling. In this research we plan to study surface states at the semiconductor-insulator interface using the tunneling technique. Tunneling spectroscopy has been reported for silicon and  $1nSb^{(35)}$ , and is briefly outlined here.

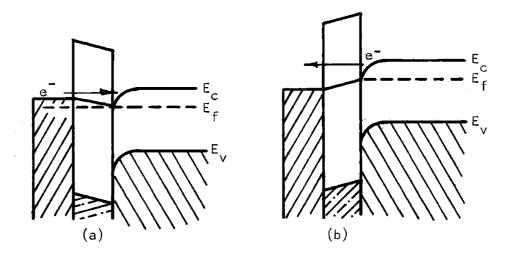

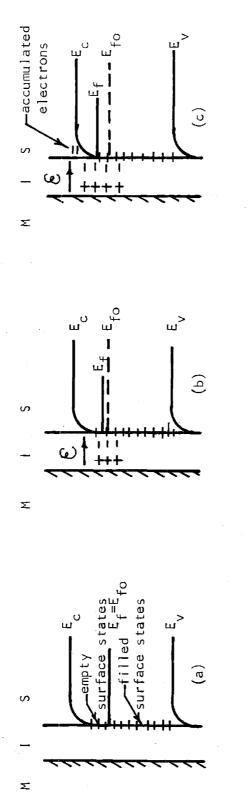

For simplicity, consider the case where the applied voltage exists entirely on the insulator. Using the energy band diagram of Figure 6(a), it is seen that the Fermi level of the metal can be swept through the band gap of the semiconductor by varying the bias on the metal. Analogous to the effect discussed earlier, i.e. tunneling in the p-type semiconductor when the Fermi level of the metal "saw" the conduction band or valence band edge, the tunneling current will increase when the Fermi level of the metal corresponds to a surface state level. In this manner, it is hoped to characterize the density and energy level of surface states in the band gap.

(b) Low Bias Effect of Positive Bias on Metal Plate of N-type MIS Structure: (a) No Bias (c) High Bias, No Penetration of Electric Field into Semiconductor

Figure 6

The simplifying assumption of the voltage drop existing entirely across the insulator, i.e. no band bending due to applied bias, must be investigated to find regions of applicability, and to make suitable modifications when necessary. The tunneling current depends on the electric field in the insulator (13,15,25), and a knowledge of how the field in the MIS insulator varies with applied voltage will permit understanding of the tunnel current.

The electric field lines resulting from the applied voltage pass through the insulator and terminate on charges in the metal and semiconductor. The charge on the metal appears at the surface and does not penetrate into the metal. The charge on the semiconductor is a more complex situation. Charge can build up in surface states and in a depletion or accumulation layer at the surface. The location of these charges determines the field in the insulator, and thus, the V-I relation of the MIS structure. Specific consideration for the charging of surface states in silicon is considered.

Silicon usually has an excess of donor type surface states. These states are partially filled, according to Fermi statistics, and create an internal electric field. This internal field affects the tunneling characteristics only when the potential barrier is altered by the field.

Many et al. (8) illustrate (Figure 6) the termination of field lines on silicon with surface states. For zero bias, in n-type silicon, the surface states above the Fermi level are empty. If a positive voltage is placed on the metal, electrons are swept to

the semiconductor surface. These excess electrons fill up surface states until equilibrium is reached. With large enough bias, all the surface states become filled so that additional voltage produces an electron accumulation region at the surface. In this situation, the charge in the semiconductor is at the surface and the field in the insulator is proportional to the applied voltage (E = V/L). The semiconductor surface appears metallic, and the field does not penetrate the semiconductor.

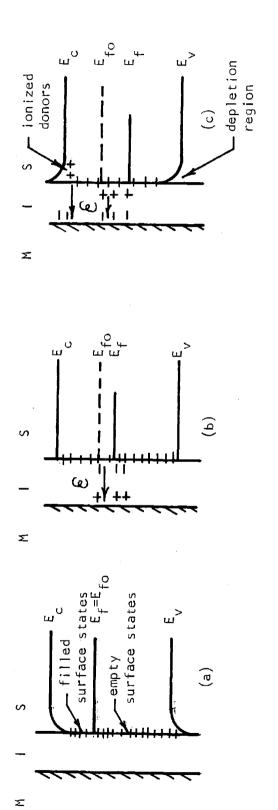

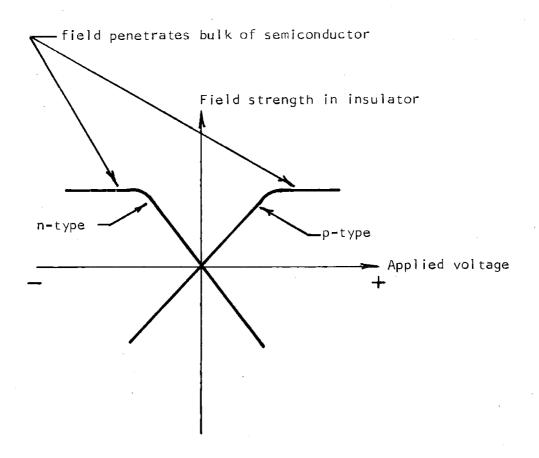

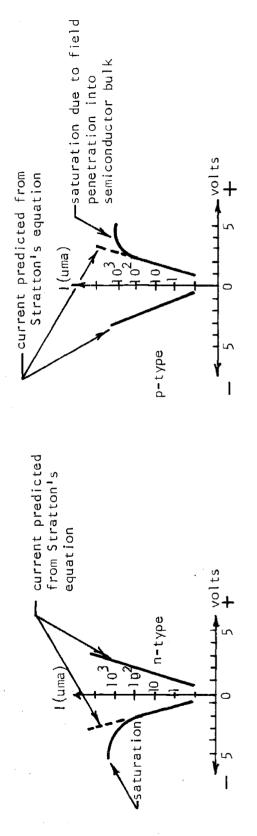

If a negative voltage is applied to the metal, electrons are swept away from the surface and the surface states start to empty. As seen in Figure 7, when the surface states are completely emptied the surface region is made up of immobile positive charges (ionized donors). Field lines terminate on these charges, and the field penetrates the bulk. The same argument holds for the p-type semiconductor, except for a reversal of polarity. This analysis predicts the insulator field to vary with applied voltage as shown in Figure 8. In the regions where the field is proportional to the applied voltage, the MIS tunneling current should increase exponentially as predicted by equation (13). When a depletion layer forms, the insulator field no longer increases proportionally to the applied voltage, and the tunneling current levels off. The predicted V-I characteristics (36) are shown in Figure 9.

The aforementioned has been a description of the technique of tunneling spectroscopy. Although we have specifically alluded to the aluminum-silicon dioxide-silicon system, it should be apparent that the same arguments hold true for the more general metal-

(a) No Bias (b) Low Bias Effect of Negative Bias on Field Plate of N-type MIS Structure: (c) High Bias Penetration of Field into Semiconductor

Figure 7

Electric Field Strength in Insulator of MIS Structure as a Function of Applied Voltage

Figure 8

I-V Tunneling Characteristics Predicted From MIS Structures With Surface States

Figure 9

insulator-semiconductor structures.

This technique, as described, permits investigation of the conduction and valence band edges, but not of surface states within the bandgap. The following approach is needed to study surface states.

If, when the Fermi level of the metal is slowly "swept" through the gap of the semiconductor, it should see a level of surface states, a tunnel current would flow (34,37) until the states filled or emptied (according to Fermi statistics), then thermal equilibrium would result. Thus, this current would only be transient, and depending on the generation-recombination rate of the surface state, probably be of too short a duration to detect. To overcome this problem, a low level AC signal is superimposed on the DC sweep. In this way, when a surface state level is reached, the AC signal will cause the state to fill and empty in response to the incremental field, and thus a steady state signal is measured. The solution of this problem gives us the added feature of being able to vary frequency to measure surface state dynamics, and also being able to use DC-AC filtering technique to permit measurement of surface states near band edges where the DC signal would dominate. Both the experimental techniques and data obtained will be detailed in the next chapter.

#### C. Other Conduction Mechanisms in MIS Structure

Having discussed tunneling spectroscopy, the question now arises on the conditions for tunneling to occur and the possibility of other components of current. What we are really asking is how do we know that the current being measured is indeed a tunnel current?

In order to properly answer this question, we must discuss other conduction mechanisms.

Electronic conduction in MIS structures may be classified in six general categories. The pertinent equations are presented in Appendix C, and a brief description of their differences is discussed here.

1. <u>Ionic conduction</u> is due to drift of ionic impurities and defects under the influence of an electric field (for example, silver in ceramic used in capacitors). Absorbed moisture may enhance ionic conduction as shown:

The Na<sup>+</sup> is small enough to move through the amorphous oxide, but the larger OH<sup>-</sup> cannot. The physical conduction process may be described as ions jumping from site to site. Evidence of this has been seen in TiO<sub>2</sub> and BaTiO<sub>3</sub>. These dielectrics become more stable to Na<sup>+</sup> drift by doping with silver. The silver ions fill in vacancies in the dielectric and the Na<sup>+</sup> is rendered immobile. The movement of ions on the surface of semiconductors can introduce leakage and device degradation. Until surface passivation was developed, surface leakage was amongst the most severe failure mechanisms in transistors.

Ionic and electronic currents are easily distinguished. The activation energy for ionic conductivity is large (3-4eV) and the ions have a long transit time (low mobility, less than 1  $\rm cm^2/V-sec$ ).

Usually DC ionic conductivity decreases with time since ions can not readily be injected or extracted from the insulator. After an initial current flow, positive and negative charges will build up and polarize the insulator. When the applied field is removed, internal fields cause some of the ions to flow back to their equilibrium position with their characteristically long time constants, and hysteresis results.

- 2. <u>Tunneling and internal field emission</u> are conduction processes via barrier penetration. The four subgrouping are: a) Zener electrons tunneling from valence band of semiconductor to conduction band of metal; b) Field ionization electrons from impurity levels of semiconductor to conduction band of metal; c) Field emission from Fermi level (cathode) to vacuum; d) Field emission from within valence band to anode. Tunnel currents are characterized by their relative temperature insensitivity and an exponential dependence on insulator width.

- 3. <u>Impurity conduction</u> electrons hop from one donor site to another (same for holes and acceptors), but not into conduction band. (This would be ohmic conduction). For very low concentrations of impurity, both donor and acceptor sites are necessary, as acceptors remove electrons from some donors. For intermediate and high concentrations of impurity, acceptors are not necessary. In intermediate concentrations, a hopping process occurs wherein phonon interaction is essential. For very high concentrations, interaction is great, and a relatively high impurity band conductivity results.

Impurity conduction in clean insulators such as  ${\rm Si0}_2$ ,  ${\rm Si0}$ , and  ${\rm Si}_3{\rm N}_4$  is at a minimum due to very few impurities and the high activation energy between nonoverlapping wave functions. Even at fields of 5 x  $10^6$  V/cm, impurity conduction in insulators is estimated at less than  $10^{-16}$  mho/cm $^{(38)}$ .

4. Ohmic conduction occurs when electrons are excited into the conduction band and drift under the influence of the applied field.

The ohmic component, which contributes mainly at higher temperatures due to its relatively large activation energy, is easily identified by a linear current voltage plot. This component reaches  $10^{-5}$  amp/cm<sup>2</sup> at 5 x  $10^{6}$  V/cm only at temperatures exceeding  $425^{\circ}$ K<sup>(39)</sup>. Thus this component is usually negligible.

Changes in insulator thickness cause linear changes in the ohmic component but cause exponential changes in the tunneling component.

The details of these mechanisms are seen in Figure 10.

5. Space charge limited flow is due to build up of a negative space charge at the cathode; further electron flow is limited by repulsive forces. At equilibrium current is proportional to voltage to the second power. Space charge limited flow becomes important only at current densities exceeding 15-20 amp/cm $^{(40)}$ .

Although tunneling has been reported through films up to  $1000A^{(39)}$ , films must be thinner than 200A to observe current densities greater than  $10^{-5}$  amp/cm<sup>2</sup>. Space charge limited currents are not observed in MIS structures with insulator thickness less than  $2000A^{(41)}$ , most likely due to very low current densities, i.e. no interactions.

Current-Temperature Characteristics of an Au-Si $_3^{

m N_4}$ -Si Structure at Applied Field of 5x10 $^6$  V/cm. The Tunnel Component Predominates at Low Temperature: the High Temperature Range can be (Reference 39) Extended by using a Thinner Insulator.

Figure 10

6. Schottky emission and Poole-Frenkel effect - both of these processes occur through electron excitation over a barrier. a) Schottky emission occurs when effective barrier height is reduced by intense applied field across the thin insulator. The electrons from the metal or semiconductor are excited to the conduction band of the insulator. b) Poole-Frenkel effect occurs when electrons trapped in insulator are excited to conduction band of insulator.

The Poole-Frenkel component is of the same order of magnitude as the tunneling current at normal intermediate temperatures. At the high temperature range, Poole-Frenkel currents dominate (Figure 10), while at low temperatures the Poole-Frenkel component disappears, so the tunnel current dominates. However, the two components are readily separated because a) the tunnel component is essentially temperature independent, while Pool-Frenkel processes are strongly temperature dependent, and b) tunnel current  $\propto V^2 \exp(-a/V)$ , while Poole-Frenkel current  $\propto V \exp(V^{1/2})$ .

The intent of the above discussion is to give some experimental understanding on the conduction mechanisms in MIS structures. It is not a rigorous argument, but one which suggests the possible mechanisms. If experiments are done near absolute zero temperature, one can be reasonably sure that the only possible currents would be either tunnel or space charge limited currents. If one uses a superconductor as the electrode, and if one observes the superconducting gap, then the transport mechanisms must be tunneling. Aside from these extremes, however, we must rely on experimental evidence and experience to analyze the actual conduction mechanism.

## III. EXPERIMENTAL PROCEDURE

## A. Sample Preparation

The tunneling devices used in these experiments were all of the aluminum-silicon dioxide-silicon structures. This decision was made because of the tremendous interest in, and data available, on silicon, the ease in working with  $\mathrm{SiO}_2$  and Al using the planar technology, and the extreme practical value of this almost universal MOS capacitor.

The criteria used in trying to fabricate a tunneling device were:

- 1) to grow a thin tunneling barrier, less than 200A thick;

- 2) since the bandgap of Si is 1.1 eV, the thin oxide must be able to withstand fields on the order of 5 x  $10^6$  V/cm;

- 3) capacitance must be minimized so that this 90° out of phase signal does not swamp out the inphase tunnel component (small device area).

Oxidation. At usual oxidation temperatures,  $1050-1200^{\circ}C$ , the oxide grows so quickly that by the time the wafer is placed inside the tube and taken out, oxides on the order of 300-700A have grown. An attempt was made at growing low temperature oxides ( $300-800^{\circ}C$ ) but these oxides had lower breakdown strengths than required ( $5 \times 10^5 \text{ V/cm}$ ). This was attributed to a very porous oxide, resulting from low temperature growths. It is known that silicon has an innate oxide 20-60A thick, when exposed to the atmosphere at room temperatures. This oxide was also unsatisfactory (analogous to the low temperature oxide). Other techniques such as anodic plating or

evaporation of  $Sio_2$  proved unsuccessful due to high pinhole density and/or high impurity density causing low breakdown strength.

A technique we discovered was that of passivating the wafer with hot concentrated nitric acid, a good oxidizing agent. The probable reaction is:

$$2HNO_3 \rightarrow H_2O + 2NO_2$$

and

with the net reaction,

$$Si + 2HNO_3 \rightarrow SiO_2 + H_2O + 2NO\uparrow$$

Because this is a relatively low temperature reaction, the oxide probably grows by diffusion of oxygen through pores in the oxide. And, as observed, the rate of growth of oxide is slow (100A in 3 min.). Yet upon testing the oxide, breakdown fields of 5 x  $10^6$  V/cm were measured, which results from hydration tightening the oxide and closing pores,

$$SiO_2 + XH_2O \longrightarrow SiO_2 \cdot (H_2O)_X$$

<u>Electrical Contact</u>. Since the excess handling and elevated temperatures required for wafer dicing and bonding were considered a principle source of device failure, we decided to make electrical contact via a joystick probe.

We encountered difficulty when contact was made to the aluminum.

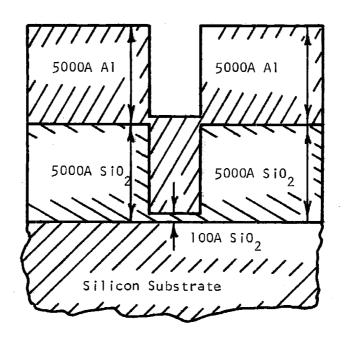

The thin oxide under the aluminum is extremely fragile, and was penetrated by the probe, thus destroying the device. This problem was overcome by fabricating an "expanded" contact. A thick oxide (5000A)

was thermally grown on the substrate, and a thin oxide grown in holes etched through the thick oxide. Evaporated aluminum coats both oxides, and probe contact is made to the stronger thick oxide. Furthermore, because of the thick oxide, extra contributions to device capacitance are minimal.

Having now overcome the basic problem in device fabrication, we go into detail on the processing steps and final device structure.

## Processing of Silicon Wafers for Tunnel Test Device

### Material used:

- a. N-type silicon, resistivity 10, 1.0,  $0.5\Omega$ -cm (donor density 5 x  $10^{14}$ , 6 x  $10^{15}$ , and 2 x  $10^{16}$ /cm<sup>3</sup> respectively) $\pm 20\%$ ; dislocation density less than  $10^3$ /cm<sup>2</sup> as determined by etch pit count; orientation (111)  $\pm 0.5^\circ$ ; phosphorous doped. The pulled crystals were grown by Texas Instruments' Lopex (low oxygen) process, with diameter 7/8 1 1/8". The crystal had a flat cut on it perpendicular to the [110] direction, and is then sliced into wafers ranging from 7.5 to 9.0 mils thick. All wafers are mechanically polished and chemically etched by the manufacturer.

- b. P-type silicon, resistivity 10, 1.0,  $0.5\Omega$ -cm (acceptor density  $10^{15}$ ,  $2 \times 10^{16}$ , and  $4 \times 10^{16}$ /cm<sup>3</sup> respectively)  $\pm 20\%$ ; dislocation density less than  $10^3$ /cm<sup>2</sup> as determined by etch pit count; orientation (111)  $\pm 0.5^\circ$ ; boron doped. The pulled crystals were grown by Texas Instruments' Lopex process, with diameter 7/8 1 1/8". The crystal had a flat cut on it

perpendicular to the [110] direction, and is then sliced into wafers ranging from 7.5 to 9.0 mils thick. All wafers were mechanically polished and chemically etched by the manufacturer.

# Wafer cleaning:

Note that in the following processes all acids and solvents used are of "Transistar" purity and deionized (DI) water with resistivity exceeding  $10^{18}~\Omega\text{-cm}$ .

- a. Immerse wafer in concentrated sulfuric acid  $(H_2SO_4)$  at 185°C for 15 minutes, then allow to cool in the acid.

- b. Rinse in DI water for 5 minutes.

- c. Heat wafers in concentrated nitric acid  $(HNO_3)$  at 120°C for 15 minutes.

- d. Rinse in DI water for 5 minutes, then dry wafers by spinning.

- e. Immerse in concentrated HF at room temperature for 1 minute.

- f. Rinse in DI water for 15 minutes, then spin dry.

#### 3. First oxidation:

- a. Set oxidation furnace to 1200°C, and purge tube with a steam of dry nitrogen.

- b. Place wafers on quartz carrier and insert into tube.

- c. Set flow of dry oxygen at 1000 cm<sup>3</sup>/min for 15 minutes.

- d. Switch to a wet oxygen (steam at 95°C) flow of 500 cm<sup>3</sup>/min for 20 minutes.

- e. Switch back to dry oxygen flow of  $1000 \text{ cm}^3/\text{min}$  for 15 minutes.

The wafers are now removed from the oxidation tube, and the wafers appear to be green-blue-green, signifying an oxide thickness of 5000A.

### 4. Oxide photo resist:

- a. Load photo resist (Shipley positive resist #AZ-111 or AZ-1350) into syringe, and apply to wafer through 1 micron Millipore filter.

- b. Spin wafer for 30 seconds to 3000 rpm to get thin (1 micron) uniform coating of photo resist on wafer.

- c. Prebake wafers at 85°C for 10 minutes in an uncovered dish.

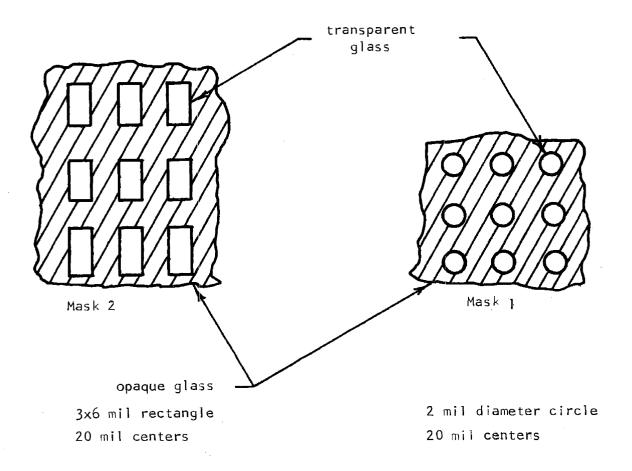

- d. Expose wafer to mask #1 (Figure 11) under ultraviolet light for 5 seconds. Resist will stay soft where exposed to light.

- e. Develop wafer for 30 seconds (use 1 part Shipley AZ-303 developer to 4 parts DI water and spray on wafer.

- f. Rinse in DI water for 5 minutes, spin dry, bake for 30 minutes at 85°C and let cool.

#### 0xide etch:

- a. Let wafers cool, then etch oxide in solution of 10 parts  $NH_3F1$  (40% solution) to 1 part concentrated HF. This is a buffered HF solution and the observed etch rate is 800A/min.

- b. Rinse in DI water for 15 minutes, then clean off remaining photo resist in  $\rm H_2SO_4$  at  $185^{\circ}C$  for 15 minutes.

- c. Allow wafers to cool, rinse in DI water for 5 minutes, then spin dry.

Photo-Lithographic Masks for Device Patterns

Figure 11 Figure 12

At this stage the wafer has the image of mask #1, i.e. 2 mil holes etched through the 5000A oxide down to bare silicon.

#### 6. Second oxidation:

- a. Immerse wafer into concentrated  $HNO_3$  at 120°C for 5 minutes.

- b. Rinse in DI water for 5 minutes, and spin.

At this step a thin oxide (later estimated to be approximately 100A thick) is grown on the silicon in the 2 mil holes.

#### 7. Metallization:

- a. Load wafers into vacuum evaporator

- b. Load pure (99.999%) aluminum into evaporator and deposit using electron beam bombardment. Deposition rate is 10,000A/min at  $5 \times 10^{-6}$  torr, and final aluminum thickness is 5000A.

- c. Dry wafers for 15 minutes at 85°C.

Aluminum metal now covers the entire wafer.

#### 8. Metallization photo resist:

- a. Mix Kodak negative photo resist 1:1 with thinner (Kodak KTFR resist and thinner).

- b. With syringe apply resist through 1 micron filter.

- c. Spin wafer at 6000 rpm for 14 seconds, approximately 8000A layer of photoresist.

- d. Air dry for 15 minutes (do not spin or blow).

- e. Prebake for 3 minutes at 85°C in an uncovered dish.

- f. Expose water to mask #2 (Figure 12) under ultraviolet light for 6 seconds. Resist hardens where exposed to light.

- g. Develop with Kodak KTFR developer for 1 minute

- h. Rinse in DI water for 15 minutes and spin dry.

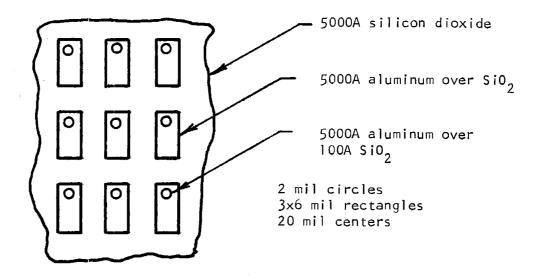

Following this step the test patterns are fabricated and appear in Figure 13.

- 10. Removal of photo resist: We cannot use  $\mathrm{H}_2\mathrm{SO}_4$  to remove the remaining photo resist because the sulfuric acid will also etch the aluminum. Therefore painstaking steps must be followed to clean the relatively insoluble photo resist.

- a. Immerse wafers in J-100 (a proprietary organic solvent) at 110°C for 10 minutes.

- b. Wash in hot xylene (or trichlorethylene-TCE) for 5 minutes.

- Rinse in cold xylene (or TCE) for 5 minutes.

- d. Rinse in acetone for 5 minutes.

- e. Rinse in methanol for 5 minutes.

- f. Rinse in DI water and spin dry.

Processing is now completed, and a cross section of the devices shown in Figure 13, appears in Figure 14.

### B. <u>Measurement Techniques</u>

In designing test apparatus for an experiment, one must carefully consider the nature of the desired data. In this experiment the requirements are:

1. DC I-V characteristics, voltage range  $\pm 1v$ , current range to  $10^{-10}$  amps.

Figure 13

Top View of Processed Wafers

Figure 14

Cross Section View of Processed Wafers

(Not to Scale)

- DC conductance-voltage measurements.

- 3. AC incremental G-V measurements dealing with currents down to  $10^{-13}$  amps.

- C-V measurements.

In cases 1-3, current levels are sufficiently small, such that noise problems are an important consideration. It must be remembered that the tunnel samples are basically high value MOS capacitors so that there is the further complication of very high impedance at low frequencies and large, 90° out of phase displacement currents superimposed on the AC tunnel component.

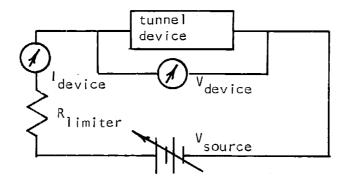

For D. C. measurements, the simplest apparatus is shown in Figure 15. This circuit is not usable here because in most cases the sample impedance is higher than the voltmeter impedance, and the current measured is that through the voltmeter. The next step would be to try a simple Wheatstone bridge; however, the problem of a high sample impedance occurs here too. The way to overcome this problem is to design a bridge with the impedances of the measuring apparatus incorporated. Figure 16 shows a bridge which, when nulled without the tunnel sample, includes all circuit loading.  $R_{\rm I}$  and  $R_{\rm V}$  represent the impedance of the current measuring and voltage measuring devices respectively (oscilloscope and X-Y recorder). If we write the network equations for this bridge we readily find that

$$V_{R_{I}} = \frac{R_{2}R_{3}R_{I}}{R_{1}R_{2} + R_{1}R_{I} + R_{2}R_{I} - R_{2}R_{3}} I_{sample}$$

(14a)

Simple Measurement Circuit for DC I-V Characteristics

Figure 15

Figure 16

Bridge Circuit Used for AC and DC Measurements on the Tunnel Test Devices

and of course

$$VR_V = V_{sample}$$

(14b)

Typical values used are R $_1$  = 1 k $\Omega$ , R $_2$  = 30 k $\Omega$ , R $_3$  = 200 k $\Omega$  ten turn pot (for nulling the bridge) and R $_I$   $\simeq$  R $_V$   $\simeq$  1 meg $\Omega$ . The actual transfer ratio for the bridge is I $_S/V_{RI}$  = 36.36  $\mu$ A/V.

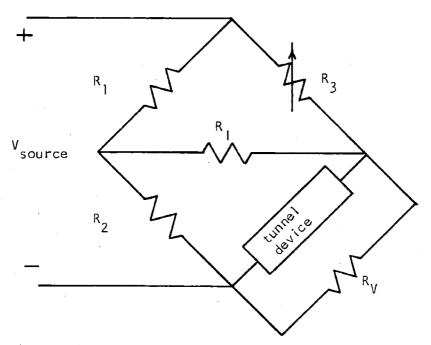

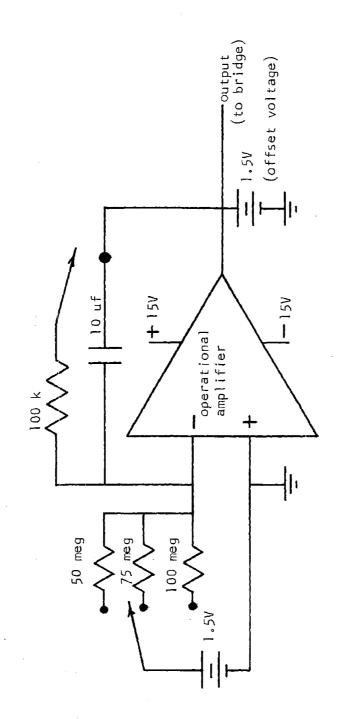

This bridge was connected to an oscilloscope and X-Y recorder, and the I-V characteristics of diodes and resistors were obtained very satisfactorily. In order to automate the measurement process, we designed a circuit to provide a constant DC sweep through the range -1.5 to +1.5 volts. This circuit, shown in Figure 17, is basically a DC integrator with a DC offset voltage. This circuit has the feature of being able to select three different sweep rates, a hold position, and a rapid discharge. Sweep rates range from 10 min/v to 60 min/v.

The next question involves AC measurements, and whether the DC equipment can be suitably modified. The important points in AC measurements are first, because of large capacitance, we need phase detection techniques, and second, because of 60 cycle and other noise problems, we need frequency selection and filtering. It happens that the PAR Lock-In Amplifier, Model HR-8 is ideally and uniquely suited for these measurements, in having both phase and frequency detection capabilities, as well as high gain.

Our DC bridge will be of value for AC measurement if, and only if, we can accurately separate the in-phase tunneling component and

Integrator Circuit Used to Provide Slow DC Sweep to Tunnel Test Devices

Figure 17

the 90° out-of-phase displacement current component. If the tunneling device is modeled as a parallel RC network, the AC analysis carried out in Appendix D shows  $\tan\theta$  of  $V_{R_V}/V_{in} \simeq 10^{-4}$ , i.e. zero for all practical purposes. This means that the measured output voltage is in phase with the applied signal and pure real. Now we have both a phase and a frequency reference to compare the device current with.

The lock-in amplifier is tuned to the desired frequency, and then, with no sample connected, the amplifier output is nulled using the phase control. It is important to note that even with no test device in the circuit, the external lead and fixture capacitance is significant (on the order of 100 picofarads). So that by using phase-nulling of the amplifier, we are in effect removing the  $90^{\circ}$  out-of-phase component. We verified this operation of the amplifier by attaching capacitors (with values ranging from 1 pf to 10 uf) to the bridge and observing no departures from null. However, when a parallel RC is attached, the amplifier output is proportional only to the conductance, even at extremes of R = 2 meg $\Omega$ , C = 10 uf, and f = 25 kHz. Therefore we can use this Wheatstone resistance bridge for DC and AC measurements in conjunction with the PAR HR-8 Lock-In Amplifier.

The sensitivity of the bridge and lock-in amplifier, and the high signal to noise ratio, permit measurement of DC current down to  $10^{-11}$  amp and AC current to  $10^{-13}$  amp. This range is more than sufficient to handle the tunnel devices we have fabricated.

The final step is that of mounting and contacting the sample. As discussed in the previous section, it was judged too inconvenient to dice the wafer into chips and then bond these chips to headers.

Instead, we etch the back of the wafer to bare silicon using HF. Then a cylindrical brass block is etched with HCl, and the wafer placed on this block. The HCl serves the dual function of cleaning the brass and acting as an electrolyte for good ohmic contact. Contact to the tunnel devices on the front side of the wafer is made with a stainless steel probe tip. Measurements on virgin silicon wafers, both n- and p-type, showed this technique to provide good ohmic contacts (resistance  $\approx$  10 ohms).

### IV. RESULTS AND DISCUSSION

# A. Results

Experimental results were obtained on twelve different test wafers. These results include DC current-voltage (I-V) curves, DC conductance, AC conductance at 10, 100, 1000, and 10,000 Hz, the difference between AC and DC conductance (to calculate surface state distribution), and capacitance-voltage measurements. The samples are identified in Table I.

Table I

| Sample number | Туре | Insulator thickness | Dopant (type | e, /cm <sup>3</sup> ) |

|---------------|------|---------------------|--------------|-----------------------|

| P-63          | р    | 40A <sup>*</sup>    | boron        | 1 x 10 <sup>15</sup>  |

| P-73          | р    | 20A <sup>*</sup>    | boron        | 4 x 10 <sup>16</sup>  |

| N-73          | n    | 58 <b>A</b>         | phosphorous  | 5 x 10 <sup>14</sup>  |

| N-83          | n    | 62A                 | phosphorous  | 6 x 10 <sup>15</sup>  |

| N-124         | n    | 52A                 | phosphorous  | 6 x 10 <sup>15</sup>  |

| N-134         | n    | 30A                 | phosphorous  |                       |

| N-144         | n    | 30A                 | phosphorous  |                       |

| P-154         | p    | 56A                 | boron        | 2 x 10 <sup>16</sup>  |

| P-164         | р.   | 51A <sup>*</sup>    | boron        | 4 x 10 <sup>16</sup>  |

| P-174         | р    | 31A                 | boron        | 1 x 10 <sup>15</sup>  |

| P-184         | р    | 67A                 | boron        | 2 x 10 <sup>16</sup>  |

| P-194         | p    | 24A <sup>*</sup>    | boron        | 1 x 10 <sup>15</sup>  |

<sup>\*</sup> Denotes rough estimate.

<u>DC Measurements</u>. In order to determine the correlation between the tunneling theory of Chapter II and actual device performance, we performed a series of measurements. The first of these measurements was the DC current-voltage characteristic.

Typical DC tunnel currents were in the 10 dp range; therefore, no special precautions other than short leads and direct grounding were needed for electrical measurements. A problem resulted, however, in making probe contact. If probe pressure were too light, contact resistance was high and the measurements were not reproducible; if pressure were too great, aluminum was scraped from the silicon dioxide and no contact was made. A successful technique was lowering the probe to the silicon surface adjacent to the contact pad, and the sliding the probe over to the aluminum, thus making contact. Measurements made using this procedure had low contact resistance and were reproducible.

Each test wafer had several hundred devices, and while many devices were non-functional (such as those at the wafer's edge where photo-resist build-up occurred), most exhibited uniform characteristics across the wafer. These characteristics were examined by measuring the current at a fixed voltage for a ten by ten array on each wafer. The measured currents were within  $\pm 3\%$  of each other for the arrays.

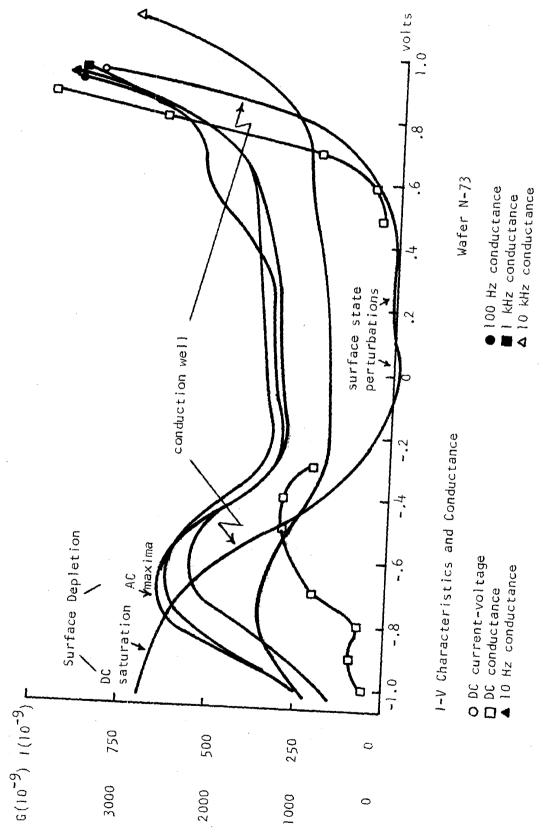

The DC I-V characteristic of Figure 18 clearly shows the existence of a conduction well in the n-type sample. This well results from the forbidden region of the semiconductor, i.e. the tunnel gap which distinguishes MIS from MIM tunneling.

Figure 18

There are small perturbations observed in this well which are attributed to the transient response of surface states. These perturbations will be discussed in the interpretation of results. Note that in this figure the width of the conduction will is approximately 1.1 eV, the band gap of silicon. Furthermore, the voltage to the positive side of the conduction well corresponds to the valence band-Fermi level separation (~ 0.7 eV); and the voltage to the negative side of the well corresponds to the Fermi level conduction band separation ( $\simeq 0.4 \text{ eV}$ ). While in this example the tunnel characteristics provide a basis for useful spectroscopic analysis of the semiconductor, there are instances where this technique does not apply, that is, when the semiconductor surface becomes depleted before the band edges are reached, as we see in the p-type sample of Figure 19. Of course, the surface of the n-type sample also becomes depleted, however, as seen in the example of Figure 18, depletion occurs after the band edge is reached.

In the enhancement mode for the n-type sample, that is, positive bias on the metal, the tunnel current rises exponentially with increasing voltage. With negative bias, the current starts to rise again (as in MIM tunneling) but the semiconductor surface is depleted, the current level becomes saturated (-.8 V), and the conduction decreases from a maxima (at -.7 V). The p-type sample (Figure 19) shows drastically different I-V characteristics. Since the bands at the surface of the silicon are bent down, the surface appears more n-type or less p-type. The n-type sample is actually enhanced at zero bias, and depletion does not result until fairly large

Figure 19

negative voltages are reached (-.8 V); but the p-type sample is depleted at zero bias, thus the positive voltage side of the conduction well is not seen. In the accumulation mode, electrons become available for tunneling, and the current and conductance increases.

During processing of the tunnel devices it is possible for the aluminum to alloy with the semiconductor and form an ohmic contact, or to just contact the semiconductor and form a rectifying barrier. By direct observation we see that conduction is nonohmic; furthermore, in an injection mode the current would be strongly dependent on temperature (43) and illumination (44), as both change carrier concentration in the semiconductor. The tunnel samples were heated on a hot plate to 85°C and virtually no changes were seen as compared with room temperature I-V characteristics. The samples were measured under no illumination, under the illumination of a microscope lamp, and that of a 250 watt spot light; no photo-effects were observed.

This line of experimentation gave confidence in the tunneling characteristics, especially in the case of p-type samples which, due to band bending, were depleted with no applied bias, thus showing a characteristic similar to a reverse biased diode.

The DC conductance was calculated by graphically differentiating the DC characteristics of Figures 18 and 19. This mechanical process was relatively inaccurate (estimated up to 20% error), but no other technique was readily available for measuring the DC conductance. The DC conductance is shown in Figures 18 and 19, and will be discussed in the interpretation of data.

<sup>\*</sup> Exception, see page

AC Measurements. Ac measurements were made in an attempt to study the dynamics of tunneling currents and surface states. Typical AC currents were in the 10<sup>-10</sup> amp range. Thus, special precautions were needed for electrical measurements. Care was taken with respect to lead length and layout, using only shielded cable, shielding of apparatus and connections with metal boxes, and the use of a two level ground system where distinction was maintained between "earth" and chassis ground. Even with these precautions, many times noise levels were too high to make AC measurements, because the laboratory was near high noise RF generators, and in the path of meteorological radar. We frequently resorted to late evening - early morning experimentation to complete AC measurements.

For the AC results,  $\Delta I$  is measured in response to a fixed  $\Delta V$  (0.5 mV) superimposed on the DC bias. Therefore the  $\Delta I$  curve is directly proportional to AC conductance, and the ordinates on the AC curves of Figures 18 and 19 are in mhos, while those in Figures 20 and 21 are in log mhos.

The important features of the AC conductance curves (Figures 18 and 19) are the AC conductance well; that fact that 10, 100 and 1000 Hz curves are almost identical while the 10 kHz curve is considerably different; and that the AC conductance in the forbidden gap region is orders of magnitude greater than DC conductance in that same region. Each of these features is significant and will be discussed in the interpretation of results.

The insulator thickness data of Table I were obtained by plotting capacitance-voltage curves (CV), finding the capacitance associated

Log I-V Characteristics and Log Conductance

Wafer P-164

- □ DC current-voltage

10 Hz conductance

- O 100 Hz conductance

Figure 21

with the tunnel insulator, and substituting this value into Equation E(2) of Appendix E. The CV measurements were taken on a Boonton Capacitance Meter at a frequency of 10 kHz. The same probe contacting setup used for DC measurements were employed, and these measurements proved especially simple to perform.

This thickness calculation depended on the assumption that a capacitance could be defined for the tunnel device. A tunnel capacitance was defined if the CV curves showed a constant value of capacitance when the semiconductor was brought into accumulation (positive bias on the metal for n-type semiconductors, and vice versa). This constant accumulation capacitance is analogous to the case of thick insulator MOS capacitors and Figure 22 shows such an example. In many other devices no constant accumulation capacitance range was observed (Figure 23), indicating departures from the ideal behavior of the MOS capacitor. For these devices, insulator thickness was roughly estimated using the capacitance at a predetermined bias voltage. This was, of course, only a guess, and a different procedure was derived (Equation 19).

A discussion of MOS behavior and interpretation of CV data are presented in Appendix A. Departures from the ideal behavior occur when tunnel currents become appreciable as compared to the displacement current. In this non-ideal case, arguments relating to space charge effects do not hold valid. The implications of this nonequilibrium effect will be presented in the interpretation of results.

Figure 22

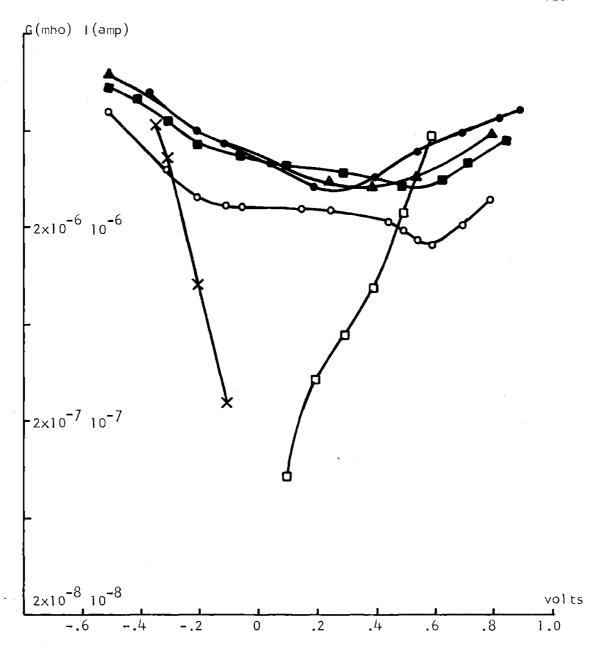

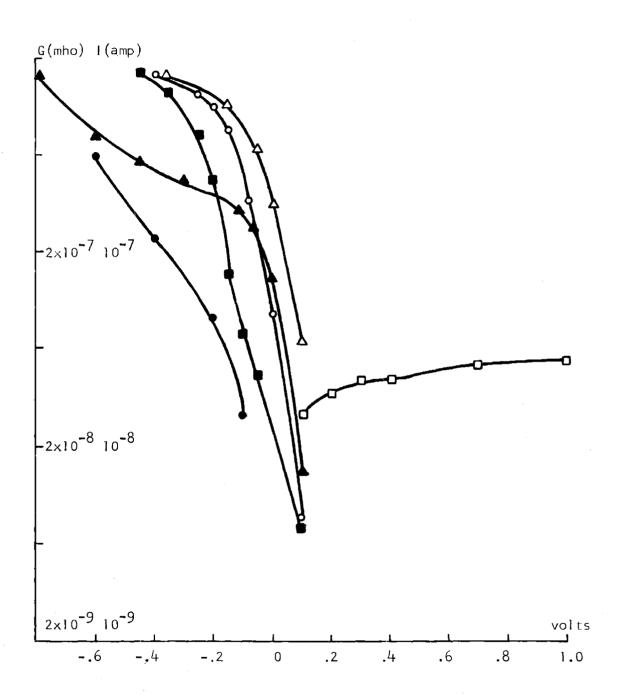

In this section we have presented the experimental data using typical curves to illustrate measurement detail. For completeness we have included data on all the other test wafers in Appendix F. Figures F1-F10 show the I-V characteristics and conduction data. Figures F11-F20 show the log of this data, and Figures F21-F30 show the CV curves.

## B. Interpretation of Experimental Results