## Mondriaan Memory Protection

by

## Emmett Jethro Witchel

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

Feb 2004

© Massachusetts Institute of Technology 2004. All rights reserved

MIT hereby grants you permission to reproduce and distribute publicly paper and electronic copies of this thesis document in whole or in part.

| Author       |                          |                 | Emmett Witchel                        |

|--------------|--------------------------|-----------------|---------------------------------------|

|              | Department of Electrical | Engineering and |                                       |

|              |                          |                 |                                       |

| Certified by |                          | •               | •                                     |

| Certified by |                          | •               | Krste Asanović<br>Associate Professor |

|              |                          |                 | Thesis Supervisor                     |

|              |                          |                 |                                       |

| Accepted by  |                          |                 |                                       |

| Accepted by  |                          |                 | Arthur C. Smith                       |

|              | Chairman, Department     | t Committee on  |                                       |

MASSACHUSETTS INSTITUTE

OF TECHNOLOGY

APR 1 5 2004

LIBRARIES

BARKER

## Mondriaan Memory Protection

by

#### Emmett Jethro Witchel

Submitted to the Department of Electrical Engineering and Computer Science on February, 2004, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

## Abstract

Reliability and security are quickly becoming users' biggest concern due to the increasing reliance on computers in all areas of society. Hardware-enforced, fine-grained memory protection can increase the reliability and security of computer systems, but will be adopted only if the protection mechanism does not compromise performance, and if the hardware mechanism can be used easily by existing software.

Mondriaan memory protection (MMP) provides fine-grained memory protection for a linear address space, while supporting an efficient hardware implementation. MMP's use of linear addressing makes it compatible with current software programming models and program binaries, and it is also backwards compatible with current operating systems and instruction sets. MMP can be implemented efficiently because it separates protection information from program data, allowing protection information to be compressed and cached efficiently. This organization is similar to paging hardware, where the translation information for a page of data bytes is compressed to a single translation value and cached in the TLB. MMP stores protection information in tables in protected system memory, just as paging hardware stores translation information in page tables. MMP is well suited to improve the robustness of modern software. Modern software development favors modules (or plugins) as a way to structure and provide extensibility for large systems, like operating systems, web servers and web clients. Protection between modules written in unsafe languages is currently provided only by programmer convention, reducing system stability. Device drivers, which are implemented as loadable modules, are now the most frequent source of operating system crashes (e.g., 85% of Windows XP crashes in one study [SBL03]). MMP provides a mechanism to enforce module boundaries, increasing system robustness by isolating modules from each other and making all memory sharing explicit.

We implement the MMP hardware in a simulator and modify a version of the Linux 2.4.19 operating system to use it. Linux loads its device drivers as kernel module extensions, and MMP enforces the module boundaries, only allowing the device drivers access to the memory they need to function. The memory isolation provided by MMP increases Linux's resistance to programmer error, and exposed two kernel bugs in common, heavily-tested drivers. Experiments with several benchmarks where MMP was used extensively indicate the space taken by the MMP data structures is less than 11% of the memory used by the kernel, and the kernel's runtime, according to a simple performance model, increases less than 12% (relative to an unmodified kernel).

Thesis Supervisor: Krste Asanović

Title: Associate Professor

## Acknowledgments

This dissertation is dedicated to the memory of Joshua Cates (1977-2004). Josh's clear thinking and quick coding contributed greatly to our ASPLOS 2002 paper. He often saw the gaps in my specification of a problem before I did. In addition to possessing great technical skill, Josh also had a great attitude, which made him a pleasure to work with. I was very happy to introduce him to the Jethro Tull album, *Heavy Horses*, which he enjoyed with great relish. The world is a lesser place with his passing.

To the man who helped me find, define, refine and write-up the ideas in my thesis and in several other projects, I would really like to thank my advisor, Professor Krste Asanović. Krste is the man, as is obvious after a few minutes of conversation with him on a startling range of topics. His ability to debug code when told of its failure conditions is scary, and extends to bugs in hardware description languages. His ability to pursue ideas for hours on end has extended beyond my body's ability to maintain sufficient blood sugar levels to my brain.

To my former advisor Professor Frans Kaashoek: who always impressed me with his values system as a researcher, and whose enthusiasm is as impressive as it is infectious. Frans' comments on this thesis were detailed enough to have a permanent effect on my writing style. He also ran the rootinest, tootinest rodeo of a group meeting I've ever been to, which was the location of many memorable graduate student moments.

To Professor Mendel Rosenblum: who took a chance on an unknown, after I pestered him enough; and whose keen intelligence and easy humor were always inspirational. Implementing statistics collection in Embra with him sitting next to me was an amazing experience in externally accelerated coding.

Graduate school is mostly about the other students and the environment, and I am thankful for my time at MIT.

To Ronny Krashinsky: whose originality of thought is startling and whose wealth of ideas makes him a potent ally.

To Chris Batten: who might have attended his lifetime limit of Mondriaan talks, but who always had interesting comments.

To Andy Ayers: a man whose deep insight is only matched by his relaxed nature. He made compiler technology a spiritual art. He taught me about the fat base class problem, among many other gems.

To Chris Metcalf: who opened my eyes to the idea that most problems with UNIX shell scripts and Makefiles come down to levels of quotation.

To Max Poletto: who inspired me with his humility and his use of ASCII pictures as code comments.

To Eddie Kohler: whose scorching mental processes I was able to observe at close range.

To David Mazières: who taught me how to be grateful. I try to be grateful.

More thanks to Chuck Blake, Doug DeCouto, Dan Aguayo, Matt Frank, Mike Taylor, Frank Dabek, Dawson Engler, Emil Sit, Russ Cox, Brian Ford, Michael Kaminsky, Heidi Pan, Ken Barr, Seongmoo Heo, Albert Ma, Jessica Tseng, Michael Zhang, Mark Hampton, Felix Klock, John Jannotti, Debbie Wallach, Fred Chung, John Bicket, Athicha Muthitacharoen,

Sanjit Biswas, Carty Castaldi, and Richard Schooler ("plans don't work, but planning does").

Special thanks to Sam Larson and C. Scott Ananian for their collaboration on papers. Extra thanks to Benjie Chen for reading a draft of my thesis and providing insightful comments.

Much thanks to Professors Anant Agarwal, Anoop Gupta, Robert Morris, Saman Amarasinghe, and Martin Rinard.

More extra thanks to Professor Barbara Liskov for reading and commenting on my thesis and for sitting on my committee.

I would like to thank the following funding sources: NSF CAREER award CCR-0093354; and DARPA PAC/C award F30602-00-2-0562.

And thank you to Neena Lyall and Shireen Yadollahpour for bringing some administrable order to my unordered travel and reimbursement needs. Thanks to Cornelia Colyer, for administrative help and discussion about France. MIT feels the loss of her death.

I view my dissertation as marking the end of my studenthood. I have long passed the mystery of the 13th grade, and now find myself at the end of the student path. I'd like to thank some of the teachers who got me here.

To Mr. Elfenbien: who taught me science in 5th grade and showed movies of his sky diving adventures, who gave ungraded general knowledge quizzes, one of which contained the question, "What is a female Czar called?" (Czarina).

To Mr. Kennefeck: who taught me English in 7th grade. He would record his lessons before classes every day and then play the tape in each class, occasionally stopping the tape to comment. This started my appreciation of academia's tolerance of eccentricity. Despite his unorthodox methods he was an excellent teacher.

To Mr. Cardinelli: who taught me English in 8th grade and tried to convince me that infer and imply were synonyms. This began my frustration with misunderstanding.

To Dr. Bumby: who taught me math in 10th grade and introduced me to imaginary numbers. I was hooked.

To Mr. New: who taught me physics and AP physics from a midwesterner's perspective. The man liked guns and took some interesting fast-exposure pictures. He gave me a battery tester that I still use today.

To Steve Fisher: who taught my second programming class at Stanford, which was one of the most fun intellectual experiences of my life. He talked fast and had a great feel for the material. I remember him explaining null terminated strings.

To the professor who taught me Modern Algebra (Math 120) at Stanford during the Autumn of 1993: who was human enough to break down in front of the class during the proof of Sylow's theorem and admit that the theorems we were proving were too abstract to relate to anything real, but what he was actually trying to do was teach us how to think.

To my mother: who was involved in my education from the start, often taking a hands on role e.g., by quizzing me on vocabulary words; who related to and encouraged my interest in science; and who endured an extended period of my childhood where my mantra was, "I don't want to go to school," with more patience than should be required of any parent.

To my father: who used to lie on the floor and read the encyclopedia on weekends; who would read a book, listen to the radio and watch TV all at the same time.

To the ancestors: as they were, so I am.

To Dan Yaverbaum: with whom I have asked and answered more questions than anyone else.

To Danielle Adler: with whom I plan to learn the rest of my days. Special thanks for the inspiration of the art of the Grateful Dead and Bob Dylan.

For me, pushing myself is way more about, "It's hard to make something that's interesting." It's really, really hard, and I'm sure we don't succeed with every story on every show. Basically, anything that anyone makes. . . It's like a law of nature, a law of aerodynamics, that anything that's written or anything that's created wants to be mediocre. The natural state of all writing is mediocrity. It's all tending toward mediocrity in the same way that all atoms are sort of dissipating out toward the expanse of the universe. Everything wants to be mediocre, so what it takes to make anything more than mediocre is such a fucking act of will. Anyone who makes something for a living, or even not for a living, if they're really excited about it. . . You just have to exert so much will into something for it to be good. That feels exactly the same now as it did the first week of the show. That hasn't changed at all. That's the premise of what it takes to make something.

—Ira Glass (producer of National Public Radio's *This American Life*) from an interview in *The Onion*.

Songs are songs - I don't believe in expecting too much out of any one thing.

#### —Bob Dylan

We can only see a short distance ahead, but we can see plenty there that needs to be done.

#### —Alan Turing

# Contents

| 1 | Intr | $\mathbf{oduction}$ |                                   |      |   | 1   | 7  |

|---|------|---------------------|-----------------------------------|------|---|-----|----|

|   | 1.1  | The problem of      | module safety                     |      |   | . 1 | 8. |

|   | 1.2  | Fine-grained pr     | otection domains                  |      |   | . 1 | 9  |

|   | 1.3  | MMP Overview        | 7                                 |      |   | . 2 | 0  |

|   | 1.4  | Example and re      | equirements                       |      |   | . 2 | 22 |

|   | 1.5  | Contributions of    | of the thesis                     |      |   | . 2 | 23 |

|   | 1.6  | Thesis outline.     |                                   |      | ٠ | . 2 | 25 |

| 2 | Mei  | mory Protection     | on                                |      |   | 2   | 7  |

|   | 2.1  | Page-based pro      | tection                           |      |   | . 2 | 27 |

|   |      | 2.1.1 Page sha      | aring                             | <br> |   | . 2 | 28 |

|   |      | 2.1.2 Groupin       | g pages                           | <br> |   | . 2 | 29 |

|   | 2.2  | Segmentation .      |                                   |      |   | . 2 | 29 |

|   | 2.3  | Capabilities        |                                   |      |   | . 3 | 30 |

|   | 2.4  | Embedded system     | ems                               |      |   | . 3 | 32 |

|   | 2.5  | Software techni     | ques                              | <br> |   | . 3 | 32 |

|   |      | 2.5.1 Nooks         | -<br>                             | <br> |   | . 3 | 32 |

|   |      | 2.5.2 Safe lan      | guages                            | <br> |   | . 3 | 3  |

|   |      | 2.5.3 Software      | e capability systems              | <br> |   | . 3 | 33 |

|   |      | 2.5.4 Single a      | ddress space operating systems    | <br> |   | . 3 | 34 |

|   |      |                     | nalysis and model checking        |      |   |     | 34 |

|   |      | 2.5.6 Lightwe       | ight remote procedure call        | <br> |   | . 3 | 34 |

|   |      | 2.5.7 Software      | e fault isolation                 | <br> |   | . 3 | 34 |

|   |      | 2.5.8 Proof-ca      | arrying code                      | <br> |   | . 3 | 35 |

|   | 2.6  |                     | rol flow                          |      |   |     | 35 |

|   |      | _                   |                                   |      |   |     | 35 |

|   |      |                     | ng control flow with capabilities |      |   |     | 36 |

|   |      |                     | m rnels                           |      |   |     | 36 |

|   | 2.7  |                     |                                   |      |   |     | 37 |

| 3 | MN   | IP Permissions      | s Table                           |      |   | 3   | 9  |

|   | 3.1  | Sorted segment      | table                             | <br> |   | . 4 | 10 |

|   | 3.2  | ~                   |                                   |      |   |     | 11 |

|   |      |                     | ion Vector Entries                |      |   |     | 11 |

|   |      |                     | gth encoded entries               |      |   |     | 12 |

|   | 3.3                                                  | Gate t                              | ables                                            | 45  |  |  |  |  |  |  |  |

|---|------------------------------------------------------|-------------------------------------|--------------------------------------------------|-----|--|--|--|--|--|--|--|

|   | 3.4                                                  | Possibl                             | le table optimizations                           | 47  |  |  |  |  |  |  |  |

|   |                                                      | 3.4.1                               | Extension to 64-bits addresses                   | 47  |  |  |  |  |  |  |  |

|   |                                                      | 3.4.2                               | Sharing permission tables                        | 47  |  |  |  |  |  |  |  |

|   |                                                      | 3.4.3                               | Alternate permissions encodings                  | 48  |  |  |  |  |  |  |  |

| 4 | N/N                                                  | IP Har                              | dwara                                            | 51  |  |  |  |  |  |  |  |

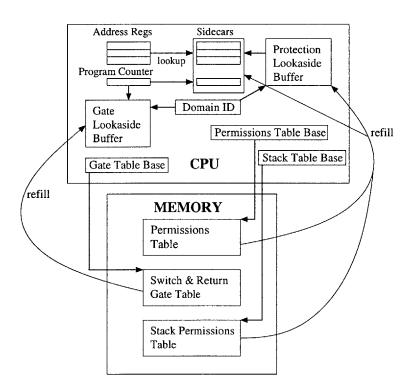

| 4 | 4.1                                                  |                                     | dware<br>side Buffers                            |     |  |  |  |  |  |  |  |

|   | 4.1                                                  | 4.1.1                               | Protection Lookaside Buffer (PLB)                |     |  |  |  |  |  |  |  |

|   |                                                      | 4.1.1 $4.1.2$                       | Gate protections lookaside buffer (GPLB)         |     |  |  |  |  |  |  |  |

|   | 4.2                                                  |                                     | r registers                                      |     |  |  |  |  |  |  |  |

|   | 4.2                                                  |                                     | domain calling                                   |     |  |  |  |  |  |  |  |

|   | 4.5                                                  | 4.3.1                               |                                                  |     |  |  |  |  |  |  |  |

|   |                                                      | 4.3.1 $4.3.2$                       | Gate requirements                                |     |  |  |  |  |  |  |  |

|   |                                                      |                                     | Gate implementation                              |     |  |  |  |  |  |  |  |

|   | 4.4                                                  | 4.3.3                               | Cross-domain call example                        |     |  |  |  |  |  |  |  |

|   | 4.4                                                  |                                     | are implementation issues                        |     |  |  |  |  |  |  |  |

|   |                                                      | 4.4.1                               | In-order pipeline implementation                 |     |  |  |  |  |  |  |  |

|   |                                                      | 4.4.2                               | Out-of-order pipeline implementation             |     |  |  |  |  |  |  |  |

|   |                                                      | 4.4.3                               | Mixing mapped and pinned memory                  |     |  |  |  |  |  |  |  |

|   |                                                      | 4.4.4                               | The problem with inlining code                   |     |  |  |  |  |  |  |  |

|   |                                                      | 4.4.5                               | Approaches for multi-processors                  | 59  |  |  |  |  |  |  |  |

| 5 | MN                                                   | MMP Evaluation for User Programs 61 |                                                  |     |  |  |  |  |  |  |  |

|   | 5.1                                                  |                                     | tion Methodology                                 |     |  |  |  |  |  |  |  |

|   | 5.2                                                  |                                     | mark overview and methodology                    |     |  |  |  |  |  |  |  |

|   | 5.3                                                  |                                     | -Grained Protection Results                      |     |  |  |  |  |  |  |  |

|   | 5.4                                                  |                                     | rained Protection Results                        |     |  |  |  |  |  |  |  |

|   | 5.5                                                  |                                     | ry Hierarchy Performance                         |     |  |  |  |  |  |  |  |

| c | 1. <i>(</i> 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1 | (D. N.(                             | G                                                | c c |  |  |  |  |  |  |  |

| 6 | 6.1                                                  |                                     | mory Supervisor                                  | 69  |  |  |  |  |  |  |  |

|   |                                                      |                                     | ry supervisor concepts                           |     |  |  |  |  |  |  |  |

|   | 6.2                                                  |                                     | the supervisor for a modular application         |     |  |  |  |  |  |  |  |

|   | $6.3 \\ 6.4$                                         |                                     | ry supervisor overview                           |     |  |  |  |  |  |  |  |

|   | 0.4                                                  |                                     | ry supervisor API                                |     |  |  |  |  |  |  |  |

|   |                                                      | 6.4.1                               | Protection domain creation                       |     |  |  |  |  |  |  |  |

|   |                                                      | 6.4.2                               | Protection domain deletion                       |     |  |  |  |  |  |  |  |

|   |                                                      | 6.4.3                               | Changing memory permissions                      |     |  |  |  |  |  |  |  |

|   |                                                      | 6.4.4                               | Setting gate permissions                         |     |  |  |  |  |  |  |  |

|   |                                                      | 6.4.5                               | Dynamic memory allocation                        |     |  |  |  |  |  |  |  |

|   |                                                      | 6.4.6                               | Naming domains                                   |     |  |  |  |  |  |  |  |

|   |                                                      | 6.4.7                               | Group protection domains                         |     |  |  |  |  |  |  |  |

|   | 6.5                                                  | _                                   | for memory ownership and permissions             |     |  |  |  |  |  |  |  |

|   | 6.6                                                  |                                     | nic memory allocation                            |     |  |  |  |  |  |  |  |

|   |                                                      | 6.6.1                               | Design of a generic memory allocator             |     |  |  |  |  |  |  |  |

|   |                                                      | 6.6.2                               | Freeing memory                                   |     |  |  |  |  |  |  |  |

|   | _                                                    | 6.6.3                               | Dynamically allocated memory and domain deletion |     |  |  |  |  |  |  |  |

|   | 67                                                   | Momor                               | ry supervisor data structures                    | 80  |  |  |  |  |  |  |  |

|   |     | 6.7.1  | Tracking memory sharing across domains                                |

|---|-----|--------|-----------------------------------------------------------------------|

|   |     | 6.7.2  | Tracking group protection domains                                     |

| _ |     |        |                                                                       |

| 7 |     |        | the MMP-Enabled Linux Prototype 83                                    |

|   | 7.1 |        | system reset to kernel initialization                                 |

|   | 7.2 |        | ng modules into protection domains                                    |

|   |     | 7.2.1  | Modifying insmod                                                      |

|   |     | 7.2.2  | Domain creation with module loading                                   |

|   |     | 7.2.3  | The mmp-kernel-symbols module                                         |

|   |     | 7.2.4  | Setting permissions on kernel program sections                        |

|   |     | 7.2.5  | Communicating memory sharing patterns to MMP 88                       |

|   |     | 7.2.6  | Initial RAM disk                                                      |

|   |     | 7.2.7  | The printk domain                                                     |

|   | 7.3 | Dynar  | mic memory allocation in Mondrix                                      |

|   |     | 7.3.1  | Background on Linux's memory allocators                               |

|   |     | 7.3.2  | Integrating the memory supervisor with Linux's memory allocators . 91 |

|   |     | 7.3.3  | Executing the allocator and memory supervisor atomically 92           |

|   |     | 7.3.4  | Providing length information to the memory supervisor 92              |

|   |     | 7.3.5  | Reducing memory supervisor work during (de)allocation 92              |

|   |     | 7.3.6  | Supporting custom allocators                                          |

|   |     | 7.3.7  | Trusting the caller of mmp_mem_free                                   |

|   | 7.4 | Manag  | ging permissions in Mondrix                                           |

|   |     | 7.4.1  | EIDE disk driver                                                      |

|   |     | 7.4.2  | NE2000 network driver                                                 |

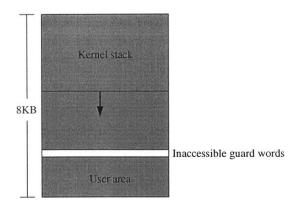

|   |     | 7.4.3  | Kernel stack/user area                                                |

|   |     | 7.4.4  | Optimizing PLB performance for kernel stack/user area 96              |

|   |     | 7.4.5  | Optimizing function pointers                                          |

|   |     | 7.4.6  | Runtime adjustment of permissions                                     |

|   | 7.5 | Cross- | domain calling                                                        |

|   |     | 7.5.1  | Interrupts                                                            |

|   |     | 7.5.2  | Passing arguments                                                     |

|   |     | 7.5.3  | Inlined functions and protection domains                              |

|   |     |        | •                                                                     |

| 8 | Exp | erime  | ntal Evaluation of Mondrix 99                                         |

|   | 8.1 | MMP    | exposes an error                                                      |

|   | 8.2 | Exper  | imental methodology                                                   |

|   | 8.3 |        | ations of model accuracy                                              |

|   | 8.4 | Result |                                                                       |

|   | 8.5 | Evalua | ation of cross-domain calling in the Linux kernel                     |

| _ | T 1 |        |                                                                       |

| 9 |     | _      | Stack Permissions 107                                                 |

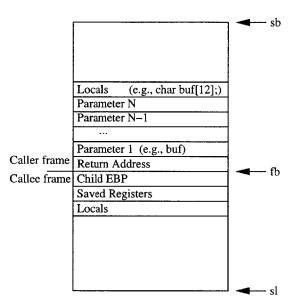

|   | 9.1 |        | ry supervisor's stack responsibilities                                |

|   | 9.2 |        | ging stack permissions with extra registers                           |

|   | 9.3 |        | allocated parameters                                                  |

|   | 9.4 | Altern | atives to sharing stack memory 110                                    |

| 10 | Adding Translation to MMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 111   |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|    | 10.1 Zero-copy networking background                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 112 |

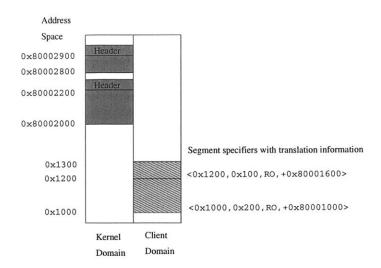

|    | 10.2 Memory translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | . 112 |

|    | 10.3 Implementing zero-copy networking with MMPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 112 |

|    | 10.4 Translation hardware implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

|    | 10.5 Complications from byte-level translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 115 |

|    | 10.5.1 Adding translation to sorted segment table entries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

|    | 10.5.2 Adding translation to run-length encoded entries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

|    | 10.6 Evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| 11 | Additional Applications, Future Work, and Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 119   |

|    | 11.1 Additional applications for MMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

|    | 11.1.1 Combining fine-grained protection and translation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |

|    | 11.2 MMP and programming languages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

|    | 11.2.1 Language-level interface to MMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |

|    | 11.2.2 Implementing exceptions and continuations in MMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |

|    | · • ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |

|    | 11.3 Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 122 |

|    | Total Control of the | 105   |

| A  | Interface file for Mondrix memory supervisor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 125   |

# List of Figures

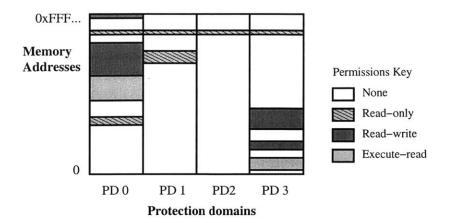

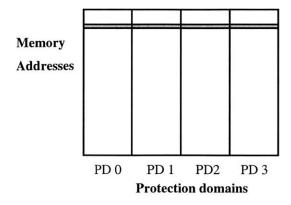

| 1-1  | A visual depiction of multiple memory protection domains within a single shared address space                                                                                  | 19              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

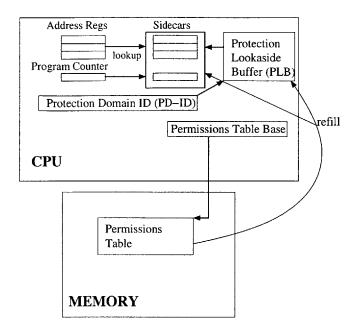

| 1-2  | The major components of the Mondriaan memory protection system                                                                                                                 | 2               |

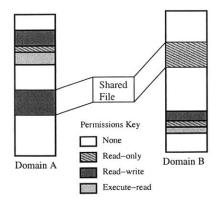

| 2-1  | Sharing memory at page granularity via mmap                                                                                                                                    | 28              |

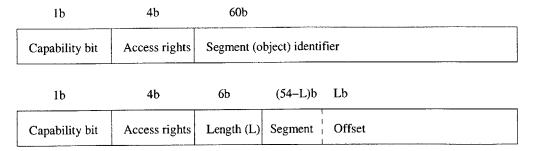

| 2-2  | Two example capabilities                                                                                                                                                       | 30              |

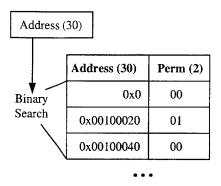

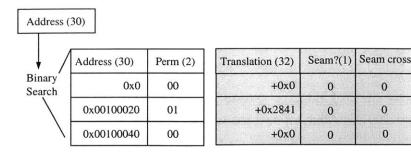

| 3-1  | A sorted segment table (SST). Entries are kept in sorted order and binary searched on lookup. In this example, there is a single read-only region from 0x00100020 - 0x0010003F | 40              |

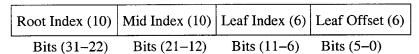

| 3-2  | How an address indexes the trie.                                                                                                                                               | 41              |

| 3-3  | Pseudo-code for the trie table lookup algorithm.                                                                                                                               | 42              |

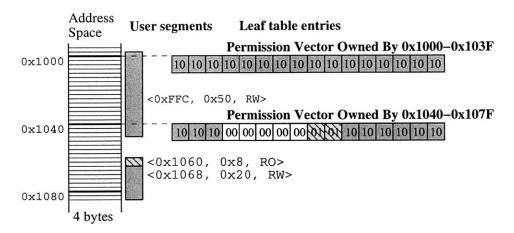

| 3-4  | A trie table entry consisting of a permissions vector                                                                                                                          | 43              |

| 3-5  | The bit allocation for upper level entries in the permissions vector trie table, and the implementation of the function used in trie_table_lookup                              | 43              |

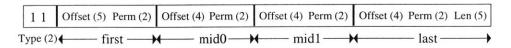

| 3-6  | The bit allocation for a run-length encoded permission table entry                                                                                                             | 44              |

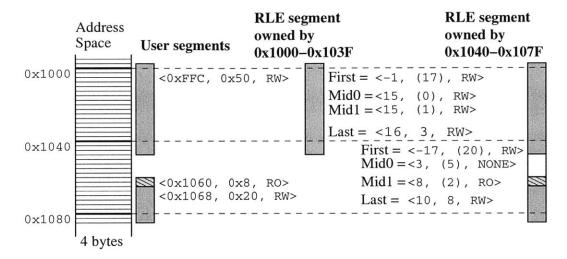

| 3-7  | An example of segment representation for run-length encoded entries                                                                                                            | 44              |

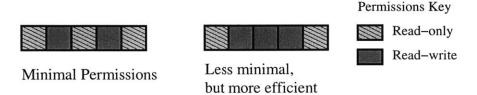

| 3-8  | Permissions minimality example                                                                                                                                                 | 45              |

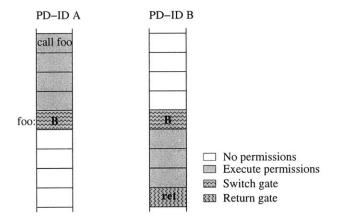

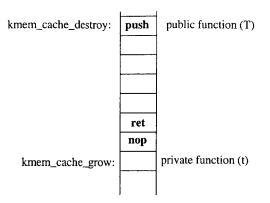

| 3-9  | How gates permissions are placed on instructions for cross-domain calling                                                                                                      | 46              |

| 3-10 | The format of an entry in the gate permission table                                                                                                                            | 47              |

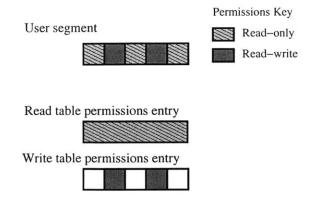

| 3-11 | How independent tables for independent permissions values can yield efficient entries.                                                                                         | 48              |

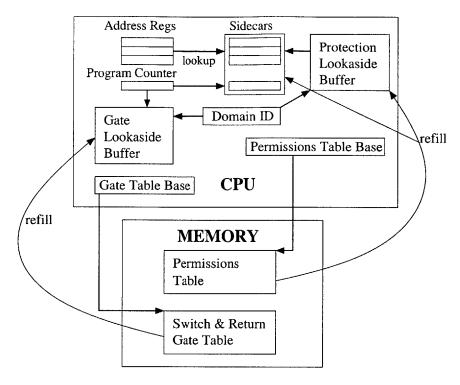

| 4-1  | The major components of the Mondriaan memory protection system, with support for switch and return gates.                                                                      | 52              |

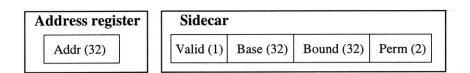

| 4-2  | The layout of an address register with its sidecar register.                                                                                                                   | $\frac{52}{53}$ |

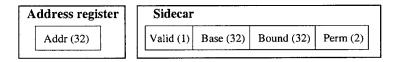

| 4-3  | How MMP is used for cross-domain calling                                                                                                                                       | 55              |

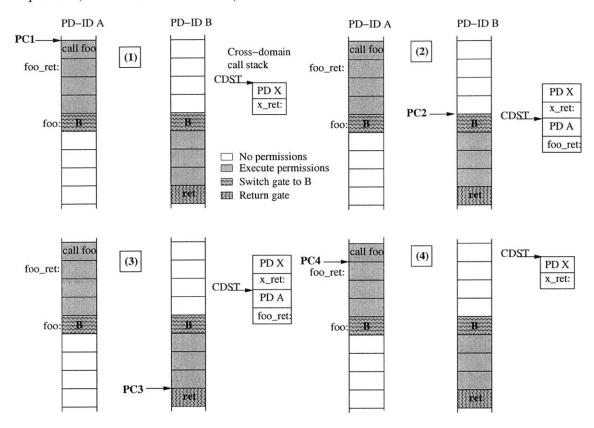

| 4-4  | How the same code (eg, interrupt stubs) can be mapped into every domain.                                                                                                       | 56              |

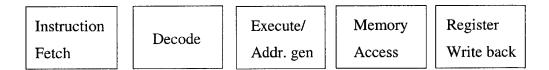

| 4-5  | An in-order, five-stage pipeline.                                                                                                                                              | 57              |

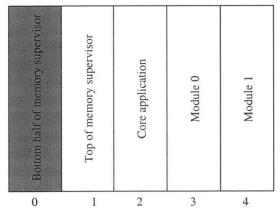

| 6-1  | Structuring a generic, modular application to use multiple domains                                                                                                             | 70              |

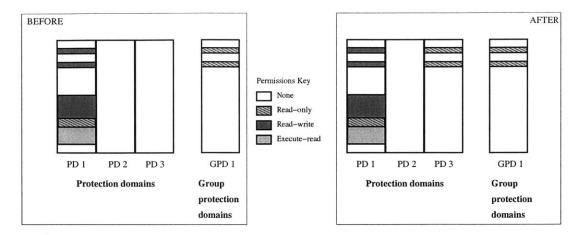

| 6-2  | An example of a group protection domain                                                                                                                                        | 75              |

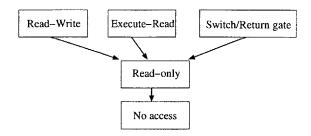

| 6-3  | A partial order on permissions values                                                                                                                                          | 78              |

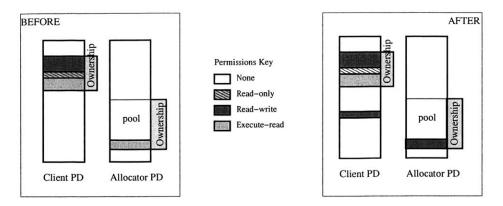

| 6-4  | A before and after picture for memory allocation                                                                                                                               | 79              |

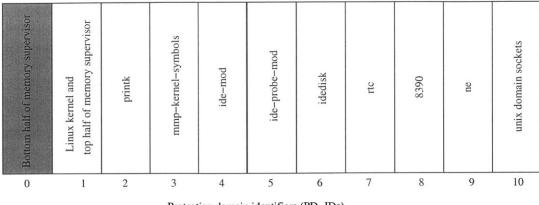

| 7-1  | How Mondrix loads different modules into different protection domains                                                                                                          | 84              |

| 7-2  | Finding the start and end of function implementations                                                                                                                          | 86              |

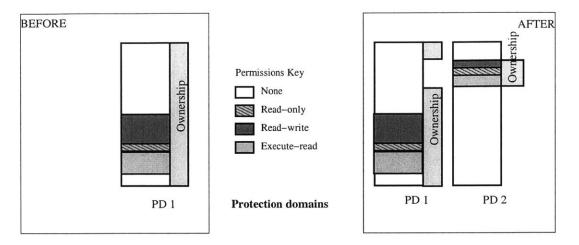

| 7-3  | A before and after picture for domain creation with module loading                                                                                                             | 87              |

| 7-4  | Named and anonymous sharing of code and data                                  | 88  |

|------|-------------------------------------------------------------------------------|-----|

| 7-5  | Memory permissions corruption scenario if dynamic memory allocator and        |     |

|      | memory supervisor do not execute atomically                                   | 92  |

| 7-6  | How MMP can protect the user area from the kernel stack                       | 95  |

| 9-1  | Providing stack safety with three hardware registers                          | 108 |

| 9-2  | The major components of the Mondriaan memory protection, including sup-       |     |

|      | port for managing stack permissions.                                          | 109 |

| 10-1 | An example of byte-level translation                                          | 113 |

| 10-2 | Using memory protection and segment translation to implement zero-copy        |     |

|      | networking                                                                    | 114 |

| 10-3 | The layout of an address register with sidecar which has translation informa- |     |

|      | tion (shaded portion)                                                         | 114 |

| 10-4 | A sorted segment table (SST) with translation information                     | 116 |

|      | The format for a record with a run-length encoded entry and translation       |     |

|      | information.                                                                  | 116 |

# List of Tables

| 3.1 | Example permission values and their meaning.                                   | 38         |

|-----|--------------------------------------------------------------------------------|------------|

| 3.2 | The different types of trie table entries, and the implementation of the func- |            |

|     | tion used in trie_table_lookup                                                 | <b>4</b> 5 |

| 3.3 | Gate types and their associated data                                           | 46         |

| 5.1 | The reference behavior of benchmarks                                           | 63         |

| 5.2 | Coarse-grained protection results                                              | 64         |

| 5.3 | Comparison of time and space overheads with inaccessible words before and      |            |

|     | after every malloced region                                                    | 66         |

| 5.4 | Measurements of miss rates for a trie table with run-length encoded entries    |            |

|     | and a 60 entry PLB                                                             | 67         |

| 5.5 | Cache behavior of user applications using fine-grained protection              | 68         |

| 6.1 | Memory supervisor policy for memory ownership and permissions                  | 77         |

| 8.1 | The names and descriptions of the modules that Mondrix loads                   | 100        |

| 8.2 | The names and descriptions of the benchmarks run by Mondrix to evaluate        |            |