# Characterization of Schottky Barrier Carbon Nanotube Transistors and their Applications to Digital Circuit Design

by

Julia Van Meter Cline

B.Sc., Brown University (2002)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Masters of Science in Electrical Engineering and Computer Science

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2004

| M/ | ASSACHUSETTS INSTITUTE<br>OF TECHNOLOGY |  |

|----|-----------------------------------------|--|

|    | JUL 2 6 2004                            |  |

| _  | LIBRARIES                               |  |

© Massachusetts Institute of Technology 2004

Signature of Author...... Department of Electrical Engineering and Computer Science May 24, 2004

Certified by .....

Certified by .....

Anantha Chandrakasan Professor, EECS Thesis Supervisor

Dimitri Antoniadis Professor, EECS Thesis Supervisor

Accepted by.....

Arthur C. Smith Chairman, EECS Department Committee on Graduate Students

# Characterization of Schottky Barrier Carbon Nanotube Transistors and their Applications to Digital Circuit Design

by

Julia Van Meter Cline

Submitted to the Department of Electrical Engineering and Computer Science on May 21, 2004, in partial fulfillment of the requirements for the degree of Masters of Science in Electrical Engineering and Computer Science

#### Abstract

The difficulty in shrinking silicon transistors past a certain feature size has been acknowledged for years. Carbon nanotubes (CNTs) offer a technology with an exciting solution to the scaling issues of transistors and interconnects and with the possibility of coexistence in the present silicon technology. The goal of the present work is to propose circuit models for carbon nanotube field effect transistors (CNTFETs) and apply them to aspects of digital circuit design.

This research models the current voltage characteristics of CNTFETs below and above threshold. The current characteristics are similar to MOSFETs, but with a few caveats. Under standard conditions, the devices do not enter saturation. Also, it is shown that CNTFETs are ambipolar devices, with a minimum current at  $V_{ds}/2$ . Despite this distinction from MOSFETs, CNTFETs show impressive voltage transfer characteristics (VTC), even at low voltages. The large noise margin and notable output voltage swing can be traded-off for higher on-current, depending on the nanotube diameter, as shown in this work. Thus, digital designers have an ability to control both performance and power by changing the nanotube diameters.

Carbon nanotubes FETs can become prominent in the arena of array devices, which are a technical front runner for the integration of wires and transistors. This work shows that carbon nanotube field effect transistors have strong potential in read only memory (ROM) arrays. Many CNTFETs can be placed along the length of a nanotube to create intermolecular devices and small array applications. The present process variations within carbon nanotubes lead to possible metallic CNTs and added redundancy. The necessary redundancy is illustrated in detail in this thesis along with the corresponding trade-offs for redundancy, area, and performance.

In conclusion, the striking properties of carbon nanotubes give CNTFET noteworthy IV characteristics and offer many opportunities for digital circuit designers in the near future. This thesis research models and characterizes the future opportunities of CNTFETs within digital designs.

Thesis Supervisor: Anantha Chandrakasan Title: Professor, EECS

Thesis Supervisor: Dimitri Antoniadis Title: Professor, EECS

(1,1,1,1)

# Acknowledgements

I would like to thank Anantha Chandrakasan for giving me the opportunity to work on this project and in his group for two years; his advice, comments, support, and contacts have been invaluable. These past two years have been a struggle for me at times; however, I have learned an enormous amount.

Without a background, this field was difficult to enter and hard to find a focused project; Professor Antoniadis's discussions and advice on the topic were very helpful. Also, his comments on my thesis were especially enlightening.

I would like to thank Joerg Appenzeller and Phillip Wong at IBM. My phone call discussions with Joerg were incredibly helpful. It was wonderful to have the perspective and knowledge of someone working first hand within the nanotube field.

The Semiconducting Research Corporation (SRC) gave me the opportunity to research this interesting future topic. My SRC Master's Fellowship opened up many possibilities for me. And, I would also like to thank the SRC for introducing me to an amazing community.

I would not have been at this place in my career without the help and support from the following people. Kerry Bernstein at IBM gave me an endless amount of thought provoking comments, contacts, and confidence. Also, Professor Friedman, at the University of Rochester, gave me the opportunity to start exploring the field of digital circuit design and Professor Beresford gave me continual support and advice throughout my Brown University career.

Thank you to Johnna Powell for being my proofreader, outlet, and friend. And, I would also like to thank Anantha-group past and present. Alex, Frank, Ben, Alice, Nathan, Rex, Puneet, Dave, Brian, Naveen, Fred, Raul, Daniel, Payam, and Denis gave me help, comments, questions, and friendships. It was a pleasure working in the same lab with them.

I would also like to thank Kate Martin. As I figure out my career path, I hope to make both of our paths cross again soon; I do not know how I will manage without her. I'm leaving my exercise partner, my every-night-date, my study partner, and most importantly my best friend. I would have never made it through without her. I would also like to thank Steve Kelly for giving me his love, support, confidence, jokes, and stories. I look forward to our time together. Thank you also to Betsy More. It is unbelievable how our lives are so opposite, but take us to the same places. I hope that continues. Thank you to April, Taylor, Nancy, Kathy, Chrissy, Alison, and Angela for their friendship on and off the field. Also, it was a true honor to play with sMITe through any condition and any opponent.

I would like to thank Jackie; it is because of our endless discussions that I have found my own path through MIT and into the future.

And last but not at all least, I would like to thank my family. My dad and mom have gotten me through everything, good and bad. I do not know how to thank them enough. It seems the more I grow up, the more help and advice I ask for. No distance will ever be great enough to keep me from calling home everyday and sometimes even a few times a day. Once a parent, always a parent! Thank you also to my brother Geoffrey, who has shown me how to follow what I really want and keep me calm through any storm.

# Contents

| 1                                 | Car | bon Nanotubes Structure, Properties, and Growth          | 15 |

|-----------------------------------|-----|----------------------------------------------------------|----|

|                                   | 1.1 | Background                                               | 15 |

|                                   | 1.2 | Structure of Carbon Nanotubes                            | 16 |

|                                   |     | 1.2.1 Chirality                                          | 16 |

|                                   |     | 1.2.2 Single Walled versus Multi Walled Carbon Nanotubes | 17 |

|                                   | 1.3 | Growth Processes                                         | 19 |

|                                   |     | 1.3.1 Arc-Discharge                                      | 20 |

|                                   |     | 1.3.2 Chemical Vapor Deposition                          | 20 |

|                                   |     | 1.3.3 Laser Ablation                                     | 20 |

|                                   |     | 1.3.4 Growth Processes Variation                         | 23 |

|                                   | 1.4 | Electron Mobility Characteristics in Carbon Nanotubes    | 23 |

|                                   | 1.5 | Conclusion                                               | 24 |

| 2 Carbon Nanotubes as Transistors |     | bon Nanotubes as Transistors                             | 25 |

|                                   | 2.1 | Schottky Barrier Field Effect Transistors: Fabrication   | 25 |

|                                   | 2.2 | Schottky Barrier Field Effect Transistors: Operation     | 27 |

|                                   | 2.3 | Carbon Nanotube Transistor Width                         | 32 |

|                                   | 2.4 | P-Channel versus N-Channel Schottky barrier CNTFETs      | 33 |

|                                   |     | 2.4.1 Annealing                                          | 34 |

|                                   |     | 2.4.2 Doping with Alkali Metals                          | 34 |

|                                   |     | 2.4.3 Conclusion                                         | 36 |

|                                   | 2.5 | CNTFET Scaling                                           | 36 |

|   | 2.6 | Conc   | lusion                                             | 38 |

|---|-----|--------|----------------------------------------------------|----|

| 3 | Sub | thresh | old Carbon Nanotube Field Effect Transistors       | 39 |

|   | 3.1 | Subth  | reshold CNTFET Current                             | 40 |

|   |     | 3.1.1  | Current versus $V_{Gate-Source}$ Characteristics   | 41 |

|   | 3.2 | Matla  | b Model                                            | 44 |

|   |     | 3.2.1  | $I_{drain}$ versus $V_{gate-source}$ Model         | 44 |

|   |     | 3.2.2  | Current versus $V_{Drain-Source}$ Model            | 49 |

|   | 3.3 | Invert | er                                                 | 51 |

|   |     | 3.3.1  | Voltage Transfer Characteristics of an Inverter    | 51 |

|   | 3.4 | Proces | s Variations                                       | 59 |

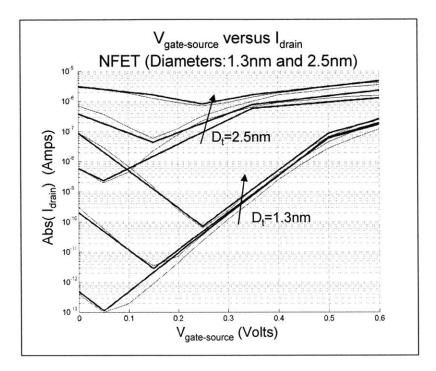

|   |     | 3.4.1  | Varying Nanotube Diameter                          | 59 |

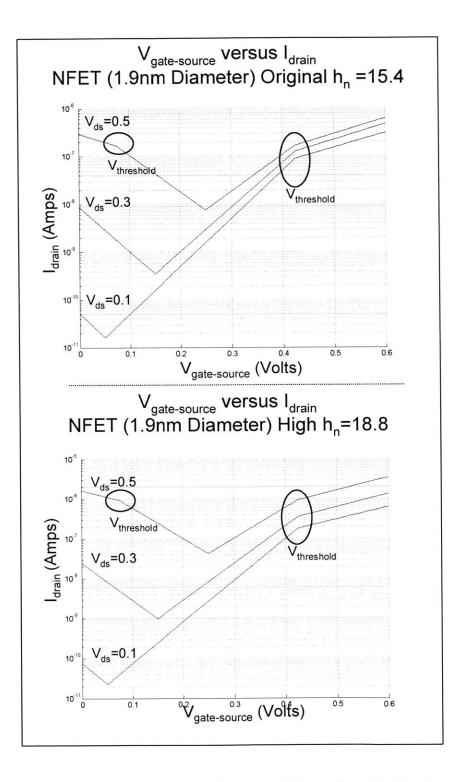

|   |     | 3.4.2  | Changing Drain Control versus Gate Control $(h_n)$ | 61 |

| 4 | Cap | acitan | ce, Energy, and Delay of Subthreshold CNTFETs      | 64 |

|   |     | 4.0.3  | Capacitance                                        | 64 |

|   |     | 4.0.4  | Delay                                              | 75 |

|   |     | 4.0.5  | Conclusion                                         | 76 |

| 5 | Abo | ove Th | reshold Model                                      | 78 |

|   |     | 5.0.6  | Linear Regime                                      | 78 |

|   |     | 5.0.7  | Saturation Point                                   | 81 |

|   |     | 5.0.8  | Saturation Regime                                  | 83 |

|   |     | 5.0.9  | MOSFETs compared to CNTFETs                        | 84 |

|   |     | 5.0.10 | Process Variations                                 | 85 |

| 6 | RO  | M Res  | earch                                              | 87 |

|   | 6.1 | Schott | ky Barrier ROM Array Structures                    | 88 |

|   |     | 6.1.1  | NOR ROMs                                           | 88 |

|   |     | 6.1.2  | Programing ROM Arrays                              | 88 |

|   |     | 6.1.3  | ROM Redundancy                                     | 93 |

|   |     | 6.1.4  | ROM Area                                           | 95 |

.

|   | 6.1.5     | ROM Capacitance                                                                              |

|---|-----------|----------------------------------------------------------------------------------------------|

|   | 6.1.6     | ROM Resistance                                                                               |

|   | 6.1.7     | Conclusion                                                                                   |

| 7 | Conclusio | ns 103                                                                                       |

| A | Appendix  | 110                                                                                          |

|   | A.1 Matla | b Code for $I_d$ versus $V_{gs}$ and $V_{ds}$ including Voltage Transfer Characteristics 110 |

|   | A.2 Matla | b Code for ROM Capacitance Model                                                             |

$\mathbb{R}^{2}_{\sigma}$

••••

# List of Figures

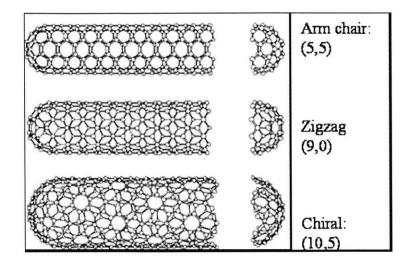

| 1-1 | Carbon nanotube cylinders with varying chiralities. (From [1])                                              | 16 |

|-----|-------------------------------------------------------------------------------------------------------------|----|

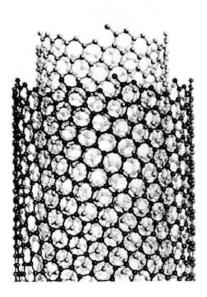

| 1-2 | A multi walled carbon nanotube. (From [2])                                                                  | 18 |

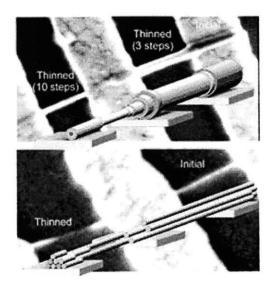

| 1-3 | Multi walled carbon nanotubes are shown at the top and single walled carbon                                 |    |

|     | nanotubes are bundled in the second picture. (From [3]) $\ldots \ldots \ldots \ldots \ldots$                | 19 |

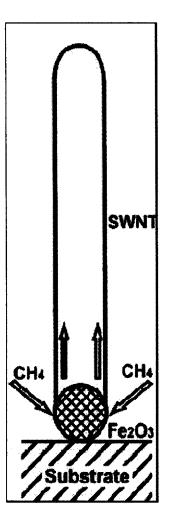

| 1-4 | A diagram illustrating SWCNT growth by chemical vapor deposition. (From [4])                                | 21 |

| 1-5 | Picture of CVD growth from [4]. The bottom bar is a scale of 10 nm in length. $% \mathcal{L}^{(1)}$ .       | 22 |

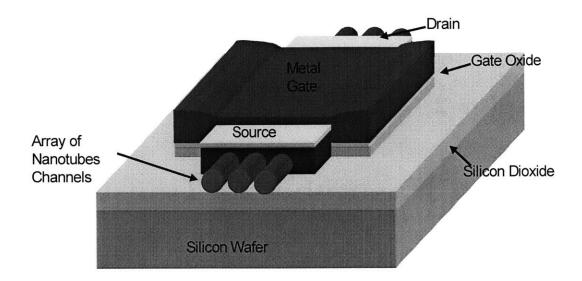

| 2-1 | Diagram of a top gated CNT transistor structure                                                             | 26 |

| 2-2 | Illustration of band diagrams for a Schottky barrier CNT transistor in the 'off'                            |    |

|     | and 'on' states, respectively. (From [5].)                                                                  | 28 |

| 2-3 | Subthreshold band diagrams for Schottky barrier transistors related to the $\mathbf{I}_d$                   |    |

|     | versus $V_{gs}$ graph                                                                                       | 28 |

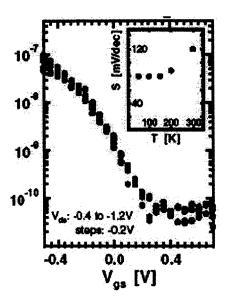

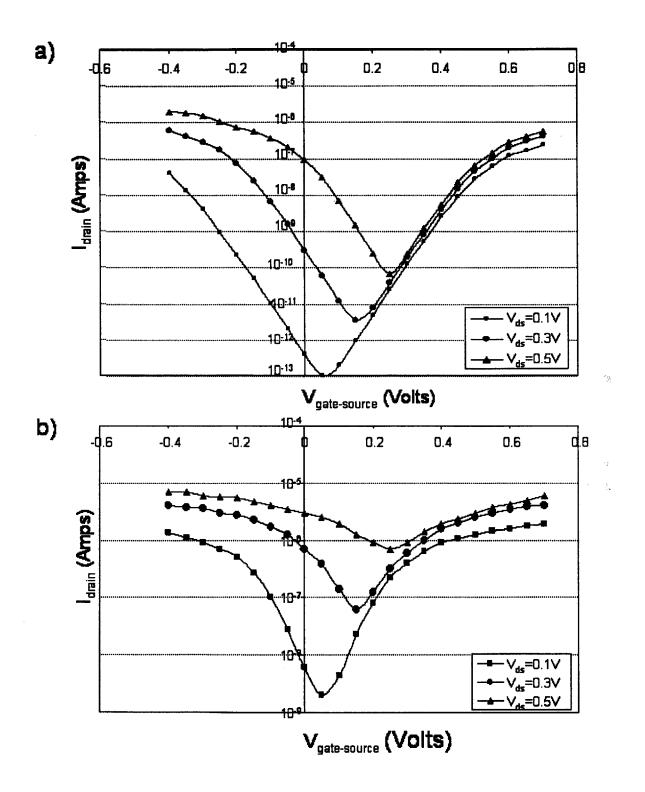

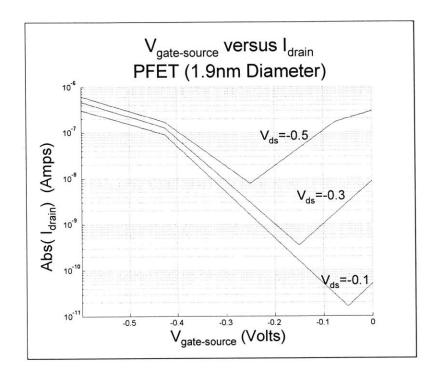

| 2-4 | $\mathbf{I}_d$ versus $\mathbf{V}_{gs}$ subthreshold characteristics for a p-type transitor, with a channel |    |

|     | length of 300nm and a gate oxide thickness $(t_{ox})$ , HfO <sub>2</sub> , of 20nm. The subthresh-          |    |

|     | old characteristics do not vary largely with $V_{ds}$ and the subthreshold slope, S,                        |    |

|     | remains relatively constant with temperature. (From $[5]$ )                                                 | 29 |

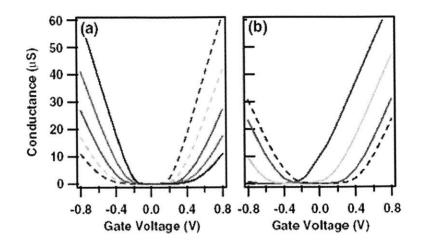

| 2-5 | Conductance changes as the work function of the drain and source metals are                                 |    |

|     | varied to the band gap of the semiconducting CNT. Also, these graphs note how                               |    |

|     | current increases if an opposite gate voltage is applied. (From [6]) $\ldots \ldots \ldots$                 | 30 |

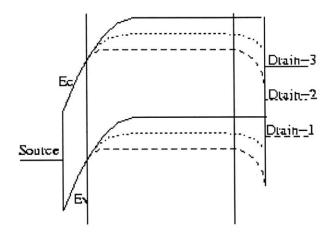

| 2-6 | Band diagrams for a Schottky barrier transistor in the triode regime and at the                             |    |

|     | saturation point.                                                                                           | 31 |

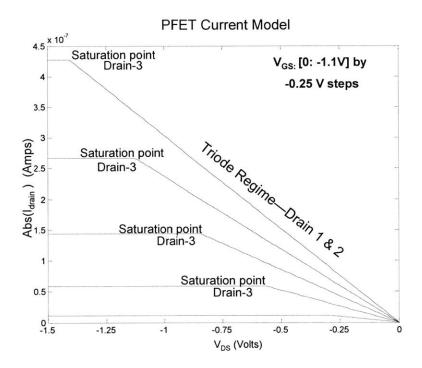

| 2-7 | This figure follows the drain voltages shown in Figure 2-6. Drain-1 & 2: Linear                             |    |

|     | Regime, Drain-3: Saturation point                                                                           | 31 |

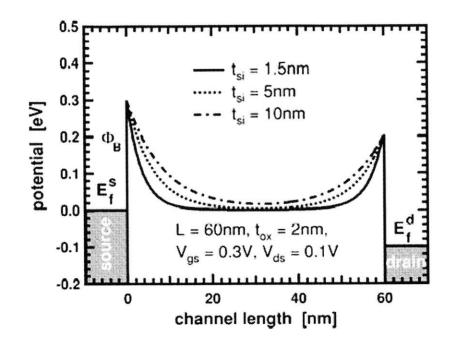

| 2-8 | Energy band bending of a CNTFET is larger with a thinner gate oxide. (From [7]) 32 |

|-----|------------------------------------------------------------------------------------|

| 2-9 | CNTFET IV characteristics, depending on oxidation of the CNT to metal inter-       |

- 2-10 Shifting of  $I_d$  versus  $V_{gs}$  curves, with a varying amounts of potassium. (From [6]) 36

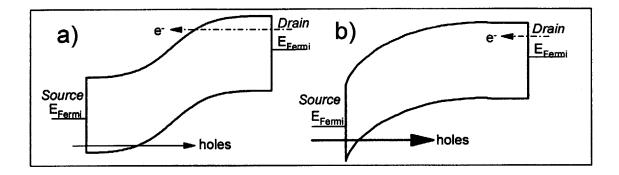

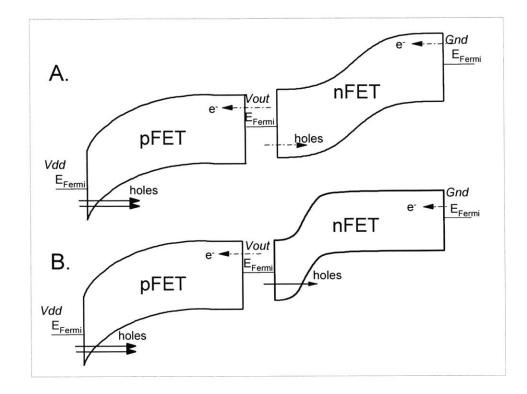

- 3-1 Picture A represents the band modulation of a transistor with the least current; the  $V_{ds}$  voltage is split evenly between the source to channel and drain to channel and thus the Schottky barriers are thickest and the current is at a minimum. In picture B, the band diagrams illustrate a transistor that is 'on', with a larger negative gate voltage. The hole tunneling current from the source is orders of magnitude larger than the electron tunneling current from the drain. In both A and B, the arrows represent the hole and electron tunneling currents. The relative size of these arrows represents the relative size of the tunneling currents. 42

9

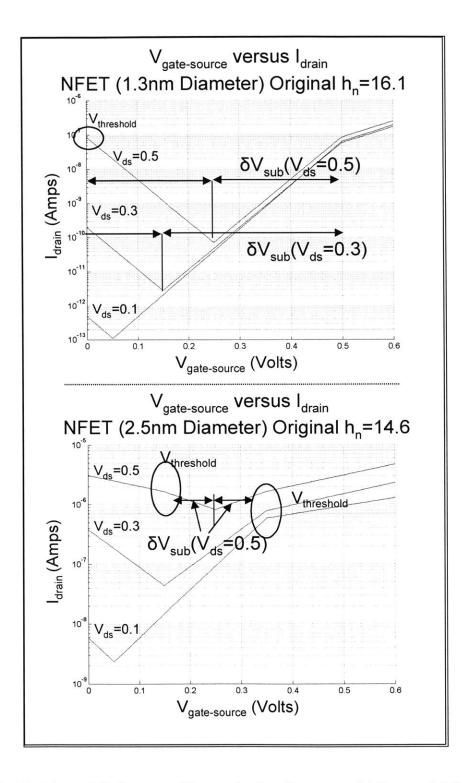

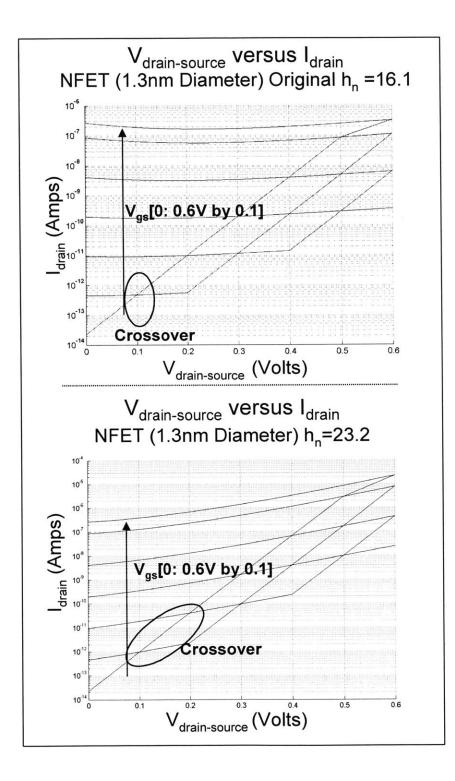

| Current versus drain to source voltage for a CNTFET with a CNT diameter of                                |                                                                                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.3nm and a changing drain control versus gate control level, $h_n$ . Low $h_n$ in the                    |                                                                                                                                                                                                                              |

| top graph, gives little slope to the high $V_{gs}$ lines. With a higher $h_n$ in the second               |                                                                                                                                                                                                                              |

| graph, the lines have a much larger slope. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 52                                                                                                                                                                                                                           |

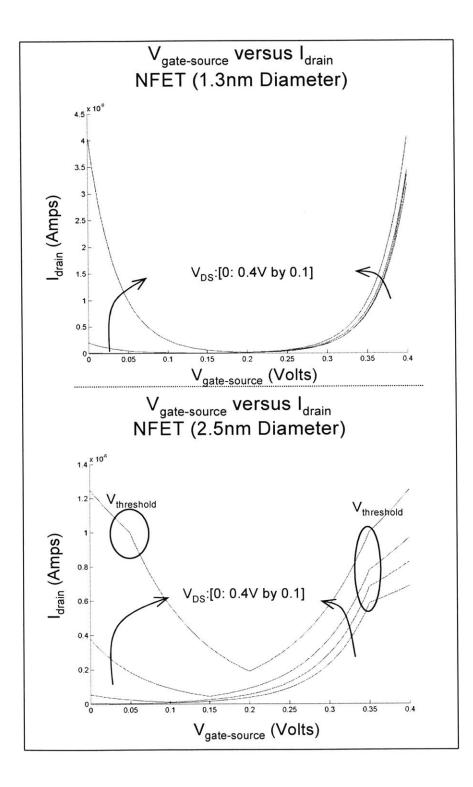

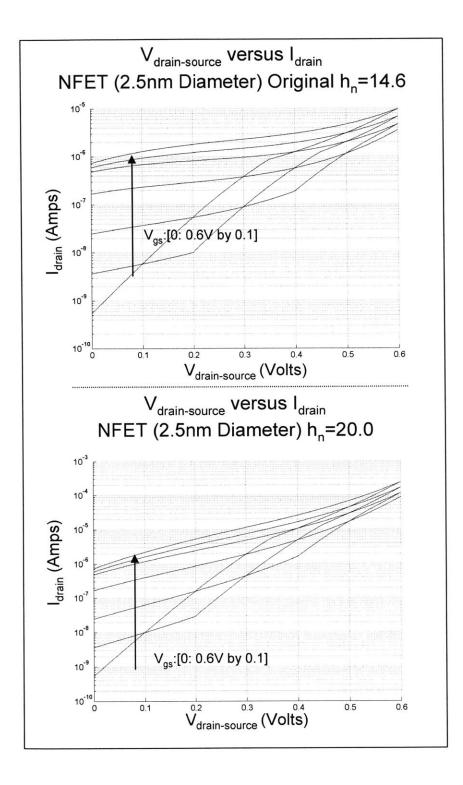

| $I_d$ versus $V_{ds}$ characteristics for a 2.5nm diameter CNT, in a Matlab modeled                       |                                                                                                                                                                                                                              |

| CNTFET. The $h_n$ level changes from the top to the bottom graphs: original,                              |                                                                                                                                                                                                                              |

| $h_n = 14.6$ , to high, $h_n = 20.0$ , levels respectively.                                               | 53                                                                                                                                                                                                                           |

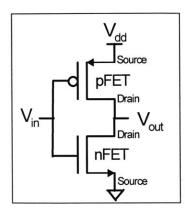

| Inverter structure composed of both an NFET and a PFET transistor                                         | 54                                                                                                                                                                                                                           |

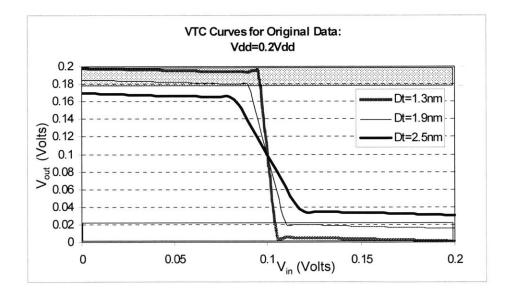

| The voltage transfer characteristics for various diameter CNT transistors. (D_t=                          |                                                                                                                                                                                                                              |

| 1.3nm, 1.9nm, and 2.5nm) The shaded area represents less than $10\% V_{dd}$ and                           |                                                                                                                                                                                                                              |

| more than 90% $V_{dd}$ .                                                                                  | 54                                                                                                                                                                                                                           |

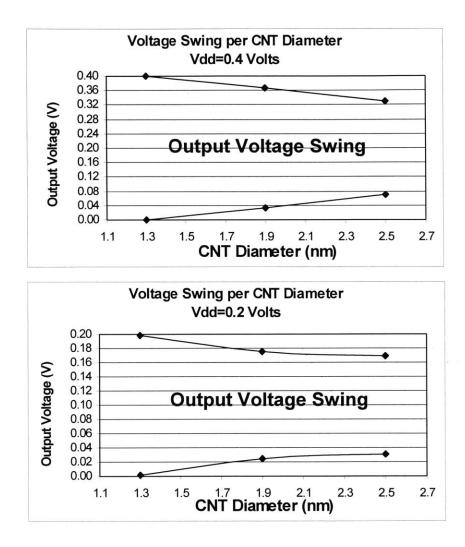

| High and low limits for the output votlage swing of an inverter versus the CNT                            |                                                                                                                                                                                                                              |

| diameter, for Vdd=0.4V                                                                                    | 56                                                                                                                                                                                                                           |

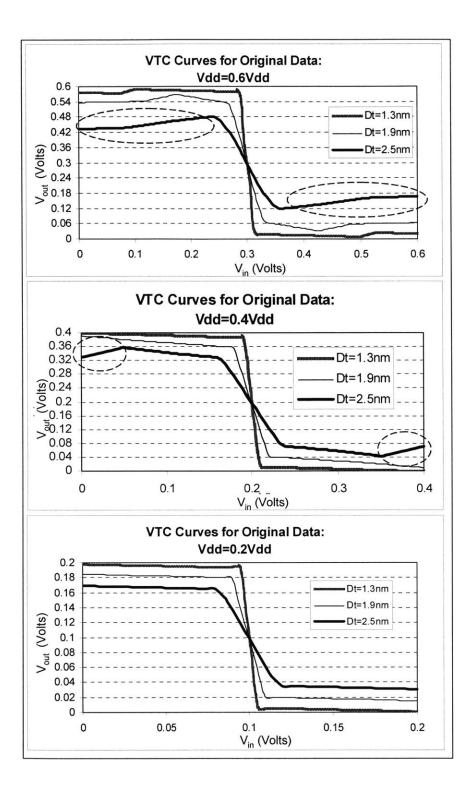

| Model VTC curves at varying supply voltage levels $V_{dd} = [0.6V, 0.4V, 0.2V]$                           |                                                                                                                                                                                                                              |

| As the supply voltage is lowered, CNTFETs continue to keep similar and large                              |                                                                                                                                                                                                                              |

| voltage swing for various diameter tubes. The dotten circles illustrate the output                        |                                                                                                                                                                                                                              |

| voltage swing away from the $V_{dd}$ and ground rails with large diameter nanotubes.                      | 57                                                                                                                                                                                                                           |

| The band diagrams in A represent the maximum output voltage state. The                                    |                                                                                                                                                                                                                              |

| NFET current is at a minimum and, therefore, the output voltage is at a maxi-                             |                                                                                                                                                                                                                              |

| mum. B represents the output voltage when $V_{in}=0V$ ; thus, $V_{out}$ is high, but less                 |                                                                                                                                                                                                                              |

| than $V_{out}$ for case A.                                                                                | 58                                                                                                                                                                                                                           |

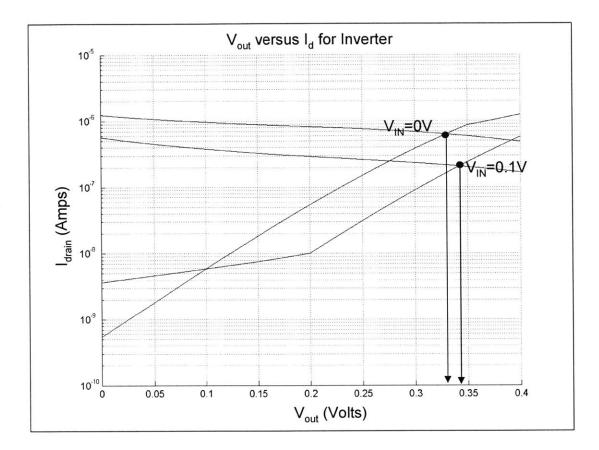

| $V_{out}$ versus $V_{in}$ , for an inverter structure, can be concluded using the load lines              |                                                                                                                                                                                                                              |

| (I <sub>d</sub> versus $V_{out}$ curves). Here, $V_{out}$ is found for $V_{in}=0V$ and $V_{in}=0.1V$ .    | 59                                                                                                                                                                                                                           |

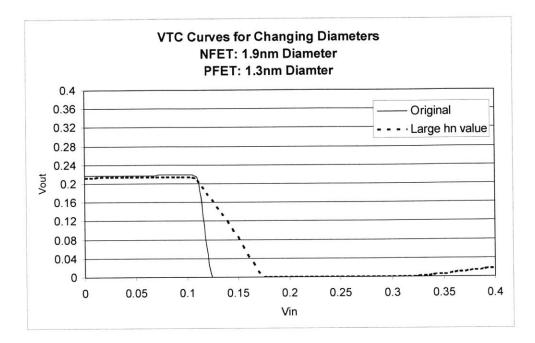

| When the CNT diameter changes between the two transistors in an inverter, the                             |                                                                                                                                                                                                                              |

| inverter will not function properly. Here, the VTC curve illustrates the inability                        |                                                                                                                                                                                                                              |

| of an inverter to pull the output node high                                                               | 60                                                                                                                                                                                                                           |

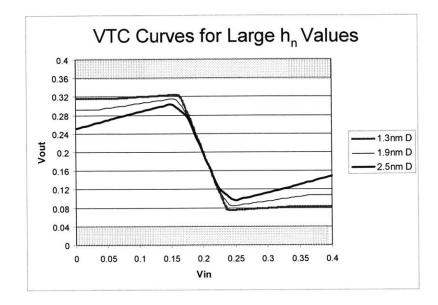

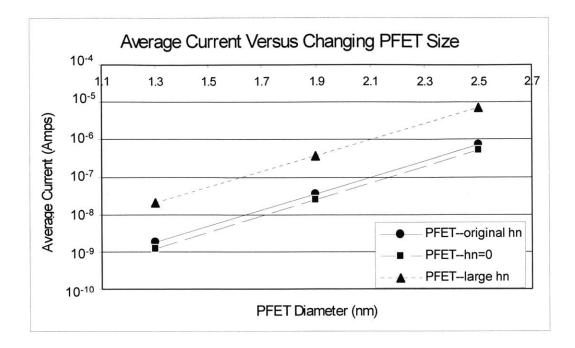

| With the addition of large $h_n$ values, the output voltage swing will not be more                        |                                                                                                                                                                                                                              |

| than $10\%$ to $90\%$ of the supply voltage. The larger the tube diameter, the more                       |                                                                                                                                                                                                                              |

| effect $h_n$ has on the output swing.                                                                     | 62                                                                                                                                                                                                                           |

|                                                                                                           | 1.3nm and a changing drain control versus gate control level, $h_n$ . Low $h_n$ in the top graph, gives little slope to the high $V_{gs}$ lines. With a higher $h_n$ in the second graph, the lines have a much larger slope |

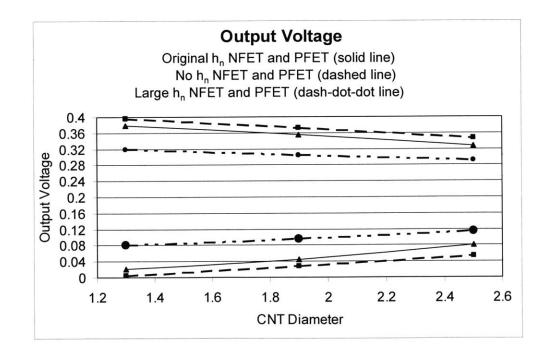

| 3-18 | The output voltage swing varying by drain-control and carbon nanotube diam-                                   |

|------|---------------------------------------------------------------------------------------------------------------|

|      | eter. The more drain-control, the less voltage swing is possible on an inverter's                             |

|      | output voltage                                                                                                |

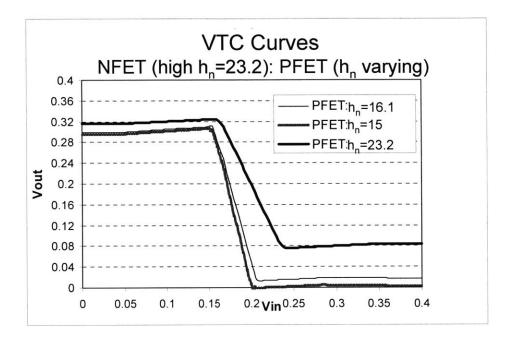

| 3-19 | A VTC curve, illustrating the potential effect of different $h_n$ levels between the                          |

|      | NFET and PFET transistors within an inverter                                                                  |

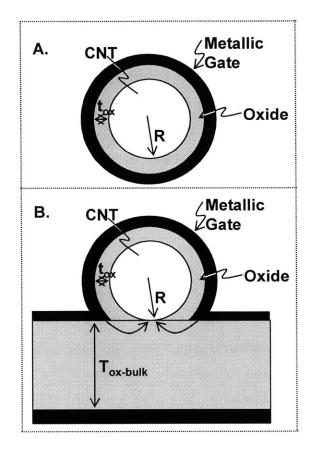

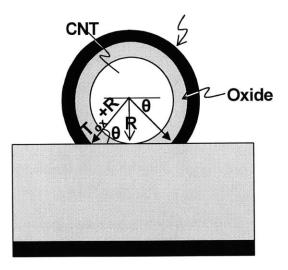

| 4-1  | The capacitance of a CNTFET is modeled as a cylinder with an oxide and cylin-                                 |

|      | drical gate. However, when a CNT is placed on a thick bulk oxide, the capaci-                                 |

|      | tance model must change. B contains fringe capacitance                                                        |

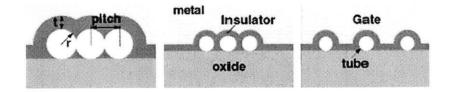

| 4-2  | An illustration of a carbon nanotube arrays with varying pitch. This research                                 |

|      | assumes that the nanotubes are more than $2^*(R+t_{oxide})$ apart, to eliminate ca-                           |

|      | pacitance coupling between devices. From [9]                                                                  |

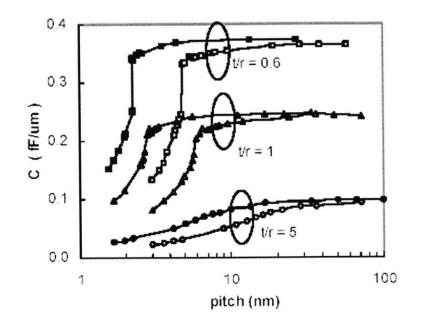

| 4-3  | The $C_{gate}$ (for a nanotube in the middle of an array of parallel tubes) versus                            |

|      | the pitch. The solid symbols represent $r=0.7nm$ and the open symbols are for                                 |

|      | r=1.5nm, where r is the CNT radius and t is the oxide thickness.[9]                                           |

| 4-4  | To model the capacitance of a CNTFET, that is partially covered by a metallic                                 |

|      | top gate, the percentage of the nanotube circumference covered by the gate must                               |

|      | be found.                                                                                                     |

| 4-5  | The table above illustrates the modeled capacitance measurements for this re-                                 |

|      | search compared to those given in citation [9]                                                                |

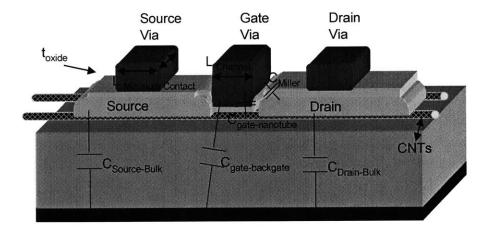

| 4-6  | A CNTFET channel length is dictated by the gate via contact dimensions. The                                   |

|      | drain and source vias are dictated by the same constraints. The $C_{drain-bulk}$ ,                            |

|      | $C_{gate-backgate}$ , $C_{gate-nanotube}$ , $C_{miller}$ , and $C_{source-bulk}$ are shown in the diagram. 69 |

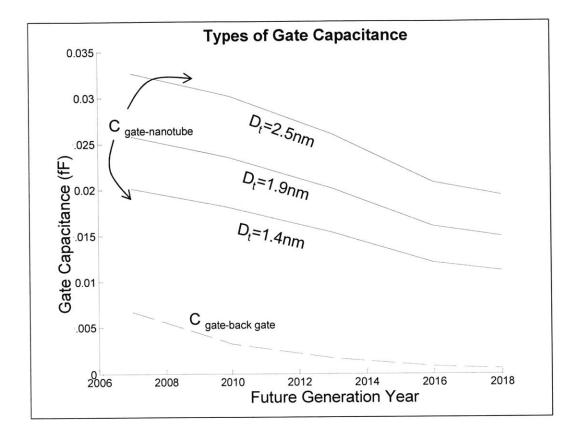

| 4-7  | The gate capacitance consists of both the metal gate to backgate and the metal                                |

|      | gate to nanotube capacitances. The gate to nanotube capacitance depends on                                    |

|      | the nanotube diameter. Here the two types of gate capacitances are graphed                                    |

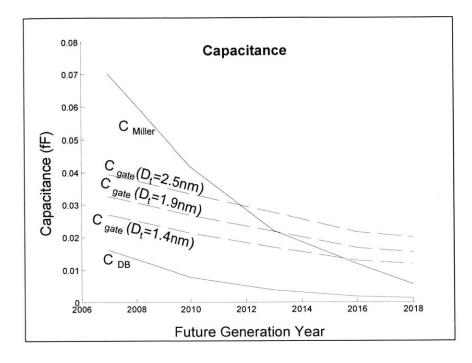

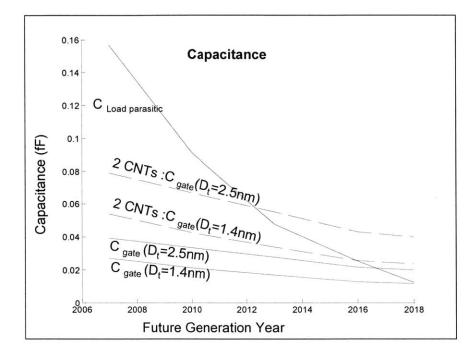

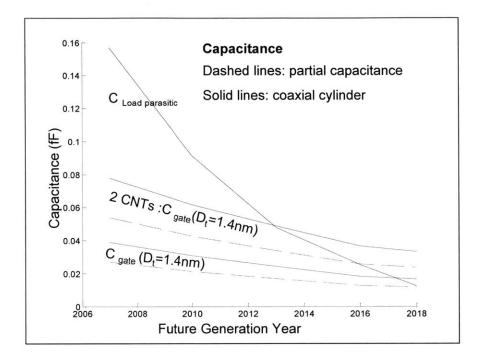

|      | versus the future lithographic generations for multiple nanotube diameters $(D_t)$ .                          |

|      | The backgate oxide thickness is 100nm, compared to the gate oxide thickness                                   |

|      | of [1.1, 0.8, 0.65, 0.55, 0.5] for years [2007, 2010, 2013, 2016, 2018] respectively.                         |

|      | The channel lengths are dependent on the ITRS Roadmap's lithographic speci-                                   |

|      | fications                                                                                                     |

S. .

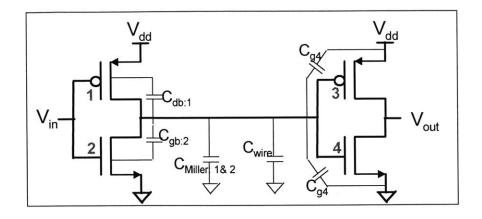

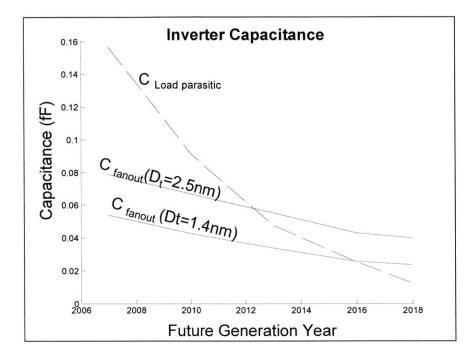

- 4-8 The load capacitance of an inverter chain depends on the Miller capacitance, the wire capacitance, the drain to bulk capacitance of the driving transistors (Transistors: 1 & 2), and the gate capacitances of the driven transistors (Transistors: 3 & 4).

71

- 4-9 As the years increase, the lithographic dimensions are decreasing according to the 2003 ITRS roadmap [10]. The Miller capacitance scales dramatically with lithography because it depends on both the width and the length of the contacts and the gate overlap. The gate capacitance mainly depends on the channel length. The drain to bulk capacitance depends on the metal via scaling. . . . . 72

74

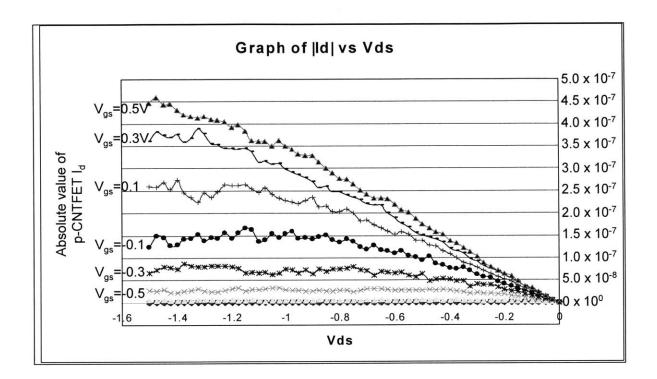

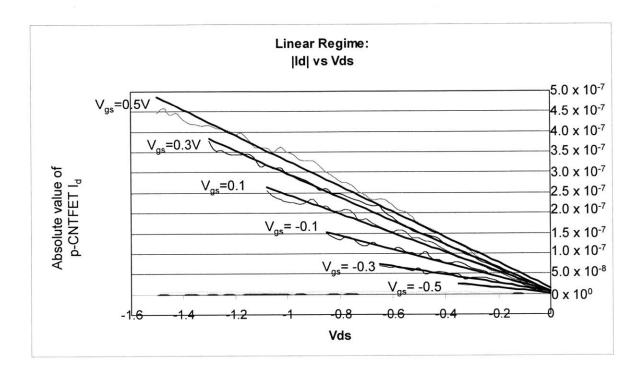

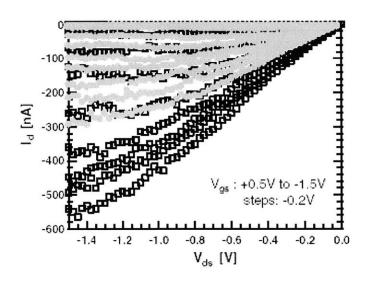

- 5-2 Graph of  $I_d$  versus  $V_{ds}$  for a CNTFET's linear regime, data curtisy of IBM. Placed atop the data are trend lines to show the linearity of the data. . . . . . . 80

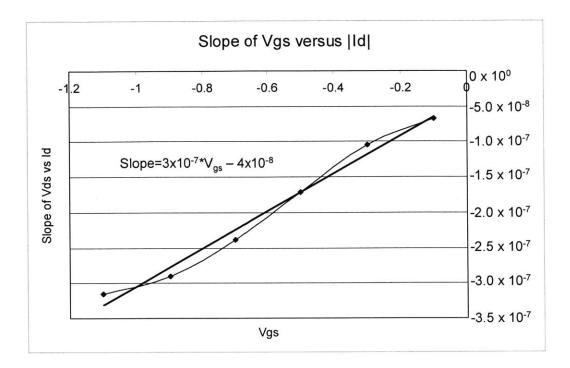

| 5-3        | The slope of the triode regime depends linearly on the gate to source voltage,                                                                                         |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | due to the control of the Schottky Barrier at the source                                                                                                               |

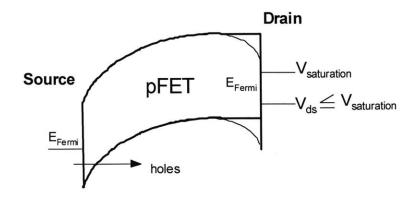

| 5-4        | Illustration dipicting the votlage that leads to saturation for a p-type carbon                                                                                        |

|            | nanotube FET. Saturation occurs when no Schottky barrier exists at the drain. 82                                                                                       |

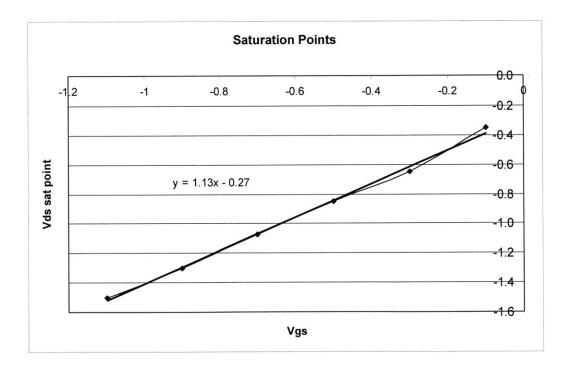

| 5-5        | The saturation voltage occurs linearly with a changing gate voltage 82                                                                                                 |

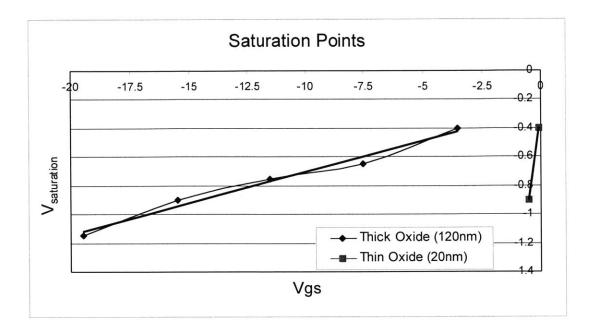

| 5-6        | CNTFETs with thinner gate oxides have more control over the energy band                                                                                                |

|            | diagrams and, thus, tighter control over the irIV characteristics. Thin oxide                                                                                          |

|            | data from [12]                                                                                                                                                         |

| 5-7        | Table depicting the characteristics of CNTFETs in comparison to future MOS-                                                                                            |

|            | FETs                                                                                                                                                                   |

| 5-8        | CNTFET IV characteristics for one nanotube measured in one dirction. The                                                                                               |

|            | CNT was then flipped around and the current was measured again. The varying                                                                                            |

|            | current levels prove that the intrinsic nanotube does not control the current                                                                                          |

|            | voltage characteristics. [5]                                                                                                                                           |

|            |                                                                                                                                                                        |

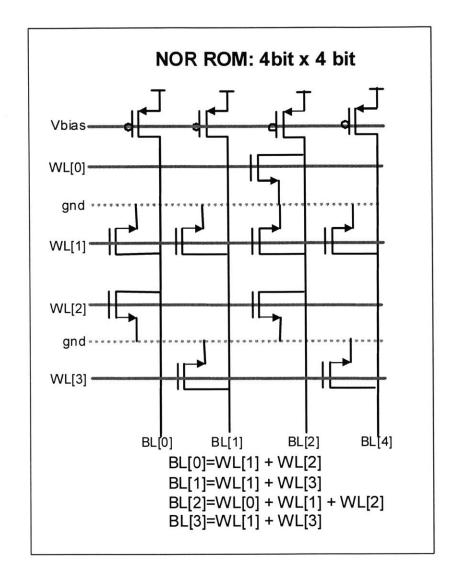

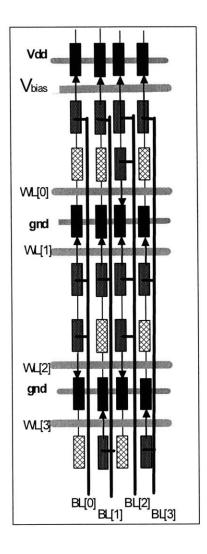

| 6-1        | NOR ROM arrays are created out of parallel NFET transistors from either MOS-                                                                                           |

| 6-1        | NOR ROM arrays are created out of parallel NFET transistors from either MOS-<br>FET or CNTFET technology, sharing a ground contact to save area. The V <sub>bias</sub> |

| 6-1        | FET or CNTFET technology, sharing a ground contact to save area. The $V_{bias}$                                                                                        |

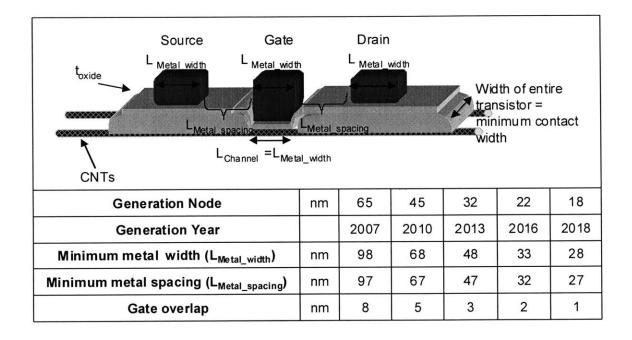

| 6-1<br>6-2 | FET or CNTFET technology, sharing a ground contact to save area. The $V_{bias}$ is an input to p-channel transistors that act as pull-up resistors                     |

|            | FET or CNTFET technology, sharing a ground contact to save area. The $V_{bias}$<br>is an input to p-channel transistors that act as pull-up resistors                  |

|            | FET or CNTFET technology, sharing a ground contact to save area. The $V_{bias}$ is an input to p-channel transistors that act as pull-up resistors                     |

|            | FET or CNTFET technology, sharing a ground contact to save area. The $V_{bias}$<br>is an input to p-channel transistors that act as pull-up resistors                  |

|            | FET or CNTFET technology, sharing a ground contact to save area. The V <sub>bias</sub><br>is an input to p-channel transistors that act as pull-up resistors           |

|            | FET or CNTFET technology, sharing a ground contact to save area. The $V_{bias}$ is an input to p-channel transistors that act as pull-up resistors                     |

|            | FET or CNTFET technology, sharing a ground contact to save area. The V <sub>bias</sub><br>is an input to p-channel transistors that act as pull-up resistors           |

|            | FET or CNTFET technology, sharing a ground contact to save area. The V <sub>bias</sub><br>is an input to p-channel transistors that act as pull-up resistors           |

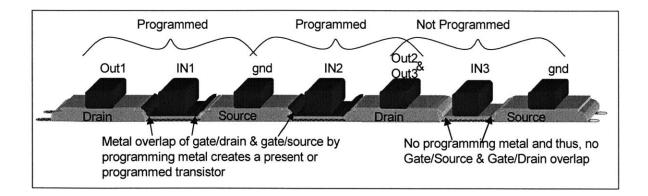

| 6-2<br>6-3 | FET or CNTFET technology, sharing a ground contact to save area. The V <sub>bias</sub><br>is an input to p-channel transistors that act as pull-up resistors           |

| 6-2<br>6-3 | FET or CNTFET technology, sharing a ground contact to save area. The V <sub>bias</sub><br>is an input to p-channel transistors that act as pull-up resistors           |

| 6-2<br>6-3 | FET or CNTFET technology, sharing a ground contact to save area. The V <sub>bias</sub><br>is an input to p-channel transistors that act as pull-up resistors           |

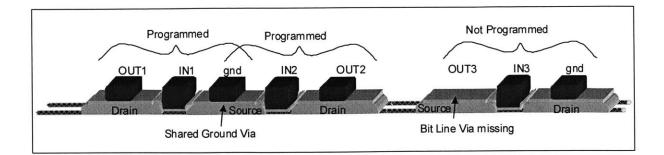

| 6-5  | An overlap is needed by the gate to source and gate to drain-without an over-    |

|------|----------------------------------------------------------------------------------|

|      | lap, a transistor will not work properly. A CNTFET ROM, programmed by            |

|      | the extended channel method, eliminates the need for extra drain contacts by     |

|      | selectively adding gate/drain and gate/souce overlaps to present transistors 93  |

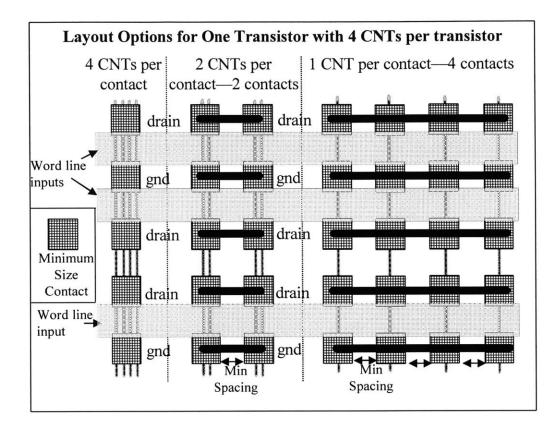

| 6-6  | To increase the current drive of transistors, CNTs can be added in parrallel. To |

|      | save area and contact capactiance, 4 nanotubes can be placed under the same      |

|      | contact. Other layouts include 2 CNTs placed under 2 seperate contacts and       |

|      | the contacts wired together or, each CNT placed under a seperate contact. The    |

|      | contact number and dimensions dictates the area of the array                     |

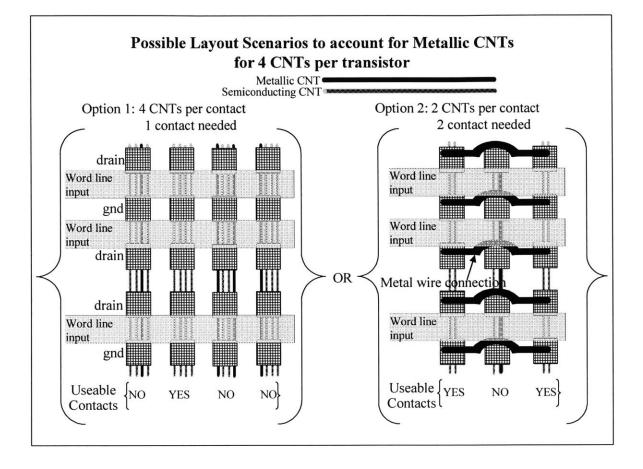

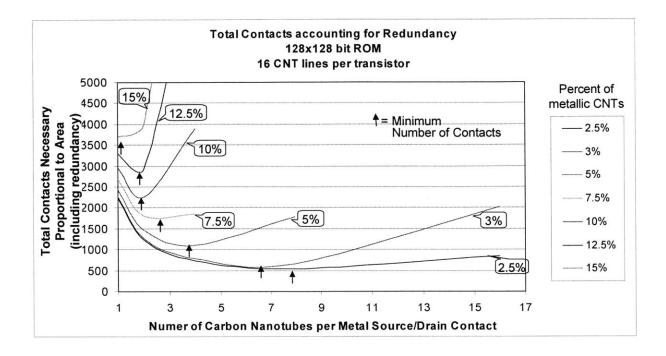

| 6-7  | The area savings associated with multiple nanotubes per contact can be out-      |

|      | weighed by the redundancy associated with metallic nanotubes as shown in the     |

|      | scenario above. Here 4 CNTs per transistor are needed; in this case, it is ben-  |

|      | eficial in terms of area to have few CNTs per contact (Option 2) rather than     |

|      | Option 1 with 4 CNTs per contact                                                 |

| 6-8  | The total number of contacts for a 128bit wide ROM, with 16 parallel CNTs per    |

|      | transistor. The number of CNTs per metal gate is varied on the x-axis and the    |

|      | percent of metallic CNTs is also varied                                          |

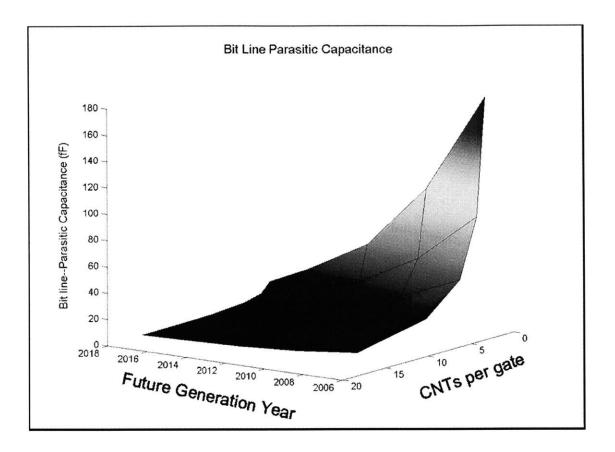

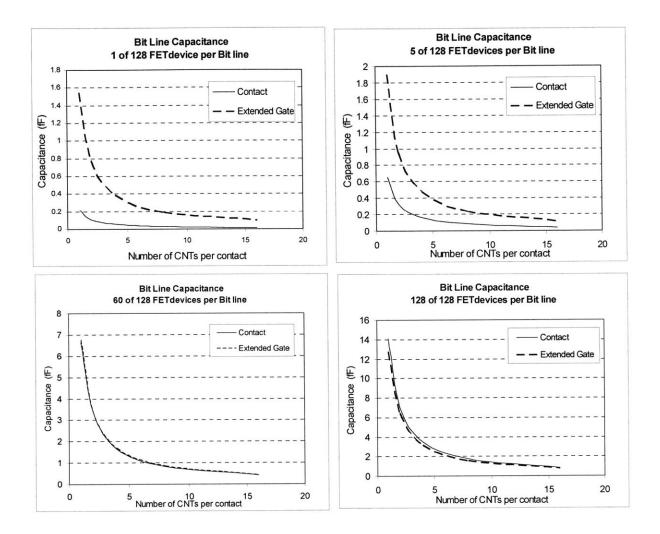

| 6-9  | The parasitic capacitance per bit line drops as the number of output contacts    |

|      | decrease, or the number of CNTs per contact increases. This graph shows the      |

|      | capacitance for a 128x128 ROM, with 16 CNTs per transistor, programmed by        |

|      | drain vias                                                                       |

| 6-10 | A ROM programmed with an extended gate will have a relatively large capac-       |

|      | itance when few FET devices are present per bit line. This is because of the     |

|      | connection to all output contacts. However, as the number of FET devices in-     |

|      | creases per bitline, the shared contacts, used in the extended gate programming  |

|      | method, begin to become advantageous                                             |

|      |                                                                                  |

# Chapter 1

# Carbon Nanotubes Structure, Properties, and Growth

### 1.1 Background

The electronics industry continues to push the limits of Moore's Law. However, the physical restrictions of scaling metal oxide semiconductor field effect transistors (MOSFET) are becoming more prevalent; as these limitations arise, alternative technologies must replace the standard silicon technology. Completely disruptive technologies are being researched and among them carbon nanotubes offer a technology with a unique solution to scaling transistors and interconnects and with the possibility of integration into the well established, current Silicon technology, in the near future.

Since the discovery of carbon nanotubes in 1991, by Sumio Iijima [13], their many extraordinary properties and applications have been researched closely. Carbon nanotubes (CNT) can grow up to millimeters in length; however, their diameters are around 1nm to 40nm. These long thin nanotubes can withstand incredibly high current rates and can be used as both metal wires and channels of field effect transistors (FET). With these impressive properties, CNTs can aid the problem of shrinking electronics.

Figure 1-1: Carbon nanotube cylinders with varying chiralities. (From [1])

### 1.2 Structure of Carbon Nanotubes

Carbon nanotubes have extraordinary properties and applications on account of their unique structure. Carbon nanotubes are quantum wires with diameters ranging from approximately 1nm to 40nm and lengths reaching the millimeter range. [14] Such long thin nanotubes are formed out of flat sheets of hexagonal carbon lattices, called graphene sheets. To lower the large dangling bond energy of these flat graphene sheets, the sheets roll into cylindrical nanotubes. Such nanotubes are energetically favorable; the savings in dangling bond energy outweighs the increased strain energy of the tight cylinders. [15] To eliminate all dangling bonds within the nanotubes, the ends are usually capped with half a fullerene molecule.

#### 1.2.1 Chirality

The particular roll orientation of a carbon nanotube (CNT) is called the chirality, see Figure 1-1 for examples. The chirality determines both the structure and the properties of a nanotube and is described by the chiral vector,  $C_h = n \hat{a}_1 + m \hat{a}_2$ , where n and m are integers in a two dimensional lattice space described by  $\hat{a}_1$  and  $\hat{a}_2$ . [1]

There are three types of rolls: armchair, zigzag, and chiral as shown in Figure 1-1. Armchair nanotubes are formed when n=m, and thus, the angle between the chiral vectors is 30 degrees.

These nanotubes display metal characteristics. Zigzag nanotubes are formed when either n or m is equal to zero, and chiral nanotubes are created from all other angles. If n+m=3j, where j is an integer, the CNT forms a small band gap semiconductor and displays semi-metallic characteristics. The other angles, including zigzag and chiral, form semiconducting CNTs.

The single sheet of graphene, forming a carbon nanotube, limits the number of atomic standing wave vectors and confines electrons to travel along the nanotube axis. The number of possible wave vectors for conduction depends on the diameter of the nanotube. With a larger diameter, there is an increase in carbon atoms around the CNT perimeter and therefore, more atomic wave vectors exist. These extra wave vectors create additional band states, lowering the semiconducting band gap energy. Consequently, the diameter of the nanotube is proportional to  $\frac{1}{Bandgap \ Energy}$ . [1] [15] A nanotube with a lattice vector of (n, m)=(10,10) has a band gap of 0.5-0.65 eV and a diameter of 1.4 nm. With a diameter of approximately 3 nm, the bandgap energy is approximately equal to  $\frac{kT}{q}$  at room temperature.

Theoretically, if the chirality could be controlled during CNT formation, it would be possible to change the properties of a nanotube within the growth process. A metal to semiconducting junction or a junction between two semiconductors of different bandgaps could be made within the same nanotube. In this way, Schottky barriers could be created within a nanotube. This change in band structure along a CNT's length can happen if a carbon pentagon-heptagonal pair is theoretically added as a defect to a nanotube, the addition would change the chirality from (n,m) to (n-1, m+1) or (n+1, m-1). The defect would case a permutation on the nanotube infinitely far away. If this control is available in future electronics, wires, diodes, and FET structures can be created and attached within a carbon nanotube structure, without the need for separate metal contacts. Presently, such control is impossible and only theoretical; this CNT characteristics will not be considered in this thesis.

This research and thesis will compare the characteristics of a nanotube's chirality and diameter to specific electronic applications.

#### 1.2.2 Single Walled versus Multi Walled Carbon Nanotubes

The cylindrical carbon nanotubes described above can grow in two forms: multi walled or single walled. Multi walled carbon nanotubes (MWCNT) consist of concentric CNT cylinders held

Figure 1-2: A multi walled carbon nanotube. (From [2])

within each other by van der Waals forces. The distance between shells is approximately 3.4Å, which is the van der Waals distance for two graphite carbon lattices. [15] An example of a MWCNT is shown in Figure 1-2.

The concentric shells of MWCNTs can differ in their chirality and can consist of both semiconducting and metallic nanotubes. If a MWCNT consists of both semiconducting and metallic cylinders, the metallic shells can negate the possible semiconducting properties. As a consequence, these multi walled carbon nanotubes have limited use in electronics. There is a process by which MWCNT shells can be eliminated, however, the outer shells are eliminated first. The elimination process involves large currents being placed on a MWCNT; a large percentage of the current is transferred down the outermost shell because of its direct contact with the electrode. Shells can withstand approximately  $10^9 \text{ A/cm}^2$ ; however, with a larger current on a MWCNT, there will be a shell by shell failure due to current induced electrical breakdown. This breakdown of the outer shells can be seen in Figure 1-3.

Single walled carbon nanotubes (SWCNT) consist of one graphene cylinder of either a metallic or a semiconducting nature. Because of the single shell, these nanotubes can be classified by their properties related to their tube structure. For the rest of this research and

Figure 1-3: Multi walled carbon nanotubes are shown at the top and single walled carbon nanotubes are bundled in the second picture. (From [3])

thesis, only SWCNTs will be described, since they are a possible basis for future electronics; unless otherwise specified, CNT will mean SWCNT.

### 1.3 Growth Processes

Presently, much of the research involving carbon nanotubes is related to CNT growth and characterization. SWCNTs are difficult to grow. Currently, there are three methods by which to produce mass quantities of single walled nanotubes with a reasonably high yield: arc-discharge, chemical vapor deposition (CVD), and laser ablation. All three processes require a transition metal catalyst, such as Fe, Co, Ni, or Ti, for growth; the size and type of the catalyst, to some extent, controls the properties of a nanotube. However, none of these three processes can completely control the nanotube properties; all produce mixtures of metallic and semiconducting nanotubes with a wide range in CNT lengths and diameters. None of the three methods are ideal for the electronic industry. Below is a short description of the three processes that create carbon nanotubes, with micro to millimeter length scales.

#### **1.3.1** Arc-Discharge

The process of arc-discharge can create large amounts of macroscopic CNTs. [16] In this process, two graphite rods are placed millimeters apart and are attached to a power supply. At the moment the power supply is turned on, a spark vaporizes the carbon into a plasma; when the plasma re-condenses, approximately 30% of it forms nanotubes at catalyst sites. [15] [17] This process creates very defect free structures; however, the process forms large amounts of by-products and the CNTs tend to be both multi walled and single walled, placed randomly in all directions, and the nanotubes are relatively short ( $\leq 50\mu m$ ).

#### **1.3.2** Chemical Vapor Deposition

Endo and Kroto [18] first created CNTs via chemical vapor deposition (CVD); Dai's group has continued to look closely at the CVD process. [19] [20] [21] To create CNTs via CVD, a substrate made of a powder-based transition metal catalyst [20] is placed in a heating chamber at approximately 600°C and hydrocarbon gas, such as methane, is added to the heating chamber. The gas decomposes and frees carbon atoms; these free carbon atoms can recombine at either a catalyst site or at the end of a carbon nanotube to increase the length of the nanotubes, see Figures 1-4 and 1-5.

Dai's group employs this CVD method to control the placement and direction of growth. The gas flow direction and the catalyst placement, by e-beam lithography, are closely monitored to help align nanotubes carefully on the substrate. The CVD method can theoretically produce large quantities of nanotubes at site specific locations. [22] However, this process does have limitations. CVD introduces more defects into the CNTs than arc-discharge. [17] Also, the alignment process still has large placement concerns, and chirality is not fully controlled.

#### 1.3.3 Laser Ablation

CVD and laser ablation are the two main processes used to create CNTs for electronics. Laser ablation was discovered by Smalley's group. [23] A laser pulse is fired at graphite rods that contain a small amount of Co or Ni to help the carbon condense into SWCNTs. This process produces a hot carbon gas which condenses into bundles of 70%-90% single walled carbon nanotubes. [15] By using a particular catalyst, SWCNT can be created with a large percentage

ź.

çer en

Figure 1-4: A diagram illustrating SWCNT growth by chemical vapor deposition. (From [4])

Figure 1-5: Picture of CVD growth from [4]. The bottom bar is a scale of 10 nm in length.

of similar diameter nanotubes. The diameters can be controlled by changing the reaction temperature and the catalyst. Typically the yield of carbon CNTs to total carbon processed is around 70%; however, it is the most expensive of the three processes.

Both the arc-discharge process and the laser ablation process necessitate solid-state carbon precursors and temperatures reaching up to thousands of degrees Celsius.

#### **1.3.4** Growth Processes Variation

Presently, it is very difficult to achieve uniform diameters among nanotubes. Thus, the properties of each nanotube must be discovered after fabrication. The uncertainty of whether a nanotube is metallic or semiconducting creates large problems for circuit application of CNTs and will be considered in the read only memory chapter of this thesis. This research assumes some of these problems will be curtailed in the near future, or at least, the process variations must be controlled before carbon nanotubes can become truly integrated into circuit design applications.

#### **1.4** Electron Mobility Characteristics in Carbon Nanotubes

Single walled carbon nanotubes have large potential for applications in electronics because of both their metallic and semiconducting properties and their capability for high current rates. Electrons and holes have a high current density along the length of a CNT due to the low scattering rates along the CNT axis. This type of structure is similar to an ideal waveguide.

When an electron or hole moves along the axis of a metallic or semiconducting CNT, the scattering rates are negligible. The scattering lengths for a carbon nanotube are on the micro meter length scale, while the relevant electronic distances are in the nanometer range. This is because of the limited number of impurities and defects in a carbon nanotube structure, and the lack of interface problems because of the saturated and stable chemical bonds forming the CNT. Atomic wave vectors create circular standing waves around the core and confine electrons and holes to travel solely in the axial direction. [15] The stable and saturated carbon-carbon bonds also limit electro migration in nanotubes; CNTs can carry current around 10  $\mu$ A/nm<sup>2</sup>, while standard metal wires have a current carrying capability around 10 nA/nm<sup>2</sup>. Thus, carbon

nanotubes have the ideal current carrying capacity: a quintessential mobility and high electro migration thresholds. [15]

## 1.5 Conclusion

Carbon nanotubes offer an intriguing solution to the scaling of silicon electronics. Single walled carbon nanotubes, with their high carrier mobility and their possible metallic or semiconducting properties can be used in many electronic applications, such as the channel of transistors and metal interconnects. This thesis is centered around carbon nanotube applications to field effect transistors (FET). There continue to be many research groups studying CNT current, growth, and structure; however, little at this time has been done related to circuit characteristics and models.

This thesis strives to model semiconducting carbon nanotube FETs to illustrate their potential applications within the electronics industry. Chapter 2 of this thesis models the current voltage (IV) characteristics of a carbon nanotube transistor in the subthreshold or low voltage regime. The current in carbon nanotube FETs (CNTFET) is carefully described because it is due to a completely different physical process than the current within standard silicon devices. To create a full circuit model for these CNTFET devices, the above threshold IV model is described along with the capacitive model used in this research to characterize the energy and delay of CNTFET transistors.

The current models created in this research for CNTFETs are used in circuit structures, such as a voltage inverter and a read only memory (ROM). The trade-offs associated with different diameter carbon nanotubes is discussed in terms of voltage inverters. And, the potential benefits and trade-offs of CNT ROMs are discussed in relation to future generations of lithography and the possibility of metallic CNTs within the ROM. In general, this thesis models, and characterizes semiconducting CNT field effect transistors within digital circuit designs.

# Chapter 2

# **Carbon Nanotubes as Transistors**

The transport of electrons and holes in carbon nanotubes (CNT) has been described in Chapter 1: Carbon Nanotubes Structure, Properties, and Growth. Semiconducting single walled CNT current can be modulated with a voltage and can have similar IV characteristics to a metal oxide semiconducting field effect transistor (MOSFET). Therefore, these s-CNTs can be used in FET devices, but with higher current rates and a possibility for better scaling characteristics compared to Silicon devices.

There are two main types of carbon nanotube FETs differing by their current injection methods: Schottky barrier FETs [5] [6] [8] [24] [25] [26], and doped CNTFETs, [14] [19]. This research only models Schottky Barrier (SB) carbon nanotube FETs.

### 2.1 Schottky Barrier Field Effect Transistors: Fabrication

It has been shown that semiconducting carbon nanotubes can be used as the conducting channel in Schottky barrier carbon nanotube FETs (CNTFET). [5] [6] [8] [24] [25] [26] [27] [28] To create such devices, nanotubes are grown on top of a thick silicon dioxide, which is itself on a silicon wafer. Metal contacts, commonly made of Titanium or Cobalt, are placed over the nanotube to create source and drain contacts. To form a strong interaction between the metal and the nanotube, the metal is annealed at 850°C for approximately 100 seconds to form metal carbides. [29] These high annealing temperatures are acceptable because the carbon nanotube structure can withstand temperatures up to its melting point of around 3,000°C. [15] When multiple

Figure 2-1: Diagram of a top gated CNT transistor structure.

metal contacts are laid along the length of a nanotube, many transistors are formed along the CNT. The length of the nanotube, between two contacts, acts as the channel of a transistor with metal source and drain. Because of the fixed CNT diameter once a nanotube is grown, the width of the nanotube cannot be changed to increase the current drive; instead, a transistor's width and current drive can be increased by adding nanotubes in parallel.

A metal gate, in contrast to a MOSFET's poly Silicon gate, is used to modulate the electronic band structure of the source, drain, and carbon nanotube through a thin gate oxide. The metal gate and oxide must overlap slightly with the source and drain contacts. This overlap limits the area savings of CNTFETs because of the lithographic pitch requirements between the metal gate and the metal source and drain contacts and vias. The current is regulated by the gate to source and gate to drain interactions. Figure 2-1 is a theoretical illustration of a carbon nanotube FET structure. The structure resembles that of a MOSFET, but the nanotube is the channel for conduction. The structure and operation of CNTFETs will be given below.

# 2.2 Schottky Barrier Field Effect Transistors: Operation

#### Background

To understand the operation of a Schottky barrier CNTFET, the energy band diagram for the structure should be studied. At the intersection between the metal carbide contacts and the semiconducting carbon nanotube, Schottky barriers are created. The energy band diagrams in Figure 2-2 illustrate this situation. The current in CNTFETs is from the tunneling of carriers through the Schottky barriers. The type of metal for the contacts is chosen so that its work function forces the metal Fermi Level to lie between the valance and conduction band of the CNT, hopefully lining up approximately in the center of the s-CNT's energy band. The work function for Al is 4.2eV and Ti is 3.9eV; these are similar to the work function of a CNT with a diameter of 1.4nm ( $\approx 4.5 \text{ eV}$ ). [12] Titanium is used most frequently because of its stable carbide. [15] For the strongest nanotube to contact interactions, the contact is best placed at the end of a nanotube, because of possible loose carbon-carbon bonds within the tube structure. However, if many transistors are placed along the length of a nanotube, tube-end contacts are not always possible.

At sufficiently short channel lights, the CNT channel can become ballistic and hence, the metal contact resistance and the Schottky barriers at the source and drain ends limit the current drive through the nanotube. Thus, a low contact resistance, such as that of Titanium, is desirable. Presently, the control of the metal contacts to carbon nanotubes is not consistent and the tunneling current levels between transistors can vary greatly, even on the order of magnitude. This problem must be addressed before mass numbers of CNT circuits can be realized.

#### Operation

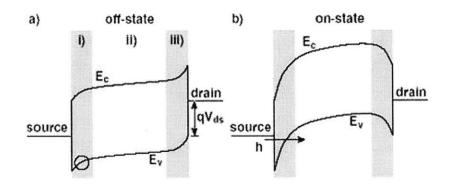

Typically, CNTFETs are pFETs. When a negative voltage is applied between the drain and source, the band structure, of the CNT, is modulated to account for the drain to source voltage  $(V_{ds})$  as shown in Figure 2-2.

When a small negative gate to source voltage is applied, a CNTFET is in the subthreshold regime. With a negative gate voltage applied, the Schottky barrier width at the source is

Figure 2-2: Illustration of band diagrams for a Schottky barrier CNT transistor in the 'off' and 'on' states, respectively. (From [5].)

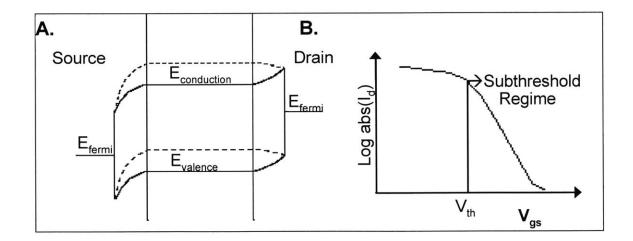

Figure 2-3: Subthreshold band diagrams for Schottky barrier transistors related to the  ${\rm I}_d$  versus  ${\rm V}_{gs}$  graph.

Figure 2-4:  $I_d$  versus  $V_{gs}$  subthreshold characteristics for a p-type transitor, with a channel length of 300nm and a gate oxide thickness  $(t_{ox})$ , HfO<sub>2</sub>, of 20nm. The subthreshold characteristics do not vary largely with  $V_{ds}$  and the subthreshold slope, S, remains relatively constant with temperature. (From [5])

modulated, allowing for holes to tunnel through the valence band and pass unimpeded to the drain. This state is illustrated in of Figure 2-2 b. The thickness of the source Schottky barrier at the metal Fermi level decreases exponentially with an increasing gate to source voltage. Thus, the tunneling current through the Schottky barrier increases exponentially, inversely to the barrier thickness. See Figure 2-3 for the exponential current-voltage (IV) characteristics of the subthreshold regime. The  $I_d$  versus  $V_{gs}$  graphs do not differ greatly with a changing  $V_{ds}$  because the drain voltage does not significantly control the source Schottky barrier. This exponential current relation can be seen in the Figure 2-4.

If the gate voltage increases in the opposite direction, with a positive  $V_{gs}$ , the same effect will occur due to the Schottky Barrier on the opposite side of the s-CNT energy band; however, since the metal Fermi level is further away from the conduction band, a larger gate voltage is needed to achieve similar current levels. See Figure 2-5 to explain how a CNTFET can act as an ambipolar device-both an n-channel and a p-channel transistor depending on the FET voltages. Also, to note about CNTFET devices is, if the metal work function is varied, the

Figure 2-5: Conductance changes as the work function of the drain and source metals are varied to the band gap of the semiconducting CNT. Also, these graphs note how current increases if an opposite gate voltage is applied. (From [6])

graph of the  $I_{ds}$  versus  $V_{gs}$  curves are shifted horizontally on the voltage axis as shown in Figure 2-5.

The transistor threshold voltage, where the device acts similarly to an 'on' MOSFET, is reached when the metal source Fermi level is approximately even with the valence or conduction band of the s-CNT, in a p-channel or n-channel respectively. If the gate voltage continues to increase above this threshold, the Schottky barrier thickness at the source will remain constant and the current will not continue to increase exponentially. Above the threshold voltage, the current will only increase linearly with  $V_{ds}$ . See Figure 2-6 along with Figure 2-7 to show this effect.

Above the CNTFET threshold voltage, the current voltage characteristics look very similar to a MOSFET's IV characteristics; the current increases linearly with  $V_{ds}$ ; and, when the barrier at the drain is completely eliminated, the FET current saturates. A saturated SB-CNTFETs has very little slope on the  $I_d$  versus  $V_{ds}$  graph, unlike short channel MOSFETs.

The start of the saturation regime is dependent on the gate to source and the drain to source voltages. By studying the energy bands shown in Figure 2-6, it can be seen that the band modulation from  $V_{ds}$  has to be greater or equal to the band modulation due to  $V_{gs}$  for CNTFETs that use Titanium for the source, drain, and gate. In most electronic applications,

Figure 2-6: Band diagrams for a Schottky barrier transistor in the triode regime and at the saturation point.

Figure 2-7: This figure follows the drain voltages shown in Figure 2-6. Drain-1 & 2: Linear Regime, Drain-3: Saturation point

Figure 2-8: Energy band bending of a CNTFET is larger with a thinner gate oxide. (From [7])

the gate to source voltage does not surpass the drain to source voltage. Thus, CNTFETs will be in the linear (triode) or the subthreshold regime and will not enter saturation.

In Schottky barrier devices, it is beneficial to have the gate voltage modulate the tunneling barrier at the source end as strongly as possible. To achieve this, the gate-channel capacitance must be very high (at the moment SiO<sub>2</sub> oxides range in thickness around 1-10nm and high  $\kappa$ dielectrics, such as ZrO<sub>2</sub>, have been used to lower this capacitance [21]), see Figure 2-8. Many types of dielectrics can be used in carbon nanotube FETs. All carbon-carbon bonds are satisfied in carbon nanotubes and as a consequence, they have no interface states associated with oxides.

In this research, IBM data is used to model the current in CNTFETs. The model will be described in the following chapters of this thesis.

### 2.3 Carbon Nanotube Transistor Width

If large current rates are needed in CNTFETs, the nanotube diameters cannot be increased. To increase the transistor width, nanotubes can be added in parallel under a shared metallic gate, see Figure 2-1. Thus, the width of a CNTFET can not be increased linearly, but rather the width is quantized by the number of nanotubes in parallel.

Multiple nanotubes can be placed in close proximity, sharing the same metallic gate; however, the nanotubes cannot be placed directly next to or on top of each other. The gate capacitance limits the proximity of these parallel nanotubes. If carbon nanotubes are placed too close to each other, capacitive screening of the gate, from neighboring CNTs, will become a problem. [26] More capacitance related issues will be discussed in Chapter 4: Capacitance, Energy, and Delay of Subthreshold CNTFETs.

### 2.4 P-Channel versus N-Channel Schottky barrier CNTFETs

It was mentioned previously that CNTFET current is a result of hole or electron tunneling through the source and drain contact Schottky barriers, depending on the gate and drain voltages. In all of the band diagrams previously described, the current is the product of holes tunneling through the Schottky barrier on the valance band. However, if the gate and source are given large positive voltages, electrons will begin to tunnel through the Schottky barrier at the conduction band edge, to create an n-channel transistor. Thus, a CNTFET can act as both an n-channel and a p-channel transistor depending on the voltages; this type of device is called an ambipolar transistor.

Theoretically, if the work function of the source metal were aligned directly with the middle of the s-CNT, the current would be perfectly symmetrical for holes and electrons around a certain gate to source and gate to drain voltage. As the voltages increase, in either direction, the FET will act as either a p-channel transistor or an n-channel transistor with equal, but opposite characteristics. This is because short CNTs have ballistic current and therefore, the mobility for holes and electrons is essentially the same. This fact must be taken into consideration when sizing transistors: the standard MOSFET assumption, that PMOS transistors must be 2-3 times as wide in as NMOS transistors, is not applicable in this case. CNT n-channel and p-channel transistors will be sized symmetrically. This fact will help in complementary logic style circuit designs.

If the source Fermi level lines-up closer to the CNT valence band, a carbon nanotube

transistor will have better p-type characteristics. Changing the relation of the metal  $E_{fermi}$  to the s-CNT band gap effects the thickness of the Schottky barrier and therefore, influences the tunneling rate of holes or electrons and changes the current characteristics. At first glance, if the work function of the metal were changed to line-up with the valence band of the CNT, one would assume a perfect ohmic contact and an ideal p-channel transistor. However, a Schottky barrier is created at the junction independent of the metal work function. [7]

The CNTFETs created by IBM have better p-channel characteristics because of the work function of Ti in relation to the CNT energy band. However, better n-channel characteristics can be achieved by shifting the line-up of the source Fermi level with the CNT band gap. This shifting can happen through either an annealing or a doping process. Below is a short description of these two processes.

#### 2.4.1 Annealing

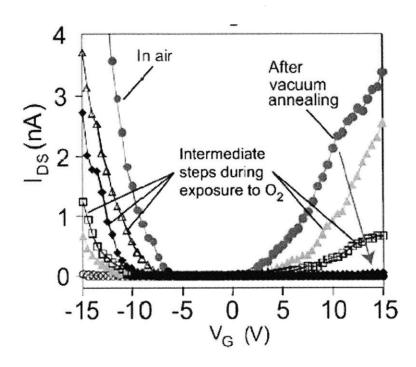

If CNT transistors, with better PFET characteristics (p-channel transistors), are vacuum annealed, they can be converted to better n-channel CNTFETs. In the annealing process, absorbed oxygen is driven out of the contact region; this process shifts the metal Fermi level up in relation to the CNT band gap and thus, lowers the Schottky barrier at the conduction band edge. In turn, the electron tunneling current increases and the device has better n-channel characteristics. Graphically, the annealing process moves the  $I_{ds}$ - $V_{gs}$  curve toward more negative gate voltages; however, it does not change the shape of the curve; see Figure 2-9. Physically, annealing removes the oxygen from the contact, which changes the surface potential of the metal contacts to the CNT band gap. This process is reversible; if the CNT is exposed to air, the original IV characteristics will return.

#### 2.4.2 Doping with Alkali Metals

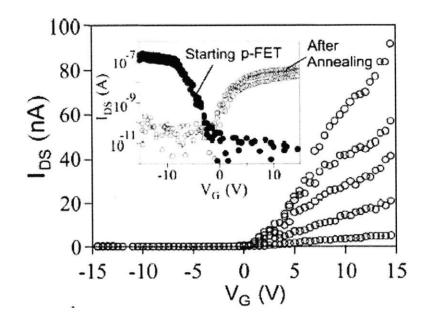

Doping nanotubes with an alkali metal, such as potassium, has the same result as the annealing process; transistors can be made to have better p- or n-channel properties by graphically shifting the IV characteristics of a Schottky barrier transistor. Physically, potassium can be used to adjust the s-CNT bandgap in relation to the source and drain metal Fermi levels. Doping does not lead to intrinsic CNTs, instead doping shifts the current versus gate voltage curves, as can

Figure 2-9: CNTFET IV characteristics, depending on oxidation of the CNT to metal interface. (From [7])

Figure 2-10: Shifting of  $I_d$  versus  $V_{gs}$  curves, with a varying amounts of potassium. (From [6]) be seen from the graphs in Figures 2-10 and 2-11.

#### 2.4.3 Conclusion

Ambipolar Schottky barrier CNTFETs can be used as both p-channel and n-channel FETs depending on the relative drain, gate and source voltages. If the transistors are doped or annealed, their IV characteristics can be shifted towards better p-type or n-type transistors. This shift can be used to the advantage of a circuit designer if there are precise process controls.

# 2.5 CNTFET Scaling

The carbon nanotube transistor devices described in this chapter are similar in structure and IV characteristics to MOSFETs, however, they have certain properties that make them viable candidates for future technologies. CNTFETs have ballistic transport, ambipolar voltage characteristics, and increased scaling ability. MOSFETs scale in dimension to increase speed and density and to lower power. However, fundamental scaling limits are going to constrain future Silicon devices. Currently increased device performance and lower power are achieved by scaling all dimensions and characteristics by  $\alpha > 1$ . The following describes the generalized scaling methodology for MOSFETs.

Figure 2-11: Conversion between P and N type CNTFETs, using an annealing process in vacuum. (From [8])

| Dimensions       | $\frac{t_{oxide}}{\alpha}, \frac{Channel\_Length}{\alpha}, \frac{Vertical}{\alpha}$ | $\frac{Dimensions}{\alpha}$ , | $\frac{Width}{\alpha}$ |

|------------------|-------------------------------------------------------------------------------------|-------------------------------|------------------------|

| Substrate Doping | $lpha * N_A$                                                                        |                               |                        |

| Lower Voltage    | $Vdd \Downarrow$                                                                    |                               |                        |

| Higher Density   | $\alpha^2$                                                                          |                               |                        |

| Higher Speed     | $\alpha$                                                                            |                               |                        |

| Power Density    | constant                                                                            | with each                     | futuro                 |

MOSFET scaling is causing more severe problems with each future generation. Carbon nanotube transistors are immune from some of the same scaling constraints. The current levels in a CNTFET do not depend on the channel length. Thus, in comparison to MOSFETs, there is no channel length minimization or subsequent substrate doping problems. Also, in MOSFETs, the gate oxide thickness has already entered the nanometer range; channel scattering from the rough oxide interface and tunneling through the thin oxide are becoming prevalent problems. Carbon nanotube transistors do not have these difficulties; all chemical bonds are satisfied in a CNT and thus, there are fewer oxide to channel interface problems. A multitude of oxides can be placed on the nanotubes and thus, many high- $\kappa$  dielectrics can be incorporated into CNTFETs to reduce the tunneling currents. And, the nanotube, in essence, protects the conducting channel form any interface problems; ballistic transport can continue in a CNT independent of the oxide.

# 2.6 Conclusion

In conclusion, complementary transistors can be created along the length of a carbon nanotube. And thus, intermolecular devices are possible. Certain aspects of these CNTFETs make them strong candidates for future electronics. Carbon nanotube FET devices do not have problems with short channel effects, there is no electro migration, the breakdown is very high. And, the NFET and PFET devices are symmetrical, which is ideal for CMOS structures. These characteristics leave CNTFETs as a viable option for future technology generations.

# Chapter 3

# Subthreshold Carbon Nanotube Field Effect Transistors

The portable electronics industry has expanded dramatically in the recent years. With this increase, there has been a focus on lower power applications. Future technologies, such as carbon nanotube transistors must accommodate and follow these low power trends.

Scaling down the supply voltage of electronics decreases the power quadratically. Weak inversion or subthreshold circuit operation allows the ultimate in voltage supply scaling; the supply voltage is lower than the threshold voltage of a transistor; thus, the transistor 'on' to 'off' current ratio is small. Such logic MOSFET subthreshold circuits have been tested functional down to approximately 180mV. [30] The threshold voltage of carbon nanotube transistors will scale down when the gate oxide and the gate work function decrease or the CNT diameter is increased. The CNT diameter is not linked with technology scaling. Therefore, the threshold voltage will probably not scale as fast as the supply voltages and CNTFETs will have to operate in the low voltage, subthreshold regime. It is also important to research CNTFETs in the subthreshold regime because of their future operation at low voltages and the disparity in CNTFET low voltage characteristics from MOSFET subthreshold IV characteristics. Because of this difference, this chapter will look closely at the subthreshold characteristics of CNTFETs.

An important metric in subthreshold design is the ratio of on-current to off-current  $(I_{on}:I_{off})$ . This ratio characterizes the difference in current between a closed and open switch, or a transistor with an 'on' voltage versus 'off' voltage on the control gate. A large ratio of leakage currents,  $I_{on}:I_{off}$ , will give functionality in digital logic design. Carbon nanotubes have a varying  $I_{on}:I_{off}$  ratio, depending on the nanotube structure and properties.

Many low power applications, such as hearing aids, trade performance for power savings; the 'off' current is a crucial factor in lowering the power. The 'on' or high current is still an important metric in subthreshold design. Carbon nanotubes have very high current because of their ballistic transport and their limited electron and hole scattering. Therefore, CNTs have the ability to increase performance while adhering to lower power requirements in subthreshold circuits.

The  $I_{on}$  in MOSFETs decreases exponentially as the supply voltage is lowered; the same is true in carbon nanotube transistors. However, compared to MOSFETs, the off-current in CNTFETs continues to decrease as the voltage across the FET from drain to source decreases. Thus, as the supply voltage is lowered in CNTFETs, the ratio of  $I_{on}:I_{off}$  can remain large for certain circuits.

This research will model, using Matlab, CNT Schottky barrier (SB) transistors in the low voltage, subthreshold regime from data given by Appenzeller at TJ Watson Research Center, IBM. The Matlab model will be used to determine the functionality of future subthreshold CNTFETs in digital design, accounting for changing nanotube properties and process variations.

# 3.1 Subthreshold CNTFET Current

CNTFETs can act as ambipolar transistors, however, the IBM data given are for CNTFETs acting as n-channel transistors. In this research, an assumption is made that a carbon nanotube transistor has symmetric current drives for holes and electrons around a minimum current. Also, as was previously described, the source and drain Fermi levels can be moved in relation to the CNT band gap. With this fact, n-channel and p-channel IV characteristics can be equal for the absolute value of the applied voltages,  $|V_{drain-source}|$  ( $|V_{ds}|$ ) and  $|V_{gate-source}|$  ( $|V_{gs}|$ ). This result is based on the physical understanding that carbon nanotube channels conduct ballistically at the length ranges in question and, as a result, both electrons and holes have the same velocity. This means that p-channel or n-channel transistors can have the same current

levels when their widths and process variations are equal and the  $V_{gs}$  and  $V_{ds}$  are equal and of opposite sign.

# 3.1.1 Current versus V<sub>Gate-Source</sub> Characteristics

It was described in Chapter 2 that the subthreshold current of a CNTFET increases exponentially as the thickness of the Schottky barrier at the source decreases. In this section, the  $I_d$ versus  $V_{gate-source}$  characteristics will be discussed and modeled.

#### Minimum Current