Solder Self-Assembly for MEMS Fabrication

by

Hin Meng Au

B.S., Mechanical Engineering (2001) University of Michigan, Ann Arbor

Submitted to the Department of Mechanical Engineering in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Mechanical Engineering

at the

Massachusetts Institute of Technology

September 2004

© 2004 Massachusetts Institute of Technology All Rights Reserved

.

**^** .

August 6, 2004

Certified by..... Carol Livermore Assistant Professor of Mechanical Engineering Thesis Supervisor Ain A. Sonin Chairman, Department Committee on Graduate Students

| MAS | SSACHUSETTS INSTITUTE<br>OF TECHNOLOGY |

|-----|----------------------------------------|

|     | MAY 0 5 2005                           |

|     | RRARIES                                |

BARKER

#### Solder Self-Assembly for MEMS Fabrication

by

#### Hin Meng Au

Submitted to the Department of Mechanical Engineering on August 6, 2004 in Partial Fulfillment of the Requirements for the Degree of Master of Science in Mechanical Engineering

#### ABSTRACT

This thesis examines and demonstrates self-assembly of MEMS components on the 25 micron scale onto substrates using the capillary force of solder. This is an order of magnitude smaller than current solder self-assembly in the literature. This thesis also examines self-assembly of high aspect ratio (2:1) microfabricated structures, which poses a greater challenge in terms of alignment and orientation compared to self-assembly of flat structures. The goal of the assembly is to construct a DEP-based cell trap, which consists of sets of high aspect ratio conducting posts on a pyrex substrate, along with electrical connections to the posts.

The posts and substrates are fabricated separately and then combined together through a self-assembly process. The posts are made of silicon and are 25  $\mu$ m in diameter and 50  $\mu$ m tall with a thin gold cap on one end to serve as a wetting site. The substrates are pyrex wafers which are patterned with arrays of binding sites and electrical connections, and selectively coated with a low melting point bismuth solder alloy on the binding sites. Self-assembly of the posts onto the substrate is then driven by the free surface energy minimization of solder when the gold-capped ends of the silicon posts come into contact with the solder bumps.

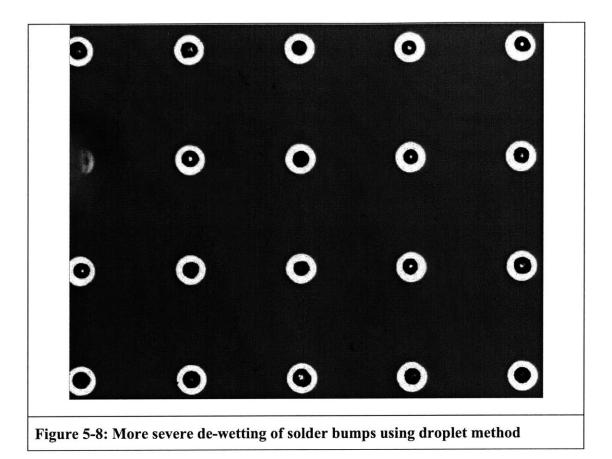

In this project, self-assembly has been successfully demonstrated with a yield of about 50%. However, it also becomes increasingly difficult to control component placement and orientation at these small size scales, because deviations in components and sites from their ideal geometries become relatively pronounced as feature size is reduced. It is observed that post concentration, agitation, and solder wetting of the substrate and posts binding sites are critical for successful assembly. Solder de-wetting, and the peeling of gold caps due to prolonged HF exposure, also limits the yield and the orientation of the assembled posts.

Thesis Supervisor: Carol Livermore Title: Assistant Professor of Mechanical Engineering

# Acknowledgements

First and foremost, I would like to extend my deepest gratitude to Professor Carol Livermore for giving me the opportunity to work on this project, and for her immense patience, guidance, and time over these past two years. I cannot thank her enough for always keeping a personal stake and upholding a keen interest in the projects and the students' welfare, for her enthusiasm in visiting the lab or fab to discuss results and observations, and for her willingness to trudge through problems together to gain deeper insights or to develop a solution. I deeply appreciate her as a teacher and mentor, and I look up to her for her intellect and sharp observation skills, as well as her positive approach in tackling problems. I have learnt a lot during this time, and I am especially indebted to her for imbuing in me the power of experimentation and observation, which I will carry and develop further on my lifelong journey of learning.

My most sincere thanks go out to the staff at the Microsystems Technologies Laboratories (MTL), especially Kurt Broderick and Paul Tierney, for their responsiveness and eagerness to help when and wherever possible. I would also like to thank Luis Fernando and Dennis Ward for their invaluable advice on microfabrication processing and recipes. I owe my present fab skills and working knowledge to all these people, Prof Carol Livermore, and many more who have so willingly shared their potpourri of microfabrication experiences.

I would also like to thank Sunghwan for being such a wonderful group-mate all this while. I admire him for his intellect, and I will always relish the myriad diverse and wonderful conversations we have had.

I am also very grateful to my dear friends at MIT for their support and encouragement throughout my time here. Without this bunch of close-knitted Singaporean friends, life at MIT would only have been half the experience. Special mention goes out to Leonard, Ziliang (for his help too in the PDMS), Mindy, Trevor, Bala, Poh, and Tony for their friendship and camaraderie, and to Yinthai for the intellectually stimulating conversations on science.

Last but not least, I would like to thank my parents, Cheong Choy Lin and Au Kok Wing, for putting me through school and for their unbounded love, support and encouragement all these years. Also, I would like to express my heartfelt gratitude to my grandmother Ho Seong, and my aunt and uncle-in-law, Au Oi Sung and Tan Ngak Liang; without their kindness and support, I would not have had the opportunity to pursue an overseas education.

# Contents

| Abstract  |                                 |

|-----------|---------------------------------|

| Acknowle  | edgements3                      |

| Contents  |                                 |

| Figures   |                                 |

| Tables    |                                 |

| Chapter 1 | Introduction10                  |

| 1.1       | Background 10                   |

| 1.2       | Extruded DEP cell trap 12       |

| 1.3       | Fabrication issues              |

| 1.4       | Self-assembly15                 |

| Chapter 2 | 2 Design 17                     |

| 2.1       | System requirements 17          |

| 2.2       | Design of cell trap 17          |

| Chapter 3 | Device fabrication              |

| 3.1       | Design of fabrication processes |

| 3.1.1     | Silicon posts fabrication       |

| 3.1.2     | 2 Substrate fabrication 46      |

| 3.2       | Fabrication issues              |

| Chapter 4 | Solder Technology               |

| 4.1       | Solder alloy                    |

| 4.1.1     | Solderability                   |

| 4.2      | Wetting of surfaces                     | 57 |

|----------|-----------------------------------------|----|

| 4.2.     | 2.1 Surface tension                     | 58 |

| 4.2.     | 2.2 Need for flux                       | 62 |

| 4.2.     | Degrees of wetting                      | 62 |

| 4.3      | Coating of solder on substrate          | 64 |

| 4.3.     | Fabrication change (addition of copper) | 69 |

| Chapter  | 5 Testing and Characterization          | 75 |

| 5.1      | Assembling the posts                    | 75 |

| Chapter  | 6 Summary                               | 96 |

| 6.1      | Summary and conclusions                 |    |

| 6.2      | Future work                             | 97 |

| Referenc | ıces                                    |    |

# **List of Figures**

| Figure 1-1: Self-assembly (using solder) demonstrated by the Whitesides' group [2] 11                                                         | 1 |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---|

| Figure 1-2: Self-assembly (using self-assembled monolayers and a heat-curable acrylate-<br>based adhesive) demonstrated by the Howe group [3] |   |

| Figure 1-3: Dielectrophoresis and the creation of a potential energy well at the center of the quadrupole due to a non-uniform AC field [4]   | 3 |

| Figure 1-4: Fabrication process for the extruded DEP-based cell trap [4] 13                                                                   | 3 |

| Figure 1-5: SU-8 shrinkage in PGMEA causing cracks [4]15                                                                                      | 5 |

| Figure 1-6: Prof Voldman's extruded DEP-based cell trap [4] 15                                                                                | 5 |

| Figure 1-7: Schematic of how the solder self-assembly for the posts works                                                                     | 5 |

| Figure 2-1: Schematic of how the solder self-assembly for the posts works                                                                     | 3 |

| Figure 2-2: Clear-field mask (zoom-in view) for fabricating the interconnect lines on the substrate                                           |   |

| Figure 2-3: Dark-field mask (zoom-in view) for fabricating the contact pads (binding sites) on the substrate                                  | 2 |

| Figure 2-4: Schematic of how the substrate should look like at the end of the fabrication                                                     | 2 |

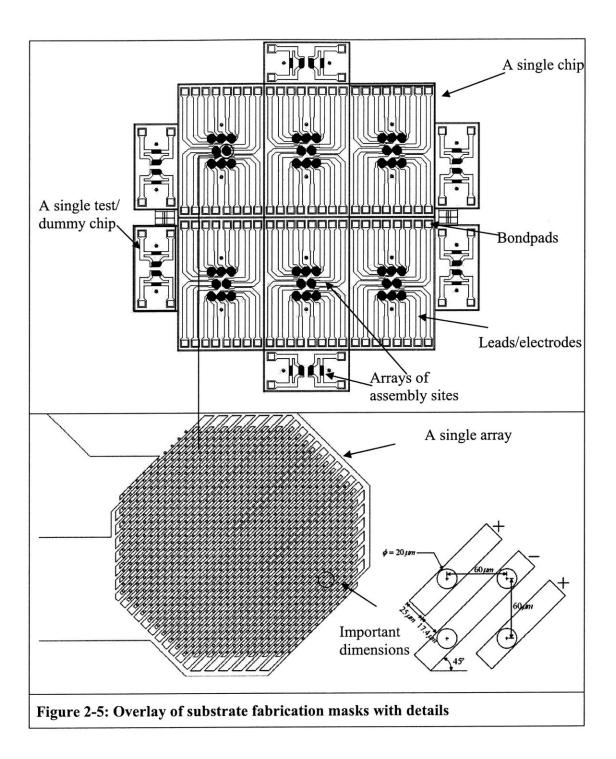

| Figure 2-5: Overlay of substrate fabrication masks with details                                                                               | 3 |

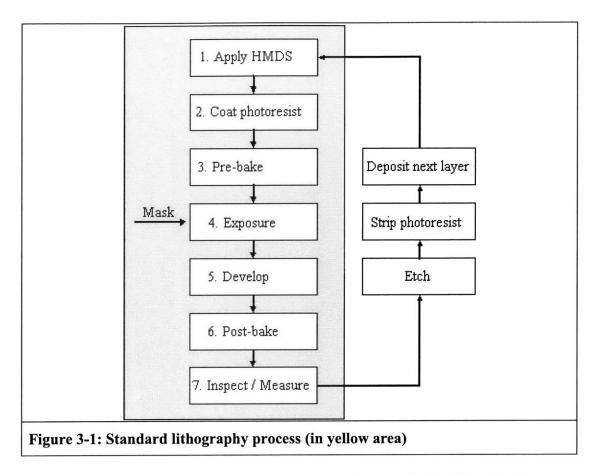

| Figure 3-1: Standard lithography process (in yellow area)                                                                                     | 5 |

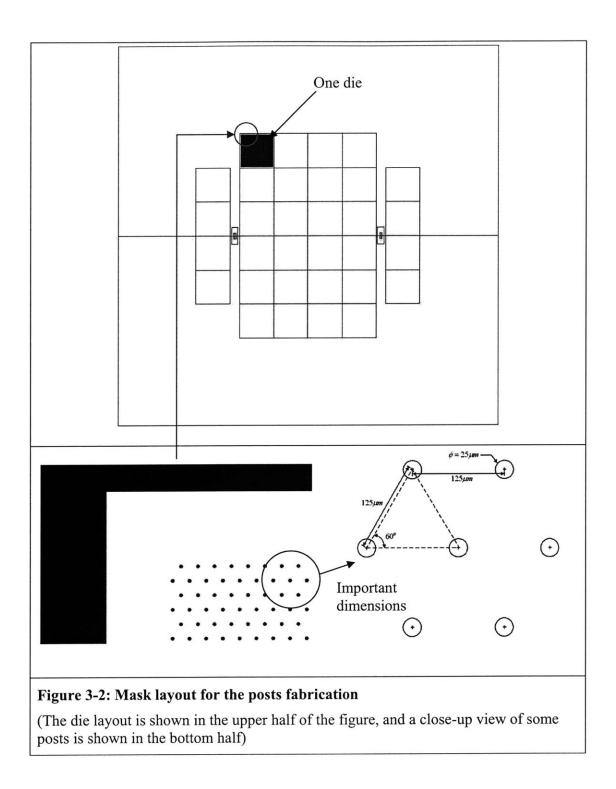

| Figure 3-2: Mask layout for the posts fabrication                                                                                             | 7 |

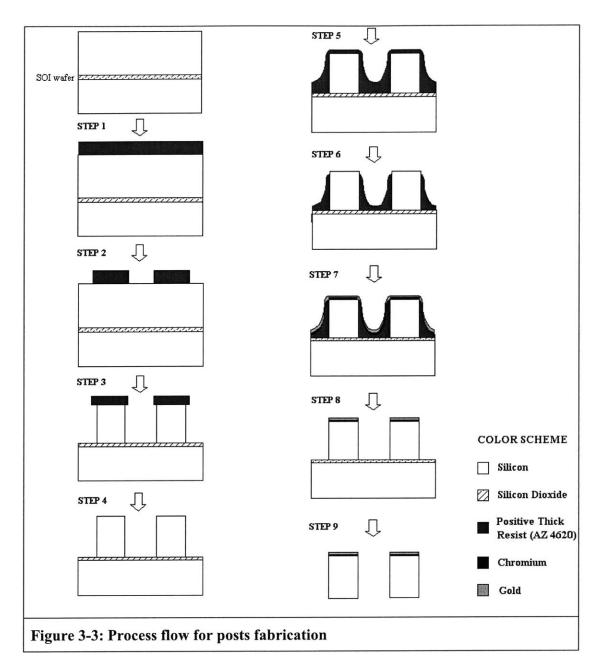

| Figure 3-3: Process flow for posts fabrication                                                                                                | 3 |

| Figure 3-4: Schematic diagram of an STS inductively coupled etch system used for ASE <sup>TM</sup>                                            | 1 |

| Figure 3-5: Base profile of etched silicon posts on a dummy Si wafer                                                                          | 4 |

| Figure 3-6: Base profile of an etched silicon post on an SOI wafer                                                                            | 5 |

| Figure 3-7: Honeycomb-like pattern field                                                                    | . 37 |

|-------------------------------------------------------------------------------------------------------------|------|

| Figure 3-8: Tops of silicon posts showing uncleared resist (left) and clear of resist (rig                  |      |

| Figure 3-9: Silicon posts with Cr/Au caps after lift-off process                                            |      |

| Figure 3-10: Cr/Au cap on top of the silicon post                                                           | 40   |

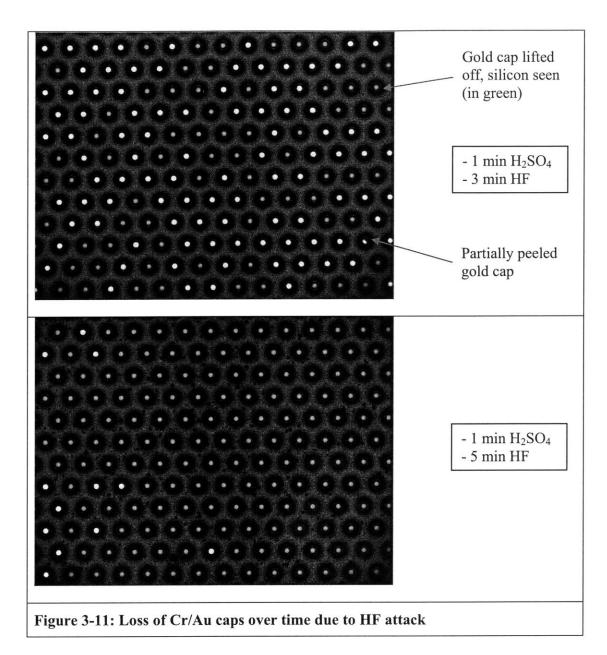

| Figure 3-11: Loss of Cr/Au caps over time due to HF attack                                                  | . 42 |

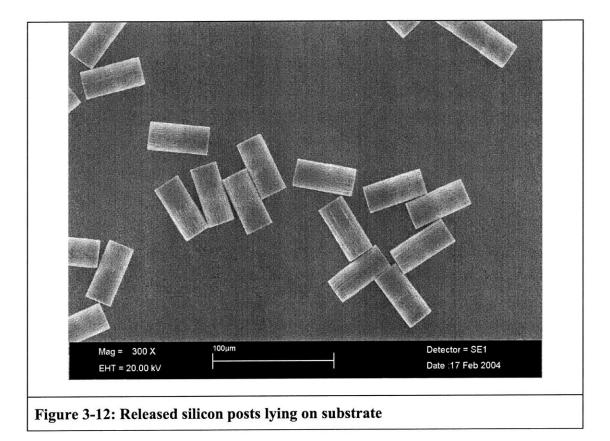

| Figure 3-12: Released silicon posts lying on substrate                                                      | . 44 |

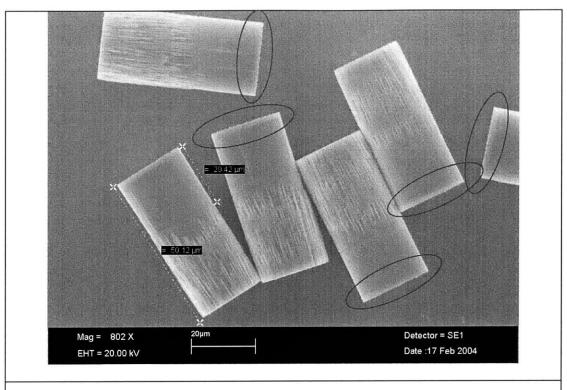

| Figure 3-13: Dimensions of silicon posts and evidence of gold cap                                           | . 45 |

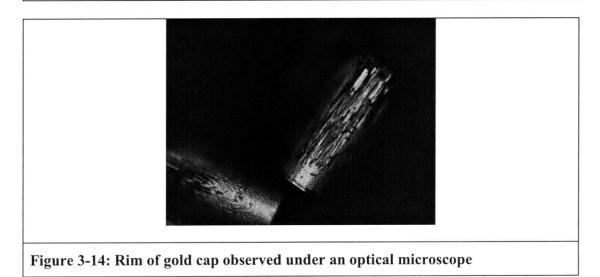

| Figure 3-14: Rim of gold cap observed under an optical microscope                                           | . 45 |

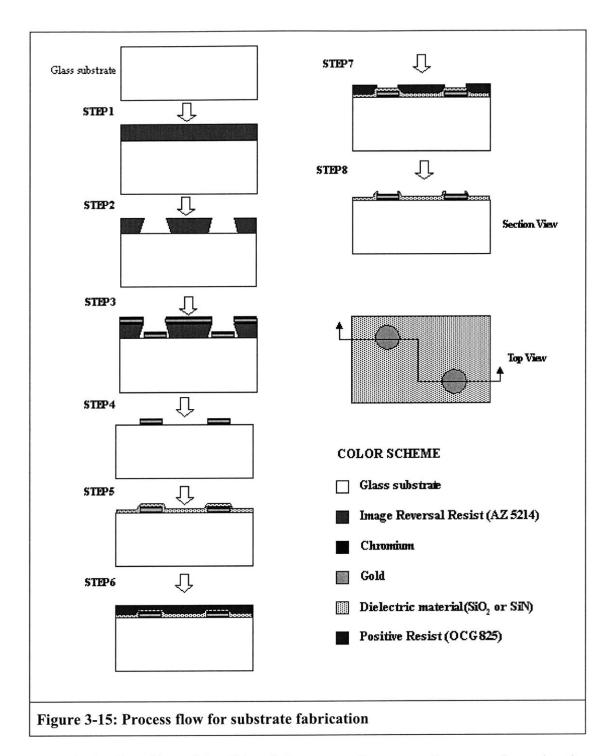

| Figure 3-15: Process flow for substrate fabrication                                                         | . 47 |

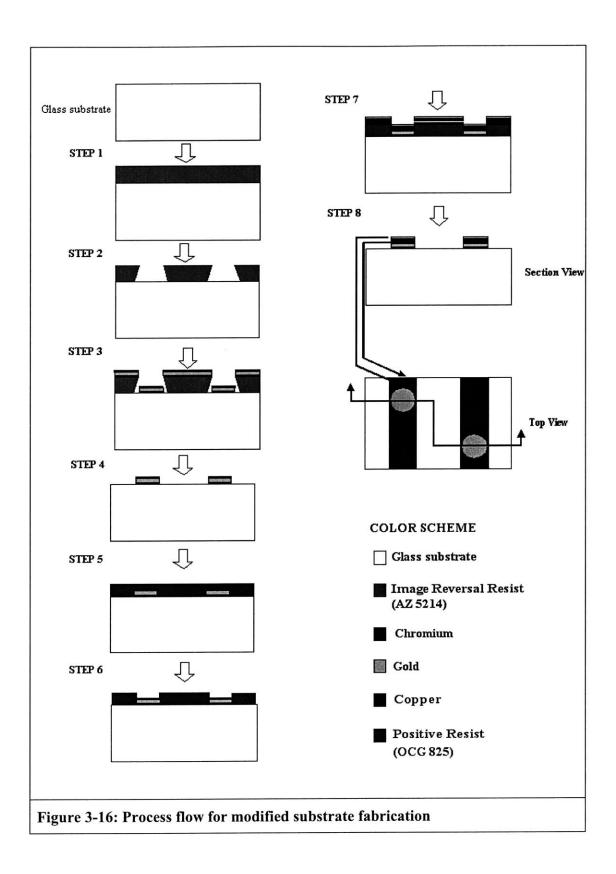

| Figure 3-16: Process flow for modified substrate fabrication                                                | . 52 |

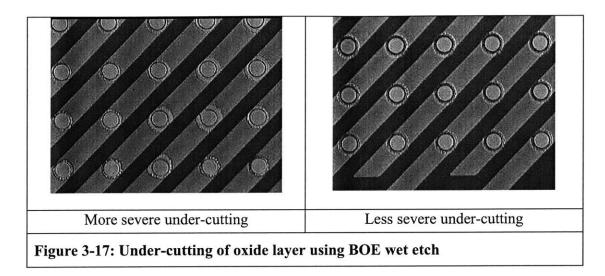

| Figure 3-17: Under-cutting of oxide layer using BOE wet etch                                                | . 54 |

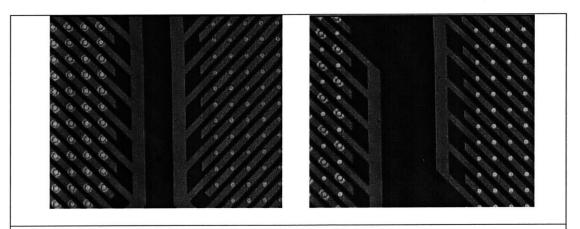

| Figure 3-18: Extreme variations in the under-cutting of Cr using a CR-7 wet etch (after the oxide dry etch) |      |

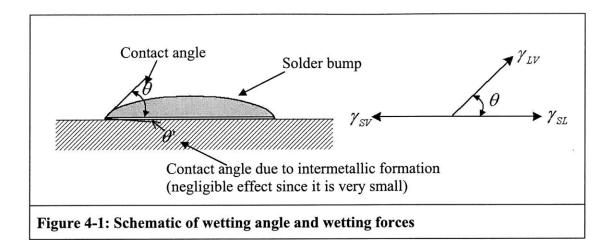

| Figure 4-1: Schematic of wetting angle and wetting forces                                                   | . 59 |

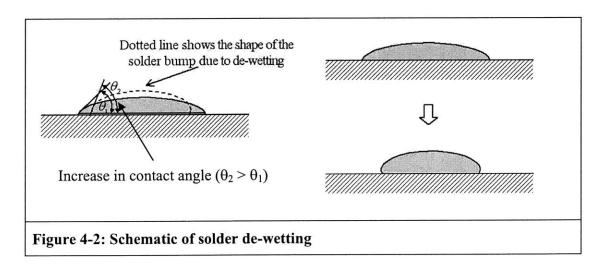

| Figure 4-2: Schematic of solder de-wetting                                                                  | . 63 |

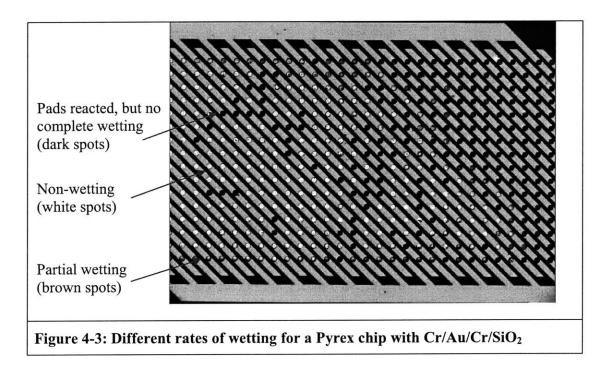

| Figure 4-3: Different rates of wetting for a Pyrex chip with Cr/Au/Cr/SiO <sub>2</sub>                      | . 66 |

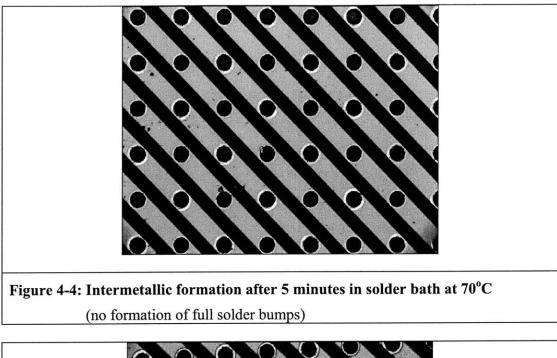

| Figure 4-4: Intermetallic formation after 5 minutes in solder bath at 70°C                                  | . 67 |

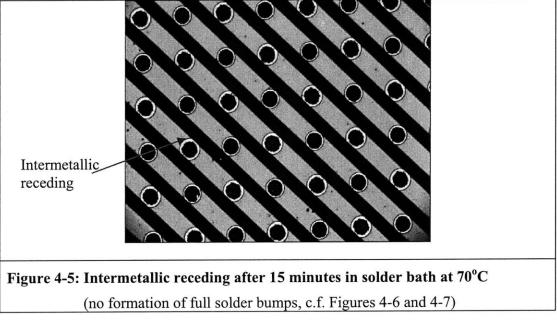

| Figure 4-5: Intermetallic receding after 15 minutes in solder bath at 70°C                                  | . 67 |

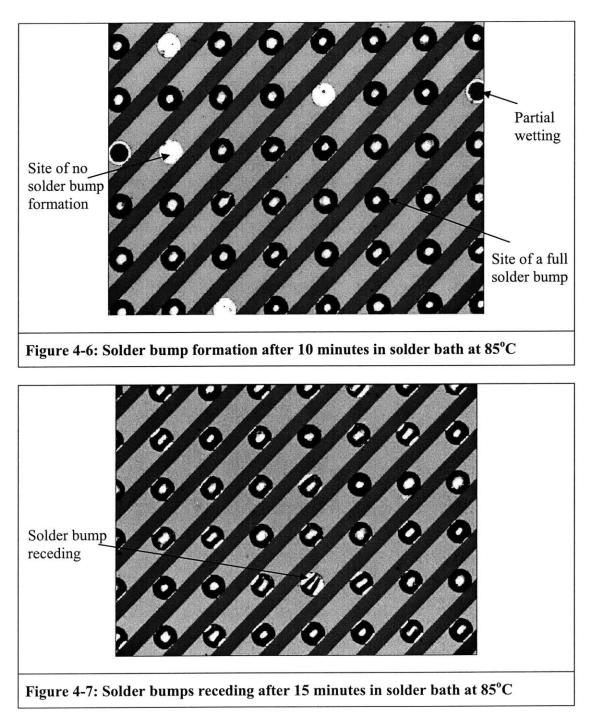

| Figure 4-6: Solder bump formation after 10 minutes in solder bath at 85°C                                   | . 68 |

| Figure 4-7: Solder bumps receding after 15 minutes in solder bath at 85°C                                   | . 68 |

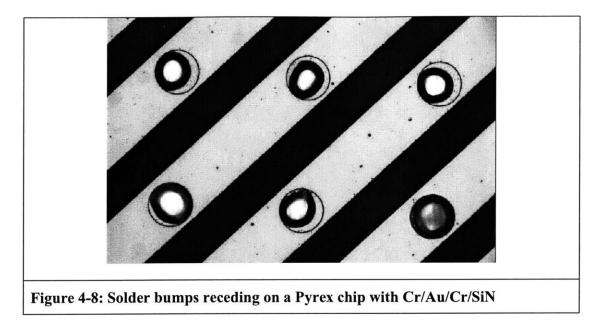

| Figure 4-8: Solder bumps receding on a Pyrex chip with Cr/Au/Cr/SiN                                         | . 69 |

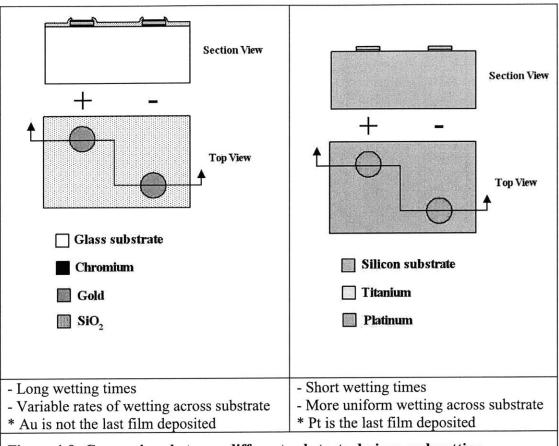

| Figure 4-9: Comparison between different substrate designs and wetting characteristic                       | s71  |

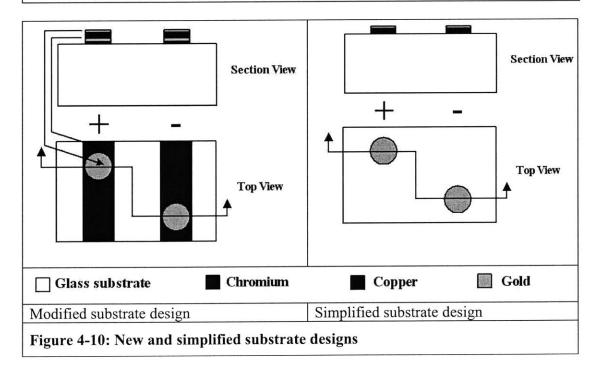

| Figure 4-10: New and simplified substrate designs                                                           | 71   |

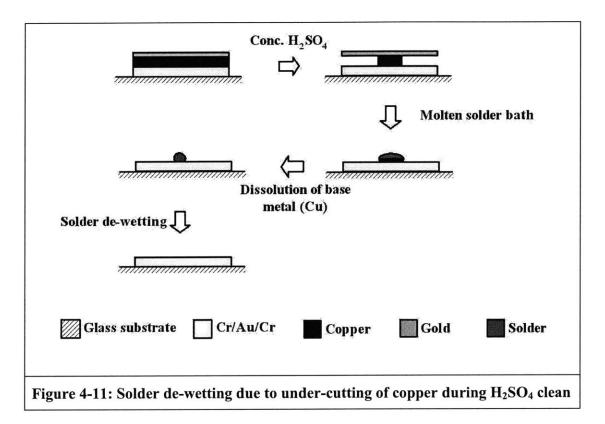

| Figure 4-11: Solder de-wetting due to under-cutting of copper during H <sub>2</sub> SO <sub>4</sub> clean 72 |

|--------------------------------------------------------------------------------------------------------------|

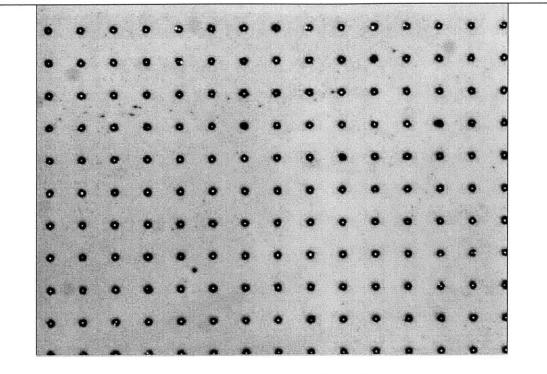

| Figure 4-12: Faster and more uniform solder wetting using the simplified substrate design                    |

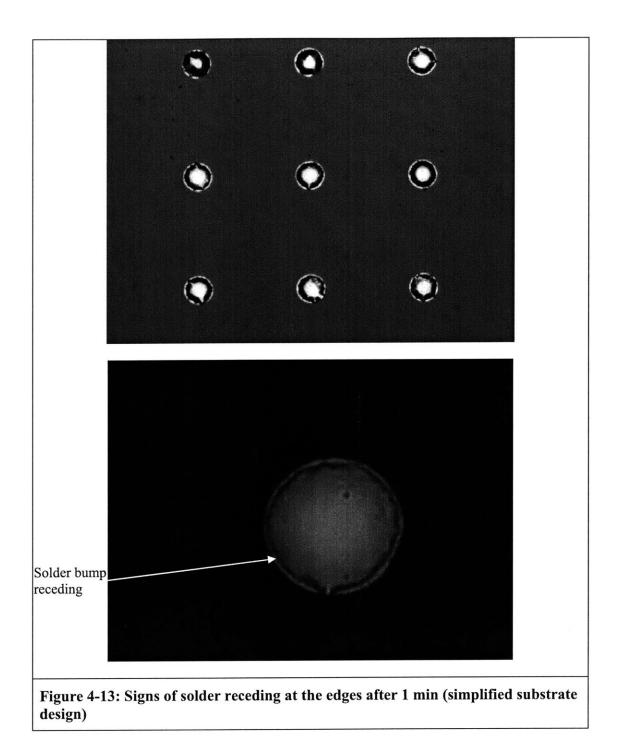

| Figure 4-13: Signs of solder receding at the edges after 1 min (simplified substrate design)                 |

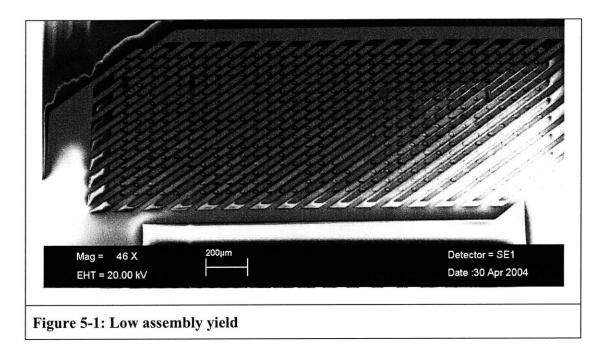

| Figure 5-1: Low assembly yield79                                                                             |

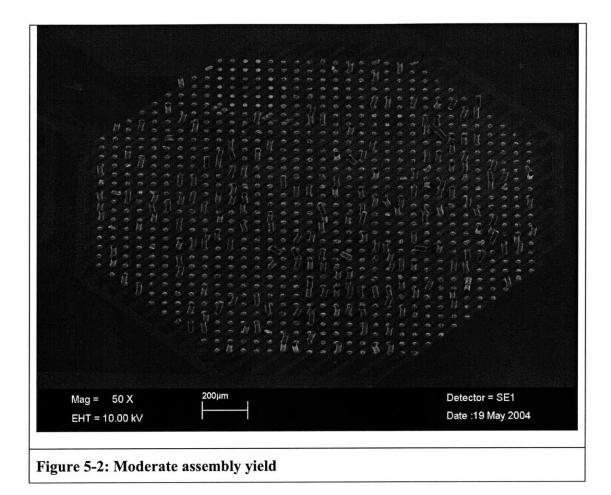

| Figure 5-2: Moderate assembly yield 80                                                                       |

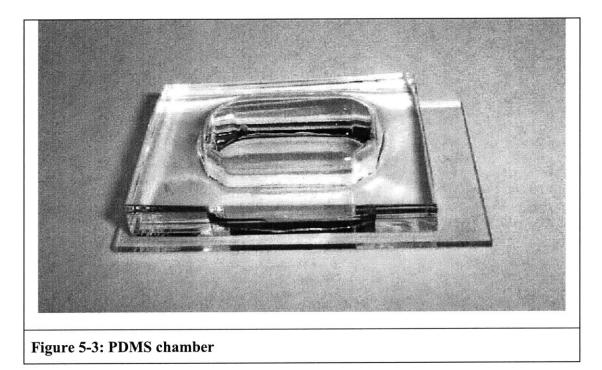

| Figure 5-3: PDMS chamber 81                                                                                  |

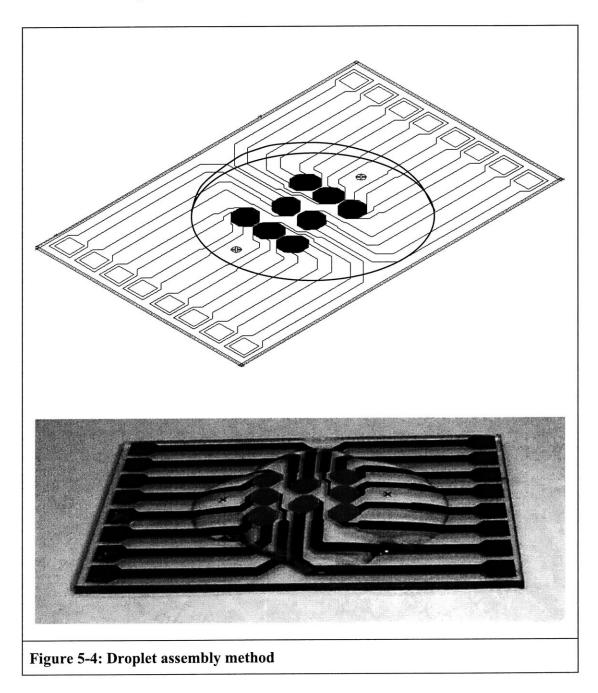

| Figure 5-4: Droplet assembly method                                                                          |

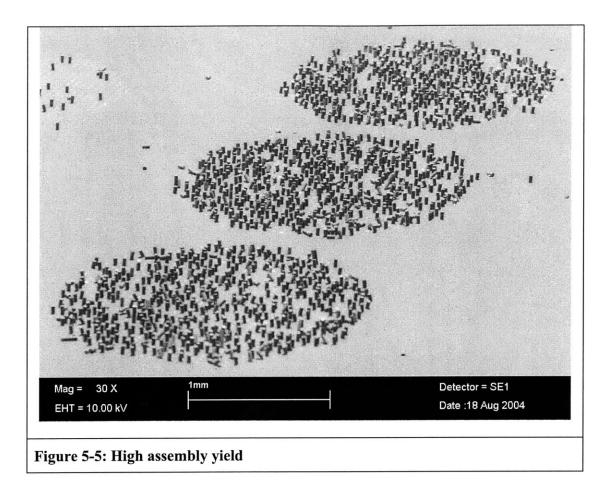

| Figure 5-5: High assembly yield                                                                              |

| Figure 5-6: Effect of ultrasound on solder bumps                                                             |

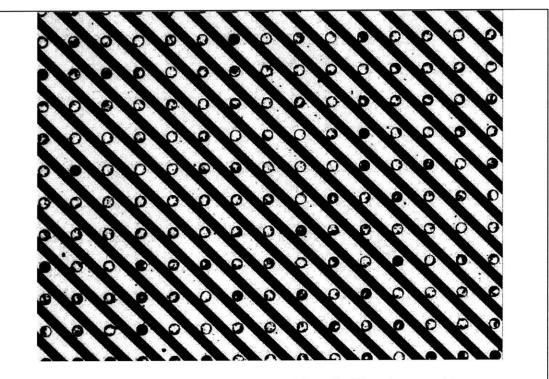

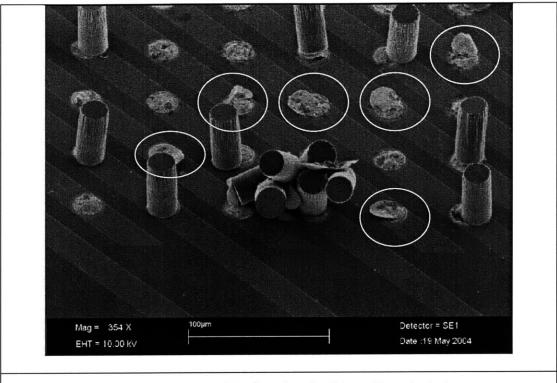

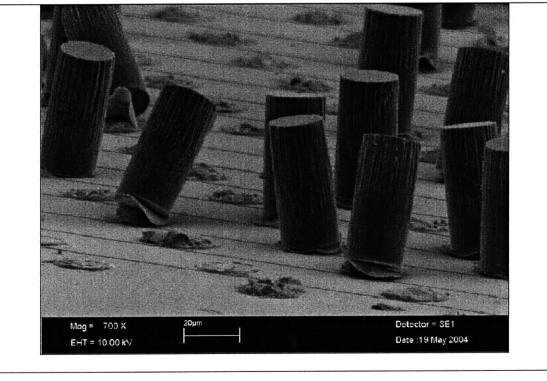

| Figure 5-7: Horizontal posts within an array (circled)                                                       |

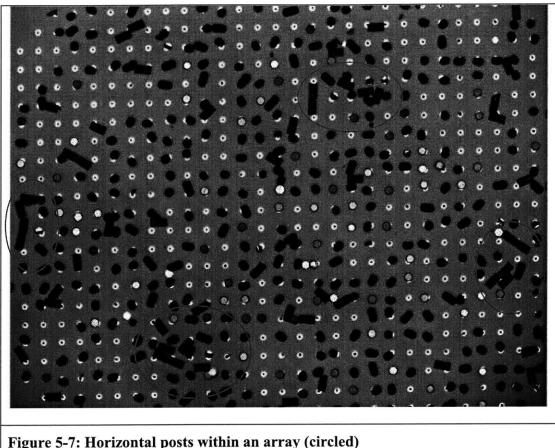

| Figure 5-8: More severe de-wetting of solder bumps using droplet method                                      |

| Figure 5-9: Cr/Au caps on assembly sites (marked in yellow circles)                                          |

| Figure 5-10: Peeling of caps leading to posts assembling at different angles                                 |

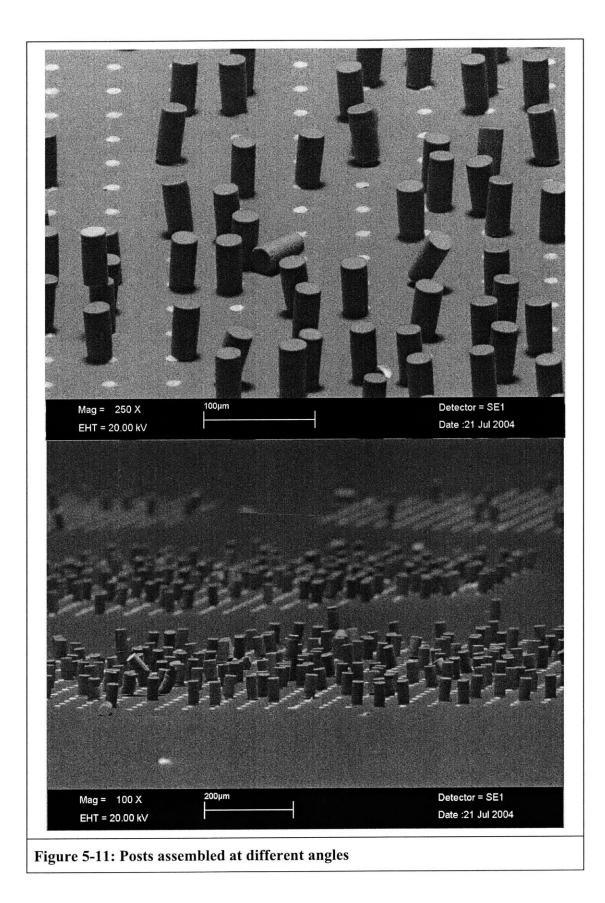

| Figure 5-11: Posts assembled at different angles                                                             |

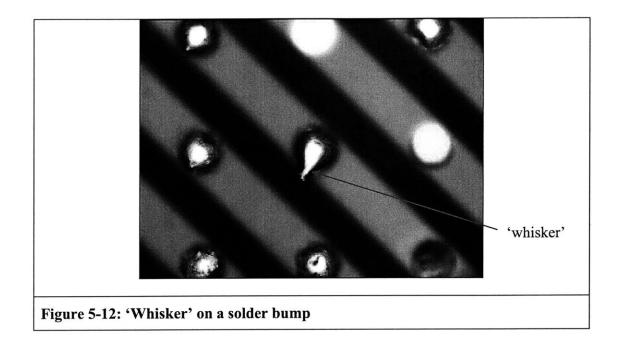

| Figure 5-12: 'Whisker' on a solder bump                                                                      |

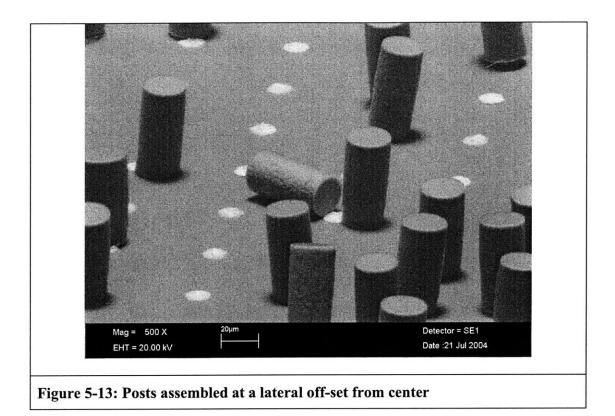

| Figure 5-13: Posts assembled at a lateral off-set from center                                                |

| Figure 5-14: Schematic of a possible local energy minimum                                                    |

# **List of Tables**

| Table 2-1: RC time for Au electrodes                                                | 0 |

|-------------------------------------------------------------------------------------|---|

| Table 2-2: RC time for Si posts 20                                                  | 0 |

| Table 3-1 : SOI wafer specifications                                                | 5 |

| Table 3-2: <ole3> recipe, STS2</ole3>                                               | 3 |

| Table 3-3: Typical etch rates for <ole3> using the mask layout in Figure 3-2</ole3> | 3 |

| Table 3-4: Process parameters for electron beam evaporation of Cr and Au    38      | 8 |

| Table 3-5: <sio2-dep> recipe, ECR-CVD (Plasmaquest)    48</sio2-dep>                | 8 |

| Table 3-6: <etchsio2>, RIE (Plasmaquest)</etchsio2>                                 | 0 |

| Table 4-1: Low melting point bismuth alloy specifications [15]                      | 6 |

| Table 4-2: Potentially non-toxic biocompatible low melting solder alloy    57       | 7 |

| Table 5-1: Comparison between the self-assembly methods in different groups         | 7 |

## Chapter 1 Introduction

#### 1.1 Background

The next generation of powerful complex microsystems will require the seamless integration of microelectromechanical systems (MEMS) sensors and actuators with other classes of microcomponents – electronic, optical, and fluidic – onto a single substrate to enable myriad systems-on-chip [1]. There are two possible integration approaches to the above: One would be to microfabricate the components in the desired locations using a serial micromachining 2-D process, and the other approach would be to fabricate diverse microstructures separately and then position and integrate them in the final system using microassembly techniques. At present, the former approach remains a major challenge since the fabrication sequences and material requirements of the different components are often incompatible due to chemical compatibility or fabrication temperature issues. Currently, for the latter approach, there exist several methods focused on microassembly, but each suffers from some limitations. For instance, the serial pick and place process is inefficient with large numbers of components; it is also ineffective with components of dimensions smaller than 100 µm because adhesive forces often dominate gravitational forces on that scale. On the other hand, both micromanipulator-based assembly and wafer-to-wafer transfer methods work poorly on non-planar surfaces, in cavities, and in the fabrication of three-dimensional (3-D) systems [2]. Self-assembly offers an alternative approach to assembling such systems. With self-assembly, free energy minimization drives the system into a desired configuration.

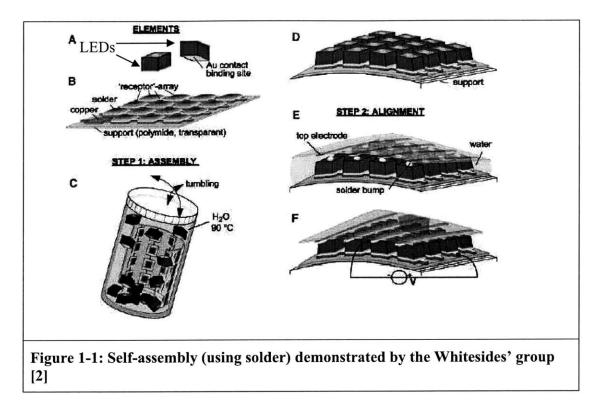

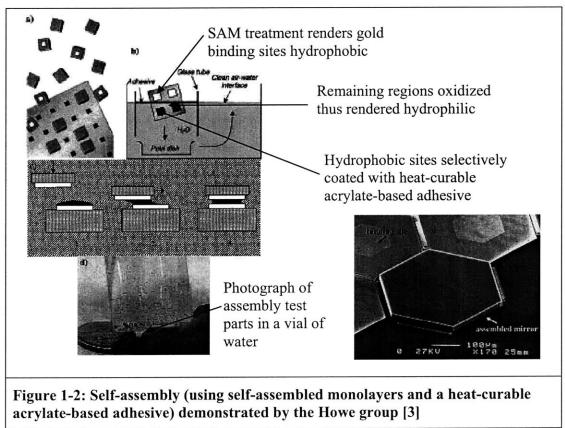

Recently, capillary-based self-assembly has been successfully demonstrated by several groups on the sub-millimeter scale, with lateral dimensions down to 150  $\mu$ m. The Whitesides' group used a solder-based self-assembly method to fabricate a cylindrical display [2] (Figure 1-1), and the Howe group used a heat-curable acrylate-based adhesive to assemble micromirrors onto microactuators [1,3] (Figure 1-2). The above-mentioned self-assembly methods are intrinsically parallel and offer the potential for submicrometer accuracy in positioning [2].

This thesis strives to improve upon the work done by the previous groups by demonstrating self-assembly of smaller and higher aspect ratio parts onto separately fabricated substrates. The feature size is on the sub-100  $\mu$ m (10<sup>1</sup>~10<sup>2</sup>  $\mu$ m) scale and is an order of magnitude smaller than the parts used in current MEMS self-assembly found in the literature [1,2,3,16]. This project is also motivated by the belief that successful and reliable means of self-assembly will impact the next generation of MEMS by integrating different and previously incompatible regimes, thereby allowing greater flexibility in the design of MEMS and processes. At the same time, by decoupling the current serial micromachining processes (into parallel), more efficient use of materials and lower yield losses can be achieved.

As with all enabling processes, self-assembly should be researched with an application or device in mind, and Prof Voldman's extruded dielectrophoresis (DEP)-based cell trap [4] (discussed below) provides a good avenue for investigating self-assembly. At the same time, this project also aims to alleviate some problems in Prof Voldman's original microfabrication process.

#### **1.2 Extruded DEP cell trap**

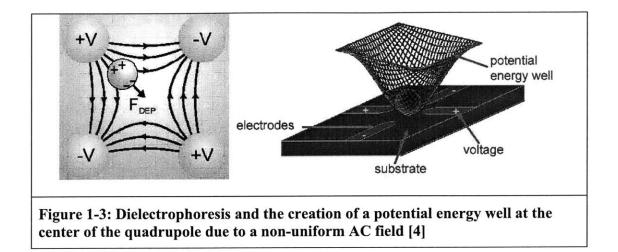

A DEP-based cell trapping array is used as a cytometer to screen cells for complex behavior [4]. It is designed to have the capability to hold and sort single cells so that assays may be performed on them. The traps use the phenomenon of dielectrophoresis, which is the action of polarizable bodies in a non-uniform electric field, to make electrically addressable potential energy wells as shown in Figure 1-3. An AC field applied to the quadrupole cell trap induces a dipole in the cell, and the driving force will be toward a field minimum (n-DEP) at the center, which traps the cell on the central axis.

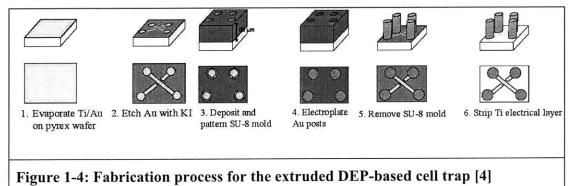

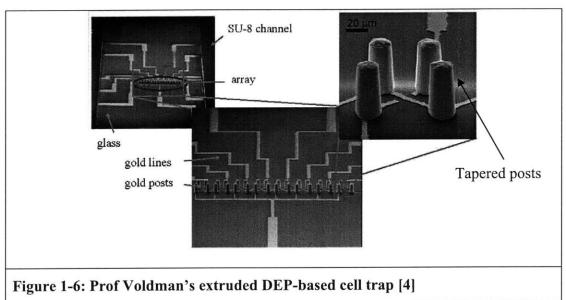

The extruded DEP-based cell trap described in Prof Voldman's work [4] consists of arrays of high aspect ratio conducting posts on a pyrex substrate, along with electrical connections to the posts. Figure 1-4 shows the fabrication process for the extruded posts, which essentially involves electroplating into a mold. In step 1, 170 nm of Ti and 500 nm of Au are evaporated onto the pyrex wafer using an e-beam. Following deposition, the substrate interconnect is defined using standard contact lithography and patterned etching of the gold in step 2. The gold is etched using a potassium iodide-based etchant [4], which displays high selectivity to titanium and glass. In step 3, a 60 µm thick SU-8 layer is spun on and patterned, and this forms the mold for electro-plating. SU-8 is an epoxy-based negative photoresist which is useful because it can be patterned with contact photolithography into high aspect-ratio microstructures. In step 4, gold is electroplated into the mold to form the posts and interconnects. In step 5, the SU-8 mold is removed and in step 6, the titanium layer is removed (except for the adhesion layer beneath the gold).

The packaging/encapsulation steps will not be depicted here since they are not central to the focus of this project on self-assembly. For more details about the fabrication process, please refer to [4].

#### **1.3 Fabrication issues**

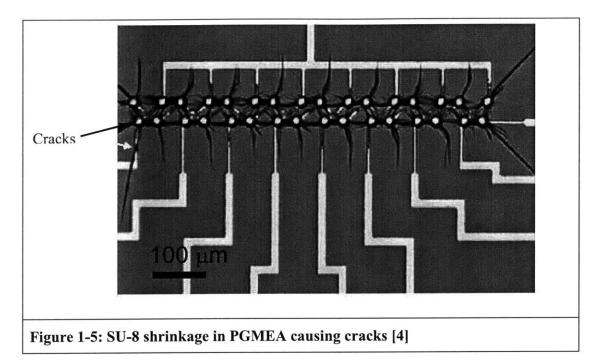

There are several problems or issues associated with the above process; these are described in more detail in [4]. Firstly, it is difficult to remove all the organic debris at the bottom of the holes at the end of step 3 due to the thickness of the SU-8 mold. This interferes with the electroplating process in step 4 since a clean gold surface is required for the process to initiate. Ashing helps to improve the yield of post initiation, but it has to be minimized and timed well because overashing will reduce the adhesion of the SU-8 to the substrate and cause underplating. Secondly, SU-8 shrinkage in PGMEA induces stress, causing cracks as shown in Figure 1-5. These cracks can affect adhesion to the substrate and cause subsequent underplating, depending on the pattern and total stress involved. Thirdly, it is difficult to achieve uniformity both in posts' height and width with high aspect ratio electroplating. The post heights varied  $\sim 10\%$  across the wafer and showed a slight taper due to the shape of the hole in the electroplating mold [4] (Figure 1-6). Lastly, the Ti layer that provides electrical contact for electroplating needs to be removed or else it will short the posts together. This is done using a dilute  $HF:H_2O$  etch, but needs to be endpointed carefully because the titanium adhesion layer under the gold can be undercut, consequently leading to lift-off and yield loss.

### 1.4 Self-assembly

It is hoped that using a self-assembly process can alleviate some of the above problems by approaching the fabrication from a different standpoint. Through the use of different processes, the posts and substrate can be fabricated separately, thus allowing more flexibility in the choice of materials and processes used. The use of SU-8 and the electroplating process can be circumvented if the fabrication process for the posts and substrate is decoupled, thereby eliminating the source of the above issues (posts' taper, process irreproducibility, posts' non-uniformity, yield, etc). Also, the posts can be fabricated from a different process other than electroplating and need not be gold, as will be shown in Chapter 2.

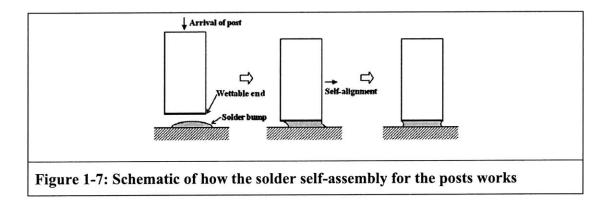

In this project, solder is used as the adhesive between the posts and substrate because electrical connections are needed in order for dielectrophoresis to work. Gold is used to define the receptor sites on the substrate because it is easily wetted by solder [5,6,7]. Dipping the patterned substrate into a solder bath will then result in the solder only selectively wetting (and coating) the gold receptor sites on the substrate, and not coating the non-wettable regions elsewhere on the substrate. After that, the solder-coated substrate and posts are placed into a fluid for assembly, and the self-assembly process will be driven by the free surface energy minimization of the solder bumps when the wettable ends of the posts come into contact with the solder bumps on the substrate as shown in Figure 1-7.

## Chapter 2 Design

#### 2.1 System requirements

In order to ensure functionality of the newly designed cell trap, the following aspects that should be fundamental to both systems (old and new) are identified. Firstly, the substrate or chip has to include a flow chamber for biological fluids. Secondly, thin film electrodes and interconnects are required in order to apply an externally driven AC field to the quadrupole array of posts. Lastly, the posts have to be extruded (50  $\mu$ m tall), uniform in size and height, and electrically connected to the electrodes. One of the objectives is to eliminate the taper observed in the previous gold posts.

### 2.2 Design of cell trap

The glass (Pyrex 7740) substrate is adopted from the previous design since it has good rigidity and is also a commonly used biocompatible material. More importantly, it is not wetted by solder, thus requiring only the patterning of (wettable) gold receptor sites on the substrate.

A new process is created to fabricate the posts. Instead of building the posts from bottom up (i.e. through multiple layer deposition or growth), the posts can be etched down into a substrate and then released for collection. In micromachining, it is often easier to etch to a large depth than to deposit a film of the same thickness. The idea of using silicon as the posts' material evolved since there are many well-developed processes for silicon micromachining and also due to the availability of SOI (silicon on insulator) wafers. SOI consists of a device (or mechanically active) layer of single crystal silicon on an intermediate (sacrificial) layer of silicon dioxide grown on a silicon substrate (handle wafer). The MEMS structures are usually defined by vertical plasma etching in the device layer, and locally released by using HF to etch the sacrificial oxide layer [6]. In these experiments, the posts are etched in an SOI wafer. This approach allows quick and large scale fabrication of high quality posts with which to examine the self-assembly process on this size scale. However, the relatively high cost of SOI wafers would make this economically not viable for commercial applications. Another source or method for fabricating the posts would then be required when a stable and reliable self-assembly process is developed.

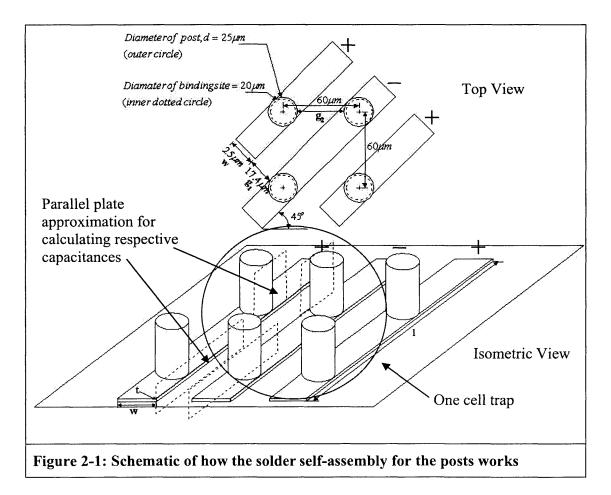

Figure 2-1 shows a close-up of the geometry and layout of the new cell trap. The array consists of interdigitated fingers of metallic interconnects which has an AC voltage of reverse polarity applied to alternate lines. The interdigitated fingers do not meet, or else the system will short. The receptor sites are connected by the interconnecting lines, and this wiring pattern creates the quadrupole pattern over arrays of arbitrary size. The aim of this project is to position the posts in the given configuration on the receptor sites through self-assembly, with the solder providing the adhesion and electrical connection. The circled region in the figure shows an effective cell-trap.

However, the feasibility of the system using silicon posts has first to be determined from its RC time, which needs to be faster than the high frequency AC field driven at 10's of MHz [7]. A rough approximation of the RC time is made by considering the resistance and capacitance of the electrodes (interdigitated lines) and posts. A parallel plate approximation is used to simplify the capacitance calculations for both the electrodes and the posts, which will yield a conservative (long) estimate of the RC time. In this approximation, features are replaced by parallel plates at the point of closest approach as shown in Figure 2-1. Tables 2-1 and 2-2 list the important parameters and show the results of the calculations using Equations 2-1 to 2-3:

$$R = \frac{\rho l}{A_{flow}}$$

(2-1)

$$C = \frac{\varepsilon A_{plate}}{g}$$

(2-2)

$$\tau = R C \tag{2-3}$$

where R is the resistance,  $\rho$  is the resistivity, l is the length,  $A_{flow}$  is the cross-sectional area of flow, C is the capacitance,  $\varepsilon$  is the permittivity of glass,  $A_{plate}$  is the area of the capacitor plate, g is the dielectric gap distance between parallel interconnects, and  $\tau$  is the RC time.

| Parameter                                                 | Lines (Au)                            |

|-----------------------------------------------------------|---------------------------------------|

| Linewidth of electrode/interconnect, w                    | 25 μm                                 |

| Thickness of electrode/interconnect, t                    | 100 nm                                |

| Dielectric gap distance between parallel                  | 17.4 μm                               |

| interconnects, $g_1$                                      |                                       |

| ε                                                         | $4\varepsilon_0$                      |

| Length of interconnect, $l_1$                             | Ranges from 0.1 mm to 10 mm (use a    |

|                                                           | high value, 10 mm, for a conservative |

|                                                           | estimate)                             |

| <b>Capacitance</b> $C = \frac{\varepsilon w l_1}{\alpha}$ |                                       |

| $g_1$                                                     | 5.1 x 10 <sup>-13</sup> F             |

| Table 2-1: RC time for Au electrode        | s                                 |

|--------------------------------------------|-----------------------------------|

| <i>RC</i> time                             | 5.0 x 10 <sup>-11</sup> s         |

| <b>Resistance</b> $R = \frac{\rho l_1}{A}$ | 97.6 Ω                            |

| Cross-sectional area $A_{plate} = t w$     | $2.5 \times 10^{-12} \text{ m}^2$ |

| Resistivity $\rho_{Au}$                    | 2.44 x 10 <sup>-8</sup> Ω.m       |

| Parameter                                                  | Posts (Si)                                                  |

|------------------------------------------------------------|-------------------------------------------------------------|

| Diameter of post, d                                        | 25 μm                                                       |

| Length of post, $l_2$                                      | 50 µm                                                       |

| Area used in parallel plate approximation,                 | $2.0 \times 10^{-9} \text{ m}^2$                            |

| $A_{plate} = \frac{\pi  d  l_2}{2}$                        |                                                             |

| Dielectric gap distance between adjacent                   | 40 µm                                                       |

| posts (edge to edge), $g_2$                                |                                                             |

| $\mathcal{E}_0$                                            | 8.85 x 10 <sup>-12</sup> F/m                                |

| <b>Capacitance</b> $C = \frac{\varepsilon A_{plate}}{g_2}$ | 4.3 x 10 <sup>-16</sup> F                                   |

| Resistivity $\rho_{Si}$                                    | Ranges from 8 x $10^{-5}$ to 2 x $10^{-4}$ $\Omega$ .m (use |

|                                                            | the higher value, $2 \times 10^{-4} \Omega$ .m, for a       |

|                                                            | conservative estimate)                                      |

| Cross-sectional area $A_{flow} = \frac{\pi d^2}{4}$        | $4.9 \times 10^{-10} \text{ m}^2$                           |

| <b>Resistance</b> $R = \frac{\rho_{Si} l_2}{A_{flow}}$     | 20.4 Ω                                                      |

| <i>RC</i> time                                             | 8.9 x 10 <sup>-15</sup> s                                   |

| Table 2-2: RC time for Si posts                            |                                                             |

Assuming a minimum driving frequency of 1 MHz, the RC time needs to be much less than  $10^{-6}$  sec for the signal to reach the posts. The results in Tables 2-1 and 2-2 show that the RC times using the gold interconnect lines and silicon posts are many orders of

magnitude below the  $10^{-6}$  sec limit due to the small length-scale of the system, thus ensuring the feasibility of using silicon posts and the above given linewidth/space in the new system.

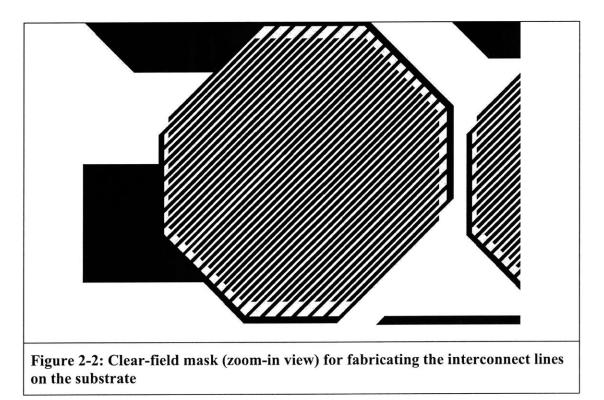

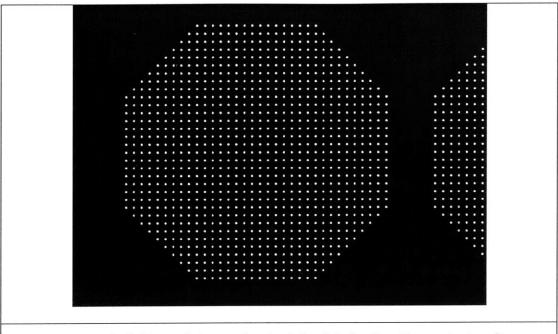

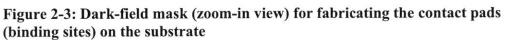

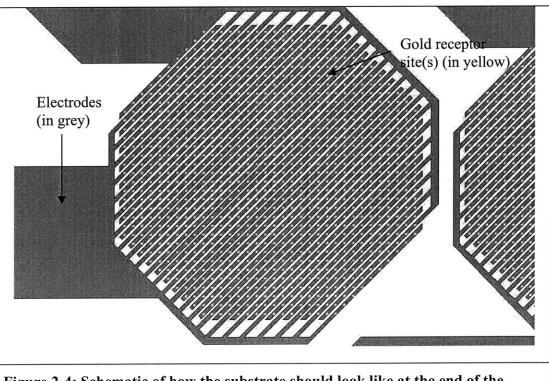

Three masks were designed: two for the substrate fabrication and one for the posts fabrication (from the SOI). Figure 2-2 shows a single array of traps from the first mask (clear-field) used for patterning the interconnect lines, and Figure 2-3 shows a single array from the second mask (dark-field) used for patterning the gold contact pads for the solder coating. Figure 2-4 displays what an array pattern should look like under a microscope at the end of the fabrication. Figure 2-5 shows the superposition of the two masks for the substrate fabrication, and the critical dimensions for the array. A 4" pyrex wafer having undergone successful completion of microfabrication contains 6 full-sized actual chips, each with 8 arrays of receptors sites, and 6 dummy chips for testing and solder characterization.

Figure 2-4: Schematic of how the substrate should look like at the end of the fabrication

## **Chapter 3 Device fabrication**

### 3.1 Design of fabrication processes

The cell trap primarily consists of posts, and substrates, and the material providing the capillary force for self-assembly, which is a low melting point bismuth alloy (Small Parts, Miami Lakes, Florida, LMA-117 [15]). In this chapter, the fabrication processes for the posts and substrates will be listed in detail. The micromachining processes used are serial and inherently 2-D in nature, and involve a series of steps such as photolithography, thin film deposition, and etching. The posts and substrates were fabricated using the clean room facilities in the Integrated Circuits Lab (ICL), Technology Research Lab (TRL), and Exploratory Materials Lab (EML), all collectively coming under the MIT Microsystems Technologies Laboratories (MTL).

### 3.1.1 Silicon posts fabrication

The starting materials for making the silicon posts are 6" SOI (silicon on insulator) wafers. The posts are defined by vertical plasma etching in the device layer, and locally released by using HF to etch the sacrificial oxide layer. The specifications of the SOI wafers (Ultrasil Corporation, Hayward, CA) used are given in Table 3-1. The key parameters to note are the device layer resistivity which needs to be low (i.e. highly-doped) so that the resistance of the posts is low to allow good conductivity, and the device layer thickness which determines the height of the silicon posts in the cell traps. The 2  $\mu$ m buried oxide layer is sufficient to act as an etch stop for the deep reactive ion etching (DRIE) process since it has etch selectivities ranging from 120 to 200:1.

| Size (mm)             | 150±0.2 |  |

|-----------------------|---------|--|

| Type / Dopant         | N / Sb  |  |

| Orientation           | <100>   |  |

| Device thickness (µm) | 50±2    |  |

| Table 3-1 : SOI wafer specifications     | [             |         |

|------------------------------------------|---------------|---------|

| Handle wafer resistivity ( $\Omega$ -cm) | 0.01 to 0.05  | <u></u> |

| Handle wafer thickness (µm)              | 600±20        |         |

| Buried oxide thickness (µm)              | 2             |         |

| Device resistivity (Ω-cm)                | 0.008 to 0.02 |         |

The fabrication processes for the silicon posts can be broadly divided into photolithography, plasma etching, electron-beam evaporation and wet processing such as HF etch release and metal lift-off using acetone. The processing will be detailed in the following sections, as well as any special steps taken for precaution.

A brief overview on photolithography is given because it is the key method for pattern transfer and comprises a major portion of the processing. Lithography is the process in which patterns on the mask are transferred onto the substrate by selectively exposing (and developing) areas on a light-sensitive photoresist. An overview of a standard lithography process is depicted in Figure 3-1.

Figure 3-2 shows the mask for the posts fabrication, and also lists the important dimensions. The close-up of a corner of one die is shown in the lower half of the figure, which indicates that it is clear-field within each die (the total number of dies on a wafer is 32) and dark-field outside of the dies.

Figure 3-3 shows the process flow for the posts fabrication.

In step 1, the SOI wafers are first put into the HMDS oven in the TRL for a 15 minute dehydration bake to dry off the water. Next, the wafers are primed with hexamethyldisilizane (HMDS) which is an adhesion promoter for the photoresist. HMDS converts the hydrophilic native oxide layer on the silicon wafer to create a hydrophobic surface, to which the photoresist will adhere readily. For AZP 4620 positive thick photoresist, recipe 3 in the TRL HMDS oven (60 secs HMDS dispense) is used which gives a photoresist contact angle of  $55^{\circ}$  after the bake, exposure and development. After

allowing the wafers to cool for five minutes, AZP 4620 thick resist is dynamically dispensed onto the wafer in the TRL coater at 1750 rpm for 12 secs, followed by spreading of the resist at 3500 rpm for 60 secs, and finally a spin of 5000 rpm for 10 secs. The spreading speed determines the thickness of the AZP 4620 resist which is about 7 µm after post-bake. The spread speed (giving this thickness of the photoresist) is chosen due to the type of photoresist available in the TRL, which does not have photoresist of intermediate thickness range from 2 to 5  $\mu$ m. It is difficult to achieve good resist coats at high speeds due to the vortices, which introduces resist non-uniformity and defects. The above photoresist recipe is used because it gives uniform, consistent resist coats with few defects. The final 10 secs high speed spin helps to reduce edge-beads which form at the circumference of the wafers during thick resist coating. In addition, holding a fab swab 5 to 10 mm away from the edge of the spinning wafer during the coating process helps to reduce particles, edge-beads, and other defects on the resist coat. Before coating the actual SOI wafers with the resist, the process is carried out on a dummy silicon wafer to practise obtaining a good photoresist coat, which is often dependent on the eccentricity of the wafer on the vacuum chuck and the centering of the dispensing nozzle tip.

After the resist coating, the Teflon carrier holding the SOI wafers is placed into the TRL pre-bake oven for a 60 minute pre-bake at  $95^{\circ}$  C. This is to drive off the residual casting solvent from the photoresist film.

In step 2, the wafers are exposed on the TRL EV1, which is an Electronics Visions EV620 Mask Aligner. The exposure system uses a 350-watt high pressure mercury lamp and has an exposure controller with 3 channels: constant power, or constant intensity (CI) 1 or 2. CI 1, set at 10 mW/cm<sup>2</sup>/sec, is always used, and the wavelengths are 365-405 nm [8]. The exposure settings are as follow:

- 1. Maskholder size (7") and thickness (3.045mm or 0.12");

- 2. Substrate size (6"), thickness (0.53mm);

- 3. Separation distance (45 um),

- 4. Process (top side) and mode (transparent),

- 5. Exposure mode (interval),

#### 6. Contact mode (soft contact).

The soft contact mode is usually used for the first mask since no alignment between the mask and wafer is necessary. The exposure is carried out in 3 intervals of 5 sec each with a 5 sec delay in between, giving a total exposure time of 15 sec for the 7  $\mu$ m thick AZP 4620 resist. The 5 sec delay is to allow the resist to cool down between exposures to prevent resist bubbling.

After exposure, the resist is developed in AZ 440 for about 1 min 45 secs (until the patterns become clear). The developing is done in a beaker just bigger than the wafer, with about  $\frac{1}{4}$ " (1/2 cm) of developer. For AZP 4620 thick resist, the developer is agitated in a non-repetitive pattern, as the developing is diffusion rate limited. The wafers are then rinsed with water for 3 mins after the development.

Following development is a 30 minute hard bake at 95° C, which is used to harden the resist against further energetic processes such as plasma etching.

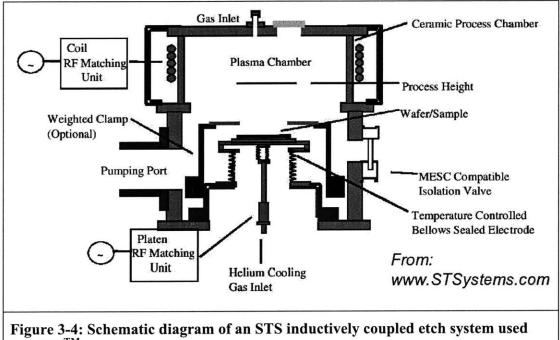

Step 3 uses Deep Reactive Ion Etching (DRIE) to etch the posts in the device layer. DRIE relies on an inductively coupled plasma source and successive cycles of etching and passivation to achieve high aspect ratio silicon structures. The alternating between the etching and passivation steps is known as "TMDE"-Time Multiplexed Deep Etch [9]. The machine used is the STS2 in TRL, which is developed by Surface Technology Systems (STS) using their advanced silicon etch ( $ASE^{TM}$ ) process. A schematic of the STS DRIE etcher can be seen in Figure 3-4. The plasma is created within the plasma chamber, using an induction coil connected to a 13.56 MHz RF source to create excitation of the gas. A second 13.56 MHz RF source is connected to a platen where the wafer to be etched is placed. This second RF source creates a bias between the plasma and wafer which is required for the ASE process. The passivation cycle is to minimize lateral etching of the sidewalls from the highly reactive neutrals of the RIE chemical component. It involves the deposition of a Teflon-like (polymerized CF<sub>2</sub>) polymer about 50 nm thick on the side walls and the base of the features by the ionization and dissociation of octaflurocylcobutane (C<sub>4</sub>F<sub>8</sub>). The chamber is then evacuated of C<sub>4</sub>F<sub>8</sub> prior

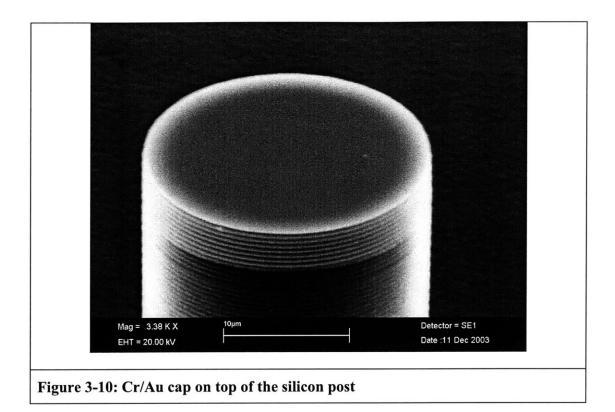

to the etch step beginning. The etch step introduces  $SF_6$  and  $O_2$  into the chamber, decoupling them into ions and radicals (a neutral species). The ion bombardment rapidly removes the polymer from the horizontal base surface, and serves to enhance the etching process by damaging the silicon surface making it more susceptible to reaction with the fluorine radicals. The sidewalls remain protected by the polymer which receives no ion bombardment (since the ions are columnated), and consequently no chemical etch, either [9]. One drawback is that the process leaves scalloped sidewalls on the features as a result of the multiplexing, as can be seen in Figure 3-10.

Figure 3-4: Schematic diagram of an STS inductively coupled etch system used for ASE<sup>TM</sup>

The STS2 uses a mechanical clamp made up of eight ceramic 'fingers' to pin down the edge of the wafer and hold it onto the chuck. The chuck provides He backside cooling to the wafers. This keeps the wafer cool enough during the plasma process so that the resist does not etch too quickly (selectivity to silicon is about 75:1), and also to minimize resist burning [10]. The wafer to chuck interface is aided by a lip seal which stops the He from leaking into the chamber and changing the etch rate. As such, the backside of the wafers needs to be clean of resist or debris which if present will break the seal. If the pressure on the screen is greater than 15 mtorr/min (indicating a high He leak-out rate), the

process will not begin and the backside of the wafer needs to be cleaned of particles or resist using a fab swab dipped in methanol in the solvent hood. After cleaning with methanol, it is good practice to put the wafer into the pre-bake oven for one or two minutes to drive off any remaining solvent before putting it into the STS2 chamber for subsequent etching. It is suspected that trace amounts of solvents remaining on the wafer may contribute to patches of photoresist scum on the wafer surface during the etch.

The recipe used is <OLE3>, which is a variation of <MIT37\_A>. <MIT37\_A> is a recipe that reliably yields vertical sidewall profiles and good etch uniformity between small and large features. The profile of the etched silicon posts needs to be straight and is important since one of the objectives of this project is to reduce post taper and to produce more uniform posts. The recipe for <OLE3> is given in Table 3-2. The <OLE3> recipe is first run on a patterned silicon dummy wafer to determine the etch rate. This is because the etch rates for the STS2 vary both across the wafer (macroscopic non-uniformity) and for different mask layouts and geometry (microscopic non-uniformity) [11]. For better etch uniformity, the wafer is rotated after each time interval. The total etch depth after each time interval is shown in Table 3-3.

|                    | General settings                     | Parameter                     |  |

|--------------------|--------------------------------------|-------------------------------|--|

| Process            | Pump down time                       | 20 secs                       |  |

|                    | Gas stabilisation                    | 10 secs                       |  |

|                    | Process time                         | Entered by user based on etch |  |

|                    |                                      | rate and desired etch depth   |  |

|                    | Process pressure (mTorr)             | 31 mTorr                      |  |

|                    | Pump out time                        | 30 secs                       |  |

| Order (etch first) | Etch step                            | 14                            |  |

|                    | Passivate step                       | 12.5                          |  |

| Gas Flows          | C <sub>4</sub> F <sub>8</sub> (sccm) | SF <sub>6</sub> (sccm)        |  |

| Etch step          | 0                                    | 140                           |  |

| Passivate step     | 95                                   | 0                             |  |

| RF power           | Platen generator                     | Coil generator                |  |

| settings       |       |       |  |

|----------------|-------|-------|--|

| Etch step      | 140 W | 600 W |  |

| Passivate step | 0 W   | 600 W |  |

| Etch pass | Time (min) | Etch depth (µm) | Etch rate (µm/min) |

|-----------|------------|-----------------|--------------------|

| 1         | 20         | 15              | 0.75               |

| 2         | 20         | 28              | 0.65               |

| 3         | 15         | 40              | 0.8                |

| 4         | 13         | 50              | 0.77               |

From the above table, it is seen that it takes 68 mins to etch 50  $\mu$ m of the silicon dummy wafer. The average etch rate is calculated to be about 0.74  $\mu$ m/min. From this test, a ballpark estimate of the time required to etch the silicon posts on the SOI in the STS2 is obtained.

For the etching of the SOI wafer, it is ensured that each process interval ended on an etch step instead of a passivation step. The system is vented and the wafer is rotated between etch time intervals; typical time intervals are (17:53, 17:53, 17:53, 13:53). The first glimpse of the buried oxide layer is observed 3 mins into the third interval. The oxide layer has a purple color and the etch front is seen to advance inwards from the edge of the wafer, which means that the outside etches faster than the inside. This "bulls-eye" pattern is usually due to depletion effects as the gas flows from the outside of the wafer to the inside [11]. Since the etch pattern on the wafer is uniform, microloading is not an issue. Microloading occurs when etch rates vary over small distances on the surface of the wafer due to differences in the density of the unmasked area [11]. Because of nonuniformities in the etch rate, a certain amount of overetching is done to ensure that complete etching is achieved everywhere on the wafer. This is often 10-20%, in terms of time, past the endpoint detection [11]. For etching the posts in this project, the endpoint

detection is when most of the field is etched to down to the oxide and is visible (by color), and the etch is not extended beyond the endpoint detection. This is because when using the STS plasma etcher to etch SOI wafers, there is a problem known as "notching" as the plasma etches through to the oxide layer [9]. Notching takes the form of cavities at the base of the etched features adjacent to the oxide layer. This is caused by a charging effect on the oxide layer which scatters previously columated ions into the sidewalls, causing impact damage to the sidewalls in local proximity to the oxide layer. When the following passivation layer is deposited, it is unable to completely coat the newly created cavity and therefore does not protect the damaged areas from further chemical etching, thus enhancing the impact damage [9].

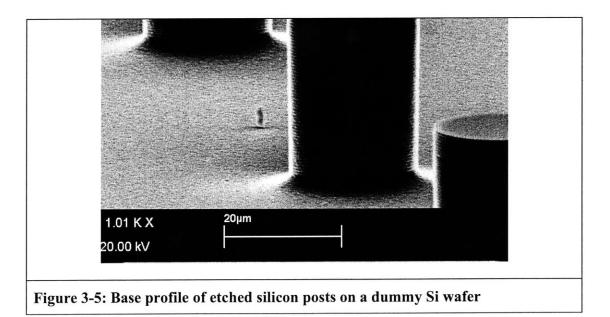

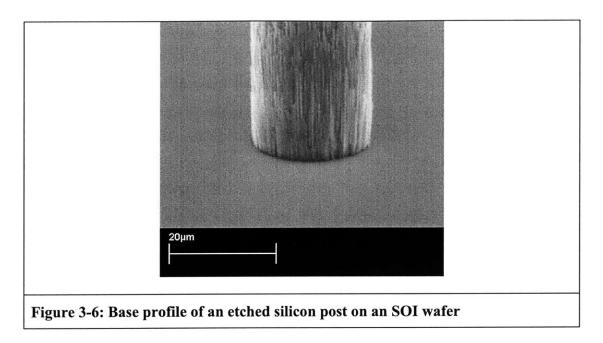

Figure 3-5 shows an SEM micrograph of the base of etched silicon posts on a plain silicon dummy wafer, and Figure 3-6 shows an SEM micrograph of the base of etched silicon posts on an SOI wafer. For the dummy wafer, the silicon continues to be etched because there is no etch stop, and this results in a sloped profile at the base of the silicon posts. For the SOI wafer, vertical etching slows down considerably at the buried oxide etch stop layer, but lateral etching at the base of the posts continues due to notching.

In step 4, after the SOI wafers have been etched to completion, they are immersed for 10 mins in a glass beaker containing a solution of  $3 H_2SO_4 : 1 H_2O_2$  in the acid-hood. This solution is commonly known as "Piranha" and is used to strip photoresist off wafers and for general wafer cleaning. After the photoresist is removed, the wafers are rinsed for 3 cycles in the dump-rinser and then spun-dry.

To remove the Teflon-like polymer on the sidewalls of the silicon posts, the SOI wafers are ashed for 30 mins in the TRL asher. This dual-barrel downstream asher uses an oxygen plasma generated by a 1200 W 13.56mHz RF power supply to remove organic films and contamination from wafers by exposing them to the chemical reactivity and kinetic energy of oxygen ions [8]. After the chamber pressure has stabilized to 0.09 mm Hg with both the vacuum and oxygen switched on, the RF forward power dial is adjusted to 1000 W.

In steps 5 and 6, photolithography is performed on the etched SOI wafers in preparation for the self-aligned process. The self-aligned process in principle works similar to a liftoff process, except that it does not require a mask and uses the existing topography of the wafer (and the resist) to lay down metal patterns. This potentially leads to cost savings in masks since one mask less is required, compared with the approach of depositing and etching the Pt metal. No HMDS priming is necessary for this step because the resist adhesion to the substrate and its resistance to etch are not crucial for the self-aligned process. In fact, it works better in the reverse case since it is essentially a variant of the lift-off process. AZP 4620 thick resist is dispensed onto the center of the stationary wafer in the TRL coater for 18 secs and allowed to sit for 10 secs to let the bubbles rise. If insufficient time is allowed to let the bubbles rise, they will manifest as defects on the resist coat. Any visible bubble is lightly removed by a fab swab before the spread cycle at 750 rpm for 10 secs, and then the spin cycle at 1000 rpm for 60 secs. After the resist coating, the SOI wafers are placed into the TRL pre-bake oven for a 60 minute pre-bake at  $95^{\circ}$  C.

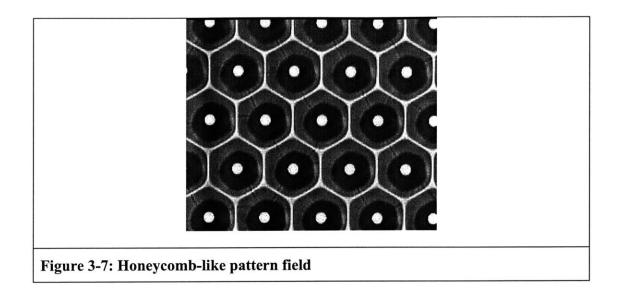

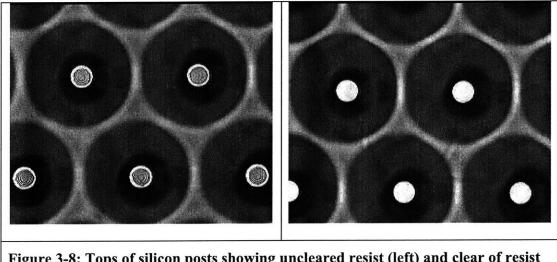

In Step 6, the wafers are flood exposed for 2 secs under the EV1. The theory is that the thin layer of resist on the top of the posts will be fully exposed while the rest of the field will be under or little exposed. Upon developing, the top of the posts will be cleared of resist while most of the field still has a thick layer of resist. The wafers are then developed in AZ 440 for 20-25 secs. Figure 3-7 shows a picture of the wafer at this stage, which has a honeycomb-like pattern due to etch non-uniformity in the regions between the posts. It is advisable to develop first for 15 secs and then inspect under the microscope to see if there is still any resist on the top of the silicon posts. Colored rings on the top of the silicon posts will be observed if resist is still present, as seen on the left of Figure 3-8. If necessary, develop further until the top of the silicon posts is cleared of resist as seen on the right of Figure 3-8. The wafers are then rinsed with water for 3 mins after the development. No further post-bake is necessary.

Figure 3-8: Tops of silicon posts showing uncleared resist (left) and clear of resist (right)

Step 7 is the electron beam evaporation of a 10 nm Cr / 120 nm Au layer onto the SOI wafers using the TRL ebeam. The Cr is necessary as an adhesion layer for Au, which is a relatively non-reactive noble metal. An electron beam (10 keV, 200 mA) is scanned over the Cr and Au targets respectively in a vacuum chamber at  $2x10^{-6}$  Torr, generating a vapor for deposition [8]. The step coverage for electron beam evaporation is poor because of the molecular ballistic flow of the evaporated atomic flux (long mean free path) in the vacuum chamber [12]. This is useful for our purpose since we only want metal caps on top of the posts and not on the sidewalls. Furthermore, the poor step

coverage aids in the subsequent lift-off process, which would be very difficult if the film were conformally deposited, for instance, using sputtering. Sputtering is not used because of the high baking temperature and considerable heating of the substrate from the secondary electrons emitted from the target, which hardens the photoresist and makes it difficult to remove for the metal lift-off. The parameters for the Cr and Au evaporation process are shown in Table 3-4. The lift-off plate is used instead of the planetary carrier, and to achieve a more uniform coating, the lift-off plate is rotated using a motor during the deposition.

| Process                    | Chromium                 | Gold                       |

|----------------------------|--------------------------|----------------------------|

| Rise time (min)            | 1.3                      | 2                          |

| Soak time (min)            | 2                        | 2.3                        |

| Predeposit time (min)      | 0.3                      | 1.3                        |

| Setpoint                   | 0                        | 0                          |

| Soak power (%)             | 15                       | 15                         |

| Predeposit power (%)       | 16                       | 16                         |

| Maximum power (%)          | 18                       | 25                         |

| Idle power (%)             | 0                        | 0                          |

| Deposition rate (A/sec)    | 2                        | 3                          |

| Thickness (kA)             | 0.1                      | 1.2                        |

| Source/sensor              | 11                       | 11                         |

| Response                   | 15                       | 10                         |

| Error limit                | 10                       | 10                         |

| Tooling (%)                | 61                       | 55                         |

| Density of material        | 7.2                      | 19.3                       |

| Acoustic impedance         | 28.9                     | 23.18                      |

| * Make sure crystal health | is greater than 85% befo | ore starting process       |

| Table 3-4: Process param   | neters for electron bea  | m evaporation of Cr and Au |

Step 8 is the lift-off patterning of the Cr/Au caps on the tops of the silicon posts. The thick resist field acts as a "sacrificial" mask, and is dissolved in acetone, in the process

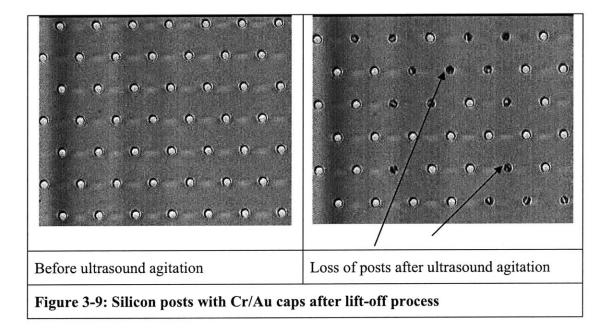

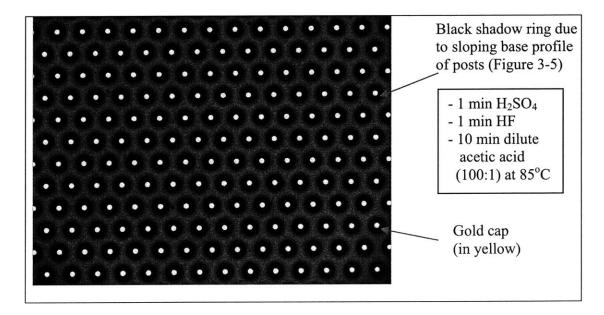

"lifting off" the unwanted metal. The lift-off is carried out in an ultrasonic bath to speed up the process. After most of the field is clear of Au (and resist), the SOI wafers are rinsed in methanol, followed by isopropanol, and then water. Care must be taken not to allow the acetone on the SOI wafers to dry while transferring the wafers between beakers for cleaning, because this will make the Au debris and resist scum stick onto the wafers, where it is very difficult to remove in the subsequent cleaning steps. The left-hand side of Figure 3-9 shows a picture of the silicon posts with Cr/Au caps after the lift-off. The Au color will be a distinct gold/yellow when observed under the microscope. The right side of Figure 3-9 shows the loss of some silicon posts (< 5%) due to the energy of the ultrasonic agitation. Figure 3-10 is an SEM micrograph showing the Cr/Au cap on the top of a silicon post.

Between steps 8 and 9, the dicing of the SOI wafers is carried out in the ICL packaging room. The wafers are first coated with AZP 4620 thick resist (followed by a 1/2 hr prebake at 90°C) to protect the silicon posts and Cr/Au caps prior to the die-saw. Before beginning the die-saw, it is necessary to check if the correct blade (thick silicon blade – 220  $\mu$ m) is on the spindle and that it is clamped properly. The wafer must also be mounted carefully on the adhesive tape to minimize air gaps between the bottom of the wafer and the tape. If there are large air gaps, the wafer piece will shift or lift during the die-sawing process, and this will lead to both wafer and blade damage. All the above precautions are necessary to make clean cuts and for safety reasons. The standard cutting speed for silicon wafers (0.0031 inches/sec) is used [8].

After die-sawing the wafer into 32mm x 32mm chips, the protective photoresist on the chips is removed using acetone. The chips are then rinsed with methanol, IPA, and water in the EML solvent hood.

Prior to the HF release of the silicon posts on the SOI wafers in step 9, a test is conducted on dummy silicon chips with gold-capped posts to see how the Cr/Au caps withstand HF

attack. This is important because HF is used to release the posts from the substrate, and it is necessary that the Cr/Au caps not be removed in the process. The Cr/Au caps are necessary for the solder to wet and for the self-assembly of the posts to take place. It is found in literature [13] that Au is not etched by HF, while for Cr films, some peeling may be observed. The objective of the test is to determine if the Cr adhesion layer can withstand the HF long enough for the buried oxide layer to be etched and the posts released, without peeling off and lifting off the Au cap with it. Posts without Au caps are rendered useless because they will not be wetted, and these constituted a large proportion of the posts in early batches when little was known then about the effect of the acids on the caps.

The dummy silicon chips, which had etched posts capped with Cr/Au, were subjected to the release and cleaning steps that they would undergo under several cleaning scenarios, such as the  $H_2SO_4$  clean, HF release, and the exposure to the water/dilute acetic mixture (flux used in the solder coating and assembly). The  $H_2SO_4$  cleaning protocol is for removing organics which may impede solderability, while the water/dilute acetic mixture acts as a flux for removing oxides on the solder during the solder coating and selfassembly processes. Figure 3-11 shows the time characterization of the effect of HF on the posts' Cr/Au caps.

It is optimal to minimize the amount of acid used and the time involved, so that the parts can be easily and quickly cleaned or diluted to a level that will not attack the Cr/Au caps. The etch rate for thermally grown wet oxide using concentrated 49% HF is 2.4  $\mu$ m/min [13] and based on this etch rate, it should take about 5 minutes to etch laterally from the edge of the post to its center. However, the original HF release process using a shallow level of HF on the SOI die in a small beaker showed the oxide etched to completion (observable by the change in color) in about 3 minutes. This suggests that the etch rate is much faster than that listed in [13]. Another approach to minimize the amount of HF

used (by using HF vapor) did not work well since one needed to lift the cover occasionally to inspect if the oxide had been etched and this allowed the fumes to escape, making the etch very difficult to control or characterize. In principle, it worked essentially like a wet etch since the HF vapor (high vapor pressure) condenses onto the surface of the SOI die. Also, the etch rate across the die is not uniform, and this could be related to the (fluctuations in) circulation of HF fumes within the beaker.

The HF vapor method inspired the use of the droplet approach in which a few drops of HF are released using a plastic pipette onto the die surface. The advantages of this method are as follows: Firstly, only a minute amount of HF is used, thus allowing the HF to be contained on the surface of the die itself. Secondly, there is much less HF introduced into the dilution beaker since most of the HF droplet on the die either etched (reacted with) the oxide or evaporated inside the acid hood. Thirdly, the posts will stick onto the surface after release and can then be rinsed with water into the dilution beaker. The water from the beaker is extracted using a pipette and successively rinsed with fresh DI water to dilute the HF. No posts are lost during the transfer compared to previous methods in which many released posts floated off the top of the die into the HF bath due to the liquid movements during the transfer between beakers. In the previous methods, it was then a risk to try to retrieve these posts because it meant introducing more acid into the dilution beaker, which would subject the caps to more aggressive acid attack since it will take a longer time to neutralize. It has been observed that it does not require the oxide layer to be completely etched for the posts to be released. The posts will be released after 1 min in HF, and the oxide layer is still clearly present. This could be attributed to the HF attacking the silicon/oxide interface much more rapidly than the field oxide layer. This is positive news with regard to the integrity of the Cr/Au caps on the posts since the HF release time has been reduced from the original 3 minutes to 1 minute, resulting in a lower loss of Cr/Au caps.

The pH of the water in the vial containing the posts needs to be as close to neutral as possible because prolonged storage in dilute HF can lead to peeling of the Cr/Au caps. The successive dilution steps take a long time, but it is necessary too with regard to safety reasons during future handling. As a result, the pH of the water in all the bottles and vials

containing the posts is always checked with pH paper before the containers leave the fab for the group lab for the solder coating and assembly process.

Figure 3-12 shows a picture of the posts after they have been released. Figure 3-13 shows evidence of the gold cap as can be seen by the rim at the top of the posts (circled). Figure 3-14 shows further evidence that the gold cap is still intact, as can be seen by the bright yellow ring at the top of the posts.

Figure 3-13: Dimensions of silicon posts and evidence of gold cap

#### **3.1.2 Substrate fabrication**

The process flow for the substrate fabrication is shown in Figure 3-15 (the masks are described in Chapter 2).

The starting materials are 4" Pyrex wafers of 700 µm thickness. In step 1, the pyrex wafers are put into the HMDS oven in the TRL for a 15 minute dehydration bake to dry off the water. Next, the wafers are primed with HMDS, which is especially necessary to promote adhesion since glass is hydrophilic. Recipe 5 in the TRL HMDS oven (10 secs HMDS dispense) is used which gives a photoresist contact angle of  $72^{\circ}$  after the bake, exposure and development. AZ 5214 image reversal photoresist is used, and since it is a negative photoresist, exposed areas remain after development. After allowing the wafers to cool for five minutes, AZ 5214 resist is dynamically dispensed onto the wafer in the TRL coater at 500 rpm for 6 secs, followed by spreading of the resist at 750 rpm for 6 secs, and finally a spin at 4500 rpm for 30 secs. The thickness of the resist is about 1.2  $\mu$ m. After a 30 min softbake at 95°C, the wafers are exposed for 1.5 secs using the EV1 in step 2. The mask used is the one for patterning the interconnect lines as seen in Figure 2-2. Following that is a 30 min post-exposure bake at 95°C and then a 45 sec flood exposure (without mask) using the EV1. Finally, the resist is developed in AZ 422 for about 65 secs until the pattern becomes clear. The wafers are then rinsed with water for 3 mins after the development. No further post-bake is necessary.

Step 3 is the electron beam evaporation of a 20 nm Cr / 200 nm Au / 20nm trilayer onto the above pyrex wafers using the TRL ebeam. The top Cr layer acts as an adhesion layer for the top silicon dioxide layer which is subsequently deposited in Step 5. If the top Cr layer is not present, the silicon dioxide layer will not adhere well to the Au and water will seep in during any subsequent photolithography development and wet processing steps. Step 4 is the metal lift-off of the Cr/Au/Cr using acetone, methanol, IPA and water. Ultrasonic agitation is not necessary for this lift-off process, and in fact, it is observed that the substrates are cleaner (with less residual metal particles) without having gone into the ultrasound bath.

Step 5 is the deposition of the dielectric layer onto the patterned pyrex wafers using the TRL Plasmaquest, which is an Electron Cyclotron Resonance (ECR) enhanced Reactive Ion Etcher (RIE) and Chemical Vapor Deposition (CVD) system. Either silicon dioxide or silicon nitride can be used, but the following process description will only be on

silicon dioxide since more processing has been done with it. The silicon dioxide layer makes the field non-wettable so that the solder will only coat selectively on the gold sites that have been exposed (it has been demonstrated later in a modified process that the silicon dioxide layer is not necessary since the Cr is not wetted by solder). For ECR-CVD depositions, the temperature should be set to 80° C [8]. A cleaning step using the recipe <EtchCln> is run for 600 secs to clean the chamber prior to beginning the deposition, and after every micron deposited. If the deposited material is allowed to accumulate on the sidewalls of the chamber, it will start flaking once it becomes too thick. The flakes or particles will fall off and contaminate the substrates during the deposition, which will result in a poor non-uniform coating and stresses in the film. The silicon dioxide film is deposited as a result of the reaction between silane (SiH<sub>4</sub>) and oxygen, and the recipe used is <SiO2-dep> which is given in Table 3-5. Step 1 is the standby step, and step 2 is a transient step which is usually added to allow the ECR power to stabilize and ramp up before the deposition in step 3. For CVD using the Plasmaquest, only ECR is used and one has to adjust the microwave tuning stubs during the deposition to ensure that the reflected power is less than 10 watts [8].

| Processing parameters              | Step 1        | Step 2          | Step 3 |

|------------------------------------|---------------|-----------------|--------|

| O <sub>2</sub> (sccm)              | 12            | 12              | 12     |

| SiH <sub>4</sub> (sccm)            | 105           | 105             | 105    |

| Pressure (mtorr)                   | 20            | 20              | 20     |

| ECR system (watts)                 | 0             | 10              | 200    |

| Chuck temperature (°C)             | 80            | 80              | 80     |

| Step processing time               | 30            | 5               | 440    |

| (sec)                              |               |                 |        |

| Table 3-5: <sio2-dep> r</sio2-dep> | ecipe, ECR-CV | D (Plasmaquest) |        |

The process is first run on a 4" plain Si dummy wafer to determine the deposition rate by measuring the film thickness using the TRL Nanospec. Since the substrates are pyrex wafers, they cannot be used for film thickness characterization because they are transparent, as is the silicon dioxide layer. The Nanospec has a precision

microspectrophotometer head, which can measure in the wavelength range of 370 to 800nm, using a computer-controlled grating monochromator, photomultiplier tube detector, and amplifier [23]. When the MEAS key is pressed, the spectrophotometer head scans, generating a corrected spectrum by computing a ratio to a bare silicon reference previously stored. The resulting spectral data is then analyzed by the computer, which determines the exact film thickness corresponding to the interference pattern [14]. By dividing the average film thickness by the process time, the deposition rate for the recipe is found to be 6.82 A/sec. For a film thickness of 300nm, a process time of 440 secs in step3 is required.

Steps 6 and 7 show the photolithography on the substrates in preparation for the final etch to the gold receptor sites. The substrates are primed with HMDS recipe 5 (10 secs HMDS dispense) following a 15 minute dehydration bake. OCG 825 is used, which is a positive photoresist. After allowing the wafers to cool for five minutes, OCG 825 resist is dynamically dispensed onto the wafer at 500 rpm for 6 secs, followed by spreading of the resist at 750 rpm for 6 secs, and finally a spin at 3000 rpm for 30 secs. The thickness of the resist is about 1  $\mu$ m. After a 30 min softbake at 95°C, the wafers are exposed for 2 secs using the EV1. The mask used is the one for patterning the gold receptor sites. The resist is then developed in OCG 934 1:1 for about 55 secs until the pattern becomes clear. The wafers are then rinsed with water for 3 mins and spun dry before a 30 min postbake at 95°C.

The silicon dioxide layer can either be dry or wet etched in step 8. For RIE using the Plasmaquest, both ECR and RF are used and as before in the CVD step, and one has to adjust the microwave tuning stubs during the etch process to ensure that the reflected power is less than 10 watts [8]. For plasma etching of silicon dioxide, recipe <etchSiO2>, shown in Table 3-6, is used. Steps 1, 2, and 3 are the standby, transient, and etch steps respectively. The etch rate for this recipe is about 7.84 A/sec as determined by etching the previous dummy silicon wafer and measuring the remaining film thickness using the Nanospec. To ensure that the silicon dioxide on top of all the gold receptor sites is fully etched, the process time is extended to 150% of the calculated required time. The overetch does not result in undercutting of the oxide since the plasma etch is directional

in nature due to the RF source [11]. Alternatively, the silicon dioxide can also be etched using BOE. This is carried out in a water bath with a degas option in order to remove air bubbles, which may form at some of the receptor sites and impede the etch. The etch is complete once the end contact pads on the substrate change color from violet (silicon dioxide on Cr) to grey (Cr only), and this takes about 50 secs. The etch must be timed carefully and the substrates must be rinsed well to prevent further under-cutting of the oxide.

| Processing parameters                | Step 1       | Step 2 | Step 3 |

|--------------------------------------|--------------|--------|--------|

| $O_2$ (sccm)                         | 4            | 4      | 4      |

| CF <sub>4</sub> (sccm)               | 40           | 40     | 40     |

| Pressure (mtorr)                     | 20           | 20     | 20     |

| ECR system (watts)                   | 0            | 1      | 100    |

| RF system                            | 0            | 20     | 20     |

| Chuck temperature (°C)               | 25           | 25     | 25     |

| Step processing time (sec)           | 30           | 5      | 450    |

| Table 3-6: <etchsio2>, RI</etchsio2> | E (Plasmaque | st)    |        |

The second part of Step 8 involves the etching of the top Cr layer at the receptor sites to expose the underlying Au. By putting the substrates into the asher for 3 hrs, the Cr layer on top of the Au receptor sites can be removed. Finally, the substrates are coated with thin resist for protection and diced into chips using the die-saw.

#### **3.1.2.1** Modified substrate fabrication

The solder coating and self-assembly experiments uncovered problems with the substrates produced using the original process flow for substrate fabrication. The diagnosis of these problems is described in Chapter 4, and the motivation behind the process change will start in Section 4.3.1. The resulting design is shown in Figure 3-16, which shows the modified process flow for the substrate fabrication. This is the eventual

process used in the fabrication of the substrates, but one should note that this process flow should not be considered the final solution for the DEP-based cell trap device.

The processes are almost the same as the previous one (Figure 3-15) except for the use of standard OCG 825 positive resist for a metal lift-off process from step 5 onward, the electron beam evaporation of a Cr/Cu/Au stack in step 7, and the omission of a deposited oxide layer. The photolithography step for the OCG 825 resist is the same as in the original process described earlier, except for the final spin speed which is at 2000 rpm to give a thickness of about 1.2  $\mu$ m. The mask used is the one for patterning the gold receptor sites. In step 7, the thickness of the metal stack is 30nm Cr : 150nm Cu : 20nm Au.

## **3.2** Fabrication issues

The following are some issues uncovered in the course of fabricating the posts and substrates, and this section discusses the steps to either solve or circumvent the problems.

#### Etching of platinum

Platinum is a noble metal that is very difficult to etch. Initially, the approach was to etch circular patterns on the deposited platinum on the SOI, and then cover the platinum caps with photoresist for the DRIE step. The platinum was etched using dilute aqua regia (HNO<sub>3</sub> : HCl :  $H_2O = 1.8.7$ ) at 65°C; however, a layer of scum often appeared on different regions of the wafers. The scum is basically photoresist and un-etched Ti, which is due to the HNO<sub>3</sub> attacking the resist causing parts of it to delaminate. Also, since the concentration of HNO<sub>3</sub> is high, the Ti will be partially passivated because of heavy oxidation once the upper layer of Pt has been etched (however, the HCl will dissolve some of the Ti). Due to the presence of the scum, some regions get etched faster than others, and at the same time, there is a lot of lateral under-cutting, which gives rise to severely under-sized (5 µm diameter) Ti/Pt caps. The best way to pattern platinum is to use a lift-off process. However, due to machine and process incompatibility in the TRL, this method cannot be used. Subsequently, the Pt wet etch process was discarded in favor of the self-aligned process as shown earlier in steps 5 to 8 of Figure 3-3.

#### Etching of silicon dioxide layer

The wet etching of silicon dioxide using BOE, if not timed or controlled properly, will lead to the under-cutting of the oxide layer as shown in Figure 3-17. Despite the fact that there is usually a minute amount of under-cutting even under the best circumstances, wet etching of the oxide is preferred over the dry etch using Plasmaquest. This is because the etch differed greatly across the substrate, which becomes very evident after etching the top Cr layer with the chrome etchant CR-7 (Figure 3-18). The cause is unknown; however, it has been speculated that it might be due to the inter-digitated metal lines charging up during the etch inside the Plasmaquest chamber due to the RF.

#### Etching of top Cr adhesion layer

The chrome etchant CR-7, with an etch rate of 110nm/min [13], was originally used to etch the top Cr layer at the receptor sites to expose the underlying Au. However, since the top Cr layer is only 30nm thick, the etch proceeded very quickly and a significant amount of under-cutting in an erratic manner is observed as seen in Figure 3-18. There is a dearth of information on the dry etching of Cr, but nevertheless, discussions with staff members of the MTL yielded some information on Cr being etched by an oxygen plasma ash, albeit slowly. The Cr dry etch approach was taken, which does not result in any under-cutting of the Cr. Since the Au and SiO<sub>2</sub> layers are not etched by the oxygen plasma, the end-point for the Cr dry etch is not critical.

Figure 3-18: Extreme variations in the under-cutting of Cr using a CR-7 wet etch (after the oxide dry etch)

# Chapter 4 Solder Technology