### The Design of a High Efficiency RF Power Amplifier for an MCM Process

by

James Noonan

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Engineering in Computer Science and Engineering

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

May 2005

© James Noonan, MMV. All rights reserved.

The author hereby grants to MIT permission to reproduce and distribute publicly paper and electronic copies of this thesis document in whole or in part.

| Author                                                     |

|------------------------------------------------------------|

| Department of Electrical Engineering and Computer Science  |

| May 19, 2005                                               |

| Certified by                                               |

| Doug White                                                 |

| Principal Member of the Technical Staff, Draper Laboratory |

| Thesis Supervisor                                          |

| Certified by                                               |

| Joel Dawson                                                |

| Assistant Professor                                        |

| Thesis Supervisor                                          |

| Accepted by                                                |

| Arthur C. Smith                                            |

| Chairman, Department Committee on Graduate Students        |

### The Design of a High Efficiency RF Power Amplifier for an MCM Process

by

James Noonan

Submitted to the Department of Electrical Engineering and Computer Science on May 19, 2005, in partial fulfillment of the requirements for the degree of Master of Engineering in Computer Science and Engineering

#### Abstract

In this thesis, I addressed issues arising in the design of a high efficiency RF power amplifier for the Draper Laboratory multi-chip module (MCM) process. A design for a 2.3 GHz PCB amplifier using an enhancement-mode pHEMT device that achieves 68.9% PAE at 30 dBm output power is presented. Analysis of heat management, die connection parasitics, and transmission line structures in the context of the MCM process is performed to show that a similar design could realistically be adapted to the MCM process with possible performance enhancement.

Thesis Supervisor: Doug White Title: Principal Member of the Technical Staff, Draper Laboratory

Thesis Supervisor: Joel Dawson Title: Assistant Professor

#### Acknowledgments

First and foremost I would like to thank Doug White, my advisor at Draper Laboratory. Doug's vast experience and patient, thorough explanations made this thesis an incredible learning experience. I walked away from almost every conversation we had having learned something new about electrical engineering. This entire work was guided by his extensive research and comprehensive understanding of high efficiency amplifier design.

I would also like to thank Professor Joel Dawson for providing feedback and encouragement throughout the year.

I would like to thank Jay Bruso at Draper for showing me the ropes of RF engineering and for always being available to answer questions and help bail me out of various crises. Thanks to fellow Draper students Jim Warren, Dian Chen, and Nancy Sun for offering encouragement and solidarity during the occasional long day at Draper. And thanks to my (many) office-mates who made working in all three of the offices we were moved around to this semester more pleasant.

Many thanks to the amazing technicians at Draper for assembling the first and only circuit I have ever tested that worked the first time it was turned on. Thanks also to Microwave Circuit Technology for doing a quick, thorough job on the board fabrication.

Last but not least, thanks to my family and friends for your constant support.

This thesis was prepared at The Charles Stark Draper Laboratory, Inc., under Internal Company Sponsored Research Project: High Efficiency RF Circuits.

Publication of this thesis does not constitute approval by Draper or the sponsoring agency of the findings or conclusions contained herein. It is published for the exchange and stimulation of ideas.

James Noonan

## Contents

| 1        | Intr | oducti   | on                                 | 15 |

|----------|------|----------|------------------------------------|----|

|          | 1.1  | Multi-   | Chip Modules                       | 16 |

|          |      | 1.1.1    | The Draper MCM-D Process           | 16 |

|          | 1.2  | RF Pc    | ower Amplifiers                    | 18 |

|          |      | 1.2.1    | Topologies                         | 18 |

|          |      | 1.2.2    | Class E Power Amplifiers           | 20 |

|          |      | 1.2.3    | Class F Power Amplifiers           | 22 |

| <b>2</b> | Tra  | nsistor  | Selection                          | 25 |

|          | 2.1  | RF Pc    | ower Transistors                   | 25 |

|          |      | 2.1.1    | Enhancement-Mode pHEMTs            | 26 |

|          |      | 2.1.2    | Heterojunction Bipolar Transistors | 27 |

|          | 2.2  | Transi   | stor Selection                     | 27 |

|          |      | 2.2.1    | Supply Voltage                     | 29 |

|          |      | 2.2.2    | ATF511P8 Device Model              | 31 |

| 3        | MC   | M Hea    | at Conduction for RF Circuits      | 33 |

|          | 3.1  | Heat I   | Flow in an MCM                     | 34 |

|          | 3.2  | Therm    | nal Vias                           | 37 |

|          |      | 3.2.1    | Practical Considerations           | 40 |

|          | 3.3  | Summ     | ary                                | 41 |

| 4        | Par  | asitic 1 | Effects of Die Connections         | 43 |

|          | 4.1 | Parasitics of a Surface Mount Package 44 |

|----------|-----|------------------------------------------|

|          | 4.2 | Parasitics in the MCM 46                 |

|          |     | 4.2.1 The Draper MCM-D Process           |

|          |     | 4.2.2 Series Inductance and Resistance   |

|          |     | 4.2.3 Parallel Capacitance               |

|          | 4.3 | Summary 51                               |

| <b>5</b> | Tra | nsmission Line Structures 53             |

|          | 5.1 | Transmission Line Structures             |

|          | 5.2 | Basic Transmission Line Simulations      |

|          |     | 5.2.1 Microstrip                         |

|          |     | 5.2.2 Stripline                          |

|          |     | 5.2.3 Coplanar Waveguide With Ground     |

|          | 5.3 | Variations on Basic Structures           |

|          |     | 5.3.1 Embedded Microstrip                |

|          |     | 5.3.2 Unbalanced Stripline               |

|          | 5.4 | Summary                                  |

| 6        | PCI | B Power Amplifier Design 63              |

|          | 6.1 | Design Tools                             |

|          | 6.2 | Design Procedure                         |

|          | 6.3 | Numerical Impedance Optimization         |

|          | 6.4 | Microstrip Network Designs               |

|          |     | 6.4.1 Load Network Design                |

|          |     | 6.4.2 Input Network Design               |

|          |     | 6.4.3 Bias Network Design                |

|          | 6.5 | Momentum Simulations                     |

|          | 6.6 | Summary of Simulation Results            |

|          | 6.7 | Layout                                   |

| 7 | PCI | 3 Amplifier Testing | 81 |

|---|-----|---------------------|----|

|   | 7.1 | Test Setup          | 81 |

|   | 7.2 | Device Turn-On      | 82 |

|   | 7.3 | Tuning              | 83 |

|   | 7.4 | Test Results        | 84 |

|   | 7.5 | Summary of Results  | 85 |

| 0 | C   |                     | 00 |

| 8 | Con | clusion             | 89 |

# List of Figures

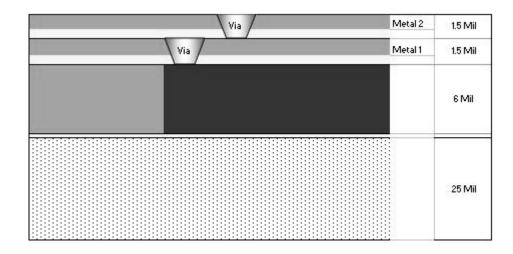

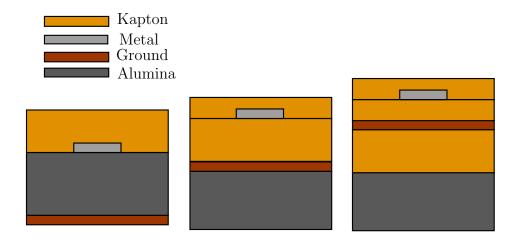

| 1-1 | MCM-D Cross Section                                                     | 17 |

|-----|-------------------------------------------------------------------------|----|

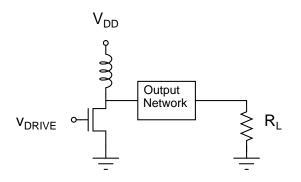

| 1-2 | General RF Power Amplifier Topology                                     | 18 |

| 1-3 | Class E Voltage and Current Waveforms                                   | 21 |

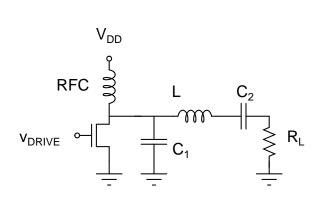

| 1-4 | Lumped Element Class E Topology                                         | 21 |

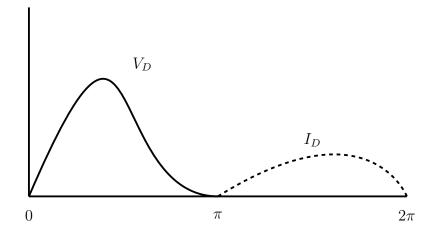

| 1-5 | Class F Voltage and Current Waveforms                                   | 22 |

| 1-6 | Class F Topology Using Resonant Tank and $\lambda/4$ Line               | 23 |

| 3-1 | Heat Flow in an MCM                                                     | 35 |

| 3-2 | Log(Mean Time to Failure) vs. Temperature                               | 37 |

| 3-3 | Placement of Thermal Vias in an MCM                                     | 38 |

| 3-4 | Change in Temperature Across Substrate vs. Thermal Via Area $\ .\ .\ .$ | 40 |

| 3-5 | Copper Tungsten Area Under Die                                          | 41 |

| 4-1 | X-rays of the ATF501P8 Surface Mount Package                            | 44 |

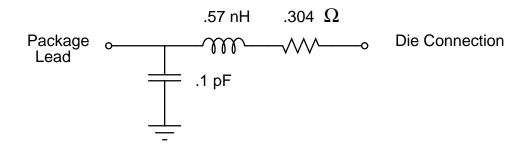

| 4-2 | Parasitic Elements for a Bondwire Connection                            | 45 |

| 4-3 | Agilent Model for the ATF501P8 Gate Connection                          | 45 |

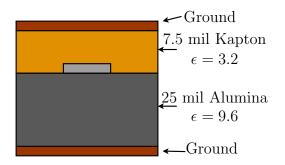

| 4-4 | MCM Cross Section                                                       | 47 |

| 4-5 | Die Connections to Various Layers                                       | 48 |

| 4-6 | Parallel Capacitance Resulting From Via Pads                            | 50 |

| 5-1 | Basic Transmission Line Structures                                      | 54 |

| 5-2 | Variations on Basic Transmission Line Structures                        | 55 |

| 5-3 | Geometries for Microstrip Structures                                    | 56 |

| 5-4 | Geometries for Stripline Structures                                     | 56 |

| 5 - 5 | Embedded Microstrip Structures                                      | 59 |

|-------|---------------------------------------------------------------------|----|

| 5-6   | Unbalanced Stripline Structure                                      | 60 |

| 6-1   | ATF511P8 Gate Package Parasitics                                    | 65 |

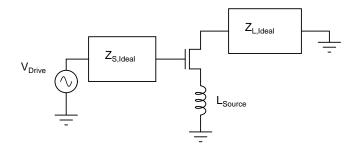

| 6-2   | Schematic Representation of Numerical Optimization Setup $\ldots$ . | 66 |

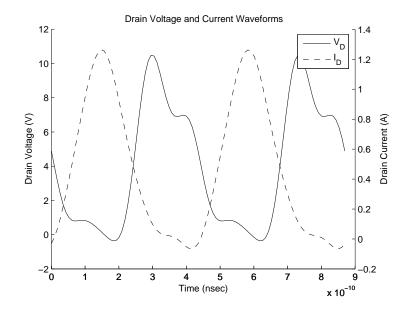

| 6-3   | Time Domain Drain Voltage and Current Waveforms                     | 67 |

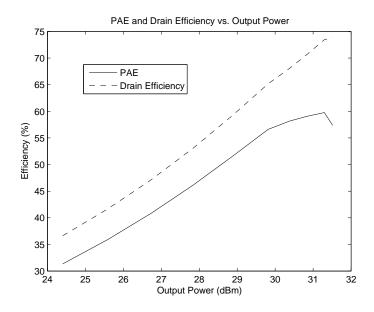

| 6-4   | Comparison of PAE and Drain Efficiency                              | 69 |

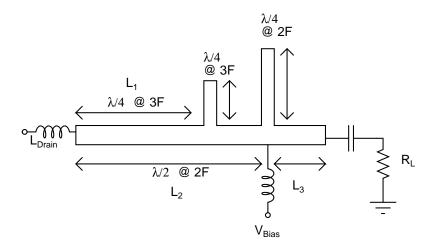

| 6-5   | Load Network Topology                                               | 70 |

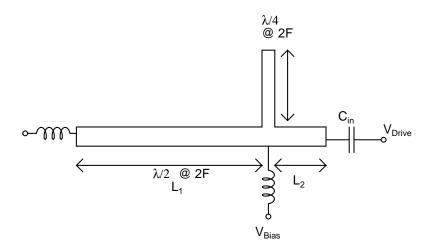

| 6-6   | Input Network Topology                                              | 72 |

| 6-7   | Input Match With $\lambda/4$ Transformer                            | 73 |

| 6-8   | Input Match With $\lambda/4$ Transformer and Series Capacitor       | 73 |

| 6-9   | Output Network Momentum Layout                                      | 77 |

| 6-10  | $V_{DG}$ Time Domain Waveforms for Two Bias Conditions              | 78 |

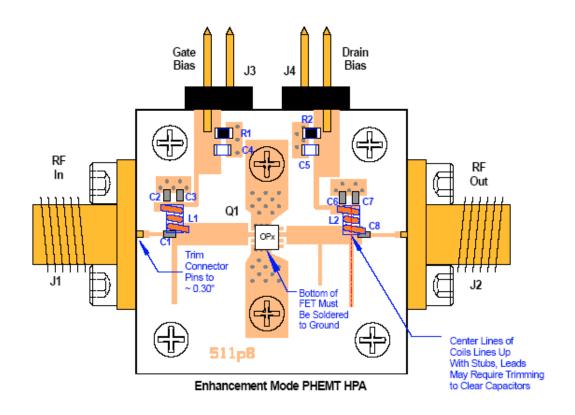

| 6-11  | Full PCB Amp Layout                                                 | 80 |

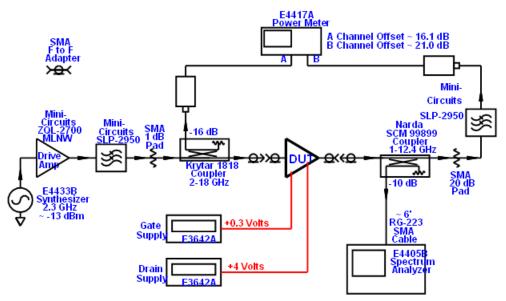

| 7-1   | E-pHEMT Amplifier Test Setup                                        | 82 |

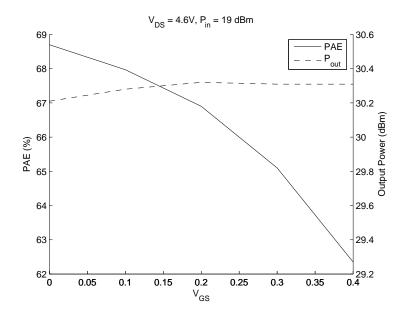

| 7-2   | PAE and $P_{out}$ vs. $V_{GS}$                                      | 85 |

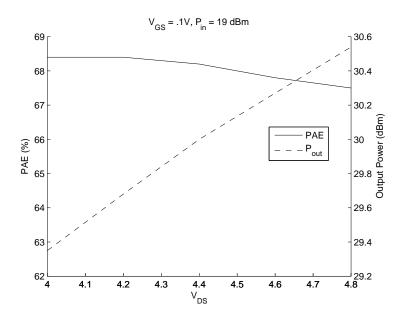

| 7-3   | PAE and $P_{out}$ vs. $V_{DS}$                                      | 86 |

| 7-4   | PAE and $P_{out}$ vs. $P_{in}$                                      | 86 |

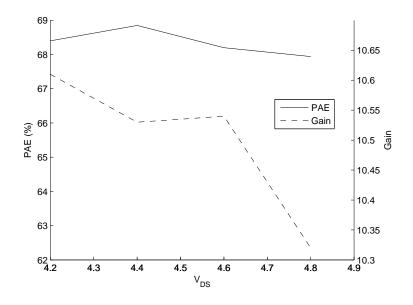

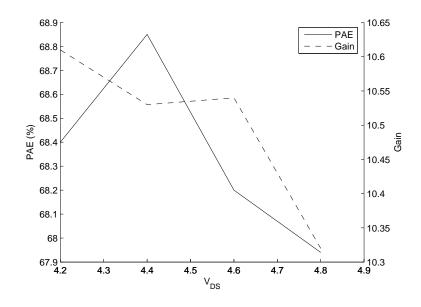

| 7-5   | PAE and Gain vs. $V_{DS}$                                           | 87 |

# List of Tables

| 3.1 | Thermal Conductivities                                                         | 35 |

|-----|--------------------------------------------------------------------------------|----|

| 3.2 | Material Properties                                                            | 38 |

| 6.1 | ATF511P8 Optimized Numerical Impedances                                        | 67 |

| 6.2 | ATF511P8 Input and Output Network Impedances                                   | 75 |

| 6.3 | Comparison Of Amplifier Performances with Ideal and Microstrip Net-            |    |

|     | works                                                                          | 75 |

| 6.4 | Power Loss in Microstrip Networks                                              | 76 |

| 6.5 | Momentum Simulations of Amps Under Different Bias Conditions                   | 77 |

| 6.6 | Power Loss in Microstrip Networks: Linear Sim. vs. Momentum                    | 78 |

| 7.1 | Performance for Maximum PAE with Pout $> 30$ dBm $\ldots \ldots \ldots \ldots$ | 84 |

### Chapter 1

### Introduction

Progress in the field of portable communication devices has resulted in a demand for small and efficient electronics. Modern communication devices like cellular phones require electronics for a wide variety of functions, from digital computation to transmission and reception of radio frequency (RF) signals. Such a variety of functions calls for a variety of integrated circuits, fabricated in different processes with different materials. These electronics must all be incorporated with larger elements like a battery and an antenna into a small, hand-held device. Combining separate packaged chips can quickly take up a lot of space. On the other hand, fabricating all of these electronics onto a single integrated circuit using a single process and material will result in sub-optimal performance from components better suited to other processes.

Multi-chip module (MCM) technology provides a solution to the problem of incorporating a variety of electronics into a small volume. In an MCM fabrication process, bare dice are combined onto a common substrate and interconnected, allowing a variety of functional blocks to exist on a single chip. In addition to occupying a smaller area, the parasitic effects associated with the packaging of chips and discrete components are reduced.

Another concern in portable communication devices is power consumption. High power consumption results in large batteries and/or short battery lifetimes. Efficient electronics maximize the performance of a device given the constraints of a battery. The circuit within such a device that typically consumes the most power (sometimes as much as half of the DC power supplied) is the RF power amplifier, which converts DC power from the battery into the RF signal that is transmitted through an antenna. Maximizing the efficiency of the power amplifier can allow for reduction in battery size, prolonged battery life, increased signal strength, or a combination of the three. Efficient amplifiers also generate less heat, increasing device lifetime and reliability.

The work described in this thesis was completed at Draper Laboratory. Draper is currently doing research into both MCM's and high efficiency power amplifiers. This thesis combines these two research areas by analyzing issues arising in the design of high efficiency RF power amplifiers for an MCM process.

#### 1.1 Multi-Chip Modules

As stated before, the idea behind MCMs is to attach and interconnect multiple bare dice and passive components onto a single substrate, allowing IC's fabricated in different processes to exist on the same compact circuit. For example, in a cellular phone, one must combine digital electronics with high power RF electronics in a small space. Ideally, one might want to use a CMOS process on a silicon substrate for the digital electronics while using a GaAs power FET for RF amplification. Using separate packaged parts for each of these functions quickly takes up precious space inside the device. MCM technology allows these circuits to be combined into a small area while preserving the functional benefits derived from the different fabrication processes.

#### 1.1.1 The Draper MCM-D Process

The specific process this work will look at is Draper Laboratory's MCM-D (Multi-Chip Module-Deposited) process. This process uses a 25 mil thick alumina substrate with multiple Kapton film layers above it. The dice are attached to the substrate and contained within the lowest Kapton layer, which is 6 mils thick. Interconnects are done in the layers above, each of which consists of a 1 mil thick Kapton film and .5 mils of adhesive. The copper metalization is approximately .2 mils thick.

A significant challenge posed by the integration of RF power devices into MCMs is

Figure 1-1: MCM-D Cross Section

the management of heat. Incorporating a variety of devices into a small volume makes it difficult to conduct heat away from the devices. Heat can have a significant effect on the electrical performance and operational lifetime of a device. Temperature variations can also cause different materials to physically expand or contract by different amounts. These variations can easily cause structural damage in an MCM, where a variety of materials are housed in close proximity. Chapter 3 of this thesis explores some of the thermal issues that will arise in incorporating RF electronics in an MCM.

One of the main potential benefits of MCM technology is the reduction of the parasitic effects associated with die connections. In packaged devices, the die is typically connected to leads on a package through thin bondwires which can introduce parasitic inductance and resistance. The package and the leads themselves can also introduce capacitive parasitic effects. These parasitic effects can be particularly problematic at RF frequencies. MCM technology offers the potential to bring interconnects close to the bare die for low impedance connections. Chapter 4 of this thesis will use simulations to show the reduction in parasitic effects that can be achieved in an MCM over a surface mount package.

At high frequencies, the behavior of an RF network is largely defined by its physical dimensions and by the dielectric properties of the materials it resides on. When talking about incorporating RF electronics into a process, it is extremely important to

Figure 1-2: General RF Power Amplifier Topology

understand the RF characteristics that transmission lines will have when fabricated in the process. Chapter 5 of this thesis will explore the electrical properties of various transmission line structures achievable in the MCM process.

In chapter 2, we will identify a transistor suitable for use in an MCM high efficiency power amplifier design to provide a realistic framework for the analyses mentioned above. Chapter 6 will detail the design of a PCB high efficiency power amplifier using this transistor in order to demonstrate a design procedure and evaluate this transistor for use in high efficiency amplifiers. Chapter 7 will describe the testing of this design and give analysis of the results. Chapter 8 will conclude the thesis.

#### **1.2 RF Power Amplifiers**

We will now take a look at RF power amplifiers and how they can be designed for high efficiency operation.

#### 1.2.1 Topologies

An RF power amplifier is a circuit that converts DC power into RF power. In a transmitter, the PA amplifies the outgoing signal to a level sufficient to drive the transmitting antenna. The most common RF power amplifier topology is given in Figure 1-2. The topology consists of a single active device. The drain of the transistor is coupled to the DC power supply through a large inductor (or RF "choke") that

sets the drain bias but acts as an open circuit at high frequencies. The input signal is connected to the gate through a passive impedance network, which provides an impedance match at the fundamental drive frequency and can also provide harmonic impedance characteristics. The drain of the transistor is connected to the load through an output impedance network.

Most RF power amplifiers fit into one of six common classes: A,B,C,D,E, or F. The distinctions between these classes lie primarily in the biasing conditions of the transistor and the design of the output network that couples the drain to the load. Each class has its own strengths and weaknesses, and choosing a class amounts to compromising between various power amplifier figures of merit, which include gain, linearity, and efficiency. For example, Class A and B power amplifiers offer high gain and a wide linear range, but are inefficient. On the other hand, class E and F power amplifiers can achieve high efficiency but do not provide linear amplification. In this application we are mainly concerned with efficiency, so we will look exclusively at Class E and Class F power amplifiers.

We will use Power Added Efficiency (PAE) as our measure of efficiency. PAE is defined as the ratio between the output power minus the RF drive power and the total DC power dissipated from the supply:

$$PAE = \frac{P_{out} - P_{RF}}{P_{DC}} \tag{1.1}$$

For a fixed power gain, the problem of maximizing PAE amounts to minimizing the amount of power dissipated in the transistor, thereby maximizing the amount of power delivered to the load. The power dissipated in the transistor is primarily given by the product of the drain current  $I_D$  and the drain to source voltage  $V_{DS}$ . To maximize PAE, we want to minimize the amount of time during which the transistor simultaneously has a non-zero  $V_{DS}$  and  $I_D$ . We will now look at Class E and Class F power amplifiers to see how this is accomplished.

#### **1.2.2** Class E Power Amplifiers

Class E power amplifiers are members of a class of amplifiers called "switching-mode" power amplifiers. The idea behind switching mode power amplifiers is to drive the transistor hard enough so that it acts like a switch (as opposed to a linear voltage dependent current source). An ideal switch will never simultaneously conduct current and have a voltage across it: while the switch is "on", it conducts current but is a short, so there is no voltage drop, and while the switch is "off", it conducts no current but can support a voltage. If the transistor operates like an ideal switch, the theoretical power dissipation at the drain will be zero.

In reality, transistors do not behave like ideal switches. In operating any transistor, there will be some non-zero switching time associated with charging parasitic capacitances. During these switching times, the transistor simultaneously drops a voltage and conducts current. If the switching time of the transistor is a significant portion of the RF signal period (which it often is at GHz frequencies), then significant power dissipation can occur.

The idea behind Class E amplification is to use an output impedance network at the drain of the transistor to shape the drain voltage and current waveforms to minimize overlap. Theoretical target curves for Class E operation are shown in Figure 1-3. The goal of the Class E design is to achieve a drain voltage waveform that has both zero value and zero slope when the transistor turns on. The zero slope condition assures that the drain voltage will be close to zero around the turn-on time of the transistor, so that even if the voltage and current waveforms overlap, power dissipation will be low. The cost of the increased efficiency encountered in Class E design comes with lowered power gain and increased harmonic distortion.

One possible lumped element topology for a Class E PA is given in Figure 1-4. Analysis and design equations for the Class E PA are given in [12].

Figure 1-3: Class E Voltage and Current Waveforms

Figure 1-4: Lumped Element Class E Topology

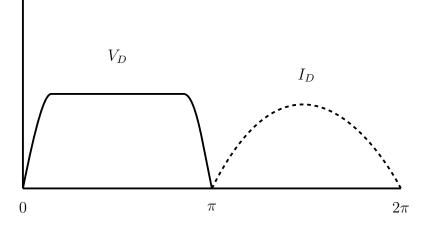

Figure 1-5: Class F Voltage and Current Waveforms

#### 1.2.3 Class F Power Amplifiers

Class F amplifiers are another class of switching-mode amplifiers that use a passive output network to shape the drain voltage waveform. In this case, the goal is a drain voltage waveform that approaches a square wave and a drain current waveform that approaches a half sinusoid. Theoretical Class F waveforms are shown in Figure 1-5. An alternative approach, known as Inverse Class F, uses a square wave in current and a half sinusoid in voltage. Theoretically, these waveforms will not overlap in time, and assuming very large gain, we will approach 100% PAE. In practice, parasitic effects limit our ability to produce ideal waveforms.

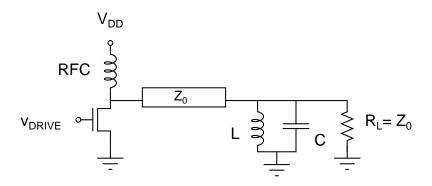

A square wave at frequency  $\omega_0$  contains the fundamental frequency and all odd harmonics of the fundamental. In order to make the drain voltage approach a square wave, the output impedance network presents a high impedance to all of the odd harmonics and a low impedance to all of the even harmonics. One possible Class F topology is given in Figure 1-6 [7]. In this circuit, the parallel LC tank is tuned to the fundamental frequency  $\omega_0$ , with a Q large enough to present an effective short at all multiples of  $\omega_0$ . The key to presenting the proper harmonic terminations for Class F operation lies in the quarter wavelength transmission line connecting the transistor drain to the LC tank. A quarter wavelength transmission line has an input impedance

Figure 1-6: Class F Topology Using Resonant Tank and  $\lambda/4$  Line

proportional to the reciprocal of its load impedance:

$$Z_{in} = \frac{Z_0^2}{Z_L} \tag{1.2}$$

If the transmission line's characteristic impedance is matched to the load impedance, the drain will see the load impedance at the fundamental frequency. At even harmonic frequencies, the transmission line is a multiple of a half wavelength, so the drain will simply see the short circuit presented by the LC tank at the end of the transmission line. At odd harmonic frequencies, the transmission line is an odd multiple of a quarter wavelength, so the drain sees the reciprocal of the short circuit presented by the LC tank, or an open circuit. Thus, we present all odd harmonics with a high impedance and all even harmonics with a low impedance, producing the desired square wave in voltage at the drain of the transistor.

The topology in Figure 1-6 provides an extremely simple and elegant theoretical solution to the Class F problem. Unfortunately parasitic effects make the design impractical at the frequencies of interest. The parasitic inductance at the drain of the transistor will make the length of the quarter wave line look different at different frequencies. Moreover, the design gives no flexibility in tuning the individual harmonic impedances once the impedance at the fundamental is set. In practice, transmission line networks with harmonic traps at some small number of harmonic frequencies are used to get close to a square wave in voltage. Such a design will be described in detail in Chapter 6.

### Chapter 2

### **Transistor Selection**

There are currently a wide variety of RF power transistors available that are suitable for use in high efficiency power amplifiers. The choice of transistor for a given design impacts a broad variety of circuit and system level parameters. The electrical properties of the transistor will determine what power amplifier topologies will be possible or effective. The bias conditions required will affect not only the performance of the amplifier, but also what external circuitry is required to provide those bias conditions. Dimensions of the die and placement of the bond pads will dictate how connections can be made to the die and what parasitic effects those connections will have. Thermal properties of the die will affect heat management needs.

In order to provide a realistic framework for looking at the issues stated above, we must first identify a transistor that is suitable for our design.

#### 2.1 RF Power Transistors

Most popular RF power transistors are fabricated using compound semiconductors like GaAs or SiGe. These materials offer higher electron mobility than silicon and hence better high frequency performance. One of the first popular RF power transistors was the GaAs metal-semiconductor field effect transistor (MESFET) [1]. The primary difference between a MESFET and a standard MOSFET is the use of a Schottky gate junction instead of a standard MOS structure. The Schottky junction serves to lower the input capacitance, making the device easier to drive at high frequencies. An improvement on the MESFET structure came with the pseudomorphic high-electron-mobility transistor (pHEMT). The pHEMT uses an AlGaAs/GaAs heterojunction in the gate to offer better high frequency performance than the MESFET [9]. Both types of devices in their standard forms are "depletion mode" devices, meaning they require a negative gate bias to operate as amplifiers.

The need for a negative gate bias to operate is a serious setback when one is designing for a small battery operated device. There are two main reasons for this. Firstly, in order to provide a negative DC voltage to the gate, one needs to add an additional circuit to the system such as a charge pump or a DC-DC converter, which will take up extra space. The second problem posed by a negative gate bias concerns sequencing the application of bias voltages to the gate and drain. With zero voltage applied to the gate, a depletion mode device is biased in saturation. If the drain power supply is applied before the negative gate supply, the transistor will conduct its saturation current, effectively shorting the power supply to ground. To avoid damaging the transistor or other circuit components, one has to ensure that the negative gate bias will be applied before the drain bias when the device is turned on. Extra circuitry is usually required to accomplish such sequencing.

As a result of the increased circuit area and system complexity imposed by depletion mode devices, there has been much interest in developing RF power transistors that operate with a positive gate bias. Since Draper began looking into high efficiency power amplifier design, a couple of promising new types of transistors have become available as off the shelf parts: enhancement-mode pHEMTs (E-pHEMTs) and heterojunction bipolar transistors (HBTs).

#### 2.1.1 Enhancement-Mode pHEMTs

Enhancement-mode pHEMTs (E-pHEMTS) are pHEMTs that, through careful control of semiconductor layer thickness and composition, do not conduct current with a  $V_{GS}$ of zero and thus can be operated with a single positive supply. E-pHEMTs have only recently begun to become available as discrete packaged components. Most E-pHEMT devices described in the literature operate at low supply voltages, which demand high currents and can make achieving high PAE a challenge. However, some highly efficiency E-pHEMTs have been reported. A 3V E-pHEMT running at 65% PAE at 33 dBm and 1.8 GHz is reported in [14], and a 2.4V E-pHEMT running at 61% PAE at 32 dBm output power and 1.9 GHz is reported in [2].

#### 2.1.2 Heterojunction Bipolar Transistors

Most HBTs are made using GaAs, though more recently some have been made using SiGe. HBTs operate in much the same way as bipolar junction transistors. Instead of using doping to form a standard pn junction, an AlGaAs/GaAs heterojunction is used. This allows for heavy doping in the base, resulting in low base resistance and improved high frequency operation [9]. As with E-pHEMTS, some promising results have been reported for efficient operation of HBTs. A SiGeC HBT running at 72% PAE at .9 GHz with 1W output power is reported in [10], and a GaAs HBT running at 72% PAE at 12 GHz with 1W output is reported in [11].

#### 2.2 Transistor Selection

In the search for a suitable transistor, the following were identified as important criteria:

- 1. Single supply operation

- 2. 30 dBm output capability at 2.3 GHz

- 3. Efficient operation

- 4. Availability of a large signal model

- 5. Available as discrete packaged device

One device that was considered was the SGA-9289, a SiGe HBT from Sirenza Microdevices. The device meets the single supply criteria. The data sheet for this part reported a 1dB gain compression point (P1dB) of 28 dBm around the frequencies of interest. Because switching mode amplifiers are often driven past 1dB of gain compression, it is feasible that this device could achieve the desired 30 dBm output power specification.

Unfortunately there was no non-linear model for the device available at the time this work was completed. Since having devices modeled was beyond the scope of this project, completing a design with this device would have been difficult. Beyond the lack of models, there were other characteristics of the device that made it less than ideal. The power gain reported on the data sheet at 1960 MHz was only 10.8 dB. In our application, we would drive the device hard enough for it to exhibit switching behavior, so we would expect our gain to be lower than this figure. A power gain of 8 or 9 dB would be relatively low and would have a negative effect on PAE. For example, if the amp achieved 8 dB of gain at 30 dBm output power, even if we achieved a drain efficiency (defined as  $\eta = P_{out}/P_{DC}$ ) of 70%, our PAE would only be 59% as a result of our low power gain. The device also has a relatively low supply voltage (3-5V). A low supply voltage requires a high drain current, which will tend to increase power dissipation in the transistor and the output network and lower efficiency. While this device's data sheet does not include data on efficiency, SiGe HBTs are known to be less efficienct than GaAs HBTs [9].

A more promising device found was the ATF511P8, an enhancement-mode pHEMT from Agilent Technologies. Agilent provides a large signal model of the device for use in their Advanced Design System (ADS) software, which is the RF circuit simulator used at Draper. At 2 GHz, the data sheet reports a P1dB of 30 dBm and a gain of 14.8 dB, both of which are high enough for our application. Perhaps most promising of all is the PAE spec of 69%, which is an extremely high figure. All of these criteria made the 511P8 an excellent candidate for the design. Before deciding on this device, however, there were some important issues relating to supply voltage that needed to be addressed.

Agilent offers a similar device, the ATF501P8, which it released as an improvement upon the AFT511P8, claiming the newer die had better thermal properties. In initial simulations, the device model for the 501P8 performed slightly better than the model for the 511P8. However, the ATF501P8 reports slightly lower PAE and P1dB on its data sheet. Since it was unclear which device would ultimately perform better, both are considered in this work.

#### 2.2.1 Supply Voltage

While the 511P8 is rated to support a maximum DC  $V_{DS}$  of 7 volts, the true upper limit on the power supply for use in a Class E or Class F amplifier would be set by the maximum DC  $V_{DG}$  tolerated, which is 5 volts.  $V_{DG}$  sets the upper bound because our gate bias will have to be near the pinch-off voltage  $(V_P)$  to achieve switchingmode operation.  $V_P$  is the voltage at which the transistor effectively stops conducting current. Biasing the gate near  $V_P$  ensures that the device is truly turned "off" during the negative half cycle of the driving sinusoid and that very little current is conducted. For this device,  $V_P$  is around .3V, so our drain supply is limited to being at most 5V above .3V, or around 5.3V.

Another concern when deciding what maximum supply voltage the device can tolerate is the  $V_{DG}$  breakdown voltage, or the maximum voltage that can exist across the gate and drain terminals during the RF period. The data sheet does not provide this specification for the device, and Agilent was unable to provide it when contacted. The maximum DC  $V_{DG}$  spec of 5V suggests that the drain-gate junction should be able to support at least 10V with RF applied, but it is unclear what maximum voltage the junction can support for safe operation. This is a specification that would have to be watched closely when executing a design.

Beyond the question of what supply voltages the device can tolerate, there are also some system level design requirements imposed by the supply voltage. As stated earlier, one of the goals of Draper's high efficiency amplifier research is to develop efficient technology for use in battery operated communication devices. In such devices, the power amplifier can not be viewed in isolation. Having an efficient power amplifier is all for naught if a DC supply voltage of sufficient power cannot be consistently and efficiently supplied. It was therefore desirable to identify a DC to DC conversion solution that would allow the power amplifier to operate in spite of voltage variations over the lifetime of a battery. In a case where efficiency is a concern, the most common solutions are "buck" and "boost" switching regulators. Buck converters provide a DC output voltage that is lower than their DC input, requiring that the input voltage always remain higher than the DC output. Boost converters do the opposite, requiring the input to stay below the DC output.

The batteries that Draper has worked with in past high efficiency power amplifier designs have an output voltage ranging from 6.8 down to 3.4 volts over the lifetime of the battery. In all cases a supply of above 6.8 volts was used and generated by a single boost converter. Because we would be limited to a 5V maximum supply in this case, a single boost converter would no longer be an option. The two options that remained were using a single buck converter to generate a supply of around 3V, or using a buck and boost converter in series to generate a voltage between 3 and 5 volts. In order to compare these options, a survey of currently available power converters was done.

The most recent high efficiency power amplifier design executed at Draper used an LM 2731 boost converter to supply 7.1V at 400mA. The data sheet for this part suggests that it would run at about 85% efficiency under these conditions. The best option found for a single 3V buck converter was the LTC 1879 from Linear Technology. The data sheet indicates that this part should run at around 88% efficiency when supplying 3V at around 600mA. For a 3-5 volt output solution, Maxim offers the MAX711, a buckboost converter that supplies an adjustable output voltage up to 5.5V with an input voltage range from 1.8 to 11V. This part runs at around 83% efficiency at the power level of interest.

Thus, to operate between 3 and 5V we would have to sacrifice around 2% efficiency in the DC-DC converter over the single boost converter case. Operating below 3V would actually result in a 3% gain in converter efficiency. However, such a low voltage supply would require high currents to supply enough output power, making high efficiency more of a challenge. Therefore, the 3-5V solution was viewed more favorably. It was ultimately decided that the 2% sacrifice in converter efficiency resulting from the low drain supply of the ATF511P8 would be worth the system level benefits of using a single supply device, and this device was chosen as the focus of this thesis.

#### 2.2.2 ATF511P8 Device Model

Some initial simulations were performed to see if the device model could achieve as high performance as the specs on the data sheet. The data sheet gave the following data for a bias of  $V_D = 4.5$ V,  $I_D = 200$ mA:

| Freq  | Gamma Source                                | Gamma Load | Gain  | P1dB  | PAE   |

|-------|---------------------------------------------|------------|-------|-------|-------|

| (GHz) | $\operatorname{Mag}$ , $\operatorname{Ang}$ | Mag, Ang   | (dB)  | (dBm) | (%)   |

| 2.0   | .872, -171                                  | .683, -179 | 15.06 | 30.12 | 66.8% |

| 2.4   | .893, -162                                  | .715, -174 | 14.03 | 29.90 | 64.5% |

It was attempted to reproduce these results using the device model. The impedances listed were presented to the drain and gate of the transistor with ideal numerical impedances. Bias voltages were applied to the drain and gate using ideal RF chokes. Since no mention of harmonic terminations was made in the data sheet, 2nd-4th harmonic impedances were optimized over PAE. The following results were obtained:

| Freq  | Gain | P1dB  | PAE   |

|-------|------|-------|-------|

| (GHz) | (dB) | (dBm) | (%)   |

| 2.0   | 14   | 26    | 46.9% |

| 2.4   | 12   | 26    | 47.2% |

In an attempt to produce better results, the impedances at the fundamental frequencies were then optimized over PAE, yielding:

| Freq  | Gain | P1dB  | PAE    |

|-------|------|-------|--------|

| (GHz) | (dB) | (dBm) | (%)    |

| 2.0   | 13.7 | 26    | 50.7%  |

| 2.4   | 12   | 26    | 52.87% |

Since the exact details of the test setup that yielded the data sheet results were not known, it is not surprising that the results could not be duplicated exactly. Nevertheless, the transistor model operated with significantly lower P1dB and PAE than was suggested on the data sheet. Agilent was contacted about this, and they said that, due to the way the model was created, the PAE results on the data sheet may not be achievable in simulation. This would have to be kept in mind when using the model to design a high efficiency amplifier.

### Chapter 3

# MCM Heat Conduction for RF Circuits

In the design of RF power circuits, heat management is always an important concern. Semiconductor devices like FETs typically have some maximum channel temperature above which the device fails. Even if this temperature is never exceeded, the mean time to failure (MTTF) of a device typically drops exponentially with temperature, so devices are more reliable for longer periods of time at lower temperatures. Heat can also pose structural problems for a circuit. Different materials with different thermal coefficients of expansion (TCE) will swell and shrink by different amounts across different temperatures. High temperatures in a circuit can therefore cause structural deformation resulting in broken connections or short circuits.

Aside from conserving energy from the power source, one of the main benefits of high efficiency power amplifiers is that less power is dissipated as heat in the transistor. But even highly efficient power amplifiers can still generate a significant amount of heat. A 1 Watt power amplifier running at an impressive 70% PAE will still dissipate 430 mW as heat.

When shrinking down electronics into a small volume, heat becomes even more of a challenge. Small power amplifiers still have to dissipate significant amounts of heat, but there is less material to spread the heat into. Heat generation has an increased effect on neighboring components and the system as a whole. Moreover, in the MCM fabrication process, which has strict design rules, one is limited in the types of materials one can choose and the placement of those materials for the conduction of heat. Even if heat can be conducted away from the device, if the device runs at a high temperature, a large heat sink will be required outside of the module to adequately conduct the heat to the ambient. The heatsink could potentially nullify any volumetric gains from reducing the size of the electronics.

#### 3.1 Heat Flow in an MCM

Before looking at thermal issues in an MCM, we will first look at how heat is managed in a conventional surface mount board to provide a mode of comparison. In the case of the ATF501P8 power transistor, the die sits in the package on top of a piece of metal that acts as both the electrical and thermal ground. Most of the heat is generated in the channel at the top of the die, and it must travel through the die to the metal ground. The metal ground is directly connected to ground on the board, and from here the designer can attach heat sinks with large surface areas to absorb heat. Thus, as soon as the heat has passed out of the bottom of the die, it has a low thermal conductivity path out to the heatsinking structure.

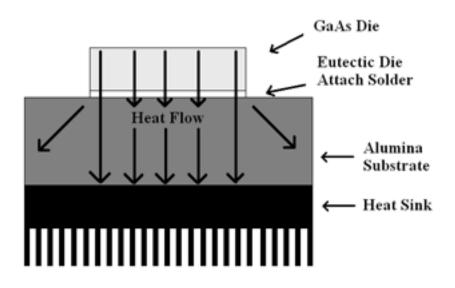

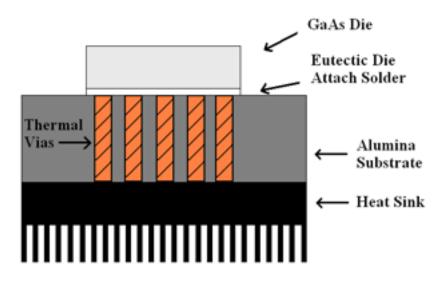

This is not the case in an MCM. Figure 3-1 shows the path that heat takes from the channel in the transistor out to the heatsink. In this case, the GaAs die is attached to a 25 mil thick alumina substrate with a thin layer of eutectic die attach solder. The 25 mils of alumina, which has a relatively low thermal conductivity, adds significant thermal resistance to the heat conduction path. Table 3.1 lists thermal conductivities for some of the materials used in and around MCMs.

We will now look at how much of a problem is posed by the presence of the alumina substrate in the thermal path. In order to do so we will use the thermal properties of the ATF501P8 die. The die is rated for a maximum channel temperature of 150°C. The channel to board thermal resistance ( $\theta_{ch\_b}$ ) is 23°C/W, meaning for every Watt dissipated in the transistor there will be a difference of 23°C between the channel temperature and the mounting surface. We will make the assumption that the entire

Figure 3-1: Heat Flow in an MCM

| Material        | $\begin{array}{c} {\rm Thermal\ Conductivity} \\ {\rm (W/in^{\circ}C)} \end{array}$ |

|-----------------|-------------------------------------------------------------------------------------|

| Copper          | 9.9                                                                                 |

| Silicon         | 3.8                                                                                 |

| Eutectic Solder | 1.27                                                                                |

| GaAs            | 1.1                                                                                 |

| Alumina         | .7                                                                                  |

| Air             | .007                                                                                |

Table 3.1: Thermal Conductivities

temperature drop occurs across the die and not the thermally conductive metal connecting the die to the bottom of the package. X-rays revealed the die area to be 36.6 mil x 20.9 mil.

To analyze the change in temperature across the substrate, we will use the following standard relationship:

$$\Delta T = Q \frac{L}{A\kappa} \tag{3.1}$$

Here  $\Delta T$  is the change in temperature, Q is the heat flow in Watts, L is the length of the conduction path, A is the cross sectional area of the conduction path, and  $\kappa$  is the coefficient of thermal conductivity, with units of W/in°C.

If we assume that we have a 1 Watt amplifier running at 50% efficiency, then the transistor will have to dissipate 1 Watt of power as heat. Assuming heat flow occurs straight downward (ie, the cross sectional area of the conduction path is just the area of the die), we get a change in temperature across the alumina substrate of 46.7°C. Under the same assumptions, the eutectic solder will add about 1°C for a 1 mil layer. At 1 Watt, we get a 23°C temperature difference from the channel to the bottom of the transistor die resulting from  $\theta_{ch,b}$ . Thus, we have a total temperature difference of just over 70°C from the channel to the outside of the module. If we assume our amplifier is specified to run at a 70°C ambient, as is common in military applications, then our junction temperature for the device. This is assuming a perfect heatsink is placed outside the module, with zero rise above the ambient. In reality, there could be a drop of several degrees across the heatsink, and our channel temperature could be even higher.

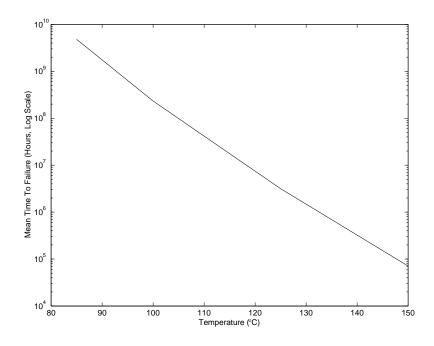

Aside from risking exceeding the maximum channel temperature, operating at such a high temperature will dramatically reduce the reliability of the device. Figure 3-2 shows MTTF of the ATF501P8 as a function of temperature. These data were provided in the reliability data sheet for the device. The graph shows an exponential drop in MTTF with increasing temperature. At 140°C, the MTTF is around  $3.2 \cdot 10^5$  hours, or 37 years, and we are near the bottom of the curve. With a 10°C drop across the

Figure 3-2: Log(Mean Time to Failure) vs. Temperature

heatsink, the channel temperature rises to its maximum allowed value of 150°C, with a MTTF of 71,000 hours, or 8 years. The data suggest that a much longer MTTF is achievable.

In our analysis we have assumed that all of our heat flows straight downward, when in reality some heat will flow laterally outward, effectively reducing the thermal resistance of the substrate. Thus, our assessment of the channel temperature is probably pessimistically high. Nonetheless, our analysis suggests that to operate the device reliably for a long period of time, a more effective heat conduction solution is required.

## 3.2 Thermal Vias

A common cooling solution for MCMs described in the literature is the use of thermal vias [6], [4]. The idea behind thermal vias is to drill holes in the substrate below the die and fill them with a thermally conductive material in order to reduce the thermal resistance between the die and the ambient. Figure 3-3 shows placement of the vias. Materials used for thermal vias are usually compound metals. In addition to

Figure 3-3: Placement of Thermal Vias in an MCM

| Material   | Thermal Conductivity | TCE    |

|------------|----------------------|--------|

|            | $W/in^{\circ}C$      | ppm/°C |

| CuW/15-85  | 4.57                 | 7.0    |

| CuW/10-90  | 5.31                 | 6.5    |

| AlSiC      | 4.57                 | 6.7    |

| CuMo/15-85 | 4.67                 | 6.6    |

| Silvar-K   | 2.97                 | 7.0    |

| Alumina    | .7                   | 6.9    |

| GaAs       | 1.1                  | 6.5    |

Table 3.2: Material Properties

high thermal conductivity, it is essential that thermal vias have a similar TCE as the substrate and the transistor. If the TCEs are unmatched, damage could be done to the substrate or device with large swings in temperature. This is especially true with thin microwave devices made out of GaAs, which is very brittle. Some common alloys used in thermal vias, along with thermal conduction coefficients and TCEs are shown in table 3.2.

With a TCE of 7 ppm/°C and a thermal conductivity of 4.57 W/in°C, the 15% copper/85% tungsten alloy provides the best compromise between high thermal conductivity and a match to the thermal coefficients of expansion of alumina (6.9 ppm/°C)

and GaAs (6.5 ppm/ $^{\circ}$ C).

In order to estimate how effective thermal vias would be in lowering the thermal resistance of the conduction path in the MCM, we will use the analysis in [5]. In this work, two methods for modeling the effect of thermal vias in an MCM substrate were compared. The best agreement with experimental results were obtained by modeling the substrate containing the thermal vias as a single material with an adjusted thermal conductivity. The thermal conductivity is adjusted according to the following equation:

$$\lambda_T = \frac{\lambda_1 (A - B) + \lambda_2}{A} \tag{3.2}$$

where  $\lambda_1$  is the substrate thermal conductivity,  $\lambda_2$  is the via material thermal conductivity, A is the cross sectional area of the substrate below the die, B is the total cross sectional area of the vias, and  $\lambda_T$  is the adjusted thermal conductivity. The equation essentially states that the effective thermal conductivity of the substrate/via combination is equal to the weighted sum of the individual conductivities of the two materials, where the weights are given by the percentage area occupied.

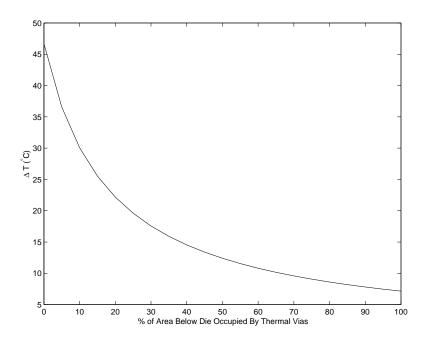

Using the thermal conductivity of Cu-W for  $\lambda_2$ , we can now model the change in temperature across the substrate as a function of the percentage of thermal via area under the die. The results are shown in Figure 3-4.

With a thermal via area of 0%, we see a temperature drop of 46.7°C as expected. The graph clearly shows diminishing returns on via area after around 25%. Indeed, more of a temperature drop is gained with the first 15% of via area than with the final 85%. With 10% via area, the change in temperature across the substrate has dropped from 46.7°C to 30.1°C, a change of 16.6 degrees. Assuming again a 70°C ambient, this places the channel temperature at 124.1°C instead of 140.7°C, a much safer margin for operating the device. The MTTF at 124.1°C is around 3.7x10<sup>6</sup> hours, or 424 years, which is more than a 10-fold increase above the MTTF at 140.7°C.

Figure 3-4: Change in Temperature Across Substrate vs. Thermal Via Area

#### **3.2.1** Practical Considerations

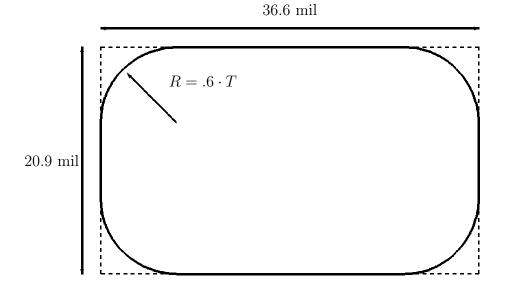

The question remains as to what area ratios are achievable given the constraints of practical alumina substrate processing techniques. Current processes place lower limits on how small vias can be and how close to one another they can be placed. These dimensions are usually determined by the thickness of the substrate. A survey of design rules from MCM substrate vendors revealed a typical minimum hole diameter of  $.6 \cdot T$ , where T is the thickness of the substrate. Spacing between vias is typically on the order of the substrate thickness. At these dimensions, only one via can be placed below a 20.9 by 36.6 mil die. A single via with a diameter equal to the width of the die (which is greater than  $.6 \cdot T$ ) will yield an area ratio of 45%. Applying this figure to the graph in Figure 3-4, we get a temperature drop across the substrate of only 13.4°C, yielding a MTTF of 7,440 years. This is of course only a rough approximation, since we are not modeling several vias below the die as the analysis in [5] assumes.

Another option is to use a non-circular via. In general there is a limitation on how sharp corners can be made when drilling into a substrate, since sharp corners tend to concentrate stresses in the material and cause structural problems. If we assume the

Figure 3-5: Copper Tungsten Area Under Die

minimum radius of a corner is given by the minimum via radius, then the shape in Figure 3-5 should be feasible. Using this shape, the copper tungsten will occupy 86% of the area under the die. According to the above analysis, the temperature across the substrate drops to 8.1°C for a MTTF of 22,000 years.

## 3.3 Summary

The analysis in this chapter is based upon some simplifying assumptions about how heat flows in an MCM substrate. Nonetheless our analysis suggests that thermal vias can be used to dramatically increase MTTF of the transistor in our amplifier.

# Chapter 4

# **Parasitic Effects of Die Connections**

As stated earlier, one of the promising features of MCM technology is the potential to reduce the parasitic effects of making connections to a bare die. In a surface mount package, connections are made between the die and the package leads with long, thin bondwires, which can have significant parasitic inductance and resistance. The package itself can also have capacitive effects. When operating at RF frequencies, these package parasitics can have a significant impact on circuit behavior.

MCM technology offers the potential to make low impedance connections close to the die. There are, however, constraints on how these connections can be made. For a given die and MCM process, the geometry of die connections will be determined by a broad range of parameters, such as location of bond pads on the die, dielectric layer thickness, via dimensions, via pad sizes, inter-layer via spacing, and the location of the ground plane. Thus, the claim that the MCM process allows for reduced parasitics requires justification.

In this chapter we will look at the parasitic effects of connecting to a transistor die, specifically the ATF501P8, using the Draper MCM-D process. This is accomplished using a 3-D electromagnetic (EM) fieldsolver called CST Microwave Studio. We will also look at parasitics in the ATF501P8 surface mount package to show that a reduction in parasitics can be achieved in the MCM.

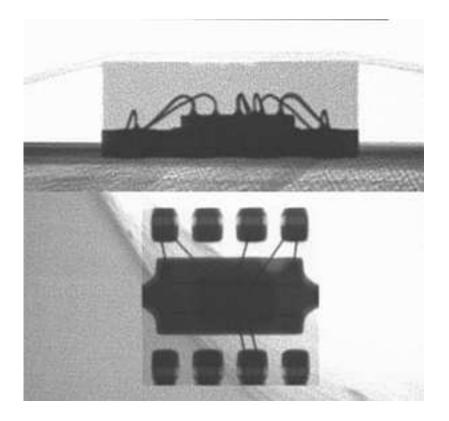

Figure 4-1: X-rays of the ATF501P8 Surface Mount Package

## 4.1 Parasitics of a Surface Mount Package

The ATF501P8 comes packaged in a 2mm x 2mm leadless plastic chip carrier (LPCC) package. X-rays were taken of the package to determine the internal bondwire geometry (Figure 4-1). The die sits on a metal block that serves as the source connection as well as the thermal ground. The x-rays revealed one bondwire connecting the gate to its external lead, two bondwires connecting the drain, and a total of six bondwires connecting the source to the two source leads on the package and to the thermal ground (some of which are not visible in the figure).

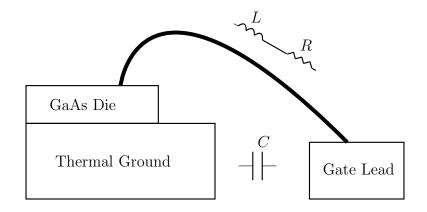

In order to simplify our analysis, we will focus on the gate connection, since it involves a single bondwire. The internal geometry suggests that there will be three main parasitic elements in a model of the gate connection. The bondwire connecting the lead to the die will present a series parasitic resistance and inductance, and a parallel capacitance will exist between the metal lead and the thermal ground. Figure 4-2

Figure 4-2: Parasitic Elements for a Bondwire Connection

Figure 4-3: Agilent Model for the ATF501P8 Gate Connection

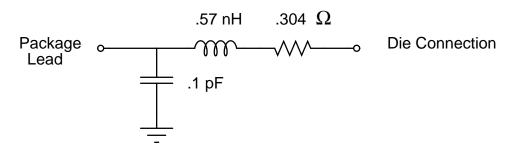

shows the placement of these elements. Agilent provides a lumped element model of the surface mount package with their large signal model of the ATF501P8. Their model of the gate connection, shown in Figure 4-3 agrees with the geometry in Figure 4-2 under the assumption that the thermal ground acts as RF ground, as it will in ours and most applications.

A model of the gate bondwire structure was created in CST Microwave Studio. The purpose of modeling the surface mount structure in the EM simulator was to see how well our simulations would agree with the model provided by Agilent and to provide a consistent mode of comparison within the EM simulator between bondwire structures and MCM structures. The geometry of the connection was constructed as it appeared in the x-rays. A dielectric constant of 3 was estimated for the plastic in the package. The bondwire was constructed using Microwave Studio's bondwire model.

Two separate S-parameter simulations were performed. First, the impedance from the die to the gate lead was measured to yield the series impedance of the connection. The impedance from the thermal ground to the gate lead was then measured to find the shunt capacitance value. Lumped element models were then fit to these S-parameter measurements using an optimizer in ADS. A summary of the results is shown in the following table:

| Model         | $L_{series}$        | $R_{series}$ | $C_{shunt}$ |

|---------------|---------------------|--------------|-------------|

| Agilent       | $.552 \mathrm{~nH}$ | $.304\Omega$ | .10 pF      |

| EM Simulation | .816 nH             | $.035\Omega$ | .203 pF     |

The EM simulation predicted significantly lower series resistance and slightly larger series inductance and shunt capacitance. The results show reasonable agreement considering that the geometry of the structure could only be roughly approximated from the x-rays. In addition, the material properties of the bondwire and package modeled in Microwave Studio may not have perfectly matched those in the physical device.

## 4.2 Parasitics in the MCM

Now that we have closely analyzed parasitic effects in a surface mount package and demonstrated their measurement in the EM simulator, we will look at parasitics in the MCM process.

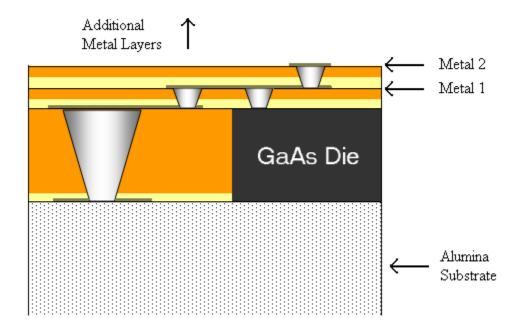

#### 4.2.1 The Draper MCM-D Process

In the Draper MCM-D process, the die sits on the substrate in a 6 mil layer of Kapton film. Layers above the die consist of Kapton and adhesive and are 1.5 mils thick. Connections are made to the die with vias through the first Kapton layer. Thus, the shape and sizes of these vias are instrumental in determining parasitic effects of die connections.

However, these vias do not tell the whole story. From here parasitic effects are closely tied to the transmission line structure one is using in the circuit. The structure

Figure 4-4: MCM Cross Section

determines what metal layer each terminal of the transistor must be connected to. If the transmission lines are going to reside on a metal layer 2 layers above the die, then the parasitic effects will include via connections through 2 layers. Moreover, the placement of these vias will be constrained by the process design rules, which put a lower limit on the distance between vias in adjacent layers. The parasitics will therefore include the metal required to connect the two spaced vias. The choice of structure also determines the placement of the ground plane(s), which affects parasitic capacitance.

Thus, we see that there are many variables in determining the parasitic effects of connecting to the die. In order to provide a broad analysis of the many configurations possible, we will analyze series parasitic elements separately from shunt capacitive elements. This will give a picture of parasitic effects that can be generalized to a broad variety of connection structures.

It should be noted that the current Draper MCM-D process does not currently support metalization on the substrate or filled vias through the 6 mil die layer. Nonetheless, because of the high dielectric constant of alumina, patterning on the substrate holds

Figure 4-5: Die Connections to Various Layers

the potential for making compact transmission line structures in MCMs (see chapter 5). As a result it may be desirable to work this capability into the process in the future. This work will therefore include analysis of connections made from the die down to the substrate. Vias through the 6 mil layers were assumed to be proportional in aspect ratio to vias through the 1.5 mil layers, as were pad sizes for the vias.

#### 4.2.2 Series Inductance and Resistance

In order to mestimate series parasitics in the MCM, structures were created in Microwave Studio connecting the die to various layers in the MCM, and the impedances of these connections were calculated. The geometries were determined by bond pad placement on the die observed in the x-rays as well as by the design rules of the MCM process. Figure 4-5 shows the different geometries tested. As was done with the bondwire structures, inductance and resistance values were fit to S-parameter values using ADS. The results are shown in the following table:

| Geometry         | $L_{series}$         | $R_{series}$ |

|------------------|----------------------|--------------|

| Die to Substrate | $.395 \ \mathrm{nH}$ | $.054\Omega$ |

| Die to Metal 1   | $.027 \ \mathrm{nH}$ | $.006\Omega$ |

| Die to Metal 2   | $.050 \ \mathrm{nH}$ | $.030\Omega$ |

| Die to Metal 3   | .106 nH              | $.057\Omega$ |

The largest parasitic inductance occurs in connecting the die to the substrate. Even in this case, the series inductance is lower than the inductance in both the Agilent package model and the EM bondwire simulation. In the latter case it is more than 50% lower. When connecting to the metal 1 later, the parasitic inductance is only .027 nH, which is more than a factor of 10 lower than the inductance in either bondwire model.

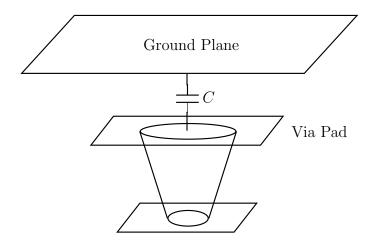

### 4.2.3 Parallel Capacitance

The primary source of parallel capacitance in MCM die connections will be the metal pads on the vias (Figure 4-6). We can expect the parasitic capacitances to be roughly proportional to  $\epsilon A/d$ , where A is the total metal area, d is the the distance to the ground plane, and  $\epsilon$  is the dielectric constant of the material separating the pad and ground. To provide an estimate of parallel capacitances, die connections were made to the substrate and the first two metal layers. For each structure, ground planes were placed on a variety of different layers. The impedances from the die connection to ground were then simulated and fit to capacitance values.

Figure 4-6: Parallel Capacitance Resulting From Via Pads

| Connection Type  | Ground Plane    | $C_{shunt}$          |

|------------------|-----------------|----------------------|

|                  | Location        |                      |

| Die to Substrate | Below Substrate | .143 pF              |

| Die to Substrate | Metal 2         | $.156~\mathrm{pF}$   |

| Die to Substrate | Metal 3         | $.125 \mathrm{ pF}$  |

| Die to Metal 1   | Metal 2         | $.041~\mathrm{pF}$   |

| Die to Metal 1   | Metal 3         | $.032 \mathrm{\ pF}$ |

| Die to Metal 1   | On Substrate    | $.040 \mathrm{\ pF}$ |

| Die to Metal 2   | Metal 3         | $.050~\mathrm{pF}$   |

For the case of connecting the die to the substrate, our parasitic capacitances will be on the same order of magnitude as they are in the surface mount package. This is primarily the result of the large via pad required by the via through the 6 mil Kapton layer. Even though the ground plane is far away from the via pad when it is placed below the substrate, we still get a large  $C_{shunt}$  because of the high dielectric constant of alumina. If we are dealing with a transmission line structure that uses two ground planes, we have to add the capacitances resulting from each. For example, if we put transmission lines on the substrate and have ground planes below the substrate and on metal 2, our total  $C_{shunt}$  would be .156 pF + .143 pF = .299 pF. This  $C_{shunt}$  value is higher than that in either model of the surface mount package's gate connection. In the case of connections to the metal layers above the die, the shunt capacitances are lower than in the bondwire case. Even though the metal connections are close to the ground planes, the smaller via pad areas result in lower capacitances than we see when connecting to the substrate.

## 4.3 Summary

Our simulations suggest that, when connecting the transistor to the upper metal layers, we can achieve significant reductions in series inductance and resistance and modest reductions in shunt capacitance over a surface mount package. When connecting to the substrate, we can still achieve a reduction in series inductance and resistance, but shunt capacitance remains unchanged and in some cases increased when compared to the surface mount package.

These results are quite positive for our application. Series inductance at the transistor terminals can be problematic, particularly in the source connection of a power amplifier. Inductance from the source to ground can provide a feedback path from output to input and cause instability. We have shown that we can reduce series inductance over a surface mount package regardless of where we put our ground plane, and that we can reduce it by over a factor of 10 if the ground plane is in one of the metal layers above the die.

In addition, the shunt capacitances are not necessarily a big problem. The gate and drain capacitances of an RF power transistor are generally pretty large. In the case of the ATF501P8, the die model gives a  $C_{gs}$  of 10.0pF. An additional .1-.3 pF will not have a significant effect.  $C_{gd}$  is 1.3 pF, but since the drain would likely be connected to a low impedance (as a result of the low drain supply), a modest increase in shunt capacitance here would be unlikely to impact circuit performance very much.

# Chapter 5

# **Transmission Line Structures**

At high frequencies, a circuit's behavior is largely determined by its physical dimensions and by the dielectric properties of the materials it is fabricated on. It is therefore important to understand what the electrical properties of different transmission line structures will be within the constraints of a given process. In this chapter we will use simulations to look at the electrical properties of several transmission line structures as they would be constructed in an MCM.

For each structure, we will try to answer two main questions:

- 1. What is the line width for a  $50\Omega$  line?

- 2. How long is a  $\lambda/4$  line at 2.3 GHz?

Since our amplifier (and, in general, most RF circuits) will require  $50\Omega$  lines, the first question is a good indicator of whether a transmission line structure is practical or not. The minimum line width supported by the Draper MCM-D process is 2 mils. If  $50\Omega$  lines in a given structure are thinner than 2 mils, then the structure will be problematic for use in RF circuits. Even if the  $50\Omega$  line width is slightly larger than 2 mils, the line impedances will still be especially prone to errors resulting from line width tolerances. On the other hand, if line widths grow too large, transmission line behavior can become less predictable.

The second question will give us a feel for how compact we will be able to make transmission line networks. Many transmission line networks will use dimensions on

Figure 5-1: Basic Transmission Line Structures

the order of a quarter wavelength at the fundamental in order to achieve impedance transformations. With this metric we will be able to rank transmission line structures in terms of how compact networks are likely to be.

## 5.1 Transmission Line Structures

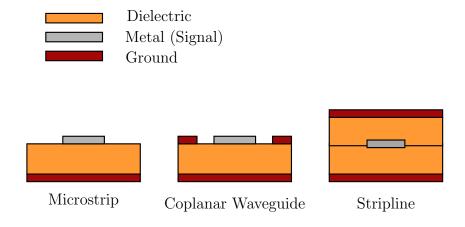

The basic transmission line structures considered in this chapter are shown in Figure 5-1. Microstrip consists of a single dielectric layer sandwiched between the transmission line and the ground plane. The coplanar waveguide with ground (CPWG) structure is similar to microstrip, but contains an additional ground in the plane of the transmission line. In a stripline structure, the transmission line lies in a dielectric material symmetrically spaced between two ground planes.

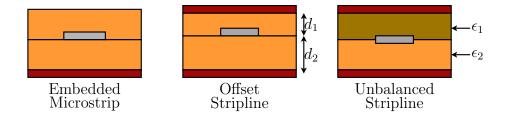

Some variations on these geometries will also be considered. Examples are shown in Figure 5-2. Embedded microstrip is a microstrip structure with a dielectric layer on top. Offset stripline has the transmission line offset from the center of the two ground planes. Unbalanced stripline has two different dielectric materials above and below the conductor.

Figure 5-2: Variations on Basic Transmission Line Structures

## 5.2 Basic Transmission Line Simulations

Basic transmission line structures were analyzed using the ADS LineCalc tool. LineCalc takes substrate material properties and thickness as input and calculates transmission line dimensions given desired electrical lengths and impedances.

### 5.2.1 Microstrip

The only parameter that can be varied besides line width and length in a straightforward MCM microstrip structure is the thickness of the Kapton dielectric between the transmission line and the ground plane. In the upper layers of the MCM, this parameter can be varied in 1.5 mil increments as more layers are placed above the ground plane. Another possible structure has a ground plane on the substrate and the conductor in the metal 1 layer, for a total dielectric thickness of 7.5 mil. The possible geometries are shown in Figure 5-3. The results of simulations are given here:

| Geometry   | Dielectric Thickness (mil) | $W_{50\Omega}$ (mil) | $L_{\lambda/4}$ (mil) |

|------------|----------------------------|----------------------|-----------------------|

| Microstrip | 1.5                        | 3.41                 | 813                   |

| Microstrip | 3                          | 6.99                 | 808                   |

| Microstrip | 4.5                        | 10.6                 | 807                   |

| Microstrip | 7.5                        | 17.8                 | 805                   |

We see that a variety of line impedances are available with microstrip configurations, but that a quarter wavelength line will be more than eight tenths of an inch long. In the interest of compact designs, a shorter line length would be desirable.

Figure 5-3: Geometries for Microstrip Structures

Symmetric Stripline

Offset Stripline

Figure 5-4: Geometries for Stripline Structures

### 5.2.2 Stripline

Because stripline occupies two layers in the MCM, fewer configurations are possible. We can achieve a total dielectric thickness of either 3 or 6 mils by occupying 3 or 5 metal layers respectively. The geometries are shown on the left in Figure 5-4. The results for stripline are shown here:

| Geometry  | Dielectric Thickness (mil) | $W_{50\Omega}$ (mil) | $L_{\lambda/4}$ (mil) |

|-----------|----------------------------|----------------------|-----------------------|

| Stripline | 3                          | 1.44                 | 717                   |

| Stripline | 6                          | 3.24                 | 717                   |

Stripline offers slightly shorter lines than microstrip. With the ground planes spaced 3 mils apart, the  $50\Omega$  line width is shorter than the 2 mil minimum line width allowed in the process, so this structure is not practical. Spacing the ground planes 4 layers apart brings the line width above 2 mils, but one might not want the transmission line structure to occupy that many metal layers, so this structure is not very attractive either.

A slight variation on stripline is the offset stripline structure, where the conductor is placed asymmetrically between the two ground planes. One configuration places two 1.5 mil Kapton layers below the conductor and 1 above it. A second configuration considered has the lower ground plane on the substrate, the conductor on metal 1, and the upper ground plane on metal 2. The two geometries are shown on the right in Figure 5-4. Dimensions obtained for these structures are as follows:

| Geometry         | Lower Dielectric | Upper Dielectric | $W_{50\Omega}$ (mil) | $L_{\lambda/4}$ (mil) |

|------------------|------------------|------------------|----------------------|-----------------------|

| Offset Stripline | 3 mil Kapton     | 1.5 mil Kapton   | 2.33                 | 717                   |

| Offset Stripline | 7.5 mil Kapton   | 1.5 mil Kapton   | 4.31                 | 717                   |

The offset stripline structure behaves in a similar fashion as the symmetric stripline structure. By placing more dielectric between the ground planes we are able to increase the 50 $\Omega$  line width, but the quarter-wave line length stays unchanged.

### 5.2.3 Coplanar Waveguide With Ground

The coplanar waveguide with ground structure gives another parameter to vary besides dielectric thickness: the distance between the transmission line and the ground metal within the transmission line's plane (here denoted as S). The lower bound for S is 2 mils, given by the minimum metal to metal spacing in the Draper MCM-D process. Results for the CPWG simulations are given here:

| Geometry | Dielectric Thickness (mil) | S (mil) | $W_{50\Omega}$ (mil) | $L_{\lambda/4}$ (mil) |

|----------|----------------------------|---------|----------------------|-----------------------|

| CPWG     | 1.5                        | 2       | 3.32                 | 823                   |

| CPWG     | 1.5                        | 4       | 3.66                 | 801                   |

| CPWG     | 1.5                        | 6       | 3.82                 | 791                   |

| CPWG     | 3                          | 2       | 5.94                 | 841                   |

| CPWG     | 3                          | 4       | 6.84                 | 817                   |

| CPWG     | 3                          | 6       | 7.22                 | 805                   |

The simulations show the CPWG structure behaving like the microstrip structure, with similar line widths and lengths.

Ultimately, all three of the structures above yield long quarter wave line lengths at 2.3 GHz as a result of the relatively low dielectric constant of Kapton. Since we are

interested in designing small circuits for hand held devices, it would be nice to identify a structure that could use shorter line lengths for impedance transformations. We will identify two such structures in the following section.

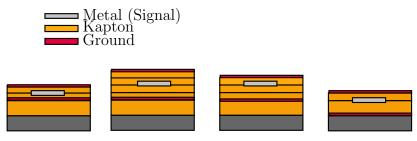

### 5.3 Variations on Basic Structures

The following two structures employ patterning transmission lines on the alumina substrate to take advantage of its high dielectric constant. It should be noted as it was in the previous chapter that this feature is not currently supported in the Draper MCM-D process. The analysis here serves to point out a potential benefit of pursuing patterning on the substrate in future processes.

The transmission line structures discussed in the following sections are not supported by the ADS LineCalc tool and do not loan themselves to simple analysis.  $50\Omega$ line widths and  $\lambda/4$  line lengths were identified using an electromagnetic fieldsolver from Agilent called Momentum. Momentum is a "2.5 dimensional" field solver, termed as such because it models the interactions between multiple layers of a planar transmission line structure but does not analyze arbitrary 3-D structures. The following geometries were constructed in Momentum, and line widths and lengths were adjusted until the 50 $\Omega$  line widths and  $\lambda/4$  line lengths were found.

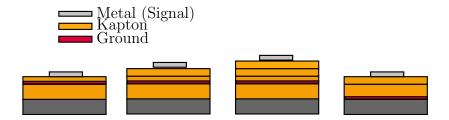

#### 5.3.1 Embedded Microstrip

As stated before, in an embedded microstrip structure, an additional dielectric layer is placed on top of the transmission line. The effective dielectric constant seen by the transmission line is increased, because the line sees the dielectric material instead of free space above it. The three geometries shown in Figure 5-5 were simulated. In the geometry on the left, the line resides on the alumina substrate. The ground plane is placed below the substrate, and the dielectric layer above the line is 7.5 mils thick. In the geometry in the center, the line resides on the metal 1 layer. The ground plane is on top of the substrate, and the upper dielectric is formed with additional Kapton film layers. In the geometry on the right, all of the metal lies in the upper layers. The

Figure 5-5: Embedded Microstrip Structures

ground plane lies on the metal 1 layer and the transmission line lies in a layer above it. The results of the simulations are summarized here:

| Geometry        | Lower Dielectric | Upper Dielectric | $W_{50\Omega}$ (mil) | $L_{\lambda/4}$ (mil) |

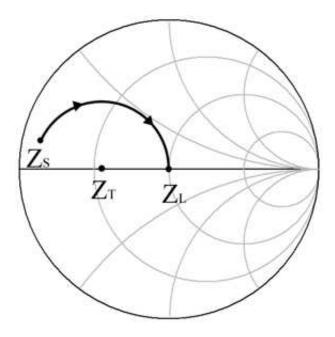

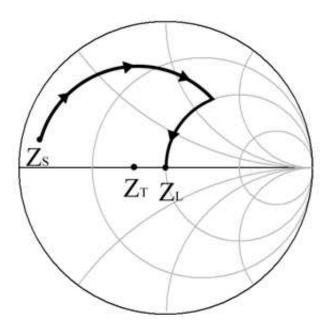

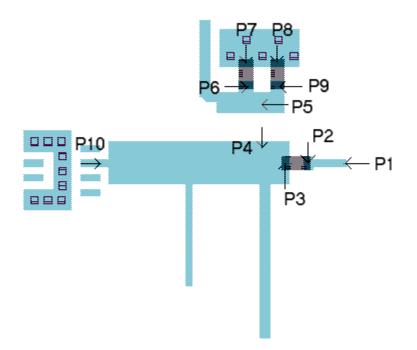

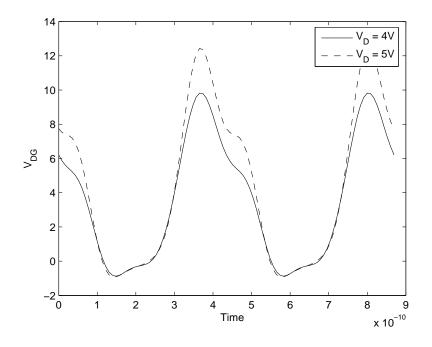

|-----------------|------------------|------------------|----------------------|-----------------------|