### A VLSI Systolic Array Processor for Complex Singular Value Decomposition

by

Christopher Charles Niessen

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degrees of

Bachelor of Science in Electrical Engineering

and

| Author                    | of Electrical Engineering and Computer Science<br>May 6, 1994           |

|---------------------------|-------------------------------------------------------------------------|

|                           | .4                                                                      |

|                           | Srinivas Devadas                                                        |

|                           | Associate Professor of Electrical Engineering                           |

|                           | Thesis Supervisor                                                       |

| Certified by              | Steven R. Broadstone                                                    |

| , (                       | Steven R. Broadstone                                                    |

|                           | Staff, MIT Lincoln Laboratory                                           |

| •                         | Company Supervisor                                                      |

| Certified by $\ldots_{v}$ | H. T. Kung<br>H. A. Professor, Harvard University                       |

| - 0                       | H. T. Kung                                                              |

|                           | Professor, Harvard University                                           |

| Accepted by               |                                                                         |

|                           | Frederic R. Morganthaler                                                |

| Chairman,                 | Frederic R. Morganthaler<br>Departmental Committee on Graduate Students |

|                           | l l                                                                     |

### A VLSI Systolic Array Processor for Complex Singular Value Decomposition

by

Christopher Charles Niessen

Submitted to the Department of Electrical Engineering and Computer Science on May 6, 1994, in partial fulfillment of the requirements for the degrees of Bachelor of Science in Electrical Engineering and Master of Science in Electrical Engineering

#### Abstract

The singular value decomposition is one example of a variety of more complex routines that are finding use in modern high performance signal processing systems. In the interest of achieving the maximum possible performance, a systolic array processor for computing the singular value decomposition of an arbitrary complex matrix was designed using a silicon compiler system. This system allows for ease of design by specification of the processor architecture in a high level language, utilizing parts from a variety of cell libraries, while still benefiting from the power of custom VLSI. The level of abstraction provided by this system allowed more complex functional units to be built up from existing simple library parts. A novel fast interpolation cell for computation of square roots and inverse square roots was designed, allowing for a new algebraic approach to the singular value decomposition problem. The processors connect together in a systolic array to maximize computational efficiency while minimizing overhead due to high communication requirements.

Thesis Supervisor: Srinivas Devadas Title: Associate Professor of Electrical Engineering

Company Supervisor: Steven R. Broadstone Title: Staff, MIT Lincoln Laboratory

Reader: H. T. Kung Title: Professor, Harvard University

### Acknowledgments

I would like to extend my deepest gratitude to Dr. Steven Broadstone for all of the help he has given me throughout this thesis. His help and guidance have proved to be absolutely essebtial.

I would also like to thank Professor Srinivas Devadas for supervising this thesis and for his helpful input, and Professor Kung of Harvard University for reading and commenting on my thesis. In addition, I would like to thank the members of MIT Lincoln Laboratory Group 44 for the assistance they have provided.

I would like to thank my father for believing in me all of these years, and for convincing me that I could handle anything the Institute could throw at me. I also would like to thank Gen for making everything just a little bit better.

# Contents

| 1 | Intr | oduction                                | 10 |

|---|------|-----------------------------------------|----|

|   | 1.1  | Parallel Implementations of the SVD     | 10 |

|   | 1.2  | Systolic Processor Array                | 11 |

|   | 1.3  | Overview of the Thesis                  | 12 |

| 2 | The  | e Singular Value Decomposition          | 13 |

|   | 2.1  | SVD of a Real, Symmetric Matrix         | 13 |

|   | 2.2  | SVD of an arbitrary real matrix         | 16 |

|   | 2.3  | SVD of an arbitrary complex matrix      | 17 |

|   | 2.4  | SVD of an $n \times n$ Matrix           | 21 |

|   | 2.5  | Parallel Computation of the SVD         | 23 |

| 3 | Sys  | tolic Processor Array                   | 26 |

|   | 3.1  | The Systolic Array                      | 26 |

|   | 3.2  | The Brent-Luk-Van Loan Systolic Array   | 28 |

|   | 3.3  | Changes to the Brent-Luk-Van Loan Array | 32 |

| 4 | Sys  | tolic Processor Elements                | 37 |

|   | 4.1  | Processor Element Design                | 37 |

|   | 4.2  | Functional Unit Design                  | 38 |

|   | 4.3  | Processor Element Architecture          | 40 |

| 5 | Fast | t Interpolation Cell                    | 46 |

|   | 5.1  | Interpolation                           | 47 |

|              | 5.2 | Interpolation Cell          | 51 |

|--------------|-----|-----------------------------|----|

| 6            | LAC | GER Silicon Assembly System | 55 |

|              | 6.1 | The LAGER Tools             | 55 |

|              | 6.2 | Design Hierarchy            | 58 |

| 7            | Rea | lization                    | 67 |

|              | 7.1 | Specifications              | 67 |

|              | 7.2 | Implementation Difficulties | 69 |

| 8            | Con | clusions                    | 73 |

|              | 8.1 | Future Work                 | 73 |

|              | 8.2 | Concluding Remarks          | 74 |

| $\mathbf{A}$ | Sou | rce Code                    | 76 |

|              | A.1 | SDL Code                    | 76 |

|              |     | A.1.1 2to1mux.sdl           | 76 |

|              |     | A.1.2 2to1muxdpp.sdl        | 77 |

|              |     | A.1.3 2to1muxlogic.sdl      | 78 |

|              |     | A.1.4 3to1mux.sdl           | 79 |

|              |     | A.1.5 2to1muxdpp.sdl        | 80 |

|              |     | A.1.6 3to1muxlogic.sdl      | 81 |

|              |     | A.1.7 addsub.sdl            | 81 |

|              |     | A.1.8 addsubdpp.sdl         | 83 |

|              |     | A.1.9 addsublogic.sdl       | 84 |

|              |     | A.1.10 bus2adder.sdl        | 84 |

|              |     | A.1.11 bus2bshift.sdl       | 87 |

|              |     | A.1.12 bus2bshiftdpp.sdl    | 88 |

|              |     | A.1.13 bus2bshiflogic.sdl   | 90 |

|              |     | A.1.14 bus2cmult.sdl        | 91 |

|              |     | A.1.15 bus2interp.sdl       | 92 |

|              |     | A.1.16 bus2logic.sdl        | 93 |

| A.1.17 ł | bus2out.sdl          | 94  |

|----------|----------------------|-----|

| A.1.18 ł | busserio.sdl         | 95  |

| A.1.19 b | busseriodpp.sdl      | 97  |

| A.1.20 ł | busseriologic.sdl    | 99  |

| A.1.21 c | cmult.sdl            | 101 |

| A.1.22 c | deltarom.sdl         | 105 |

| A.1.23 d | diag2.sdl            | 113 |

| A.1.24 c | diag2chip.sdl        | 117 |

| A.1.25 c | diagctl.sdl          | 122 |

| A.1.26 I | From.sdl             | 124 |

| A.1.27 ( | Grom.sdl             | 133 |

| A.1.28 i | inc.sdl              | 141 |

| A.1.29 i | incdpp.sdl           | 142 |

| A.1.30 i | interp.sdl           | 143 |

| A.1.31 i | interpentl.sdl       | 148 |

| А.1.32 г | multiplier.sdl       | 149 |

| А.1.33 г | negator.sdl          | 150 |

| A.1.34 r | normalizer.sdl       | 151 |

| A.1.35 r | normalizerbuffer.sdl | 152 |

| A.1.36 r | normalizerdpp.sdl    | 153 |

| A.1.37 r | normalizerlogic.sdl  | 153 |

| A.1.38 c | offdiag2.sdl         | 154 |

| A.1.39 c | offdiag2chip.sdl     | 157 |

| A.1.40 c | offdiagctl.sdl       | 162 |

| A.1.41 r | regfile2p.sdl        | 164 |

| A.1.42 r | regfile2pdpp.sdl     | 166 |

| A.1.43 r | regfile2plogic.sdl   | 168 |

| A.1.44 r | register.sdl         | 169 |

| A.1.45 r | registerdpp.sdl      | 170 |

| A.1.46 r | egisterlogic.sdl     | 171 |

| A.2 | BDS F | `iles          | • | • | <br>• |   | • | • | • |     | • |   | • | • | • | • | • | • | • | • | • | • | • |   | • | 172 |

|-----|-------|----------------|---|---|-------|---|---|---|---|-----|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-----|

|     | A.2.1 | diagctl.bds    | • | • | <br>• | • | • | • | • | • • | • | • |   | • | • |   | • |   | • | • |   | • | • | • | • | 172 |

|     | A.2.2 | interpcntl.bds | • | • | <br>• |   | • | • | • |     | • |   |   | • |   |   | • |   | • | • | • | • | • | • | • | 196 |

|     | A.2.3 | offdiagctl.bds | • | • | <br>• |   | • | • | • |     |   |   |   | • |   |   | • | • | • |   | • | • | • | • |   | 199 |

|     | A.2.4 | prienc.bds     | • | • | <br>• | • |   | • | • |     | • |   |   |   |   |   | • | • | • |   | • |   |   |   |   | 216 |

# List of Figures

| 3-1 | Dataflow Connections for Each Processor Element                        | 29 |

|-----|------------------------------------------------------------------------|----|

| 3-2 | Rotation Parameter Flow for Off-Diagonal Processor Elements            | 29 |

| 3-3 | Rotation Parameter Flow for Diagonal Processor Elements                | 30 |

| 3-4 | Complete Interconnections for Off-Diagonal Processor Elements          | 30 |

| 3-5 | Complete Interconnections for Diagonal Processor Elements              | 30 |

| 3-6 | Example Systolic Array                                                 | 31 |

| 4-1 | Block Diagram of Off-Diagonal Processor Element                        | 42 |

| 4-2 | Block Diagram of Diagonal Processor Element                            | 43 |

| 5-1 | Block Diagram of Fast Interpolation Cell Data Paths                    | 52 |

| 6-1 | Design Hierarchy for the Top Level of the Diagonal Processor Element   | 59 |

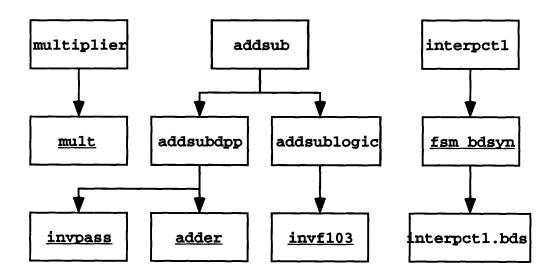

| 6-2 | Design Hierarchy for Adder, Multiplier, and Top Level of Interpolator  | 62 |

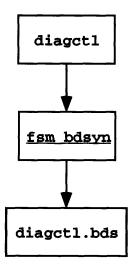

| 6-3 | Design Hierarchy for Processor Controller                              | 63 |

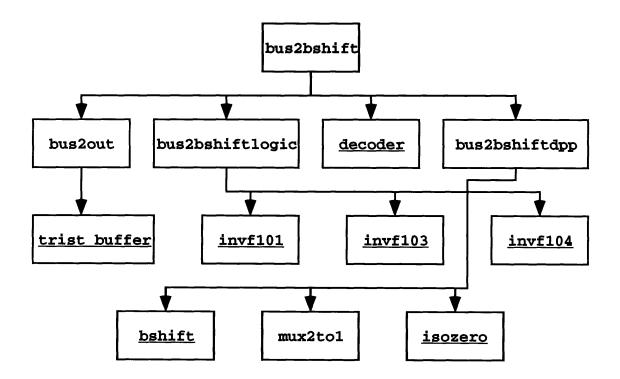

| 6-4 | Design Hierarchy for Barrel Shifter                                    | 63 |

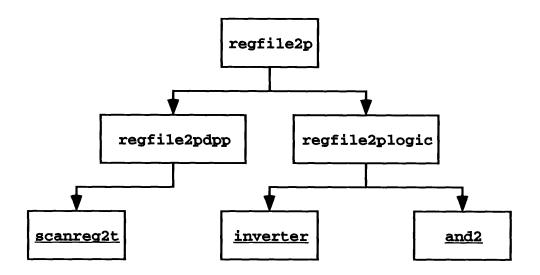

| 6-5 | Design Hierarchy for Register File                                     | 64 |

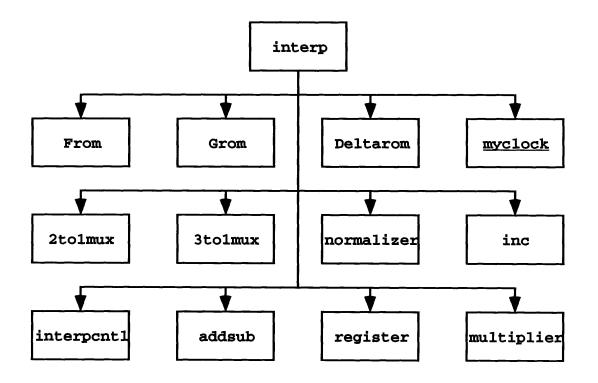

| 6-6 | Top Level Design Hierarchy for Fast Interpolation Cell                 | 64 |

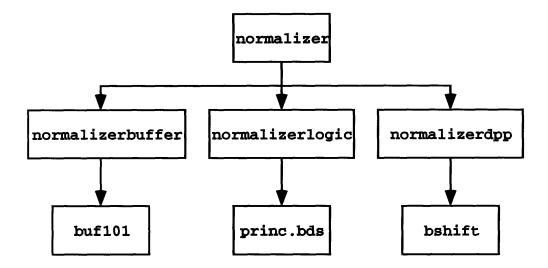

| 6-7 | Design Hierarchy for Fast Interpolation Normalization Subcell $\ldots$ | 65 |

| 6-8 | Design Hierarchy for Fast Interpolation Cell Multiplier, Adder, and    |    |

|     | Controller                                                             | 65 |

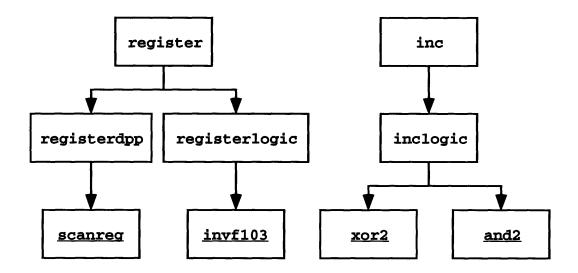

| 6-9 | Hierarchy for Fast Interpolation Cell Incrementor and Register         | 66 |

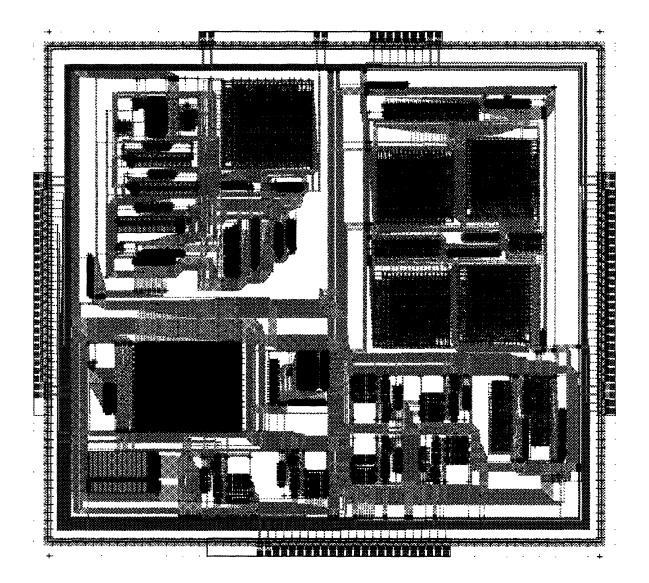

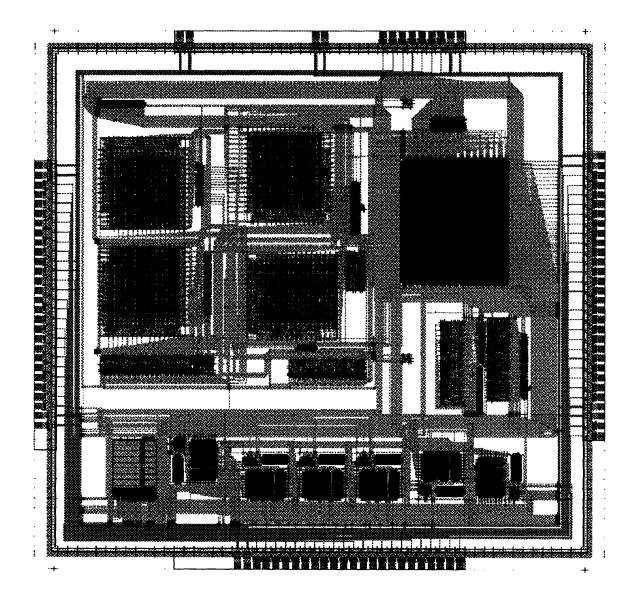

| 7-1 | Layout of Diagonal Processor                                           | 70 |

| 7-2 | Layout of Off-Diagonal Processor                                       | 71 |

|     |                                                                        |    |

# List of Tables

| 3.1 | Processor Cycle Usage                             | 34 |

|-----|---------------------------------------------------|----|

| 4.1 | Comparison of Three Different Complex Multipliers | 44 |

| 5.1 | Interpolator Cycle Computations                   | 53 |

## Chapter 1

### Introduction

The singular value decomposition (SVD) of an arbitrary complex matrix is a computationally intensive problem. However, this matrix factorization is useful in a wide variety of signal processing applications. As signal processing algorithms become more complex, new and different implementations need to be devised. Most SVD algorithms make assumptions about the input matrix which limit their flexibility. This thesis will develop a method for computing the SVD of a complex matrix that makes no assumptions about the input data. In addition, a VLSI design of this implementation on a systolic processor array will be presented.

#### **1.1** Parallel Implementations of the SVD

The problem of computing the SVD factorization of a complex matrix requires a large number of computations. However, it is also an algorithm with a high level of inherent parallelism. This parallelism, which comes from the independent nature of the computations, allow it to be realized very efficiently on a massively parallel computation engine. Algorithms for calculation of the SVD in an orderly fashion have been around for a long time [6], but only since the advent of high performance, low cost specialized processor subsystems has the problem been addressed with a parallel implementation in mind [3]. These new parallel algorithms have given rise to several proposed designs for systems tailored for SVD computation.

Several implementations of parallel architectures for SVD have been suggested [3, 7, 4]. However, there may be difficulties with existing designs. [3] is intended for real matrices, and [7] and [4] make use of the CORDIC (COordinate Rotation Digital Computer) [20] engine, which is inefficient for longer word widths. In this thesis, the general methods detailed in |3| are expanded to accommodate complex matrices, and the computations are pipelined to increase efficiency. In addition, the SVD problem will be solved algebraically, without the need for direct implementation of trigonometric functions. The CORDIC engine used in [7] will be replaced by a novel fast interpolation cell that is capable of performing complicated functions in a time much less dependent on output word width, while maintaining accuracy. In addition, this design will be implemented entirely in a high level structural description language used as input to a silicon compiler system. This allowed the entire design to be parameterized and altered with minimal effort. The processor elements are designed to utilize the high level of abstraction afforded by the silicon compiler system; specifically, they may be used as frameworks for application specific digital signal processors. These nature of these designs allow additional functional units to be added or removed easily, making for high performance systems while maintaining an extremely low design time.

#### **1.2 Systolic Processor Array**

The nature of the SVD algorithm requires very little data for each calculation, and it can be implemented without the ability to move data quickly over large distances across the system. These qualities of the algorithm make it ideal for implementation in a systolic processor array. A systolic processor array is a mesh connected set of processors. The only data interconnections are to immediately adjacent nodes. The array is termed a systolic array because the data "pumps" through the system as if blood were pumping through a body. The array performance has no dependence on the overall size, due to the locality of the interconnects. Given multiple processors all connected to one central resource, as in a shared memory or a data bus, the overall size should be limited, as any increase necessitates an alteration in the design. Using a systolic array, all processor interconnection is to the nearest neighbor. Isolating each processor from the rest of the array allows the system to grow nearly without bound, with little or no change in the overall design.

### 1.3 Overview of the Thesis

In chapter 2, a two step process for computing the singular value decomposition of an arbitrary complex matrix is developed, including details on how it will be carried out in a parallel system. In chapter 3, the design of the systolic processor array is discussed, detailing the data flow through the array and necessary design issues and trade-offs. Chapter 4 will discuss the individual processor elements, including their functional units and architecture. Chapter 5 will examine the design of the fast interpolation functional unit and its benefits. Chapter 6 will discuss the LAGER silicon assembly system used for the realization of the design. The trade-offs of design time and performance will be considered. Chapter 7 will discuss the specific implementation of this system, and finally, chapter 8 will discuss possible improvements and future work.

## Chapter 2

# The Singular Value Decomposition

The singular value decomposition (SVD) is a matrix factorization technique that is of use in many areas of signal processing. SVD can be used to help reconstruct the electrical activity inside the brain using non-invasive electrodes placed on the scalp [14]. It is also used to decrease the data rate needed to transmit images [18]. For adaptive array signal processing, SVD can be used to separate the signal subspace from the noise subspace [15]. All of these applications involve reducing a given data matrix to one of smaller effective rank. The amount of information that is retained from the original matrix is determined by a chosen threshold level imposed upon the singular values of the matrix. Having chosen an acceptable cutoff threshold, the elements of the matrix that are below the threshold value can be discarded with little or no information loss. This method is extremely effective for distinguishing the important information in the matrix.

### 2.1 SVD of a Real, Symmetric Matrix

To begin, the Singular Value Decomposition of a real, symmetric matrix will be examined, because it is the simplest case. The singular value decomposition for a  $n \times n$  real, symmetric matrix A is

$$A = U\Sigma V^T \tag{2.1}$$

where U and V are  $n \times n$  orthogonal matrices, and  $\Sigma$  is a diagonal matrix of the singular values of A in non-increasing order down the diagonal. In the following, only  $2 \times 2$  matrices will be considered. The cyclic Jacobi method detailed in [6] suggests a method for calculating the SVD of a  $n \times n$  matrix by breaking it into a series of  $2 \times 2$  matrices, so the SVD of only  $2 \times 2$  matrices can be discussed without a loss of generality. Given that U and V are orthogonal matrices, (2.1) can be re-written as

$$U^T A V = \Sigma.$$

U and V need to be chosen such that  $U^T A V$  yields a diagonal matrix  $\Sigma$  of the singular values of A. For a real, symmetric matrix, U and V are chosen to be real and equal. They are rotation matrices of the form

$$R(\theta) = \begin{bmatrix} \cos \theta & \sin \theta \\ -\sin \theta & \cos \theta \end{bmatrix}.$$

The problem is to choose a real angle,  $\theta_{SVD}$ , such that

$$R(\theta_{SVD})^T A R(\theta_{SVD}) = \Sigma.$$

(2.2)

[3] gives a method of selecting  $\theta_{SVD}$  given A.

However, what is really of interest is  $\sin \theta_{SVD}$  and  $\cos \theta_{SVD}$ , not  $\theta_{SVD}$  itself. If the matrix multiplication of (2.2) is carried out, with

$$A = \left[ \begin{array}{cc} p & q \\ q & r \end{array} \right],$$

where  $q \neq 0$ , the result is

$$\begin{bmatrix} \cos \theta_{SVD} & \sin \theta_{SVD} \\ -\sin \theta_{SVD} & \cos \theta_{SVD} \end{bmatrix}^T \begin{bmatrix} p & q \\ q & r \end{bmatrix} \begin{bmatrix} \cos \theta_{SVD} & \sin \theta_{SVD} \\ -\sin \theta_{SVD} & \cos \theta_{SVD} \end{bmatrix} = \begin{bmatrix} \sigma_1 & 0 \\ 0 & \sigma_2 \end{bmatrix},$$

where  $\sigma_1$  and  $\sigma_2$  are the singular values of A. Expanding this through multiplication,

it is found for the bottom left element and top right element of  $\Sigma$  that

$$q(\cos^2\theta_{SVD} - \sin^2\theta_{SVD}) + (p - r)(\cos\theta_{SVD}\sin\theta_{SVD}) = 0.$$

(2.3)

To solve for  $\cos \theta_{SVD}$  and  $\sin \theta_{SVD}$ , the substitution

$$t = \frac{\cos \theta_{SVD}}{\sin \theta_{SVD}},$$

is made, allowing equation (2.3) to b rewritten as

$$qt^2 + (p-r)t - q = 0.$$

Making the additional substitution

$$\rho = \frac{p-r}{2q}$$

allows (2.3) be further simplified,

$$t^2 + 2\rho t - 1 = 0.$$

Using the quadratic formula and trigonometric identities [3] to solve this eequation yields

$$t = -\rho \pm \sqrt{\rho^2 + 1} \cos \theta_{SVD} = \frac{1}{\sqrt{1+t^2}}, \quad \sin \theta_{SVD} = t \cos \theta_{SVD}.$$

The two possible values for t correspond to the two possible rotation angles, one positive, one negative.

Now, the SVD of A is complete, with

$$U = V = \begin{bmatrix} \cos \theta_{SVD} & \sin \theta_{SVD} \\ -\sin \theta_{SVD} & \cos \theta_{SVD} \end{bmatrix}$$

and

$$\Sigma = UAV^T.$$

### 2.2 SVD of an arbitrary real matrix

In the SVD of an arbitrary real  $2 \times 2$  matrix, U and V are no longer equal, however, U and V are still orthogonal rotation matrices. This means that two separate angles,  $\theta_{left}$  and  $\theta_{right}$ , must be chosen to satisfy

$$R(\theta_{left})^T A R(\theta_{right}) = \Sigma.$$

(2.4)

$\theta_{left}$  and  $\theta_{right}$  are chosen directly, or, alternately, a one-sided rotation by a real angle  $\theta_{sym}$  is chosen such that

$$R(\theta_{sym})^T A = B, \tag{2.5}$$

where B is real and symmetric. This allows the SVD algorithm to be performed on B as in (2.2).  $\theta_{sym}$  is chosen such that the angle between the rows and the angle between the columns of A become equal. (2.5) can be rewritten as

$$R(\theta_{sym})^T A = \begin{bmatrix} \cos \theta_{sym} & \sin \theta_{sym} \\ -\sin \theta_{sym} & \cos \theta_{sym} \end{bmatrix}^T \begin{bmatrix} w & x \\ y & z \end{bmatrix} = \begin{bmatrix} p & q \\ q & r \end{bmatrix}.$$

Solving for q

$$q = x \cos \theta_{sym} - z \sin \theta_{sym} = y \cos \theta_{sym} + w \sin \theta_{sym},$$

and rearranging terms finds that

$$x\cos\theta_{sym} - y\cos\theta_{sym} = w\sin\theta_{sym} + z\sin\theta_{sym}.$$

By making the subsitutions

$$\sin\theta_{sym} = \sqrt{1 - \sin^2\theta_{sym}}$$

and

$$\rho = \frac{w+z}{x-y},$$

it becomes simple to find  $\sin \theta_{sym}$ , and therefore  $\cos \theta_{sym}$ .

$$\sin \theta_{sym} = \frac{1}{\sqrt{1+\rho^2}}, \quad \cos \theta_{sym} = \frac{\rho}{\sqrt{1+\rho^2}}$$

This yields the one sided Givens rotation necessary to make A symmetric. So the SVD of an arbitrary, real  $2 \times 2$  matrix can be expressed as

$$R(\theta_{SVD})^T R(\theta_{sym})^T A R(\theta_{SVD}) = \Sigma.$$

This can be rewritten as in (2.4), if  $\theta_{left} = \theta_{SVD} + \theta_{sym}$ , and  $\theta_{right} = \theta_{SVD}$ .

### 2.3 SVD of an arbitrary complex matrix

An approach similar to that suggested in [7] and [4] for computing the SVD of an arbitrary complex matrix is often chosen. Initially, a complex matrix

$$M = \begin{bmatrix} Ae^{i\theta_A} & Be^{i\theta_B} \\ Ce^{i\theta_C} & De^{i\theta_D} \end{bmatrix}$$

is first multiplied by a modified complex Givens rotation to zero out the bottom left element. The method of [7] has been slightly modified such that the top left element becomes real after the Givens rotation. To accomplish this, the modified complex Givens rotation is separated into a unitary transform, followed by a real Givens rotation. First, M is pre-multiplied by the unitary transform

$$T^{H}_{lpha} = \left[ egin{array}{cc} e^{i heta_{lpha}} & 0 \ 0 & e^{i heta_{\gamma}} \end{array}

ight],$$

where  $\theta_{\alpha} = -\theta_A$ , and  $\theta_{\gamma} = -\theta_C$ , yielding

$$T^{H}M = \begin{bmatrix} A & Be^{i(\theta_{B}-\theta_{A})} \\ C & De^{i(\theta_{D}-\theta_{C})} \end{bmatrix},$$

then a real Givens rotation,  $G(\psi)$

$$G(\psi)_{\alpha}^{T} = \begin{bmatrix} \cos\psi & \sin\psi \\ -\sin\psi & \cos\psi \end{bmatrix},$$

with  $\psi = \tan^{-1}(\frac{C}{A})$ , is performed. Given A and C,  $\cos \psi$  and  $\sin \psi$  are easily computed. They are

$$\cos \psi = \frac{C}{\sqrt{A^2 + C^2}}, \sin \psi = \frac{A}{\sqrt{A^2 + C^2}}.$$

The Givens rotation yields

$$M' = G(\psi)^T T^H_{\alpha} M = \begin{bmatrix} A' & B' e^{i\theta_{B'}} \\ 0 & D' e^{i\theta_{D'}} \end{bmatrix},$$

where

$$A' = A\cos\psi + C\sin\psi,$$

which is real. These two steps can be combined into one left-sided unitary transformation matrix  $L(\psi, \theta_{\alpha}, \theta_{\gamma})$

$$L(\psi, \theta_{\alpha}, \theta_{\gamma})^{T} = G(\psi)T_{\alpha} = \begin{bmatrix} e^{i\theta_{\alpha}}\cos\psi & e^{i\theta_{\gamma}}\sin\psi\\ -e^{i\theta_{\alpha}}\sin\psi & e^{i\theta_{\gamma}}\cos\psi \end{bmatrix}$$

$L(\psi, \theta_{\alpha}, \theta_{\gamma})$  is considered to be a modified complex Givens rotation [4]. A standard complex Givens rotation takes this modified complex Givens rotation and premultiplies it by another unitary transform to produce real diagonal elements. For the purposes of making the matrix M entirely real, this step can be omitted.

Next, the right column of the matrix is rotated to make the top right element,  $B'e^{i\theta_{B'}}$ , real. The bottom right element remains complex, and only its angle is affected. Post-multiplying by a simple transformation matrix

$$T_{\beta} = \left[ \begin{array}{cc} 1 & 0 \\ 0 & e^{i\theta_{\beta}} \end{array} \right],$$

where  $\theta_{\beta} = -\theta_{B'}$ , yields

$$M'' = M'T_{\beta} = \left[ \begin{array}{cc} A' & B' \\ 0 & D'e^{i(\theta_{D'} - \theta_{B'})} \end{array} \right],$$

Finally, the bottom row of M'' is rotated to make the bottom right element real. The bottom left element is unaffected, because it already equals 0. This is accomplished by pre-multiplying M'' by

$$T^H_{\delta} = \left[ \begin{array}{cc} 1 & 0 \\ 0 & e^{i\theta_{\delta}} \end{array} \right],$$

where  $\theta_{\delta} = -(\theta_{D'} - \theta_{B'})$ . This gives

$$T^H_\delta M'' = \left[ \begin{array}{cc} A' & B' \\ 0 & D' \end{array} \right],$$

with A', B', and D' all real. Explicitly,

$$T_{\delta}^{H}G(\psi)^{T}T_{\alpha}^{H}MT_{\gamma} = \begin{bmatrix} A' & B' \\ 0 & D' \end{bmatrix}$$

Then the SVD of an arbitrary real matrix proceeds as outlined above. Starting with

$$A = R^H_\delta g(\psi)^T T^H M R_\gamma,$$

section 2.2 shows how to find two more rotation angles,  $\theta_{left}$  and  $\theta_{right}$ , that will make A diagonal. All that remains is to arrange the singular values of A in non-increasing order. The resulting matrix, after  $R(\theta_{left})$  and  $R(\theta_{right})$  have been applied is of the form

$$\Sigma = \left[ \begin{array}{cc} \sigma_1 & 0 \\ 0 & \sigma_2 \end{array} \right].$$

If  $\sigma_1 < \sigma_2$ , then the matrix needs to be rearranged. This can be accomplished by pre-

and post-multiplying  $\Sigma$  by a transformation matrix

$$N = \left[ \begin{array}{cc} 0 & 1 \\ 1 & 0 \end{array} \right].$$

If  $\sigma_1 \geq \sigma_2$ , then N can be set to the identity matrix.

The complete SVD algorithm can be expressed as

$$R(\theta_{left_2})^H R(\theta_{left_1})^H M R(\theta_{right_1}) R(\theta_{right_2}) = \Sigma$$

where

$$\begin{aligned} R(\theta_{left_1}) &= T_{\alpha}G(\psi)T_{\delta}, \\ R(\theta_{left_2}) &= R(\theta_{sym})R(\theta_{SVD})N, \\ R(\theta_{right_1}) &= T_{\gamma}, \\ R(\theta_{right_2}) &= R(\theta_{SVD})N. \end{aligned}$$

Using this method, the SVD of the complex matrix can be thought of as a pair of two-sided transformations. The first transform produces a real matrix, while the second set makes it diagonal. It should be noted that because all of the individual transformation matrices are unitary, the two-sided transformation matrices are also unitary, and therefore their products are unitary transformation matrices. U and V are therefore

$$R(\theta_{left_1})R(\theta_{left_2}) = U,$$

and

$$R(\theta_{right_1})R(\theta_{right_2}) = V,$$

giving the complete SVD as in (2.1).

#### **2.4** SVD of an $n \times n$ Matrix

The singular value decomposition has been known for over 100 years, but only recently have efficient, stable algorithms for computation of the SVD of general matrices been introduced. One algorithm that has been examined is the cyclic Jacobi method [6]. The original algorithm was intended for finding the eigenvalues of symmetric real matrices. It was later modified to perform for the SVD of real, square matrices. Kogbetliantz [11] showed that it was straightforward to extend Jacobi's method to arbitrary square complex matrices.

The algorithm begins with an  $n \times n$  matrix A. First, the pair of off-diagonal elements,  $a_{ij}$  and  $a_{ji}$ , that have the largest combined magnitude, with i < j < n, are chosen. Indices i and j are chosen such that

$$|a_{ij}|^2 + |a_{ji}|^2 = max\{|a_{pq}|^2 + |a_{pq}|^2\},\$$

where p and q represent the index into the matrix for all possible combinations of p and q, with  $i \neq j$  and  $p \neq q$ . This allows us to select largest off-diagonal matrix elements for elimination. To eliminate these elements, the matrix

$$\left[ egin{array}{cc} a_{ii} & a_{ji} \ a_{ij} & a_{jj} \end{array}

ight]$$

is considered. The SVD of this  $2 \times 2$  matrix is performed, which creates zeros at  $a_{ij}$ and  $a_{ji}$ . In order to propagate the effects of the SVD of this submatrix, larger  $n \times n$ rotation matrices are constructed from smaller  $2 \times 2$  transformation matrices T, with

$$R_{pq} = \begin{cases} 1, & \text{if } p = q \text{ and } p, q \neq i, j, \\ T_{11}, & \text{if } p = q = i, \\ T_{12}, & \text{if } p = i \text{ and } q = j, \\ T_{21}, & \text{if } p = j \text{ and } q = i, \\ T_{22}, & \text{if } p = q = j, \\ 0, & \text{otherwise.} \end{cases}$$

The entire matrix A is then multiplied by the larger transformation matrices R. Then the next largest pair of off diagonal elements is chosen, and the process is repeated. The total magnitude of the off diagonal elements, given by

$$\sum_{p=1}^{n} \sum_{q=p+1}^{n} |a_{pq}|^2 + |a_{qp}|^2 \tag{2.6}$$

is reduced at each step. When this sum has fallen to below some preset threshold, the matrix is considered to be diagonal and the process stops.

There are a few problems with actually implementing this algorithm. First, it is necessary to examine n(n-1)/2 possible pairs of off-diagonal elements to select the best pair for elimination. In addition, since this algorithm iterates until the sum of the off-diagonals, as given in (2.6), has fallen below some acceptable threshold, the off-diagonal matrix elements must each be examined at every iteration to compute the sum of their magnitudes.

The first concern is dealt with by [3], where efficiency is sacrificed for completeness. What is suggested is to simply not consider which off-diagonal pair reduces the total sum the most. Every pair of off diagonals gets eliminated in turn. Because of the fact that after each pair of off-diagonals is eliminated, the sum of the magnitudes of the off-diagonal elements as given by (2.6) is either reduced or stays the same, the extra computations required using approach do not corrupt the matrix, however, more than the minimum number of computations will be performed. When this is compared to the extra complexity required to inspect the entire matrix, the suggested modification becomes an acceptable tradeoff. Each pass through the matrix eliminating every possible off-diagonal pair is considered to be a complete *sweep*.

The second concern is dealt with in [7]. While no proof for the exact rate of convergence of the off-diagonals has been offered, extensive simulations of the algorithm reveals that the required number of sweeps through the matrix is nearly constant for a large variety of input matrices. For instance, when matrices of sizes ranging from n = 4 up to n = 100 were simulated, the difference in the average number of sweeps and the maximum number of sweeps required was less than 1. It was also found that average number of sweeps required for convergence with n = 100 was only six more than the average number required with n = 4. This data shows that even for varying values of n, a fixed number of sweeps can be chosen for the array. By examining the number of sweeps needed for convergence through simulation with an upper bound for n, a fixed value can be chosen such that the SVD will complete nearly all the time. Due to the invariance of the number of sweeps required for convergence for different values of n, n can be allowed to vary, within limits, with convergence nearly guaranteed. In addition, if the matrix has not finished converging to the preset threshold when the fixed number of sweeps is complete, the off-diagonal elements will have been steadily reduced througout the computations, and the values on the diagonal elements will be close approximations of their final values. That is, they will not be completely unrelated interim results. This means that if this approach is employed, a near constant processing time is achieved in exchange for possibly having a slight error introduced in certain cases, making it useful in real-time processing applications.

#### 2.5 Parallel Computation of the SVD

An advantage of the cyclic Jacobi method is that with each elimination of an off-diagonal pair, only the rows and columns that contain the pair are affected. By exploiting this fact, the modification suggested by [3], where every possible pair is eliminated, becomes significantly less time consuming to implement than if each elimination is performed sequentially. Because only the two rows and two columns that contain the pair are affected by each elimination, up to n/2 eliminations can be performed simultaneously. The time for a complete sweep through the matrix is now, at best, n-1 time steps, where each elimination requires one time step. This reduces the time required from  $O(n^2)$  to O(n).

A parallel ordering scheme is suggested in [2] that can be used to maximally exploit the parallelism possible through this algorithm, insuring that it only takes n-1 time steps to complete a sweep. This parallel ordering is illustrated for the n = 8 case:

| (1, 2) | (3,4)  | (5,6)  | (7, 8) |

|--------|--------|--------|--------|

| (1, 4) | (2, 6) | (3,8)  | (5,7)  |

| (1, 6) | (4, 8) | (2,7)  | (3,5)  |

| (1, 8) | (6, 7) | (4, 5) | (2, 3) |

| (1, 7) | (5, 8) | (3, 6) | (2, 4) |

| (1, 5) | (3, 7) | (2, 8) | (4, 6) |

|        |        | (4, 7) |        |

where (i, j) means that an elimination of  $a_{ij}$  and  $a_{ji}$  takes place.

This ordering naturally suggests an implementation on a parallel array of  $n \times n$ processing elements, however, the amount of communication required to realize this implementation is enormous. At some point, each processor has to communicate with every other processor. It is unwieldy to implement an array in which each processor has a direct communication link to every other processor for any reasonably sized array. The alternative is fixed communication paths, but this leads to long communication latencies, requiring excessive times for messages to pass from one side of the array to the other.

This implementation also requires that every processor element have equal computation ability. However, only a small fraction of the time will any given processor element have to perform difficult computations, such as those required to generate the rotation angles. The majority of the time, a processor is applying an angle calculated by some other processor in its row or column. As a consequence, complex functional units are required for all processors, but are idle most of the time. An alternative architecture has been suggested that moves the matrix in the array to simulate the new selection of (i, j) pairs, while allowing the actual processor elements that calculate the rotation angles to be the same in each time step [3]. Therefore, only 2n processor elements need the complex functional units required for computation of the rotation parameters, and the remaining elements only need simple multiplication and addition units to apply the rotation angles. The drawback of this arrangement is that it becomes difficult to arrange the eliminations such that the singular values of the larger matrix are in non-increasing order down the diagonal when computation stops because it is difficult to predict where a given data element will be after each shift of the data. It becomes easier to reorder the matrix after the computation of the singular values has finished.

A possible implementation of this algorithm is described in [3]. A more thorough implementation is described in [7]. An approach similar to that of [7] is taken, with modifications to increase the efficiency of the algorithm and some changes to increase the performance of the individual processor elements. Many parallel implementations of this architecture have been suggested [2, 16, 13], but most attempt to map the algorithm onto existing hardware, similar to the simulations run in [7] on the Connection Machine CM-5. To maximize the performance using a real time system, specialized hardware must be designed, and the algorithm must be modified by shifting the data to perform the complex angle calculations using a few, fixed processor elements.

## Chapter 3

### Systolic Processor Array

The systolic array represents a unique balance between the possible limitations of finite processing power and finite communications capability. Too often, a large problem is tackled by simply throwing more computational units at it, with little heed to the problem of moving data around. However, at this point in time, processing power has become inexpensive enough that it is not the limiting factor. No matter how fast a processing element is, it cannot realize its full potential if it does not have any data to work on. The systolic array takes both factors into account, and attempts to achieve an optimal balance, so that the system's resources can be efficiently used.

#### 3.1 The Systolic Array

The notion of the systolic array was first developed at Carnegie-Mellon University in the late 1970's [12]. The systolic array is a number of relatively simple processing elements connected together, usually in a linear or mesh-like pattern. Each processing element communicates only with its nearest neighbor. This arrangement means that the communications load is distributed throughout the array. As a consequence, it also means that only certain types of problems are amenable to implementation on a systolic array. The problem must be one where a fixed amount of data is applied against another fixed amount of data repetitively. An example of this type of problem would be one-dimensional convolution [12]. This problem is well suited for implementation using a linear array of processors. For this problem, a vector of data, X is convolved with a vector W of weights, and the result Y is given by

$$y_n = \sum_{m=0}^n x_m w_{n-m}$$

Each element of X is eventually multiplied by every element of W. As a consequence, a relatively small amount of data goes into the array, and a small amount of data goes out of the array, but in order to perform the calculations, a large amount of data must flow throughout the array.

One possible way to implement the convolution is to move the weights and the data vectors linearly through the array in opposite directions, multiplying them when they meet, and to have the resulting sums stay in each systolic processor element. Each weight sees each data point as they pass by each other, and each processor element accumulates the sum of each datum multiplied by each weight. After the weights and the data are moved through the array, the convolution vector Y remains to be shifted out of the processor elements.

It is important to note that only certain problems can be mapped efficiently into systolic arrays; they are meant to balance communication bandwidth with processing power. If the problem requires more of one or the other, then a systolic array will be inefficient. Fortunately, singular value decomposition can be mapped very efficiently onto a systolic array. To implement the singular value decomposition on a systolic array, the problem must be broken down into a series of smaller problems. Using the method for computation of the SVD given in the previous chapter, the problem can be implemented as a two-step process. First, the rotation angles needed to perform the SVD must be calculated, and then applied to the rows and columns of the particular submatrix being diagonalized. To calculate the rotation angles, the processor only needs access to the four elements of the submatrix being worked on. After calculating the rotation angles, it can then pass these values on to other processors that are handling the problem of applying the rotation matrices to the rest of the rows and columns. Remembering that the problem can be arranged such that only a few processors need to be able to calculate rotation parameters, this would suggest a possible architecture in which the diagonal processor elements can calculate the rotation parameters, and the off-diagonal processors apply them.

### 3.2 The Brent-Luk-Van Loan Systolic Array

A systolic array for computation of real SVD has been suggested in [3]. This approach starts with an array of processors that is  $n/2 \times n/2$  in size. Each processor,  $P_{ij}$ , operates on a small submatrix

$$\left[ egin{array}{cc} lpha_{ij} & eta_{ij} \ \gamma_{ij} & \delta_{ij} \end{array}

ight],$$

Initially, the processor element  $P_{ij}$  is loaded with a submatrix of A

$$\begin{bmatrix} a_{2i-1,2j-1} & a_{2i-1,2j} \\ a_{2i,2j-1} & a_{2i,2j} \end{bmatrix}$$

The diagonal processor elements contain the necessary hardware to calculate the rotation parameters, and the off-diagonal elements only contain enough processing capability to apply these parameters.

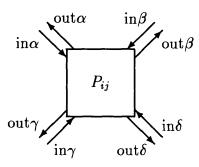

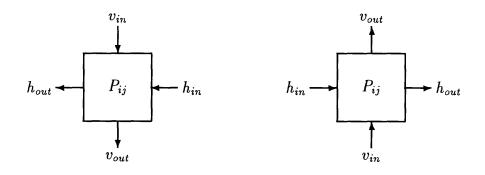

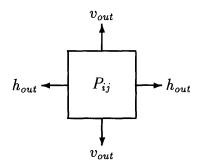

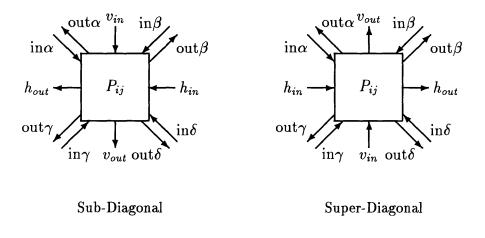

When computation begins, the processors on the diagonals of the array,  $P_{ii}, 1 \leq i \leq n/2$ , compute the rotation angles necessary for diagonalization of their data matrix. These rotation matrices affect only the data values in the same row and column of the array as the submatrix being diagonalized. By utilizing the communication links suggested in [3], it is possible to move the data through the array to maintain this special relationship between the data in the diagonal processor elements and that in the off-diagonal elements, while carrying out the suggested parallel ordering to maximize computational efficiency. These data flow interconnections can be seen in figure 3-1. Recalling that parallel ordering coupled with the suggested data flow paths allowed all angle computations to be carried out in the diagonal processor elements of the suggest of the suggest

Figure 3-1: Dataflow Connections for Each Processor Element

ements, the processors on the diagonal of the array are more important than those above and below the diagonal. In fact, the off-diagonal processor elements become slave processors, applying values generated elsewhere to the data values they contain. The angle parameter connections for the off-diagonal processors are illustrated in figure 3-2, and the connections for the diagonal processor elements are depicted in figure 3-3. As shown, the angle connections become very different for the off-diagonal processor elements and the diagonal processor elements. It should be noted that the sub-diagonal processor elements,  $P_{ij}$  with i > j, have just the mirror image of the super-diagonal processor element,  $P_{ij}$  with i < j, connections. This set of diagonal

Sub-Diagonal Super-Diagonal

Figure 3-2: Rotation Parameter Flow for Off-Diagonal Processor Elements

connections represent the complete set of data pathways needed in the array. When combined, a schematic representation of the data connections for the off-diagonal pro-

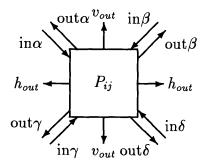

Figure 3-3: Rotation Parameter Flow for Diagonal Processor Elements

cessor elements is produced, as in figure 3-4 and for the diagonal processor elements in figure 3-5. These connections are assembled into a representation of the complete

Figure 3-4: Complete Interconnections for Off-Diagonal Processor Elements

Figure 3-5: Complete Interconnections for Diagonal Processor Elements

array. The processor interconnections at the edges of the array were handled in a

slightly different way to tie up all loose connections. Formally, these interconnections can be represented by

$$\operatorname{out}\alpha_{y,x} \Leftrightarrow \begin{cases} \operatorname{in}\alpha_{y,x}, & \operatorname{if} y = 1, x = 1; \\ \operatorname{in}\beta_{y,x}, & \operatorname{if} y = 1, x > 1; \\ \operatorname{in}\gamma_{y-1,x}, & \operatorname{if} y > 1, x = 1; \\ \operatorname{in}\delta_{y-1,x-1}, & \operatorname{if} y > 1, x > 1. \end{cases} \quad \operatorname{out}\beta_{y,x} \Leftrightarrow \begin{cases} \operatorname{in}\alpha_{y,x+1}, & \operatorname{if} y = 1, x < \frac{n}{2}; \\ \operatorname{in}\beta_{y,x}, & \operatorname{if} y = 1, x = \frac{n}{2}; \\ \operatorname{in}\beta_{y,x}, & \operatorname{if} y = 1, x < \frac{n}{2}; \\ \operatorname{in}\gamma_{y-1,x+1}, & \operatorname{if} y > 1, x > 1. \end{cases}$$

$$\operatorname{out}\beta_{y,x} \Leftrightarrow \begin{cases} \operatorname{in}\alpha_{y,x+1}, & \operatorname{if} y = 1, x < \frac{n}{2}; \\ \operatorname{in}\beta_{y,x}, & \operatorname{if} y = 1, x < \frac{n}{2}; \\ \operatorname{in}\gamma_{y-1,x+1}, & \operatorname{if} y > 1, x > 1. \end{cases}$$

$$\operatorname{out}\beta_{y,x} \Leftrightarrow \begin{cases} \operatorname{in}\alpha_{y,x+1}, & \operatorname{if} y > 1, x < \frac{n}{2}; \\ \operatorname{in}\beta_{y-1,x+1}, & \operatorname{if} y < \frac{n}{2}, x > 1; \\ \operatorname{in}\beta_{y-1,x+1}, & \operatorname{if} y < \frac{n}{2}, x > 1; \\ \operatorname{in}\gamma_{y,x}, & \operatorname{if} y = \frac{n}{2}, x > 1; \\ \operatorname{in}\beta_{y,x+1}, & \operatorname{if} y = \frac{n}{2}, x < 1; \\ \operatorname{in}\beta_{y,x+1}, & \operatorname{if} y = \frac{n}{2}, x < \frac{n}{2}; \\ \operatorname{in}\beta_{y,x}, & \operatorname{if} y = \frac{n}{2}, x < 1. \end{cases}$$

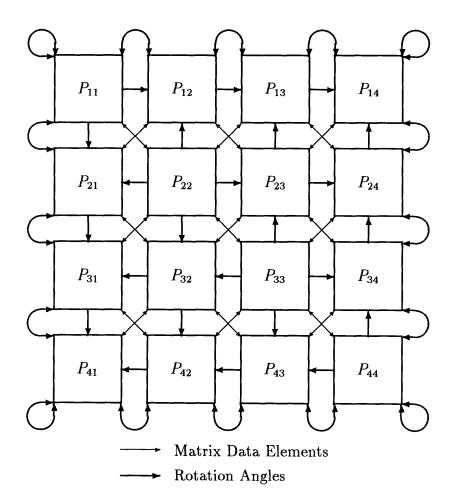

A complete  $4 \times 4$  array utilizing these interconnections can be seen in figure 3-6. For

Figure 3-6: Example Systolic Array

the array with n = 8, one sweep through the array requires 7 time steps to complete.

In order to move the data to take advantage of the parallel ordering scheme being used, data must be exported out of the processing nodes according to the interchange algorithm presented in [3]. At the end of each time step, the data in each processing element is made available on its outputs for the adjacent processor elements according to:

$$\begin{array}{c} \operatorname{if} y = 1 \ \operatorname{and} x = 1 \ \operatorname{then} \\ \left[ \begin{array}{c} \operatorname{out} \alpha \ \leftarrow \ \alpha & \operatorname{out} \beta \ \leftarrow \ \beta \\ \operatorname{out} \gamma \ \leftarrow \ \gamma & \operatorname{out} \delta \ \leftarrow \ \delta \end{array} \right] \\ \\ \operatorname{else} \ \operatorname{if} y = 1 \ \operatorname{then} \\ \left[ \begin{array}{c} \operatorname{out} \alpha \ \leftarrow \ \beta & \operatorname{out} \beta \ \leftarrow \ \alpha \\ \operatorname{out} \gamma \ \leftarrow \ \delta & \operatorname{out} \delta \ \leftarrow \ \gamma \end{array} \right] \\ \\ \operatorname{else} \ \operatorname{if} x = 1 \ \operatorname{then} \\ \left[ \begin{array}{c} \operatorname{out} \alpha \ \leftarrow \ \beta & \operatorname{out} \beta \ \leftarrow \ \alpha \\ \operatorname{out} \gamma \ \leftarrow \ \alpha & \operatorname{out} \beta \ \leftarrow \ \beta \end{array} \right] \\ \\ \operatorname{else} \\ \end{array} \right]$$

$$\begin{array}{c} \operatorname{else} \left[ \begin{array}{c} \operatorname{out} \alpha \ \leftarrow \ \gamma & \operatorname{out} \beta \ \leftarrow \ \delta \\ \operatorname{out} \gamma \ \leftarrow \ \alpha & \operatorname{out} \beta \ \leftarrow \ \beta \end{array} \right] \\ \\ \operatorname{else} \\ \end{array} \right] \\ \\ \operatorname{else} \\ \end{array} \left[ \begin{array}{c} \operatorname{out} \alpha \ \leftarrow \ \delta & \operatorname{out} \beta \ \leftarrow \ \gamma \\ \operatorname{out} \gamma \ \leftarrow \ \beta & \operatorname{out} \beta \ \leftarrow \ \gamma \end{array} \right] \\ \\ \operatorname{else} \\ \end{array} \right]$$

Then, after the outputs have propagated to adjacent processors,

$$\left[\begin{array}{cccc} \alpha \ \leftarrow \ \mathrm{in}\alpha & \beta \ \leftarrow \ \mathrm{in}\beta \\ \gamma \ \leftarrow \ \mathrm{in}\gamma & \delta \ \leftarrow \ \mathrm{in}\delta \end{array}\right]$$

This details how data flows in the fully systolic Brent-Luk-Van Loan systolic array.

### 3.3 Changes to the Brent-Luk-Van Loan Array

The systolic array for real-valued SVD presented in [3] has been used a starting point and extensive modifications have been applied to it. Such modifications were necessary because the original design was intended for real-valued matrices. Most importantly, by expanding this array to handle complex-valued data elements, the SVD algorithm has changed from a single cycle to a two cycle algorithm. Originally, the complete SVD of the  $2 \times 2$  submatrix contained in each processor was completed prior to any data interchange. In the array for complex SVD, the angles used to make the submatrix real can be made available prior to the entire SVD completing. In addition, the original array was fully systolic; that is, each processor was connected only to its nearest neighbors. This is not absoultely required, as long as care is taken when making compromises to not destroy the overall systolic nature of the array.

To improve performance, a compromise was made in that a fully systolic implementation, in this case, would introduce unnecessary delays. It was decided that the rotation angles generated by the diagonal processor elements would be broadcast throughout their rows and columns. In the original array, there was a long delay associated with propagating rotation parameters to off-diagonal nodes, applying those rotations in the off-diagonals, and then propagating the resultant data back to the diagonal element. Only after this could new rotations be started. As a consequence, each processor element was active for only one in three cycles, with each step in a sweep of the array being three cycles long. This is a major inefficiency of the Brent-Luk-Van Loan array.

Complex SVD is a two-stage process which allows some pipelining to take place in the interest of streamlining computations and increasing efficiency. In [7], the two-step SVD is arranged so that each processing element is active for two cycles out of four, with each step of a sweep being comprised of 4 cycles. Even with this advancement, the efficiency of the array is 50%. It is this efficiency, coupled with external design considerations, that necessitated the broadcasting of the rotation parameters.

The major disadvantage of a partially systolic architecture to a fully systolic one is that the partially systolic array has some limitations on the maximum size to which it can grow. When real-world external design considerations are taken into account, other, possibly more severe limitations may be placed upon the array size. Without any external hardware, a fan-out of 10 from the diagonal processors to the off-diagonal processors is acceptable. Thus, an  $11 \times 11$  array would be possible without the need for any external logic. This processor array could handle data matrices up to  $22 \times 22$ in size, having 121 processing elements. Assuming that each processing element costs approximately \$500 yeilds a total array cost of over \$60,000. With the addition of one additional buffer per diagonal element, effectively quadrupling the limiting size of the array, the cost for the complete system grows to nearly \$250,000. In addition, as the data arrays become large, the amount of time needed to complete each sweep, and therefore to diagonalize the entire matrix, grows to be prohibitively long for use in real-time systems. It is these real-world design limitations, in addition to the increased performance, that makes the decision to sacrifice the fully systolic nature of the array suitable.

It should be noted, however, that the individual processor elements have been designed in such a way that they do contain all of the necessary hardware for a fully systolic implementation. Only the internal programming of the processors would need to be changed, in addition to the timing control and the wiring of the array. The fully systolic implementation requires a different number of cycles per sweep step, and a different amount of time per cycle. The details of the data interchange in a two-step, complex-valued, fully systolic array are given in [7].

Knowing that the rotation parameters will be broadcast throughout the array, the processor cycles can be optimized in such a way that the overall efficiency of the array increases to each processor being active for two cycles out of three, with each step in a sweep through the matrix being comprised of three cycles. The actions of each processor during the three cycles are summarized in table 3.1. The off-diagonal

| Cycle | Diagonal processor                        | Off-Diagonal processor                                              |

|-------|-------------------------------------------|---------------------------------------------------------------------|

| 1     | Calculate angles to make ma-<br>trix real | Idle                                                                |

| 2     | Calculate angles for real SVD             | Apply angles that made sub-<br>matrix in diagonal processor<br>real |

| 3     | Finish applying angles for real SVD       | Apply angles from diagonal<br>processor real SVD                    |

Table 3.1: Processor Cycle Usage

processors are only active for 2 out of 3 cycles. Because there are n(n-2)/4 more

off-diagonal than diagonal processors, this limits the efficiency of the array.

The algorithm used in the processor elements is a direct adaptation of the algorithm given in section 2.3. For the first cycle, the diagonal processor elements calculate the component angles of  $\theta_{left1}$  and  $\theta_{right1}$ , which are the angles needed to make the matrix real and upper triangular. Next, these angles are made available to the off-diagonal processors, which were idle during the first cycle. During the second cycle, the diagonal processor elements first compute the angles needed to make the real, upper diagonal matrix symmetric, and then the angle needed to make it diagonal. These angles are then broadcast. During this cycle, the off-diagonal processors apply the rotation angles previously received. For the third cycle, the diagonal processor elements finish applying the rotation angles needed to make the matrix diagonal. To make all of the rotation angles available as early as possible, use of the rotation angles in the diagonal elements is delayed until the third cycle. At this point, the off-diagonal processors also make use of these angles, applying them to the rest of the matrix. At the end of the third cycle, the data matrix is interchanged between processors as given in the interchange algorithm in (3.1).

Following the data interchange, the process repeats for a specified number of sweeps through the array. At this time the off-diagonals have converged to values below a certain preset threshold. The data is available to be unloaded from the array. To rapidly load and unload the array, a second set of interconnections, along the columns of the array, have been inserted. When the array is to be initially loaded, the data enters the top of the array and is passed down the array by rows until the array is full. After the array is loaded, the data connections down the columns are no longer used, and remain dormant until the processing is complete, at which time the data is unloaded out the bottom of the array. Separate communications channels were provided for loading and processing due to the fact that the method by which the data is inserted into and extracted from the array is implementation dependent, and the flexibility of the array is compromised by assuming that certain pathways always exist. Therefore, having extra channels for loading and unloading was considered an acceptable design tradeoff because this allows the core processor elements to remain unchanged for a variety of implementations.

Although the unitary matricies U and V from (2.1) are being generated, they are not being saved. Only the final result matrix,  $\Sigma$ , is retained. It would be simple to construct additional hardware that attaches to the edges of the array and collects the rotation matrices being generated by the diagonal processors. These matrices can be multiplied together to recover U and V.

# Chapter 4

### Systolic Processor Elements

The highest possible computational throughput while maintaining a reasonable cost are the primary design goals of the processor elements used in the systolic array. When considering the compute engines used in the array, the assumption made is that each node has a specified number of communication channels for transmission of the matrix data rotation angles. The functionality of the processors has been dictated by the mathematics of the algorithm, however, the implementation details have not been restricted beyond this criteria.

#### 4.1 **Processor Element Design**

There are two major design methods that might have been used to implement the individual processors: they could have been constructed from off-the-shelf parts like commercial digital signal processors, or they could be designed using custom VLSI parts. In order to meet the design goals of the system, it was found that implementation of the individual nodes in commonly available commercial parts would have been complicated and expensive. The individual nodes would have needed a DSP in addition to external hardware to handle the I/O requirements and program store. This would have increased the cost and complexity. In addition, the algorithm calls for complicated functions, in the form of trigonometric routines or square roots. Existing DSP's do not implement these algorithms in hardware, so their computation is accomplished using a multi-cycle iterative routine, which adversely affects performance. In addition, a DSP includes some features that would go unused in the systolic architecture.

By implementing the design in custom VLSI, the processor can be made algorithm specific. Functional units can be added or removed depending on whether or not they are needed. In addition, different functional units that offer varying levels of performance while maintaining the same functionality can be used, allowing for performance tradeoffs in the interest of reducing cost. With the common availability of high-level design tools, and accessibility to fabrication resources, the total cost for a VLSI implementation is lower than for a DSP-based system.

In addition to the price/performance advantage that VLSI implementations can offer, there is a great deal of flexibility in the design details of the processor. For example, the processor can be designed to use an arbitrarily large word size. The algorithm in question can be simulated to determine the amount of round-off error introduced through the computations, and the processor word size can be adjusted accordingly. Commercial DSP's are available in a few word sizes, usually 16 or 24 bit, and beyond that, they typically use floating point representations. In a design such as this, to have 24 bits of accuracy in the final result may be require a 26 bit internal representation. In custom VLSI, this is simple to realize. In a commercial DSP, it is often necessary to use double length representation, which invariably requires more computational time to implement. The VLSI implementation allows a previously unavailable match between the hardware and the algorithm.

#### 4.2 Functional Unit Design

To calculate the singular value decomposition, it is necessary to calculate certain trigonometric functions. The algorithm presented in section 2.3 presents an implementation that trades these trigonometric functions for square roots and inverse square roots. This tradeoff was made in the interest of simplicity. Making this change allows the algorithm to deal explicitly with the sine and cosine of the rotation angles and not the angles themselves. The angles are not needed, so it would be inefficient to calculate them. Also, by broadcasting the sine and cosine of the rotation angles instead of just the angles, the off-diagonal processor elements do not need complicated functional units. They implement a matrix multiplication, which only requires multiplication and addition. Simplicity in the off-diagonal processors has been traded for communication bandwidth, since twice as much data is now being sent from each diagonal processor.

The decision to calculate the SVD algebraically, as opposed to trigonometrically, dictated a change in the functional units. There have been many designs presented for efficient computation of the inverse and the square root [10, 8, 5, 9]. Expanding on these works, a fast interpolation cell was constructed for computing either the square root or the inverse square root of a value in 6 clock cycles, which is noticeably faster than any other multi-cycle method. Extensive research has gone into numerical methods for these computations. Iterative routines require a non-constant time for completion, making instruction scheduling difficult. Having a constant-time functional unit for these calculations allows the processor central controller to be simpler, and therefore smaller.

Another advantage to this cell is that most trigonometric functions can be implemented in a reasonable time with the addition of external hardware that would be present in almost any design, such as a multiplier. The interpolation cell adds to the flexibility of the design; it could be re-used in another system that had no need for trigonometric functions, or, by making use of the inverse square root capability and a multiplier, it could be used as a divider. One of the design goals of this system was to allow the functional units to be useful in other designs, and the interpolation cell was found to be the most flexible.

Other implementations of the SVD on systolic processor arrays [7, 4] make use of CORDIC [20] functional units. The CORDIC algorithm is primarily used for direct implementation of geometric problems. It can calculate sines, cosines, tangents, arc sines, arc cosines, arc tangents, products, square roots, and quotients. However, to implement each function, a particular CORDIC unit must include hardware specific to the computation. To calculate a value, the CORDIC algorithms iteratively converge to the desired result at a linear rate of one bit of output per time step. This means that for each angle calculation using 24-bit internal word representations, it takes a full 24 clock cycles to complete. As the word size increases, the amount of time required for the computations increases linearly. While the CORDIC algorithms represent a common set of algorithms for direct implementation of a wide variety of functions, improved performance is achieved by using a smaller number of optimized cells that implement specific functions.

In comparison, the functions that the CORDIC engines calculate can be simulated by a few more cells in less time, and the performance benefit of the interpolation cell grows as the desired word size increases. The amount of time required for computation of functions in the interpolation cell increases at a rate significantly less than linear as word size increases. The interpolation cell is discussed in chapter 5. The CORDIC implementations may be less complicated, using more regular design, but the amount of area they require is comparable to the area required for the interpolation cell.

While the CORDIC engine can perform direct computation of the square root, however, it is much slower due to the performance limitations inherent in its design. The amount of time required to perform the square root of a reasonably large word can be greater than the time required for a general-purpose DSP which uses an iterative method. While the CORDIC algorithms present methods for making very powerful functional units, the flexibility they offer is outweighed by the amount of time they require for processing.

### 4.3 **Processor Element Architecture**

One of the key issues in the design of the processor elements was for the implementation to be useful as a flexible framework for a variety of algorithm specific processors. They were designed to make no assumptions about the data flow through the processor that might limit their flexibility. This regular design of the processor elements also makes the inclusion or exclusion of functional units simple, yielding an open architecture.

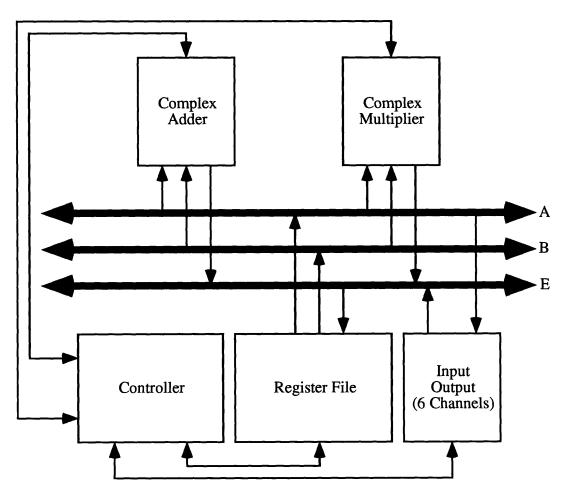

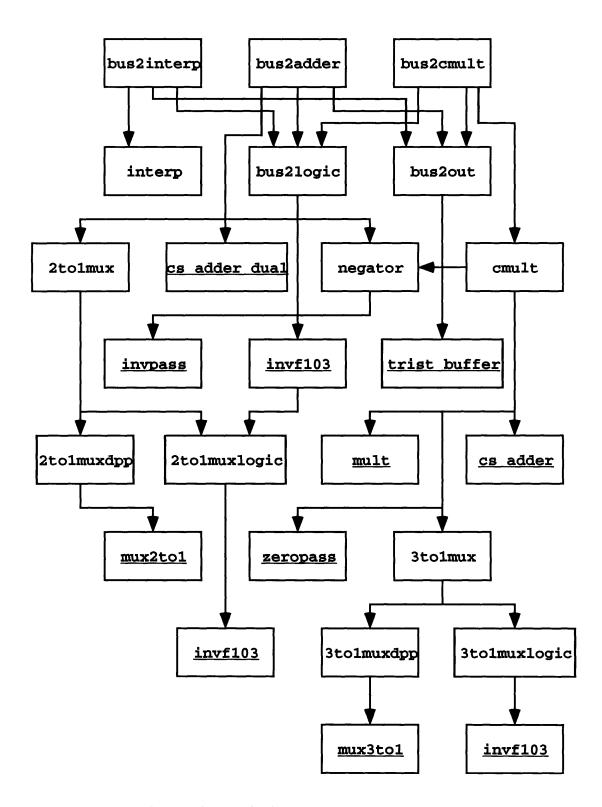

The architecture that was used required that all functional units be connected to at least one of two operand busses, and one result bus. Data storage is handled through a register file. A functional unit works by reading one or two parameters off of the operand busses, and presenting its result on the result bus. By enforcing a standard interface for all functional units, it becomes easy to make changes in the set of functional units contained in a given processor. Although some efficiency may be lost through requiring every result to be written back into the register file, any performance gain achieved by providing short cut paths between the functional units would be outweighed by this limitation on the design's flexibility and generality.

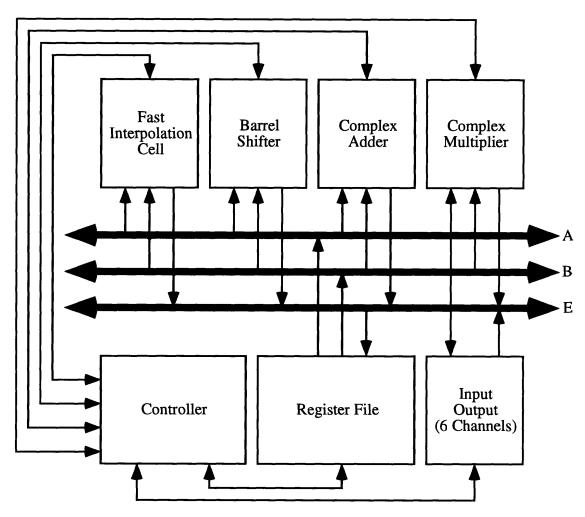

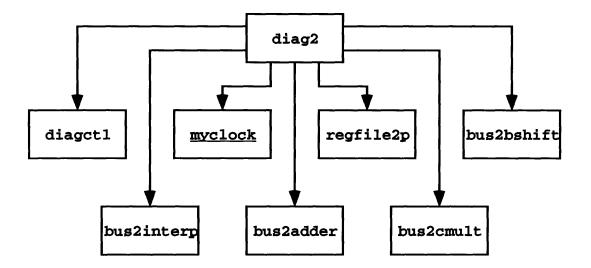

The basic blocks used in these processors included complex multipliers, complex adders, register files, interpolation cells, barrel shifters, and off-chip input/output blocks. The block-level design for the off-diagonal processor can be seen in figure 4-1 and for the diagonal processor in figure 4-2, where the A and B busses represent the operand busses and the E bus represents the results bus. The only part of the processors that depends on which functional units are installed is the central controller. This unit must be designed with every change to the processor. However, by using a high-level description of the controller's functionality in a form closely resembling assembly language, the effort required to implement changes is minimal.

As can be seen in figures 4-1 and 4-2, the functional units of the off-diagonal processor are a subset of those in the diagonal processor. The difference between the two processors is in the controller. This similarity can be used in an attempt to keep prototyping costs down. One chip can be designed that implements the functionality of both processors. The controller unit could be modified to examine some external state input to tell the processor whether or not it is on a diagonal of the array. If it is, it runs the diagonal processor routines, and if it is not, it behaves as an off-diagonal processor, and does not use its interpolation cell or its barrel shifter. This single part is useful for small prototyping runs, as only one processor needs to be fabricated.

Having the controller for the processor elements as a separate unit, as opposed to being distributed throughout the design, allows more freedom in the design of

Figure 4-1: Block Diagram of Off-Diagonal Processor Element

the controller. It is currently implemented as a finite state machine, using a PLA lattice to store the program. However, the program can be implemented in the form of an internal or external program store that could be dynamically loaded. In this configuration, which would not require extensive changes, the processor could function as a small, application-specific digital signal processor. The particular algorithm could be loaded at run time, and could be changed at any time, even when the processor is running. Thus, a new class of custom DSP's could be created where the designer is free to specify the capabilities necessary for a particular application. It would not be limited to an application-specific integrated circuit, because it would be programmable.

Additional flexibility is gained by having all of the functional units share inputs and outputs. This insures that only the necessary control information was required

Figure 4-2: Block Diagram of Diagonal Processor Element

at the inputs to the cell. For example, if true and complement values of a control signal were required, only the true signal is propagated; the complementary signal is generated locally. While this may have made for more complicated functional units, with each unit typically requiring a small section of random logic used for control signal generation, it made for a more standard interface. The flexibility afforded by this is that multiple versions of the same functional unit can be created, with differing levels of performance and size. For instance, a complex multiplier might have a start control input, a busy control output, two operand inputs A and B, and one result output E.

Three different multipliers were created in the course of this design. One design used the fastest available cells, which used large numbers of parallel carry paths and other speed optimizations. The second model used more space conservative design techniques, but was essentially the same architecture, with the first two performing complex multiplication by using four real multipliers and two real adders, allowing for a complete complex multiplication in a single cycle. The third design, made further tradeoffs in an attempt to minimize area. It used a single multiplier of the type used in the second model, and two real adders. It had registers to hold the temporary values, and it required four clock cycles to complete a computation. It multiplied the real part of **A** first by the real part of **B** and saved it, then by the imaginary part of **B** and saved that. Next it repeated these steps with the imaginary part of **A**. Finally, it summed the real parts and the imaginary parts.

By requiring a standard interface with start and busy inputs, multi-cycle computations are provided for. In the first two multipliers, the busy input could just be tied to the start input. In the third multiplier, the controller that handled the multiplications would also have to generate the busy signal given the start signal. Requiring a least common denominator set of interface signals can cause some inefficiencies, but at the same time, it provides a level of abstraction for the designer that makes it much simpler to meet design objectives about performance and cost. Since the three multipliers all shared a common interface, they could be used interchangeably, depending on the area and time requirements of the system. The first multiplier was an order of magnitude faster and larger than the third, which shows that there can be a wide variance in performance and size, with identical functionality. The layout area and computation times for these three multipliers can be seen in table 4.1.

| Multiplier | Multiply Time (nsec) | Area $(mm^2)$ |

|------------|----------------------|---------------|

| 1          | 40                   | 124.98        |

| 2          | 80                   | 45.90         |

| 3          | 350                  | 13.67         |

Table 4.1: Comparison of Three Different Complex Multipliers

Every attempt has been made to provide hierarchical levels of abstraction throughout the design of the processors. Individual functional units can be hand optimized for the best performance, with no change required in the overall design. As much of the design as possible has been automated, so that the designer can focus on what is needed, as opposed to how to get it. However, some of this abstraction can cause inefficiencies in the system. In the example implementation, discussed in chapter 7, the provision for multi-cycle addition and multiplication has been removed, because this feature greatly increases the complexity of the controlling program, as status lines must be monitored after each instruction to determine when the functional unit has completed its computation. The size and performance of the single cycle implementations were found to be acceptable, removing the need for the multi-cycle implementations.

There is a tradeoff of simplicity versus performance. As was the case with the multi-cycle provision, by limiting some of the functionality of the individual units, the levels of abstraction start to disappear; the designer is no longer insulated from implementation specific details. However, with small modifications at the highest levels of the system, large performance gains can be achieved. As the modifications affect the inner workings of elements in the design, the performance benefits of optimizing the design for a specific algorithm decrease, to the point where the benefits that the abstraction provide to the ease of design outweigh the potential improvements. Exactly where this threshold lies depends on the performance requirements of the processor.

# Chapter 5

### **Fast Interpolation Cell**

There exist a number of classical methods for designing hardware for computation of only a few mathematical functions. Typically, any digital signal processing hardware will contain some combination of multipliers and adders. For algorithms that require more complicated functions, there are few options. For some cases, the function can be implemented in the form of a look-up table. However, for an input word size of more than about 16 bits, the memory required becomes prohibitively large. For some functions, iterative routines, in which an initial guess is successively refined until it is considered to be a match to the desired value, can be used. In order to be able to realize a function in an iterative algorithm, there must exist a way to evaluate the error in the estimate. An example of such a function would be the square root. While it is not possible to find the square root of a number x using only multiplications and additions, it is possible to evaluate how close an estimate y is to  $\sqrt{x}$ . This is accomplished by examining the error function, given by  $e = x - y^2$ . Based on this error, y is modified to minimize e.

Even though certain functions can be implemented using iterative routines, the execution time required depends on the goodness of the initial estimate, how quickly the chosen minimization routine converges, and on the rate of change of the function itself. To make the abstraction that the functional unit requires a fixed amount of time to complete, which makes instruction scheduling significantly less difficult, the amount of time allocated to the algorithm needs to be long enough that it will converge

even in the worst case. This leads to inefficient implementations where the processor sits idle as the routine may complete early. This inefficiency can be reduced by either allowing for variable processing time, or by making use of an entirely different method that works in fixed time. The latter approach was chosen because it offers increased efficiency without additional complexity in the processor controller.

#### 5.1 Interpolation

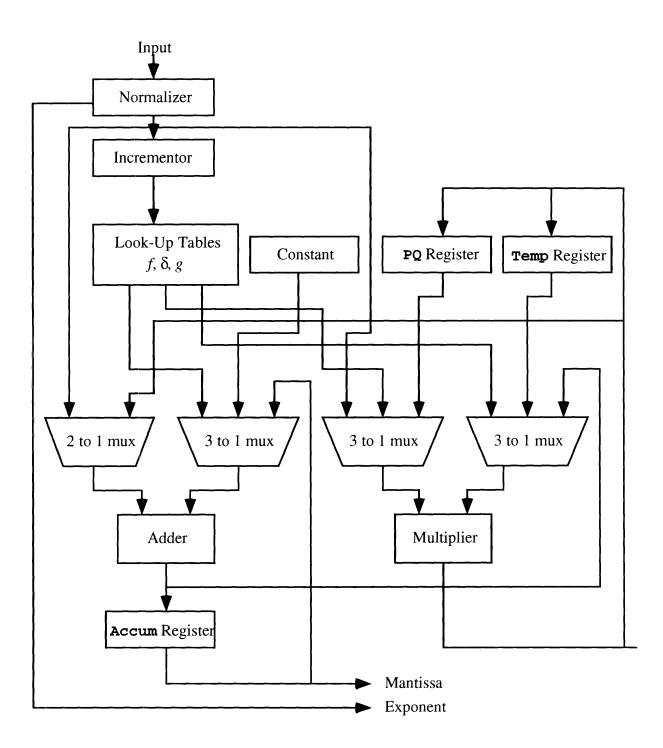

An alternative to iteration will be considered. For interpolation, the problem is to make an educated guess of the value of the function at any point, given only the values of the function at selected points. This is accomplished by making assumptions about the behavior of the function in between the given points. The simplest method assumes that the function is linear. For a slowly varying function, with the selected data points fairly closely spaced, this is an acceptable approximation. In this case, the value of the function f(x) at a given point x is given by

$$f_i(x) = \frac{x - x_i}{x_{i+1} - x_i} f(x_i) + \frac{x_{i+1} - x}{x_{i+1} - x_i} f(x_{i+1}),$$

(5.1)

where  $x_i$  and  $x_{i+1}$  are the points at which the corresponding values of the function f(x)are given, and  $f_i(x)$  is the interpolated value of f(x). This is a linear interpolation, where the desired function is modeled as a straight line, and the model is matched to the actual function at the two points  $(x_i, f(x_i))$  and  $(x_{i+1}, f(x_{i+1}))$ .

The error in the interpolated value can be reduced by choosing a better approximation to the desired function f(x). It only takes two points to completely determine a line, so using this as our model for f(x) only allows an exact match of the desired function at two points. To match more points, a more complicated model must be choosen. One approach is to expand f(x) into its Taylor series. If  $x = x_i + a$  then

$$f(x_i + a) = f(x_i) + af'(x_i) + \frac{a^2}{2!}f''(x_i) + \cdots,$$

(5.2)

where  $f(x_i)$ ,  $f'(x_i)$ ,  $f''(x_i)$ , ... are known, allowing an accurate approximation for