# The Impact of Indirect Distribution Strategies on Supply Chain Operations

by

Mark A. Parrish

B.S., Operations Research Studies (Mechanical Engineering)

United States Military Academy, 1987

Submitted to the Department of Mechanical Engineering and the Sloan School of Management in Partial Fulfillment of the Requirements for the Degrees of

Master of Science in Mechanical Engineering and Master of Science in Management

in conjunction with the

Leaders for Manufacturing Program

at the

Massachusetts Institute of Technology

June 1995

© 1995 Massachusetts Institute of Technology. All rights reserved.

| Signature of Au | thor -  |                                       |                                                                                                                                |

|-----------------|---------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

|                 |         |                                       | Department of Mechanical Engineering                                                                                           |

|                 | /. /    |                                       | Sloan School of Management<br>May 12, 1995                                                                                     |

| Certified by    |         |                                       |                                                                                                                                |

|                 | 1       |                                       | Seering, Professor of Mechanical Engineering nent of Mechanical Engineering Thesis Advisor                                     |

| Certified by    |         |                                       |                                                                                                                                |

|                 |         | Donald                                | B. Rosenfield, Senior Lecturer of Management<br>and Director, LFM Fellows Program<br>Sloan School of Management Thesis Advisor |

| Accepted by     | <i></i> | · · · · · · · · · · · · · · · · · · · |                                                                                                                                |

|                 |         |                                       | Ain A. Sonin<br>Chairman, Graduate Committee                                                                                   |

|                 |         | MASSACHUSETTS<br>OF TECHNO            | INSTITUT Department of Mechanical Engineering                                                                                  |

AUG 31 1995 Barker Eng

# The Impact of Indirect Distribution Strategies on Supply Chain Operations

by

### Mark A. Parrish

Submitted to the MIT Department of Mechanical Engineering and the Sloan School of Management in Partial Fulfillment of the Requirements for the Degrees of

Master of Science in Mechanical Engineering

and

Master of Science in Management

### **ABSTRACT**

Manufacturers deliver product to market through direct sales and distribution, indirect distribution channels, or some mix of the two. But what of the challenge facing firms committed to changing from one distribution strategy to another? This thesis explores this question in detail through an evaluation of the server market in the computer and electronics industry. The objective of the thesis is to substantiate the hypothesis that a change in distribution strategies from direct to indirect channels significantly impacts business practices and manufacturing processes.

Within the server market, indirect channel partners provide benefits to both manufacturers and end users alike. However, these benefits bring with them associated costs. One of the largest of these costs, and the one most difficult to manage by corporations adopting channel strategies, lies in the area of quality assurance.

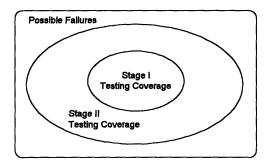

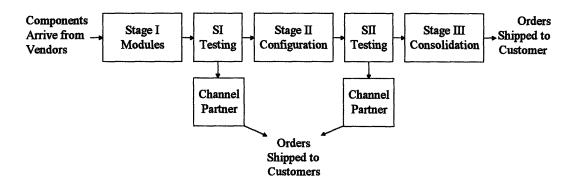

Server manufacturing occurs in three value-added stages—module manufacturing, system configuration, and order consolidation. Current quality assurance strategies call for testing to occur at the end of each stage. Such strategies are based on a "safety net" approach that relies upon later testing to capture escaped faults from earlier test steps. However, under an indirect distribution strategy this safety net is removed as product departs the manufacturing process prior to arriving at the later test station.

A mathematical model is created to determine the cost of lost quality associated with changing distribution strategies. The results of this model indicate that traditional methods of quality assurance, those that rely on increased test coverage to gain greater process yields, are incapable of meeting the challenge posed by an indirect distribution strategy. Manufacturers can only compete in the channels' arena by adopting a comprehensive strategy that optimizes both business practices and manufacturing processes around its distribution model. Finally, to ensure success this strategy must be pursued with a demonstrated commitment to channel partners' success.

Thesis Advisors:

Donald B. Rosenfield, Senior Lecturer of Management Warren Seering, Professor of Mechanical Engineering

### ACKNOWLEDGMENTS

The research presented in this thesis was performed under the auspices of the MIT Leaders for Manufacturing Program, a partnership between MIT and thirteen major U.S. manufacturing companies. I am grateful to the LFM partners for their support throughout my MIT experience. Their continued dedication to LFM and its ideals provides encouragement and inspiration to those committed to American manufacturing excellence.

Of these companies, I especially wish to thank Digital Equipment Corporation for its unlimited support of my internship and this work. Within Digital I wish to extend a personal word of gratitude to several key individuals.

Thank you, Joan Hurley, Hank Rauch, and Chris St. Cyr, for allowing me to engage the company early on in the process before my internship commenced. Thank you, Eugene McCabe, for your willingness to pick up the supervisor responsibilities so late in my internship. And thanks to the product development team for your energy, encouragement, and commitment to my endeavors.

I wish to extend a few very warm and special thanks to three individuals that made my Digital experience particularly rewarding. Thank you, John Doyle, for your counsel and for always knowing where to go for corporate resources—truly a jack of all trades and a master of many as well. Thank you, Dave Citorik, for your continued support throughout the internship and beyond. And thank you, Mary Doddy, for your supervision, your seminal efforts at tying manufacturing to a channels strategy, and for your continued friendship even after departing the company. I have benefited immensely from our association.

I wish to extend a word of gratitude to my advisors, Don Rosenfield and Warren Seering. Don, thank you not only for your support on the internship and thesis, but also for your venerable guidance throughout my LFM experience. I look forward to maintaining our association as an alum. And Warren, thank you for your leadership and for always insisting that I was the customer. Your guidance and project management skills have provided me as much insight into the world of management as your knowledge and expertise have in engineering. I am grateful for your balance.

In closing, I would be remise if I failed to acknowledge those women most special to me. Thank you, Allison, for your understanding, patience, and unending words of encouragement and praise. I look forward to now supporting your endeavors. And thank you, Elizabeth and Emily, for your infinite smiles and hugs so graciously given. Through your innocence you continually remind me of how much I have yet to learn.

To my father-in-law, Col. Gaines M. Timberlake, USAF (Ret.), who departed this world for the next during my tenure as an intern at Digital Equipment Corporation. Let it be written here for all to witness:

He fought the good fight.

We miss you dearly, Sir.

# **Table of Contents**

| CHAPTER 1 INTRODUCTION                                        | 7  |

|---------------------------------------------------------------|----|

| 1.1 COMPUTER AND ELECTRONICS INDUSTRY EVOLUTION               | 7  |

| 1.2 COMPANY BACKGROUND                                        | 8  |

| 1.3 STATEMENT OF THE PROBLEM.                                 | 10 |

| 1.4 Thesis Objectives                                         | 10 |

| 1.5 SCOPE AND LIMITATIONS                                     | 11 |

| 1.6 Thesis Overview                                           |    |

| CHAPTER 2 PROJECT BACKGROUND                                  | 13 |

| 2.1 THE SERVER PRODUCT DEVELOPMENT TEAM                       | 13 |

| 2.2 THE SERVER MARKET                                         |    |

| 2.3 Literature Search.                                        |    |

| 2.3.1 How Channels Impact the Manufacturing Discipline        |    |

| 2.3.2 Channels of Distribution: A Foundation                  |    |

| 2.3.3 Thesis-Related Literature                               |    |

| CHAPTER 3 SERVER CHANNELS OF DISTRIBUTION                     | 23 |

| 3.1 SERVER CHANNEL PARTNERS.                                  |    |

| 3.1.1 Resellers                                               |    |

| 3.1.2 Distributors                                            |    |

| 3.1.3 Value Added Resellers (VAR)                             |    |

| 3.1.4 Systems Integrators (SI)                                |    |

| 3.1.5 Original Equipment Manufacturers (OEM)                  |    |

| 3.1.6 Independent Software Vendors (ISV)                      |    |

| 3.2 CHANNEL BENEFITS                                          |    |

| 3.3 CHANNEL PARTNERS AS CUSTOMERS.                            |    |

| 3.4 MEETING CHANNEL NEEDS THROUGH BUSINESS PRACTICES          |    |

| 3.4.1 Pricing                                                 |    |

| 3.4.2 Training                                                |    |

| 3.4.3 Packaging                                               |    |

| 3.5 WHY CHANNELS NOW?                                         |    |

| 3.6 THE COST OF DOING BUSINESS WITH CHANNEL PARTNERS.         |    |

|                                                               |    |

| CHAPTER 4 SERVER MANUFACTURING AT DIGITAL                     |    |

| 4.1 STAGE 1: MODULE MANUFACTURING                             |    |

| 4.2 STAGE 2. SYSTEM CONFIGURATION                             |    |

| 4.4 Testing Strategy                                          |    |

|                                                               |    |

| 4.4.1 Stage I Testing                                         |    |

| 4.4.2 Stage 2 Testing                                         |    |

| 4.4.3 The Testing "Safety Net"                                |    |

| 4.5 CHANNEL STRATEGY MANUFACTURING IMPLICATIONS               |    |

| 4.5.1 How Channels Might Work at Digital                      |    |

| 4.5.2 Module Quality Assurance Through Channels               |    |

| 4.5.3 A Modeling Approach                                     |    |

| CHAPTER 5 MATHEMATICAL MODEL OF SERVER QUALITY                |    |

| 5.1 THE MODELING PROCESS                                      |    |

| 3.1.1 Mase 1: Capturing and Normalizing the Donor Nerver Pata | 46 |

| 5.1.2 Phase 2: Translating the Normalized Data                                                | .48 |

|-----------------------------------------------------------------------------------------------|-----|

| 5.1.3 Phase 3: Applying Current Test Detection Capabilities to the Translated Data            |     |

| 5.2 SUMMARY OF FINDINGS                                                                       | 49  |

| 5.3 OPTION 3: CAPITAL INVESTMENT IN TEST STRATEGY REDESIGN                                    | 50  |

| 5.4 REVISITING THE OTHER OPTIONS                                                              |     |

| 5.5 CRITIQUE OF MODELING METHODOLOGY                                                          | 53  |

| CHAPTER 6 CONCLUSIONS AND RECOMMENDATIONS                                                     | 55  |

| 6.1 Thesis Summary                                                                            | 55  |

| 6.2 MAJOR CONCLUSIONS                                                                         | 55  |

| 6.3 RECOMMENDATIONS FOR FURTHER STUDIES                                                       | 56  |

| 6.3.1 Channel Migration                                                                       |     |

| 6.3.2 Partners in the Life Cycle                                                              | 57  |

| BIBLIOGRAPHY                                                                                  | 59  |

| APPENDIX A SAMPLE CHANNEL PARTNER NEEDS                                                       | 63  |

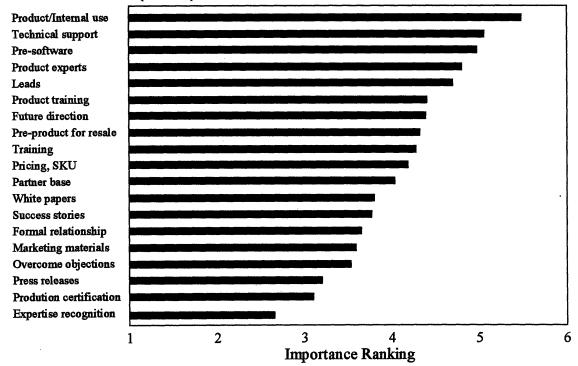

| A.1 SME VARs (TIERED)                                                                         |     |

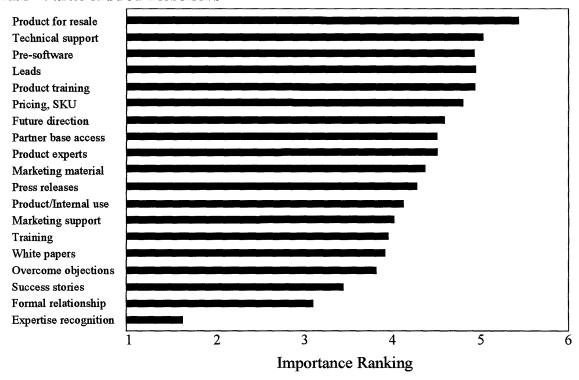

| A.2 VALUE ADDED RESELLERS                                                                     |     |

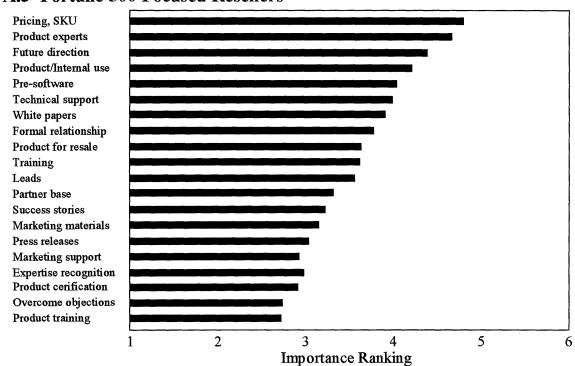

| A.3 FORTUNE 500 FOCUSED RESELLERS                                                             |     |

| A.4 Independent Software Vendors (also known as Commercial Developers).                       |     |

| A.5 Systems Integrators                                                                       |     |

| APPENDIX B SERVER MANUFACTURING PROCESS FLOW                                                  |     |

| APPENDIX C QUALITY MODEL SAMPLE DATA                                                          | 70  |

| PHASE 1: CAPTURING AND NORMALIZING THE DONOR SERVER DATA                                      |     |

| Actual Donor Module #1 Captured Data:                                                         |     |

| Actual Donor Module #1 Captured Data:  Actual Donor Module #2 Captured Data:                  |     |

| Actual Donor Module #2 Captured Data:  Actual Donor Module #3 Captured Data:                  |     |

| Sample Normalized Stage I Test Assembly Defect Rates (per million leads)                      |     |

| Sample Normalized Stage I Test Component Defect Rates (per million components)                |     |

| Sample Normalized Stage Field Failure Module Defect Rates                                     |     |

| Sample Calculation of Total Defect Opportunities and Complexity Scaling Factor                |     |

| PHASE 2: Translating the Normalized Data                                                      |     |

| Sample of New Server's Stage I, Module #1 Translated Defect Rates Across All Failure Modes    |     |

| (Calculated from Normalized Donor Data)                                                       | 76  |

| Sample Translation of New Server's Defect Per Module Rates from Normalized Donor Data for Six |     |

| Modules Across all Manufacturing Stages                                                       |     |

| PHASE 3: APPLYING CURRENT TEST DETECTION CAPABILITIES TO THE TRANSLATED DATA TO ARRIVE AT     |     |

| STAGE I ESCAPE RATES                                                                          |     |

| Sample Calculation of New Server's Stage I, Module #1 Defect Escape Rates                     | .77 |

| APPENDIX D INVENTORY CALCULATIONS                                                             | 78  |

# 1.1 Computer and Electronics Industry Evolution

Darwin's theory of biological evolution postulates that genetic mutations occur in response to environmental stimuli. These mutations propagate through a natural selection process until they become characteristic of the species, by which time new stimuli have initiated the next adaptation (Darwin, 9). I find this same adaptive evolution process an effective descriptor of the events that have occurred in the computer and electronics industry. Using this parlance, the industry is now entering its third generation of adaptive evolution. I refer to the three as the Genesis, the Technology Proliferation, and the Personal Computer (PC) Generations, respectively. Each generation is identified by a unique business model, and each has stimulated a new breed of company that has led to its demise.

International Business Machines (IBM) epitomizes the Genesis Generation. Spanning the 1940s and 50s, this era marked the dawning of the computer age. In response to Remington Rand's introduction of the UNIVAC (1951), IBM fielded its first commercial mainframe computer (the IBM 701, 1952). Through a direct distribution strategy reliant upon a sales force renowned for its white shirts and dark suits, IBM triumphed time and again with successes that spawned both subsequent generations (Hoover's Handbook Database, IBM).

In 1953 MIT's Lincoln Laboratory loaned a young engineer named Ken Olsen to IBM (Rifkin and Harrar, 22). Motivated by his sabbatical, Olsen gave life to the Technology Proliferation Generation with his creation of Digital Equipment Corporation (also known as DEC and Digital) in 1957. Spanning the 1960s and 70s, this generation avoided direct competition with IBM by creating niches on the industry behemoths' periphery. Characterized by Digital Equipment Corporation's business model and minicomputer

product line, companies succeeded by selling to end users both directly through a sales force and indirectly through Original Equipment Manufacturers (OEMs).

IBM's widespread introduction of the personal computer in 1981, and Digital's ability to leverage its distribution channels, provided the impetus for the PC Generation. Beginning in the 1980s and continuing to the present, this generation's business model mutation occurred in the area of product development and distribution. Where I classify the first two as technology-driven, successful manufacturers of this third generation now provide market-driven products to end users through indirect channels of distribution. Corporate objectives focus on the optimization of business practices and manufacturing processes rather than on the innovation of highly technical products. Companies like Compaq Computer Corporation (Compaq), the world's number one manufacturer of PC-based client servers, epitomize this era.

It is within the context of this latest generation that I conducted the research for my thesis at Digital. The company hoped that I would join a host of others dedicated to its successful transition from one generation to the next. This thesis explores the challenge of such a transition from a manufacturing perspective by pursuing the impact of a best-in-class distribution practice on Digital's value chain

# 1.2 Company Background

In 1988 Digital Equipment Corporation enjoyed the enviable position of being number two (second only to IBM) in the computer and electronics industry while having one of its best years ever. The workforce approached 130,000 employees, sales were booming at \$12.7 billion by year's end, and net income cleared the invisible hurdle at \$1.07 billion.

However, within a few tumultuous years the company found itself in the red and leading the industry in layoffs and losses. Having faced rough times before, Digital dug in and prepared for battle. To survive this onslaught, it chose to re-engineer its business practices under the guide of a new leader, Robert Palmer.

In July of 1994 Palmer announced some of the latest re-engineering initiatives he wished to pursue. Among these was a renewed emphasis on indirect channels of distribution. What follows is an explanation of why.

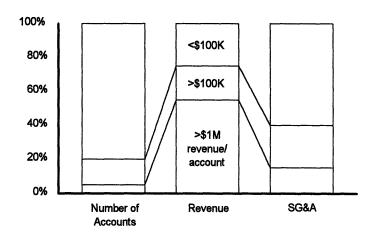

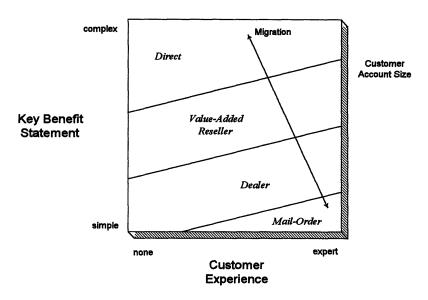

As shown in Figure 1.1, Digital's customer profile tells an insightful tale about the economics of the company's direct sales coverage. As testimony to the eighty-twenty rule, twenty percent of Digital's accounts contributed nearly eighty percent of its revenues. Even more startling, however, is the fact that in terms of the cost of doing business (as reflected in Sales, General and Administrative, or SG&A) these eighty percent were achieved through a mere forty percent of burden. Some industry analysts reasoned that Digital could literally become profitable over night if it simply stopped selling to the most costly eighty percent of its accounts!

Figure 1.1: Digital's Direct Coverage Economics (Palmer, 7)

A quick benchmarking calculation demonstrated that those companies relying upon indirect sales had SG&A's some ten percent lower than Digital's in terms of percentage of revenue (Digital=30%, Industry Standard=18-20%) (Pesatori, 14 Sep. 1994). Therefore, an indirect distribution strategy that aggressively incorporated channel partners in reaching the most costly accounts was proposed as a means of decreasing SG&A while maintaining revenues. With his July announcement Palmer accepted this proposal. The question now facing Digital was how to develop and build products that ensured profitability through indirect channels of distribution.

#### 1.3 Statement of the Problem

Within the manufacturing environment two schools of thought evolved around how best to address the question of how to develop and build products for channels. One school believed that change would only be necessitated in business practices and that the way Digital builds products will remain unchanged despite the shift in emphasis to indirect channels of distribution. The other school, however, believed that a change in distribution strategy, one that incorporated channel partners in the supply chain, brought with it a major change in customer base. These new customers would add greater demands—demands to be addressed not only through business practices but also through product and manufacturing process design.

This second school of thought is the focus of this thesis. In it I evaluate the shift in majority customer profile from end users to indirect channels partners. I substantiate the hypothesis that this change in customer profile has a significant impact on the supply chain with particular emphasis placed on the manufacturing link. This impact is, in fact, so significant that traditional quality assurance techniques cannot compensate for it. Finally, I accomplish both of these tasks through quantitative analysis based on my experiences as an external consultant to the management team of a new product development initiative in the server market.

# 1.4 Thesis Objectives

By writing this thesis I hope to accomplish three objectives. First, by circulating it within the product development team (PDT) I hope to increase their awareness of how channels affect their efforts. Second, by making it available throughout the rest of Digital and to the other Leaders for Manufacturing Program sponsors I hope to facilitate a channels discussion within the manufacturing community. Finally, I hope to bridge the gap between manufacturing and other business disciplines through a single document that captures the impact of business decisions on the manufacturing function of an enterprise.

This last objective is accomplished by gaining an understanding of Digital's current manufacturing processes and then using a mathematical model to determine the impact channels might have on them. Although tailored to one specific product line in the computer and electronics industry, the model can conceptually be adapted to any manufacturing process, or industry for that matter, to assess the impact of indirect distribution strategies on supply chain operations.

#### The thesis deliverables include:

- 1. a description of the channel's environment—the key players, their roles, and their interests.

- 2. a mathematical model for use in determining the expected quality of proposed products, and

- 3. a recommendation on where to best focus continued research on indirect channels of distribution.

# 1.5 Scope and Limitations

Within the thesis I describe in general terms the channels' environment and its importance to manufacturers. However, the quantitative analysis I conduct is limited in scope to a single server product within the computer and electronics industry. As such, its solution is unique to both this market and the challenges Digital faces in it. Nevertheless, the modeling *process* has numerous applications and lends itself to easy replication. Any enterprise interested in assessing the impact of an indirect distribution strategy on its supply chain management can conceptually adapt the model to its environment.

Because of the dynamic nature of the channels' environment there exists a temporal limitation on the accuracy of this study. It is but a snapshot of a continually evolving environment. The key channels players, their roles, and the resultant business models they spawn change so rapidly that even during the course of this writing the industry terms used to describe them varied. As the channels environment continues to evolve, so too might the industry within which this evolution occurs, bringing with it a new generation of business models and their associated challenges not addressed within this study.

Finally, this study only addresses in detail the channels' impact on manufacturing. As I highlight later in the thesis, manufacturing is but one of many communities impacted by a migration to indirect distribution. A thorough commitment to a channels strategy requires that the entire manufacturing enterprise adopt a new mindset on how to successfully conduct business with another company's profitability in mind.

## 1.6 Thesis Overview

I have divided the thesis by chapters and appendices into three sections. The first section covers thesis background data and includes Chapter 2 and Chapter 3. In Chapter 2 I discuss the background for my research. I include a description of the server market, my PDT, and a review of current literature on both channels and electronic testing. In Chapter 3 I present the server market's channels of distribution. I elaborate on why they are of significance now and what challenges manufacturers face in meeting their needs.

The second section covers the impact of indirect distribution strategies on supply chain operations and includes Chapter 4 and Chapter 5. In Chapter 4 I focus specifically on the impact of channels on manufacturing. I detail server manufacturing and testing processes and posit how they might change under an indirect distribution strategy. In Chapter 5 I describe a quantitative model created to substantiate my assertions and then use its results to calculate the additional investment in testing coverage needed to ensure quality through channels. From these calculations I conclude that the implications to manufacturing of pursuing an indirect distribution strategy are so significant that investment in traditional processes alone is not enough.

Finally, the third section covers thesis conclusions and ancillary data and includes Chapter 6 and Appendices A through D. I close the thesis in chapter six by summarizing my findings, presenting the conclusions drawn from them, and recommending areas for continued research. Throughout the text I frequently reference the four appendices that follow the chapters. In them I provide supplemental data and supporting documentation that the reader may find of interest.

# CHAPTER 2 PROJECT BACKGROUND

This chapter provides the context for the thesis research. In Section 2.1 I present the internal project environment by describing the organizational landscape within which I gathered data. In Section 2.2 I present the external project environment by providing an overview of the server market. Finally, in Section 2.3 I provide the results of a literature search on not only channels of distribution, but also on the thesis-relevant topics of business process reengineering, lean manufacturing, vertical integration, and electronic test strategy.

# 2.1 The Server Product Development Team

In response to the changes brought on by its reengineering efforts, Digital announced a reorganization into six product and service divisions in July of 1994. The reorganization chartered the Computer Systems Division (CSD) to provide the market with computer systems through three worldwide business units. The CSD built each of these business units around specific business models that reflected the purchasing patterns of the customers they targeted. The Accounts Business Unit dealt directly with the largest system accounts as illustrated in Figure 1.1. The PC Business Unit targeted the personal computer market through indirect mediums, emphasizing catalogue and telephonic sales. Finally, the Systems Business Unit (SBU) targeted the high-volume system market through indirect channels of distribution (LIVEWIRE, 18 Jul. 1994).

The SBU's Alpha Systems Business Group is responsible for designing and manufacturing computer systems based on Digital's proprietary Alpha chip technology. The proposed server I address throughout this thesis falls into this category. The server PDT consisted of numerous design and manufacturing engineers that reported directly to a management team. This team consisted of representatives from each of the business group's disciplines.

The role within which I conducted my research was as an external consultant to the manufacturing representative to the PDT management team. In accordance with the CSD charter and the reengineering objectives laid out by Palmer in his announcement, the team defined for itself the mission of designing the next server as a "channels ready" product. Their intent was to incorporate channel partner needs directly into the server design, manufacturing, and distribution processes. I was to facilitate the incorporation of these needs into new product and process design by gathering data on "Design for Channels" principles. I would then use this data to assess the impact to manufacturing of switching from a direct to an indirect distribution strategy in the server market. Part of my assessment was to included recommended areas for additional investment. Methods of data collection at my disposal included quantitative modeling, published literature, customer interviews, benchmarking studies, on-site studies of the proposed manufacturing facility for the new product, and the support of previous server PDTs.

# 2.2 The Server Market

Enterprises that purchased data processing capability during the Genesis and Technology Proliferation Generations grew heavily reliant upon mainframes and minicomputers for their needs. However, the <u>Financial Times</u> last year reported that of these companies nearly half anticipate a shift to client-server computing in the next few years (Manchester, 3). Dataquest, Inc., a computer industry analyst, reports that server shipments will grow in excess of eight percent per year through 1997. More noteworthy, however, is Dataquest's forecast of the midrange server segment growth at greater than twenty percent per year during the same period (Maltzman, 1). Why the projections of steady server market growth, and what of this midrange server category and its amazingly aggressive forecasts? Answers to these questions lie in the technology development and purchasing patterns found throughout the industry.

Client-server technology conceptually parcels computer systems into two domains. First, the client domain consists of the front-end, decentralized, user-interface components and typically includes a keyboard, monitor, and processing unit. The server domain consists of

the back-end, centralized components and may include storage, memory and code accessible by each of the client sites simultaneously (Manchester, 3). Analysts segment the server market by processing capability and price into four categories: mainframes/supercomputers, midrange servers, workstations, and personal computer servers (Maltzman, 2).

This segmentation reflects the shift mentioned earlier from mainframe and minicomputer processing to client-server computing. As the PC Generation evolved many large companies purchased personal computers and relied upon them to meet their distributed processing needs. However, as PC technology advanced the computing economies of scale offered by volume-built PC, or low-end, servers enormously increased. As a result, a pooling of these distributed PC resources into a network managed by low-end to midrange servers occurred. Based on PC technologies, these servers are now as advanced as many of the larger and more expensive systems they replaced.

From the largest customers' perspective servers offer affordable, no-frill mainframe performance. For small to medium-sized enterprises unable to fully utilize a mainframe's capabilities, servers offer an alternative solution. Finally, as Information Technology proliferates the business landscape, servers become an attractive means of managing the electronic networks that evolve. No matter whom the customer is, though, one fact is certain: Gone are the days when hardware technology drove purchasing patterns. The customer of today instead purchases business solutions, and is typically indifferent of the platform or software upon which that solution is derived. This fact does not sit well with manufacturers that differentiated themselves on hardware technology. As if that were not enough, customers are no longer alone in their purchasing decisions. An entire army of consultants has evolved with the market. For manufacturers these solution consultants take the form of channel partners that drive not only customer purchasing patterns but also manufacturers' business practices.

One of the companies most adept at dealing with channel partners in the server market is Compaq. As a PC Generation corporation, Compaq from its inception relied heavily upon channel partners. As its technology capabilities advanced and the popularity of servers grew, Compaq expanded its business model to include the server market. Its success thus far has been staggering and has established the best-in-class standard so many of its competitors now pursue.

Where technology had for years driven product strategies in the industry, Compaq chose to pursue product strategies driven by its distribution model (Raulerson, 1). Within two years of committing itself to a "channel ready" product strategy the company had increased net income 117 percent and captured over sixty-four percent of the PC Server market (as measured by units shipped). Even more amazing is Compaq's best-in-class SG&A following this model—an amazing 11.6% of revenue (King, 1). Compaq accomplished these feats through an aggressive relationship-building initiative aimed at ensuring channel partners' success. In chapter three I introduce channel-friendly actions like those taken by Compaq that assure success through indirect distribution.

## 2.3 Literature Search

I divide the results of my literature search into three sections. In the first section I present contemporary journal articles pertaining directly to the impact of indirect distribution strategies on supply chain management, with particular emphasis given the manufacturing link. These articles are critical references for those wishing to pursue a deeper understanding of the impact of a channels strategy on supply chain management and the manufacturing discipline. In the second section I present works that provide the foundation for an understanding of the channels' environment. While more general in nature, they address both the role and the management of channels. Finally, in the third section I briefly present a collection of books and articles considered relevant but not critical to a thorough understanding of the thesis.

## 2.3.1 How Channels Impact the Manufacturing Discipline

In his article entitled "The Distribution Revolution," Tim Davis addresses the impact of indirect distribution on the manufacturing discipline within several enterprises. Davis asserts that enlightened manufacturing firms, those realizing the benefits to be gained by partnering with channels, are learning new ways of adding value while cutting costs and increasing delivery speed. This is especially critical in the manufacturing industry, where the cost of direct distribution may be as much as forty percent of revenue. As evidence to support his assertion he presents several case studies from within the industry. At Tupperware, the distribution network has been incorporated into manufacturing via an automated storage retrieval system. By aggressively pursuing a more integrated approach to supply chain management, Tupperware has realized huge gains in efficiency without calling for workforce reductions. Finally, Davis offers Philips Consumer Electronics' efforts at distribution integration as the epitome of the enlightened manufacturing firm. Philips completely reengineered its design, prototyping, and testing processes for new products in order to shorten development times in support of its channel strategy (Davis, 43).

In his article entitled "Reinventing the Warehouse," William C. Copacino elaborates on Davis' assertion, claiming that companies now view their supply chains, and the role of distribution within these chains, differently. Copacino argues that there are three driving factors behind this change. First, technology is enabling firms to reengineer their business processes. Second, product flows are being optimized by leveraging new transportation service offerings. Finally, customer demands for lower costs, better customer service, and faster response times are reshaping how manufacturers deliver product to market. In response to this dynamic environment, some firms have chosen to redesign their supply chain around the role of the distribution center, or warehouse. By introducing concepts such as flexible manufacturing and flow-through distribution, and by outsourcing to distribution channels what once were considered value-added manufacturing activities, Copacino believes these responsive firms will leverage the logistics function as a powerful competitive advantage (Copacino, 32).

Kistner et al., in their report entitled "An Integrated Approach to the Development of Channel Strategy," point to the role of distribution channels in delivering satisfaction to the customer through product and service delivery. They argue that manufacturing firms cannot be successful without incorporating channel partners into both their strategic and product planning processes. To facilitate this process, they present a distribution strategy framework that manufacturing firms can use in seeking the optimal balance between corporate strategic goals and the interests of channel partners. This framework requires the manufacturer to view the channel as a customer, and to address the critical issues of channel loyalty, effectiveness and conflict. They present emerging trends and contemporary issues in industrial distribution as evidence to substantiate their strategic framework (Kistner et al., 315).

The Electronic Business Buyer specifically focuses on the issue of new product development that Kistner et al. alluded to in the above reference. In an article entitled "Distributors' New Services Save Time and Money," the journal reports that cost reduction efforts force manufacturers to outsource manufacturing activities. This results in an even greater incentive to partner early in the product development cycle with indirect channels of distribution. Early contact with the channels can result in lower development costs, as these key players combine customer knowledge with new technology in generating the right solution the first time. Fewer prototypes and on-time releases mean lower development costs for the manufacturer. Once the product is launched, several manufacturing tools can be extended to channel partners to facilitate their involvement in the later stages of the product life cycle. Just-in-time delivery to channels is feasible through inventory replenishment systems such as those mentioned in the Davis article. Computer networks that permit distributors to access manufacturers' finished goods inventories are growing in popularity. Finally, in-plant stores managed by channel partners are presented as a growing trend aimed at reducing material handling and order management costs ("Distributors", S7).

Most recently, the Spring 1995 Sloan Management Review included an article entitled "Channel Partnerships Streamline Distribution." Although focused on the retailer-supplier interface, the article provides a conceptual framework applicable to myriad channel relationships. Buzzell and Ortmeyer describe the benefits of a cooperative supply chain relationship between manufacturers and their channel partners. Among these benefits are greater inventory turns, improved customer service, reduced need for markdowns, and lower overall distribution costs. After outlining the key features of such a partnership, the authors discuss the reasons for the rapid growth these relationships have experienced throughout the decade. They close by presenting those facets considered requirements for a successful channel partnership to evolve.

#### 2.3.2 Channels of Distribution: A Foundation

While the references of Section 2.3.1 specifically addressed issues presented in this thesis, the following works are more general in nature and provide a broader perspective on distribution channels. The books presented below discuss the topics of channel management and their benefits. The journal articles presented below address the relationship between channels and manufacturing firms and the issue of channel conflict.

Stern and El-Ansary, Lewis, and Mallen all three provide excellent background research needed for understanding the workings of channels. Their works describe role specification, the use of power, and conflict management in the channels' environment. Woodside explores in depth the firm's activities from the perspective of both the manufacturer and the channel partner. Anderson and Weitz provide a study on the importance of commitment to channels strategy, emphasizing that pledges to these partners' successes can build and sustain critical relationships. Magrath and Hardy acknowledge that conflict between manufacturers and channels is inevitable but need not be unmanageable. They present strategies for coping with the issue of channel conflict. Rosenbloom provides a management focus to channels, emphasizing the knowledge needed to make more effective channel decisions. Finally, Urban and Hauser describe the role of channels in new product development. They elaborate on relative power between

manufacturers and channels, channel contributions to innovation, pricing to ensure channel partner success, and viewing channels as customers when developing product.

Forrest takes the Urban and Hauser argument one step further. He discusses the benefits offered by channel partners throughout the product life cycle, arguing that leveraged channels bring with them reduced development, production, order processing, and delivery cycle times (Forrest, 23). Adler echoes these sentiments and adds that channels need not fear competition from direct sales. He asserts that, although it is often difficult to prove the impact of channels on manufacturing, channels directly and significantly impact market share and revenues. Because of their knowledge of the market and the configuration services they offer, channel partners are uniquely qualified to provide greater satisfaction to a more sophisticated end user (Adler, "Direct" 151; "Soft," 249). There are numerous other works on the management of channels. The above references, however, provide a substantial basis of knowledge on the subject.

#### 2.3.3 Thesis-Related Literature

The following references are considered relevant but not critical to a thorough understanding of the thesis. As I present the thesis, there evolves a need to address business process reengineering as a possible solution to the challenges posed by channels. One must ask if reengineering is the result of poor processes, or whether it is simply necessitated by outdated policies and practices? To answer this question, Hayes and Wheelwright define reengineering as the necessary response manufacturers must take in surviving environmental changes brought on by technological shifts. Because server customers' expectations have grown with their technological sophistication, it is this definition that is pertinent to the channel's environment. In their work entitled Restoring Our Competitive Edge: Competing Through Manufacturing, the authors detail a strategy that addresses production facilities, equipment and management system selection, supplier relationships, and continuous improvement. Of particular importance, however, is their presentation in Chapter 10 of the challenges of managing changes in manufacturing's structure brought about by events such as a shift in distribution strategy.

Hammer and Champy, in their seminal work entitled Reengineering the Corporation: A Manifesto for Business Revolution, introduce the reengineering of business processes as the only way to sustain competitive advantage. They recommend changing mental models about how business is conducted as the path to success, emphasizing specific areas within the firm as ripe with reengineering opportunities. Williams provides a list of recommendations tailored to the needs of manufacturing firms pursuing reengineering. In her article "Ten Tips for Reengineering Manufacturing," she highlights fundamental rethinking of the supply chain, not simply patchwork, as necessary for achieving an optimal system solution (Williams, 12). Finally, Managing Office Technology, also addresses reengineering from a manufacturer's perspective in answering the ten most frequently asked questions pertaining to the topic ("Manufacturing," 22).

No presentation on supply chain management and optimization would be complete without addressing the issue of leanness. In <u>The Machine that Changed the World</u>, Womack et al. present a thorough study of the fundamental principles of lean manufacturing through an analysis of the auto industry. Additionally, Sohal and Egglestone capture what they consider are the core characteristics of world-class, lean manufacturing and distribution management in a comprehensive survey of fifty one Australian manufacturing firms (Sohal and Egglestone, 35).

Any firm considering farming out manufacturing tasks to channel partners must first comprehend the dynamics of vertical integration. Stuckey and White discuss the intricacies of such decisions in their article entitled "When and When not to Vertically Integrate." Vertical integration is defined as the means of coordinating different stages of the supply chain when inter-company partnerships *are not* beneficial. In this article, the authors present four reasons for vertical integration: 1) there exists a risky and unreliable market, 2) as a defense against market power, 3) to create and exploit market power, and 4) as a response to industry life cycle dynamics. Vertical integration is difficult to implement and costly to fix if overdone. For these reasons the authors advise that it be

avoided unless absolutely necessary. They recommend that managers consider quasiintegration strategies such as those addressed in this thesis before accepting the risk of full vertical integration.

Finally, in his article entitled "When is Software Ready for Release?", Michael Foody provides a commentary on the issue of quality assurance through testing. He elaborates on increased stress testing, hardware and software burn-in, and factory installed software testing coverage as a way of ensuring greater customer satisfaction (Foody, 35). The pertinence of these last references on business process reengineering, leanness, and testing strategies shall become more evident throughout the remainder of the thesis.

# CHAPTER 3 <u>SERVER CHANNELS OF DISTRIBUTION</u>

The manufacturer's role is to deliver customer satisfaction through a supply chain that encompasses all activities from raw material acquisition to the shipment of products to market. As the competition in maturing markets increases, leading manufacturers battle for their share of ever-shrinking margins by optimizing each link of this chain. Evidence exists that indicates optimization of the distribution link of the supply chain requires an intimate relationship between indirect channel partners and the manufacturer. Moreover, this evidence suggests that such a relationship is absolutely critical to business success in today's competitive server environment.

Channel partners' ability to customize (sometimes at quality levels higher than the manufacturer), deliver, and stock product, at costs below what manufacturers can achieve, establishes them as valued manufacturer customers. As with any customer, manufacturers must meet their needs through responsive Product (the "P" signifies the customers' perception of product as the aggregate of hardware, software and service) and process design. In this chapter I introduce indirect channel partners in the server market. I present their roles, interests, and the benefits they offer. I address the issue of why channels have come to play such a significant role in today's server supply chain. Finally, I address the impact to business practices that partnering imparts before transitioning to the manufacturing impacts in Chapter 4.

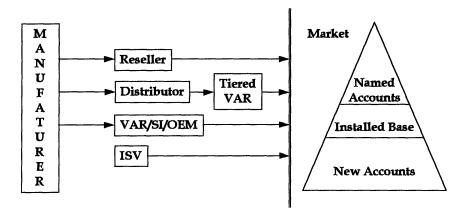

## 3.1 Server Channel Partners

I divide server channel partners into two categories—those that deal directly with manufacturers and those that do not. Both categories include multiple players that differentiate themselves by business model. Figure 3.1 illustrates the interaction of these channel partners as they facilitate the flow of product to market. The descriptions that follow are the result of a coalescence of research and interview data from across the industry. As the relationship between manufacturers and channel partners evolves so too

do the expected roles of channel participants. The details below are a snapshot of these dynamic expectations taken at the time of this writing.

Figure 3.1: Server Channels of Distribution (Partnering for Success, 7)

#### 3.1.1 Resellers

Resellers pursue a volume-based business model.. They extend the manufacturer's reach in the market by delivering high volumes of low-end, add-on, and upgrade products directly to end users. Resellers also provide end users with services in accordance with the terms and conditions identified in contractual agreements with the manufacturer. They stock inventory for immediate fulfillment to end users, provide rapid and convenient delivery, and aggressively solicit new accounts. Avnet, Wyle, and Pioneer Electronics are examples of resellers (Schavone, 50) (Lawrence, 2) (TNSG, 4).

#### 3.1.2 Distributors

Like resellers, distributors also pursue a volume-based business model. To achieve volume sales distributors partner with value-added resellers in a two-tiered relationship. Distributors solicit new VARs, provide them training on product configuration methods and new product introductions, and manage them as valued resources of the manufacturer. Hallmark, Intelligent Electronics, and Merisel are examples of distributors (Schavone, 50) (Lawrence, 2) (TNSG, 12).

### 3.1.3 Value Added Resellers (VAR)

Unlike its predecessors, VARs pursue a value-based business model. VARs focus entirely on designing, developing, and delivering complete business problem solutions to end users. These solutions may include hardware, software, and services. VARs drive manufacturing activities to align with market demands by completely customizing solutions to the needs of each customer. Cerner, Innovative Interfaces, and Informatica are examples of VARs (Schavone, 50) (Lawrence, 1) (TNSG, 18). The role of the tiered VAR business model resembles that of the direct VAR but, because of its smaller volumes, has been relegated to deal indirectly with the manufacturer through a distributor network.

### 3.1.4 Systems Integrators (SI)

System integrators pursue a value-added business model by fulfilling the role of full-service consultant within the server market. They specialize in selling and integrating products for complex solutions. SI activities include system requirements analysis, configuration, installation, and service support. General Electric, Andersen Consulting, and EDS are examples of firms possessing these capabilities (Schavone, 50) (Lawrence, 2) (TNSG, 48)

#### 3.1.5 Original Equipment Manufacturers (OEM)

OEMs pursue a value-added business model by imbedding the manufacturer's products into larger systems, or "turn-key" solutions, to control processes or monitoring activities. Typically the manufacturer's component represents a small portion of the total product and often looses its brand identity. MTS Systems, Honeywell, and Fisher Controls are examples of OEMs (Schavone, 50) (Lawrence, 2).

#### 3.1.6 Independent Software Vendors (ISV)

ISVs pursue a value-based business model The ISV is a source of application solutions and does not directly sell hardware platforms. However, they play a critical role in influencing end user purchasing behavior by recommending such platforms. As such, manufacturers must incorporate ISVs early in their product design phase to ensure

hardware and software compatibility. Oracle, Sybase, and Computer Associates are all examples of ISVs (Schavone, 50) (Lawrence, 3) (TNSG, 35).

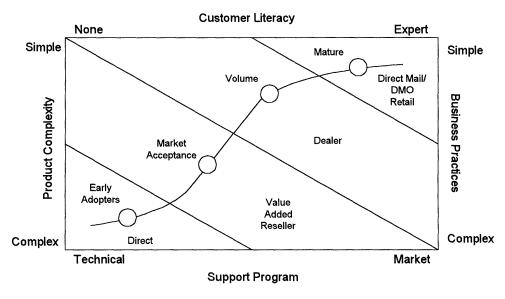

In closing this section I want to remind the reader that although the above descriptions are particular to servers, these channel partners have counterparts in nearly every industry and market. What any manufacturer must do in pursuing its particular channel's environment is to first identify a target market segment for its product. Once this task is accomplished the firm then determines the channels for its product based on several primary factors. These factors include market maturity, product complexity, channel partners' buying and selling approaches, level of end user sophistication, and product price points just to name a few. Manufacturers can optimize the flow of their product to market by leveraging the strengths of those partners most capable of dealing with these factors.

## 3.2 Channel Benefits

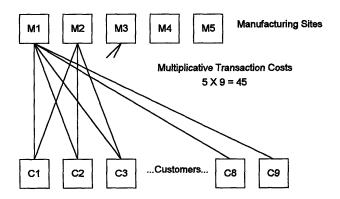

The manufacturer often has multiple sites responsible for delivering products to numerous customers. From a macro perspective this is analogous to multiple firms delivering products to numerous markets. Each of these deliveries has an associated transaction cost that typically includes overhead accounted for in SG&A. As illustrated in Figure 3.2, under a direct sales and distribution model these costs are multiplicative in nature.

Figure 3.2 Direct Distribution Transaction Costs (Hauser, Session 14)

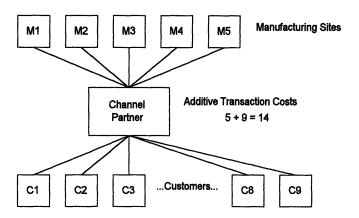

The immediate and most direct benefit of channels manifests itself in decreased transaction costs. Under an indirect distribution model a portion of the costs rolled up in SG&A are

additive rather than multiplicative. The go-between, or channel partner, provides efficiencies of scale the manufacturer is otherwise unable to obtain (see Figure 3.3).

Figure 3.3 Indirect Distribution Transaction Costs (Hauser, Session 14)

Additionally, the distribution efficiencies introduced by channels bring with them a decreased burden cost as firms eliminate no longer needed portions of the direct sales force. However, cost reduction is only a fraction of the benefits realized through channel partnering.

Not only do manufacturers recognize direct and immediate reductions in SG&A, they also benefit from economies of scale in a second way. As channel relationships evolve manufacturers gain increasing market representation through what I call the "feet on the street" phenomenon. The hypothetical manufacturer possessing a sales force of one thousand may, under an indirect distribution strategy, have ten times that many people pushing its product in the market. The decreased transaction and overhead costs, when combined with the feet on the street phenomena, actually result in increased market coverage at a lower SG&A (Rines, 2). In addition to this win-win effect, channel partners assist manufacturers by providing support services and local market knowledge while managing costly end user relationships. Finally, they also increase product availability to a loyal customer base by managing orders, inventory, and fulfillment.

Although I have to this point only addressed indirect distribution benefits to manufacturers, channels are also a source of greater end user satisfaction. Channel partners assist end users by providing increased product availability through rapid response and customization. They serve as consultants by advising end users on how to use products. Through the terms and conditions of their partnering contracts they are empowered to provide select warranty and guarantee services. Finally, they decrease customer search costs through multi-vendor offerings (Hauser, Session 14). One can imagine that with all this to offer both manufacturers and end users, channel partners can be justifiably demanding in their inter-corporate dealings. The logical follow-on question that becomes a major concern to manufacturing firms pursuing a channel strategy is, "What are the needs of this powerful new customer and how do I best meet them?"

#### 3.3 Channel Partners as Customers

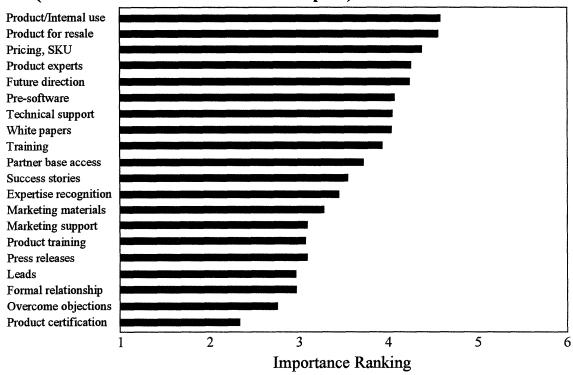

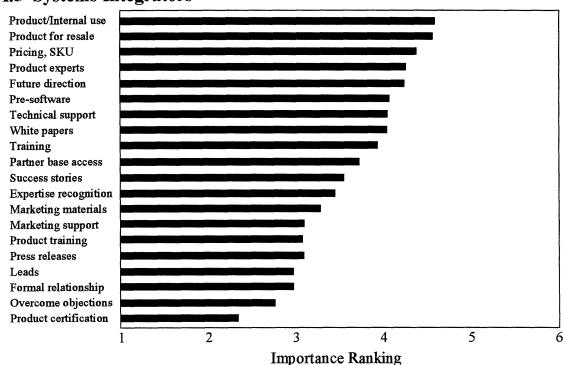

Not unlike any other customer, channel partners have particular needs that manufacturing firms must address to be successful. In a recent study of the server market one study captured numerous common values sought by channel partners (Hutchinson, 19). The following is a list, in order of priority, of the business practices and product attributes a large distributor listed as most valuable to a lucrative partnership.<sup>1</sup>

- 1. product availability

- 2. delivery performance

- 3. ease of doing business

- 4. return policies for faulty shipments

- 5. credit policies

- 6. relationships with sales people, account representatives, and customer service)

- 7. price as reflected in favorable discount terms

- 8. updated product information that is easily utilized

- 9. easy to understand price book and structure

- 10. breadth of product line and menu offerings

- 11. technical support via phone hotlines

- 12. pre and post-sale technical support programs

- 13. vendor authorization assistance

- 14. order integration and system configuration capability

- 15. technical training programs from the vendor

<sup>&</sup>lt;sup>1</sup> I have included additional examples of channel partner needs in Appendix A, Sample Channel Partner Needs.

- 16. product training, especially for new products

- 17. advertising support

- 18. technical marketing programs

- 19. general marketing support programs

- 20. installation support as needed

I divide the above list of needs into issues manufacturing firms address through business practices and manufacturing processes. Because the remainder of this thesis focuses on manufacturing, I have chosen to briefly present here several best-in-class business practices that address these needs.

# 3.4 Meeting Channel Needs Through Business Practices

When a firm commits to a channel strategy it no longer can simply concern itself with its own profitability. It must now recognize its success relies upon a symbiotic, if not at times precarious, relationship. One of the greatest signals a manufacturer can send a partner in making the transition to channels is the minimization of channel conflict through its business practices. Three channel-specific business practices, ones focused on the minimization of channel conflict, are reflected in the manufacturer's training, and packaging policies.

#### **3.4.1 Pricing (Need #7)**

Current server pricing practices rely on a discount off manufacturer's list price (MLP) in establishing the transfer price between channel partners and their manufacturing vendors. The vendor establishes the MLP through a market analysis that considers price-to-performance metrics and consumer pricing sensitivities. This market-minus pricing practice promotes channel conflict when the vendor's independent sales force, under the pressures of end-of-quarter quotas, undercuts channel partners by offering similar discounts directly to end users. Rather than being MLP based, channel pricing policies must instead be based on a cost-plus model. Such a model would incorporate the end user's perceived value of the product or its components no matter where in the supply chain the value is added. One such approach available to manufacturers wishing to pursue lucrative partner relationships is reflected in an economic value to the customer (EVC) pricing policy.

EVC is a value-based policy that assigns the relative value (defined as benefits per cost) a given product offers to its customers as that product's market price. This value equals the maximum quantity the customer would pay for the product given perfect competitive information (Forbis and Mehta, 233). If a manufacturer is efficient, the EVC price consists of the actual manufacturing cost plus some reasonable value-added premium. Under such a policy, no one player in the market feels victimized. The EVC market price is the best value—benefits per cost—available to the consumer at the time of purchase.

I find it useful to extrapolate the EVC concept to channel-vendor transfer prices in creating a cost-plus pricing policy under a channels strategy. Using this conceptual framework, each value-added manufacturing activity in the supply chain would have an associated economic value to the end user. This EVC would consist of the benchmarked, best-in-class manufacturing cost plus some premium reflective of manufacturing efficiencies. For those manufacturers approaching the best-in-class standard, this premium would be higher. An EVC would be assigned each supply chain task no matter who in the chain performed the step—the manufacturer or its channel partner. Under such a model, when the manufacturer chooses to farm out supply chain tasks to its channels, the transfer price the channel partner pays is simply a sum of the EVCs up to that point in the process. No confusing discounting policy or convolution of MLP is necessary. This approach, by assigning value-based prices to all supply chain activities regardless of who performs them, altogether avoids the issue of channel conflict over pricing.

## **3.4.2 Training (Needs #6, 8, 11-13, 15, 16, 19 & 20)**

Channels are in many ways a sales force for their vendors. As with any sales person, a channel partner will gladly discuss with customers the product it knows most about in an effort to avoid questions pertaining to those products about which it knows the least. As manufacturers introduce a new product, partners feel left alone to figure out its inner workings—a sink or swim approach to channel management. Using this sink or swim analogy, such an approach to new product introductions results in many products sinking

at the channel level when, if partners had simply been made more aware of their attributes, the new releases might have swam all the way to the customer's shore.

Throughout my interviews with channel partners I came to recognize the vast opportunities afforded manufacturers by properly trained channel partners. With little capital investment, manufacturers can completely alleviate concern over this issue while building loyalty and product confidence with their partners through an aggressive training program. A comprehensive program, one that spans the product's life cycle, is easy to manage and costs little to implement. The simplest and most inexpensive training program involves continual discussions between design engineers, manufacturing engineers, and channel representatives. This approach to training not only facilitates the product's success but also creates fertile grounds for a burgeoning relationship.

## **3.4.3 Packaging** (Needs #3 & 10)

Packaging refers to both the containers within which product is shipped and the menu offerings that manufacturers provide channels. Many products are shipped in containers that are disposed of upon arrival at the partner site. Pass-through packaging provides an efficient means of avoiding these costs. Pass-through packaging incorporates each channel player's needs in the original vendor container. As product arrives at the next link in the supply chain this container is removed and temporarily stored while the partner adds value to the system. Then, in preparation for shipping, the system is repackaged in its original container. This pass-through process requires little coordination and offers great savings to the manufacturer in consumable packaging.

Manufacturers manage product packages, or offerings, through their menu management policies. These practices are a source of channel conflict because they offer numerous, often unsolicited, packages that reflect ease of manufacturing rather than customer needs. A more sensitive packaging strategy, one reflective of channel partners' needs, must be implemented to successfully convince these critical customers of the manufacturer's commitment to their success.

# 3.5 Why Channels Now?

Consumer purchasing is a negotiation between the buyer and the seller. As with any negotiation, the power sources available to participants play a significant role in the final settlement. One such source available to the participants of a commercial negotiation is market power. From a microeconomics perspective, market power may be defined as the ability to influence the price consumers are willing to pay for a product.

Prior to 1985, computer manufacturers had market power over their customers. Price-insensitive consumers, eager to explore the high-technology world, paid heavily for immature hardware platforms based on complex designs. This complexity served as a barrier to consumer knowledge and ensured that the lions share of market power stayed in the hands of those participants capable of comprehending the intricacies of their systems—the manufacturers. During this period relatively standardized application packages were non-differentiable and provided few unique solutions. However, the situation was soon to change.

By the mid 1980s the personal computer revolution was in full gear. One of the most fundamental impacts of this era was that new participants entered market negotiations. These new players were much more knowledgeable and demanding of the technologies in the industry. At the same time, software applications began to blossom while hardware technology matured. The result: applications became diverse, the complexity advantage shifted to the buyer, and consumers rather than manufacaturers now held overall market power (Burris, 3-4).

Product architectures soon began to reflect these changes. Where customers were once tolerant of high-cost, high-margin systems based on proprietary standards, they now demanded low-margin, high-volume, open systems based on common industry standards. The computer and electronics industry had evolved from being technology driven to market driven (Pesatori, 14 Sep. 1994).

The net result to the manufacturing firm of this market power shift was that margins shrank and overhead reduction through business process reengineering became necessary for survival. Part of this reengineering focused directly on the cost of distribution.

Because of the benefits to manufacturers cited in Section 3.2 above, channels became an obvious solution for firms wishing to remain competitive under the stresses imposed by their newly empowered customer base.

# 3.6 The Cost of Doing Business with Channel Partners

Although channels offer immense benefits to the market, they come at a cost. Dealing with them requires time, coordination, and money. They potentially create a barrier between manufacturers and the end users of their products, thereby preventing quick and accurate assessments of customers' needs in a dynamic market. Rather than providing more accurate market data, they potentially induce delivery variability through the mismanagement of their own business practices. Finally, there is the issue of quality assurance through indirect distribution.<sup>2</sup>

I summarize the list of partner needs in Section 3.3 in two product attributes channel-friendly packages must have. Manufacturers must design products that are: 1) easy to sell, and 2) technologically comprehensible. They must then deliver these products to market through partner relationships that minimize channel conflict using the business practices mentioned in Section 3.4. To summarize in a single word, quality is what makes the difference to channels. Quality products are easy to sell. Quality products are through DFX principles technologically comprehensible. Therefore, I assert that quality products, ones designed using Design for Channels principles and manufactured using mature process technologies, meet the needs of channel partners. For this reason I focus specifically on the issue of the cost of quality to manufacturing under a channels strategy throughout the remainder of the thesis.

33

<sup>&</sup>lt;sup>2</sup> I wish to acknowledge Mark Coggin, Leaders for Manufacturing Fellow (Class of 1995), for his insightful comments pertaining to the issue of channel costs.

# CHAPTER 4 SERVER MANUFACTURING AT DIGITAL

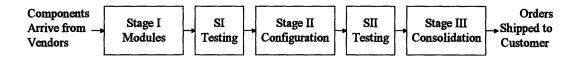

Digital server manufacturing occurs in three value-added stages. Stage I, Module Manufacturing, refers to the process whereby humans and machines populate printed circuit boards with components. Stage II, System Configuration, refers to the compilation of modules from Stage I with other subassemblies (backplanes, cabinets, etc.) to form fully functioning systems. Finally, Stage III, Order Consolidation, refers to the merging of systems into customer orders. In-house testing occurs at the end of Stage I and Stage II (see Appendix B, Server Manufacturing Process Flow).

Figure 4.1: Digital's Server Manufacturing Model Under a Direct Distribution Strategy

Originally, the proponent organizations chartered with each of the above levels of value-added activities were independent entities, sometimes dispersed between several manufacturing sites. However, over the years Digital has consolidated the activities associated with Stage I and II manufacturing such that the "consolidation centers" of old are the only exceptions to a standing rule of co-location.

# 4.1 Stage 1: Module Manufacturing

Server module assembly occurs in three distinct phases. These phases correspond to the orientation of the Printed Circuit Board (PCB, also known as Printed Wiring Boards) during assembly. Phase one refers to the placement of Surface Mount Technology (SMT) components on side one of the PCB. Phase two refers to SMT component placement on PCB side two. Finally, phase three refers to through-hole component placement on PCB side one.

Phase 1 begins with the deposition of solder paste onto the PCB surface. The placement of SMT passive components through a chip shooting process follows the screen printing process.<sup>3</sup> A pick and place process for active SMT components and those components possessing fine-pitched<sup>4</sup> leads (tiny medal pins providing electronic connection between component and PCB) follows the chip shooting process. Once all side one components are in place, a technician visually inspects the board and routes it through an infrared oven. This oven uses convection heat to reflow the solder paste, thereby creating the conductive bond between each component and the PCB. A machine inverts the board and phase two of Stage I assembly begins.

Phase two assembly differs from that of phase one only in the temporary adhesive used to affix the components to the PCB. In preparation for the inverted wave soldering operation of phase three, a tiny drop of epoxy holds each component in place. Epoxy deposition takes the place of the screen printing process of phase one. The heat of the reflow oven cures the epoxy just prior to through-hole component insertion.

During phase three assembly all non-machine placed SMT components and all insertable through-hole components are hand-placed on the PCB. A machine again inverts the board as it approaches the wave soldering process. Upon completion of wave soldering a conductive connection has permanently attached all components to the PCB. After wave soldering the boards receive an aqueous cleaning to remove all solder paste residue. Skilled technicians then add by hand any components determined to be too sensitive to undergo aqueous cleaning. Following a thorough visual inspection, the finished modules enter an end of Stage I testing queue before moving on to Stage II assembly (Kanata Manufacturing Team, 2-4).

-

<sup>&</sup>lt;sup>3</sup> Passive components contain no resident logic and include transistors, capacitors, and resistors.

<sup>&</sup>lt;sup>4</sup> Fine-pitched leads are those where the spacing from lead center to adjacent lead center is less than 0.025 inches.

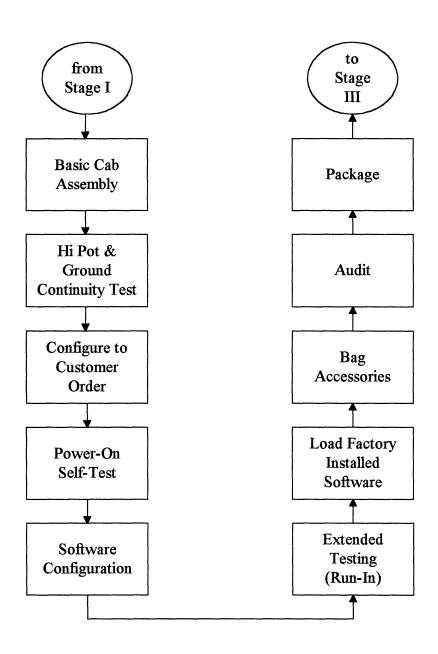

# 4.2 Stage 2: System Configuration

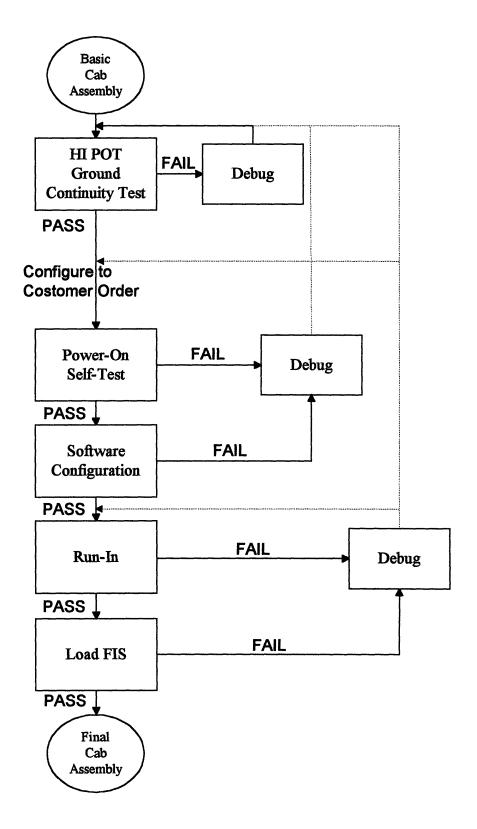

Server system configuration is a compilation of both assembly and testing processes. Workers assemble the basic cabinet (cab) from kitted parts' bins corresponding to customer orders. Cab assembly includes the placement of buses, motherboards and power supplies into the external case for the server. After assembly, a technician conducts a high potential and ground continuity test to ensure compliance with Underwriter Laboratory's electrical safety standards. Assemblers then custom configure the cab to the customer's order. This process includes the installation of cables, the central processor, memory modules and hardware options as specified by the customer. Following a power-on self-test (POST), a technician configures the software and conducts an extended system test. Once this test determines the system operational, the technician loads factory installed software (FIS) and workers prepare the system's accessories for shipment. An audit is conducted to verify the system configuration and customer order agree, then workers package the order for shipment. This final step includes installing the external covers, applying decals, cleaning, and crating the order (Kanata Manufacturing Team, 14-16).

# 4.3 Stage 3: Order Consolidation

Because customer orders include components from other manufacturing sites (keyboards, monitors, etc.), the order is still incomplete after Stage II. Therefore, the last task to be accomplished before a server reaches the customer is order consolidation. Currently there are three ways Digital accomplishes this last task.

The first option is the use of consolidation centers. Through backward planning these facilities drive the production plan such that they receive each order's components on the same day. However, because of process variability Digital sometimes replaces this method it with an in-transit merge. Contract carriers conduct an in-transit merge by pulling together orders at the loading dock of either Digital or its customer. Finally, partial shipments altogether avoid the issue of order consolidation. A partial shipment occurs when the customer consents to the shipment of components in piecemeal fashion. This

can be a costly alternative since Digital incurs additional shipping costs with each transaction.

### 4.4 Testing Strategy

Testing strategies are a function of four coupled variables: 1) the level of product quality desired, 2) the manufacturing cost of achieving this quality level, 3) the fault detection capability (expressed as test coverage) needed to achieve this quality level, and 4) the time required to achieve the desired quality level. Testing is not a value-added manufacturing process. Instead, I describe it as a value-restoration process. It is not something manufacturers wish to do, but rather is a process required to overcome variability in imperfect manufacturing processes. To accomplish this task in its server product line Digital has adopted the end-of-stage strategy pictured earlier in Figure 4.1 and described in detail below.

### 4.4.1 Stage I Testing

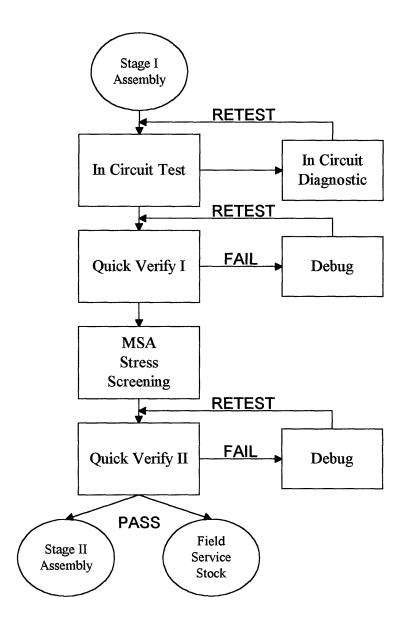

The first of five testing steps is the visual inspection for component presence that occurs at the end of Stage I assembly. Those modules passing visual inspection enter step two, incircuit testing. With a goal of over ninety-five percent component coverage, this automated "bed of nails" test detects and diagnoses assembly related defects such as shorts, opens, and placement errors. After the bed of nails, technicians test the module's functionality in step three, a five-minute quick verification process (QV1). Once again the goal is coverage greater than ninety-five percent functionality. Those modules passing QV1 undergo step four, the manufacturers stress analysis (MSA). During the MSA technicians cycle ambient temperature to place the module under environmental stresses. After the MSA, technicians verify functionality once again. QV2 is conducted exactly as QV1 to identify those failures induced by the MSA. Modules surviving the above rigors then enter the Stage II assembly process (Kanata Manufacturing Team, 6-9).

<sup>&</sup>lt;sup>5</sup> The testing community commonly refers to in-circuit testing as the beds of nails test because the equipment used resembles a small mattress having hundreds of nails protruding upward through its surface.

#### 4.4.2 Stage 2 Testing