# The Impact of the Geographic Distribution of Design Engineers on the Pace of Engineering Development

by David A. Schiller

Submitted to the System Design & Management Program In Partial Fulfillment of the Requirements for the Degree of

### Master of Science in Engineering and Management

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2006

#### © 2006 David Schiller All Rights Reserved

MASSACHUSETTS INSTITUTE OF TECHNOLOGY JUN 2 1 2006 LIBRARIES

ARCHIVES

The author hereby grants to MIT permission to reproduce and to distribute publicly paper and electronic copies of this thesis document in whole or in part.

| David A. Schiller                                                                         |         |                | Signature of Author |

|-------------------------------------------------------------------------------------------|---------|----------------|---------------------|

| System Design and Management Program<br>June 2006                                         |         |                |                     |

|                                                                                           |         | ~              |                     |

|                                                                                           |         |                | Certified By        |

| Dr. Ricardo Valerdi<br>Thesis Supervisor<br>Research Associate, Lean Aerospace Initiative |         | $\bigcap \cap$ |                     |

| Patrick Hale                                                                              | - HODEr |                | Certified By        |

| Director                                                                                  |         |                |                     |

### The Impact of the Geographic Distribution of Design Engineers on the Pace of Engineering Development

By

David A. Schiller

Submitted to the System Design & Management Program On May 12, 2006 in Partial Fulfillment of the Requirements for the Degree of Master of Science in Engineering and Management

## ABSTRACT

The increasing use of digital design tools and broadband information networks is creating an environment that permits the geographic distribution of design engineers. In order to successfully distributed engineering the consequences need to be understood. Through the examination of records of project execution, this thesis investigates whether the decision to geographically distribute engineers has a measurable impact on the pace of engineering development. A task-based Design Structure Matrix (DSM) was developed and showed that the projects studied were developed using a highly integral process. It is hypothesized the unanticipated consequences of distributing engineers geographically will slow the pace of engineering development to such an extent that costs incurred in protracted engineering development outweigh the benefits.

Three findings result from of this study. First, the geographic distribution of design engineers proved to have a negative affect on schedule performance causing distributed projects to overrun their schedules by more than twice as much as localized projects. Second, the development process for the systems studied was found to be highly iterative rather than adhering to the anticipated waterfall model espoused by the process documentation. Third, the level of task aggregation used to study this phenomenon affects the ability to identify the impact of distributed engineering.

| Thesis Supervisor: | Dr. Ricardo Valerdi       |

|--------------------|---------------------------|

| Title:             | Research Associate        |

|                    | Lean Aerospace Initiative |

# ACKNOWLEDGMENTS

I will always be grateful to my sponsor company for the opportunity to come to MIT. Particularly, I owe a debt of gratitude to George Perkins for his support throughout my career and to George Reynolds for his support while I've been at MIT. I also need to thank William H. Beck III for his enduring mentorship and friendship. My true education as a mechanical engineer happened through interactions with Bill. A number of people contributed to this work by taking the time to be interviewed and talk with me: Viguen Ter-Minassian, Michael Liu, Roy Kohn, Mike Merryman, Paul Kemlage, and Dr. John Lenard.

I've had the fortune of making and re-establishing some great friendships at MIT and through the SDM program. I will miss all of you when I leave. This thesis was expedited and enhanced because of the wisdom of Erica Fuchs and Matt LaMantia's kindred sense of how to battle procrastination.

I feel a pull of nostalgia for MIT. Jason Pinto and I have long conjectured that there are students that love their time here and students that endure their time here. I have loved almost every minute. I have found no other place in the world like MIT. I watch with pride and respect as my friends from this place move on to positions of responsibility and technology leadership throughout the world. Long may we roll.

Now, as always, I am overwhelmed with gratitude and love for my family and the example they have set for me. They have supported me without fail my entire life. They have inspired me to persist toward my dreams and focus on what is most important. I hope my parents never underestimate the value of their example to their children. Thank you. I love you.

per ardua ad astra

# TABLE OF CONTENTS

| ABSTRACT                                                               |    |

|------------------------------------------------------------------------|----|

| ACKNOWLEDGMENTS                                                        | 5  |

| TABLE OF CONTENTS                                                      |    |

| TABLE OF FIGURES                                                       | 9  |

| CHAPTER 1: INTRODUCTION & MOTIVATION                                   |    |

| Research Question & Hypothesis                                         | 12 |

| BACKGROUND & SCOPE OF WORK                                             |    |

| Incentives to Geographically Distribute Engineering Development        |    |

| Defining Engineering Development                                       |    |

| Hardware Development Compared and Contrasted with Software Development |    |

| Distributed Engineering Development Compared to Subcontracting         |    |

| DESIGN STRUCTURE MATRICES IN THE LITERATURE                            |    |

| CHAPTER 2: CASE STUDY SELECTION AND DESCRIPTION                        |    |

| SELECTING ECAS AS THE UNIT OF STUDY                                    |    |

| DATA SETS AVAILABLE FOR STUDY                                          |    |

| Description of Case Study #1                                           |    |

| Description of Case Study #2                                           |    |

| CHAPTER 3: DEVELOPING THE DSM                                          |    |

| DATA SOURCES USED FOR DEVELOPING THE DSM                               |    |

| Process Documentation                                                  |    |

| Semi-Structured Interviews                                             |    |

| CONSTRUCTING THE DSM                                                   |    |

| Developing Mini-DSMs                                                   |    |

| Concatenating the Mini-DSMs                                            |    |

| THE FINAL DSM                                                          |    |

| CHAPTER 4: ANALYSIS, RESULTS & DISCUSSION                              |    |

| Case Study #1                                                          |    |

| Analysis & Results from Case Study #1                                  |    |

| Discussion of Case Study #1 Results                                    |    |

| CASE STUDY #2                                                          |    |

| Analysis & Results From Case Study #2                                  |    |

| Discussion of Case Study #2 Results                                    |    |

| CROSS CASE DISCUSSION                                                  |    |

| CHAPTER 5: CONCLUSIONS & FUTURE WORK                                   |    |

| SUMMARY OF FINDINGS                                                    |    |

| THREATS TO THE VALIDITY OF THIS STUDY                                  |    |

| FUTURE WORK                                                            |    |

| APPENDIX A: PRIMER ON READING DSMS                                     |    |

| APPENDIX B: MINI-DSMS FOR EACH PHASE OF DESIGN                         |    |

| APPENDIX C: DATA FROM CASE STUDY #1                                    |    |

| APPENDIX D: DATA FROM CASE STUDY #2                                    |    |

| REFERENCES                                                             | 69 |

# **TABLE OF FIGURES**

| FIGURE 1–1: DIAGRAM SHOWING THE RELATIONSHIP BETWEEN ENGINEERING DEVELOPMENT AND THE ADJACENT       |

|-----------------------------------------------------------------------------------------------------|

| STAGES OF DEVELOPMENT. THIS THESIS STUDIES THE ENGINEERING TASKS BETWEEN THE AWARD OF A             |

| CONTRACT AND THE RELEASE OF DRAWINGS TO MANUFACTURING                                               |

| FIGURE 2-1: THIS EXPLODED VIEW OF AN ELECTRONICS CHASSIS SHOWS THE ELEMENTS WHICH MAKE UP A TYPICAL |

| SYSTEM. ALL OF THE ELEMENTS TAKEN TOGETHER FORM A DELIVERED PRODUCT. EACH ECA CAN IN ITSELF         |

| BE CONSIDERED AN ENGINEERING PROJECT                                                                |

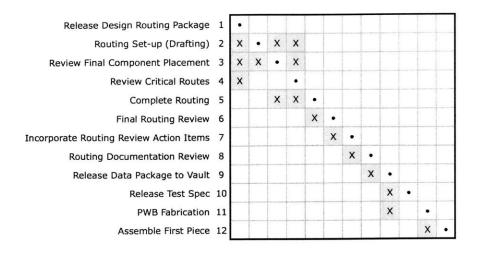

| FIGURE 2–2: DIAGRAM SHOWING THE STEPS INVOLVED IN THE CIRCUIT BOARD DESIGN PROCESS AS DOCUMENTED BY |

| THE CIRCUIT BOARD DESIGN GROUP. IT IS INTERESTING TO NOTE THAT THE STEPS ARE REPRESENTED AS         |

| OCCURRING SEQUENTIALLY, YET THE DATA COLLECTED BY THE GROUP SHOWS THAT ITERATION BETWEEN STEPS      |

| IS THE NORM                                                                                         |

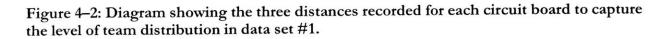

| FIGURE 3–1: DIAGRAM OF THE STAGES OF DESIGN FOR THE DEVELOPMENT OF ECAS ADAPTED FROM PROCESS        |

| DOCUMENTATION. THERE ARE FIVE DESIGN STAGES AND TWO FORMAL DESIGN REVIEWS IN THE PROCESS28          |

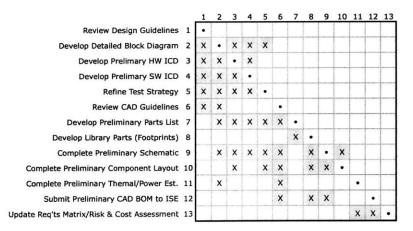

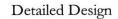

| FIGURE 3-2: MINI-DSM REPRESENTING THE PRELIMINARY DESIGN STAGE OF THE PROCESS FLOW. BOXES WHICH     |

| ARE MARKED WITH AN X INDICATE INFORMATION FLOW REQUIRED BETWEEN TASKS. THIS DSM DOCUMENTS           |

| INFORMATION CONNECTIONS WHICH ARE EXPLICITLY MENTIONED IN THE ECA DEVELOPMENT                       |

| DOCUMENTATION                                                                                       |

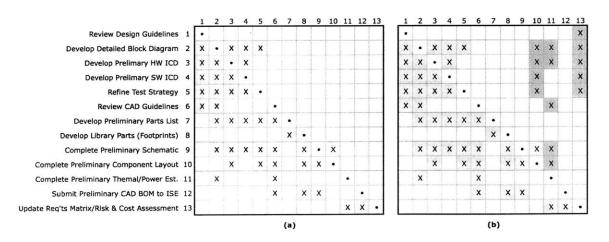

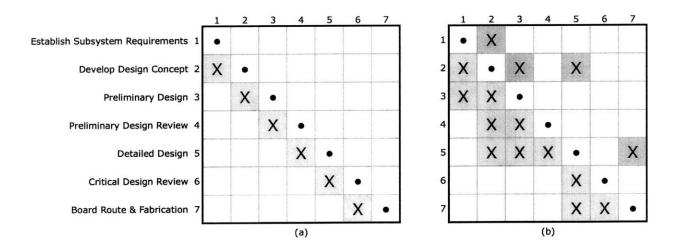

| FIGURE 3-3: A COMPARISON BETWEEN THE DSM REPRESENTING THE ESPOUSED PROCESS FOR THE PRELIMINARY      |

| DESIGN STAGE OF DEVELOPMENT (A) AND THE ACTUAL PROCESS FOR THE SAME STAGE AS REVEALED THROUGH       |

| INTERVIEWS WITH ENGINEERS (B)                                                                       |

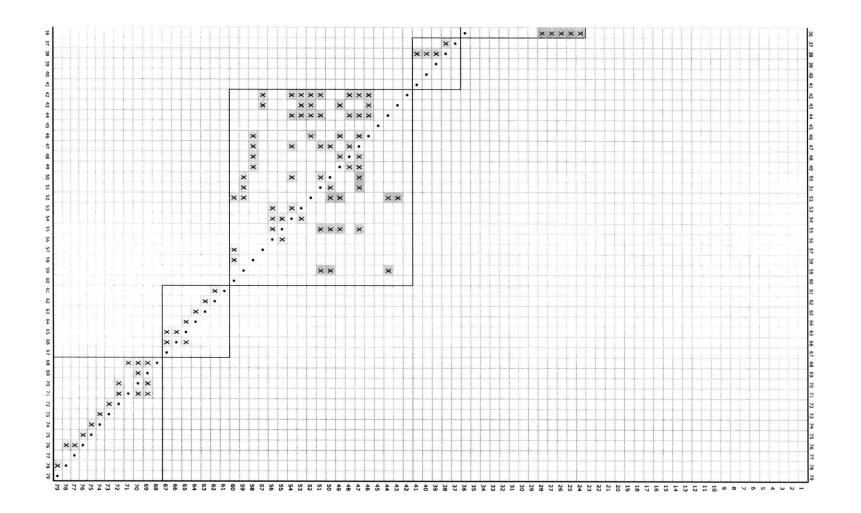

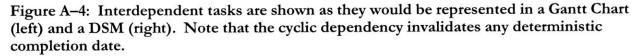

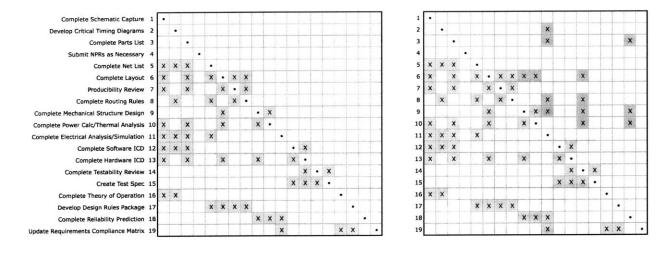

| FIGURE 3-4: (THIS PAGE AND FACING) THIS DSM, WHICH SHOWS THE CONCATENATION OF THE MINI-DSMS         |

| REPRESENTING EACH DESIGN PHASE, REFLECTS THE WATERFALL DEVELOPMENT PARADIGM USED TO CREATE          |

| THE ECA DEVELOPMENT DOCUMENTATION                                                                   |

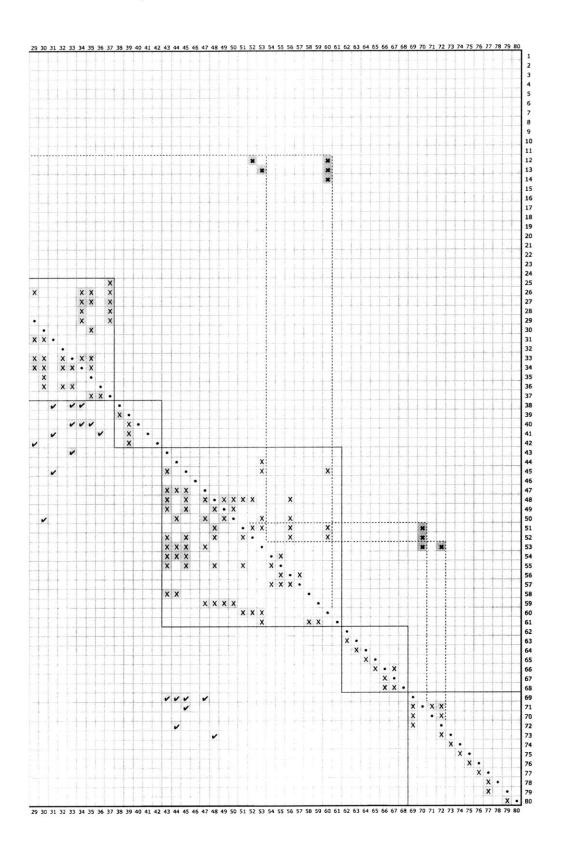

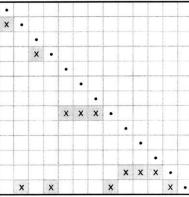

| FIGURE 3-5: (THIS PAGE AND FACING) THE COMPLETED DSM INCORPORATING THE INTERVIEW FEEDBACK OF        |

| ENGINEERS WHICH DOCUMENTS THE ECA DESIGN PROCESS. REWORK LOOPS AND ITERATIVE DEVELOPMENT            |

| PHASES ARE CLEARLY VISIBLE                                                                          |

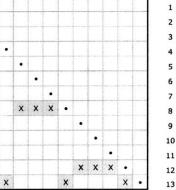

| FIGURE 3–6: META-DSM SHOWING THE INFORMATION DEPENDENCIES BETWEEN DESIGN STAGES. THE FIGURE ON      |

| THE LEFT (A) REPRESENTS THE ESPOUSED PROCESS. THE FIGURE ON THE RIGHT (B) REPRESENTS THE PROCESS IN |

| USE,                                                                                                |

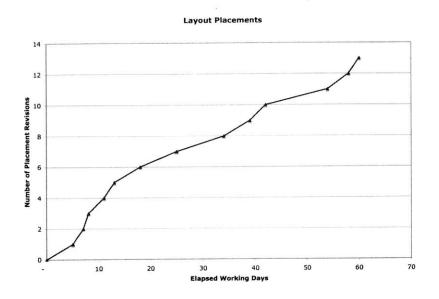

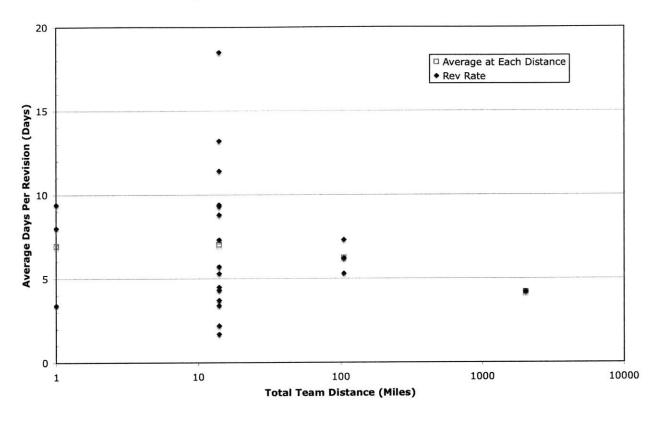

| FIGURE 41: GRAPH SHOWING THE DEVELOPMENT OF COMPONENT PLACEMENT ITERATIONS PLOTTED AGAINST          |

| ELAPSED WORKING DAYS. THE AVERAGE NUMBER OF DAYS PER REVISION WAS FOUND BY DIVIDING THE TOTAL       |

| NUMBER OF WORKING DAYS BY THE NUMBER OF REVISIONS40                                                 |

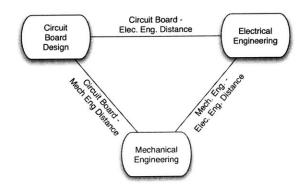

| FIGURE 4–2: DIAGRAM SHOWING THE THREE DISTANCES RECORDED FOR EACH CIRCUIT BOARD TO CAPTURE THE      |

| LEVEL OF TEAM DISTRIBUTION IN DATA SET #1                                                           |

| FIGURE 4-3: PLOT OF THE AVERAGE RATE OF COMPONENT PLACEMENT ITERATION AS A FUNCTION OF THE TOTAL    |

| DISTANCE SEPARATING THE ENGINEERS. THERE IS NO STATISTICALLY SIGNIFICANT TREND IN THIS DATA41       |

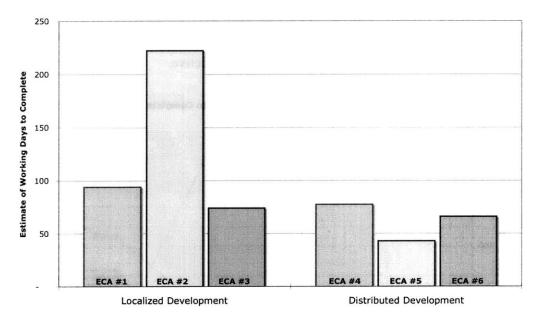

| FIGURE 4-4: GRAPH DEPICTING THE RANGE OF INITIAL ESTIMATES OF WORKING DAYS REQUIRED TO COMPLETE THE |

| PROJECT A ECAS                                                                                      |

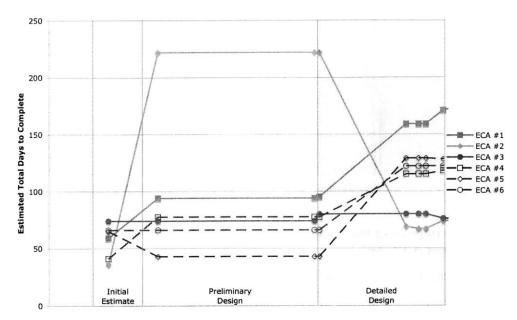

| FIGURE 4–5: PLOT SHOWING THE EVOLUTION OF THE ESTIMATED TIME TO COMPLETE EACH DESIGN AS FUNCTION OF |

| DESIGN MATURITY. NOTE THAT DURING PRELIMINARY DESIGN ESTIMATES ARE REVISED BASED ON INSIGHTS        |

| GAINED ABOUT THE DESIGN. DURING DETAILED DESIGN ALL ESTIMATES IN THIS DATA SET INCREASE BECAUSE     |

| THE PROJECTS HAVE FALLEN BEHIND SCHEDULE. DASHED LINES REPRESENT DISTRIBUTED DEVELOPMENT            |

| TEAMS                                                                                               |

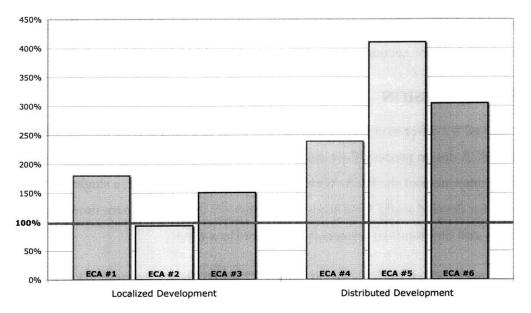

| FIGURE 4–6: GRAPH DEPICTING THE ECA DEVELOPMENT TIMES FOR LOCALIZED AND GEOGRAPHICALLY DISTRIBUTED  |

| TEAMS. RESULTS ARE PRESENTED AS A FRACTION OF THE INITIAL ESTIMATE OF THE TIME REQUIRED TO          |

| COMPLETE THE DESIGN                                                                                 |

### **CHAPTER 1: INTRODUCTION & MOTIVATION**

The topic for this thesis was formed in my mind by on the job exposure to progress-hampering decisions to geographically distribute engineering development. One particular example I witnessed involved the development of an electronics chassis which was divided between engineering facilities on the east and west coasts of the United States – locations separated by over 3,000 miles and three time zones. Responsibility for the design of the chassis itself was given to engineers on the west coast while the design of the boards which populated that chassis was relegated to engineers on the east coast. Engineers involved with this project were baffled by the division of labor. Substantial iteration and information exchange occurs between chassis designers and board designers as the interfaces between the circuit cards and a chassis evolve. Those involved with this project have horror stories to tell about the difficulties of communicating with colleagues on the opposite coast.

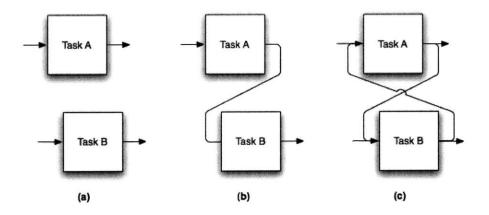

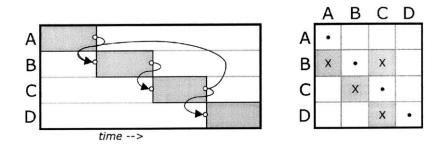

A traditional understanding of the design process views chassis design and board design as two separated tasks. In schedules for the project the tasks are shown as being completed sequentially. This is a useful simplification for scheduling the engineering design process. However, the reality is that the engineering of these components happens simultaneously. Because of their interdependent nature there is no choice other than to engineer the components together. The simplification of thinking of tasks as sequential and simply dependent can mask important dynamics of information exchange. When engineers are co-located and can communicate informally these dynamics may not be important. However, when making decisions about how to divide or distribute engineering these dynamics can be crucial.

The project described above was over budget and behind schedule when it was completed. Even in the presence of the standard the impediments to smooth engineering development – i.e. undiscovered rework, schedule and scope changes, shifting management priorities – the counterintuitive division of labor on this project was blamed by the engineers for the bulk of the problems. This thesis attempts to measure the impact of the distribution of engineers on the pace of engineering development. Quantifying the phenomenon will enable better informed decisions about distribution to be made.

There are many reasons why Engineering Development may be geographically distributed; schedule pressures, work load balancing, and cost savings must be weighed in decisions about where to locate engineering. Friedman [15] and others argue that the time has come for the global distribution of engineering development. The ubiquity of internet access combined with tools to aid in the remote collaboration of engineers has created an environment where it is possible to imagine remote collaboration where before none was possible. Geographically distributed teams are gaining in prevalence and discussion of how to manage them is growing. [10, 14, 17, 20] While modular designs may be simpler to geographically distribute, managers of monolithic projects must make difficult decisions about how to distribute engineering. As described by Tom Allen [1], the bandwidth of remote communication technologies is lower than the bandwidth of face to face communication. Certain types of ideas are best communicated when people are face to face. It is important to understand the impact on the pace of development before distribution decisions are made.

#### **RESEARCH QUESTION & HYPOTHESIS**

Through the examination of records of project execution, this thesis investigates whether the decision to geographically distribute engineers has a significant impact on the pace of engineering development. The specific research question is:

What is the schedule impact of geographically distributing engineering of design-intensive products with integral architectures when compared with localized engineering.

This research question is studied with data collected from the engineering development of electronic circuit cards (ECAs) for space flight applications. A task-based Design Structure Matrix (DSM) was constructed to map the information relationships between the engineering development tasks. The DSM showed that the development process for ECAs is highly iterative and departs from the anticipated waterfall development model espoused by engineering process documentation. Examining the DSM shows that ECAs have an integral architecture and development process. The design tasks on the path of ECA development are interdependent and cannot be accomplished without information exchange between engineers. There are no clean interfaces which can be leveraged to develop the product in a modular fashion.

Based on the nature of information exchange between development engineers working on the design of these hardware systems, I hypothesize that:

The unanticipated consequences of distributing engineers geographically will slow the pace of engineering development to such an extent that costs incurred in protracted engineering development outweigh the benefits.

Design issues which must be resolved through the collaboration of multiple engineers will proceed more slowly when using teleconferences and email because these media lack the richness of face to face communication. [1] While email and teleconferencing enable remote communication, they are poorly suited to discussions of complex spatial ideas and are more error prone and slower to provide feedback than face to face conversation.

Data was collected and analyzed at two levels of detail. The first, and more finely detailed study used low-level records of the occurrence of design updates for 25 design projects. The second level of detail was more coarse and used higher-level data typically available to program managers. There were six designs for this part of the study and they were a subset 25 design projects studied in fine detail. Review of the detailed measures of project progress – specifically the rate of circuit board design updates – does not show any significant impact of the geographic distribution of engineers. At a macro level, data retrieved from project schedules show a marked difference between the two groups. Distributed development takes substantially longer as a fraction of the time estimated to complete a project than localized development. That the impact of distribution is seen in the macro level data but not in the data of finer scale engineering indicates that the level of task aggregation used to study this phenomenon impacts the ability to identify trends.

### **BACKGROUND & SCOPE OF WORK**

### Incentives to Geographically Distribute Engineering Development

Even if we stipulate that the geographic distribution of design engineers slows the pace of engineering development, there may still be reasons why firms would pursue this practice. There may be economic advantages to the use of labor from a certain geographic location that offsets the slower pace of development. A company may replicate engineering competencies in various geographic locations through acquisition or growth. Engineers with overlapping skills in separate locations may encourage geographic distribution through efforts to level the engineering workload between locations.

There may also be intangible incentives to distribute engineering tasks having to do with synergies with other projects or the individual expertise of engineers. Geographically distributing development projects may expose engineering offices to practices and procedures from other regions. Distributing engineering development could be an instrument of disseminating corporate culture. It is possible to imagine a host of rational incentives for geographically distributing engineering development. In some instances it may be a necessity of operating the business. One goal of this thesis is to make some data based observations about the unforeseen consequences of distributed engineering development.

### **Defining Engineering Development**

This thesis will focus on the Engineering Development (ED) portion of the product development process (PDP). In the widest sense of the term, the PDP describes all stages of a product's lifecycle. It includes all of the following: initial concept development, engineering design, manufacturing, product operation and maintenance, and disposal. All of these tasks are part of the whole system PDP. [8] This thesis studies only the Engineering Development portion of the product development process because this portion of the development process is the most communication intensive and therefore the most affected by geographic distribution.

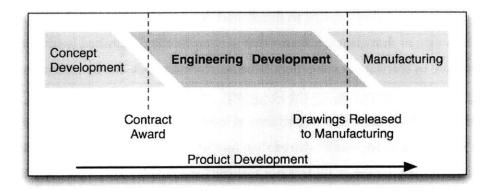

Engineering Development will be taken to mean all of the steps which occur between the award of a contract for development of a piece of hardware and the release of engineering drawings to production. The steps which precede engineering development involve the gathering of user needs and the synthesis of a product concept. When engineering development is complete the product is ready for manufacture. These three steps are illustrated in Figure 1–1.

The boundaries of engineering development are not always clear cut. In aerospace projects the nature of firm and customer interaction is somewhat reversed from what is typically observed in the development of consumer goods. Unlike consumer goods where firms develop product concepts in response to perceived user needs, in typical aerospace programs the initial concept development is performed by customer, sometimes in concert with the potential contractors and consultants. The initial concept is used to generate a request for proposals from potential contractors. The aerospace firm which wins the contract uses the preliminary product concept as a starting point to complete concept development and engineering. Because of this relationship, when a contractor begins an engineering project, the engineers are not beginning from a blank sheet of paper. In some sense, the concept for what is to be created has already been formulated and stated in the product specification. This does not mean that the architecture of the product is predetermined. The design process still evolves through a series of concept, preliminary, and detailed design steps. However, this relationship blurs the boundary of engineering development at the beginning of a project because responsibilities are shared between the customer and the contractor.

Similarly, at the end of engineering development there is a gray area between engineering and manufacturing. Modern engineering practice has embraced the notion that design engineers cannot divorce themselves from a project after the engineering is nominally complete [25] The line between engineering and manufacturing is blurred in two ways. First, manufacturing engineers are involved in the engineering development of a product as early in the process as is practical. Second, design engineers work closely with manufacturing to solve the problems which arise during manufacturing. While acknowledging the fact that engineering continues after manufacturing has begun, this thesis studies only the engineering that occurs before drawings are first released to manufacturing.

# Figure 1–1: Diagram showing the relationship between engineering development and the adjacent stages of development. This thesis studies the engineering tasks between the award of a contract and the release of drawings to manufacturing.

The decision to limit the scope of research to engineering completed before the start of manufacturing was made so that the most information intensive portion of the development process was the focus of study. The sources of data used in this thesis break the product development process into engineering and manufacturing stages. Mirroring this break is process documentation with matching boundaries in the thesis facilitated the gathering of data. This thesis is not a study of the outsourcing or off-shoring of manufacturing, the products studied in the thesis were assembled in-house from pieces purchased or manufactured domestically or even locally. See Fuchs *et al.* [16] for a discussion of the impacts of outsourcing manufacturing on engineering development.

## Hardware Development Compared and Contrasted with Software Development

This thesis studies electronic circuit card assemblies. These are electromechanical systems in the sense that they involve electrical and mechanical engineering. The primary function of these systems is to perform some electrical job. The proper functioning of the electrical circuitry is dependent not only on electrical engineering, but also on mechanical and software components. The bulk of the

engineering development time is spent of the design of hardware. While software engineering is required as part of system development, the hardware engineering throttles the pace of development. Software is rarely on the critical path. The ECAs studied here were approximately 95% hardware effort and 5% software effort on average.

It is interesting to compare the ECAs studied here to software development projects because of the large number of examples of distributed software development. Large-scale software development projects are being successfully developed using the open source software model. Typically open source software developers do not even work for the same company, much less interact face to face. [21] Software design seems ideally suited to distributed development because the product is not a physical good. In fact, at first glance, it seems that geographically distributed hardware development is hampered relative to software development because software code can be transmitted and shared geographically for almost no cost while the movement of physical goods is expensive. Furthermore while software is readily duplicated, a single piece of hardware cannot exist in two locations at once. The view that software is more readily shared than hardware mixes metaphors in a manner that is surprisingly common but incorrect. [3] It is not realistic (or valuable) to compare software development with the *manufacture* of physical goods. It is much more reasonable to compare software development with the *engineering development* portion of hardware development.

Viewed from this perspective, the prospect of distributed hardware development is not hampered by the expense of shipping or the impossibility of sharing physical goods. The majority of hardware development happens long before there is ever a physical artifact to worry about. For modern products the majority of the design is developed as digital files in one of many design tools. Physical parts are described in model files in CAD programs. Thermal analyses exist as digitized matrices describing temperatures throughout a part. The list goes on and on. Everything from structural analyses, to schematics of electrical circuits, to simulations of RF performance exist as readily transferable digital files. [4] The barrier to the geographic distribution of hardware development is not that the design cannot be readily shared or duplicated. The reasons are more subtle.

One difficulty in the development of hardware is the lack of interoperability between the various design tools. Not only are engineers separated into disciplines (mechanical, electrical, software), often the tools used by engineers are so specialized that an individual will spend years becoming proficient in one piece of the development process (board designers, packaging engineers, thermal or structural analysts). In practice, the mechanical engineer does not know how to operate the electrical

engineer's schematic tools and the electrical engineer does not know how to operate the mechanical engineer's CAD tools. Therefore, just because an engineer is able to transmit a digital file does not mean that it can be understood by the recipient. Typically meta-communication about the ideas in the digital file takes place so that engineers of all disciplines can perform their jobs.

End-to-end product development of hardware systems involves many stages. However, it is only during product development that geographical distribution of participants can be achieved without incurring transportation costs. In contrast, once a product enters the manufacturing stages of development, the materials involved must be physically transported if development is to continue across locations. This is another reason the scope of this work is limited to engineering design.

### Distributed Engineering Development Compared to Subcontracting

The degree to which geographic distribution will impact the pace of engineering development depends on the degree to which a given product architecture is modular. [23] If the project can be divided into subsystems with well established and clean interfaces then the problem of communication is limited to documenting and controlling the interfaces. This is a key characteristic of a modular architecture which makes products with this style of architecture amenable to distributed development. [2, 21] Modular architectures are the norm in systems which subcontract some portion of engineering development. When engineering development is subcontracted interfaces must be defined in advance of the subcontracted system being fully designed. A trade-off is made when specifying these interfaces in that they place constraints on the system. This may result in suboptimal performance.

Where modularization is possible and desirable it is often useful. Modularizing facilitates the decomposition of systems into manageable pieces which is one tool for dealing with the complexity of large systems. However, some systems are not amenable to modularization. [26] Further, there is research which suggests that too much modularity may limit a firm's flexibility. [7, 13]

For products with an integral architecture it is often not possible to subcontract engineering projects because interfaces can not be cleanly defined. In these instances all portions of a design are in flux until the entire design is completed. The ECAs studied for this thesis have an integral architecture and as a consequence an integral design process. Because the design is integral it is not possible to cleanly separate a portion of the design process. Any work which involves engineers distributed from the rest of the team will require extensive communication between the two groups.

### **DESIGN STRUCTURE MATRICES IN THE LITERATURE**

The DSM developed for this thesis builds on published techniques for the study and analysis of engineering processes. [5, 6, 9, 11, 12, 18, 19] The DSM which resulted from the analysis of the ECA development process shares many common characteristics with previously developed DSMs. [22, 27-29]

### **CHAPTER 2: CASE STUDY SELECTION AND DESCRIPTION**

All data used in this thesis was collected from the records of a single aerospace firm. The firm employs thousands of engineers that work on a range of products. The product area of focus for this thesis is electronic systems produced for spaceflight applications. This type of engineering is commonly referred to as electronics packaging. The rigorous environmental demands placed on electronics hardware by the space environment necessitate detailed engineering analysis of every aspect of a design. In addition to ensuring that the electrical functionality of the device meet the requirements of the application, it also necessary to choose materials that are compatible with the high radiation and vacuum environment. The design must account for the vibration and shock loads endured during launch, the on-orbit temperature extremes, and the lack of convection cooling to carry away heat. Further, because of the high cost of lifting hardware to orbit, the customer places commensurately high reliability requirements on the design.

### SELECTING ECAs as THE UNIT OF STUDY

The unit of study ultimately selected for this thesis is the Electronic Card Assembly (ECA). The following section describes the process by which this selection was made.

Four criteria were established to evaluate candidate projects for study. The first of these was that the project had to be sufficiently large to support distributed engineering. Systems which are too simple do not involve enough engineers to warrant distributed engineering. In studying the development of hardware for spaceflight applications it was observed that the engineering rigor involved emphasizes the multidisciplinary nature of engineering development. Even if the delivered electrical function of an ECA is straightforward and only one engineer is required for that portion of the design, the talents of engineers from various disciplines – electrical engineering, mechanical engineering, thermal-structural analysis, materials engineering, software engineering – must be leveraged to design a successful product. Because of the disparate engineering disciplines required for each design, it is the case that even relatively simple projects require a sizeable team of engineers. ECAs are typically developed by a team that ranges in size from 10 to 15 people. This team size is sufficient for geographically distributed development. Simply stated, this first criterion was that the project cannot be too small.

The second criterion was that the project cannot be too large. When engineering projects grow beyond a certain size their development process becomes so complex that the process is effectively

never repeated. This requirement prevented the use of the entire electronics chassis as the unit of study for this thesis. The difficulty with electronics chassis is that each one is in some way different from the next. Each design has distinct challenges which alter the path and substance of the design process. The result of this heterogeneity is that any process description which is granular enough to be used for all chassis is too granular to be useful for analyzing the progress of any particular design. The process steps are so high-level that the interesting dynamics are masked.

The ECAs studied for this thesis performed a variety of functions. A sampling of the delivered functionality includes controlling the deployment of spacecraft solar cells, controlling the detonation of the explosive bolts used to separate sections of a spacecraft, battery monitoring and control, solar array power management, and command and data handling, to name a few. Even with the widely varying delivered functionality of these ECAs, the design procedure for any single ECA is largely the same as the generic procedure. Engineering analyses performed during design drive the engineering solution down different paths and the final designs of the ECAs are distinct. However, the steps that are taken and the order in which they are performed are largely the same for every ECA.

The third criterion for selecting projects was that the development process in question had been executed enough times to make a reasonable study. ECAs satisfy this requirement. The large number of designs available for study is the result of two factors. First, ECAs are the modular unit of functionality for electronics design so there are many of them. Second, as mentioned above, the design process for each design is standardized. Experience with many ECA designs has advanced the engineering firm up the learning curve to the point where the process is consistent for each design.

The fourth and final criterion used to select projects for study was that they have been developed by both localized and distributed teams. Discussions with engineers revealed many projects which had been developed by distributed engineering teams. However, few of these projects had an analogous project developed by a localized team. The purpose of restricting this thesis to the study of projects which had been developed by both localized and distributed teams was to observe the impact of one variable while maintaining other parameters affecting the pace of design constant. This helped single out the impact of geographic distribution for study.

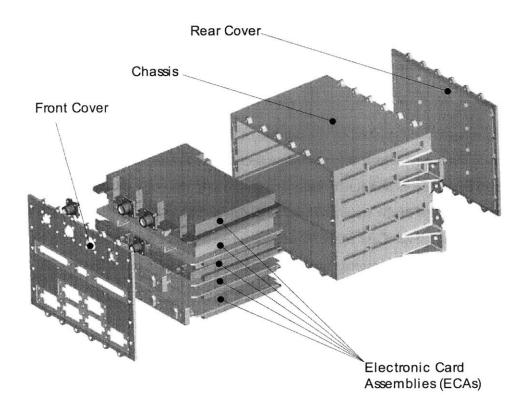

ECAs fulfill all four of the high-level criteria. An additional, less tangible reason for their selection was that I had tacit knowledge of the intricacies of the design process gained through experience designing and managing the design of these systems. Figure 2–1 illustrates the relationship between ECAs and an electronics chassis. Typically an electronic chassis is a deliverable system. It is the device a customer interacts with. The ECAs are modules within the chassis which provide each required electrical function. Like the average person interacts with a personal computer, the aerospace customer typically handles and makes connections with the chassis as a whole. It is unusual for a customer to have cause to interact with or handle the circuit boards inside. In the same way most consumers never interact with the circuit boards inside of their personal computers.

If a contract requires that multiple functions be performed by the delivered system, it is common to find each function or group of functions allocated to an individual ECA. Each ECA is a design project unto itself.

# Figure 2–1: This exploded view of an electronics chassis shows the elements which make up a typical system. All of the elements taken together form a delivered product. Each ECA can in itself be considered an engineering project.

The ECAs themselves consists of distinct subsystems. The predominant subsystem is the circuit board which interconnects all of the discreet electrical components. The circuit board is attached to a heatsink which carries away the heat generated by the electrical components and provides a

mechanical structure to support the circuit board. The heatsink typically incorporates features which are used to secure the card in the chassis. In addition to discreet electrical components which are soldered to the circuit board there are also electrical connectors which have an obvious electrical function but which must also be integrated into the mechanical design. The connectors comprise an important electrical *and* mechanical interface. Finally, some ECAs incorporate processing units which require software as part of the total design.

### DATA SETS AVAILABLE FOR STUDY

The data documenting ECA development comes from two sources and is separated into two data sets. The first source is detailed records of design iterations kept by the lead designer in a circuit board design group. These data are a record of the day to day events which comprise a portion of the engineering of 25 ECAs. The data extracted from these records constitute case study #1. The second source of data for this thesis is a collection of project schedules used to track the progress of six ECAs. Data extracted from these schedules make up case study #2. The six ECAs in case study #2 are a subset of the designs in case study #1.

The two data sets are distinguished by the portion of the ECA engineering process they document and the level of detail with which they record project progress. Case study #1 is made up of data that would be used by engineers and functional managers to take the pulse of day to day project progress. It documents only a few of the steps required to design an ECA. The data is low-level and recorded at the engineering task level. Case study #2 uses data recorded for the consumption of individuals whose perspective is program management. It condenses the design of each entire ECA into a single metric. This data is high-level and is recorded at the whole-ECA level.

### Description of Case Study #1

Data for the first case study is taken from the design records of a group of circuit board designers. An ECA's primary function is to perform some electrical task and the completed circuit board is the assembly that fulfills that role. The circuit board not only serves as the mounting surface for a majority of the electrical components, the traces inside the circuit board form the electrical interconnection between the components. Consequently, circuit board designers have a central role in the ECA development process.

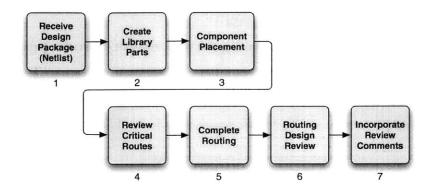

The nominal sequence of steps executed by the circuit board design group is shown in Figure 2–2. For each step, the lead designer in the group made a record noting the occurrence and the date every time a design iteration was completed. The resulting record contains information about the number and frequency of design iterations for each step in the circuit board design process. Records kept for component placement (step 3) are of particular interest for this thesis. For each placement, data is first transferred from circuit board design to mechanical and electrical engineering. The electrical and mechanical engineers subsequently review the placement and give comments back to the board designer. Coordination between these three groups is required to finalize the placement.

Figure 2–2: Diagram showing the steps involved in the circuit board design process as documented by the circuit board design group. It is interesting to note that the steps are represented as occurring sequentially, yet the data collected by the group shows that iteration between steps is the norm.

Records of these interactions were available for a 25 ECA designs. These 25 designs represent approximately two years of engineering activity. The ECAs included in this data set represent designs from both localized and distributed teams.

These exchanges of information are not formal enough to warrant a design review with detailed minutes and lists of attendees. They are significant enough to prompt the design group to make a note of their occurrence. These records of information exchange document the rate of collaborative engineering. The records do not provide any insight into the health of the project or its adherence to schedule. Case study #1 is used to study the pace of engineering iteration by observing the interactions between engineering departments. The detailed progress reports provide a record of engineering "in the small." By studying this data it is possible to make inferences about the impact of distributed development on particular interactions and portions of the design.

### Gathering Information for Case Study #1

For each the 25 ECA designs the number of component placements as well as the date each component placement was completed was recorded. The placement of components can affect

estimates of electrical performance, structural and thermal margin, and reliability. Consequently, numerous engineers are involved in the review of the component placement. The number of placement iterations is often a function of the complexity of a design. Simple designs may have only one or two placement revisions. Complicated designs may have as many as 15. Because the absolute number of placement iterations is as much a function of board complexity as anything else, it cannot in itself be used to assess the impact of the geographic distribution of design engineers. The rate of iterations is calculated and used for comparison to account for the differences in complexity.

The rate of design iteration is calculated by taking the total number of working days required to finalize a placement and dividing by the total number of placement iterations. This metric provides some measure of the pace of development. Numerous engineering departments are involved in developing a finalized placement so this metric seems a likely candidate to reveal changes in the pace of design.

### The Nature of Distributed Engineering in Case Study #1

The ECAs which make up this data set represent a range of geographic distribution. Of the population of designs that was studied, six were developed for one project which shall be referred to as Project A. Of the six ECAs developed for Project A, three were developed by localized teams and three were developed by distributed teams. The localized teams were all working in the same building or campus of buildings. The engineers on localized teams were within walking distance of each other and could meet face to face whenever the need arose.

The distribution of engineering development on Project A occurred in the following manner. At the beginning of the program, the detailed electrical engineering was assigned to an offsite group of engineers approximately 30 miles from the primary engineering facility. Furthermore, the circuit board layout and routing was assigned to a group approximately 50 miles from the primary engineering facility. All other design tasks for these ECAs were undertaken by engineers in the primary facility.

As the project progressed and the detailed electrical design was nominally finished, the engineers who had been doing the work moved on to other projects. Responsibility for the electrical engineering was given to engineers in the primary facility. A similar pattern was followed for the circuit board layout. Once the design was nominally finished, responsibility for board layout was transferred to engineers at the primary facility. In both cases, even though the design was nominally complete, substantial work was done by the engineers in the primary facility on tasks that were originally assigned to engineers in remote facilities.

There was one further example of distributed engineering in the data collected for case study #2. The electrical engineering for one ECA was performed by an engineer who tele-commuted from Florida. For this design the mechanical and board design functions were located in the primary engineering facility.

The remaining designs in this population were designed by teams that were either localized or separated by distances which were small enough to allow face to face communication. Engineers that worked in the same group and met regularly through group meetings were considered to be essentially co-located even though they may not necessarily work in the same building.

# Description of Case Study #2

Case study #2 comes from the schedule records for the development of the six Project A ECAs. All were developed during the same time period. These ECAs are a subset of the designs in case study #1. As detailed above, three Project A ECAs involved the geographic distribution of the mechanical, electrical, and board design functions. Each engineering group was separated by 30 to 50 miles.

Data was available for this project because the management team regularly updated a number of reports which tracked the progress of the program at regular intervals. Saved copies of these reports were available for study. Paramount among these reports was an Integrated Master Schedule (IMS). The IMS contains dependency, overall duration, and progress information for all of the tasks which are planned for the development of the project. The IMS also provides a baseline estimate of the time required to complete each task which was established at the beginning of the program. By studying changes made to the IMS it is possible to observe how the estimate of the time required to complete any particular task or group of tasks evolved over time.

The data in the IMS is useful for studying engineering "in the large." It records what happened but contains no record as to why. The tasks listed in the IMS may correspond to more than one individual engineering task. Consequently, each IMS task may involve engineers from a variety of disciplines as well as locations. It is known which ECAs were developed by distributed teams, so the design durations for the ECAs can be used to study the impact of distribution on the pace of ECA design. However, case study #2 provides no insight into the dynamics of project execution which may have impacted the pace of project development.

### Gathering Information for Case Study #2

The IMS contained metatasks which correspond to the engineering design of the six ECAs. Each engineering design metatask was composed of several subtasks. Each subtask in the IMS equates to more than one of the subtasks which make up the DSM. In other words, the IMS is less granular than the DSM

The Project A management team saved a version of the IMS approximately weekly for the duration of the project. For each saved version of the schedule the following data were recorded: the duration of each ECA engineering design task, the percent complete of each ECA design metatasks, the duration of each circuit board design task, and the percentage complete of each circuit board design. This data was tabulated and analyzed for trends. The complete data table is presented in Appendix C.

# **CHAPTER 3: DEVELOPING THE DSM**

The design process for the development of ECAs was studied and documented in a task-based DSM in the manner described in previous publications on this topic. [5, 27-29] The purpose of developing this DSM was to gain insight into the patterns of communication involved in the development of ECAs. The task-based DSM makes a record of the information connections between all of the tasks required for the development of an ECA. The following sections will document the process by which the DSM was constructed. The terms *stage of design* and *design task* will used throughout. In this context, the stage of design refers to the macro level design stages found in the process documentation. These are the waterfall design stages. Smaller design tasks comprise the stages of design. These tasks are the atomic level of process documentation in this thesis.

### DATA SOURCES USED FOR DEVELOPING THE DSM

### **Process Documentation**

The information foundation for the development of the DSM was process documentation. The aerospace company studied for this thesis has a large library of documents which describe the steps involved in designing ECAs. All available ECA process documentation was collected and analyzed. The process documentation as written divides the overall process description along two dimensions. The documentation is divided by process stage and by engineering discipline.

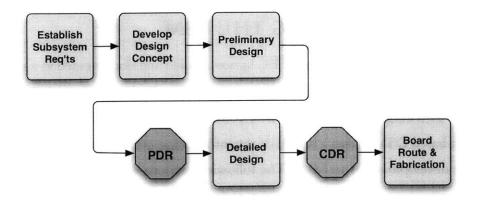

The first of these divisions represents the understanding of the development process by the authors of the documentation. The reigning paradigm of engineering development in use at the aerospace company is a waterfall development model. This is evident in the linked-list nature of metadevelopment tasks -- or stages of development. They are shown in Figure 3–1. The second division, occurs because process documentation tends to be written by engineers for engineers. It is not written for insights into the overall process of engineering development. Consequently, each design stage tends to have a separate process document for each engineering discipline – in this case mechanical engineering, electrical engineering, circuit board design, and systems engineering each have their own process documents.

In order to create a DSM representing the complete process these two divisions had to be undone. The re-combination of the process documentation to create a single DSM is described later in this chapter.

Figure 3–1: Diagram of the stages of design for the development of ECAs adapted from process documentation. There are five design stages and two formal design reviews in the process.

### Semi-Structured Interviews

The process documentation describes the espoused process used to develop an ECA. However, the process-in-use by engineers may differ considerably from the espoused process. In order to gain an understanding of the process-in-use, engineers were engaged in semi-structured interviews. These interviews focused on discussions of the espoused process, covering both its shortcomings and the ways in which it is adequate. Interviews were conducted with engineers from multiple disciplines to get varied perspectives. Specifically interviews were conducted with representative from the following departments: electrical engineering, mechanical engineering, mechanical analysis, circuit board design, and software engineering.

The interviews resulted in minor changes to the list of tasks and the order in which they occur. The tasks listed in the process documentation encompass the vast majority of the design tasks the engineers perform. Furthermore, the order of the tasks was not much changed through the process of interviewing the engineers. The tasks in the espoused process are largely the same tasks identified by engineers when describing what they actually do to complete a project. The aspect of the DSM which was most changed by conversations with engineers was the information connections between tasks.

### **CONSTRUCTING THE DSM**

### **Developing Mini-DSMs**

As mentioned above, the process documentation makes two simplifying assumptions which had to be undone before the DSM could be constructed. The first assumption made by the authors of the process documentation was that the processes for each engineering discipline could be written separately. For example, the process documentation for electrical engineers is a separate document from the process for mechanical engineers. To capture the interactions between the multiple engineering disciplines involved with the design it was necessary to combine multiple engineering domain specific process documents into single, multi-domain process.

This was accomplished by extracting the tasks from the process documentation and concatenating them into a single list of tasks for each stage of design. In most instances the task descriptions were identical for each engineering discipline. Where unique tasks existed they were added to the task list for that stage of design. An example of a combined task list is shown with it's accompanying mini-DSM in Figure 3–2. This early stage mini-DSM shows only the information connections explicitly mentioned in the process documentation.

# Figure 3–2: Mini-DSM representing the preliminary design stage of the process flow. Boxes which are marked with an X indicate information flow required between tasks. This DSM documents information connections which are explicitly mentioned in the ECA development documentation.

The mini-DSM shown above represents only the espoused information connections between design tasks. In order to properly represent the design process it was necessary to capture the actual information dependencies for ECA design. This was accomplished by showing the mini-DSMs to

design engineers so that the tasks could be reviewed and information connections could be added or removed as necessary. Each engineer was shown all seven of the mini-DSMs and asked for comments.

When discussing information dependencies with engineers it was necessary to establish likelihood threshold to aid in deciding which dependencies rose to the level of being documented and which dependencies were too unlikely to be important. The guideline given to engineers was to only indicate an information dependency in the DSM if there was a substantial probability that one portion of a design would impact another. A one-in-four likelihood was used as a rough guideline. It was necessary to establish this threshold because at some level nearly every aspect of a design impacts every other. If even the most unlikely of interactions was documented on the DSM, the matrix would be completely populated rather than sparsely populated. A fully populated DSM provides no insight in to the design process. The likelihood threshold acts as a filter to help maintain a high signal to noise ratio in the DSM.

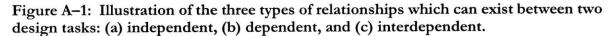

The mini-DSM representing the espoused process and the process in use for the preliminary stage of design is shown in Figure 3–3. Using the procedures described above mini-DSMs were constructed for all seven stages of the development process. All of the mini-DSMs are presented in Appendix A:. It is interesting to note that the engineers were aware of many undocumented information dependencies in the process of designing ECAs.

Figure 3–3: A comparison between the DSM representing the espoused process for the preliminary design stage of development (a) and the actual process for the same stage as revealed through interviews with engineers (b).

### Concatenating the Mini-DSMs

The second assumption in the process documentation which needed to be undone was that each stage can be documented separately from the others. This assumption is the result of an adherence to a waterfall development paradigm. Each stage is documented as a process unto itself which is impacted only by the design stages which have come before. Under this paradigm information is passed forward to upcoming design tasks but information is never passed backward. This manner of documenting the development process is useful because it simplifies the prescription for how to perform the engineering tasks. However, this manner of describing the tasks masks the information dependencies present in the context of the end-to-end design process.

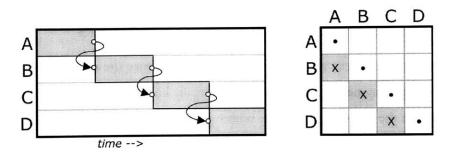

This assumption was undone in two steps. The first step involved concatenating the mini-DSMs into a single large DSM. This is a straightforward process and the result is shown in Figure 3–4. This large DSM lists the tasks for the entire ECA development process. It remains divided into highly iterative design stages because information dependencies between stages have not yet been added.

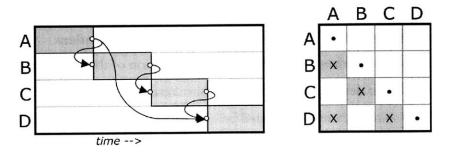

To fill in the remaining information dependencies this end-to-end DSM was taken back to engineers for a second round of discussion. Viewed in the context of the larger engineering process, the engineers once again made changes to the list of tasks. Some tasks were eliminated. Others tasks were combined. More importantly, the engineers now made comments about information dependencies between the stages of design. The majority of these dependencies involved the feedforward of information from one stage to the next. These dependencies are represented by marks below the diagonal of the DSM and outside of the highly iterative design stage regions. A second sort of dependency was also added. These dependencies are potential rework loops represented by marks above the diagonal in the DSM. The result of the second round of interviews with engineers is shown in Figure 3–5.

| Establish Subsystem | 1 Authorize to Proceed                                               |     | 2    |   | 1   | 1   | 7   | 8                |            | T |   |   | 1 | 1   |               | 1       |         |   |   |           | i. |    |       |     | 1 |   |     | 1        |

|---------------------|----------------------------------------------------------------------|-----|------|---|-----|-----|-----|------------------|------------|---|---|---|---|-----|---------------|---------|---------|---|---|-----------|----|----|-------|-----|---|---|-----|----------|

| Req'ts              | 2 Review Contract Specification                                      | x   | •    |   |     |     |     |                  |            |   |   |   |   |     |               |         |         |   |   |           |    |    |       |     |   |   |     |          |

|                     | 3 Review System Architecture                                         |     | x    | • |     |     |     |                  |            |   |   |   |   |     |               |         |         |   |   |           |    |    |       |     |   |   |     |          |

|                     | 4 Develop Preliminary Reg'ts Compliance Matrix                       |     | x    | X | •   |     |     |                  |            |   |   |   |   |     |               |         |         |   |   |           |    |    |       |     |   |   |     |          |

|                     | 5 Establish Primary Derived Requirements                             |     | x    | x |     | •   | 1   |                  |            |   |   |   |   |     |               |         |         |   |   |           |    |    |       |     |   |   |     |          |

|                     | 6 Establish Sub-Element CAIV Targets                                 |     | x    |   |     | •   |     |                  |            |   |   |   |   |     |               |         |         |   |   |           |    |    |       |     |   |   |     |          |

|                     | 7 Identify Driving Req'ts for Further Trade-off                      |     |      | X | X   |     | •   |                  | 1          |   |   |   |   |     |               |         |         |   |   |           |    | 1  |       |     | - |   |     |          |

|                     | 8 Establish Supportability Req'ts                                    | 19  | X    |   |     | -   |     | •                |            |   |   |   |   |     |               |         |         |   |   | -         |    |    |       |     |   |   |     |          |

|                     | 9 Complete Requirements Analysis Checklist                           |     | -    | ) | x ) | ( X | X   | x                |            |   |   |   |   |     |               |         |         |   |   |           |    |    |       |     | 1 |   |     | <u> </u> |

|                     | 10 Create Design Development File                                    |     | -    | 1 | _   | _   | -   | 10               | <b>K</b> • | - |   | _ | _ | 1   |               | -       | 1       | _ | 1 | -         | 4  |    |       |     | - |   | -   | -        |

| Develop Design      | 11 Address Technology Issues                                         |     | -    |   |     | -   | į   |                  |            | • |   |   |   | X   | >             | ( X     |         |   |   | -         |    | 1  |       |     |   |   |     | -        |

| Concept             | 12 Address Producibility Issues                                      |     | -    |   |     |     |     |                  | -          | X | • |   |   | x   |               | X       | 110,000 |   |   | -         | -  | +  |       | -   | - |   | -   | -        |

|                     | 13 Develop Mechanical Approach                                       |     | -    |   | -   | -   |     |                  |            | - | - | • | - | -   | >             |         | X       | _ |   | -         | -  | +  |       |     | - |   |     |          |

|                     | 14 Define Design Approach                                            | -   | -    |   |     | +   |     |                  | -          |   | - | X |   | 1-1 | ,             | X       |         | - |   | +         | -  | -  |       |     | + |   |     | -        |

|                     | 15 Indentify Firmware Requirements                                   |     | -    |   | +   |     | -   |                  | -          |   | - |   | • |     |               | <u></u> | -       |   |   | +         | ÷  | 1  | ++    |     | - | 1 |     |          |

|                     | 16 Define ICD Approach                                               |     | +    |   |     |     | fin |                  | +          |   |   |   |   | -   |               |         |         |   |   | +         | +- |    | +     |     |   |   | -   | -        |

|                     | 17 Define Interfaces                                                 |     |      | - |     | -   |     | -                | 1          |   |   |   | ¥ | Y   | x             |         |         |   |   | +         |    |    |       |     | 1 |   | -   |          |

|                     | 18 Review Prelim. Concept Block Diagram                              |     | +    |   |     | +   | +   |                  |            | - | - | - | ^ | ^   | ^ •           |         | -       |   |   | -         | +  | +  |       |     | + |   |     | -        |

|                     | 19 Generate Final Derived Oper. Req'ts                               |     |      |   |     |     | -   |                  | +          |   | - |   |   |     |               | -       |         |   |   | +         |    |    |       |     | - |   |     |          |

|                     | 20 Review Key Characteristics                                        |     | +    |   |     | -   |     |                  | -          |   |   |   |   | 1   |               | -       |         |   |   |           | 1  |    | -     |     |   |   | 1   | -        |

|                     | 21 Update Req'ts Matrix/Risk Assesment                               |     | 1    |   |     |     |     |                  | 1          |   |   |   |   |     |               | x       | x       | x |   | 1         |    |    |       |     | 1 |   |     |          |

|                     | 22 Develop Factory Test Approach<br>23 Develop BIT Philosophy        |     |      |   | -   |     | 1   |                  |            | 1 | x | 1 | ĸ |     | >             |         | 1       |   | x |           |    | 1  | H     |     | 1 |   | 1   | 1        |

| reliminary Design   | 23 Develop BT Philosophy<br>24 Review Design Guidelines              |     | 1    | 1 | t   | 1   | 1   |                  | -          | H |   |   | - | 11  |               | 1       | 1       |   | 1 |           | 1  | 1  |       |     | 1 |   |     | 1        |

| reaminery Design    | 25 Develop Detailed Block Diagram                                    | 1   | 1    |   | +   | 1   | 1   |                  | 1          | T |   | - |   |     |               | 1       | T       |   | T | X         |    | X  | x     | x   | 1 |   | X   | x        |

|                     | 26 Develop Prelimary HW ICD                                          |     | 1    |   |     | -   | -   | and and a second |            | - | - |   |   | 11  |               | 1       |         |   |   |           |    | •  |       |     | 1 |   |     | x        |

|                     | 27 Develop Prelimary SW ICD                                          |     | 1    |   | 1   | 1   | 1   |                  |            |   |   |   |   |     |               |         |         |   |   |           |    | x  |       |     | 1 |   | x   |          |

|                     | 28 Refine Test Strategy                                              |     |      |   | 1   |     | -   |                  | 1          |   |   |   | 1 | 1   |               | 1       |         |   |   |           |    |    | X     | •   | T |   | x   |          |

|                     | 29 Review CAD Guidelines                                             |     |      |   |     |     |     |                  |            |   |   |   |   |     |               |         | 1       |   |   | X         | X  |    |       | •   |   |   |     | х        |

|                     | 30 Develop Preliminary Parts List                                    |     | 0.00 |   |     |     | 1   |                  | 1          |   |   |   |   |     |               |         |         |   |   |           | X  | x  | X     | x x | • |   |     |          |

|                     | 31 Develop Library Parts (Footprints)                                |     | 1    |   |     |     |     |                  |            |   |   |   |   |     |               |         |         |   |   |           |    |    |       |     |   | • |     | 1        |

|                     | 32 Complete Preliminary Schematic                                    |     |      |   |     |     |     |                  |            |   |   |   |   |     |               |         |         |   |   |           | X  | X  | X     | xx  |   | x | • X |          |

|                     | 33 Complete Preliminary Component Layout                             |     |      |   |     |     | 1   |                  |            |   |   |   |   |     |               | 1       |         |   |   |           | 1  | X  |       | XX  |   | X | x • | X        |

|                     | 34 Complete Preliminary Themal/Power Est.                            |     |      |   |     |     |     |                  | 1          |   |   |   | 1 |     |               |         |         |   |   |           | X  |    |       | X   |   |   | _   | •        |

|                     | 35 Submit Preliminary CAD BOM to ISE                                 |     |      |   |     |     |     |                  |            |   |   |   |   |     |               | 1       |         |   |   |           |    |    |       | ×   |   | X | x   | 1        |

|                     | 36 Update Reg'ts Matrix/Risk Assesment/Cost                          |     | -    |   |     |     |     |                  |            |   |   |   |   | -   |               | 1       |         |   |   |           |    |    |       |     |   |   |     | X        |

| DR                  | 37 Electrical Peer Design Review                                     |     | _    |   |     |     | 1   |                  |            | 1 |   |   |   |     |               | -       |         |   | 1 |           |    | 1  |       |     |   |   |     | -        |

|                     | 38 Update Design Documents                                           |     | _    |   |     | 1   | 1   |                  | -          |   | _ |   | - | 1   | -             | 4       |         |   |   |           |    | -  |       |     | - |   |     | -        |

|                     | 39 Hold PDR (Design)                                                 | 1   | 4    |   |     | 1   | 1   |                  |            |   | _ |   |   |     |               | -       | 1       |   |   |           |    | -  |       |     |   |   |     | -        |

|                     | 40 Hold PDR (Producability)                                          | 1   | -    |   | -   | _   |     | ļ                |            | - | _ | - |   |     |               | -       | -       | - | - |           | ÷  | -  |       |     | - |   |     | -        |

|                     | 41 Hold PDR (Testability)                                            |     | -    |   |     | -   | -   |                  |            |   |   |   |   |     |               |         | -       |   | 1 | -         | -  | 1  | -     |     | - |   | _   | 1        |

| Detailed Design     | 42 Complete Schematic Capture                                        |     | -    |   |     |     |     |                  | +          | - | _ |   | - |     |               | -       | -       |   |   |           | -  | 1  |       |     | + |   |     | -        |

|                     | 43 Develop Critical Timing Diagrams                                  |     |      |   | +   |     |     |                  |            |   |   |   |   | 1   | in the second |         | -       |   |   |           | +  | 1- |       |     | + |   |     | -        |

|                     | 44 Complete Parts List                                               |     | -    |   |     |     |     |                  | 1          |   | - |   |   | 1   |               | -       |         |   | - | +         | +  | 1  |       |     | 1 |   | -   | -        |

|                     | 45 Submit NPRs as Necessary                                          |     | -    |   |     |     | -   |                  |            |   |   |   | 1 | 1   |               |         |         |   |   | -         | +  | 1  | +     |     | - |   | -   |          |

|                     | 46 Complete Net List                                                 |     | +    |   |     | -   | -   |                  | -          |   | - |   |   | -   |               | -       |         |   |   | -         | +  | -  | -     |     | + |   |     | -        |

|                     | 47 Complete Layout                                                   |     | +    | - | 1   | +   | 1   |                  | -          | - |   | - | + | 1   |               | 1       |         |   |   | 1         | t  |    |       |     | 1 |   | 1   | 1        |

|                     | 48 Producibility Review                                              |     | +    | - |     |     | -   |                  | 1          | 1 |   |   | - | -   |               |         | 1       |   | 1 | 1         | -  | 1  |       |     | T |   |     | 1        |

|                     | 49 Complete Routing Rules<br>50 Complete Mechanical Structure Design | T   | 1    |   | 1   | 1   | 1   |                  |            |   | - |   |   | 1   |               | 1       | 1       |   |   | ter frank | 1  | -  | 1     |     | T |   |     | 1        |

|                     | 51 Complete Power Calc/Thermal Analysis                              |     | 1    | - | -   |     |     |                  |            | 1 |   |   |   | 11  |               |         |         |   |   |           | 1  | 1  |       |     |   |   |     | 1        |

|                     | 52 Complete Electrical Analysis/Simulation                           | 1   | -    | 1 | 1   | 1   | -   |                  | 1          | 1 |   |   |   | 11  |               |         | 1       |   |   |           | 1  |    |       |     | 1 |   |     |          |

|                     | 53 Complete Software ICD                                             |     | 1    |   |     | 1   | 1   |                  | 1          | 1 |   | 1 |   |     |               | 1       | 1       |   | T | 1         | T  |    | T     |     |   |   |     | 1        |

|                     | 54 Complete Hardware ICD                                             | T   | 1    |   | 1   | 1   | 1   |                  | T          |   |   |   |   | 11  |               | 1       |         |   | 1 | Ĩ         |    | 1. |       |     | T |   | 1   | 1        |

|                     | 55 Complete Testability Review                                       |     | 1    | - | 1   |     | 1   |                  | 1          |   |   |   |   |     |               |         |         |   | 1 |           | F  | 10 |       |     | 1 |   |     |          |

|                     | 56 Create Test Spec                                                  |     |      |   |     |     | -   |                  | 1          |   |   |   |   |     |               | I       |         |   |   |           |    | 1  |       |     |   |   |     |          |

|                     | 57 Complete Theory of Operation                                      |     | 1    |   | -   |     | -   |                  | -          |   |   |   |   |     |               |         |         |   |   |           |    | 1  | 1     |     | 1 |   |     |          |

|                     | 58 Develop Design Rules Package                                      |     |      |   | 1   |     |     |                  |            |   |   |   |   |     |               |         |         |   |   |           |    | 1  |       |     |   |   |     | 1        |

|                     | 59 Complete Reliability Prediction                                   |     |      |   |     |     | 1   |                  |            |   |   |   |   |     |               | 1       |         |   |   | 1         | 1  |    |       |     |   |   |     |          |

|                     | 60 Update Requirements Compliance Matrix                             |     | 1    |   | 1   |     |     |                  |            |   |   |   |   |     |               |         |         |   |   |           |    |    |       |     |   |   |     |          |

| DR                  | 61 Electrical Peer Design Review                                     |     | _    |   |     |     | 1   |                  | 1          |   |   |   |   |     |               |         |         |   |   | 1         |    |    |       |     |   |   | 1   | 1        |

|                     | 62 Update Design Documents                                           |     |      |   |     |     |     |                  | 1          |   |   |   |   |     |               |         |         |   |   |           | 1  |    |       |     |   |   | -   | _        |

|                     | 63 Hold Critical Design Review                                       |     |      |   |     |     | 1   |                  |            |   |   |   |   |     |               | 1       |         |   |   | 1         |    |    |       |     |   |   | 1   | -        |

|                     | 64 Action Item Review & Response                                     |     | _    |   |     |     |     |                  | 1          |   |   |   |   |     |               |         |         | _ | _ |           | 1  |    |       |     | - |   |     | _        |