### Multipass Communication Systems for Tiled Processor Architectures

by

Nathan Robert Shnidman

Bachelor of Science in Electrical Engineering and Computer Science Massachusetts Institute of Technology, 1995

Master of Engineering in Electrical Engineering and Computer Science Massachusetts Institute of Technology, 1996

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering and Computer Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 2006

© Massachusetts Institute of Technology 2006. All rights reserved.

Chairman, Department Committee on Graduate Students

| M | ASSACHUSETTS INSTITU<br>OF TECHNOLOGY | TE |

|---|---------------------------------------|----|

|   | JUL 1 0 2006                          |    |

|   | LIBRARIES                             |    |

|   |                                       |    |

ARCHIVES

$\mathbf{2}$

#### Multipass Communication Systems for Tiled Processor Architectures

by

Nathan Robert Shnidman

Submitted to the Department of Electrical Engineering and Computer Science on February 3, 2006, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering and Computer Science

#### Abstract

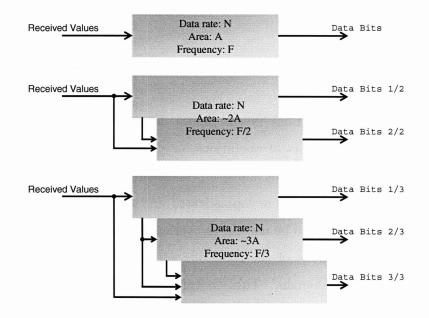

*Multipass* communication systems utilize multiple sets of parallel baseband receiver functions to balance communication data rates and available computation capabilities. This is achieved by spatially pipelining baseband functions across parallel resources to perform multiple processing passes on the same set of received values, thus allowing the system to simultaneously convey multiple sequences of data using a single wireless link.

The use of multiple passes mitigates the effects of data rate on receiver processing bottlenecks, making the use of general-purpose processing elements for high data rate communication functions viable. The flexibility of general-purpose processing, in turn, allows the receiver composition to trade-off resource usage and required processing rate. For instance, a communication system could be distributed across 2 passes using  $2\times$  the overall area, but reducing the data rate for each pass and the resultant overall required processing rate, and hence clock speed, by 1/2. Lowering the clock speed can also be leveraged to reduce power through voltage scaling and/or the use of higher  $V_t$  devices.

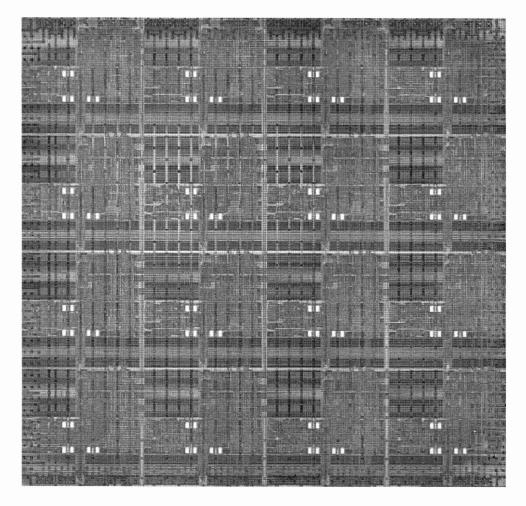

The characteristics of general-purpose parallel processors for communications processing are explored, as well as the applicability of specific parallel designs to communications processing. In particular, an in depth look is taken of the Raw processor's tiled architecture as a general-purpose parallel processor particularly well suited to portable communications processing.

An example of a multipass system, based on the 802.11a baseband, implemented on the Raw processor along with the accompanying hardware implementation is presented as both a proof-of-concept, as well as a means to explore some of the advantages and trade-offs of such a system. A bit-error rate study is presented which shows this multipass system to be within a small fraction of 1dB of the performance of an equivalent data rate single pass system, thus demonstrating the viability of the multipass algorithm.

In addition, the capability of tiled processors to maximize processing capabilities at the system block level, as well as the system architectural level, is shown. Parallel implementations of two processing intensive functions: the FFT and the Viterbi decoder are shown. A parallelized assembly language FFT utilizing 16 tiles is shown to have a  $1,000 \times$  improvement, and a parallelized 48-tile assembly language Viterbi decoder is shown to have a  $10,000 \times$  improvement over corresponding serial C implementations.

#### Thesis Supervisor: Anant Agarwal

Title: Professor of Electrical Engineering and Computer Science

#### Acknowledgments

This thesis is the culmination of much hard work and perseverance on my part, but it would not have been possible without the help, support, and good wishes of a large number of people. I would especially like to thank my fiancée Alison for her help and understanding. Her presence has comforted me and been my foundation in the last hectic push to finish. My parents and family have been behind me for years and made it possible for me to pursue my educational goals. My advisor Anant Agarwal has provided me with guidance and the freedom to explore my ideas, a precious gift that I truly appreciate. Charlie Sodini and Anantha Chandrakasan first and foremost for being friends and mentors and helping me find my way, and secondly for being my thesis committee.

I would also like to thank many of the students whom I have met along the way and who have made this graduate experience so much more than just this thesis. The whole Raw group has contributed to my research and understanding and for their friendship and for that I thank them. In particular I would like thank Jason Miller for being a good friend, officemate, and sounding board. Matthew Frank for also sharing an office and for some truly thought provoking and exciting conversations, as well as his help and support. David Wentzlaff for his ideas, insight, and companionship. Hank Hoffman and Theodoros Konstantakopoulos for their friendship and their editing help. Benjamin Walker for his work on the Wireless RF board, as well as for allowing me to share a bit of what I have learned with him.

Dan McMahill, Don Hitko, and Andy Wang have provided camaraderie, teaching, learning, and shared experience and for that I thank them. Charlie Sodini's Group, Harry Lee's Group, and Anantha Chandrakasan's Group have all provided me with friendship, help, and support at various times throughout my career which has been much appreciated.

Thanks to Jennifer Tucker, Cornelia Colyer, Mary McDavitt, and all of the staff who have given so generously of their time and have kept the completion of this thesis and my continued sanity from being mutually exclusive concepts.

I would also like to thank DARPA for the financial support which made this thesis possible, and the Engim Corporation for their generous donation of RF components, schematics, and time.

# Contents

| 1 | Intr | ntroduction                                              |    |  |  |  |  |

|---|------|----------------------------------------------------------|----|--|--|--|--|

|   | 1.1  | Portable Processing                                      | 17 |  |  |  |  |

|   | 1.2  | Digital Computation for Communication                    | 19 |  |  |  |  |

|   |      | 1.2.1 Digital Communications Overview                    | 19 |  |  |  |  |

|   |      | 1.2.2 Bottleneck Problem                                 | 20 |  |  |  |  |

|   | 1.3  | Thesis Contributions                                     | 30 |  |  |  |  |

|   | 1.4  | Dissertation Structure                                   | 32 |  |  |  |  |

| 2 | Dig  | ital Communications                                      | 35 |  |  |  |  |

|   | 2.1  | Digital Communication Systems                            | 35 |  |  |  |  |

|   | 2.2  | Modulation Techniques                                    | 39 |  |  |  |  |

| 3 | Dig  | gital Radios 4                                           |    |  |  |  |  |

|   | 3.1  | Digital Implementation Approach                          | 46 |  |  |  |  |

|   | 3.2  | Software Radios                                          | 48 |  |  |  |  |

|   | 3.3  | Digital Radio Strengths                                  |    |  |  |  |  |

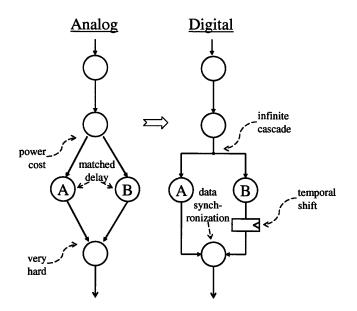

|   |      | 3.3.1 Infinite Cascade                                   | 49 |  |  |  |  |

|   |      | 3.3.2 Data Synchronization                               | 51 |  |  |  |  |

|   |      | 3.3.3 Temporal Shift                                     | 51 |  |  |  |  |

|   | 3.4  | Software Implementation Benefits                         | 52 |  |  |  |  |

| 4 | Cor  | nmunication Systems on Parallel Processing Architectures | 55 |  |  |  |  |

|   | 4.1  | Parallel Processing Trends                               | 56 |  |  |  |  |

|   | 4.2  | Effects of Interconnect on Communication System Design   | 57 |  |  |  |  |

|   | 4.3  | Effects of I/O on Communication System Design            | 59 |  |  |  |  |

|   | 4.4 | Effects of Reuse on Communication System Design |

|---|-----|-------------------------------------------------|

|   | 4.5 | Parallel Architectures for Communication        |

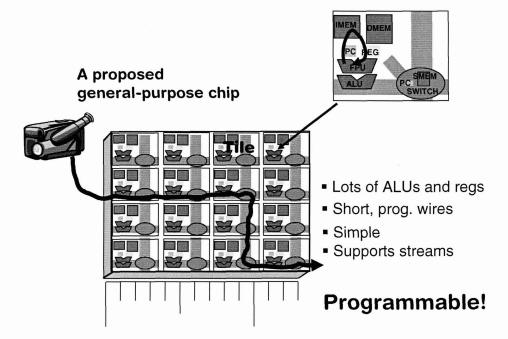

|   |     | 4.5.1 Tiled Architectures                       |

|   |     | 4.5.2 Chip Multi-Processor (CMP)                |

|   |     | 4.5.3 Multi-chip Systems                        |

|   |     | 4.5.4 Networked Clusters                        |

| 5 | Mu  | ltipass 73                                      |

|   | 5.1 | Concept                                         |

|   |     | 5.1.1 Digital Domain Enablers                   |

|   | 5.2 | Multipass System Example                        |

|   |     | 5.2.1 Transmitter                               |

|   |     | 5.2.2 Channel                                   |

|   |     | 5.2.3 Receiver                                  |

|   | 5.3 | Further Multipass Compositions                  |

|   | 5.4 | Benefits of a Multipass System                  |

|   |     | 5.4.1 Reduced Power Consumption                 |

|   | 5.5 | Limitations on Multipass Systems                |

| 6 | The | e Raw Processor – A Tiled Architecture 95       |

|   | 6.1 | Design Philosophy                               |

|   |     | 6.1.1 Scalability                               |

|   |     | 6.1.2 Designability                             |

|   |     | 6.1.3 Exposed Communication                     |

|   |     | 6.1.4 Streaming I/O                             |

|   | 6.2 | Communication Networks                          |

|   |     | 6.2.1 Low-latency, High-speed Interconnect      |

|   |     | 6.2.2 Dynamic Networks 9                        |

|   |     | 6.2.3 Switch Processor                          |

|   | 6.3 | Raw Implementation                              |

|   |     | 6.3.1 BTL Simulator                             |

|   |     | 6.3.2 Technology Scaling 10                     |

| 7 | $\mathbf{M}\mathbf{u}$ | ltipass | Implementation System                                                    | 105 |

|---|------------------------|---------|--------------------------------------------------------------------------|-----|

|   | 7.1                    | Selecti | ion of 802.11a Baseband                                                  | 106 |

|   | 7.2                    | 802.11  | a Specification Overview                                                 | 108 |

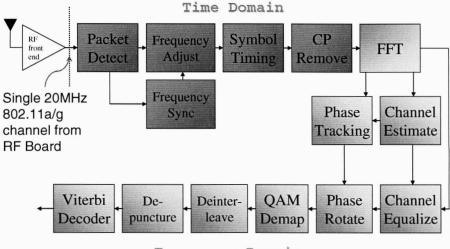

|   |                        | 7.2.1   | Orthogonal Frequency Division Multiplexing (OFDM) $\ldots \ldots \ldots$ | 108 |

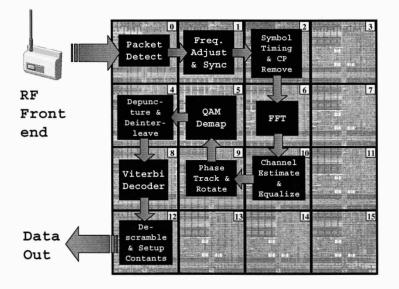

|   |                        | 7.2.2   | 802.11a Block Diagram                                                    | 109 |

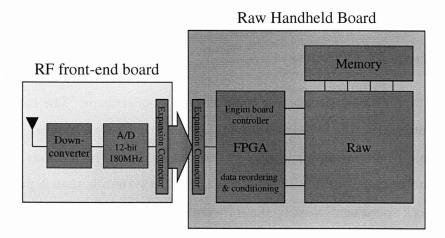

|   | 7.3                    | System  | n Hardware                                                               | 113 |

|   |                        | 7.3.1   | Raw Wireless System                                                      | 113 |

|   |                        | 7.3.2   | Raw Handheld Board                                                       | 113 |

|   |                        | 7.3.3   | Wireless Board                                                           | 116 |

|   | 7.4                    | System  | n Software                                                               | 118 |

|   |                        | 7.4.1   | Sequential, Single Pass Design                                           | 119 |

|   |                        | 7.4.2   | Matlab, Single Pass Design                                               | 122 |

|   |                        | 7.4.3   | Single Tile, Single Pass Design                                          | 122 |

|   |                        | 7.4.4   | Multi-tile, Single Pass Design                                           | 123 |

|   |                        | 7.4.5   | Optimized Multi-tile, Single Pass Design                                 | 125 |

|   |                        | 7.4.6   | Optimized Multi-tile, Multipass Design                                   | 140 |

|   |                        | 7.4.7   | Simulated Optimized Multi-tile, Multipass Design                         | 143 |

| 8 | Res                    | ults ar | nd Analysis                                                              | 145 |

|   | 8.1                    | Testin  | g Methodology                                                            | 146 |

|   | 8.2                    | Pass2   | Scaling                                                                  | 147 |

|   |                        | 8.2.1   | Asymmetric Passes                                                        | 149 |

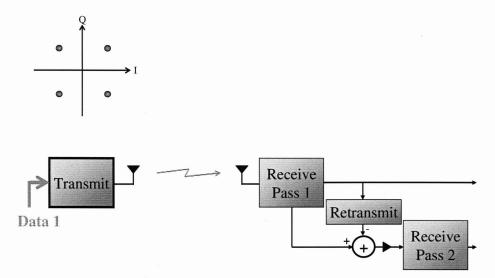

|   | 8.3                    | QPSK    | QPSK 2-pass Multipass System                                             | 150 |

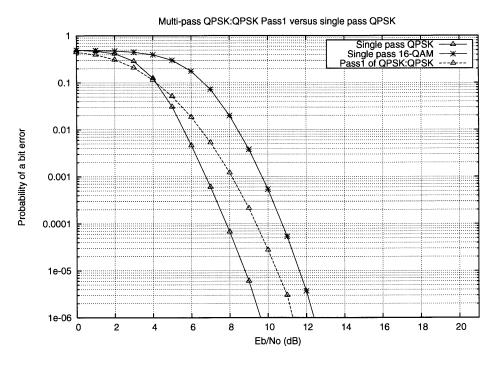

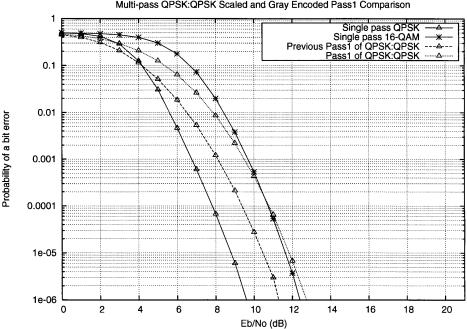

|   |                        | 8.3.1   | QPSK:QPSK Pass1                                                          | 150 |

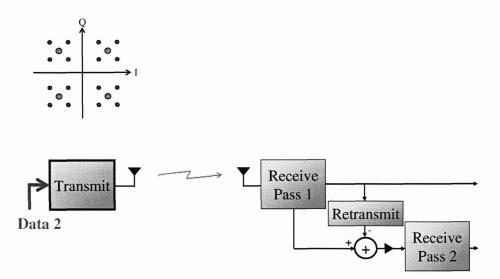

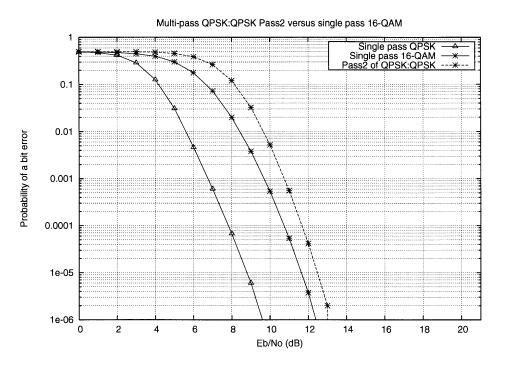

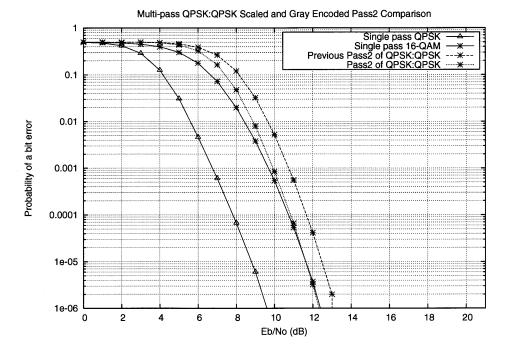

|   |                        | 8.3.2   | QPSK:QPSK Pass2                                                          | 152 |

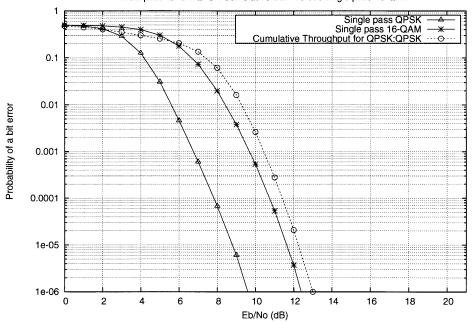

|   |                        | 8.3.3   | QPSK:QPSK Cumulative Throughput                                          | 154 |

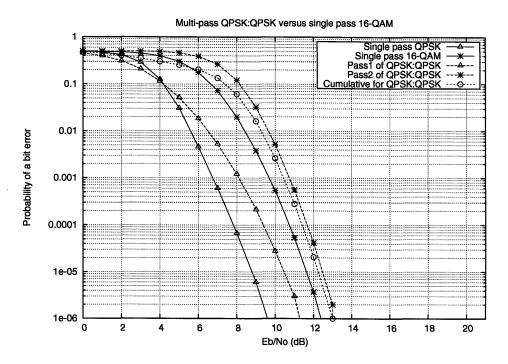

|   |                        | 8.3.4   | QPSK:QPSK Multipass                                                      | 155 |

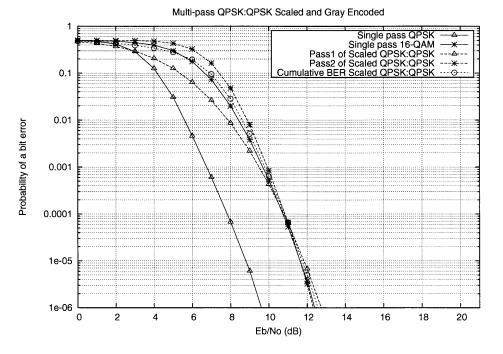

|   | 8.4                    | Scaled  | QPSK:QPSK Performance                                                    | 156 |

|   |                        | 8.4.1   | Scaling Revisited                                                        | 156 |

|   |                        | 8.4.2   | Gray Encoding                                                            | 158 |

|   |                        | 8.4.3   | Scaled QPSK:QPSK Multipass                                               | 160 |

|   | 8.5                    | Summ    | ary                                                                      | 166 |

| 9  | Conclusions                                | 167 |  |  |  |  |

|----|--------------------------------------------|-----|--|--|--|--|

| 10 | 10 Related Work 17                         |     |  |  |  |  |

|    | 10.1 Multipass-like Systems                | 171 |  |  |  |  |

|    | 10.2 Software Radios                       | 174 |  |  |  |  |

|    | 10.3 Other Tiled Architecture Platforms    | 175 |  |  |  |  |

|    | 10.4 Viterbi Decoder Work                  | 176 |  |  |  |  |

| 11 | Future Work                                | 179 |  |  |  |  |

|    | 11.1 Alternate Combining Functions         | 179 |  |  |  |  |

|    | 11.1.1 Data Layering                       | 180 |  |  |  |  |

|    | 11.1.2 Colored Data Layering               | 184 |  |  |  |  |

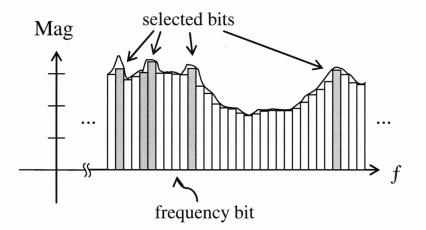

|    | 11.1.3 Frequency Bits                      | 184 |  |  |  |  |

|    | 11.2 Alternate Channel and Radio Models    | 185 |  |  |  |  |

|    | 11.3 Implementation on Alternate Platforms | 186 |  |  |  |  |

|    | 11.3.1 Other Parallel GPP Systems          | 186 |  |  |  |  |

|    | 11.3.2 ASICs                               | 187 |  |  |  |  |

|    | 11.3.3 FPGAs                               | 187 |  |  |  |  |

|    | 11.4 Adaptable Systems                     | 187 |  |  |  |  |

| A  | 802.11a Specification Values               | 189 |  |  |  |  |

# List of Figures

| 1-1  | Digital communication system block diagram                                 | 19 |

|------|----------------------------------------------------------------------------|----|

| 1-2  | Bottleneck Problem – Single Receiver                                       | 21 |

| 1-3  | Bottleneck Problem – Multiple Fixed Receivers                              | 24 |

| 1-4  | Bottleneck Problem – Multiple Flexible Receivers                           | 27 |

| 1-5  | Distributing Bottlenecked Functions                                        | 29 |

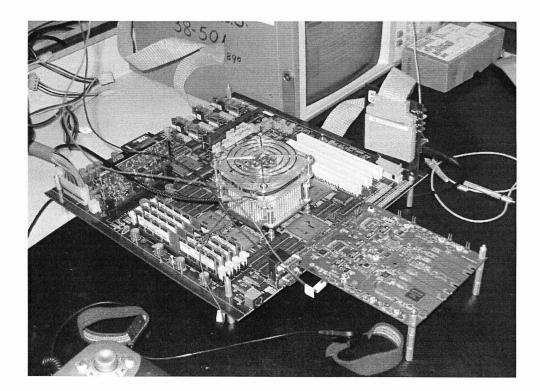

| 1-6  | Raw Wireless System Photo                                                  | 31 |

| 2-1  | Digital communication system block diagram                                 | 36 |

| 2-2  | Additive White Gaussian Noise (AWGN) channel model                         | 37 |

| 2-3  | Modulation Examples                                                        | 42 |

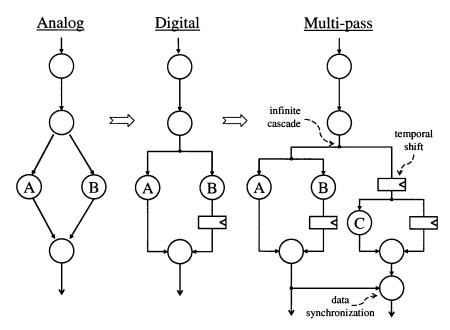

| 3-1  | Digital domain properties for digital radios                               | 50 |

| 4-1  | An example of a Tiled Architecture.                                        | 66 |

| 5-1  | Multipass Trade-off                                                        | 74 |

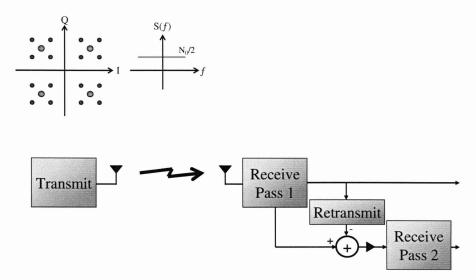

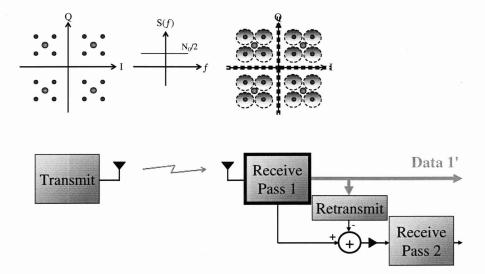

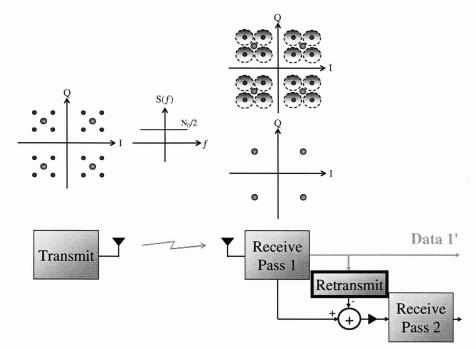

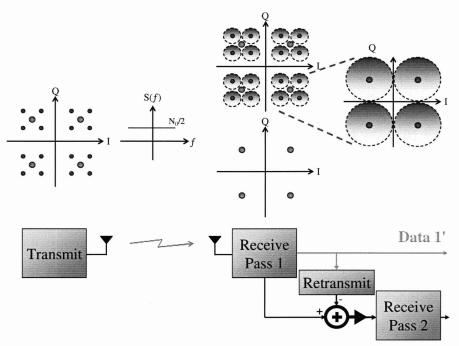

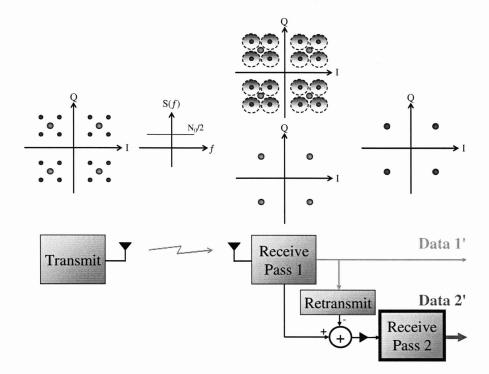

| 5-2  | Multipass general concept                                                  | 76 |

| 5-3  | Noise source comparison between implementation types                       | 78 |

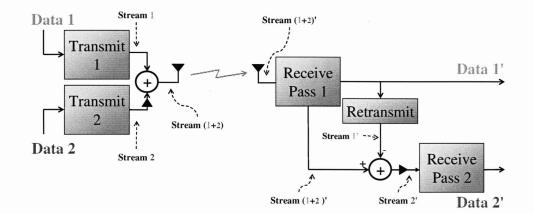

| 5-4  | 2-pass multipass system example                                            | 80 |

| 5-5  | QPSK:QPSK 2-Pass Multipass System Example – Transmit Phase I $\ .\ .\ .$   | 81 |

| 5-6  | QPSK:QPSK 2-Pass Multipass System Example – Transmit Phase II              | 82 |

| 5-7  | QPSK:QPSK 2-Pass Multipass System Example – Wireless Channel $\ . \ . \ .$ | 84 |

| 5-8  | QPSK:QPSK 2-Pass Multipass System Example – Receive Phase I $\ .\ .\ .$    | 85 |

| 5-9  | QPSK:QPSK 2-Pass Multipass System Example – Receive Phase II $\ldots$      | 86 |

| 5-10 | QPSK:QPSK 2-Pass Multipass System Example – Receive Phase III $\ldots$     | 87 |

| 5-11 | QPSK:QPSK 2-Pass Multipass System Example – Receive Phase IV               | 88 |

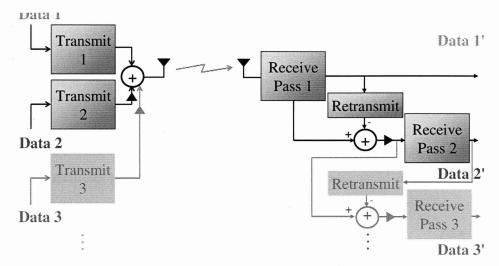

| 5-12 | Beyond 2-Pass Multipass System                                  | 89           |

|------|-----------------------------------------------------------------|--------------|

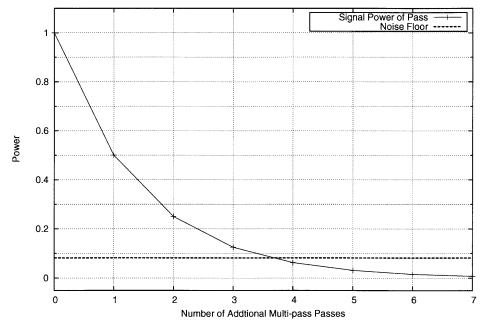

| 5-13 | Multipass noise limitations                                     | 93           |

| 6-1  | Raw die photo                                                   | 102          |

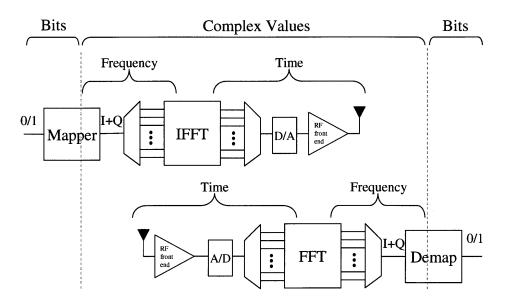

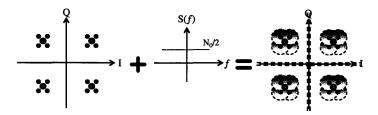

| 7-1  | OFDM Overview                                                   | 109          |

| 7-2  | 802.11a receiver block diagram                                  | 110          |

| 7-3  | Wireless System Overview                                        | 114          |

| 7-4  | Raw Wireless System Photo                                       | 114          |

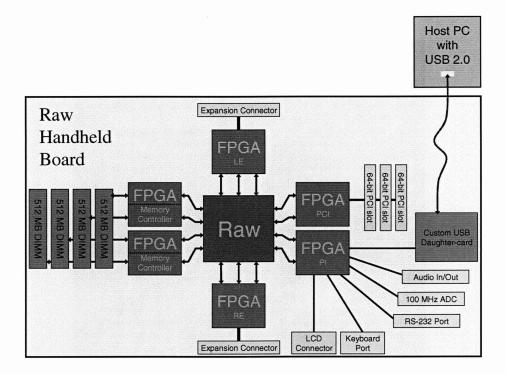

| 7-5  | Block diagram of the Raw Handheld Board                         | 115          |

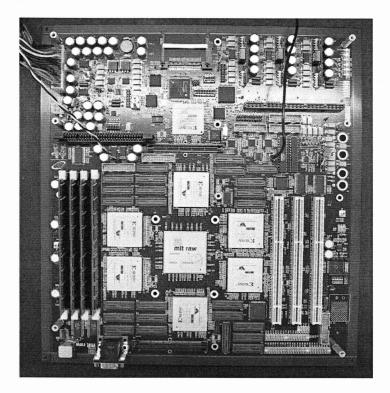

| 7-6  | Raw Handheld Board                                              | 116          |

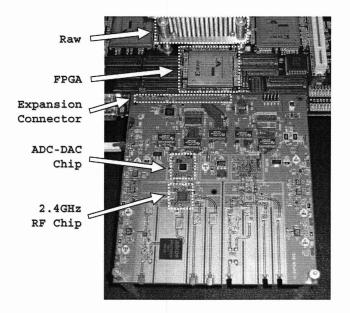

| 7-7  | Raw Wireless Board                                              | 117          |

| 7-8  | C single pass BER                                               | 121          |

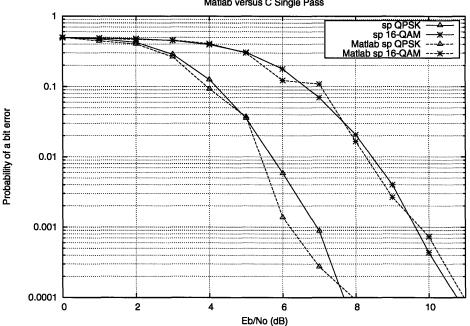

| 7-9  | Matlab versus C single pass BER                                 | 122          |

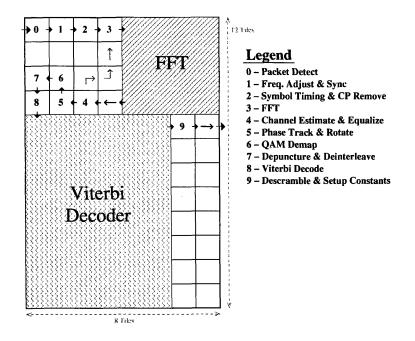

| 7-10 | Multiple tile receiver Raw mapping                              | 124          |

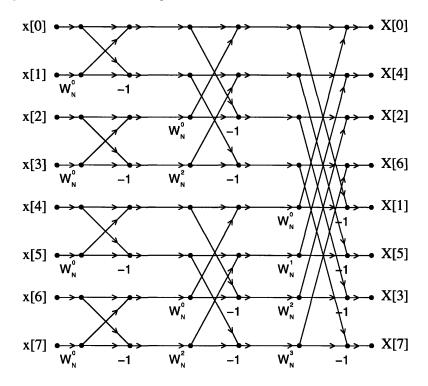

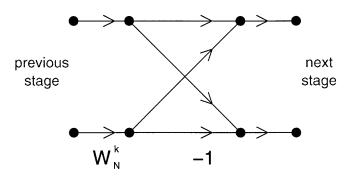

| 7-11 | Example FFT Dataflow                                            | 1 <b>2</b> 6 |

| 7-12 | FFT butterfly                                                   | 127          |

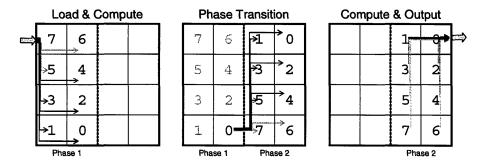

| 7-13 | Optimized FFT phases                                            | 128          |

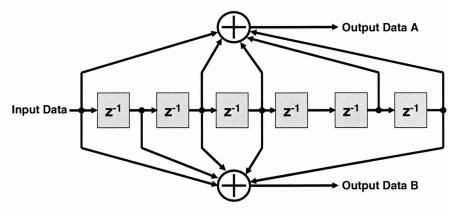

| 7-14 | 802.11a Convolutional Encoder                                   | 133          |

| 7-15 | Overview of the Viterbi decoder block diagram                   | 134          |

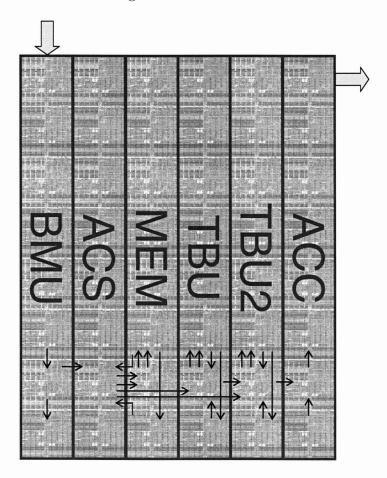

| 7-16 | Parallel Viterbi decoder layout                                 | 134          |

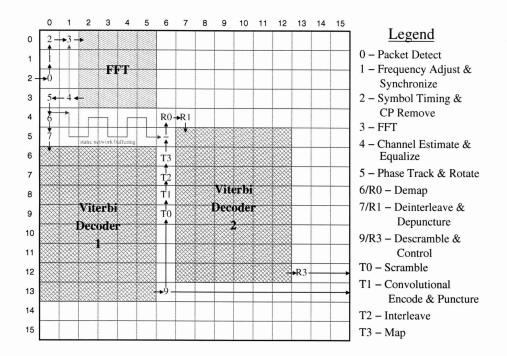

| 7-17 | Optimized multiple tile receiver Raw mapping                    | 140          |

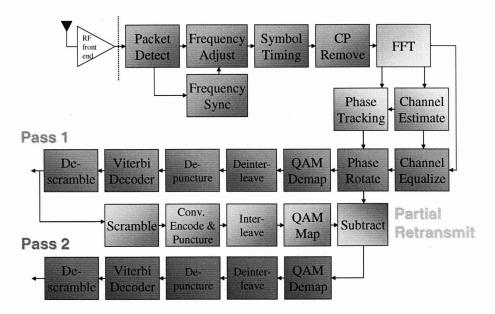

| 7-18 | Multipass 802.11a receiver block diagram                        | 141          |

| 7-19 | Multipass receiver Raw mapping                                  | 142          |

| 8-1  | A heavily scaled down Pass2 multipass constellation             | 148          |

| 8-2  | A lightly scaled down Pass2 multipass constellation             | 148          |

| 8-3  | BER comparison - QPSK:QPSK Pass1 vs. Single Pass QPSK           | 151          |

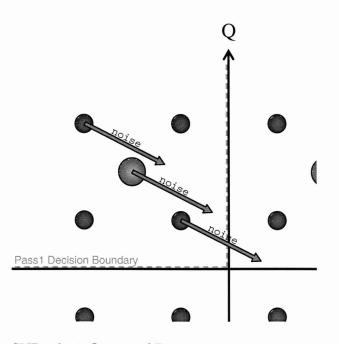

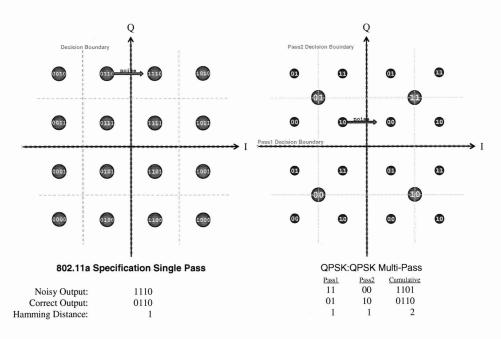

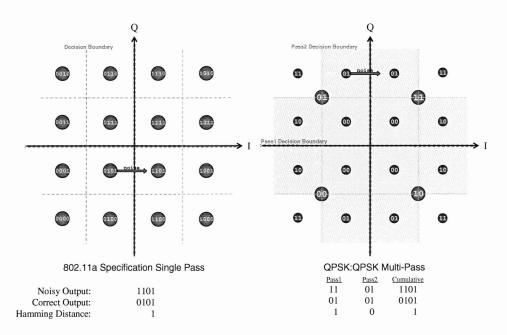

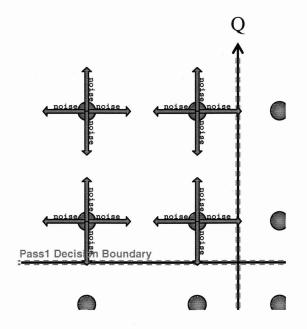

| 8-4  | Potential Impact of High SNR Noise on a QPSK:QPSK constellation | 152          |

| 8-5  | BER comparison - QPSK:QPSK Pass2 vs. Single Pass 16-QAM         | 153          |

| 8-6  | BER comparison - QPSK:QPSK Cumulative vs. Single Pass 16-QAM    | 155          |

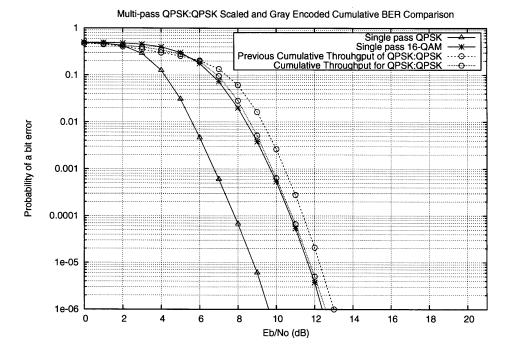

| 8-7  | BER comparison - QPSK:QPSK vs. Single Pass, all curves          | 156          |

| 8-8  | Hamming Distances of Multipass System                           | 159          |

| 8-9  | Hamming Distance of Gray Encoding Multipass System                                | 159 |

|------|-----------------------------------------------------------------------------------|-----|

| 8-10 | BER comparison - Scaled QPSK:QPSK vs. Single Pass, Pass1                          | 160 |

| 8-11 | BER comparison - Scaled QPSK:QPSK vs. Single Pass, Pass2                          | 161 |

| 8-12 | Potential Effects of Noise on the Scaled Pass1                                    | 163 |

| 8-13 | BER comparison - Scaled QPSK:<br>QPSK Cumulative vs. Single Pass                  | 164 |

| 8-14 | BER comparison - Scaled QPSK:<br>QPSK vs. Single Pass, all curves $\ \ . \ . \ .$ | 165 |

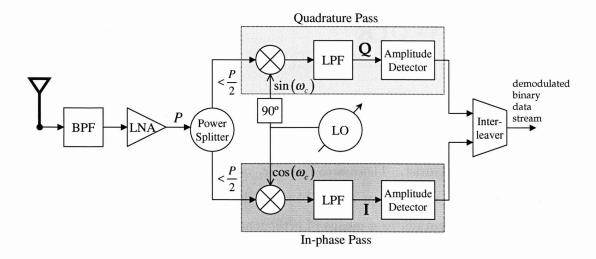

| 10-1 | Direct conversion quadrature receiver block diagram                               | 172 |

| 11-1 | Data layering virtual channels                                                    | 181 |

| 11-2 | Data layering example                                                             | 181 |

| 11-3 | Data layering frequency spreading                                                 | 182 |

| 11-4 | Colored data layering frequency spectrum                                          | 184 |

| 11-5 | The spectrum parceled into frequency bits                                         | 185 |

# List of Tables

| 4.1 | Comparison of parallel architecture systems                   | 66  |

|-----|---------------------------------------------------------------|-----|

| 6.1 | Speculative effects of technology scaling on Raw processors   | 103 |

| 7.1 | Data rate equivalencies of multipass 802.11a modulation types | 107 |

| 7.2 | Comparison of FFT Implementation Properties                   | 130 |

| 7.3 | Comparison of Viterbi decoder Implementation Properties       | 138 |

| A.1 | Major Parameters of the 802.11a OFDM PHY                      | 189 |

| A.2 | 802.11a Data Rate Values                                      | 190 |

| A.3 | 802.11a System Values                                         | 190 |

·

16

### Chapter 1

## Introduction

Increased functional demands on portable digital devices such as PDAs, cell phones, handheld gaming consoles, and laptops have led to a corresponding demand for more powerful processing capabilities in such devices [1]. Portable devices have become integrated into everyday life to such an extent that it is often impractical to carry an individual device to perform each desired user task. Thus, the trend and expectation is toward merging the functionality originally distributed among multiple devices into a single device [2]. Wireless connectivity is a capability which is increasingly important to the portability of such devices. The integration of wireless networking into portable devices enables them to perform a much fuller and more fully-functioned set of tasks. Future device designs will continue further along this trend [3].

This growing array of tasks assigned to portable devices is rapidly precluding the use of highly specialized digital processing elements. To satisfy the diversity of applications envisioned, more general-purpose processing capabilities are required. In addition, the functionality of such devices requires (or is supplemented by) incorporating faster and more efficient wireless capabilities. General-purpose parallel digital processors, which are becoming more common [4, 5, 6, 7, 8, 9], can be utilized to meet these coincident demands [10].

#### 1.1 Portable Processing

Ubiquitous wireless access has quickly become an integral part of everyday life [2, 11]. As wireless devices have become more commonplace, the competition to incorporate more functionality and utility into small portable devices has grown [12]. Cell phones are expected to play videos, search the Internet, and act as portable email clients [13]. Game devices are used to watch movies and play Internet-linked games, in addition to their traditional functions [14, 15]. Laptops, tablet PCs, and PDAs come equipped with wireless capabilities such as Wi-Fi and Bluetooth connectivity [16, 17, 18].

The varied and disparate nature of the applications bundled on a single wireless device create a technology and design challenge. Powerful general-purpose processing will be required to provide the myriad set of functions envisioned for portable devices. Given the need for such processors, these processing resources can also be utilized for communications processing.

The advantages of reusing a system's general-purpose processor (GPP) for performing digital communications processing, as opposed to using a separate application-specific implementation, are threefold. First, there is the obvious reduction in cost. Since portable devices will already require powerful processing units, these units can be reused for communications. This will help amortize the costs already associated with providing such processors and preclude further expenditure to provide communications baseband processing.

A second major advantage is the ease of development and use associated with a generalpurpose processing solution. By using a GPP, communications functions can be implemented in software. Implementation using a high level language, compiler infrastructure, and debugger can allow quicker and easier implementation of communication algorithms. This translates to a reduction in development costs and time.

Finally, the flexibility afforded by a general-purpose processing solution is extremely valuable. A software implementation allows the communication algorithms used, and even the baseband structure itself, to be modified or replaced as needed. Applications can adapt or change the algorithms applied in response to current conditions. For instance, the type of equalization used can be changed depending on the amount and types of noise observed on the communication channel. Under poor conditions, a more ambitious but complex equalization could be used to try and maximize the received signal. When conditions are more favorable, a simpler but less effective equalization algorithm might be sufficient, with the reduced processing overhead freeing up resources for other tasks or enabling a corresponding reduction in the frequency of operation.

Using a software implementation also allows system changes at a later date. Changing standards, additional functions, improved algorithms, or even bug fixes can be easily im-

plemented in the communications chain simply through a software update. In a hardware system, a whole new revision of the hardware would be required.

#### **1.2** Digital Computation for Communication

The majority of modern portable devices operate on digital information. As such, most wireless systems used by portable devices are digital communication systems. They are systems which have digital bits as both the input to and output from the communication link, but which convert this digital information to an analog waveform for transmission across a physical wireless link [19, 20]

The general properties and makeup of a digital communication system will be discussed in general in Section 1.2.1 and in greater detail in Chapter 2. Section 1.2.2 then addresses the bottleneck problem – the issue of the processing requirements of certain communications functions increasing dramatically as data rates increase. Such bottlenecks are of particular concern in the uniprocessor GPP or DSP case where processing requirements can rapidly outstrip the capabilities of the available resources.

#### **1.2.1** Digital Communications Overview

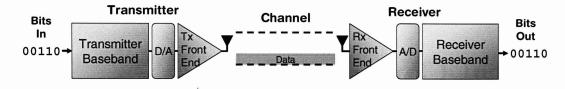

A communication system is a system which conveys information from a transmitter to a receiver across a medium. The information is input at the transmitter, is conveyed across the channel, and is then output by the receiver. A digital communication system is a communication system in which the system inputs and outputs are digital bits, see Figure 1-1.

Figure 1-1: A canonical wireless digital communication system block diagram.

The receiver is often the focus of communication system design as its mandate is the most difficult. The data presented to the transmitter is deterministic. The transmitter knows exactly what information is to be sent. The job of the transmitter is to generate a minimal representation of the information to be sent which is, at the same time, robust under the rigors of communication and then to condition and transduce this representation onto the channel.

The process of transmitting the information across the channel inherently distorts the representation of that information and makes reception a probabilistic, instead of a deterministic, enterprise. The transmitter itself introduces non-linearities and component noise to transmitted signals. In addition, the channel adds uncertainty to the system through path loss and propagation effects and obfuscates the information sent by the transmitter. The receiver itself further distorts the transmitter signals through the nonlinearities and noise of its own components.

In this environment, it is the job of the receiver to overcome the distortion and uncertainty of the received signals and attempt to retrieve the information originally sent. The receiver must attempt to recover the signal which was intended to be communicated from the noise which obscures it. Due to the inherent challenges of the job of reception, receivers are necessarily more complex and difficult to design than transmitters in a duplex<sup>1</sup> communication system. The ability to successfully perform reception therefore implies sufficient capabilities to perform transmission. Consequently, this dissertation will focus more heavily on the receiver functions than transmitter functions.

#### 1.2.2 Bottleneck Problem

In an ideal communication system data would flow across the wireless link at the fastest rate which the channel and applications could sustain. The ability of the receiver to process this data would never be an issue. Ideally, the applications producing and consuming the data and the channel are the drivers in setting the communication data rate. There are some receiver functions, however, whose processing requirements grow very large with increasing data rates. These functions can require more temporal reuse, and thus faster operation, than the receiver components will allow. The system then fails to meet its steady-state real-time deadlines. This is especially a problem for single GPP or DSP receiver architectures where a single set of hardware must be reused in time to try and perform all necessary functions. Even if such processors have the capability to implement a receiver and meet the real-time system requirements, there is little ability to increase temporal reuse to accommodate any increased processing required by higher data rates. This issue commonly limits the usage

$<sup>^{1}</sup>A$  duplex system is one in which all devices can both transmit and receive information.

of GPPs and DSPs in communications systems.

#### Single Receiver System

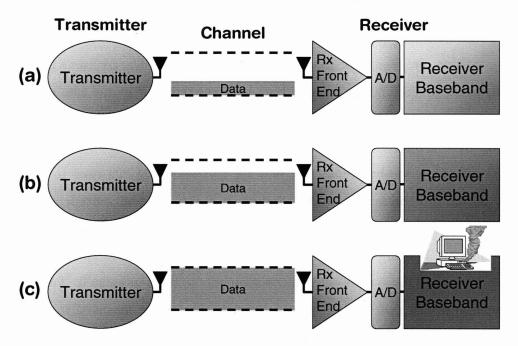

The problem of receiver processing limiting functionality can severely impact the maximum achievable data rate of the system. Depending on the channel conditions, the wireless application may be able to utilize a higher communication data rate. The receiver components, however, may not be able to sustain that higher rate, see Figure 1-2.

Figure 1-2: Effect of growing data rate on a single receiver system.(a) For low data rates, the receiver can sufficiently process the received data.(b) As the data rate increases, the increased reuse of the same receiver begins to push the temporal limits of the hardware.

(c) If the desired data rate is too high, the receiver hardware can no longer keep up.

For case (a), above, at a low data rate, the receiver can successfully process the flow of data. The receiver has been designed such that, with accommodating channel characteristics, the requested data rate is one which is available and sustainable. As the amount of data increases in case (b), however, the receiver starts to have problems keeping up. The high data rate requires more temporal reuse of the receiver resources, as well as a receiver design compatible with the higher data rate. When the desired data rate goes too high, as in case (c), the hardware resources can no longer keep up with the flow of information. Temporal reuse of the same receiver is no longer feasible and the communication link can

no longer be sustained.

This problem is a reflection of the bottlenecks encountered at many of the receiver elements. Two types of bottlenecks are the main limiters of the processing data rate in receive chains. These bottleneck types are referred to here as *data expansion* and *data chunking*.

#### **Data Expansion**

Data expansion occurs when a change in data representation increases the rate of processing within a receiver functional block. This is similar to a multiplication factor being applied to the processing rate seen prior to the data expansion block. The receiver's ability to deal with this faster processing requirement then becomes the limit to the rate at which data can be sent across the wireless channel.

For instance, a receiver demapping stage converts received symbols, the complex values which represent the received sinusoids, into the corresponding bits used to generate the symbol. Since the bandwidth of the wireless channel is generally fixed, an increase in data rate is achieved by having the symbols represent a larger number of bits. When the received data symbols are converted back into bits, the receiver data flow rate grows from the symbol rate into the symbol rate times the number of bits represented. This potentially large increase in the rate of data passed through the system means that the allowable number of bits per symbol must be limited by the receiver's ability to process this higher rate of bits.

Another example of data expansion can be seen in a Viterbi decoder [21, 22], where each set of bits generates a large amount of processing as they are used to create a new set of nodes in a trellis structure. As the data rate increases, the number of bits to be processed grows and the amount of processing work becomes very difficult to schedule. Viterbi decoders, and especially an optimized tiled Viterbi decoder implementation, will be discussed in Section 7.4.5.

#### Data Chunking

Data chunking occurs when data must be buffered into blocks before processing can occur. The negative impact of data chunking is that streaming-type processing is stalled by the need to use relatively large memory elements in order to gather sufficient amounts of data for processing to proceed. In essence, data pipelining is interrupted by a function which relies on correlation of a large amount of data or temporally random access. This interruption breaks the streaming model (see Section 4.3).

The deinterleaving function is an example of a data chunking function in a receiver chain. Deinterleaving is a process by which the ordering of bits within a portion of the bit stream is pseudo-randomly shuffled. It is the compliment to the interleaving function which is performed at the transmitter. The shuffling and unshuffling of bits by the interleaver and deinterleaver, respectively, provide a way to mitigate transmission errors. By ordering the bits in an essentially random fashion, the system improves the chances of recovering from a localized error. This is because many channel coding processes work on consecutive bits and can recover from single bit isolated errors much more easily than multi-bit errors. By moving these consecutive bits away from each other, the hope is that the impact of an error which corrupts multiple consecutive bits will be lessened. When the deinterleaving function restores the original bit ordering, it separates these consecutive error bits and turns them into isolated errors. In order to reshuffle a section of bits, however, the intermediate partial ordering of bits must be stored until the reordering can be completed. Once a whole deinterleaving block of bits has been stored, the newly order bits can be streamed out and the deinterleaver can begin on the next set of bits. Thus, the flow of processing bits is interrupted by the need to accumulate a whole section of bits.

A data chunking function like deinterleaving can be mitigated by a sufficient amount of storage. This is a possibility because the deinterleave function does not perform any operations on the bits themselves; it is only focused on the ordering of those bits. A function like the Fast Fourier Transform (FFT) [23], however, is a more complicated example of a data chunking function as it has a profound effect on both the relative ordering of information and the data itself. The FFT processing requires interaction between data values such that multiple data values must be accumulated before operation on the data can proceed. As such, certain wireless systems, for example, the 802.11a specification [24] (see Section 7.2 and appendix A), provide a maximum acceptable latency for the FFT. This maximum latency represents the amount of time the receiver pipeline can be stalled before disrupting the flow of received information. All necessary data must be buffered and all processing must be done within this maximum latency limit. A more careful examination of the FFT and its impact on receiver processing can be found in Section 7.4.5.

#### Multiple Receiver System

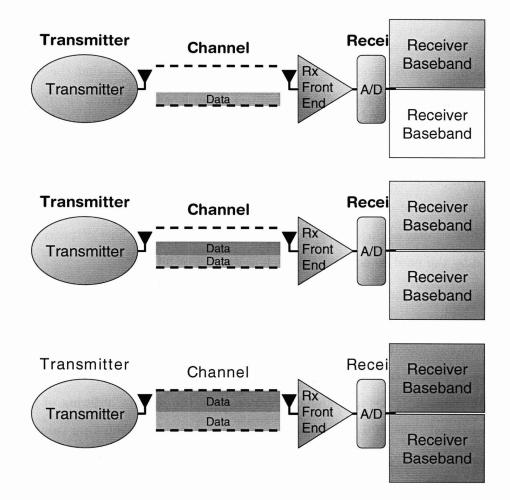

One way to overcome bottlenecks at the receiver and enable higher data rate communication is to use multiple receivers. A system with multiple receive chains that could distinguish between and appropriately direct data destined for each of these receivers would be able to accommodate multiple data streams with higher aggregate data rate than a single receiver system. For a given data rate, each of the multiple receivers could operate at a fraction of the total data rate, thus mitigating the bottlenecked portions of the receive chain, see Figure 1-3.

Figure 1-3: Use multiple receivers to try and accommodate higher data rates.

(a) Only a single receiver might be required for a low data rate. Any other receivers would then sit idle with under-utilized resources.

(b) If the data rate increases, however, a system which could spread the load over multiple fixed receivers would allow the system to operate on a higher aggregate data rate.

(c) A yet further increase in data rate, however, could be too much for even multiple fixed receivers.

The key to such a system would be in the combining and separating of data streams. Multiple different data streams or the demultiplexed data from a single data stream could be treated as multiple subchannels of data sent in parallel. Subchannels could be distinguished by frequency, by time, or by any means which would allow the subchannels to be combined and then later distinguished. What would be needed is a combining function which would allow multiple streams of data to be joined at the transmitter, but in an orthogonal way such that they could be disambiguated at the receiver. One specific approach using superposition as the combining function is presented in Chapter 5. Some additional potential combining functions are discussed in Section 11.1.

A multiple fixed receiver system reduces the impact of bottlenecks over a single fixed receiver system by providing both spatial and temporal reuse of the receive chain, as opposed to the temporal-only reuse of the single fixed receiver system. Spatial reuse is the reuse of a design to create multiple hardware instances which can operate in parallel. Functions can then be migrated onto parallel resources to reduce the load on a single resource. Higher data rates may be accommodated by a combination of streaming more data through each receive chain (temporal reuse) and by using multiple receive chains in parallel (spatial reuse).

This type of system does have some drawbacks, however. First of all, the system itself is fixed. While multiple receivers do allow higher data rates, there still exists a data rate threshold above which the system cannot operate. This threshold is higher than in the single receiver case as multiple receive chains must now be saturated to reach the threshold, but it still exists.

In addition, there are much higher costs associated with a multiple receiver system. In terms of characteristics important for portable wireless devices, such as physical size, dollar cost, and power, the multiple fixed receiver system is more expensive than a single receiver system. These costs might preclude building enough receivers to allow the desired maximum data rate. In effect, having multiple fixed receivers incurs the cost of the "worst" case, even in the more common or "lesser" cases. The system must be design around the maximum data rate envisioned. This means the resources required for the maximum data rate must be present even if they are not needed or in use.

From a design point of view, however, there is a significant savings in the use of multiple receivers. The spatial reuse of parallel resources means that a receive chain must only be designed once and can then be reused with little or no modification for each of the multiple receivers. The reuse of a single less ambitious or previously generated design can provide similar functionality to a more difficult, new, higher data rate design. The same problem still exists as in the single receiver case, though, of having to choose *a priori* which data rates the receivers will support. Fixing the number and design of receivers results in the forced choice of a single system architecture design point with a specific maximum data rate. This limits the multiple fixed receiver system both in terms of maximum data rate as well as possible combinations of lower data rates distributed among the multiple receivers.

The multiple receiver system as described above is an application of the multipass algorithm introduced in Section 1.2.2 and explored more fully in Chapter 5. While most of the discussion here focuses on the general-purpose processing space and the flexible receiver system presented below, the multipass algorithm is applicable to the fixed receiver case regardless of implementation method (e.g. GPP, ASIC, FPGA, etc.). The multipass algorithm can be used to achieve high data rate processing which trades increased area for a lower overall clock rate. A lower clock rate eases the temporal constraints on the system which translates to an increased ease of implementation with a corresponding reduction in design time. In addition, a lower minimum clock rate can be parlayed into lower overall power consumption through a reduction in  $V_{dd}$  and/or the use of higher  $V_t$  devices (see Section 5.4.1.

#### Flexible Receiver System

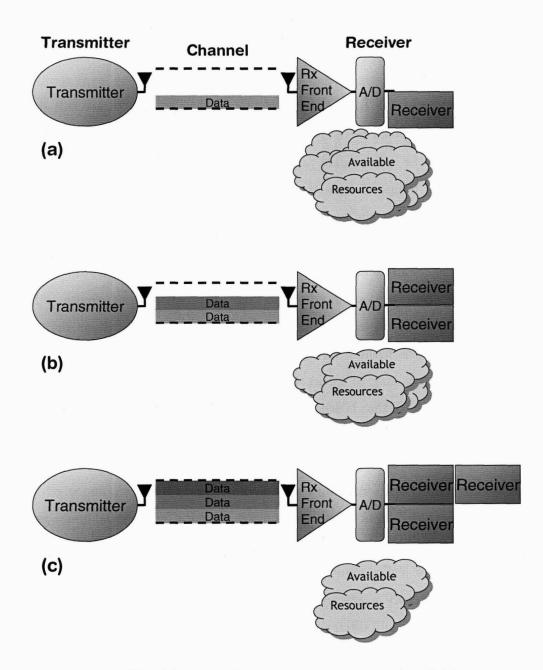

A wireless system which focuses on taking advantage of increases in processing speed provided by parallel resources and flexibility of general-purpose processing could do no more than slavishly re-implement elements from a traditional analog wireless systems inrece the digital domain. A better approach would be a system which could "construct" receivers as they are needed. Such a system could retask elements from a group of available resources in order to compose these resources into as many receivers as the desired data rate requires, see Figure 1-4. If later the data rate were to lower, or if other processing tasks were to take priority, these resources could then be freed up and reassigned for use in other tasks.

Such a flexible system offers the opportunity to trade-off temporal and spatial reuse to find a "sweet spot" based on the current conditions. For lower data rates, where temporal reuse is sufficient, a single receive chain can be used. When processing speeds begin to exceed the available or desired temporal reuse, however, spatial reuse can be employed to create

Figure 1-4: A means of flexibly composing receivers out of a set of available resources would allow the system to adjust to current conditions as needed.

(a) For lower data rates using only a small amount of resources to construct a single receiver might be sufficient.

(b) As the amount of data to be communicated grows more resources could be assigned to create additional receivers in order to successfully process the higher rate of data.

(c) A yet further increase in data rate could still be accommodated simply by making use of yet more of the available resources.

multiple parallel receive chains. This reduces the demands of temporal reuse and allows more, but slower and less ambitious, receivers to meet the processing needs. Even higher data rates may be accommodated by simply assigning more resources for communication in order to build additional receive chains. There is no need to know how many receive chains are needed ahead of time, or to design the system to accept every conceivable data rate. The system simply composes as many receivers as necessary in whatever configuration is necessitated by meet the current data rate.

This balancing of temporal reuse constraints and spatial reuse constraints allows the system to explicitly manage the trade-off between communication and computation. The system can offer more resources to communication to achieve higher data rates, but at the cost of reducing the resources available for computation of that or other data.

Such a system also provides the ability to take advantage of design reuse and reuse a single receive chain design to compose the additional receivers. This allows the system to adjust to data rate needs without having to *a priori* design in the ability to handle every data rate and without having to spend time on multiple receiver designs. A single design and verification effort is all that is needed. The system can simply reuse an already existing design to gain the use of additional cumulative data rates through the composition of receive chains.

A computer architecture suited for such a communications system, one which provides flexible hardware which allows a balance of both temporal and spatial reuse as well as concurrent independent computation, will be presented in Chapter 4. Furthermore, a communication technology, called multipass, which allows a flexible system to dynamically trade-off increased resource usage and area for lower processing rates and required clock speeds is introduced next and discussed in detail in Chapter 5.

#### Multipass

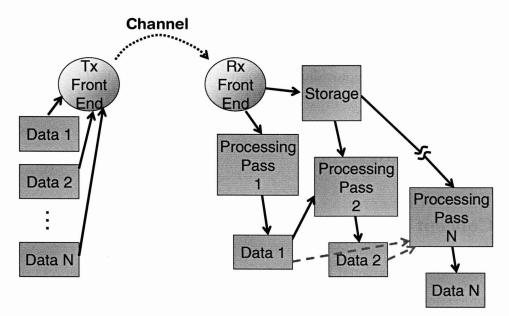

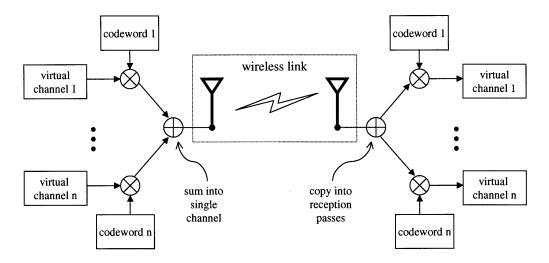

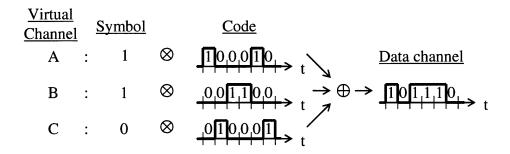

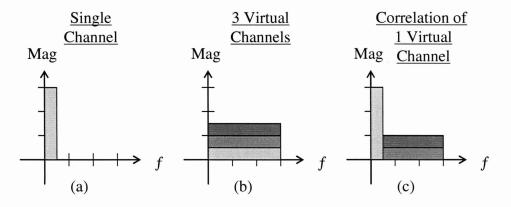

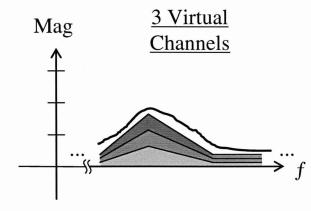

The *Multipass* algorithm is a method of communicating multiple streams of data in parallel across a single communication link. Multiple streams of data are processed individually at the transmitter and then combined for transmission across the channel. At the receiver, the combined data is decomposed into separate data streams, each of which is processed by its own baseband receiver processing pass.

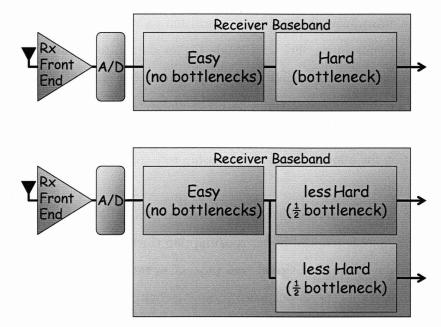

The multipass algorithm allows communication systems to utilize multiple receiver

passes in parallel to recover the data sent across a communication link. Multiple sets of resources distribute the receiver processing load for the "Hard" bottleneck functions, see Figure 1-5. For the system discussed in Chapter 7 the Viterbi decoder is this "Hard" bottleneck function. The multipass algorithm allows the system to achieve a high cumulative data rate through the use multiple baseband processing passes, and hence multiple Viterbi decoder instantiations, each running at a slower data rate. This enables the system to trade increased resource usage and area for a lower required processing rate and system clock speed. A slower clock speed can then be translated into a reduction in system power through the use of a lower supply voltage, or the use of lower  $V_t$  devices, as explored in Section 5.4.1.

Figure 1-5: Utilizing a single receiver processing pass forces a single set of hardware to attempt to overcome bottlenecks. While the "Easy" processing functions do not require a high processing rate, a multipass system can distribute the load of the "Hard" bottlenecked processing functions across multiple sets of hardware, requiring only half the processing rate for each. This reduces the impact of bottlenecks on the system and provides the opportunity for either higher data rate processing or lower system clock speeds. In the system discussed in Chapter 7, the "Hard" bottlenecked function is the Viterbi decoder. Multiple instances of the Viterbi decoder are utilized to mitigate the requirements of this function.

In a fixed receiver system, this trade-off between area and processing rate must be decided *a priori*, but the multipass algorithm allows increased flexibility in the initial system design. In a flexible receiver system built with general-purpose processing elements, however, the multipass algorithm allows the system to dynamically adjust the number and type of passes used to meet communication and computation constraints. The ability to decompose a high data rate communication stream into multiple lower rate streams makes feasible the use of general-purpose processors for high data rate communication processing. A lower required processing rate enables system viability by reducing the data rate requirements to a level compatible with the computational overhead incurred by general-purpose processing systems. A flexible multiple receiver system which takes advantage of the multipass algorithm is discussed in Chapter 5.

#### **1.3** Thesis Contributions

This dissertation introduces the multipass algorithm, a means of communicating multiple information streams in parallel as a single higher data rate stream over the channel. The multipass algorithm utilizes multiple receiver processing chains, or passes, to extract the lower data rate information streams from this single higher data rate received stream. Adding additional passes allows the system to trade-off increased area and processing resource consumption for a lower required processing rate for each pass, while maintaining a high cumulative data rate.

Reducing the required processing rate allows a lower minimum clock speed. A lower clock speed can, in turn, enable reduced power consumption through the use of voltage scaling or lower leakage devices. Lower individual pass processing rates also make possible high data rate communications in a general-purpose processing environment and allow a direct tradeoff between communications and computation in that environment. While the multipass algorithm itself is implementation agnostic, it is as appropriate for specialized hardware or FPGA implementations as a software implementation, multipass will be discussed here in the context of general-purpose processing tiled architectures.

Multipass communications systems offer a means to utilize tiled architectures in the communications realm. Such systems take advantage of the multiple parallel general-purpose processing elements of a tiled architecture to dynamically compose receive passes. The number and rate of these passes can then be flexibly adjusted to balance the overall required communication rate with the available computation resources, while maintaining a clock rate compatible with a general-purpose processing tiled architecture.

As a first step in the proof-of-concept of a multipass system, an effort was taken to

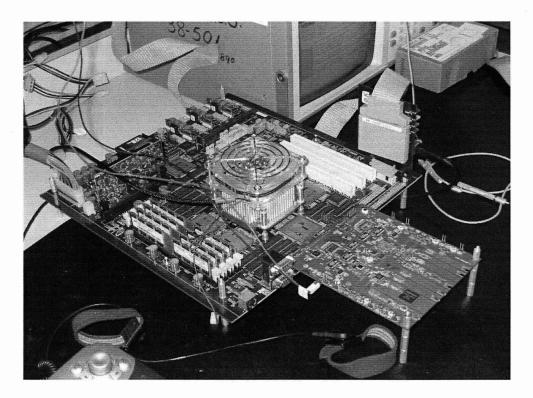

implement an 802.11a software receiver on a tiled architecture. The Raw processor was used as a tiled architecture platform to implement this baseband design. A hardware radio front-end board, the Raw Wireless Board, was designed and built to interface with the Raw handheld motherboard in order to complement and complete the receiver system, see Figure 1-6.

Figure 1-6: Photo of the Raw Wireless System.

The 802.11a Raw baseband design was then improved and expanded to become the first multipass receiver implementation. A multipass system, including a software multipass transmitter and a cycle-accurate Raw simulation of a multipass receiver was designed and tested. Versions of the multipass system using C and Matlab were also implemented and verified with the cycle-accurate results in order to improve simulation speeds.

As part of the optimization effort to make the 802.11a baseband compatible with realtime operation in a general-purpose processing environment, critical path receiver functions were parallelized and optimized. Chief among these bottlenecked functions were the FFT and Viterbi decoder functions. Assembly versions of both functions consistent with 54Mbps operation on a Raw digital processor were designed. This resulted in a 70 cycle 48-tile parallelized version of the Viterbi decoder, a  $10,000 \times$  improvement, as well as a 16-tile parallelized FFT which resulted in a  $1,000 \times$  improvement in performance.

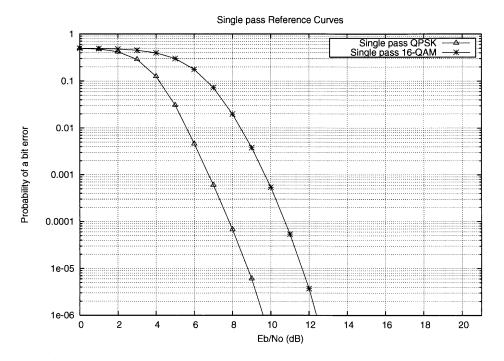

Given that the multipass approach enables high data rate communication system implementation on a general-purpose processing substrate, an evaluation of the performance of a multipass communication system relative to an application specific single pass system was undertaken. The feasibility of the multipass communication approach is shown, with a multipass system using a superposition combining function achieving performance reasonably close to the single pass case. System improvements which enhance this performance to within a small fraction of 1dB of that of the single pass case are discussed. In addition, future potential compositions of multipass systems using better-performing or application-specific combining functions are discussed.

#### **1.4** Dissertation Structure

The rest of this dissertation is structured as follows. Chapter 3 provides motivation for digital radios. It discusses the unique aspects of the digital domain which provide opportunities for new radio processing techniques. Chapter 2 provides a very brief overview of digital communication systems. Readers familiar which such systems can feel free to skip this chapter. Chapter 4 explores the characteristics of multiple types of parallel architectures. The impact of these various designs are discussed in relation to implementation of a digital radio communication system.

Chapter 5 presents the definition and a description of a multipass system, a means of utilizing the aspects of parallel architectures to implement a flexible digital radio. Chapter 6 provides details on the Raw processor, the tiled architecture used as the implementation target for the multipass system design.

Chapter 7 explores the implemented systems. A quick overview of the 802.11a specification, as well as the elements of a general 802.11a system are discussed. The details of the various system functions are explored. The hardware elements of the system and their interaction is also discussed. The software effort, including the simulation infrastructure is covered. Finally, the expansion of an 802.11a system into a multipass design, as well as the implementation details of a multipass system are presented. The optimization and parallelization of critical functions is overviewed.

Chapter 8 offers the multipass system performance results. The testing methodology is

presented. Comparison with the single pass case, as well as an analysis of the results and methods of improvement, are given.

Chapter 9 is a summary of the conclusions derived from this work.

The similarity of the multipass approach to other system solutions is considered in Chapter 10, including the commonality between multipass system and multiple user access schemes.

Finally, Chapter 11 envisions future multipass system configurations and applications. The use of additional and more complex combining functions is discussed. Also contemplated is the utilization of the general-purpose flexibility enabled by multipass systems to implement adaptable algorithms and other flexible receiver architectures. The application of multipass designs to other parallel platforms is also briefly considered.

### Chapter 2

### **Digital Communications**

This chapter provides a slighly more detailed overview of digital communication systems than in Section 1.2.1. Section 2.1 discusses the general aspects of digital communication systems, including the design elements of the transmitter and receiver, as well as a model for the wireless channel. Section 2.2 provides a more in-depth description of the various modulation techniques employed by such systems. These techniques play an important role in transforming digital bits into continuous waveforms. Readers who are familiar with digital communications can feel free to skip this chapter.

#### 2.1 Digital Communication Systems

A digital communication system is comprised of a transmitter and a receiver which communicate digital information across a channel, see Figure 2-1. The transmitter converts the digital information, the *Bits In*, into values for transmission across the channel. These values are then sent across the wireless channel to the receiver. The receiver converts these values back into bits, the *Bits Out*. The receiver does this in a manner which attempts to maximize the likelihood that the *Bits Out* output from the receiver matches the *Bits In* input to the transmitter.

The transmitter typically begins by performing digital processing on the *Bits In* to increase the robustness of the data communication link, as well as its usage efficiency. This results in data values which are used to represent the processed *Bits In*. This processing which takes place prior to up-conversion to higher frequencies is commonly referred to as baseband processing. These processed digital values then undergo digital-to-analog (D/A)

conversion to generate analog values from the digital information. The radio front end of the wireless transmitter prepares these values for transmission by mixing the analog values with sinusoids to generate waveforms at the carrier frequency. The antenna then transduces these carrier frequency sinusoids to electromagnetic waves which radiate out from the antenna and across the channel.

Figure 2-1: A canonical digital communication system block diagram.

The process of transmitting the information signal across the channel reduces its fidelity. The channel conditions, such as fades, path loss, and other propagation effects, as well as interference and channel noise contribute to a degradation in signal quality. The main factor which distinguishes a wireless channel from a wired channel is the changing nature of the channel characteristics and noise.

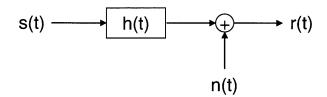

A common model used for channel noise is the Additive White Gaussian Noise (AWGN) model. While insufficient as an exact channel model, the AWGN model is often used for case studies. It provides a tractable and easily computed noise model which provides reasonable insight into the functionality of a communications system [19, 25, 26]. The AWGN model, see Figure 2-2, consists of a white Gaussian source which provides a statistically independent, identically distributed sequence of Gaussian random variables which are added to the signal as noise. Gaussian white noise is used because it provides a good approximation to the thermal noise of system components [26, 27]. The signal, as it travels through the communications system, is impacted by a large number of small, statistically independent noise sources which cumulatively, as per the Central Limit Theorem, look Gaussian in aggregate [25, 28, 29, 30]. This noise is referred to as white because it looks flat over the frequency range of interest and all of the individual noise sources are independent, like in true white noise. However, it is not true white noise in the sense that the flat spectrum does not extend over all frequencies between  $\pm \infty$  (this would require the AWGN source to have an infinite amount of power [31]).

Channel effects also play a large role in the quality of the signal received. Propagation effects such as path loss, slow and fast fades, delay spread and multipath, radiation resistance, and antenna gains can have a large impact on receiver signal strength. For instance, path loss results in the signal power falling off quickly as the distance between the transmitter and receiver is increased (thus increasing the relative impact of many channel noise sources) [32, 27, 33, 34, 35] and is proportional to the inverse of the distance (typically between  $\frac{1}{d^2}$  and  $\frac{1}{d^4}$ ). Other effects, such as fades in reception as the receiver moves into areas where the transmitted signal can't reach, or multipath effects where multiple reflected copies of the incoming signal are received, can distort and negatively impact the received signal. Direct interference from other radio sources, such as other transmitters, can also add significant non-signal power in the frequency range of interest, thus degrading the communication link. Channel effects are often expressed as a channel transfer function which is applied to the transmitted signal when it travels across the channel. Receiver functions, such as equalization, attempt to quantify and reverse the channel effects on the received signal, see Equation 2.1. The presence of noise on the received signal, however, makes this reversal of channel effects a non-linear process, and, hence, much more difficult to accomplish.

$$r(t) = s(t) * h(t) + n(t)$$

(2.1)

Figure 2-2: Additive White Gaussian Noise (AWGN) channel model.

The Signal-to-Noise Ratio (SNR) is often used as a metric of signal integrity. It relates the power or signal strength of the desired transmission as seen at the receiver to the power of all other extraneous sources observed with that signal. This is sometimes expressed as  $E_b/N_0$ , or the energy per bit divided by the noise power spectral density [36, 37]. In general, the higher the SNR, the more likely the information from the transmitter will be correctly communicated to the receiver.

At the receiver, another antenna transduces the resulting electromagnetic waves plus the accompanying noise into analog waveforms. The receiver front-end then down-converts these analog waveforms from the carrier frequency to a much lower frequency or DC. These low frequency signals are again referred to as baseband. The baseband signals are then commonly transitioned from the analog to the digital domain by an Analog-to-digital (A/D)converter. The resulting digital values are processed by the receiver's baseband receive chain in an attempt to recover the information sent and to recreate the transmitted bits, the *Bits In*. These recreated bits are the system output, the *Bits Out*.

The purpose of the digital communication system is to maximize the likelihood of correct and timely reception of the digital information from the transmitter at the receiver. Multiple signal processing techniques are applied to the information to achieve this end. These communication signal processing techniques generally fall into three categories: source coding, channel coding, and channel correction.

Source coding maximizes the usefulness of each bit to be transmitted in an information theoretic sense [19]. This consists of compressing the data such that the most information can be represented in the fewest bits possible. This compression has the effect of minimizing the correlation between bits and subsequently minimizing the number of bits in total. Reducing the total number of bits helps to contribute to the communication system's efficiency, as it results in more information being transmitted per bit sent while not affecting the amount of power required to send each bit. For the sake of the systems addressed in this dissertation, source coding is assumed to have been done prior to bits being presented as input to the digital communication system. The Separation Theorem guarantees that this assumption of a source coder separate from the channel coder does not impact the optimality of communication [38, 28].

Channel coding refers to modulation and error correction and mitigation techniques. It is a means by which to improve the likelihood of successful transmission of data across the channel. There are multiple possible techniques employed to achieve this goal [39]. Modulation techniques map data into waveforms for transmission across the channel. Modulation is discussed in greater detail in Section 2.2. Among the error correction and mitigation techniques are state-based encoding and interleaving. State-based encoding, such as convolutional encoding, adds redundancy and locally correlates the bits through the use of state information in the encoding. This results in a larger number of overall bits, but with a set of bits which are redundant enough, and correlated enough, that errors in bit transmission can often be overcome and the correct bits inferred at the receiver. Interleaving, on the other hand, is an error mitigation technique. It involves changing the ordering in a set of bits such that correlated bits, which have been generated by other channel coding techniques, are not transmitted consecutively. This is done to reduce the impact of any multi-bit errors which might occur during transmission. It is not unusual for interference or propagation errors to effect multiple consecutive bits. Interleaving is a means by which these corrupted bits can be spread out throughout a data block thereby isolating errors and giving other channel coding error recovery techniques, especially those which rely on mutual information between consecutive bits, a higher likelihood of success.

Channel coding is often at odds with source coding. Source coding focuses on efficient representation of bits in order to reduce the number of bits sent, while channel coding inflates the number of bits to maximize the tolerance of the communication link. Therefore, it is necessary to balance the transmission-level requirements of robustness and functionality in the face of error-inducing conditions with the system-level requirements of power efficiency and minimized latency.

Channel correction techniques attempt to undo the effects of the physical wireless channel on the transmitted waveforms. They are mainly concerned with compensating for error sources which are relatively constant over the course of a transmission. Error sources such as current channel effects, hardware offsets, and fading can often be addressed without regard to the specific data being sent. This data independence allows the use of meta-information, such as headers or pilot tones, which can be standardized *a priori* and known by both the transmitter and receiver to empirically determine the compensation parameters for channel correction techniques. Channel correction functions include techniques such as: channel equalization, phase correction, and frequency correction. [26, 36, 30]

An example of a digital communication system which implements a set of these signal processing techniques is presented in Section 7.2.

## 2.2 Modulation Techniques

Modulation is the mapping of data onto time-varying signals for use by the analog radio front-end. [25, 26, 27, 32] Transduction of signals by the antenna into electromagnetic waves necessarily requires these time-varying signals. Modulation commonly consists of generating a sinusoid whose specific aspects convey a piece of data. Sinusoids are typically used as the modulating waveform for numerous reasons, among them are: the prevalence of Fourier analysis and the ability of sinusoids to act as an orthonormal basis which spans the reals [40]; the convenient mixing properties of sinusoids when multiplied together [41, 23]; the use of frequency as a means of partitioning and dictating the electromagnetic spectrum; and the ease of creating sinusoidal sources in analog electronics.

There are three aspects of sinusoids which are used to encode information: amplitude, frequency, and phase. The type of modulation scheme determines which sinusoid aspect or aspects are used to distinguish data values. For instance, in terrestrial radio, two different modulation schemes are used: amplitude modulation (AM) and frequency modulation (FM). In amplitude modulation, the amplitude of a radio frequency sinusoid, or carrier wave, is directly adjusted so that it matches the data signal. The data signal can then be directly recovered from the envelope of the transmitted carrier wave. In frequency modulation, the frequency of the carrier wave is adjusted based on the data values. The deviation of the carrier wave frequency from its nominal frequency is detected at the receiver and used to recreate the transmitted data.

Complex exponentials are often used to represent the modulated sinusoids. The relationship between sinusoids and complex exponentials is expressed in Euler's formula, see Equation 2.2, and for a negative angle, see Equation 2.3. The value of a sinusoid at a constant phase, such as  $cos(\theta)$ , can thus be represented as the Real part of  $e^{i\theta}$ . A time-varying sinusoid, such as  $cos(\theta t)$ , has a phase component,  $\theta$ , which changes with time, t, where  $\theta/2\pi$  represents the frequency of the time-varying sinusoid. A change in amplitude, A, or constant offset in phase,  $\phi$ , would appear as  $Acos(\theta t + \phi)$ . Euler's formula can be restated to explicitly take into account the sinusoid aspects changed by modulation (phase, frequency, and amplitude), as seen in Equation 2.4.

$$e^{i(\theta)} = \cos(\theta) + i * \sin(\theta) \tag{2.2}$$

$$e^{-i(\theta)} = \cos(\theta) - i * \sin(\theta) \tag{2.3}$$

$$Ae^{i(\theta t + \phi)} = A[\cos(\theta t + \phi) + i * \sin(\theta t + \phi)]$$

(2.4)

Euler's formula states that, a single complex exponential can be represented as the sum of two sinusoids: a real, or cosine, sinusoid and an imaginary, or sine, sinusoid. Since both the real and imaginary sinusoids are at the same frequency,  $\theta$ , the sum of real and imaginary sinusoids combine to form a single sinusoid with a particular phase offset,  $\phi$ . The phase offset desired determines if the complex sum contains only a real cosine part, or only an imaginary sine part, or some combination of the two. Regardless of the relative size of the real and imaginary parts of the complex sum, the norm of the complex sum equals the complex exponential's amplitude, A, as required by Euler's formula. Where, in this case, the norm used is the complex norm.

$$\|x + iy\| = \sqrt{x^2 + y^2} \tag{2.5}$$

The complex norm in Equation 2.5, above, is an application of the Pythagorean theorem, Equation 2.6, to signal space where x, the Real value, and y, the Imaginary value, correspond to  $cos(\theta)$  and  $sin(\theta)$  respectively.

$$\cos^2(\theta) + \sin^2(\theta) = 1 \tag{2.6}$$

Euler's formula provides a way of representing the modulation output as a complex exponential. Since each of these outputs contains a real and imaginary part, it is common to plot the modulator output graphically as a complex vector in what is called signal space. Signal space is simply a graphical representation of the complex plane with the x-axis representing the real part of a complex vector, and the y-axis representing the imaginary part. Since the real part of a complex exponential corresponds to the cosine term in Euler's formula, it is referred to as In-phase, and the real axis, the x-axis, is labeled I in signal space. The imaginary part of the complex exponential corresponds to the sine term, which is  $\pi/4$  shifted in phase from the real term. Thus, the imaginary term is called in Quadrature (for the quarter shift), and the imaginary axis, the y-axis, is labeled Q in signal space.

Signal space is a convenient way of representing constant frequency complex exponentials and modulation schemes. In signal space, the phase and amplitude of an exponential easily translate into the angle and magnitude of a complex vector respectively. A variable frequency modulation scheme would correspond to a rotating complex vector in signal space with the angle of the vector changing in time at a rate relative to the frequency value. As this situation is not conducive to either easy representation or interpretation, signal space modulation diagrams are usually restricted to modulation types that modify phase and/or amplitude only. The modulation schemes used by the systems in this dissertation are of the constant frequency type and can therefore be readily represented in signal space.

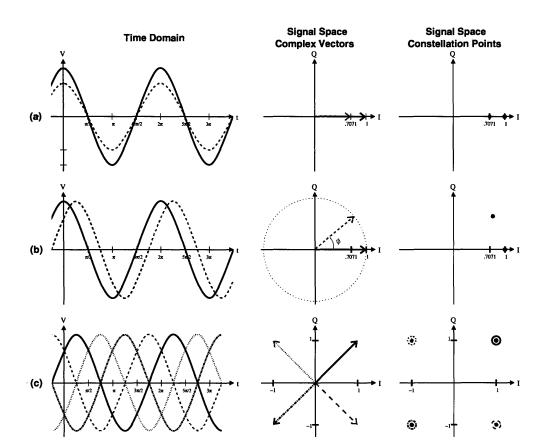

The modulation diagrams in Figure 2-3 represent three possible types of modulation using phase and/or amplitude. Equation 2.7 is the canonical equation used to represent these modulation schemes. It shows a complex exponential and its corresponding real and imaginary parts. The grouping of terms highlights the phase,  $\phi$ , and amplitude, A, values which are varied by the modulation schemes, while pulling out the frequency term,  $\theta$ , which is held constant. The specific modulation types demonstrated in Figure 2-3 are discussed below.

$$(Ae^{i\phi})e^{i(\theta t)} = A[\cos(\phi) + i * \sin(\phi)]e^{i(\theta t)}$$

$$(2.7)$$

Figure 2-3: Examples of different types of modulation. Each example is shown in three forms: time domain signal, complex vectors, and constellation points. There are three modulation types shown here: (a) Amplitude Modulation (AM); (b) Phase Modulation (PM); (c) Quadrature Amplitude Modulation (QAM)

Figure 2-3 Part (a) shows an amplitude modulation, or AM, modulation scheme. The

two modulation sinusoids can each be represented by an expression of the form of Equation 2.7, and are characterized by a different amplitude values, A. In signal space, the length of the complex vector corresponds to the norm of this expression. In this case, the vector length is shorter for the sinusoid with the smaller value of A and longer for the larger value of A. The signal space vectors lie solely on the I or real axis as both sinusoids here are pure cosines. This corresponds to the phase of the sinusoids,  $\phi$ , being zero and the complex exponential containing no imaginary part. The constellation points in Figure 2-3 are simply signal space points which correspond to the terminal locations of the complex vectors. The (x, y), or in this case (I, Q), coordinates of the constellation points correspond to the real and imaginary parts of the complex exponential and provide a more convenient notational format.

Part (b) of Figure 2-3 displays a phase modulation, or PM, modulation scheme. The phase,  $\phi$ , is modified according to the incoming data and the time domain sinusoid shifts accordingly. In signal space, the complex vector rotates in response to the change in phase dictated by the data value. The relative magnitude of the real and imaginary parts change to reflect the shift in phase and that sinusoid's constellation point is at the corresponding location. Since the amplitude remains constant, however, the length of the vector, and the distance of the constellation point from the origin does not change. This is equivalent to the norm staying constant.

Part (c) of Figure 2-3 shows a modulation scheme in which four different sinusoids are possible. These four sinusoids can be thought of (and implemented) as either a phase modulation with four different phases (a rotation of the complex vector to four different points):  $\pi/4$ ,  $3\pi/4$ ,  $-3\pi/4$ ,  $-\pi/4$ , or as a combination of phase and amplitude modulation:  $\pm \pi/4$ , and  $\pm A$ .

If implemented as a four level phase modulation such a scheme is called Quadrature Phase Shift Keying or QPSK. The term quadrature is used because the final modulated sinusoid is generated by combining two sinusoids in quadrature (sine and cosine), and Phase Shift Keying because there are four keys, or constellation points, which are reached by shifting the phase of the complex exponential. Larger PSK modulations are generated by adding more constellation points. These points are evenly spaced around the circle described by rotating the phase of the constant amplitude complex exponential through a full  $2\pi$  radians.

As a combination of phase and amplitude modulation, the modulation scheme in Part (c) of Figure 2-3 would be called 4-Quadrature Amplitude Modulation, or 4-QAM. The Quadrature term again denotes that a combination of both a cosine and sine is used to generate the modulated sinusoid. This implies that a phase shift is present (for pure amplitude modulation only a single sinusoid would be needed). The Amplitude Modulation term is used because a change in amplitude value is also used to convey information. The value 4 is used because there are four constellation points. These constellation points are typically arranged in an evenly spaced symmetric square pattern for N-QAM as it is easily generated and energy efficient. It is easily generated because symmetric variations of phase and amplitude are used. It is energy efficient because the constellation points are relatively far apart, which helps reduce errors, while keeping the average of the constellation points relatively close to the origin, which corresponds to lower transmission power. In a digital communication system, the constellation points represent sets of bits and N is commonly a power of 2 so that there is a point representing every potential set of bit values in the fully populated square constellation. Therefore, 16-QAM, 64-QAM, and 256-QAM are the likely larger constellation sizes.

# Chapter 3

# **Digital Radios**