## Asbestos: Operating System Security for Mobile Devices

by

### Martijn Stevenson

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Engineering in Computer Science and Engineering

at the

# MASSACHUSETTS INSTITUTE OF TECHNOLOGY [50-27006] May 2006

© Massachusetts Institute of Technology 2006. All rights reserved.

| Department of Electrical Engineering and Computer Science |

|-----------------------------------------------------------|

| May 26, 2006                                              |

|                                                           |

| Certified by                                              |

| Robert T. Morris                                          |

| Associate Professor                                       |

| Thesis Supervisor                                         |

| 12/                                                       |

| Accepted by                                               |

| Arthur C. Smith                                           |

| Chairman Department Committee on Graduate Students        |

**ARCHIVES**

### Asbestos: Operating System Security for Mobile Devices

by

#### Martijn Stevenson

Submitted to the Department of Electrical Engineering and Computer Science on May 26, 2006, in partial fulfillment of the requirements for the degree of Master of Engineering in Computer Science and Engineering

#### Abstract

This thesis presents the design and implementation of a port of the Asbestos operating system to the ARM processor. The port to the ARM allows Asbestos to run on mobile devices such as cell phones and personal digital assistants. These mobile, wireless-enabled devices are at risk for data attacks because they store private data but often roam in public networks. The Asbestos operating system is designed to prevent disclosure of such data. The port includes a file system and a network driver, which together enable future development of Asbestos applications on the ARM platform. This thesis evaluates the port with a performance comparison between Asbestos running on an HP iPAQ hand held computer and the original x86 Asbestos.

Thesis Supervisor: Robert T. Morris

Title: Associate Professor

### Acknowledgments

I would like to thank my thesis advisor, Robert T. Morris, for his support and guidance on this thesis. Robert always welcomed and answered technical inquiries and he provided a strong vision for what this thesis should accomplish. Without his insights the ARM Asbestos port would not have reached completion.

The people of the Parallel and Distributed Operating Systems group at MIT helped make my working environment a pleasant one. While Professor Frans Kaashoek appreciated my accomplishments, Micah Brodsky and Max Krohn shared my frustrations and often provided a helpful set of eyes or ears when problems arose. In addition, I thank Asbestos team members Eddie Kohler, Steve VanDeBogart and Petros Efstathopoulos for giving me code, critique, benchmarks and advice. Helpful also were the words of iPAQ wizard Jamey Hicks, and the work of other developers at www.handhelds.org.

Finally I want to thank my parents for the support they have given me these past five years at MIT. I have always been able to count on them for words of wisdom and encouragement.

This research was supported by a grant from Taiwan's Industrial Technology Research Institute. Portions of this thesis are adapted from and/or contain text written in master's theses by Cliff Frey and David Ziegler.

### Contents

| 1 | Intr | oduction                          | 15 |

|---|------|-----------------------------------|----|

|   | 1.1  | Motivation: Asbestos              | 15 |

|   | 1.2  | Motivation: Mobile Security       | 16 |

|   | 1.3  | Motivation: ARM                   | 17 |

|   | 1.4  | Challenges                        | 17 |

|   | 1.5  | Approach                          | 18 |

|   | 1.6  | Outline                           | 19 |

| 2 | Rel  | ted Work                          | 21 |

| 3 | Dev  | elopment Environment              | 23 |

|   | 3.1  | Hardware                          | 23 |

|   |      | 3.1.1 The iPAQ h5555              | 23 |

|   |      | 3.1.2 Bootldr: A Flash Bootloader | 24 |

|   | 3.2  | Software                          | 25 |

|   |      | 3.2.1 Simulators                  | 25 |

|   |      | 3.2.2 Compilation                 | 26 |

|   | 3.3  | ARM Platform Peculiarities        | 27 |

|   |      | 3.3.1 Data Alignment              | 27 |

|   |      | 3.3.2 Floating Point              | 29 |

|   |      | 3.3.3 Caches & Write Buffers      | 30 |

| 4 | Por  | ing the Asbestos Kernel           | 33 |

|   | 4.1                             | Bootin                                                                    | ng Asbestos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 35                                                                          |

|---|---------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

|   | 4.2                             | Enteri                                                                    | ng and Leaving the Kernel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 35                                                                          |

|   |                                 | 4.2.1                                                                     | Context Switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 35                                                                          |

|   |                                 | 4.2.2                                                                     | User Page Fault Handler                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39                                                                          |

|   |                                 | 4.2.3                                                                     | Passing Arguments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 41                                                                          |

|   | 4.3                             | Memo                                                                      | ry Management Module                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41                                                                          |

|   |                                 | 4.3.1                                                                     | Page Table Entries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41                                                                          |

|   |                                 | 4.3.2                                                                     | Page Directory Entries                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 43                                                                          |

|   |                                 | 4.3.3                                                                     | Defining the MMU HAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 44                                                                          |

|   | 4.4                             | Hardw                                                                     | vare Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 47                                                                          |

|   |                                 | 4.4.1                                                                     | Serial Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 47                                                                          |

|   |                                 | 4.4.2                                                                     | Timers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 47                                                                          |

|   |                                 | 4.4.3                                                                     | Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 48                                                                          |

|   |                                 | 4.4.4                                                                     | Memory-mapped IO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 48                                                                          |

|   |                                 |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |

| 5 | Sys                             | tem Se                                                                    | ervices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51                                                                          |

| 5 | <b>Sys</b> : 5.1                |                                                                           | ervices<br>ystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <b>51</b> 51                                                                |

| 5 |                                 |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |

| 5 |                                 | File S                                                                    | ystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51                                                                          |

| 5 |                                 | File S; 5.1.1 5.1.2                                                       | ystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51<br>51                                                                    |

| 5 | 5.1                             | File S; 5.1.1 5.1.2                                                       | ystem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 51<br>51<br>52                                                              |

| 5 | 5.1                             | File S; 5.1.1 5.1.2 Netwo                                                 | Separating Pages and Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 51<br>51<br>52<br>54                                                        |

| 5 | 5.1                             | File S: 5.1.1 5.1.2 Network 5.2.1                                         | Compact Flash Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51<br>51<br>52<br>54<br>55                                                  |

|   | 5.1                             | File S; 5.1.1 5.1.2 Netwo 5.2.1 5.2.2                                     | Compact Flash Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51<br>52<br>54<br>55<br>55                                                  |

|   | 5.1<br>5.2<br>Eva               | File S; 5.1.1 5.1.2 Netwo 5.2.1 5.2.2 luation Measu                       | Compact Flash Driver  Separating Pages and Blocks  ork  PCMCIA  The Orinoco Wireless Driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <ul><li>51</li><li>51</li><li>52</li><li>54</li><li>55</li><li>57</li></ul> |

|   | 5.1<br>5.2<br><b>Eva</b><br>6.1 | File S; 5.1.1 5.1.2 Netwo 5.2.1 5.2.2 luation Measu                       | Compact Flash Driver  Separating Pages and Blocks  ork  PCMCIA  The Orinoco Wireless Driver  number of the Description of the D | 51<br>51<br>52<br>54<br>55<br>55<br>57                                      |

|   | 5.1<br>5.2<br><b>Eva</b><br>6.1 | File System 5.1.1 5.1.2 Network 5.2.1 5.2.2 luation Measure Result        | Compact Flash Driver  Separating Pages and Blocks  ork  PCMCIA  The Orinoco Wireless Driver  number of the Description of the D | 51<br>51<br>52<br>54<br>55<br>55<br>57<br>57<br>58                          |

|   | 5.1<br>5.2<br><b>Eva</b><br>6.1 | File System 5.1.1 5.1.2 Network 5.2.1 5.2.2 Iluation Measure Result 6.2.1 | Compact Flash Driver  Separating Pages and Blocks  ork  PCMCIA  The Orinoco Wireless Driver  nuring Performance  Caching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 511<br>512<br>544<br>555<br>557<br>577<br>588<br>599                        |

| 7 | Con | clusion                                  | 67 |

|---|-----|------------------------------------------|----|

| A | Cod | e Split                                  | 69 |

| В | AR  | M Asbestos HOWTO                         | 71 |

|   | B.1 | Running Asbestos on the Skyeye Simulator | 71 |

|   | B.2 | Running Asbestos on the iPAQ             | 72 |

|   | B.3 | Hardware Notes and Resources             | 73 |

## List of Figures

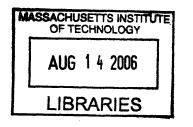

| 3-1 | Data bytes accessed by a non-aligned address   | 27 |

|-----|------------------------------------------------|----|

| 3-2 | The structure packing problem on ARM           | 28 |

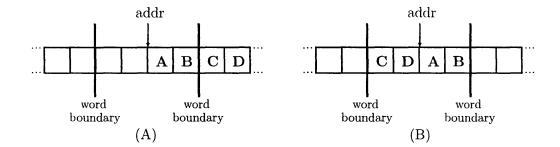

| 4-1 | The Asbestos HAL                               | 34 |

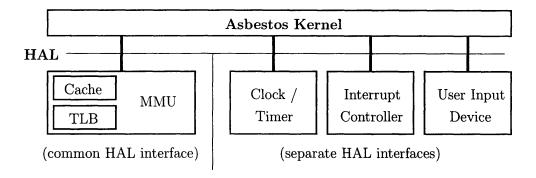

| 4-2 | An ARM context switch from kernel to user mode | 39 |

| 4-3 | An ARM context switch from user to user mode   | 40 |

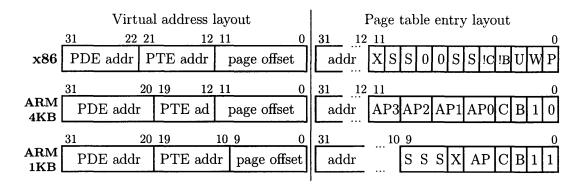

| 4-4 | Virtual addresses and page table entries       | 42 |

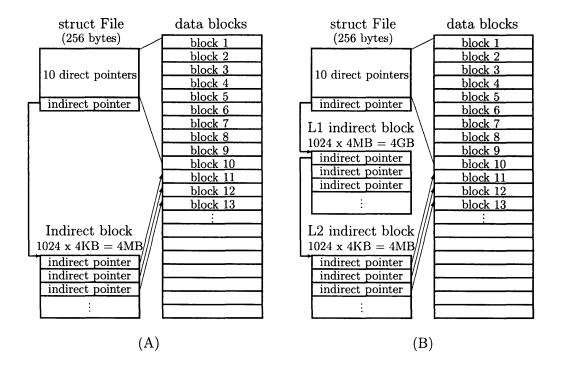

| 5-1 | Old and new Asbestos file structures           | 53 |

| 6-1 | Assembly code to test memory write performance | 64 |

### List of Tables

| 3.1 | Relative speeds of floating point operations                 | 29 |

|-----|--------------------------------------------------------------|----|

| 4.1 | ARM mapping between exceptions and resulting execution modes | 37 |

| 4.2 | Asbestos page table permission mappings                      | 45 |

| 4.3 | ARMv4 and ARMv5 access permission bits                       | 46 |

| 6.1 | Kernel label operation benchmarks in thousands of cycles     | 59 |

| 6.2 | Operating system benchmarks in thousands of cycles           | 60 |

| 6.3 | ARM efficiency for each OS benchmark                         | 63 |

| 6.4 | Random-access memory benchmarks                              | 64 |

| 6.5 | Possible caching scenarios and resulting CPI                 | 65 |

| A.1 | Separate kernel code                                         | 69 |

| A.2 | Mostly shared kernel code                                    | 70 |

| A.3 | Shared kernel code                                           | 70 |

### Chapter 1

### Introduction

This thesis presents the port of the Asbestos operating system to the ARM processor architecture. ARM Asbestos brings the operating system security guarantees of Asbestos to a mobile computer, supplemented by a file system and a network driver.

### 1.1 Motivation: Asbestos

On most networked computers, only a suite of user-level software protects private data from remote access. Experience has shown that it is too difficult to ensure that all software handling private data is free of exploitable flaws. We routinely learn about exploits made possible by buffer overflows [11, 10, 9, 12, 14], vulnerabilities in the Java virtual machine [13], and improper allocation and deallocation of memory [15]. Typically, these vulnerabilities result in the complete compromise of the system.

Instead of relying on applications to protect sensitive data, one can contain soft-ware flaws at the operating system level, using the *principle of least privilege* [36]: each part of a system should have no more than the capabilities required for it to perform its tasks. For example, an email reader should be able to confine an executable attachment by only giving it access to a display window and restricting its access to the network and file system. A Web application should be able to ensure that one user's private data cannot be sent to another user's browser by faulty Web server application code.

The Asbestos operating system employs the principle of least privilege to limit the impact of exploited software vulnerabilities [28, 19]. It allows programmers to dynamically define data compartments, and only grant access to that data to those system services that require it. An example is the OK Web Server (OKWS) for Asbestos [29]. Using the security primitive of Asbestos labels, OKWS creates a compartment for each user's data. It restricts the compartment such that it can only communicate with a specialized worker process, the trusted local database, and a single connection to the network. The rest of the network connections and the other processes cannot communicate with the worker, thus preventing the unintended disclosure of information.

### 1.2 Motivation: Mobile Security

The development of Asbestos OKWS for desktop servers was a direct response to the security breaches experienced in recent years by web-based organizations. However, desktop servers are not the only types of computers coping with threats coming from the network. The mobile device space is a prime candidate for security research, because hand held devices are facing increasing threats as their popularity grows. The security threats to mobile devices are similar to the threats facing servers in that these devices can remain on without user attention, and are always connected to a network. There are already billions of cell phone, PDA and smart phone users [34], whose devices often store private data such as phone numbers and addresses. The demand for global connectivity is quickly driving phone service providers to consolidate networks and standardize communication protocols [20], making it easier to create attacks that affect large numbers of users. Network bandwidth and storage are expanding to meet increased demand for data downloads and mobile data, increasing the risk of data leaks and the spread of malicious code. The first mobile worms have already appeared [37], and we should expect the security risks to increase as mobile networks grow and users trust their mobile device software to handle more personal data.

### 1.3 Motivation: ARM

The Asbestos port to ARM is beneficial because the ARM processor dominates mobile computing. The x86 processor is one of the most common CPUs in desktop computers. Mobile devices, on the other hand, have stringent power requirements: lower power consumption means longer battery life. The dominant chips in the mobile market are ARM processors. ARM manufactures 90 percent of processor cores for cell phones. A host of other mobile devices also run on ARM processors, including many PDAs and Apple Computer's iPod. In 2004, 1.3 billion chips shipped contained ARM cores [35]. Porting Asbestos to ARM will bring operating system security guarantees to a large number of mobile devices.

### 1.4 Challenges

Several challenges arose in porting Asbestos to the ARM. Not the least of these challenges was that, until now, Asbestos has been a pure x86 operating system. This is the first attempt to port Asbestos to any other architecture. This project had to define a Hardware Abstraction Layer (HAL), a common interface between the kernel and the hardware. This proved difficult because the ARM and x86 processors have different memory management hardware. In particular, x86 Asbestos makes use of unused bits in the hardware page table entries to store extra state. The ARM port had to mimic this behavior, sometimes without extra bit space. This first port of Asbestos also uncovered a number of previously untickled kernel bugs, as also happened frequently during the development of the OK Web Server.

Another challenge in porting Asbestos was choosing a suitable ARM platform for deployment. The ARM architecture has existed for fifteen years and has evolved considerably in that time. There are many generations of ARM processors, and while most support a consistent instruction set, there are small variations between the generations. ARM processors are used in many different configurations of commercial devices, which made it difficult to find ARM simulators that work for a specific

hardware model (the HP iPAQ, in this case). In addition, the wide range of ARM devices means open-source drivers are not available for all ARM hardware layouts. Fortunately this project was able to build on code from other ARM ports, such as ARM Linux for the iPAQ, maintained at www.handhelds.org.

Finally, there were challenges in designing the system services for ARM Asbestos, namely the file system and the network driver. The Asbestos file system (ASFS) uses little-endian ELF program images. One challenge was maintaining binary compatibility for the file system across architectures, so that program image files may be shared between the ARM and x86 builds. Another challenge was the medium on which the file system is stored. x86 Asbestos can interface with IDE disk drives for persistent storage, or can maintain file system state in RAM. To achieve persistent storage on disk-less ARM architectures, Asbestos requires a Compact Flash driver.

Implementing a new network driver presented yet other challenges. x86 Asbestos supports two wired ethernet network cards: the e1000 and the ne2k. A network interface in a mobile device is guaranteed to be a wireless network card, probably supporting 802.11 Wi-Fi. Adapting to this kind of interface requires a wholly different network driver than the drivers currently in place. Furthermore, the ARM network driver should interface with the LWIP network stack [17], just as x86 Asbestos does. This way, both builds can use netd, the user process that implements the network service.

### 1.5 Approach

The work in this thesis took place in several steps. First, to gain familiarity with the ARM instruction set and hardware, I ported the JOS kernel to ARM. The Asbestos operating system is based on the much simpler JOS operating system used for systems education at MIT, UCLA and NYU [1]. The JOS port involved setting up a simple boot process and interfacing with the serial port to establish a minimal debugging environment. Next I set up a crude memory management system and simple context switching, proving that the basic needs of Asbestos can be met by the ARM processor.

The second step was to merge this early development with the Asbestos mainline. In deciding what system modules the x86 and ARM builds would share, I defined the Asbestos Hardware Abstraction Layer (HAL), a hardware interface that determines what is required of future ports of Asbestos. The merging step ensured that the various versions of Asbestos remain synchronized as the Asbestos security mechanisms and system services develop.

Next I designed the essential services for ARM Asbestos: the file system and network driver. The file system is based largely on x86 ASFS, although file blocks had to be decoupled from x86 pages. In this thesis I discuss the design of a Compact Flash driver and wireless network driver, though their implementation is not finished at the time of writing. The goal of the Compact Flash driver is to utilize permanent storage on mobile devices. The network driver will be based on open-source ARM Linux for iPAQs, and should implement the 802.11 wireless protocol.

Finally I evaluated the port, assessing whether ARM Asbestos' performance is comparable to x86 Asbestos on commodity mobile hardware. I ensure that ARM Asbestos does indeed meet the basic usability requirements of a mobile operating system.

### 1.6 Outline

The remainder of this thesis is organized as follows. Chapter 2 discusses related work in operating systems and mobile computing. Chapter 3 summarizes the development environment for the ARM Asbestos port. A lot of time on this project was spent gaining understanding of the ARM architecture, and its software and hardware peculiarities. Chapter 4 discusses the design and implementation of the ARM Asbestos kernel. It explores how this port forked from x86 Asbestos and examines the choices made in defining the Asbestos HAL. Chapter 5 considers the design of the file system and network interface. Chapter 6 evaluates the performance of the ARM port by comparing it to x86 Asbestos. Finally, Chapter 7 concludes with a review of the contributions of this thesis, and the work that lies ahead for Asbestos on mobile

devices.

### Chapter 2

### Related Work

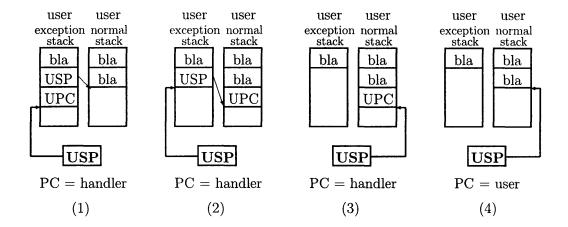

The Asbestos operating system was designed for the x86 architecture, without specific regard for future expansion. This thesis aims to run Asbestos on the ARM architecture. Other operating systems have demonstrated the utility of supporting multiple platforms. NetBSD is a Unix-like operating system that also started on the x86, and since 1993 has been ported to seventeen different processors and more than forty platforms [33]. Some operating systems were designed from the start with portability in mind. eCos, a flexible real-time operating system, now supports ten different processor architectures [18]. eCos distances the core OS software from platforms' hardware differences with a Hardware Abstraction Layer (HAL): a programming interface between hardware and software. Porting eCos involves implementing the HAL on a new system, after which the port is guaranteed to work. The Asbestos port achieves platform separation with two sets of architecture-specific code files. In essence the decisions about how to separate source files define a HAL: each new Asbestos port will only have to implement the functions that the ARM port implements.