### **Degradation Mechanisms of GaN High Electron Mobility Transistors**

by

Jungwoo Joh

### B.S. Electrical Engineering, Seoul National University, 2002

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Electrical Engineering

at the Massachusetts Institute of Technology  $\left( \begin{array}{c} February 2007 \\ January 19, 2007 \end{array} \right)$

© 2007 Massachusetts Institute of Technology All Rights Reserved.

The author hereby grants to MIT permission to reproduce and distribute publicly paper and electronic copies of this thesis and to grant others the right to so

| Author                                   |                           |                                               |

|------------------------------------------|---------------------------|-----------------------------------------------|

|                                          | Department of Electrical  | January 19, 2007                              |

| Certified by                             |                           |                                               |

|                                          |                           | Jesús A del Alamo<br>ngineering<br>Supervisor |

| Accepted by                              |                           | · · · · · · · ·                               |

| MASSACHUSETTS INSTITUTE<br>OF TECHNOLOGY | Chairman, Department Comn | · C. Smith<br>nittee on Graduate Students     |

| APR 3 () 2007                            | BARKER                    |                                               |

| LIBRARIES                                |                           |                                               |

### **Degradation Mechanisms of GaN High Electron Mobility Transistors**

by

Jungwoo Joh

Submitted to the Department of Electrical Engineering and Computer Science

January 19, 2007

in Partial Fulfillment of the Requirements for the Degree of

Master of Science in Electrical Engineering

### ABSTRACT

In spite of their extraordinary performance, GaN high electron mobility transistors (HEMT) have still limited reliability. In RF power applications, GaN HEMTs operate at high voltage where good reliability is essential. However, physical understanding of the fundamental reliability mechanisms of GaN HEMTs is still lacking today. In this thesis, we carry out systematic reliability experiments on industrial GaN HEMTs provided by our collaborators, TriQuint Semiconductor and BAE systems. In our study, GaN HEMTs have been electrically stressed at various bias conditions while they are being characterized by a benign characterization suite. We have confirmed that electrical stress on devices results in an increase in drain resistance R<sub>D</sub> and a decrease in maximum drain current I<sub>Dmax</sub>. During the stress, traps are found to be generated. We have seen that this degradation is driven mostly by electric field, and current is less relevant to electrical degradation. From a set of our experiments, we have hypothesized that the main mechanism behind device degradation is defect formation through the inverse piezoelectric effect and subsequent electron trapping. Unlike current conventional wisdom, hot electrons are less likely to be the direct cause of electrical degradation in the devices that we have studied. Our studies suggest a number of possibilities to improve the electrical reliability of GaN HEMTs.

Thesis supervisor: Jesús A. del Alamo Title: Professor of Electrical Engineering

# Acknowledgements

First of all, I would like to thank my research advisor Professor Jesús A. del Alamo for giving me this great opportunity to work on a fascinating project with the best people. His wonderful guidance throughout my days at MIT has made me better and better. He has always encouraged me with cheers no matter what I did and no matter how good my result was. I really appreciate his patience and teaching, which has always led me to advance further.

Had it not been for our collaborators at TriQuint Semiconductor and BAE Systems, I could not have done my research at all. They provided us stellar samples to study, and their feedback was amazingly conducive to my research. In particular, I want to thank Dr. Jose Jimenez from TriQuint for giving me such an interesting internship opportunity at TriQuint. I still miss the wonderful summer with the terrific people in Dallas. I also thank Dr. P.C. Chao from BAE for fruitful discussions. I should also thank the Korea Foundation for Advanced Studies for giving me the very first motivation and support for graduate study.

I would also like to express gratitude toward all in the del Alamo group. Lab work with Jörg Scholvin was always fun, and discussions with him were always productive. Special thanks to Anita Villanueva for her advice that I really needed to get on track. Dr. Dae-Hyun Kim was to me a second advisor in the group. As the only Korean in the group, he was also like my brother. I also want to thank Joyce Wu and Niamh Waldron who first introduced the original thanksgiving turkey to me. They really made my life richer. I cannot forget to thank our new members Ling Xia and Usha Gogineni, who I will share the rest of my days here with. I am always learning a lot from them.

I truly appreciate friendship and love of my oldest friends in Boston: Wooji, Zerb, Soonbam, Bohee, Monki, Bang (younger to older), and many others, who I have been sharing my life with. They always give me motivation, spirit, inspiration, and energy to go forward. Very special thanks to my friends in Korea: Bbiki, Kichi, Jaepa, KBC, No, Ging, and Goony; they are my heartening supporters. I am such a lucky man to have these fantastic and brilliant friends.

Finally, I would like to thank my loving parents, who are always giving me the kindest cares and the most encouraging support in the world. You always boost up everything I do. I also want to thank my younger brother Hoya, who has been to me sometimes a friend, sometimes a twin brother, and sometimes a teacher. I always get inspired by him. Had it not been for my family, I could not have done anything. I love you so much and hope you are always happy.

This work was made possible by Army Research Laboratory under contract # W911QX-05-C-0087 and the Korea Foundation for Advanced Studies Fellowship.

# Contents

| List of Figures9                                          |

|-----------------------------------------------------------|

| List of Tables                                            |

|                                                           |

| Chapter 1. Introduction15                                 |

| 1.1. Introduction of GaN HEMT15                           |

| 1.2. Motivation                                           |

| 1.3. Previous Studies17                                   |

| 1.4. Project Goals and Thesis Outline19                   |

| Chapter 2. Experimental                                   |

| 2.1. Introduction                                         |

| 2.2. Devices                                              |

| 2.3. MIT Reliability Test Chip22                          |

| 2.4. Electrical Experiments24                             |

| 2.4.1. Experimental Setup25                               |

| 2.4.2. Characterization Suite27                           |

| 2.5. Stress Test Methodology                              |

| 2.6. Summary                                              |

| Chapter 3. Degradation Experiments                        |

| 3.1. Overall Degradation Phenomena                        |

| 3.2. OFF-state Step-stress                                |

| 3.3. V <sub>DS</sub> =0 Condition                         |

| 3.4. Other Observations                                   |

| 3.4.1. Effect of Environment                              |

| 3.4.2. Degradation of MISFET42                            |

| 3.4.3. Critical Voltage in other Stress Bias Conditions44 |

| 3.4.4. The Origin of Gate Leakage Degradation           | 47 |

|---------------------------------------------------------|----|

| 3.4.5. Effect of L <sub>GD</sub>                        | 48 |

| 3.5. Trapping Behavior                                  | 51 |

| 3.5.1. Off-state Stress-recovery                        | 51 |

| 3.5.2. Enhanced Detrapping                              | 53 |

| 3.6. Trap Generation                                    | 56 |

| 3.7. TLM Step-stress                                    | 58 |

| 3.8. Summary of Key Findings                            | 60 |

| Chapter 4. Degradation Mechanism                        | 63 |

| 4.1. Introduction                                       | 63 |

| 4.2. Inconsistency with Hot-electron Related Mechanisms |    |

| 4.3. Piezoelectric Effect of GaN                        | 64 |

| 4.4. Hypothesis for Electrical Degradation of GaN HEMTs | 65 |

| 4.5. Order-of-magnitude Calculation                     | 67 |

| 4.6. Experimental Confirmation                          | 69 |

| 4.6.1. $L_G$ Dependency in $V_{DS}=0$ State             |    |

| 4.6.2. AlGaN Buffer                                     | 72 |

| 4.6.3. XTEM                                             | 73 |

| 4.7. Suggestions for Reliability Improvements           | 75 |

| 4.8. Conclusions                                        | 76 |

| Chapter 5. Conclusions                                  | 77 |

| 5.1. Summary of Key Findings                            | 77 |

| 5.2. Suggestions for Further Work                       | 80 |

| Bibliography                                            |    |

# List of Figures

| Figure 1-1. Change of $I_D$ and $P_{out}$ in a power soak stress test (data from TriQuint). Stress                         |

|----------------------------------------------------------------------------------------------------------------------------|

| condition: 10 GHz, V <sub>D</sub> =28 V, I <sub>DQ</sub> =150 mA/mm, P <sub>in</sub> =23 dBm, P <sub>out</sub> =33.7 dBm16 |

| Figure 1-2. Increased current collapse after a stress test (dashed: before stress; solid: after                            |

| stress) [13]18                                                                                                             |

| Figure 1-3. Degradation mechanism in AlGaN/GaN HEMT under high stress condition                                            |

| [17]                                                                                                                       |

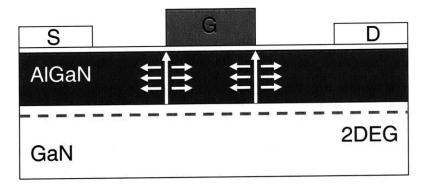

| Figure 2-1. Schematic cross section of GaN HEMT21                                                                          |

| Figure 2-2. MIT reliability test chip                                                                                      |

| Figure 2-3. A schematic of the whole experimental setup25                                                                  |

| Figure 2-4. Graphical user interface of a stress experiment program. A window to select the                                |

| type of stress experiment and to input stress bias conditions is shown                                                     |

| Figure 2-5. Change in normalized drain and source resistance after 300 device                                              |

| characterizations. In phase I, basic figures of merit are extracted. In phase II, full output                              |

| characteristics are also measured. In phase III, full transfer and sub-threshold characteristics                           |

| are measured on top of the basic characterization and output characteristics measurement.                                  |

|                                                                                                                            |

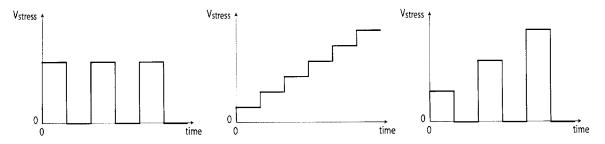

| Figure 2-6. Conceptual stress schemes: (from left to right) stress-recovery, step-stress, and                              |

| step-stress-recovery                                                                                                       |

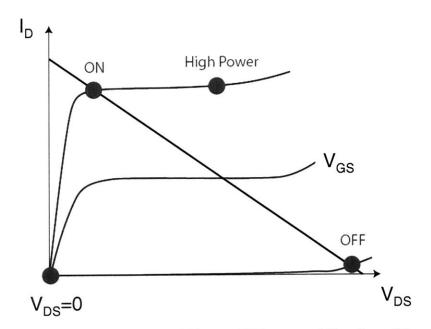

| Figure 2-7. Stress bias points: High Power, ON state, OFF state, and $V_{DS}$ =0 conditions31                              |

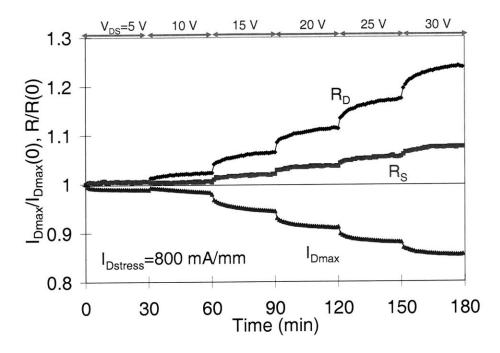

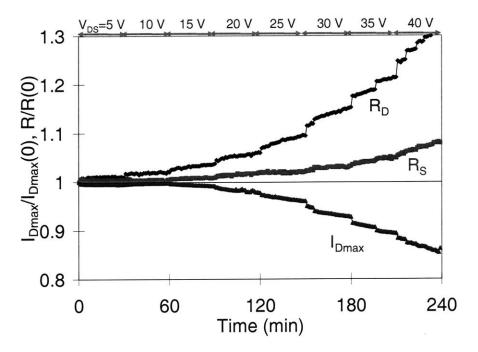

| Figure 3-1. Change in normalized $I_{Dmax}$ , $R_D$ , and $R_S$ in step-stress experiment in the high                      |

| power state ( $V_{DS}$ =5~30 V in 5 V steps, $I_D$ =800 mA/mm, 30 minutes per step)34                                      |

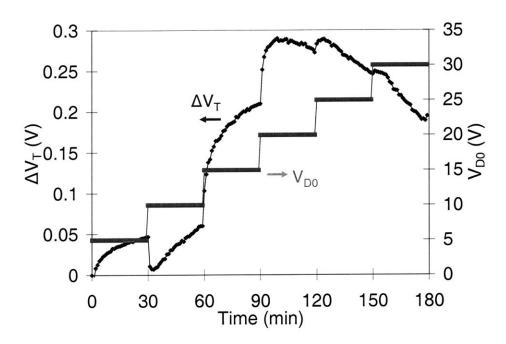

| Figure 3-2. Threshold voltage change in the same experiment as Figure 3-1                                                  |

| Figure 3-3. Output characteristics before (solid) and after (dashed) the same stress test as in                            |

| Figure 3-1. V <sub>GS</sub> =-4~2 V (2 V step)                                                                             |

| Figure 3-4. Change in sub-threshold characteristics before (solid) and after (dashed) the                                  |

| same experiment as Figure 3-1                                                                                              |

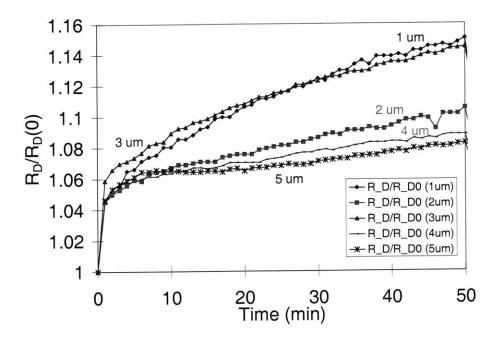

| Figure 3-19. Change in normalized $R_D$ in OFF state stress experiments on different $L_{GD}$                 |

|---------------------------------------------------------------------------------------------------------------|

| devices. Five different devices with different $L_{GD}=1\sim5$ um are stressed at $V_{DS}=30$ V and           |

| V <sub>GS</sub> =-5 V for 50 minutes                                                                          |

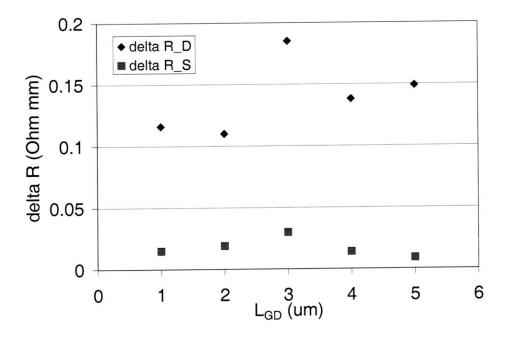

| Figure 3-20. Absolute value of change in $R_D$ and $R_S$ as a function of $L_{GD}$ in the same                |

| experiment as Figure 3-19                                                                                     |

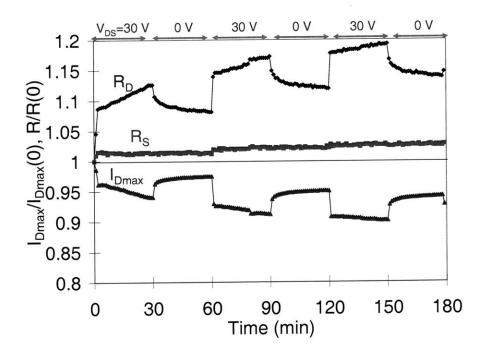

| Figure 3-21. Change in $I_{Dmax}$ , $R_D$ , and $R_S$ in a stress-recovery experiment in the OFF state        |

| $(V_{DS}=30 \text{ V}, I_{D}=20 \text{ mA/mm})$ for 30 minutes of stress followed by 30 minutes at rest. This |

| cycle is repeated for three times                                                                             |

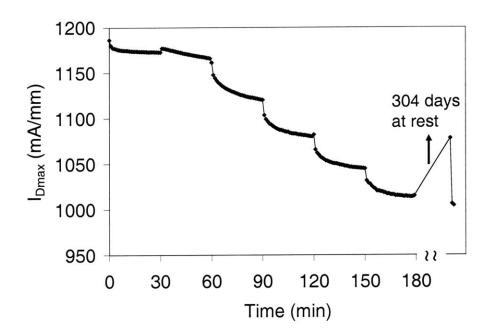

| Figure 3-22. Time evolution of I <sub>Dmax</sub> of the device in Figure 3-1. After the end of the stress     |

| experiment in Figure 3-1, the device was put at rest for 304 days before it were measured                     |

| again. After the first measurement of $I_{Dmax}$ , the same stress ( $V_{DS}$ =30 V, $I_{D}$ =800 mA/mm)      |

| was applied for 2 more minutes53                                                                              |

| Figure 3-23. Change in $I_{Dmax}$ in a stress-recovery experiment on a standard type device                   |

| stressed at $V_{DS}=0$ and $V_{GS}=-30$ V for 15 minutes and at rest for 15 minutes. Additional               |

| stress is applied for another 10 minutes. From t=20 to 25 min, microscope light was                           |

| illuminated54                                                                                                 |

| Figure 3-24. Change in $I_{Dmax}$ in a stress-recovery experiment on a standard type device                   |

| stressed at $V_{DS}=0$ and $V_{GS}=-30V$ for 30 minutes. Four stress cycles are repeated with                 |

| different values of $V_{GS}$ during the 30 minutes recovery phase (0, 1, 2, and 3 V)                          |

| Figure 3-25. Detrapping time constants in $V_{DS}$ =0 stress-recovery experiments55                           |

| Figure 3-26. Change in $I_{Dmax}$ and stress bias of a $V_{DS}$ =0 step-stress-recovery experiment.           |

| $V_{GS}$ =-15~-40 V is applied for stress, and -10 V diagnostic voltage pulses are applied during             |

| the recovery phase. The step size is -2.5 V, and the device is stress for 10 minutes in each                  |

| step. To expedite detrapping, microscope light is turned on during the test                                   |

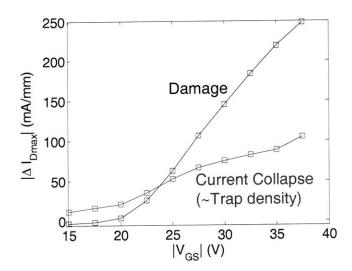

| Figure 3-27. Total damage and current collapse produced by diagnostic pulse as a function                     |

| of the stress bias                                                                                            |

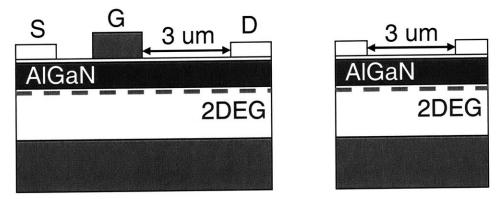

| Figure 3-28. A schematic picture of a HEMT and a TLM used for the comparison. $L_{GD}$ of                     |

| the HEMT is identical to the length of the TLM                                                                |

|                                                                                                               |

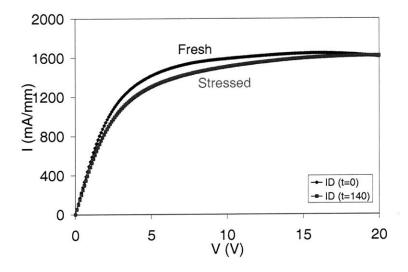

| Figure 3-29. Change in I-V characteristics of the TLM before and after the experiment of                 |

|----------------------------------------------------------------------------------------------------------|

| Figure 3-30. The device was step-stressed at V=20~26 V for 140 minutes                                   |

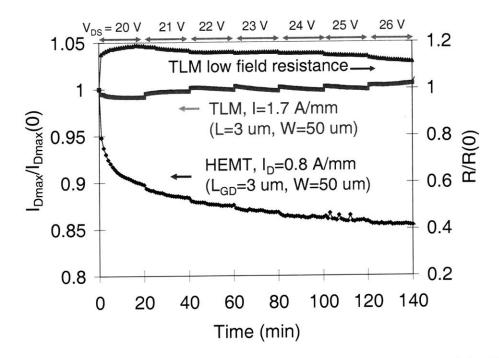

| Figure 3-30. Change in $I_{Dmax}$ of a TLM and a HEMT and low field resistance of the TLM.               |

| The HEMT is stressed at $V_{DS}$ =20~26 V (1 V step, 20 min/step) and $I_D$ =800 mA/mm. The              |

| TLM is stressed at the same voltage, but the current is around 1.7 A/mm. The length of the               |

| TLM (3 um) is the same as the gate-drain gap of the HEMT                                                 |

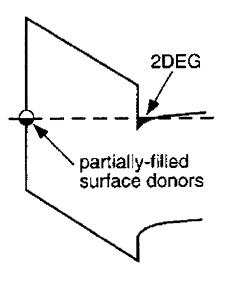

| Figure 4-1. Schematic conduction band diagram of AlGaN/GaN heterostructure [23]65                        |

| Figure 4-2. Vertical electric field under the gate edge and produced tensile strain due to               |

| inverse piezoelectric effect                                                                             |

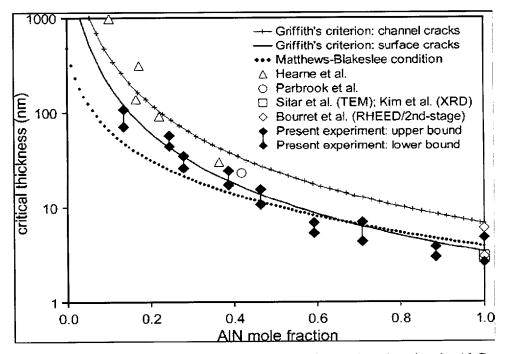

| Figure 4-3. Comparison of measured critical thicknesses for strain relaxation in                         |

| Al <sub>x</sub> Ga <sub>1-x</sub> N/GaN [24]68                                                           |

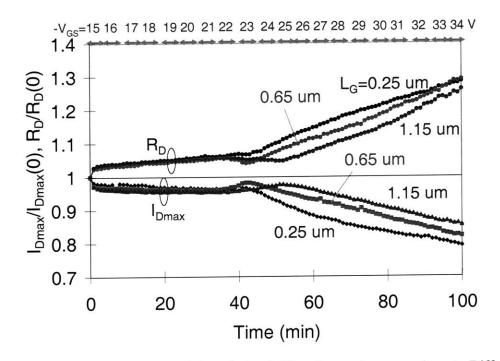

| Figure 4-4. Gate length dependence of degradation in $V_{DS}=0$ step-stress experiments.                 |

| Different gate length devices (L_G=0.25, 0.65, and 1.15 um) are stressed at $V_{DS}$ =0 and $V_{GS}$ =-  |

| 15~-34 V (-1 V step, 5 min/step). The threshold of the degradation increases with $L_G$ 70               |

| Figure 4-5. Overlap of strain field at the center of the gate region in the $V_{DS}=0$ state70           |

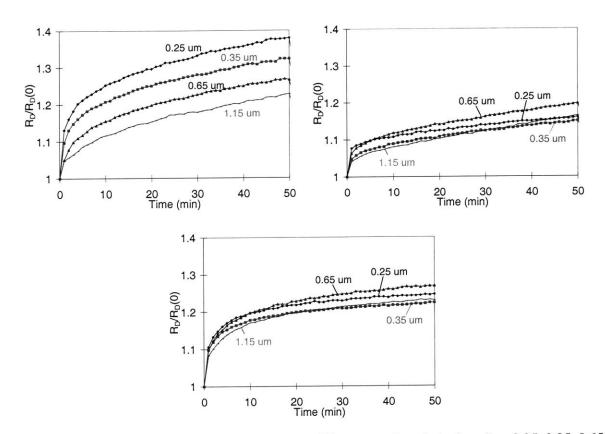

| Figure 4-6. Change in $R_D$ in stress experiments on different gate length devices ( $L_G=0.25$ ,        |

| 0.35, 0.65, and 1.15 um) in $V_{DS}=0$ state (upper left), in OFF state (upper right), and in high       |

| power state (bottom). Stress conditions are $V_{GS}$ =-30 V in the $V_{DS}$ =0 state, $V_{DS}$ =35 V and |

| $V_{GS}$ =-5 V in the OFF state, $V_{DS}$ =25 V and $I_D$ =800 mA/mm in the high power state. These      |

| devices are stressed for 50 minutes71                                                                    |

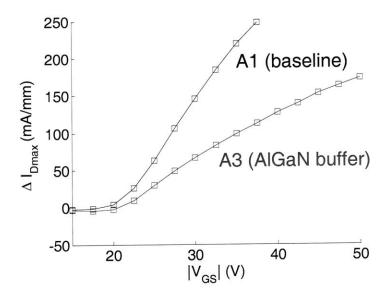

| Figure 4-7. Total damage as a function of stress bias in $V_{DS}=0$ step stress experiment on            |

| type A1 (GaN buffer) and type A3 (AlGaN buffer) devices72                                                |

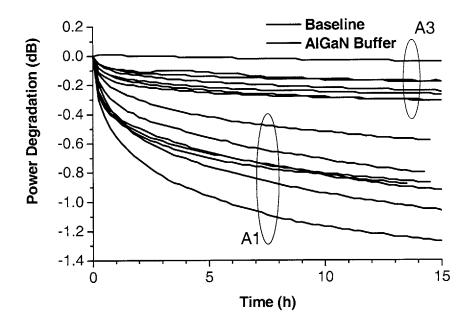

| Figure 4-8. Output power degradation of 400 um type A1 devices (baseline structure, GaN                  |

| buffer) and type A3 devices (AlGaN buffer). The devices are stressed at $P_{out}=5$ W/mm,                |

| V <sub>DS</sub> =28 V, f=10 GHz73                                                                        |

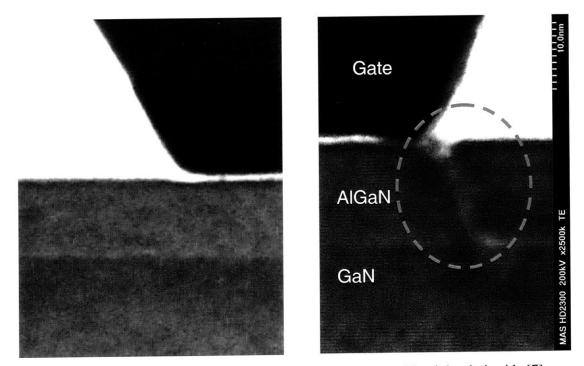

| Figure 4-9. XTEM images of a degraded GaN HEMT. Left: source side; right: drain side                     |

| [7]74                                                                                                    |

|                                                                                                          |

# List of Tables

| Table  | 2-1. D  | efinition of | of de | evice param   | eters mea  | asur | ed by th | ne chai | acteri | izatior | ı sui | te  | 27     |

|--------|---------|--------------|-------|---------------|------------|------|----------|---------|--------|---------|-------|-----|--------|

| Table  | 2-2.    | Changes      | in    | important     | figures    | of   | merit    | after   | 300    | runs    | of    | the | device |

| charac | terizat | tion suite.  | ••••• |               |            |      |          |         |        | •••••   | ••••• |     | 29     |

| Table  | 3-1. S  | tress bias o | cond  | lition for th | ree differ | ent  | step-str | ess ex  | perim  | ents    |       |     | 45     |

# **Chapter 1. Introduction**

### 1.1. Introduction of GaN HEMT

Traditionally, GaN is used for optoelectronic devices. GaN-based light emitting diodes and laser diodes have become very important devices in lightning and blu-ray technology. GaN technology for optoelectronics has already achieved the state of mass production. Recently, GaN high electron mobility transistors (HEMT) have also become of great interest for highvoltage switching and RF power applications. As a result of the large band gap (~3.4 eV) and high breakdown electric field (>3x10<sup>6</sup> V/cm) of GaN, GaN-based devices can operate at a voltage as high as 120 V [1]. Also, due to strong piezoelectric effect and spontaneous polarization of both GaN and AlN, high sheet carrier density (~10<sup>13</sup> cm<sup>-2</sup>) can be achieved at the AlGaN/GaN heterointerface without any doping. In addition, high electron mobility  $(\sim 1500 \text{ cm}^2/\text{V-s})$  and high saturation velocity  $(\sim 2x10^7 \text{ cm/s})$  make GaN-based devices suitable for high power amplification at high frequencies [2]. A large conduction band offset between AlGaN and GaN is also desirable for carrier confinement in the channel. With all these characteristics, AlGaN/GaN HEMTs have already been demonstrated with an output power density of 10.7 W/mm at 10 GHz [3]. Recently, GaN-based HEMTs have also expanded their frequency range - a power density of 2.1 W/mm has been demonstrated at 80.5 GHz [4]. This outstanding performance makes these devices of great interest for high-power, high-frequency applications such as WiMAX or WLAN base stations and radars.

#### 1.2. Motivation

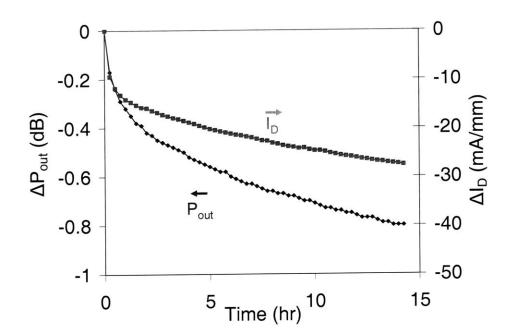

The greatest impediment today preventing the wide deployment of GaN HEMT technology is its limited electrical reliability. As GaN is still a relatively new material system for electronic devices, many problems in material quality and process controls have not been solved yet. As shown in Figure 1-1 for some of the devices studied in this research, output power as well as the drain current decreases, and device characteristics degrade even just after a few hours under typical RF device operation. In particular, because GaN HEMTs are usually operated at high voltage and high current, high reliability is not only demanding but also challenging, and designs that maximize reliability are absolutely needed. In order to tackle this reliability problem, we need to understand physical failure mechanisms. However, at the present time, there is insufficient understanding of the fundamental mechanisms limiting the reliability of GaN HEMTs.

Figure 1-1. Change of  $I_D$  and  $P_{out}$  in a power soak stress test (data from TriQuint). Stress condition: 10 GHz,  $V_D=28 V$ ,  $I_{DQ}=150 \text{ mA/mm}$ ,  $P_{in}=23 \text{ dBm}$ ,  $P_{out}=33.7 \text{ dBm}$ .

### 1.3. Previous Studies

In previous studies, it has been shown that GaN HEMTs degrade significantly after bias stress test. In particular, reduction of drain current and output power was observed [5-9]. This degradation is reported to be accompanied by an increase in drain resistance although source resistance is relatively unaffected by electrical stress [5, 10]. Along with  $I_D$  degradation, transconductance degradation is observed [5, 11, 12], but there have been no agreement on the changes in threshold voltage. Also, after device operation, increased trapping behavior has been observed [11, 13]. On the other hand, no obvious ohmic contact degradation has been found after device degradation [6, 10]. Although there have been some studies on long term reliability [11], most of the reliability studies have focused on device degradation in a relatively short period of time, as GaN HEMTs normally degrade within a few hours of device operation.

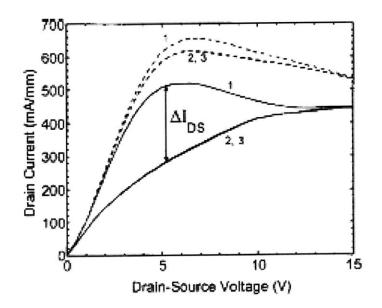

Many of the previous studies on reliability have suggested that hot electrons are at the center of device degradation. The prevailing hypotheses are hot-electron induced trap formation [11] and electron trapping at the surface [5]. Sozza et al. have proposed that an increase of trap density at the surface region between gate and drain is the origin of device degradation [11]. They have also postulated that the same type of trap that causes current collapse is involved in the degradation mechanism. They have attributed this increase in trap density to hot electron effects. Also, as shown in Figure 1-2, it has been observed that current collapse increases after a bias stress test [13]. The current collapse is a temporary decrease of drain current after applying high voltage to the device.

Figure 1-2. Increased current collapse after a stress test (dashed: before stress; solid: after stress) [13].

It has been reported that GaN HEMTs suffer from current collapse. It is widely believed that under high voltage, surface states between the gate and the drain trap hot electrons. These trapped electrons at the surface deplete the channel in the extrinsic drain resulting in a reduction of the drain current [14]. SiN passivation is known to reduce this current collapse problem. It has also been argued that electron trapping in the bulk causes the current collapse [15]. Another explanation for the current collapse is a reduction of tensile strain in the extrinsic device under negative gate bias [16].

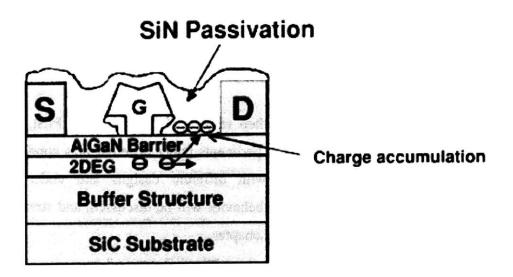

Kim et al. have also argued that device degradation is attributed to hot electron trapping [5]. They have observed an increase in drain series resistance and suggested that this increase is caused by an increase of channel depletion due to electron trapping at the surface region between gate and drain [17]. As shown in Figure 1-3, hot electrons can gain enough energy to escape the channel and get trapped on the surface. These electrons form so called virtual gate [14] and deplete channel carriers in the drain extrinsic region.

Figure 1-3. Degradation mechanism in AlGaN/GaN HEMT under high stress condition [17].

However, the detailed mechanisms behind the device failure are not still well known, and few solutions to this problem have been proposed to date. In most of the papers that suggests hot electrons as the main cause of the degradation, little experimental or theoretical proof has yet been provided. In fact, experiments that contradict to hot-electron related mechanisms will be presented in this thesis.

### 1.4. Project Goals and Thesis Outline

In this research, we have carried out systematic studies to understand the precise mechanisms of device degradation. Examining degradation phenomena in different stressing regimes on different kinds of devices, we especially focus on fundamental physics underlying device failure. Upon identifying the responsible physical mechanisms, we will then attempt to identify process and device design changes to improve the electrical reliability of GaN HEMTs.

This thesis will be organized as following: In chapter 2, GaN HEMT devices that are used in this study will be briefly described first. A reliability test chip that has been designed and fabricated will be also introduced. Then, the experimental setup will be summarized, and a characterization suite that measures device parameters of the device under test will be presented. Finally, the stress test methodology will be explained.

In chapter 3, degradation experiments and their results will be discussed. First, it will be shown how devices degrade. Then stress experiments under different bias conditions will be presented. Experiments on devices with different designs and under different environment will be also studied. Trapping behavior will be discussed, and stress tests on other test structure will be also shown in this chapter.

Finally, a hypothesis to explain the degradation mechanisms will be proposed and supporting experiments will be discussed in chapter 4. The conclusions of this research will be presented in chapter 5.

# **Chapter 2. Experimental**

# 2.1. Introduction

This chapter begins with the description of the GaN HEMTs that are used in this study. A reliability test chip that has been designed in the course of this research will be described. Finally, a device characterization suite and the different stress test schemes used in this work will be discussed.

### 2.2. Devices

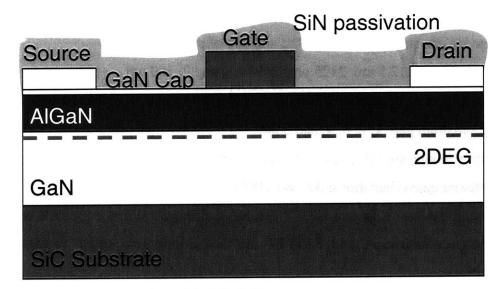

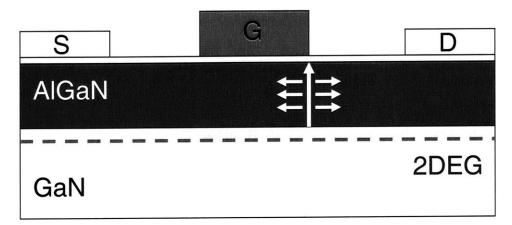

Figure 2-1. Schematic cross section of GaN HEMT.

Figure 2-1 shows a schematic cross section of the GaN HEMTs used in this study. These devices are fabricated by TriQuint Semiconductor and BAE Systems. The heterostructure is grown on a SiC substrate. GaN buffer and active channel layer is followed by AlGaN barrier layer below which 2-D electron gas is formed. Between the gate and the AlGaN layer, there is a thin GaN cap layer. Source and drain ohmic contacts are formed by annealing, and the surface is passivated by a SiN layer.

Standard devices that are mostly investigated in this study have 0.25 um (TriQuint) / 0.15 um (BAE) gate length and 2x25 um gate width. Source to drain spacing is 4 um. A typical virgin TriQuint device has a current-gain cut-off frequency  $f_T$  around 40 GHz, and  $I_{Dmax}$  is about 1.2 A/mm. The output power is about 8 W/mm, and PAE is 62 % at 10 GHz when the device is biased at 40 V [7].

#### 2.3. MIT Reliability Test Chip

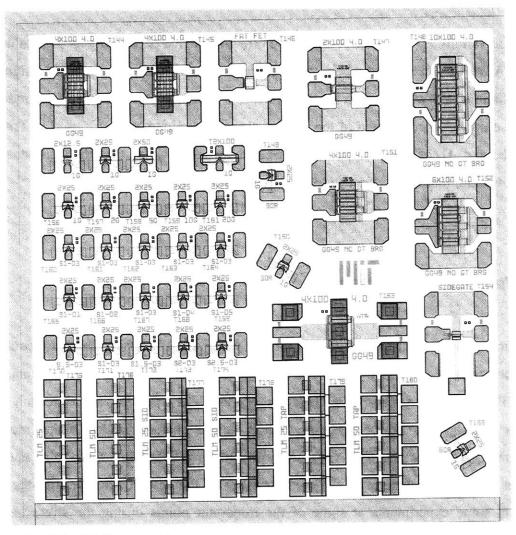

In order to carry out a systematic study of reliability, a reliability test chip was designed (Figure 2-2). Other than standard devices described in the previous section, HEMTs with different geometries are included in this chip:

- Gate length: standard, 2x, 5x, 10x, and 20x of standard device

- Gate width: 2x12.5 um, 2x25 um, 2x50 um, and 2x100 um

- The number of fingers with 100 um unit finger width: 2, 4, 6, and 10

- Gate to drain gap: 1, 2, 3, 4, and 5 um

- Source to gate gap: 0.5, 1, 1.5, 2, and 2.5 um

- Different gate orientations: 30°, 60°, 90°

- Special devices: side-gate HEMT that has a side-gate to probe the hole current due to impact ionization, and FATFET that has a long gate length to measure Hall mobility

Figure 2-2. MIT reliability test chip.

As study of degradation of Transmission-Line Method (TLM) has revealed important degradation mechanisms of InGaAs and GaAs HEMTs [18, 19], we have also designed different types of TLMs:

- Standard TLMs: W=25 um, 50 um. L = 3, 5, 7, 9, 11 um

- Tapped TLMs: W=25 um, 50 um. A tap is used to monitor the voltage at the midpoint of TLM.

- Sidegate TLMs: W=25 um, 50 um. A side gate to probe the hole current due to impact ionization.

With these variations, we can investigate the effect of device parameters as well as device physics. Also, we can sort out where the degradation takes place, what is the key signature of degradation, and what are the key dependencies (current, voltage, etc) of degradation. This test chip was incorporated in the regular process development mask used in TriQuint and BAE, and 41 of these chips are fabricated in every wafer that they produce. For different wafers, these chips were cut out and sent to MIT for this study.

### 2.4. Electrical Experiments

The basic concept of our experiments is the following: First, we fully characterize a fresh device before stressing it. This first characterization is benign enough not to damage the device. Then, we start stressing the device in a certain bias condition, and once in a while, we stop stressing the device and run a short device characterization which measures important figures of merit. This measurement runs in a short time (< 1 min) and only produces very minor changes of the characteristics of the device. Finally, after the stress test or in some experiments at some of the important points during the stress test, full characterization is again run and compared to the characteristics before the stress.

For this, we have developed a benign device characterization suite. The characterization suite is an automated program that measures several figures of merit of the device under test in different manners. The key figures of merit include  $I_{Dmax}$ ,  $R_S$ ,  $R_D$ , and  $V_T$ . It also measures full I-V characteristics at selected times along the stress experiment (e.g. at the beginning and at the end of the experiment).

#### 2.4.1. Experimental Setup

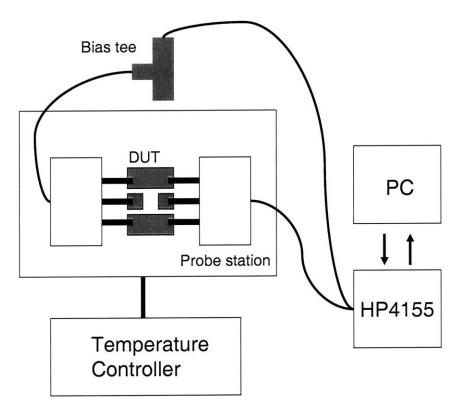

Figure 2-3. A schematic of the whole experimental setup.

A schematic diagram of our experimental setup is shown in Figure 2-3. It consists of a HP4155 semiconductor parameter analyzer with a HP41501A high power expander unit and a Cascade Microtech probe station. The chuck on the probe station is connected to temperature controller unit that regulates its temperature from -60°C to 200°C. An enclosed gas chamber enables performing measurements with the device under nitrogen and under controlled illumination conditions. As the devices under study are designed to operate at high power and high frequency, we use Picoprobe GSG 125 um microwave probes with a bias tee installed in the gate side in order to avoid any oscillations that may occur during the measurements. The HP4155 is controlled by a Windows OS PC through a GPIB connection. Some experiments were performed in air or under the microscope light illumination.

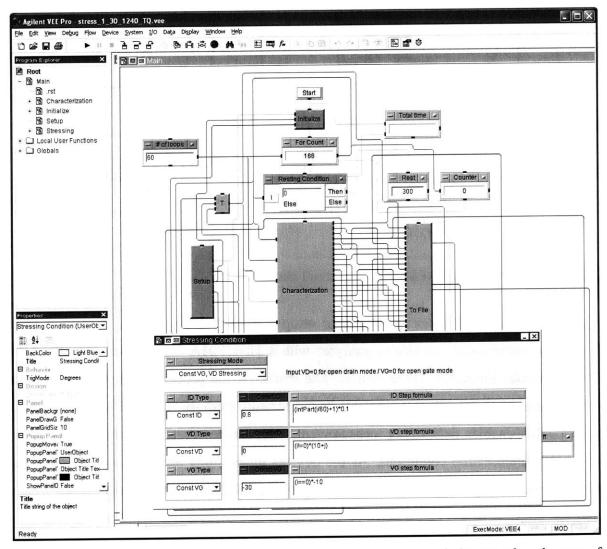

The characterization suite and the stress experiments were written in Agilent VEE 7.0, which runs the whole system. Stress experiments are programmed in a way that users can design new experiments easily without changing the structure of the whole program. For example, several drop-down options, such as step-stress, stress-recovery, constant  $I_D$  stress, and constant  $V_D$  stress, are provided for user-friendliness and efficient experiment design as shown in Figure 2-4.

Figure 2-4. Graphical user interface of a stress experiment program. A window to select the type of stress experiment and to input stress bias conditions is shown.

### 2.4.2. Characterization Suite

The characterization suite commands the HP4155 to measure figures of merit and full I-V curves. Short device characterization is done every 1 or 2 minutes in the middle of a stress experiment to keep track of device parameters. It typically takes less than 1 minute to extract all the desired figures of merit. Most measurement techniques for extracting device parameters follow the previous work on reliability of GaAs PHEMT [19], and the definitions of all figures of merit are briefly summarized in Table 2-1.

| Parameter         | Definition                                                              |  |  |  |  |  |  |

|-------------------|-------------------------------------------------------------------------|--|--|--|--|--|--|

| I <sub>Dmax</sub> | Drain current at $V_{DS}$ =5 V and $V_{GS}$ =2 V (TriQuint) / 1 V (BAE) |  |  |  |  |  |  |

| R <sub>s</sub>    | Source resistance measured with $I_G=20 \text{ mA/mm}$                  |  |  |  |  |  |  |

| R <sub>D</sub>    | Drain resistance measured with $I_G=20 \text{ mA/mm}$                   |  |  |  |  |  |  |

| R <sub>TOT</sub>  | Total resistance between drain and source with gate floating.           |  |  |  |  |  |  |

| R <sub>CH</sub>   | Channel resistance. R <sub>TOT</sub> -R <sub>S</sub> -R <sub>D</sub>    |  |  |  |  |  |  |

| V <sub>T</sub>    | $V_{GS}$ -0.5 $V_{DS}$ when $I_D$ =1 mA/mm at $V_{DS}$ =0.1 V           |  |  |  |  |  |  |

| SS                | Sub-threshold slope at $V_{DS}=0.1$ V and $I_D=1$ mA/mm                 |  |  |  |  |  |  |

| DIBL              | $V_T _{VDS=0.1 V} - V_T _{VDS=5 V}$                                     |  |  |  |  |  |  |

| g <sub>mpk</sub>  | Peak transconductance $dI_D/dV_{GS}$ at $V_{DS}=5$ V                    |  |  |  |  |  |  |

| V <sub>Gpk</sub>  | Gate voltage where $g_m$ is maximum at $V_{DS}=5$ V                     |  |  |  |  |  |  |

| gmpk2             | Peak transconductance $dI_D/dV_{GS}$ at $V_{DS}=0.1$ V                  |  |  |  |  |  |  |

| I <sub>Dmin</sub> | Minimum drain current in sub-threshold curve at $V_{DS}$ =0.1 V         |  |  |  |  |  |  |

| V <sub>Gmin</sub> | Gate voltage where $I_D$ is minimum at $V_{DS}=0.1$ V                   |  |  |  |  |  |  |

| I <sub>GVT</sub>  | Gate current at $V_{GS}=V_T$ and $V_{DS}=0.1$ V                         |  |  |  |  |  |  |

| $V_{Gon}$         | Gate voltage where I <sub>D</sub> =1 uA/mm                              |  |  |  |  |  |  |

| I <sub>Goff</sub> | Gate current at $V_{GS}$ =-5 V and $V_{DS}$ =0.1 V                      |  |  |  |  |  |  |

| I <sub>Dss</sub>  | Drain current at $V_{DS}$ =5 V and $V_{GS}$ =0 V                        |  |  |  |  |  |  |

Table 2-1. Definition of device parameters measured by the characterization suite.

The device characterization must be benign in that it must produce reliable and reproducible measurements without affecting the device under test. For this, the measurement conditions have to be selected carefully, and the effect of FOM extraction have been studied in detail. In our work, extensive repeated characterizations have been run on virgin devices to check if the characterization suite really does not produce any damage to the device.

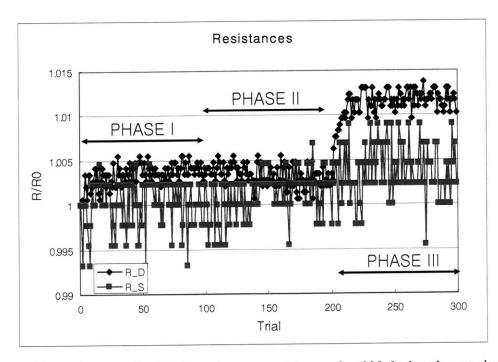

Figure 2-5. Change in normalized drain and source resistance after 300 device characterizations. In phase I, basic figures of merit are extracted. In phase II, full output characteristics are also measured. In phase III, full transfer and sub-threshold characteristics are measured on top of the basic characterization and output characteristics measurement.

Figure 2-5 describes such a typical experiment. In phase I, basic figures of merit including  $I_{Dmax}$ ,  $R_S$ ,  $R_D$ ,  $V_T$ , and  $I_{Goff}$  are extracted 100 times in a row. In phase II, on top of this basic parameter extraction, output characteristics are measured. Finally, in phase III, transfer characteristics are also measured in addition to the measurements done in phase II. As shown in Figure 2-5, the characterization suite only produced less than 1 % changes in  $R_S$  and  $R_D$  in phase I, and less than 2 % even if the device is fully characterized 300 times in a row (this includes extraction of full I-V characteristics, Phase II & III). The changes in the most important device parameters are summarized in Table 2-2. Although not perfect, the characterization suite produces only minor changes in the device parameters, compared to typical changes during the stress test, which is usually in excess of 20 %. Also, from Figure 2-5, we can see that the measurements obtained from the characterization suite are reproducible and reliable.

|                                       | I <sub>Dmax</sub> | VT     | R <sub>S</sub> | R <sub>D</sub> |

|---------------------------------------|-------------------|--------|----------------|----------------|

| Basic (100 times)                     | -0.3 %            | +6 mV  | +0.3 %         | +0.4 %         |

| Basic + Output (100 times)            | -0.8 %            | +4 mV  | 0              | -0.1 %         |

| Basic + Output + Transfer (100 times) | -0.9 %            | +2 mV  | +0.2 %         | +0.9 %         |

| Total (300 times)                     | -2 %              | +12 mV | +0.5 %         | +1.2 %         |

Table 2-2. Changes in important figures of merit after 300 runs of the device characterization suite.

In addition, this characterization suite can be easily adjustable to new device process designs, so that a new device with totally different characteristics can be easily measured by simply changing configuration parameters such as the bias point to extract  $I_{Dmax}$ .

### 2.5. Stress Test Methodology

In this thesis, we have focused on DC reliability studies. Rather than a simple stress test in which the stressing conditions are kept constant during the test, several electrical stress schemes have been investigated in the course of this research. These are graphically described in Figure 2-6.

Stress-recovery type of experiments in which stress is followed by a recovery period is performed to study how a device degrades as well as how it recovers from the degradation. In this type of experiment, a specific stress bias is applied in the stress phase, and this stress is removed in the recovery phase (Figure 2-6 left) while the device is characterized.

As discussed in previous works [18, 19], a step-stress scheme has been utilized to maximize productivity. In this type of experiment, the strength of the stress parameter such as voltage or current is stepped up from a smaller value to larger values in order to see the effect of that stress parameter over a wide range of values in a single device (Figure 2-6 middle). From this type of experiment, we obtain great insight into physical mechanisms. Finally, step-stress-recovery experiments have also been carried out (Figure 2-6 right).

Figure 2-6. Conceptual stress schemes: (from left to right) stress-recovery, step-stress, and step-stress-recovery.

Regarding the period of stress, we have mostly focused on short-term degradation which happens within a few hours. We emphasize this short-term degradation because GaN-based HEMTs are known to degrade in relatively short period of time. In fact, we have seen significant degradation even within an hour of stress. However, medium-term stress experiments (on the order of one or two days) have also been performed in order to investigate phenomena which take place in a relatively longer period of time.

Different stress bias conditions were studied: *high power state* (high V<sub>DS</sub>, high I<sub>D</sub>), *ON-state* (low V<sub>DS</sub>, high I<sub>D</sub>), and *OFF-state* (high V<sub>DS</sub>, low I<sub>D</sub>). In high power condition, we tried to simulate the RF power amplifying operation in a more severe way. By investigating both ends of the load line, ON state and OFF state, we can study where the most stressful point is during a real RF operation. In addition, we have focused on the  $V_{DS}=0$  state in which negative gate voltage is applied. In this condition, we can stress the both sides of the device simultaneously with a low current but a high voltage. These conditions are shown in Figure 2-7 relative to the position of the RF power load line that is typically followed in RF power applications.

Unless specified, all of our experiments are done at room temperature, with the device inside a dark chamber with nitrogen gas injected into it.

Figure 2-7. Stress bias points: High Power, ON state, OFF state, and V<sub>DS</sub>=0 conditions.

### 2.6. Summary

In this chapter, we have introduced the GaN HEMT devices, the reliability test chip, and the electrical experimental setup used in this thesis. In order to study degradation phenomena of GaN HEMTs, we have developed a characterization suite. Although slight changes are produced by a number of repeated device characterizations, we have shown that the characterization suite performs reliable and benign measurements of GaN HEMTs. Finally, we have introduced stress test methodologies that were used in this study. In the next chapter, results of degradation experiments will be shown, and basic degradation phenomena will be discussed.

# **Chapter 3. Degradation Experiments**

In the last chapter, we have introduced the experimental setup and the characterization and stress protocols for studying electrical reliability of GaN HEMTs. In this chapter, we describe several degradation experiments. Experiments performed in various stress bias conditions on HEMTs and TLMs are presented, and their results are discussed. Also, we discuss the effects of device geometries and environment. Based on the results, electron trapping behavior is investigated as a basic degradation mechanism.

### 3.1. Overall Degradation Phenomena

Figure 3-1 and Figure 3-2 show the overall result of a typical stress test. This is a high power step-stress experiment that is performed on a standard type device. In this experiment, the drain bias is stepped from 5 V up to 30 V. Stress current is set at 800 mA/mm throughout the experiment by adjusting the gate bias. As it can be seen in Figure 3-1, source resistance  $R_S$  increases little, whereas drain resistance  $R_D$  shows larger change as the device is stressed. The maximum drain current  $I_{Dmax}$  decreases. As shown in Figure 3-2, the threshold voltage first shifts positive at lower stress voltage, but it then shifts negative for  $V_{DS}$ >20 V.

Figure 3-1. Change in normalized  $I_{Dmax}$ ,  $R_D$ , and  $R_S$  in step-stress experiment in the high power state ( $V_{DS}$ =5~30 V in 5 V steps,  $I_D$ =800 mA/mm, 30 minutes per step).

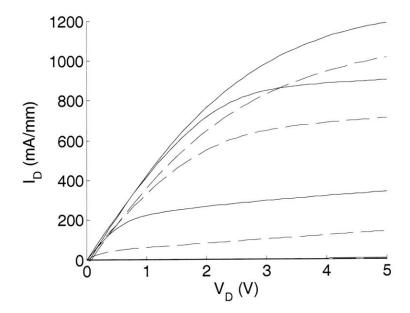

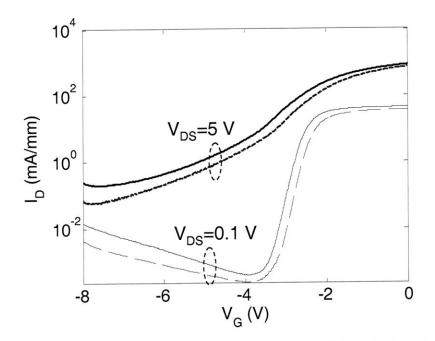

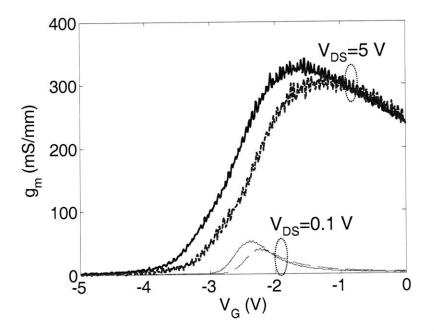

Figure 3-3 shows the change in the output characteristics before and after the stress test. As it can be seen, drain current significantly decreases after the stress. As it can be seen in Figure 3-4 and Figure 3-5, the sub-threshold slope remains relatively constant, while the maximum transconductance decreases after the stress test. For the rest of this study, we will mostly focus on the changes in  $I_{Dmax}$ ,  $R_S$  and  $R_D$ .

It is interesting to note in Figure 3-1 that degradation is negligible at low voltage (ON-state) in spite of the large current. It then seems that voltage is a more important factor for device degradation than current. This result motivated us to do similar experiments with much lower current, in the OFF state. This will be discussed in the following sections.

Figure 3-2. Threshold voltage change in the same experiment as Figure 3-1.

Figure 3-3. Output characteristics before (solid) and after (dashed) the same stress test as in Figure 3-1.  $V_{GS}$ =-4~2 V (2 V step).

Figure 3-4. Change in sub-threshold characteristics before (solid) and after (dashed) the same experiment as Figure 3-1.

Figure 3-5. Change in  $g_m$  before (solid) and after (dashed) the same experiment as Figure 3-1.

Figure 3-6. Change in normalized  $I_{Dmax}$ ,  $R_D$ , and  $R_s$  in step-stress experiment in the OFF state ( $V_{DS}$ =5~40 V in 5 V steps,  $I_D$ =25 mA/mm, 30 minutes per step).

Figure 3-6 shows the result of an OFF state step-stress experiment. In this experiment, the stress current is 25 mA/mm, which is about 3 % of that in the high power stress experiment of Figure 3-1. We also find that in the OFF state, the source resistance shows little degradation. However, although the stress current is much smaller, the degradation in  $R_D$  and  $I_{Dmax}$  is comparable to that in the high power state (see Figure 3-1). This result confirms that voltage, or electric field, is the main driver for device degradation, and current is an accelerating factor [9]. However, it is not clear whether the effect of current is supplying hot electrons to the system or increasing the junction temperature. Our results are obviously inconsistent with hot-electron based mechanisms in that degradation in OFF state is comparable to that in high power state in spite of much fewer hot electrons in the channel.

## 3.3. V<sub>DS</sub>=0 Condition

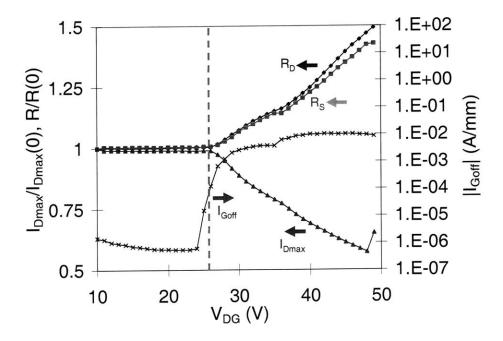

Figure 3-7. Change in normalized  $I_{Dmax}$ ,  $R_D$ ,  $R_S$ , and  $I_{Goff}$  as a function of stress voltage in a stepstress experiment in  $V_{DS}=0$  state ( $V_{DG}=10\sim50$  V in 1 V steps).

Stressing a device in  $V_{DS}=0$  condition is interesting in that no current flows through the channel, and both sides of the device can be stressed at the same time. Figure 3-7 summarizes the results of a  $V_{DS}=0$  step-stress experiment. In this experiment,  $V_{GS}$  is stepped from -10 V to -50 V. The voltage step size is -1 V, and the device is stressed for one minute at each step. As expected, both  $R_S$  and  $R_D$  degrade by about the same amount. Interestingly, we have seen no  $I_{Dmax}$  and series resistance degradation up to around 25 V, and degradation sharply starts beyond that voltage. Because of this, we define this sudden onset of degradation as taking place at a "critical voltage". Interestingly,  $I_{Goff}$ , which is defined as gate current at  $V_{DS}=0.1$  V and  $V_{GS}=-5$  V, also shows a sudden very large increase at around the critical voltage. This simultaneous degradation in  $I_D$  and  $I_G$  is generally seen in all our step-stress experiments.

Figure 3-8. Stress current of the experiment in Figure 3-7.

As shown in Figure 3-8, the drain current at -27 V, where degradation becomes apparent, is about 13 mA/mm, and it is 104 mA/mm at -40 V in this particular experiment. This might suggest that degradation is driven by the relatively large current which can then produce hot electrons. However, two observations are contradictory to that argument: first, degradation does not suddenly increase around  $V_{DG}$ =35 V where stress currents again suddenly increase; second, degradation keeps increasing after 40 V without any signature of saturation, while the stress currents almost saturate.

Moreover, it has been found that degradation of  $I_{Dmax}$  and series resistances is not correlated to the stress current in similar  $V_{DS}=0$  stress experiments carried out in other devices. In fact, in a  $V_{DS}=0$  experiment shown in Figure 3-9, very large degradation (23 % of  $I_{Dmax}$ reduction at -27 V) is introduced in spite of negligible drain current of less than 0.1 mA/mm, which is three orders of magnitude less than the stress current in the experiment of Figure 3-7. Comparing this number to the experiment in Figure 3-7, we can see that the same amount of degradation can happen regardless of the stress current. This result again

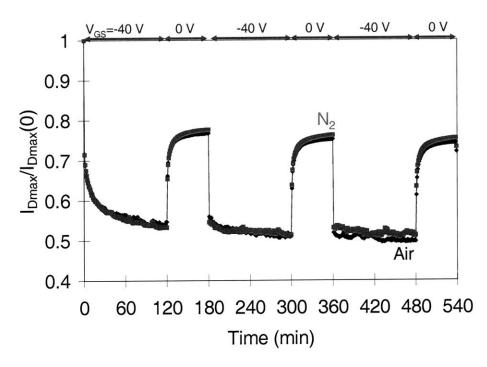

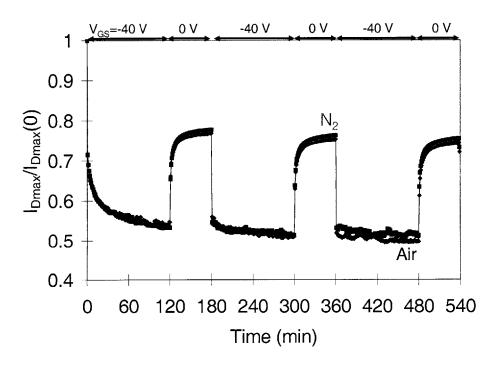

#### 3.4.1. Effect of Environment

In order to see the effect of atmosphere, we have performed a  $V_{DS}=0$  stress-recovery experiment in air and compared the result with the experiment performed in nitrogen environment. As shown in Figure 3-10, we have found that degradation is the same in air as in nitrogen environment. This result is different from the GaAs PHEMT case, in which degradation is much more pronounced in air [19] than in N<sub>2</sub>. This is consistent with a degradation mechanism for the GaN HEMT that is not of a surface type although it is also possible that these devices have a much more impermeable SiN passivation layer that protects the device from the environment in a much more effective way than the GaAs PHEMTs that we have studied [19].

Figure 3-10. Change in normalized  $I_{Dmax}$  in  $V_{DS}=0$  stress-recovery experiment with and without nitrogen gas.  $V_{GS}=-40$  V is applied during the stress period of 120 minutes.

#### 3.4.1. Effect of Environment

In order to see the effect of atmosphere, we have performed a  $V_{DS}=0$  stress-recovery experiment in air and compared the result with the experiment performed in nitrogen environment. As shown in Figure 3-10, we have found that degradation is the same in air as in nitrogen environment. This result is different from the GaAs PHEMT case, in which degradation is much more pronounced in air [19] than in N<sub>2</sub>. This is consistent with a degradation mechanism for the GaN HEMT that is not of a surface type although it is also possible that these devices have a much more impermeable SiN passivation layer that protects the device from the environment in a much more effective way than the GaAs PHEMTs that we have studied [19].

Figure 3-10. Change in normalized  $I_{Dmax}$  in  $V_{DS}=0$  stress-recovery experiment with and without nitrogen gas.  $V_{GS}=-40$  V is applied during the stress period of 120 minutes.

#### 3.4.2. Degradation of MISFET

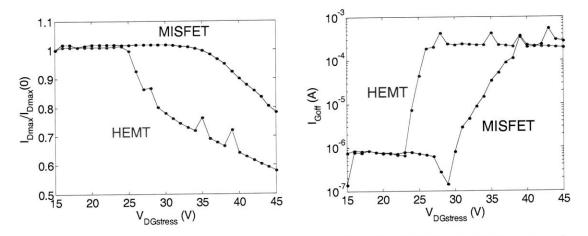

Figure 3-11. Typical  $I_{Dmax}$  (left) and  $I_{Goff}$  (right) degradation of MISFET and HEMT in  $V_{DS}=0$  stepstress experiments.

We have investigated the degradation of MISFETs and compared it with the degradation of HEMTs. We have measured devices on a wafer that has both normal HEMTs (left half) and MISFETs (right half). The process is identical except that one half of the wafer has  $SiO_2$  insulating layer between gate metal and semiconductor, while the other half does not.

Forty one devices across the wafer are step-stressed at the  $V_{DS}=0$  condition. The gate voltage  $V_{GS}$  is stepped from -15 V to -45 V, and the drain voltage  $V_{DS}$  is fixed at 0 V. The step size is -1 V, and the device is stressed for 30 seconds in each step. After each step, two figures of merits are measured:  $I_{Dmax}$  ( $I_D @ V_{DS}=5 V$ ,  $V_{GS}=2 V$ ) and  $I_{Goff}$  ( $I_G @ V_{DS}=1 V$ ,  $V_{GS}=-5 V$ ). Figure 3-11 shows typical  $I_{Dmax}$  and  $I_{Goff}$  degradation of both types of devices.

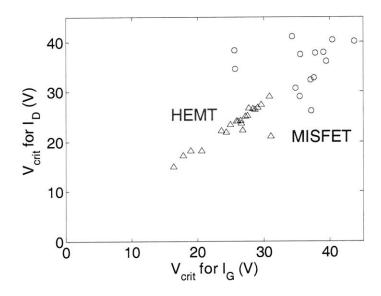

As can be seen, the critical voltage for  $I_{Dmax}$  degradation of MISFETs is higher by about 10 V than that of HEMTs. Also, the gate leakage current of HEMTs starts to increase at a lower voltage than in the case of MISFETs. In fact, we find that the critical voltage for  $I_{Dmax}$  degradation exhibits a strong correlation with the critical voltage for  $I_{Goff}$  degradation as shown in Figure 3-12. The average and the standard deviation of the critical voltage for

$I_{Dmax}$  degradation of HEMTs are 25.6 V and 4.1 V, respectively. For MISFETs, the average is 36.3 V and the standard deviation is 5.0 V.

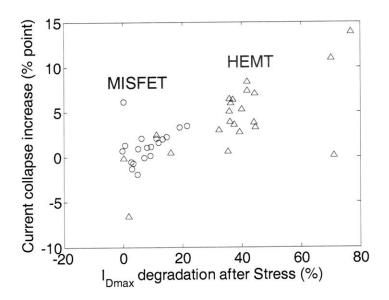

We have also measured the current collapse by applying -10 V voltage pulse to the gate before and after the stress. As shown in Figure 3-13, a device with larger  $I_{Dmax}$  degradation shows greater increase of the current collapse, which gives us a clue that degradation is somehow correlated to increase in trap density. This is examined in more detail in section 3.6.

Although MISFETs show better DC reliability, they turn out to be worse in RF power soak measurements [20]. However, it is still not clear if the worse RF degradation results from higher  $V_{DG}$  due to more negative threshold voltage of MISFETs. Because these power soak experiments have been done with the same drain bias voltage and drain bias current,  $V_{GS}$  of MISFETs are more negative than that of normal HEMTs, resulting in higher  $V_{DG}$ . Although we have found that voltage is the main driver for DC degradation, further investigation is needed to sort out other mechanisms in RF stress, if any.

Figure 3-12. The correlation between the critical voltage for  $I_D$  degradation and  $I_G$  degradation (triangle: HEMT, circle: MISFET)

Figure 3-13. The correlation between the current collapse increase and  $I_{Dmax}$  degradation (triangle: HEMT, circle: MISFET).

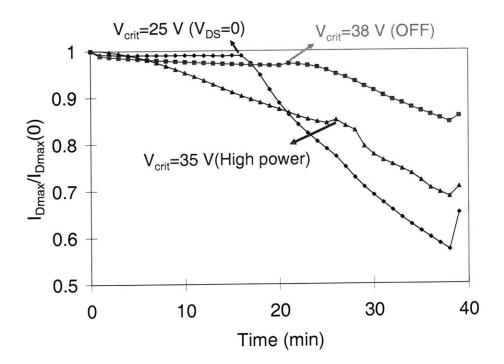

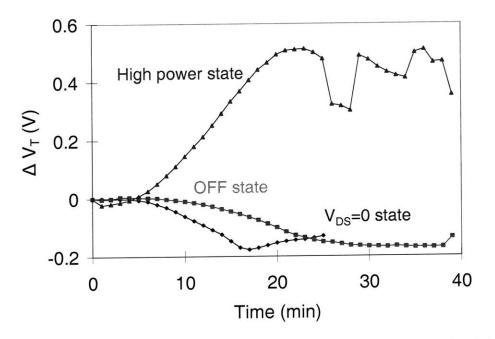

# 3.4.3. Critical Voltage in other Stress Bias Conditions

In section 3.3, we have observed a critical voltage beyond which a device starts to degrade. In the  $V_{DS}=0$  condition, this voltage is about 20~25 V. However, this critical voltage seems to be too low because devices operate normally at 30 V without degrading that much. With standard devices (W=2x25 um, L<sub>G</sub>=0.25 um, L<sub>SG</sub>=L<sub>GD</sub>=2 um), we have compared the critical voltage of degradation under different stress conditions: high power state, OFF state, and  $V_{DS}=0$  state.

Figure 3-14 shows the  $I_{Dmax}$  degradation in three different step-stress experiments. The stress bias conditions for these experiments are summarized in Table 3-1. In these experiments, the devices have been stressed for 1 minute in each step, and the step size was 1 V.

|                          | Stress condition                                    |

|--------------------------|-----------------------------------------------------|

| V <sub>DS</sub> =0 state | V <sub>GS</sub> =-10~-50 V                          |

| OFF state                | V <sub>GS</sub> =-7 V, V <sub>DS</sub> =10~50 V     |

| High power state         | I <sub>D</sub> =800 mA/mm, V <sub>DS</sub> =10~50 V |

Table 3-1. Stress bias condition for three different step-stress experiments.

As it can be seen in Figure 3-14,  $V_{DGcrit}$  is 25 V for  $V_{DS}$ =0 state, 38 V for OFF state, and 35 V for high power state. Here, this critical voltage is defined as the voltage at which a change in the slope of  $I_{Dmax}$  evolution curve occurs. In high-power condition, this definition is somehow ambiguous as the device degrades even at lower voltage. However, the part of decrease in  $I_{Dmax}$  before  $V_{DG} < 30$  V is due to large positive shift of threshold voltage as shown in Figure 3-15, and this positive shift is only observed in the high-power state stress. As  $g_m$  is about 128 mS/mm around  $V_{DS}$ =5 V and  $V_{GS}$ =2 V where we measure  $I_{Dmax}$ , threshold voltage shift of +0.5 V results in 64 mA/mm reduction of  $I_{Dmax}$ . This change is responsible for about half of the change in  $I_{Dmax}$  in  $V_{DG}$ <30 V. At around  $V_{DG}$ =35 V, there is also a change in the slope of  $I_{Dmax}$  evolution although the threshold voltage is relatively constant beyond that point.

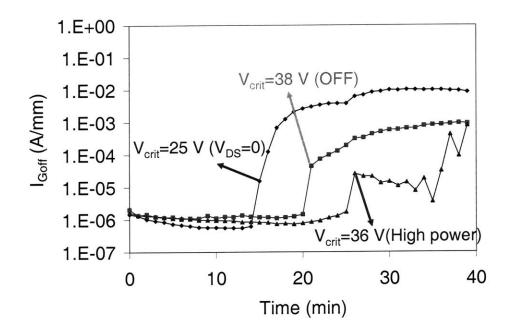

Figure 3-16 shows the time evolution of the gate leakage current. The critical voltages for sudden gate leakage current increase are 25, 38, and 36 V for  $V_{DS}$ =0 state, OFF state, and high power state, respectively, which are consistent with the critical voltage for  $I_{Dmax}$  degradation mentioned above. This critical voltage for  $I_{Goff}$  degradation is defined as the voltage at which there is a abrupt change in  $I_{Goff}$ . This large increase of gate leakage current turned out to be unrecoverable, and the correlation between the critical voltage for  $I_D$  and  $I_G$  degradation suggests a common origin. Although a different mechanisms for  $I_D$  degradation may seem to exist in high power state, this abrupt gate leakage degradation around  $V_{DG}$ =36 V justifies our previous definition of the critical voltage for  $I_D$  degradation in high power state. We can see that the critical voltage for degradation in the normal operating configuration, OFF state and high power state, is about 10~15 V larger than that in  $V_{DS}$ =0 condition.

Figure 3-14. Change in  $I_{Dmax}$  in step-stress experiments and the critical voltage  $V_{DGcrit}$  for  $I_{Dmax}$  degradation.

Figure 3-15. Change in  $V_T$  in the same experiment in Figure 3-14. In  $V_{DS}=0$  state, threshold voltage is not properly extracted after 25 minutes as the minimum drain current became larger than 1 mA/mm.

Figure 3-16. Change in gate leakage current  $I_{Goff}$  in the same experiment in Figure 3-14 and the critical voltage for  $I_{Goff}$  degradation.

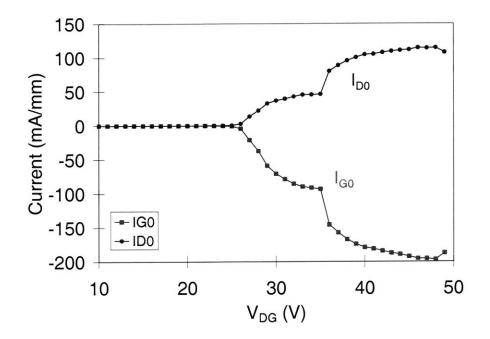

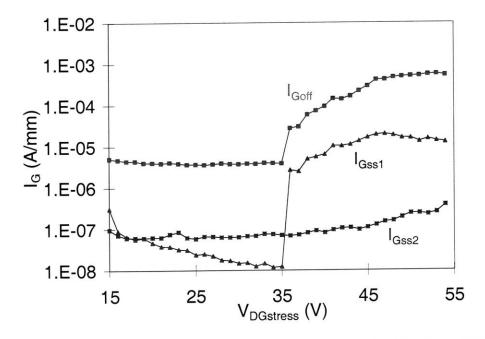

#### 3.4.4. The Origin of Gate Leakage Degradation

In section 3.4.3, we have shown that gate leakage current degrades permanently after applying a certain high voltage. In order to confirm which junction is responsible for this degradation, we have done an OFF state step-stress experiment in which we have measured two more figures of merit:  $I_{Gss1}$  is the gate current at  $V_{DS}=5$  V and  $V_{GS}=0$  V;  $I_{Gss2}$  is the gate current at  $V_{DS}=-5$  V and  $V_{GS}=-5$  V. As  $V_{GS}$  for  $I_{Gss1}$  and  $V_{GD}$  for  $I_{Gss2}$  are zero, all the gate current is from the other junction, gate-drain junction for  $I_{Gss1}$  and gate-source junction for  $I_{Gss2}$ . Therefore, by observing these currents, we can distinguish the origin of the leakage.

As shown in Figure 3-17,  $V_{DGcrit}$  for  $I_{Goff}$  degradation is 36 V in this experiment. At this voltage,  $I_{Gss1}$  starts to degrade simultaneously with  $I_{Goff}$ , whereas  $I_{Gss2}$  remains relatively unchanged. This result shows that gate leakage degradation in OFF state is originated from

gate to drain junction as expected. Similar result is also observed in high power condition. Not surprisingly, both junctions are found to degrade in  $V_{DS}=0$  state.

Figure 3-17. Change in  $I_{Goff}$ ,  $I_{Gss1}$ , and  $I_{Gss2}$  as a function of stress bias  $V_{DG}$  in an OFF state step stress experiment.  $I_{Gss1}$  is gate leakage current through gate to drain junction, and  $I_{Gss2}$  is gate leakage current through gate to source junction.

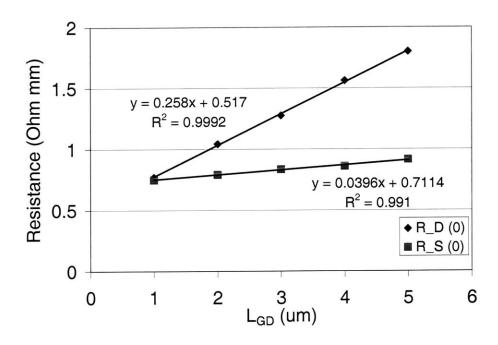

## 3.4.5. Effect of L<sub>GD</sub>

We have investigated the effect of gate-drain gap ( $L_{GD}$ ) on device degradation. In order to understand the effect of  $L_{GD}$ , we have done OFF state stress experiments with five devices with different  $L_{GD}=1\sim5$  um,  $L_{SG}=1$  um, and W=2x25 um. These devices have been stressed at  $V_{DS}=30$  V and  $V_{GS}=-5$  V for 50 minutes. The measurement of drain resistance before the stress tests revealed a contact resistance of 0.517  $\Omega$ ·mm (Figure 3-18). As expected, drain resistance increases with  $L_{GD}$ .

Figure 3-18.  $L_{GD}$  dependency of source and drain resistance of fresh devices.

As it can be seen in Figure 3-19, from the change in  $R_D$ , it appears that a device with longer  $L_{GD}$  tends to degrade less. However, it can be misleading to compare  $R_D/R_D(0)$  because the drain resistances at t=0 are different as shown in Figure 3-18. Therefore, we also need to compare the absolute value of the change in  $R_D$ .

Figure 3-20 summarizes the absolute change in  $R_D$  and  $R_S$  as a function of  $L_{GD}$ . As it can be seen,  $\Delta R_D$  seems to be quite independent of  $L_{GD}$ . This result confirms that drain resistance degradation is not a surface-type degradation because the same degree of  $\Delta R_D/R_D(0)$  is expected if degradation occurs all over the surface between the gate and the drain as in the drain resistance degradation of GaAs PHEMTs [19]. In contrast, the  $L_{GD}$  independent increase of  $R_D$  suggests that drain resistance degradation takes place at a rather localized point, presumably right next to the gate edge.

Figure 3-19. Change in normalized  $R_D$  in OFF state stress experiments on different  $L_{GD}$  devices. Five different devices with different  $L_{GD}$ =1~5 um are stressed at  $V_{DS}$ =30 V and  $V_{GS}$ =-5 V for 50 minutes.

Figure 3-20. Absolute value of change in  $R_D$  and  $R_S$  as a function of  $L_{GD}$  in the same experiment as Figure 3-19.

## 3.5. Trapping Behavior

In the previous sections, we have shown our results for the degradation phenomena of GaN HEMTs. In this section, we try to figure out the basic mechanism behind device degradation. In particular, as many of the previous studies on reliability of GaN HEMTs have reported that electron trapping is one of the main reasons of device degradations [11, 13, 17], we also investigate the trapping behavior as a device degrades.

#### 3.5.1. Off-state Stress-recovery

In our degradation experiments, we have seen that GaN HEMTs degrade in a relatively short time:  $I_{Dmax}$  decreases,  $R_D$  increases, and gate leakage current increases after a bias stress. In order to clarify why these parameters change, we have carried out OFF state stress-recovery experiments such as the one summarized in Figure 3-21. In this experiment, a 30 V drain bias is applied while the gate voltage is set to maintain a drain current of 20 mA/mm. This electrical stress is applied for 30 minutes. After the stress period, all stress biases are removed for another 30 minutes while the device continues to be characterized. This one hour cycle is repeated three times.

In the stress phase, as seen previously, the drain resistance increases, and  $I_{Dmax}$  decreases while the source resistance does not show significant degradation. In the recovery phase, both  $R_D$  and  $I_{Dmax}$  partially recover to some extent. However, as soon as the stress is reapplied,  $R_D$  and  $I_{Dmax}$  go immediately back to the value that they had when degradation stopped. From here on, degradation resumes. This is strong evidence of trapping behavior. This behavior repeats as the stress is turned on and off with the overall level of degradation increasing with every cycle. This result can be understood in the following sense. First, in the stress period, traps seem to be generated, and electrons get trapped in these traps. If the stress is turned off, some of these traps get depopulated, and the device partially recovers. However, when the stress is reapplied, electrons immediately get trapped again, and trap formation continues. In that sense, recovery is not an appropriate term, and in fact, we have observed only minor recovery with the device at rest for more than 300 days. This is shown in Figure 3-22. The same device used in the experiment of Figure 3-1 has been stressed with the same stress condition at which it had been stressed. After 304 days at rest, I<sub>Dmax</sub> of the device was partially recovered to some extent, but the device went back to the degraded state immediately upon reapplying the same stress bias. From experiments like this, we can conclude that degradation is irreversible.

Figure 3-21. Change in  $I_{Dmax}$ ,  $R_D$ , and  $R_s$  in a stress-recovery experiment in the OFF state ( $V_{DS}$ =30 V,  $I_D$ =20 mA/mm) for 30 minutes of stress followed by 30 minutes at rest. This cycle is repeated for three times.

Figure 3-22. Time evolution of  $I_{Dmax}$  of the device in Figure 3-1. After the end of the stress experiment in Figure 3-1, the device was put at rest for 304 days before it were measured again. After the first measurement of  $I_{Dmax}$ , the same stress ( $V_{DS}$ =30 V,  $I_{D}$ =800 mA/mm) was applied for 2 more minutes.

# 3.5.2. Enhanced Detrapping

In order to confirm our trapping hypothesis, additional stress-recovery experiments have been performed. In these experiments, we could confirm trapping behavior by observing enhanced detrapping in the recovery phase in three different ways.

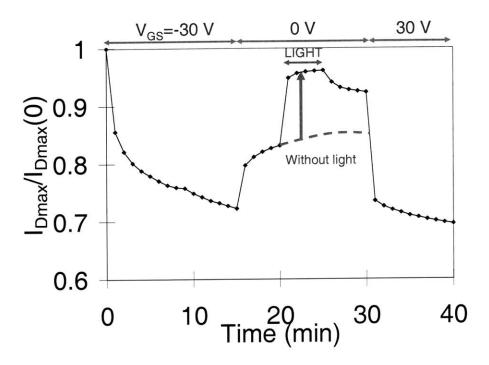

First, as shown in Figure 3-23, recovery can be enhanced by light illumination. In this experiment, microscope light is turned on for 5 minutes in the recovery period after stressing for 15 minutes. As it can be seen, light illumination greatly enhances recovery, which is a strong signature of electron detrapping.

Figure 3-23. Change in  $I_{Dmax}$  in a stress-recovery experiment on a standard type device stressed at  $V_{DS}=0$  and  $V_{GS}=-30$  V for 15 minutes and at rest for 15 minutes. Additional stress is applied for another 10 minutes. From t=20 to 25 min, microscope light was illuminated.

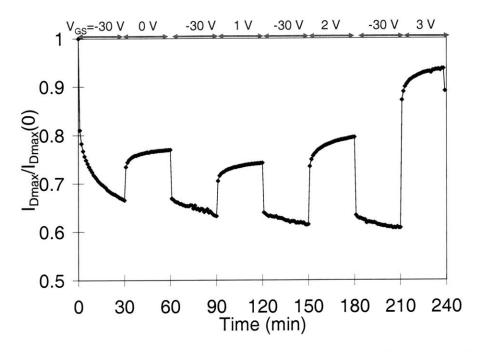

We have also observed enhanced detrapping by applying positive gate bias. As shown in Figure 3-24,  $V_{GS}>0$  is applied in the recovery phases in a  $V_{DS}=0$  stress-recovery experiment. As it can be seen in Figure 3-24, this positive gate bias enhances electron detrapping as the voltage increases.

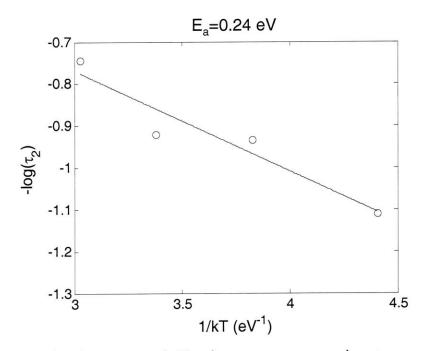

Finally, we have studied the impact of temperature on the recovery phase. We have performed  $V_{DS}=0$  stress-recovery experiments at T=-10, 30, 70, and 110 °C. As shown in Figure 3-25, time constant of detrapping turned out to be smaller at higher temperature, and activation energy of 0.24 eV can be obtained from these experiments, which is consistent with [11].

Figure 3-24. Change in  $I_{Dmax}$  in a stress-recovery experiment on a standard type device stressed at  $V_{DS}=0$  and  $V_{GS}=-30V$  for 30 minutes. Four stress cycles are repeated with different values of  $V_{GS}$  during the 30 minutes recovery phase (0, 1, 2, and 3 V).

Figure 3-25. Detrapping time constants in V<sub>DS</sub>=0 stress-recovery experiments.

All of these three experiments are consistent with an electron trapping/detrapping hypothesis, and we can confirm that device degradation is originated from increased electron trapping.

## 3.6. Trap Generation

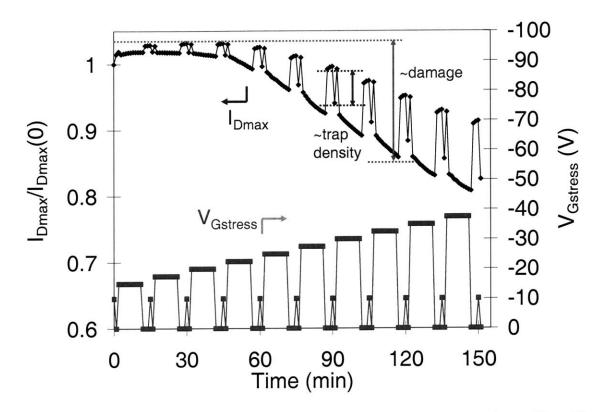

In the previous section, we have seen that degradation of GaN HEMT is strongly related to electron trapping. However, it is not still clear whether those involved traps are produced during a device stressing or they are traps that existed before device operation. In order to investigate this problem, we have designed a step-stress-recovery experiment in which we have introduced diagnostic pulses to sample trap density.

The experiment is described in Figure 3-26. We stress the device at  $V_{GS}$ =-15 V to -40 V for 10 minutes, and then the device is allowed to recover for 5 minutes. To expedite detrapping time, microscope light is illuminated on the sample throughout the entire length of this experiment. During the recovery phase, a -10 V voltage pulse is applied to the gate, which produces a momentary reduction in  $I_{Dmax}$  which is known as current collapse. As the current collapse is known to relate to trapping, we can evaluate the trap density through the response to the -10 V diagnostic pulse. Therefore, in this experiment, we track two figures of merit: the total damage is the change in  $I_{Dmax}$  from its maximum value to that at the end of a stress period. In addition, the trap density is evaluated from the current collapse produced by the diagnostic voltage pulses.

Figure 3-26. Change in  $I_{Dmax}$  and stress bias of a  $V_{DS}=0$  step-stress-recovery experiment.  $V_{GS}=-15\sim-40$  V is applied for stress, and -10 V diagnostic voltage pulses are applied during the recovery phase. The step size is -2.5 V, and the device is stress for 10 minutes in each step. To expedite detrapping, microscope light is turned on during the test.

As it can be seen in Figure 3-26, a sudden onset of degradation at a critical voltage can be again confirmed around 22.5 V. As the damage increase, so does the response to the diagnostic pulse and the trap density. This result is summarized in Figure 3-27 in which damage and current collapse are plotted as a function of the stress bias. It is clear that damage correlates with trap density, and we can confirm that traps are generated during the bias stress.

Figure 3-27. Total damage and current collapse produced by diagnostic pulse as a function of the stress bias.

## 3.7. TLM Step-stress

We have performed step-stress experiments with a Transmission Line Method (TLM) and compared the results with degradation in HEMTs. The TLM is a structure without a gate as shown in Figure 3-28. For a meaningful comparison, we have selected a TLM of which length is identical to  $L_{GD}$  of the HEMT.

Figure 3-28. A schematic picture of a HEMT and a TLM used for the comparison.  $L_{GD}$  of the HEMT is identical to the length of the TLM.

The TLM is step-stressed from 20 V to 26 V, and the HEMT is step-stressed at the same voltage with the stress current at 800 mA/mm. The change in I-V characteristics of the TLM is shown in Figure 3-29. As shown in Figure 3-29 and Figure 3-30, this stress does not introduce any significant degradation of  $I_{max}$  of the TLM in spite of a huge current (~1.7 A/mm) [9]. On the other hand,  $I_{Dmax}$  of the HEMT degrades severely although the stress current is less than half of that of the TLM. This result strongly confirms that the main driver for degradation is not current. The fact that TLM does not degrade in spite of relatively large lateral electric field suggests that the main driver for HEMT degradation may be vertical electric field that exists only in HEMTs. Also, from the time evolution of low field resistance of the TLM, we cannot see any obvious ohmic contact degradation (Figure 3-30).

From this comparison, we can conclude that HEMT degradation does not correlate with TLM degradation. This is rather different from observations in GaAs and InP HEMTs in which case TLM degradation has revealed physics that has strong correlation with HEMT degradation [19, 21]. In those cases, hot electrons play important roles in device degradation.

Figure 3-29. Change in I-V characteristics of the TLM before and after the experiment of Figure 3-30. The device was step-stressed at  $V=20\sim26$  V for 140 minutes.

Figure 3-30. Change in  $I_{Dmax}$  of a TLM and a HEMT and low field resistance of the TLM. The HEMT is stressed at  $V_{DS}=20\sim26$  V (1 V step, 20 min/step) and  $I_D=800$  mA/mm. The TLM is stressed at the same voltage, but the current is around 1.7 A/mm. The length of the TLM (3 um) is the same as the gate-drain gap of the HEMT.

In conclusion, this result gives us additional evidence that hot electrons may not be the main cause of device degradation, especially trap formation as discussed in [11].

# 3.8. Summary of Key Findings

From a number of experiments, we have seen that degradation of GaN HEMT results from trap generation and subsequent electron trapping. This trap generation seems to occur in the drain-gate gap, and sheet carrier density in the extrinsic region to the drain side decreases. However, it appears that this is not surface type degradation. As a result, drain resistance increases and drain current decreases, and this  $R_D$  degradation is not dependent on  $L_{GD}$ . This degradation is irreversible in that the device goes back to the previously degraded state

when reapplying the stress after a period of recovery. We have observed no significant recovery even after more than 300 days of rest.

As for the origin of this degradation, we have found that electric field plays the most important role, and vertical electric field seems to be more relevant to device degradation. On the other hand, current appears to only be a mild accelerating factor, but it is not clear whether the role of current is supplying hot electrons to the system or increasing temperature in the device.

Also, we have found that there exists a critical voltage beyond which degradation starts to happen, and this voltage is around 25 V in  $V_{DS}$ =0 condition. When a voltage higher than the critical voltage is applied, both drain and gate current start to degrade. This critical voltage appears to be 10~15 V higher in normal bias conditions, OFF state and high power state.

It is important to note that this overall behavior is reproducible across different devices, wafers, and processes that we have studied. However, it should still be confirmed in the future with more devices that are fabricated in different processes with different wafers.

62

-

# **Chapter 4. Degradation Mechanism**

#### 4.1. Introduction

In the previous chapter, we have experimentally studied the electrical degradation of GaN HEMTs. In a preliminary analysis, we have shown that degradation is related to trap generation and electron trapping. In this chapter, our experimental evidence that contradicts the prevailing hypothesis, hot electron involved mechanisms, will be discussed in more detail, and our hypothesis for electrical degradation of GaN HEMTs will be introduced. This hypothesis is supported by a set of additional experiments. Finally, based on our hypothesis, solutions to improve reliability will be discussed.

## 4.2. Inconsistency with Hot-electron Related Mechanisms

In section 1.3, hot-electron related hypotheses for degradation of GaN HEMTs were introduced. To summarize those mechanisms, hot electrons can gain enough energy to escape the channel and get trapped at the surface area between gate and drain [5]. These trapped electrons deplete channel carriers and degrade the device. Also, it has been postulated that hot electrons produce traps during bias stress [11].

However, several of our experiments are found not to be consistent with a model in which hot electrons are the main cause of electrical degradation. First, we have found that degradation in the OFF state is comparable to degradation in high power state in spite of the much less current that flows in the OFF state. Particularly remarkable is the  $V_{DS}=0$  state in which the role of hot electrons is most suppressed due to the absence of channel current and in some cases negligible reverse bias leakage current. Despite little effect of hot electrons, degradation in the  $V_{DS}=0$  state is sometimes more pronounced than in the high power state. Additionally, experiments on TLMs have revealed that they undergo negligible degradation in spite of a large current and relatively high lateral electric field. This result is remarkably different from GaAs and InP HEMT processes in which hot electrons produce significant damage to TLMs with a signature that is very similar to that of HEMTs [18, 19].

In our experimental results, hot electron mechanism alone cannot explain the degradation of GaN HEMT that we observe. Later in this chapter, we will see more examples of our experiments that cannot be understood by the hot-electron hypothesis. It then seems that another mechanism is involved to drive electrical degradation of GaN HEMT. This will be discussed in the following sections.

## 4.3. Piezoelectric Effect of GaN

III-N materials have large spontaneous polarization, and they are also strong piezoelectric materials. These properties are responsible for the high sheet carrier density n<sub>s</sub> that can be achieved in AlGaN/GaN heterostructures even without any intentional doping [22]. On top of spontaneous polarization charges, sheet charge is formed through piezoelectric effect at the interface between AlGaN and GaN and at the surface as AlGaN barrier is strained due to lattice mismatch with GaN channel layer. As a result, an internal electric field appears in the vertical direction. This electric field bends the band structure in the AlGaN barrier, which forms a two dimensional electron gas (2DEG) at the AlGaN/GaN interface as shown in Figure 4-1. The source of the 2DEG is believed to be surface donors because of charge neutrality [23]. Since the sheet piezoelectric polarization charge density is a function of

strain, the Al composition of the AlGaN barrier layer strongly determines the sheet carrier density in 2DEG. Also, the thickness of AlGaN barrier mildly affects  $n_s$  through the interplay among the Fermi level, occupied levels at the surface, and the conduction band edge of GaN channel [23]. As it can be seen, strain and elastic energy in the AlGaN barrier is inevitable to obtain channel carriers in GaN HEMTs.