## Parallel Integrated Receivers for Multiple Antenna Wireless LAN Systems

by

Lunal Khuon

B.S., Illinois Institute of Technology (1994) M.S., Illinois Institute of Technology (1998)

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering and Computer Science

#### at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

#### February 2007

© Massachusetts Institute of Technology 2007. All rights reserved.

Department of Electrical Engineering and Computer Science October 30, 2006 1 Charles G. Sodini Professor Thesis Supervisor Arthur C. Smith Chairman, Department Committee on Graduate Students

| MASSACHUSETTS INSTITUTE<br>OF TECHNOLOGY |  |

|------------------------------------------|--|

| APR 3 0 2007                             |  |

| LIBRARIES                                |  |

ARCHIVES

## Parallel Integrated Receivers for Multiple Antenna Wireless LAN Systems

by

Lunal Khuon

Submitted to the Department of Electrical Engineering and Computer Science on October 30, 2006, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

This thesis focuses on the design of power- and area-efficient parallel integrated receivers for multiple antenna wireless LAN systems. These receivers are part of an indoor parallel radio system that achieves 1 gigabit per second data rates and enables high bandwidth wireless communication between portable user devices and a high speed wired internet connection.

Since a critical aspect for efficiency is that an optimal number of transceivers be used to meet system requirements, this thesis first considers power dissipation and area consumption for parallel integrated transceivers. It develops parallel transceiver power dissipation and area consumption models that are functions of distance, data rate, and noise figure and incorporate the behavior of a multiple-input, multipleoutput channel and power dissipation and area consumption values for typical RF circuits. These models properly balance benefits of multiple antennas with drawbacks due to parallel radio overhead. Their application shows that the combined transceiver power dissipation can actually decrease with more antennas and also provides a circuits-based number of antennas upper bound that has not been established previously. The thesis then proposes a solution that applies multiple antenna signalto-noise ratio (SNR) gain at the receiver to reduce its power dissipation and area consumption. SNR gain trades noise figure for power- and area-efficient circuits. The implementation of a single chip 5.22-GHz area-efficient parallel receiver RFIC that shows practical application of these models, SNR gain, and area-efficient circuits is demonstrated. The context of this design comes from the Wireless Gigabit Local Area Network (WiGLAN). It's system characteristics such as a wide 150 MHz bandwidth and parallel radios uniquely determine a WiGLAN parallel receiver design.

Thesis Supervisor: Charles G. Sodini Title: Professor

To Monita and Alexander

#### Acknowledgments

I thank my advisor, Professor Charles Sodini. I cannot say enough how fortunate I feel that to have Charlie as my advisor. To say that he had guided my research is an tremendous understatement. Charlie has guided my growth as an individual. He has taught me to be independent, to rely on my intuition, and to take charge. Charlie was always there when I needed him. I will greatly miss Professor Charles Sodini.

I thank Professor Joel Dawson whose discussions lead me to discover the antennapower dissipation optimization which wonderfully ties all the thesis ideas together. I thank Professor Gregory Wornell for his unique perspectives. His insightful comments about wireless, whether theory, technology, or the business, are always a pleasure to listen to. Greg motivates me to think outside my comfort zone and gain a deeper appreciation for communication systems.

I thank my fellow student and research collaborator, Everest Huang, for all the brainstorming and aha! that we had together and for all the system explanations. Everest is always ready to explain just one more time! I also thank Everest for proofreading my many writings and presentations to make sure that I properly present the system and clearly explain the circuits.

I thank both the past and present students of the Sodini-Lee research group. In particular, I would like to acknowledge Don Hitko, Andy Wang, Anh Pham, Todd Sepke, Albert Jerng, and John Fiorenza. I thank Don for his pleasant demeanor and circuit expertise that made him the natural mentor to all new members of the group. I thank Andy for our numerous discussions and for the fond memories that include cooking at Ashdown, hiking the White Mountains, biking the suburbs of Boston, and running along the Charles River. I thank Anh for his quick decision making and fast arithmetic skills that made sure we would always know where we were going for dinner and what each person's fair share for the meal costs would be! Anh, with his super steady hands, also manually bonded my ICs to the PCBs. This saved me, a shaky lefty, from the almost impossible task of using a righthand-bias bonder. I thank Todd Sepke, the office motivator, for setting the vigorous pace for the group. Todd gives the definitive answer when it comes to circuit noise but, as ex-industry employees, we spend more time sharing "fond" memories of our previous working lives. I thank Albert Jerng, fellow dad, for sharing his parental knowledge and also for the many conversations we had on parenthood, engineering, and life in general. I thank John Fiorenza, the group's cultural ambassador, for all the left field conversations on the American culture and world history. If there's something to be known, engineering or otherwise, John is already there asking the questions.

I thank Rhonda Maynard for all her help. Rhonda handles all requests with the utmost care and efficiency and does everything with a smile! I thank Marilyn Pierce for taking care of many institution requirements on my behalf. Marilyn has been a lifesaver when it comes to making sure that I didn't miss any department requirements.

Finally, this work would not be possible without the love and support of my dearest wife, Monita. I thank Monita, with all my heart, for her patience, encouragement, understanding, and especially humor throughout the years at MIT. She has given me the little bursts of sunshine on even the cloudiest days. I thank Alex, our little baby, for bringing me so much happiness and love and providing that final push to wrap everything up. I thank my parents, Mr. and Mrs. Kandien and Sieklim Khuon, for their love and support. I thank my new parents, Mr. and Mrs. Bun Thong and Ly Keang Var, for their love and understanding. I thank Monida Var and Dr. Roger Fan for their quick wits and hilarous pokes that bring humor to life. Both Monida and Roger are passionate individuals that have the warmest hearts and the deepest love. It is truly wonderful to have them in my life. I thank my cousin and his wife, Timothy and Jenny Khuon, for always looking out for me while I was in Massachusetts. I've enjoyed the many South Shore and Costco shopping trips. Tim and Jenny's home was always open to me.

This thesis work was funded in part by the MARCO Focus Center for Circuit & System Solutions (C2S2) under contract number 2003-CT-888 and MIT Center for Integrated Circuits and Systems. Chip fabrication was provided by IBM Microelectronics.

# Contents

| 1 | Intr | oducti | on                                         | 23 |

|---|------|--------|--------------------------------------------|----|

|   | 1.1  | WiGL   | AN Parallel Receiver System                | 25 |

|   | 1.2  | Power  | and Area Models                            | 27 |

|   | 1.3  | SNR O  | Gain and Its Application                   | 28 |

|   | 1.4  | Minim  | al Power and Area Circuits                 | 30 |

|   | 1.5  | Area-e | efficient Parallel Receiver RFIC           | 30 |

|   | 1.6  | Thesis | o Outline                                  | 31 |

| 2 | Wi   | GLAN   | Parallel Receiver System                   | 33 |

|   | 2.1  | Wirele | ess Channel                                | 34 |

|   |      | 2.1.1  | Multipath Propagation and Fading           | 34 |

|   |      | 2.1.2  | WiGLAN System in a Fading Channel          | 38 |

|   | 2.2  | Digita | l IF Receiver                              | 40 |

|   |      | 2.2.1  | IQ Mismatch                                | 40 |

|   |      | 2.2.2  | Integrated Q-enhanced Image Filter         | 43 |

|   | 2.3  | Analog | g-to-Digital Converter                     | 48 |

|   | 2.4  | Multip | ole Antenna Digital Processor              | 50 |

|   |      | 2.4.1  | Orthogonal Frequency Division Multiplexing | 50 |

|   |      | 2.4.2  | Singular Value Decomposition               | 52 |

|   |      | 2.4.3  | Bit Error Rate Performance                 | 54 |

|   | 2.5  | Summ   | ary                                        | 58 |

| 3 | Pow | ver Dis | sipation and Area Consumption Models                                                                                          | 61         |

|---|-----|---------|-------------------------------------------------------------------------------------------------------------------------------|------------|

|   | 3.1 | Single  | Transceiver Models                                                                                                            | 61         |

|   | 3.2 | Paralle | el Transceiver Models                                                                                                         | 63         |

|   | 3.3 | Obser   | vations for Power Dissipation                                                                                                 | 58         |

|   |     | 3.3.1   | Number of Transceivers, $N \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                             | <u>5</u> 9 |

|   |     | 3.3.2   | Distance, $d$                                                                                                                 | 71         |

|   |     | 3.3.3   | Noise factor, $F$                                                                                                             | 74         |

|   | 3.4 | SNR (   | $Gain Applications \ldots $ | 76         |

|   |     | 3.4.1   | Optimal Number of Antennas                                                                                                    | 76         |

|   |     | 3.4.2   | Lower Operation Power                                                                                                         | 77         |

|   |     | 3.4.3   | Area Constraint                                                                                                               | 31         |

|   | 3.5 | Parall  | el Radio Models                                                                                                               | 32         |

|   | 3.6 | Coded   | Transmission                                                                                                                  | 87         |

|   | 3.7 | Summ    | ary                                                                                                                           | 90         |

| 4 | Mir | imal I  | Power and Area Circuits                                                                                                       | 91         |

|   | 4.1 | Power   | and Area for a Low Noise Amplifier                                                                                            | 91         |

|   | 4.2 | Variat  | ble Power Low Noise Amplifier                                                                                                 | 92         |

|   |     | 4.2.1   | Narrowband Cascode LNA                                                                                                        | 93         |

|   |     | 4.2.2   | LNA with Variable Bias                                                                                                        | 96         |

|   |     | 4.2.3   | LNA with Multiple Branches                                                                                                    | )1         |

|   | 4.3 | Area-e  | efficient Low Noise Amplifier                                                                                                 | )3         |

|   | 4.4 | Summ    | ary                                                                                                                           | )7         |

| 5 | An  | Area-l  | Efficient 5.22-GHz Parallel Receiver RFIC 10                                                                                  | )9         |

|   | 5.1 | Single  | WiGLAN Receiver                                                                                                               | )9         |

|   |     | 5.1.1   | Q-enhanced Notch Filter                                                                                                       | 10         |

|   |     | 5.1.2   |                                                                                                                               | 14         |

|   | 5.2 | Power   | -                                                                                                                             | 16         |

|   | 5.3 |         |                                                                                                                               | 25         |

|   |     | 5.3.1   |                                                                                                                               | 25         |

|   |     |         |                                                                                                                               | Î          |

|   |     | 5.3.2   | Test Setup                    | 128 |

|---|-----|---------|-------------------------------|-----|

|   |     | 5.3.3   | Measurement Results           | 132 |

|   |     | 5.3.4   | Q-enhanced Notch Filter Noise | 137 |

|   | 5.4 | Summ    | nary                          | 141 |

| 6 | Cor | nclusio | n and Future Work             | 143 |

|   | 6.1 | Thesis  | s Contributions               | 143 |

|   | 6.2 | Future  | e Research Directions         | 145 |

# List of Figures

| 1-1  | Wireless Gigabit Local Area Network                                                   | 26 |

|------|---------------------------------------------------------------------------------------|----|

| 1-2  | Application of SNR gain                                                               | 29 |

| 2-1  | Parallel receiver system                                                              | 33 |

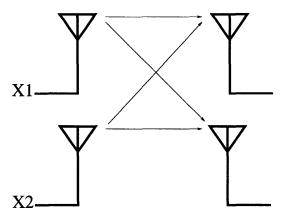

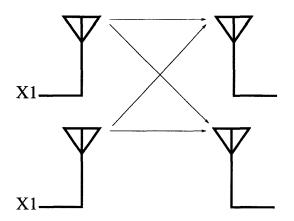

| 2-2  | Multi-path propagation and fading for two receivers                                   | 35 |

| 2-3  | Spatial multiplexing example using $2x2$ system with two separate data                |    |

|      | streams X1 and X2                                                                     | 37 |

| 2-4  | Spatial diversity example using $2x2$ system with redundant data stream               |    |

|      | X1                                                                                    | 37 |

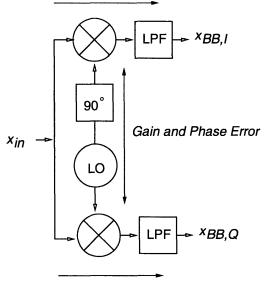

| 2-5  | Analog quadrature downconversion with gain and phase error paths $% \mathcal{A}$ .    | 41 |

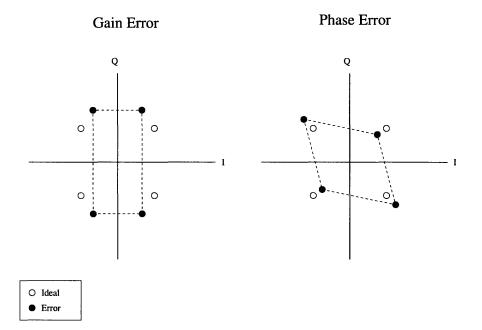

| 2-6  | Constellation plots demonstrating gain and phase errors for simple 4                  |    |

|      | QAM                                                                                   | 42 |

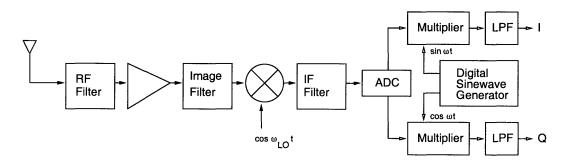

| 2-7  | A digital IF receiver and digital IQ retrieval.                                       | 42 |

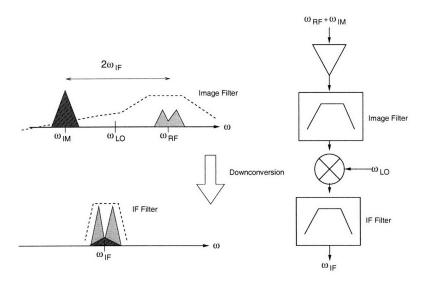

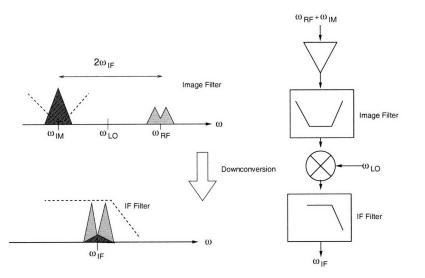

| 2-8  | Single conversion (heterodyne) receiver                                               | 44 |

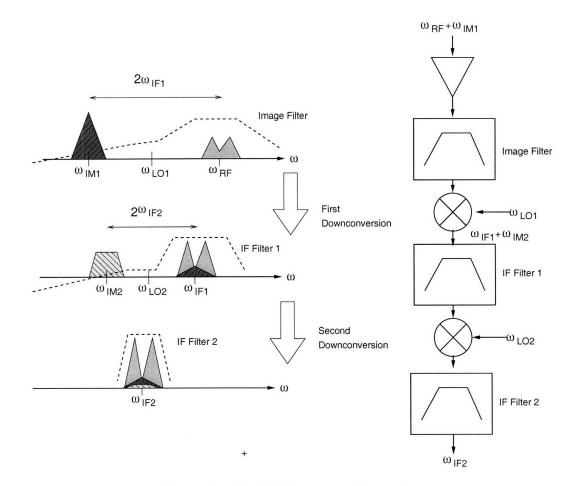

| 2-9  | Double downconversion receiver                                                        | 45 |

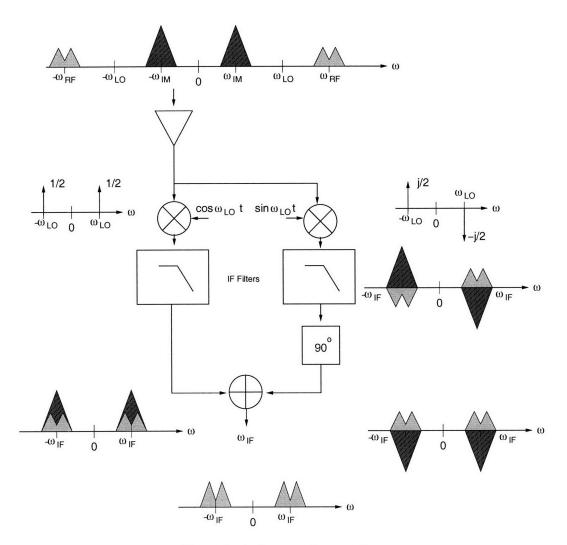

| 2-10 | Image reject receiver                                                                 | 46 |

| 2-11 | Receiver with Q-enhanced notch filter for image rejection                             | 48 |

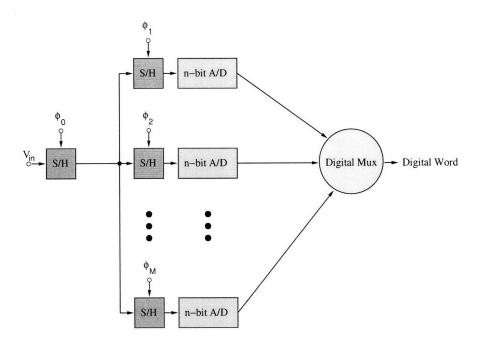

| 2-12 | An M-channel time-interleaved ADC array [47]                                          | 49 |

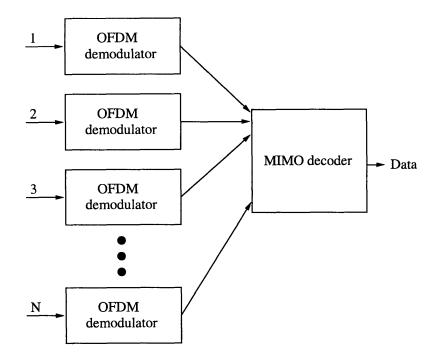

| 2-13 | Simplified diagram for WiGLAN receive digital processor                               | 50 |

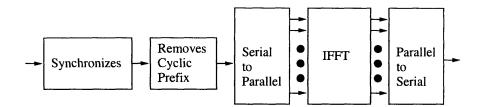

| 2-14 | An OFDM demodulator                                                                   | 51 |

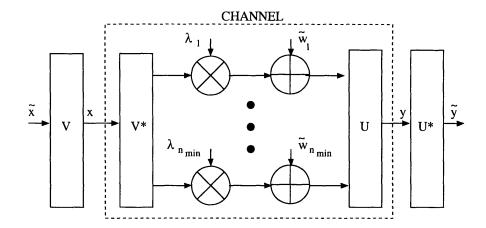

| 2-15 | Baseband SVD system with parallel subchannels [16]. Noise $\tilde{\mathbf{w}}$ is in- |    |

|      | cluded in the channel.                                                                | 53 |

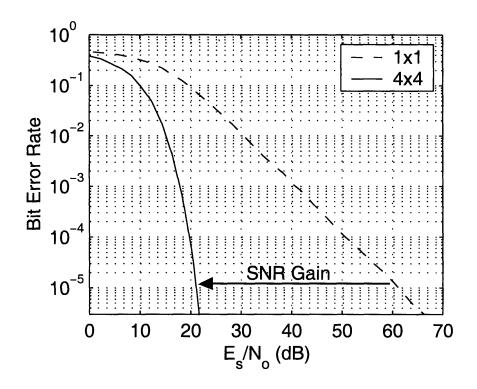

| 2-16 | Bit error rates versus signal-to-noise ratio in terms of signal energy $E_S$                                                  |    |

|------|-------------------------------------------------------------------------------------------------------------------------------|----|

|      | over noise variance $N_O$ for 1x1 and 4x4 uncoded systems in Rayleigh                                                         |    |

|      | channel with 64-QAM. 4x4 system uses maximum spatial diversity.                                                               |    |

|      | SNR gain is the difference in SNR between a 1x1 and any M transmit,                                                           |    |

|      | N receive (MxN) antenna for a specific bit error rate                                                                         | 56 |

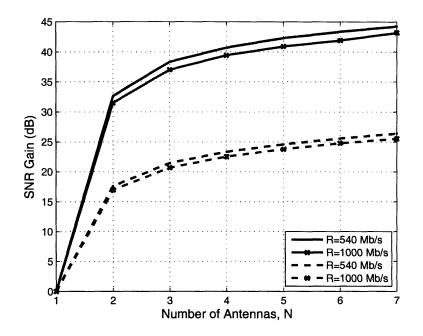

| 2-17 | SNR gain at BER= $10^{-5}$ (SOLID) and BER= $10^{-3}$ (DASH) for N an-                                                        |    |

|      | tennas and data rates 540 and 1000 Mb/s $\ \ldots \ $ | 59 |

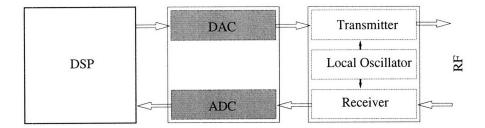

| 3-1  | Single radio frequency transceiver model.                                                                                     | 62 |

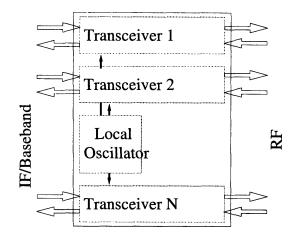

| 3-2  | Parallel radio frequency transceiver model. Each transceiver consists                                                         |    |

|      | of a transmitter and a receiver. All transceivers share one LO                                                                | 64 |

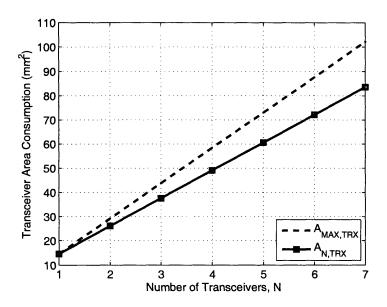

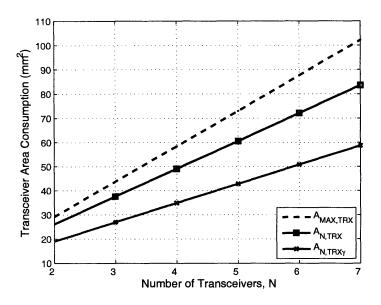

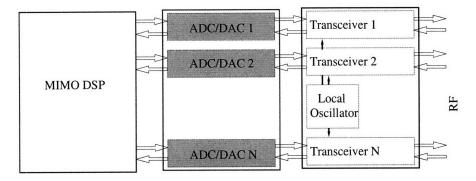

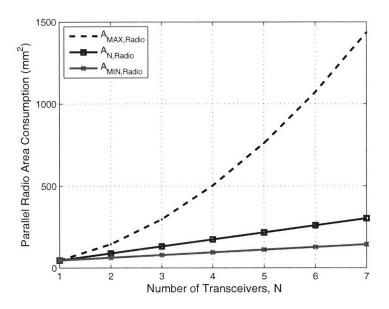

| 3-3  | Area consumption for parallel transceivers versus number of transceivers                                                      |    |

|      | $N$ without SNR gain applied. $A_{MAX,TRX}$ represents the situation                                                          |    |

|      | where the LO is not shared.                                                                                                   | 65 |

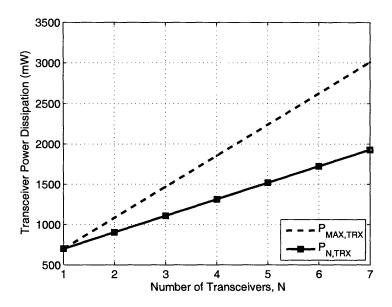

| 3-4  | Power dissipation for parallel transceivers versus number of transceivers                                                     |    |

|      | N without SNR gain applied. $P_{MAX,TRX}$ represents the situation where                                                      |    |

|      | the LO is not shared. For both $P_{N,TRX}$ and $P_{MAX,TRX}$ , total RF trans-                                                |    |

|      | mit signal power is kept constant for all $N$ transceiver systems                                                             | 66 |

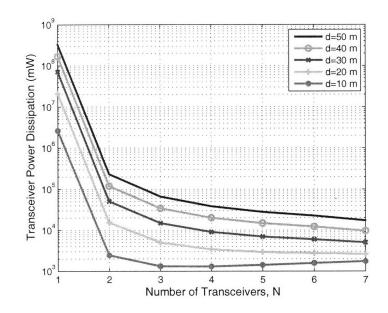

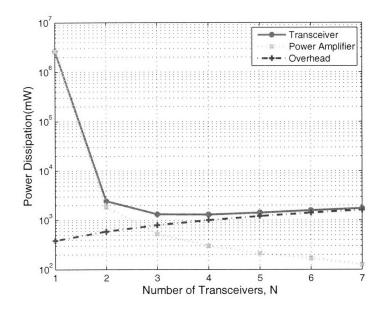

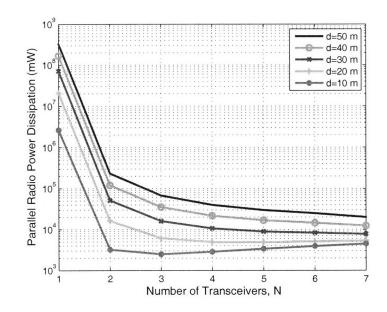

| 3-5  | Power dissipation for parallel transceivers versus number of transceivers                                                     |    |

|      | N for various distances and applying SNR gain. NF is kept constant                                                            |    |

|      | at 8 dB                                                                                                                       | 69 |

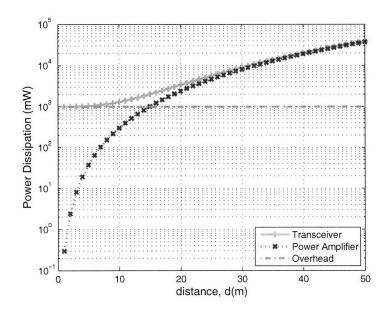

| 3-6  | Power dissipation for $d=10$ m. Minimum transceiver power dissipa-                                                            |    |

|      | tion occurs between $N=3$ and 4. Further increasing N will increase                                                           |    |

|      | transceiver power dissipation since overhead power dissipation has be-                                                        |    |

|      | come greater than PA power dissipation.                                                                                       | 70 |

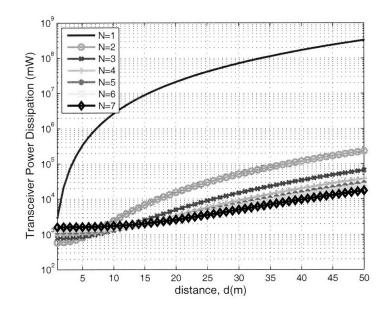

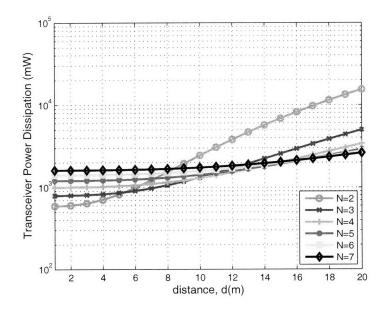

| 3-7  | Power dissipation for parallel transceiver systems versus distance $d$ . NF                                                   |    |

|      | is kept constant at 8 dB. A single transceiver system requires excessive                                                      |    |

|      | transceiver power dissipation to achieve both $BER=10^{-5}$ and 1 Gb/s.                                                       |    |

|      | Figs. 3-8 and 3-9 provide zoom-in views for this figure.                                                                      | 71 |

|      |                                                                                                                               |    |

| 3-8 |                                                                                                                                                                                                                                                                                                                                                                                                       |    |

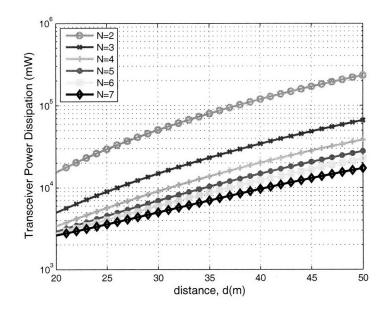

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | (except a single transceiver system) at short distances. Bottom envelope of plots gives $N$ transceiver system with lowest power dissipation.                                                                                                                                                                                                                                                         | 72 |

| 3-9 | Zoom in view no.2: Power dissipation for parallel transceiver systems (except a single transceiver system) at long distances. For long transmission distance, using the largest $N$ possible minimizes power dissipation for parallel transceivers.                                                                                                                                                   | 73 |

| 3-1 | 0 Power dissipation for $N=4$ transceivers versus distance $d$ . NF is kept constant at 8 dB. Power dissipation is dominated by overhead electronics at short distances and PA at long distances.                                                                                                                                                                                                     | 73 |

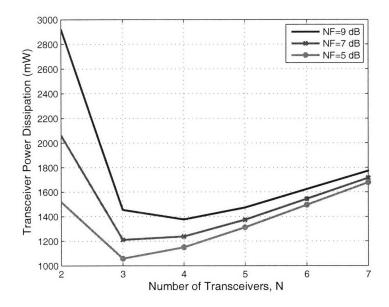

| 3-1 | 1 Power dissipation for parallel transceivers versus number of transceivers $N$ at various noise figure (NF) values (note: power is plotted on linear scale). Distance $d$ is kept constant at 10 m. Increasing NF increases power dissipation for parallel transceivers and also shifts minimum power dissipation to larger $N$ transceivers. That is, $N=3$ for NF=5 dB shifts to $N=4$ for NF=9 dB | 74 |

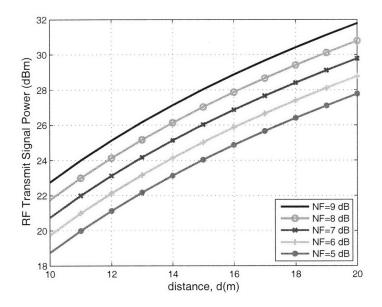

| 3-1 | 2 RF transmit signal power versus distance d for various NF values.<br>Number of transceivers N is kept constant at 4. Transmit signal power<br>increase 1 dB per 1 dB increase in noise figure                                                                                                                                                                                                       | 75 |

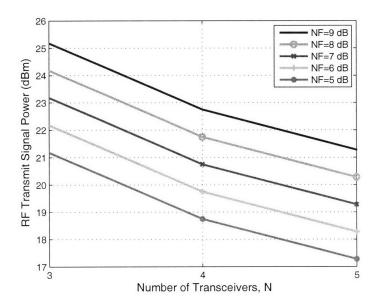

| 3-1 | 3 RF transmit signal power versus number of transceivers $N$ for various NF values. Distance $d$ is kept constant at 10 m. Transmit signal power increase 1 dB power per 1 dB increase in noise figure                                                                                                                                                                                                | 75 |

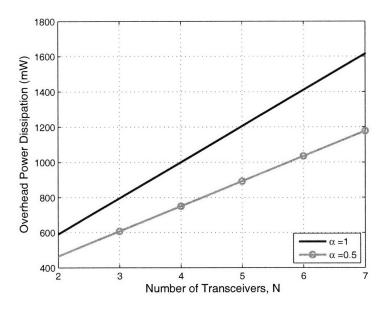

| 3-1 | 4 Overhead power dissipation for parallel transceivers versus number of transceivers $N$ with $\alpha=1$ and $\alpha=0.5$ . Reducing receiver operating power is valid for $N > 1$ when there is SNR gain available. Impact for a smaller $\alpha$ on overhead power dissipation increases with more transceivers.                                                                                    | 79 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                       |    |

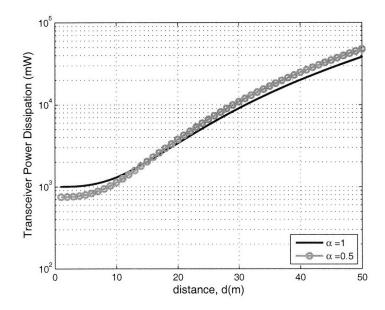

| 3-15 Power dissipation for $N=4$ transceivers versus distance $d$ with $\alpha=1$<br>and $\alpha=0.5$ . Corresponding NF values are 8 dB for $\alpha=1$ and 9 dB<br>for $\alpha=0.5$ . Reducing receiver operating power is best applied when                                                                                                                                                                                                                                                                                                                                  |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| overhead power dissipation is dominant. $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 79 |

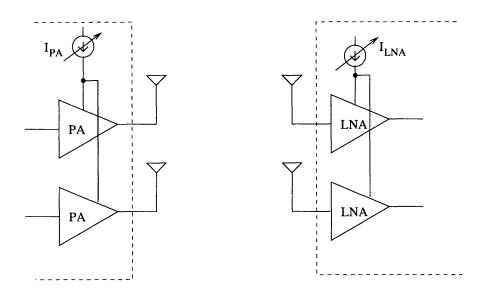

| 3-16 A variable power 2x2 system with variability applied to the PAs and LNAs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 80 |

| 3-17 Area consumption for parallel transceivers versus number of transceivers $N$ . Trading SNR gain for reduced area consumption is valid for $N > 1$ when there is SNR gain available. $A_{MAX,TRX}$ , $A_{N,TRX}$ , and $A_{N,TRX\gamma}$ represent area consumption for parallel transceivers with no LO sharing, no SNR gain ( $\gamma$ =1), and SNR gain trade for area (arbitrary $\gamma = \frac{3}{8}$ ), respectively. Unlike power dissipation for parallel transceivers, area consumption for parallel transceivers always increases with additional transceivers. | 82 |

| 3-18 A single radio model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 83 |

| 3-19 Parallel radio model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 83 |

| 3-20 Area consumption for parallel radios versus number of transceivers $N$ without SNR gain applied. An increase in area consumption for a DSP is bounded by $N^2$ ( $A_{MAX,Radio}$ ) and unity ( $A_{MIN,Radio}$ ) but is likely to be closer to $N$ ( $A_{N,Radio}$ )                                                                                                                                                                                                                                                                                                      | 86 |

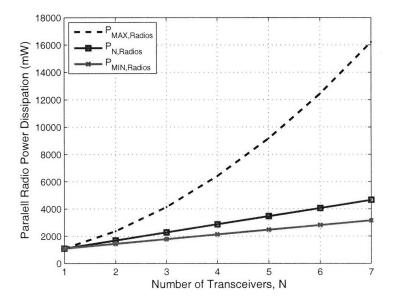

| 3-21 Power dissipation for parallel radios versus number of transceivers $N$ without SNR gain applied. An increase in power dissipation for DSP is bounded by $N^2$ ( $P_{MAX,Radio}$ ) and unity ( $P_{MIN,Radio}$ ) but is likely to be closer to $N$ ( $P_{N,Radio}$ )                                                                                                                                                                                                                                                                                                      | 86 |

| 3-22 Power dissipation for parallel radios versus number of transceivers $N$ for various distances $d$ . Plots assume SNR gain application, $\kappa = N$ , and NF=8 dB for 1 Gb/s and $10^{-5}$ BER                                                                                                                                                                                                                                                                                                                                                                            | 87 |

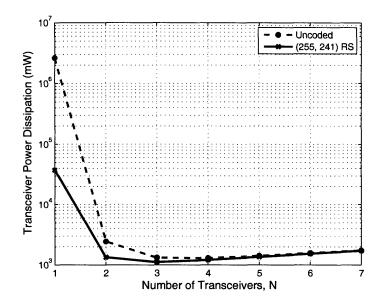

| 3-23 | Power dissipation for parallel transceivers versus number of transceivers $N$ for uncoded and (255.241) BS coded transmissions. Transmission |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | N for uncoded and (255,241) RS coded transmissions. Transmission                                                                             |    |

|      | distance is 10 m. Receivers have 8 dB NF and the systems achieve a 1 $Ch (r + h) = 10^{-5}$ DED                                              | 00 |

|      | Gb/s data rate with $10^{-5}$ BER                                                                                                            | 89 |

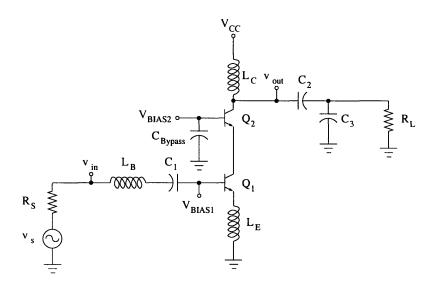

| 4-1  | Conventional single-ended narrowband cascode low noise amplifier. In-                                                                        |    |

|      | put impedance is matched to source impedance $R_S$ and output impedance                                                                      |    |

|      | is matched to load $R_L$ .                                                                                                                   | 93 |

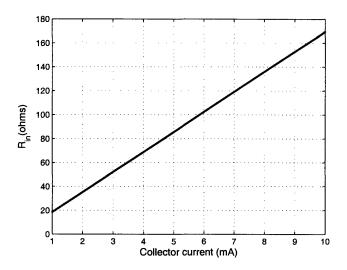

| 4-2  | Real input impedance $R_{in}$ as a function of collector current for a 5.22-                                                                 |    |

|      | GHz narrowband cascode LNA. Increasing current increases $g_m$ which                                                                         |    |

|      | then increases $R_{in}$ . Input values are $L_B=1.31$ nH and $L_E=0.960$ nH                                                                  |    |

|      | for a transistor with $r_{b1}=1.69 \ \Omega.$                                                                                                | 96 |

| 4-3  | $S_{11}$ as a function of collector current for a 5.22-GHz narrowband cas-                                                                   |    |

|      | code LNA with $R_s=50 \ \Omega$ . Plot assumes an input impedance match at                                                                   |    |

|      | resonance such that $S_{11}$ consists only of $R_S$ and $R_{in}$ . To keep $S_{11}$ less                                                     |    |

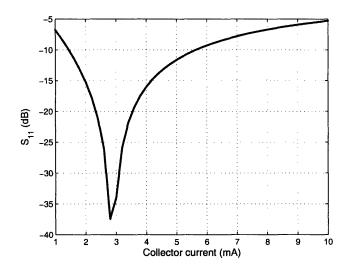

|      | than -10 dB limits collector current values to between 1.4 and 5.6 mA.                                                                       | 97 |

| 4-4  | Narrowband cascode LNA's transducer power gain versus collector cur-                                                                         |    |

|      | rent. Increasing current increases $g_m$ which then increases gain. Design                                                                   |    |

|      | values are as follow: $L_B = 1.31$ nH and $L_C = 0.960$ nH with $Q_{LC} = 20$ .                                                              |    |

|      | Source impedance $R_S$ is taken to be 50 $\Omega$ and operation frequency is                                                                 |    |

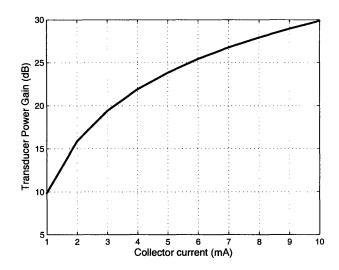

|      | at 5.22 GHz                                                                                                                                  | 98 |

| 4-5  | Narrowband cascode LNA's noise figure versus collector current. Col-                                                                         |    |

|      | lector shot noises increases noise figure at low current while base shot                                                                     |    |

|      | noise increases noise figure at high current. In addition to values given                                                                    |    |

|      | for $G_T$ plot, transistor parameters $r_b$ is 1.69 $\Omega$ , $C_{\pi 1}$ is 588 fF, $\beta_O$ is 100.                                      |    |

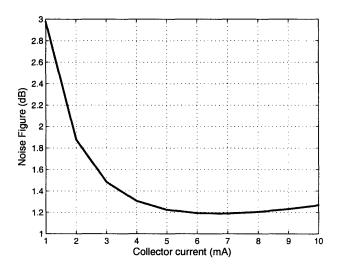

|      | To match input, emitter inductor $L_E$ is 0.25 nH                                                                                            | 98 |

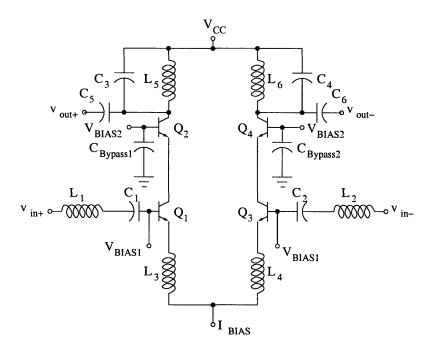

| 4-6  | Differential cascode narrowband low noise amplifier with input control                                                                       |    |

|      | current $I_{BIAS}$ [57]. Lowering $I_{BIAS}$ lowers amplifier's power consump-                                                               |    |

|      | tion but increases noise figure.                                                                                                             | 99 |

|      |                                                                                                                                              |    |

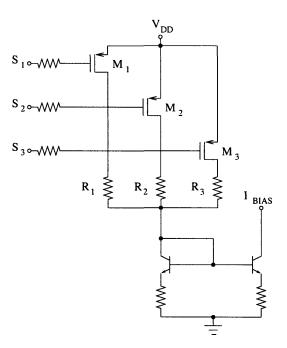

| 4-7  | Externally programmable bias current network [57]. Three-bit control                                  |     |

|------|-------------------------------------------------------------------------------------------------------|-----|

|      | $S_1, S_2, S_3$ selects a desired combination of resistors $R_1, R_2$ , and $R_3$ to                  |     |

|      | set the reference current.                                                                            | 100 |

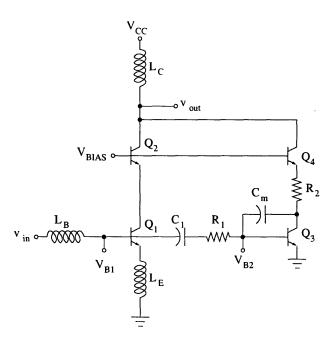

| 4-8  | VPLNA with low and high gain branches [58]. Applying either VB1                                       |     |

|      | or VB2 selects either branch for use.                                                                 | 102 |

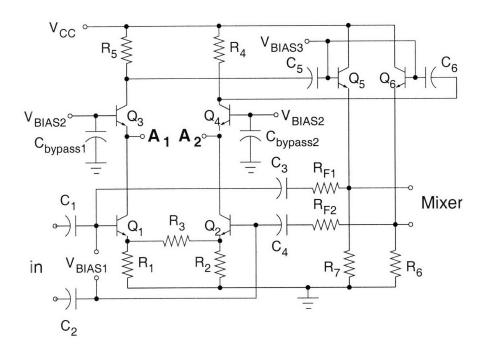

| 4-9  | Area-efficient low noise amplifier. LNA is an area-efficient shunt-series                             |     |

|      | amplifier with additional cascode and buffer circuits. Resistors $R_{F1}$                             |     |

|      | and $R_{F2}$ provide input impedance matching                                                         | 104 |

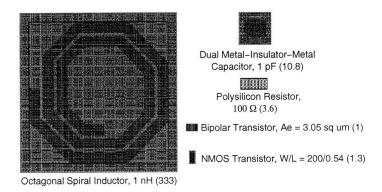

| 4-10 | On-chip passive and active components. The sizes in parentheses are                                   |     |

|      | relative to the shown bipolar transistor that has an emitter area of $3.05$                           |     |

|      | $\mu { m m}$ and occupies 172 $\mu { m m}^2$ of chip area.                                            | 104 |

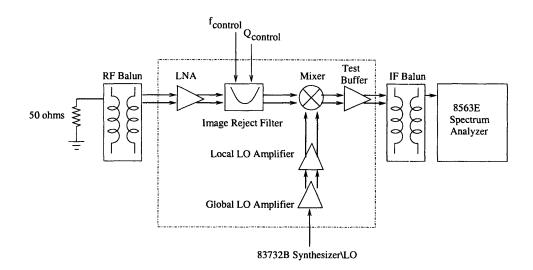

| 5-1  | A single WiGLAN RF receiver. Differential receiver consists of an                                     |     |

|      | LNA, Q-enhanced image reject filter, mixer, and local oscillator am-                                  |     |

|      | plifier. Integrated filter requires both frequency and Q tuning control                               |     |

|      | signals to set its center frequency and rejection.                                                    | 110 |

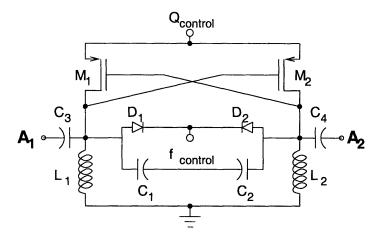

| 5-2  | 3rd order Q-enhanced image reject notch filter                                                        | 111 |

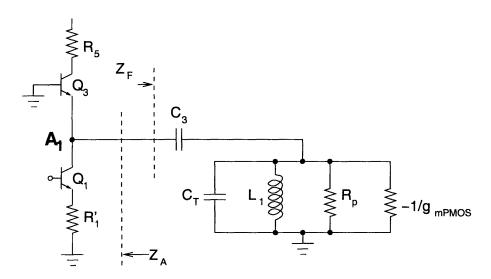

| 5-3  | Equivalent circuit for Q-enhanced image reject notch filter at point A1.                              | 112 |

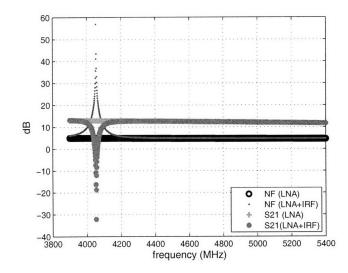

| 5-4  | Simulated noise figure and gain versus frequency for an area-efficient                                |     |

|      | LNA with and without Q-enhanced image reject notch filter. Noise                                      |     |

|      | figure and gain remain constant at 4.6 dB and 12 dB, respectively                                     |     |

|      | over frequency except at image frequency where a notch in the gain                                    |     |

|      | response produces a spike in noise figure. This spike "hides" true filter                             |     |

|      | noise contributions at the image band. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 113 |

| 5-5  | Area-efficient folded BiCMOS mixer. Area-efficiency comes from using                                  |     |

|      | RC as opposed to LC circuits at mixer's output. Folded design allows                                  |     |

|      | separate bias currents for RF transconductor and switching core, which                                |     |

|      | maximizes both transconductance and voltage swing                                                     | 114 |

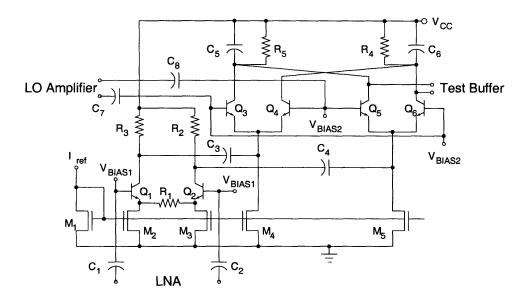

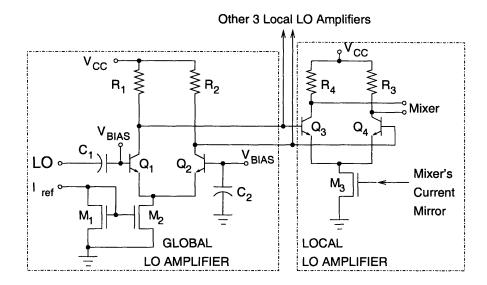

| 5-6  | Global and local LO amplifiers. Two stage amplification allows a low                                  |     |

|      | power LO signal distribution.                                                                         | 115 |

.

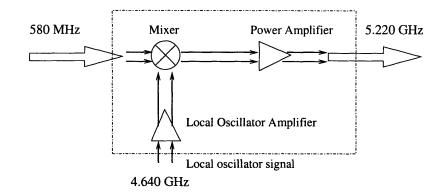

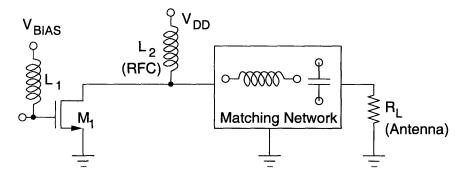

| 5-7  | A single WiGLAN RF transmitter. It consists of a mixer, local LO                            |     |

|------|---------------------------------------------------------------------------------------------|-----|

|      | amplifier, and power amplifier                                                              | 117 |

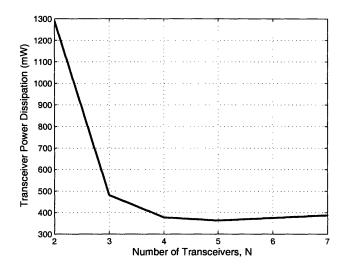

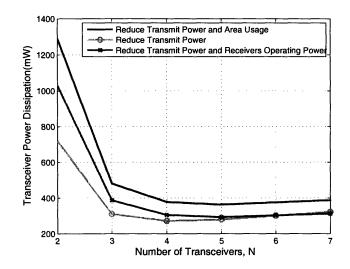

| 5-8  | Power dissipation for parallel transceivers that use area-efficient paral-                  |     |

|      | lel receivers. Minimum power of 363 mW occurs at five transceivers.                         |     |

|      | Using four transceivers consume 377 mW. Note that plot does not ac-                         |     |

|      | count for LO power dissipation since it is not necessary when seeking                       |     |

|      | <i>N</i>                                                                                    | 120 |

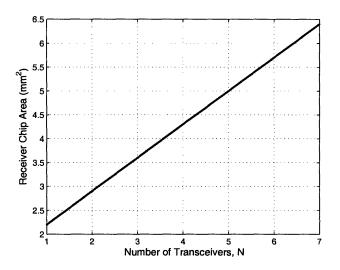

| 5-9  | Area consumption for a<br>rea-efficient parallel receivers. At $N=4$ , the                  |     |

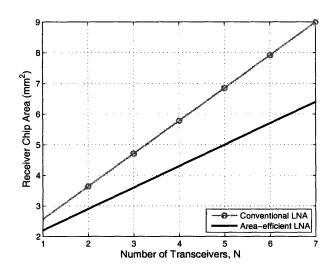

|      | receivers consume $4.3 \text{ mm}^2$ .                                                      | 121 |

| 5-10 | Floorplan for parallel receiver RFIC. Four receivers and support cir-                       |     |

|      | cuits consume 4.3 mm <sup>2</sup> . A receiver at each corner consumes $0.7 \text{ mm}^2$ . |     |

|      | It is expected that shared circuits will occupy $1.5 \text{ mm}^2$ in the center            |     |

|      | area                                                                                        | 122 |

| 5-11 | Area consumption for parallel receivers that use conventional and area-                     |     |

|      | efficient LNA. At $N=4$ , receivers that use the conventional LNA con-                      |     |

|      | sume an additional 1.5 $\mathrm{mm^2}$ over receivers that use an area-efficient            |     |

|      | LNA                                                                                         | 123 |

| 5-12 | Transceiver power dissipation for parallel receivers that use three dif-                    |     |

|      | ferent LNA approaches. An area-efficient LNA approach applies SNR                           |     |

|      | gain to reduce transmit power and area usage. A conventional LNA                            |     |

|      | approach applies SNR gain to reduce transmit power only and a vari-                         |     |

|      | able or low power LNA approach applies SNR gain to reduce transmit                          |     |

|      | power and receiver operating power                                                          | 124 |

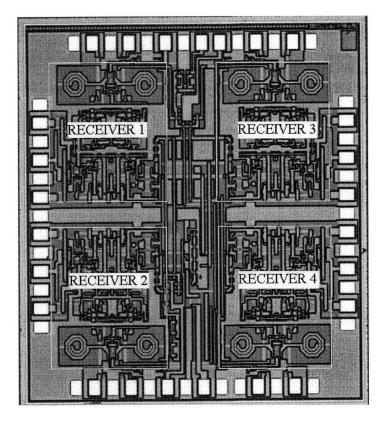

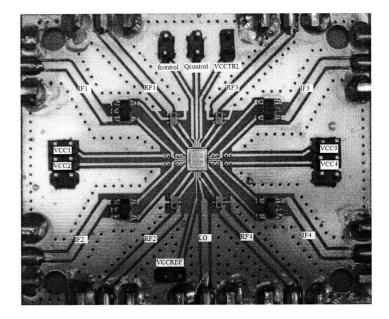

| 5-13 | WiGLAN parallel receiver RFIC die photo. Chip area is 5.65 $\rm mm^2$                       |     |

|      | (active area=4 mm²). Process is IBM 0.18 $\mu \mathrm{m}$ SiGe BiCMOS 7WL                   | 126 |

| 5-14 | Test printed circuit board (PCB) with direct die attachment at center.                      | 127 |

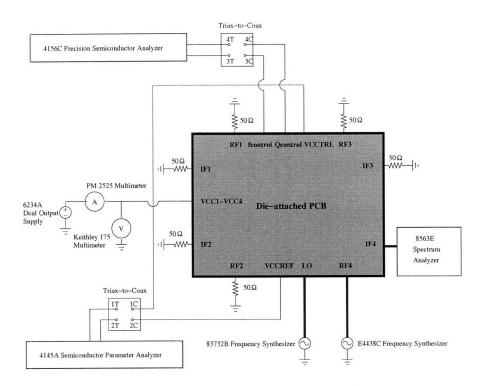

| 5-15 | Test setup for receiver power dissipation and gain measurements                             | 128 |

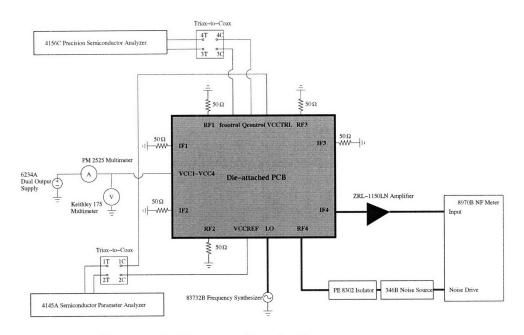

| 5-16 | Test setup for noise figure measurements                                                    | 129 |

| 5-17 | Filter frequency range measurement setup for a receiver                                     | 130 |

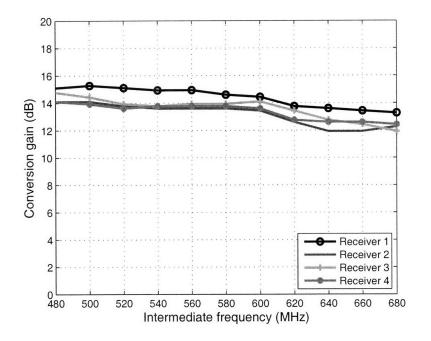

| 5-18 | Pass band conversion gains                                                                  | 133 |

|      |                                                                                             |     |

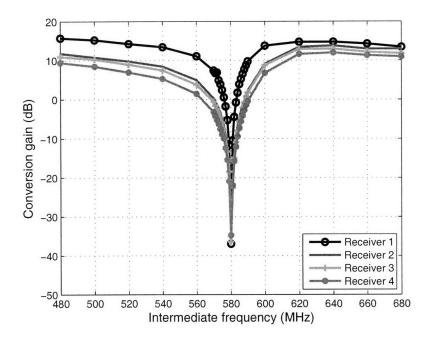

| 5-19 | Image frequency conversion gains                                                  | 134 |

|------|-----------------------------------------------------------------------------------|-----|

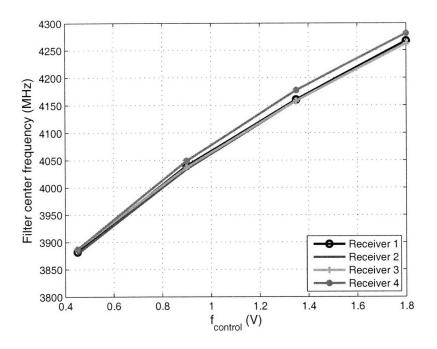

| 5-20 | Notch filters' center frequency tuning ranges                                     | 135 |

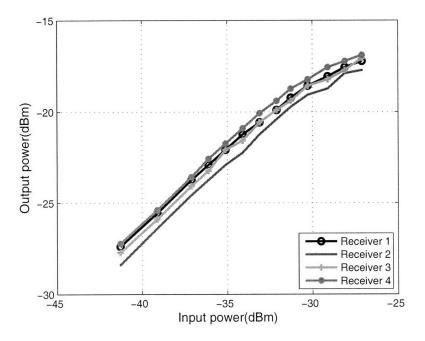

| 5-21 | Output powers versus swept input powers for 5.22-GHz RF input sig-                |     |

|      | nal. Input 1 dB compression point occurs at approximately -33 dBm.                | 135 |

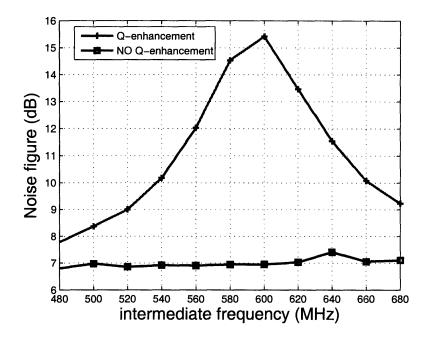

| 5-22 | Receiver noise figure with and without Q-enhancement applied for im-              |     |

|      | age reject notch filter. Q-enhancement produces a large peak in noise             |     |

|      | figure near the center frequency for the notch filter. $\ldots$ $\ldots$ $\ldots$ | 136 |

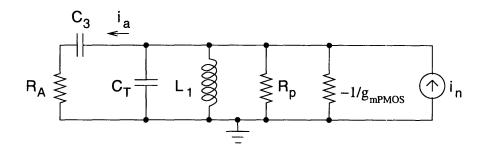

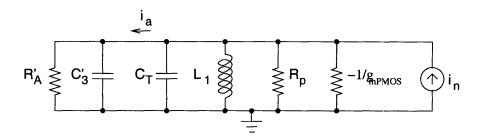

| 5-23 | Circuit for noise analysis at desired pass band frequency                         | 137 |

| 5-24 | Circuit for noise analysis at image frequency                                     | 138 |

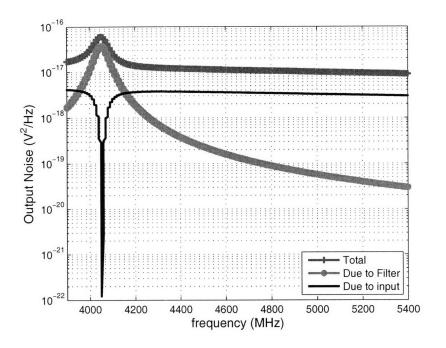

| 5-25 | Simulated output noise of LNA with Q-enhanced image reject notch                  |     |

|      | filter. Note that the output is plotted on a logarithmic scale                    | 140 |

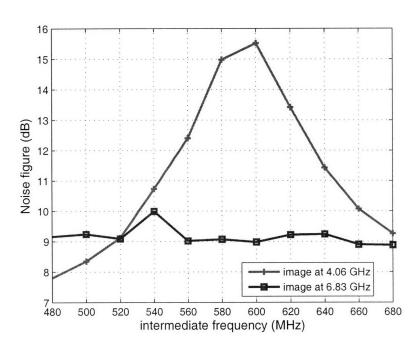

| 5-26 | Measured receiver noise figures at an intermediate frequency for notch            |     |

|      | frequency at 4.06 GHz and images centered at 4.06 GHz and 6.83 GHz.               | 140 |

| 6-1  | General power amplifier model [65]                                                | 146 |

# List of Tables

| 1.1 | Percent power dissipation for a typical 802.11a radio $[7, 8, 9, 10]$             | 23 |

|-----|-----------------------------------------------------------------------------------|----|

| 1.2 | Percent area consumption for a typical 802.11a radio $[7, 8, 9, 10]$              | 24 |

| 1.3 | Intel SRAM test chips. The cell size trend shows roughly a $50\%$ size            |    |

|     | decrease every 2 years [11]                                                       | 24 |

| 2.1 | $E_S/N_O$ values in dB for BER=10 <sup>-3</sup> , uncoded, and with adaptive mod- |    |

|     | ulation [17]                                                                      | 57 |

| 2.2 | $E_S/N_O$ values in dB for BER=10 <sup>-5</sup> , uncoded, and with adaptive mod- |    |

|     | ulation [17]                                                                      | 57 |

| 3.1 | Wireless LAN RF transceiver active area consumption and reported                  |    |

|     | power dissipation. Values are estimates based on published results for            |    |

|     | a 802.11a WLAN chipset [7, 8]                                                     | 64 |

| 3.2 | Additional model inputs not including $(E_S/N_O)_N$ and previously given          |    |

|     | transmitter, receiver, and LO power dissipation values                            | 68 |

| 3.3 | Choosing $N$ to minimize power dissipation for parallel transceivers              |    |

|     | based on maximum transmission distance for NxN systems and Figs. 3-               |    |

|     | 7, 3-8, and 3-9                                                                   | 77 |

| 3.4 | Wireless LAN baseband and MAC processor area consumption and                      |    |

|     | power dissipation. Values are taken from published results for a $802.11$         |    |

|     | a WLAN chipset [10]                                                               | 85 |

| 3.5 | Simulated $E_S/N_O$ values in dB for uncoded and (255,241) RS code                |    |

|     | to achieve 1 Gb/s data rate with $BER=10^{-5}$ and applying adaptive              |    |

|     | modulation [17]                                                                   | 88 |

|     |                                                                                   |    |

| 4.1 | Simulated values of bias current, noise figure, gain, and input for a 5.2- |     |

|-----|----------------------------------------------------------------------------|-----|

|     | GHz differential CMOS LNA with all possible combinations of control        |     |

|     | bits $S_1$ , $S_2$ , and $S_3$ [57]                                        | 101 |

| 4.2 | Reported measurement results for current consumption, noise figure,        |     |

|     | gain, and $S_{11}$ at high and low gain branches [58]                      | 103 |

| 4.3 | Simulated results for differential narrowband and area-efficient LNA .     | 106 |

| 5.1 | RF circuits power dissipation for WiGLAN receiver and transmitter.         |     |

|     | Power dissipation for receiver circuits are simulation results. Power      |     |

|     | dissipation for transmitter circuits assume that the transmitter uses a    |     |

|     | mixer and local LO amplifier with similar power dissipation to those       |     |

|     | of the receiver. Power amplifier power dissipation is absent as it is      |     |

|     | already part of the transceiver power dissipation model                    | 118 |

| 5.2 | Additional inputs for WiGLAN parallel transceiver power dissipation        |     |

|     | $model  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $   | 119 |

| 5.3 | Area consumptions for receiver and shared circuits. The shared circuits    |     |

|     | include LO, bias, and distribution circuits. Values are estimates based    |     |

|     | on floorplanning and initial layout.                                       | 120 |

| 5.4 | Estimated power dissipation and area consumption for 4 parallel re-        |     |

|     | ceivers that use either an area-efficient, conventional, or variable power |     |

|     | LNA. LNA power dissipation are simulated values.                           | 123 |

| 5.5 | Setup values corresponding to previous test diagram for receiver num-      |     |

|     | ber 4                                                                      | 131 |

| 5.6 | Chip Summary                                                               | 132 |

# Chapter 1

## Introduction

Investigations into the benefits of parallel radios, especially in the case of multiple transmit, multiple receive systems for broadband communications, tie heavily to a characterization of a multiple-input-multiple-output (MIMO) channel [1] and developments of space-time processing [2, 3, 4] and smart antennas [5, 6]. As these endeavors begin to mature, a next step considers the associated radio frequency (RF) hardware designs [2].

To begin, it is necessary to understand that power dissipation and area consumption for transceiver circuits are important concerns for multiple antenna systems. Table 1.1 lists percent power dissipation for an integrated 802.11a single radio chipset [7, 8, 9, 10]. The table shows that a transmitter and local oscillator consumes 75% of total radio power dissipation in transmit mode while a receiver and local oscillator consumes nearly 50% of total radio power dissipation in receive mode. The radio uses a transmitter that consists of programmable gain amplifiers, a pair

| Transmit Mode:              |      | Receive Mode:               |      |  |

|-----------------------------|------|-----------------------------|------|--|

| Transmitter                 | 61%  | Receiver                    | 28%  |  |

| Local Oscillator            | 14%  | Local Oscillator            | 20%  |  |

| Digital-to-Analog Converter | 5%   | Analog-to-Digital Converter | 24%  |  |

| Digital Signal Processor    | 20%  | Digital Signal Processor    | 27%  |  |

| Total                       | 100% | Total                       | 100% |  |

Table 1.1: Percent power dissipation for a typical 802.11a radio [7, 8, 9, 10]

| Transmitter                 | 10%  |

|-----------------------------|------|

| Receiver                    | 15%  |

| Local Oscillator            | 7%   |

| Analog-to-Digital Converter | 5%   |

| Digital-to-Analog Converter | 5%   |

| Digital Signal Processor    | 58%  |

| Total                       | 100% |

Table 1.2: Percent area consumption for a typical 802.11a radio [7, 8, 9, 10]

| Process(nm) | Cell Size( $\mu m^2$ ) | Memory Size(Mbit) | Chip $Size(mm^2)$ | Release     |

|-------------|------------------------|-------------------|-------------------|-------------|

| 130         | 2.45                   | 18                | 103               | March 00    |

| 90          | 1.0                    | 50                | 109               | February 02 |

| 65          | 0.57                   | 70                | 110               | April 04    |

| 45          | 0.346                  | 153               | 119               | January 06  |

Table 1.3: Intel SRAM test chips. The cell size trend shows roughly a 50% size decrease every 2 years [11].

of intermediate frequency image-reject mixers, radio frequency mixer, and a power amplifier and a receiver that consists of a low noise amplifier, radio frequency mixer, intermediate frequency quadrature mixers, and programmable gain amplifiers. These circuits along with the local oscillator form a transceiver and their power dissipation represent significant portion of total radio power dissipation. If an approximation for a multiple antenna system represents some multiple of these percentages, a first step to reduce radio power dissipation for multiple antenna systems then begins with minimization of transceiver power dissipation.

Table 1.2 lists percent area consumption for the same 802.11a single radio. Unlike percent power dissipation, the digital signal processor consumes the most chip area at 58%. A transmitter, receiver, and local oscillator together occupy 32% the total area. In terms of area, it seems that multiple antenna systems should focus on the processor. To do so, however, neglects recent trends in technology scaling that shrink digital circuits and increase transistor density. As an example, Table 1.3 lists physical cell, memory, and chip sizes for Intel's SRAM test chips that are forerunners for their processors [11]. The data shows roughly a 50% cell size decrease every 2 years. Given a recent release for a 153 Mbit SRAM that uses 0.346  $\mu$ m<sup>2</sup> cell and has more than one billion transistors, it is likely that processor area is not a cost driver for future multiple antenna systems [12].

The situation is quite different for transceiver circuits. A technology roadmap observes that obstacles to future passive integration are roadblocks to successful RF, analog, and mixed signal implementations [13]. A key point is that large value inductors and capacitors, as energy storage devices, require large area to achieve a high quality factor, or Q and therefore circuits that use them are inherently large [14]. Simply put, this implies that technology scaling does not shrink RF circuits. Therefore, similar to power dissipation, a significant step for multiple antenna systems minimizes area consumption for transceiver circuits.

This thesis takes steps to reduce power dissipation and area consumption for RF circuits in multiple antenna systems. Specifically, it investigates the design of powerand area-efficient parallel integrated receivers for a gigabit wireless LAN system. Since this design exploits the parallelism of the radio channel, the implementation allows the development of design methods specific to parallel radios and incorporates considerations for single chip integration and radio system design. This thesis proposes a system solution that utilizes multiple antenna signal-to-noise ratio (SNR) gain to minimize power dissipation and area consumption for parallel integrated receivers. To illustrate its application, it first develops power dissipation and area consumption models that incorporate SNR gain. The thesis also introduces circuits that trade SNR gain for lower power dissipation and area consumption. In the sections to follow, a brief overview of the main ideas of the thesis is given. More detailed discussions are found in the respective chapters.

## 1.1 WiGLAN Parallel Receiver System

The Wireless Gigabit Local Area Network (WiGLAN) is a current research project at the Massachusetts Institute of Technology that explores various techniques and approaches at the system and circuit levels that would allow indoor wireless communication at data rates of 1 gigabit per second [15]. In particular, it uses parallel

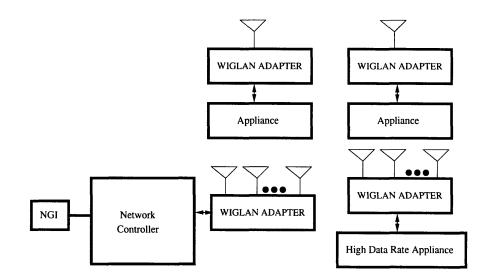

Figure 1-1: Wireless Gigabit Local Area Network

radios, 150 MHz bandwidth at 5.22 GHz, Orthogonal Frequency Division Multiplexing (OFDM), and adaptive modulation. WiGLAN's parallel radios exploit spatially independent multi-path signal propagation to relax necessary SNR for low bit error rates. OFDM allows more efficient use of a wide bandwidth while adaptive modulation seeks to efficiently use a time-varying fading channel.

As shown in Fig. 1-1, WiGLAN consists of a network controller that is connected by wire to the Next Generation Internet (NGI). The controller communicates wirelessly with various appliances that exist throughout the indoor home or office environment using an attached multiple antenna WiGLAN adapter. Application of OFDM allows the controller to determine and allocate a number of sub-carriers to each appliances depending on their rate requirements. At the appliances, low and high data rate devices use single and multiple antenna WiGLAN adapters, respectively.

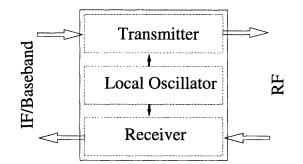

Chapter 2 examines a WiGLAN parallel receiver system. It determines that a digital intermediate frequency (IF) receiver best meets the requirements for parallel receivers. A digital IF receiver architecture avoids analog quadrature downconversion and eliminates IQ mismatch. However, since the WiGLAN receiver uses a heterodyne architecture, it must reject an image signal before performing frequency translation. An integrated Q-enhanced filter rejects this image signal and provides for a fully inte-

grated solution. The WiGLAN receiver also implements singular value decomposition (SVD) in its digital processor to exploit the benefits of multiple antennas for spatial diversity. SVD decomposes the MIMO channel matrix into equivalent parallel channels but requires that the transmitter knows the channel. WiGLAN parallel receivers characterize and send back channel information to the transmitters to meet this need.

#### **1.2** Power and Area Models

Considering a probabilistic channel alone, it appears that more antennas are always better for multiple antenna systems. An uncoded MxN antenna system in a richscattering Rayleigh fading environment has maximum diversity MN and a bit error rate that is proportional to  $SNR^{-MN}$  [16]. Each additional antenna favorably increases diversity and lowers bit error rate for a given SNR though there is less incremental diversity gain with each additional antenna. To determine a lower bound, [17] considers a system that operates in this rich-scattering channel and determines the minimum number of antennas that is sufficient to support various data and error rates. To determine an upper bound, [18] considers both the scattering condition for the channel and the area constraints for the transmit and receive antenna arrays. More clusters of scatterers increase the number of parallel subchannels while for a given wireless device's area, as the number of antennas increases, spacings between antennas decreases and the antennas eventually become correlated and degrade channel parallelism.

The first part of Chapter 3 develops a power dissipation model that adds transceiver power dissipation to the results from [17] to determine the optimal number of antennas for a multiple antenna system. This represents the most effective efficiency as it proposes to use only the number of antennas that is necessary to meet system requirements. Similar to [17], this thesis assumes a rich-scattering channel in order to focus on implementation tradeoffs. A method that considers the channel condition to determine the number of antennas is given in [18]. This chapter adapts a transceiver energy model presented in [19] for a wireless microsensor network to a general multiple antenna wireless LAN system by considering equal time operation for transmitter and receiver and incorporating a multiplication constant N that represents the number of antennas. The model determines an optimal number of antennas by capturing a decrease in RF transmit power due to increasing diversity with the increase in overhead power from each additional transceiver.

This part of the chapter also develops an area consumption model. This model simply adds area consumption for all the individual transceiver circuits to give a total. An area consumption model ensures that an optimal number of antennas that satisfies power dissipation and system requirements does not exceed available chip area.

## **1.3 SNR Gain and Its Application**

SNR gain represents a relaxation in necessary SNR for a multiple antenna system given the same data and bit error rates and operating conditions as a single transmit, single receive (1x1) antenna system. An advantage of SNR gain is that it increases transmission range for a wireless system without additional transmit signal power. This aspect has been thoroughly exploited by transceiver [20, 21] and receiver [22, 23] designers.

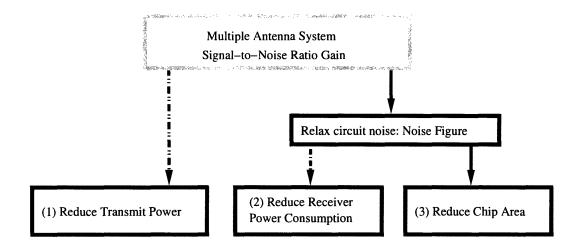

The second part of Chapter 3 proposes applying portions of SNR gain to lower power dissipation and area consumption for parallel transceivers as shown in Fig. 1-2. At the transmitter, SNR gain is applied to lower RF transmit signal power. Less RF power lowers power dissipation for a power amplifier (PA) which then lowers transceiver power dissipation. Since PA power dissipation represents a large portion of transceiver power dissipation, the reduction is significant. For the situation when RF transmit signal power generation dominates transceiver power dissipation, combined power dissipation for multiple transceivers decreases with more antennas. This implies, for example, that total power dissipation for two or more transceivers can actually be less than the power dissipation for one transceiver. At the receiver, SNR gain is applied to relax noise figure. This allows usage of receive circuits that trade power dissipation and area consumption for noise. This latter portion of the thesis is

Figure 1-2: Application of SNR gain

also reported in [24, 25].

Since the parallel transceiver power dissipation model includes multiple antenna SNR in its calculation, it inherently incorporates SNR gain to reduce the RF transmit signal power. To account for the other two SNR gain parameters, minor modifications to both power dissipation and area consumption models are necessary. Application of SNR gain to reduce receiver operating power requires that the power dissipation model incorporates the resulting higher noise figure and lower receiver operating power. Similarly, application of SNR gain to reduce receiver area consumption requires that the power dissipation model incorporates the resulting higher noise figure and that the area consumption model captures the lower receiver area consumption. These requirements simply imply introducing multiplication factors for power dissipation and area consumption and associating appropriate noise figures with them.

Embedding SNR gain within power dissipation and area consumption models allows its proper application. For example, at short distances, RF transmit power generation represents a small portion of transceiver power dissipation. In this situation, where transmit signal power is not dominant, a transceiver power dissipation model shows that it is better to apply SNR gain to relax noise figure and lower receiver operating power. In another situation, available chip area may be insufficient to support the optimal number of antennas. A transceiver area consumption model, for this case, suggests application of SNR gain to lower chip area while a transceiver power dissipation model assesses the impact.

### **1.4 Minimal Power and Area Circuits**

SNR gain application at the receiver requires circuits that are able to trade noise for lower power dissipation and area consumption. Chapter 4 introduces a variable power low noise amplifier (VPLNA) and area-efficient low noise amplifier (LNA) to answer this need. A VPLNA lowers its power dissipation when there is sufficient SNR gain to support a resulting higher noise figure. Lower power dissipation results from using a lower bias current either through adaptively controlling the current source or switching to an amplifier gain branch that consumes less current. Lower current yields less gain which then degrades noise figure for a VPLNA with adaptive current source while a lower gain branch has higher noise figure for multiple gain branch VPLNA. An area-efficient LNA consumes little chip area since it uses on-chip resistors instead of physically large on-chip inductors in its design. However, as resistors contribute additional noise, an area-efficient LNA also requires sufficient SNR gain to support its higher noise figure.

## 1.5 Area-efficient Parallel Receiver RFIC

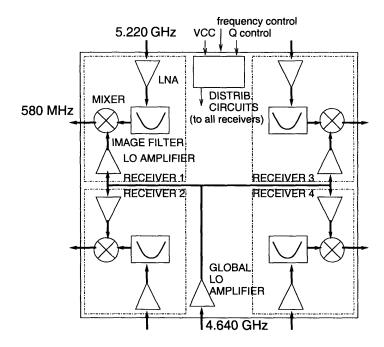

Application of power dissipation and area consumption models, SNR gain, and areaefficient circuits produces an area-efficient single-chip parallel receiver RFIC test chip for WiGLAN. Chapter 5 presents this chip that has four parallel receivers and their shared circuits. Each receiver has a low noise amplifier, Q-enhanced image reject notch filter, mixer, and local oscillator amplifier but shares a global local oscillator amplifier and distribution circuits for bias and filter tuning. Measurement shows that one receiver occupies an active area less than 1 mm<sup>2</sup>, provides 14 dB gain, and consumes 50 mW. On-chip image filters have rejections better than 30 dB at the image frequency. This portion of the thesis is also reported in [26].

## **1.6** Thesis Outline

For the rest of the thesis, brief descriptions for the chapters are as follow.

- Chapter 2 presents a parallel receiver system that uses digital IF and integrated Q-enhanced image filters and implements SVD within its digital processor to achieve spatial diversity gain.

- Chapter 3 develops the consumption models for parallel transceivers. It begins first with a single transceiver models and extends to parallel transceiver models based on spatial diversity. Using these models, this chapter examines in greater detail power and area tradeoffs for SNR gain and show their relationships to number of transceivers, distance, and noise figure.

- Chapter 4 presents variable power and area-efficient circuits. A variable power LNA lowers its power dissipation to lower transceiver power dissipation. An area-efficient LNA cost effectively enables parallel transceiver implementation on-chip. Both circuits applies SNR gain to relax noise figure requirements.

- Chapter 5 applies power dissipation and area consumption models together with area-efficient circuits to implement a parallel receiver chip with minimal transceiver power dissipation.

- Chapter 6 reviews the thesis contributions and discusses possible future research directions.

## Chapter 2

# WiGLAN Parallel Receiver System

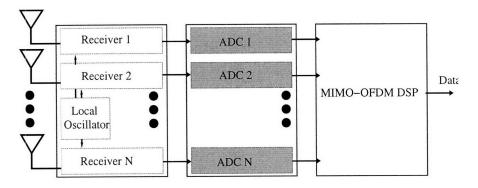

This chapter introduces the WiGLAN parallel receiver system. It consists of multiple antennas, parallel radio frequency (RF) receivers, analog-to-digital converters (ADCs), and a MIMO-OFDM digital signal processor (DSP) as shown in Fig. 2-1. With multiple antennas, each WiGLAN parallel receiver experiences spatially independent fading. It is through this independence that WiGLAN exploits the parallelism of an indoor wireless channel. Each antenna has a digital intermediate frequency (IF) receiver to convert signals from RF to a low IF and a time-interleaved ADC array to digitize an entire 150 MHz bandwidth [27]. This maintains the parallelism on-chip and also avoids analog quadrature downconversion. Inputs from each receiver then feed a MIMO-OFDM DSP that applies singular value decomposition (SVD) to achieve SNR gain [17]. In the sections to follow, this chapter discusses the

Figure 2-1: Parallel receiver system

characteristics of an indoor wireless channel, presents WiGLAN digital IF receiver, ADC, and DSP, and concludes with baseband bit error rate (BER) simulation results [17] that become critical inputs to the power dissipation and area consumption models.

#### 2.1 Wireless Channel

WiGLAN operates in an indoor wireless channel as typically found in home and business office environments. Characteristics of these environments include multiple partitions that prevent line of sight communication, small objects that scatter signals throughout, and people whose movements create motion in the channel. In such environments, WiGLAN uses multiple antennas to improve its link quality and applies OFDM so that it may operate at 5.22 GHz with a wide 150 MHz bandwidth. Since both of these techniques tie closely to the nature of the channel, the following discussion begins with a description of a wireless channel and then shows how WiGLAN uses this channel to achieve reliable high data rate wireless communication.

#### 2.1.1 Multipath Propagation and Fading

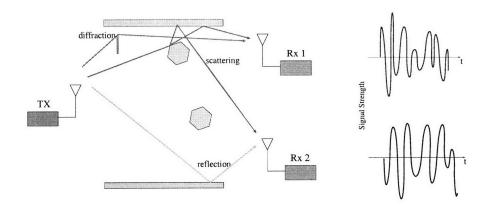

In addition to a direct path, radio waves propagate from the transmitter to the receiver by reflection, diffraction, and scattering. Fig. 2-2 shows these mechanisms between a single transmitter and two receivers. Reflection occurs when a wave encounters a large object when compared to its wavelength. Depending on the properties of the object and angle of incidence, portions or all of the wave reflect back. For example, if the wave impinges on a perfect conductor, total reflection occurs. On the other hand, if it encounters a dielectric, then part of the wave reflects while the other part refracts into the dielectric. Diffraction occurs when there is a sharp obstruction along the path. The wave bends around the corner of the obstruction such that a receiver in the shadow of the obstruction can detect the signal. Scattering occurs when the wave either encounters a rough surface or small objects compared to its wavelength. The resulting reflected waves spread out in all directions. Due to these propagation

Figure 2-2: Multi-path propagation and fading for two receivers

mechanisms, a receiver at one location detects a signal that is a combination of waves that travelled different paths of varying lengths from the transmitter to the receiver. This type of propagation is known as multipath propagation [28].

As a result of multipath propagation, multiple versions of the transmitted signal arrive at the receiver with various time delays and attenuations. This results in the spreading of the modulation symbol in time and is referred to as time dispersion. The standard deviation of the time spread is termed rms delay spread. In addition, movements within the channel produce a time varying channel that spreads the frequency components of the signal. This effect is known as frequency dispersion and the spread is specifically called the Doppler spread. The Doppler spread expands a single frequency tone into a spectrum and is a function of the velocity of motion and the signal wavelength.

Fading is a rapid fluctuation in the instantaneous received signal amplitude over a small travel distance or time. The right side of Fig. 2-2 shows the signal amplitudes for the two receivers that experience independent fading versus time. The impact of fading on a wireless system is a function of both the channel characteristics and the transmitted signal. If the modulation bandwidth is less than the coherence bandwidth, that is, the bandwidth for which the channel affects all the signal frequencies equally, the signal experiences flat fading. Viewed in the time domain, flat fading implies that the symbol period is greater than the rms delay spread. If the modulation bandwidth exceeds the coherence bandwidth, the signal experiences frequency selective fading and the channel affects the signal frequencies unequally and produces intersymbol interference. Viewed in the time domain, frequency selective fading implies that the symbol period is less than the rms delay spread. In a separate phenomenon, if the symbol period is less than the channel coherence time, that is, the period of time for which the channel affects all portions of the signal equally, the signal experiences slow fading. Viewed in the frequency domain, slow fading implies that the modulation bandwidth is greater than the Doppler spread. If, on the other hand, the symbol period is greater than the channel coherence time, the signal experiences fast fading. A fast fading channel is a channel that changes faster than the signal and results in distortion seen in time as unequal effects on the symbol during its period. Viewed in the frequency domain, fast fading implies the modulation bandwidth is less than the Doppler spread.

In a rich scattering environment, there exist parallel subchannels in space that create multiple inputs and multiple outputs for the channel. This allows parallel radios to implement spatial multiplexing and diversity. Due to multipath, each transmit antenna sees effectively a different channel and simultaneously transmits with the same frequency band. At the receivers, the channel matrix allows the receivers to extract the spatial signatures of the transmitted signals. Spatial multiplexing exploits the parallel subchannels to achieve high data rate transmissions by dividing a high rate data stream into several lower rate parallel data streams that transmit through a different antenna element separated by physical distance. At the parallel receivers, linear combinations of the received signals are spatially equalized, processed to retrieve the sub-streams, and then combined to recover the original data stream. For spatial diversity, parallel subchannels also exist between the parallel transmitters and receivers as in spatial multiplexing. However, space-time coding encodes the same signal differently and transmits each coded stream through a different antenna. Therefore, for a MIMO system, as shown in Fig. 2-3, if the parallel streams consist of different data, spatial multiplexing is achieved. On the other hand, if the same streams are redundantly transmitted as shown in Fig. 2-4, then spatial diversity is achieved. In order to exploit a MIMO channel, the receivers must be able to deter-

Figure 2-3: Spatial multiplexing example using 2x2 system with two separate data streams X1 and X2  $\,$

Figure 2-4: Spatial diversity example using 2x2 system with redundant data stream X1

mine the spatial signatures of the transmitted signals. As will be shown later, this is accomplished through the application of singular value decomposition (SVD).

Although a spatial multiplexing or diversity system uses an array of antennas, it is not a beamforming system. Certainly the individual antennas themselves could be similarly isotropic. However, a beamforming system uses an array of antennas to create a strong radiation pattern in the desired direction. A beamforming system also works relatively well in line-of-sight communication systems such satellites and pointto-point microwave links. Its antenna array does not need to exploit multipath signal propagation since the system enhances the line-of-sight transmit signal itself. This implies that a beamforming system does not depend on a MIMO channel. On the other hand, multiple antennas for spatial multiplexing and diversity systems require multipath signal propagation and normally operate in non line-of-sight situations.

### 2.1.2 WiGLAN System in a Fading Channel

At 5 GHz in an indoor environment, WiGLAN operates in a frequency selective but slow fading channel. It accounts for this channel behavior to achieve high data rate reliable communication as follow.

• Fading: WiGLAN uses multiple antennas to apply spatial diversity and overcome deep fades. Multiple antennas at antenna spacings greater than half wavelengths experience independent fading [1, 3]. Therefore, for multiple receive antennas, it is possible that while one receive antenna experiences a deep fade, another captures a strong signal. As the number of antennas increases, the chances that all receive antennas experiencing a deep fade significantly decreases. While it is certainly possible to achieve similar gains using time or frequency diversity, with multiple antennas, WiGLAN reaps the benefits of diversity without increasing time delay and frequency bandwidth. In time diversity, a data repeats its transmission with time spacings exceeding the coherence time. Although this allows each transmission to experience a different fading, a receiver using time diversity must wait for all transmissions to complete. In frequency diversity, data repeats its transmission on different carriers that are more than a coherence bandwidth apart. Similar to time diversity, each frequency transmission experiences a different fading. However, using frequency diversity without decreasing data rates requires more frequency spectrum.

Since WiGLAN applies spatial diversity instead of multiplexing, it sacrifices multiple antenna capacity for diversity gain. In [17], it was shown that at high SNR, the change in capacity,  $\Delta C$ , is given as

$$\Delta C \approx 0.33 k \Delta SNR, \tag{2.1}$$

where k represents the number of parallel subchannels and is equivalent to N antennas for an NxN system and  $\Delta SNR$  is given in dB. The relation implies that every 3 dB decrease in the SNR requirements due to spatial diversity costs k b/s/Hz in capacity. It is important to note that WiGLAN is a high diversity system that achieves gigabit per second data rates by using a wide frequency bandwidth and does not implement spatial multiplexing.

- Frequency selective fading: With its wide 150 MHz bandwidth, a WiGLAN transmission at 5.22 GHz experiences frequency selective fading. To overcome this impairment, WiGLAN applies OFDM and breaks its band into 1 MHz frequency bins. This bandwidth is well below the 4 MHz coherence bandwidth for 5-GHz non-line of sight [29] so that effectively, each modulated OFDM subcarrier experiences flat fading.

- Slow fading: An indoor environment has little motion and results in a slow fading channel. WiGLAN takes advantage of this situation and applies adaptive modulation for each OFDM subcarrier. With adaptive modulation, the receive node characterizes the channel for each subcarrier and transmits this information back to the transmit node. The transmit node then adjusts modulation order for each subcarrier corresponding to the SNR that the channel supports. WiGLAN does not use a subcarrier with very poor SNR in order to reduce errors

due to outage. For a subcarrier with good SNR, WiGLAN applies higher order modulation in order to increase data rates. Since the channel changes slowly, a transmit node can use a particular rate for some time before another channel measurement is necessary. This minimizes overhead for adaptive modulation. Near 5 GHz, the coherence time is around 24 ms with actual transmission time for WiGLAN set at 10 ms [30].

# 2.2 Digital IF Receiver