## SIMD Column-Parallel Polygon Rendering

by

## Matthew Willard Eldridge

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degrees of Bachelor of Science

and

Master of Science

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

May 1995

© Matthew Willard Eldridge, MCMXCV. All rights reserved.

The author hereby grants to MIT permission to reproduce and distribute publicly paper and electronic copies of this thesis document in whole or in part, and to grant others the right to do so.

| Author                                           | 1. VVIII W.                  |

|--------------------------------------------------|------------------------------|

| Department of Electrical Engineering an          | d Computer Science           |

| _                                                | May 12, 1995                 |

| Certified by                                     | ζ                            |

| •                                                | Seth Teller                  |

| Assistant Professor of Electrical Engineering an | <b>-</b>                     |

|                                                  | Thesis Supervisor            |

| Certified by                                     |                              |

|                                                  | Elizabeth C. Palmer          |

| Director, Employment and Development, Da         |                              |

| Accepted by                                      | Center<br>Sombanv Supervisor |

| Accepted by                                      | د                            |

| Fred                                             | eric R. Morgenthaler         |

| Chairman, breportantal Committee or              | n Graduate Students          |

JUL 171995

### SIMD Column-Parallel Polygon Rendering

by

### Matthew Willard Eldridge

Submitted to the Department of Electrical Engineering and Computer Science on May 12, 1995, in partial fulfillment of the requirements for the degrees of Bachelor of Science

and

Master of Science

#### Abstract

This thesis describes the design and implementation of a polygonal rendering system for a large one dimensional single instruction multiple data (SIMD) array of processors. Polygonal rendering enjoys a traditionally high level of available parallelism, but efficient realization of this parallelism requires communication. On large systems, such as the 1024-processor Princeton Engine studied here, communication overhead limits performance.

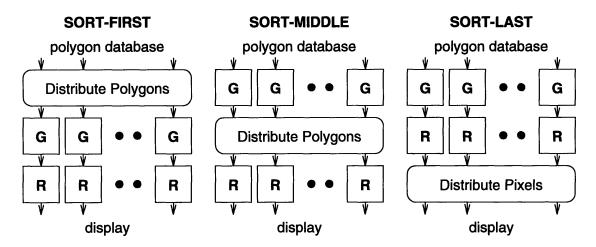

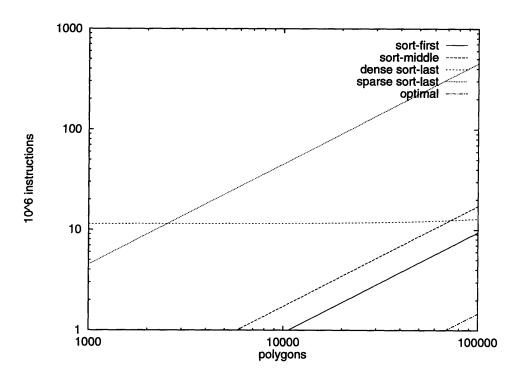

Special attention is paid to study of the analytical and experimental scalability of the design alternatives. Sort-last communication is determined to be the only design to offer linear performance improvements in the number of processors. We demonstrate that sort-first communication incurs increasingly high redundancy of calculations with increasing numbers of processors, while sort-middle communication has performance linear in the number of primitives and *independent* of the number of processors. Performance is thus be communication-limited on large sort-first and sort-middle systems.

The system described achieves interactive rendering rates of up to 30 frames per second at NTSC resolution. Scalable solutions such as sort-last proved too expensive to achieve real-time performance. Thus, to maintain interactivity a sort-middle render was implemented. A large set of communication optimizations are analyzed and implemented under the processor-managed communication architecture.

Finally a novel combination of sort-middle and sort-last communication is proposed and analyzed. The algorithm efficiently combines the performance of sort-middle architectures for small numbers of processors and polygons with the scalability of sort-last architectures for large numbers of processors to create a system with speedup linear in the number of processors. The communication structure is

substantially more efficient than traditional sort–last architectures both in time and in memory.

Thesis Supervisor: Seth Teller

Title: Assistant Professor of Electrical Engineering and Computer Science

Company Supervisor: Elizabeth C. Palmer

Title: Director, Employment and Development, David Sarnoff Research Center

## Acknowledgments

I would like to thank David Sarnoff Research Center and the Sarnoff Real Time Corporation for their support of this research. In particular, Herb Taylor for his expertise in assembly level programming of the Princeton Engine and many useful discussions; Jim Fredrickson for his willingness to modify the operating system and programming environment during development of my thesis; Joe Peters for his patience with my complaints; and Jim Kaba for his tutoring and frequent insights. I would like to thank Scott Whitman for many helpful discussions about parallel rendering and so willingly sharing the Princeton Engine with me. Thanks to all my friends at David Sarnoff Research Center and Sarnoff Real Time Corporation, you made my work and research very enjoyable.

I would like to thank my advisor, Seth Teller, for providing continual motivation to improve and extend my research. Seth has been a never ending source of suggestions and ideas, and an inspiration.

Most of all, a special thank you to my parents for supporting me here during my undergraduate years and convincing me to pursue graduate studies. Without their love and support I would have never completed this thesis.

This material is based upon work supported under a National Science Foundation Graduate Research Fellowship. Any opinions, findings, conclusions or recommendations expressed in this publication are those of the author and do not necessarily reflect the views of the National Science Foundation.

## Contents

| 1 | Intr | roduction                           | 17 |

|---|------|-------------------------------------|----|

|   | 1.1  | Background                          | 20 |

|   |      | 1.1.1 Hardware Approaches           | 20 |

|   |      | 1.1.2 Software Approaches           | 23 |

|   | 1.2  | Overview                            | 27 |

| 2 | Pri  | nceton Engine Architecture          | 31 |

|   | 2.1  | Processor Organization              | 32 |

|   | 2.2  | Interprocessor Communication        | 34 |

|   | 2.3  | Video I/O & Line-Locked Programming | 36 |

|   | 2.4  | Implementation                      | 36 |

| 3 | Gra  | aphics Pipeline                     | 39 |

|   | 3.1  | UniProcessor Pipeline               | 41 |

|   |      | 3.1.1 Geometry                      | 44 |

|   |      | 3.1.2 Rasterization                 | 47 |

|   |      | 3.1.3 Details                       | 51 |

|   | 3.2  | MultiProcessor Pipeline             | 52 |

|   |      | 3.2.1 Communication                 | 53 |

|   |      | 3.2.2 Geometry                      | 56 |

|   |      | 3.2.3 Rasterization                 | 58 |

|   | 3.3  | Summary                             | 60 |

| 4 | Sca | lability                              | 61  |

|---|-----|---------------------------------------|-----|

|   | 4.1 | Geometry                              | 62  |

|   | 4.2 | Rasterization                         | 63  |

|   | 4.3 | Communication                         | 64  |

|   |     | 4.3.1 Model                           | 64  |

|   |     | 4.3.2 Sort-First                      | 66  |

|   |     | 4.3.3 Sort-Middle                     | 67  |

|   |     | 4.3.4 Sort-Last                       | 68  |

|   | 4.4 | Analysis                              | 70  |

|   |     | 4.4.1 Sort-First vs. Sort-Middle      | 74  |

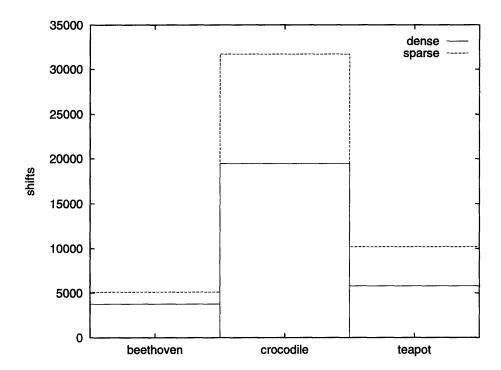

|   |     | 4.4.2 Sort-Last: Dense vs. Sparse     | 74  |

|   |     | 4.4.3 Sort-Middle vs. Dense Sort-Last | 75  |

|   | 4.5 | Summary                               | 77  |

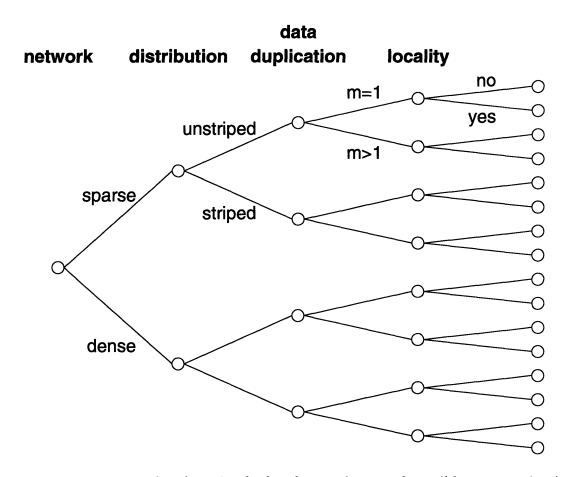

| 5 | Cor | nmunication Optimizations             | 79  |

|   | 5.1 | Sort-Middle Overview                  | 82  |

|   | 5.2 | Dense Network                         | 82  |

|   | 5.3 | Distribution                          | 85  |

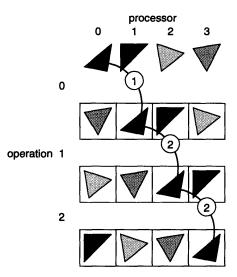

|   | 5.4 | Data Duplication                      | 90  |

|   | 5.5 | Temporal Locality                     | 96  |

|   | 5.6 | Summary                               | 97  |

| 3 | Sor | t-Twice Communication                 | 101 |

|   | 6.1 | Why is Sort-Last so Expensive?        | 101 |

|   | 6.2 | Leveraging Sort-Middle                | 102 |

|   | 6.3 | Sort-Last Compositing                 | 104 |

|   | 6.4 | Sort-Twice Cost                       | 106 |

|   | 6.5 | Deferred Shading and Texture Mapping  | 107 |

|   | 6.6 | Performance                           | 109 |

|   | 6.7 | Summary                               | 119 |

| 7 | Imp | olemen | tation                              | 115 |

|---|-----|--------|-------------------------------------|-----|

|   | 7.1 | Parall | el Pipeline                         | 118 |

|   | 7.2 | Line-l | Locked Programming                  | 119 |

|   | 7.3 | Geom   | etry                                | 120 |

|   |     | 7.3.1  | Representation                      | 120 |

|   |     | 7.3.2  | Transformation                      | 121 |

|   |     | 7.3.3  | Visibility & Clipping               | 122 |

|   |     | 7.3.4  | Lighting                            | 123 |

|   |     | 7.3.5  | Coefficient Calculation             | 124 |

|   | 7.4 | Comm   | nunication                          | 124 |

|   |     | 7.4.1  | Passing a Single Polygon Descriptor | 126 |

|   |     | 7.4.2  | Passing Multiple Descriptors        | 126 |

|   | 7.5 | Raster | rization                            | 129 |

|   |     | 7.5.1  | Normalize Linear Equations          | 129 |

|   |     | 7.5.2  | Rasterize Polygons                  | 130 |

|   |     | 7.5.3  | Rasterization Optimizations         | 133 |

|   |     | 7.5.4  | Summary                             | 134 |

|   | 7.6 | Contro | ol                                  | 135 |

|   | 7.7 | Summ   | nary                                | 136 |

| _ | _   | 1.     |                                     |     |

| 8 | Res |        |                                     | 139 |

|   | 8.1 |        | Performance                         |     |

|   |     | 8.1.1  | Geometry                            | 140 |

|   |     | 8.1.2  | Communication                       | 140 |

|   |     | 8.1.3  | Rasterization                       | 141 |

|   |     | 8.1.4  | Aggregate Performance               | 142 |

|   | 8.2 | Accou  | nting                               | 143 |

|   | 8.3 | Perfor | mance Comparison                    | 146 |

| 9  | Futi | ure Directions                       | 149 |

|----|------|--------------------------------------|-----|

|    | 9.1  | Distribution Optimization            | 149 |

|    | 9.2  | Sort-Twice                           | 150 |

|    | 9.3  | Next Generation Hardware             | 150 |

| 10 | Con  | clusions                             | 153 |

| A  | Sim  | ulator                               | 155 |

|    | A.1  | Model                                | 156 |

|    |      | A.1.1 Input Files                    | 156 |

|    |      | A.1.2 Parameters                     | 158 |

|    | A.2  | Operation                            | 160 |

|    |      | A.2.1 Data Initialization & Geometry | 160 |

|    |      | A.2.2 Communication                  | 164 |

|    |      | A.2.3 Rasterization                  | 169 |

|    | A.3  | Correctness                          | 169 |

|    | A.4  | Summary                              | 170 |

# List of Figures

| 2-1  | Princeton Engine Video I/O                     | 31 |

|------|------------------------------------------------|----|

| 2-2  | Princeton Engine                               | 33 |

| 2-3  | Communication Options on the Princeton Engine  | 35 |

| 2-4  | Princeton Engine                               | 37 |

| 3-1  | Synthetic Eyepoint                             | 39 |

| 3-2  | Beethoven                                      | 41 |

| 3-3  | Crocodile                                      | 42 |

| 3-4  | Teapot                                         | 42 |

| 3-5  | Texture Mapped Crocodile                       | 43 |

| 3-6  | Sample Texture Image                           | 43 |

| 3-7  | Uniprocessor Geometry Pipeline                 | 44 |

| 3-8  | 2D Perspective Transformation                  | 45 |

| 3-9  | Polygon Linear Equations                       | 48 |

| 3-10 | Triangle Definition by Half-Plane Intersection | 49 |

| 3-11 | Uniprocessor Rasterization                     | 50 |

| 3-12 | Sort Order                                     | 54 |

| 3-13 | SIMD Geometry Pipeline                         | 57 |

| 3-14 | SIMD Rasterization                             | 59 |

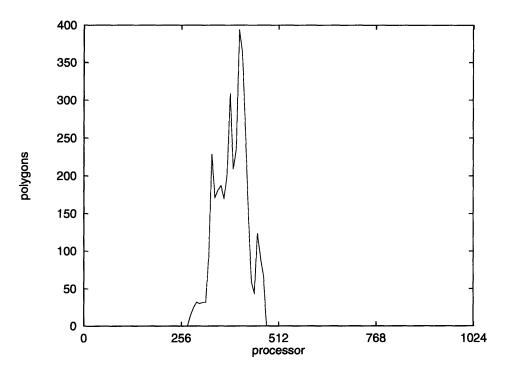

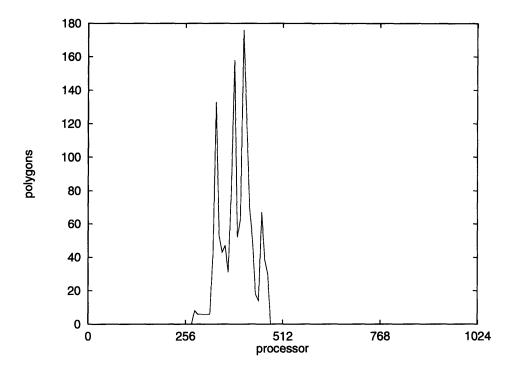

| 4-1  | Sort-First Load Imbalance                      | 72 |

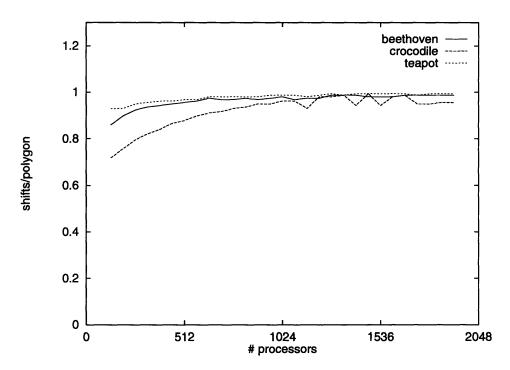

| 4-2  | Sort-Middle                                    | 73 |

| 4-3  | Communication Costs                            | 76 |

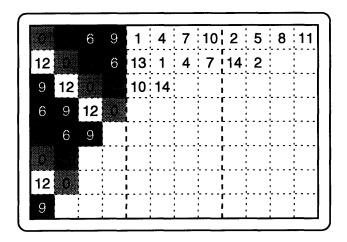

| 5-1  | Communication Optimizations                             | 80  |

|------|---------------------------------------------------------|-----|

| 5-2  | Sort-Middle Communication                               | 83  |

| 5-3  | Simulation of Sparse vs. Dense Networks                 | 84  |

| 5-4  | Pass Cost                                               | 86  |

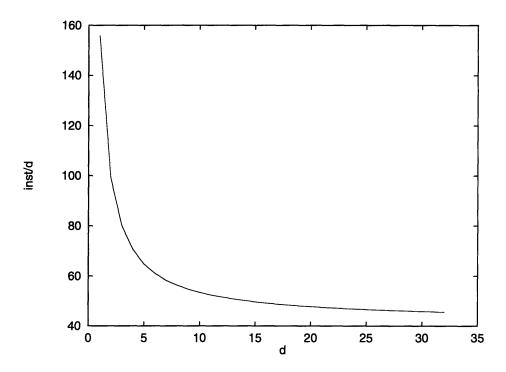

| 5-5  | $i^*$ vs. $d$ for Distribution Optimization             | 89  |

| 5-6  | Polygon Duplication                                     | 92  |

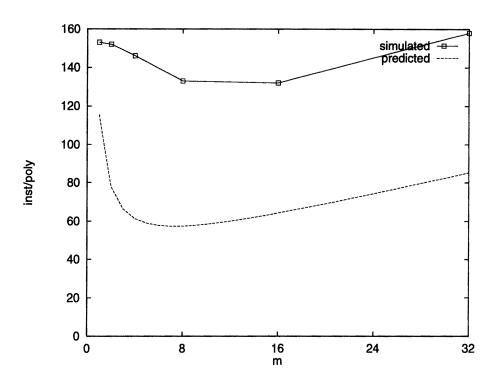

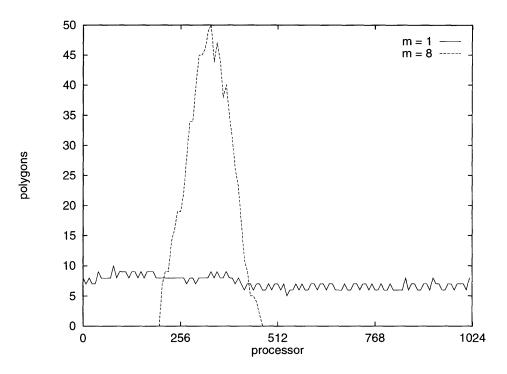

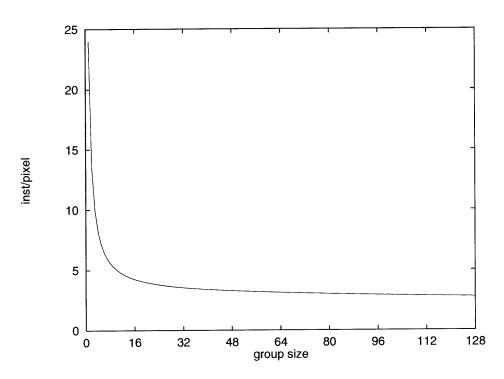

| 5-7  | Polygons Per Processor vs. m                            | 94  |

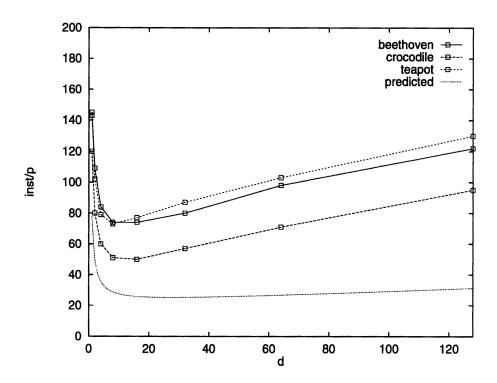

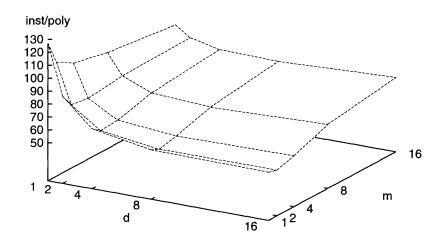

| 5-8  | Instructions Per Polygon as a function of $m$ and $d$   | 95  |

| 5-9  | Temporal Locality                                       | 98  |

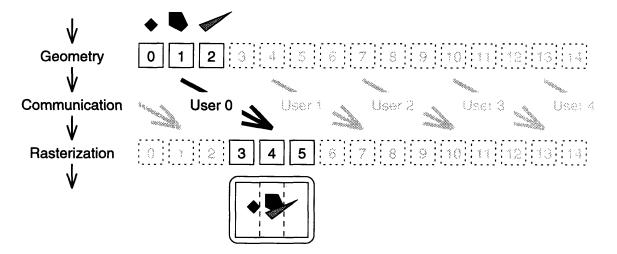

| 6-1  | Multiple Users on a Parallel Polygon Renderer           | 103 |

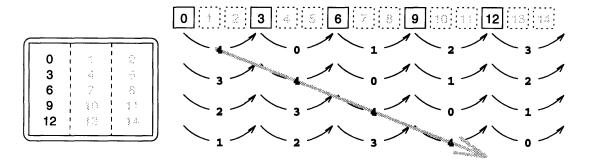

| 6-2  | Sort-Last Compositing                                   | 105 |

| 6-3  | Pixel to Processor Map                                  | 106 |

| 6-4  | Sort-Twice Compositing Time                             | 108 |

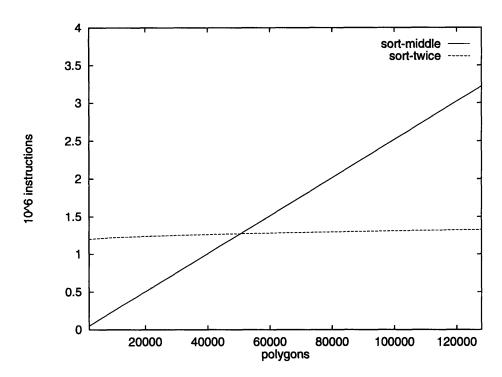

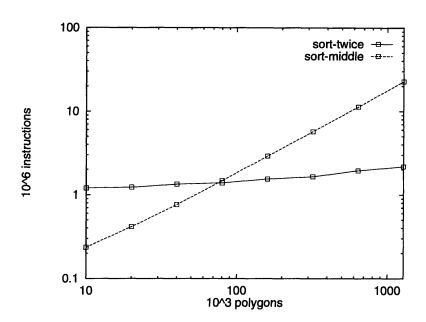

| 6-5  | Predicted Sort-Middle vs. Sort-Twice Communication Time | 111 |

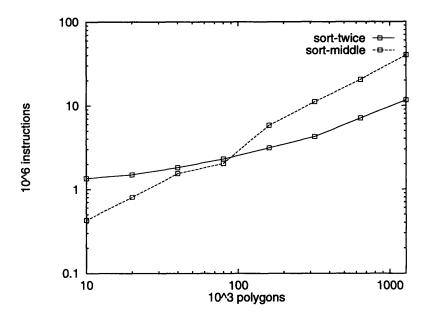

| 6-6  | Simulated Sort-Middle vs. Sort-Twice Communication Time | 112 |

| 6-7  | Simulated Sort-Middle vs. Sort-Twice Execution Time     | 113 |

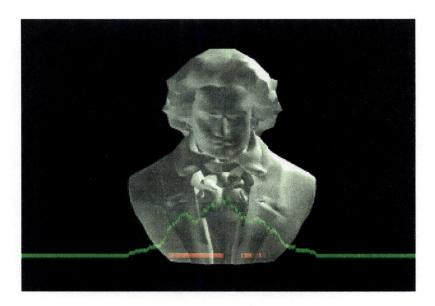

| 7-1  | Beethoven                                               | 116 |

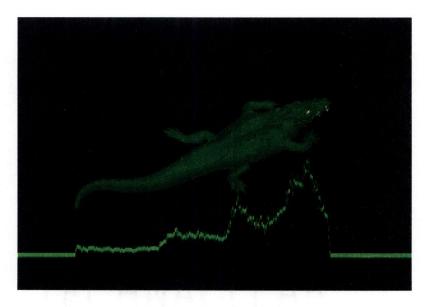

| 7-2  | Crocodile                                               | 116 |

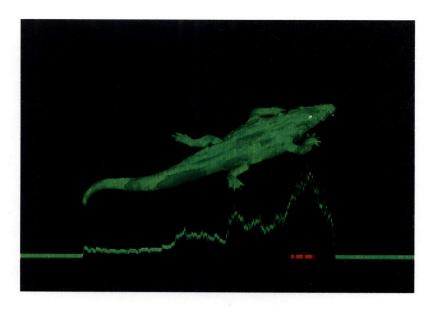

| 7-3  | Texture Mapped Crocodile                                | 117 |

| 7-4  | Teapot                                                  | 117 |

| 7-5  | Polygon Representation                                  | 121 |

| 7-6  | Polygon Descriptor                                      | 125 |

| 7-7  | Implementation for Data Distribution                    | 127 |

| 7-8  | Linear Equation Normalization                           | 129 |

| 7-9  | Rasterizing                                             | 134 |

| 7-10 | Virtual Trackball Interface                             | 136 |

| 8-1  | Execution Profile                                       | 144 |

| A-1 | Bounding-box Input File                                   | 157 |

|-----|-----------------------------------------------------------|-----|

| A-2 | Sample Screen Map                                         | 158 |

| A-3 | Simulator Model                                           | 161 |

| A-4 | Destination False Positive                                | 163 |

| A-5 | Simulator Communication                                   | 165 |

| A-6 | Destination Vector Alignment                              | 167 |

| A-7 | Destination Vector for $q \neq 1 \dots \dots \dots \dots$ | 168 |

## List of Tables

| 4.1 | Communication Modeling Variables         | 65  |

|-----|------------------------------------------|-----|

| 4.2 | Communications Costs                     | 71  |

| 4.3 | Communication Modeling Values            | 72  |

| 8.1 | Rendering Performance for Typical Scenes | 143 |

| A.1 | Simulator Parameters                     | 159 |

## Chapter 1

## Introduction

This thesis explores the implementation of an interactive polygonal renderer on the Princeton Engine, a 1024–processor single–instruction multiple–data (SIMD) parallel computer. Each processor is a simple arithmetic core able to communicate with its left and right neighbors.

This is an important architecture on which to study the implementation of polygon rendering, for many reasons:

- The interprocessor communication structure is simple and inexpensive, making the construction of larger systems practical, with cost linear in the number of processors.

- The use of SIMD processors allows very carefully managed communication to be implemented, and affords significant opportunities for optimizations.

- Current polygon rendering algorithms and architectures often exhibit poor scalability, and are designed with large and expensive crossbars to insure adequate interprocessor bandwidth. A reduction in the amount of communication required and the careful structuring of the communication algorithm, as mandated by the modest communication resources of the Princeton Engine, will have large effects on the feasibility of future larger machines.

Many parallel renderers have been implemented, but most were either executed on smaller machines or on machines with a higher dimension communication network than the Princeton Engine. The use of a large machine with narrow interconnect such as the Princeton Engine makes the polygon rendering problem significantly different.

Polygon rendering provides a viewport into a three–dimensional (3D) space on a two–dimensional (2D) display device. The space may be of any sort, real or imagined. There are two broad approaches taken to polygon rendering: realism and interactivity. Realism requires precise and generally expensive computation to accurately model a scene. Interactivity requires real–time computation of a scene, at a possible loss of realism.

Polygon rendering models a scene as composed of a set of polygons in 3D being observed by a viewer from any arbitrary location. Geometry computations transform the polygonal scene from a 3D model to a 2D model and then rasterization computations render the 2D polygons to the display device. Both the geometry and the rasterization computations are highly parallel, but their parallelization exposes a sorting problem. Polygon rendering generally relies on the notion of polygons being rendered in the "correct" order, so that polygons nearer to the observer's viewpoint obscure polygons farther away. If the polygon rendering process is distributed across processors this ordering constraint will require interprocessor communication to resolve.

The ordering constraint is generally resolved in one of three ways, referred to by where they place the communication in the rendering process. Sort-first and sort-middle algorithms place polygons that overlap once projected to the screen on the same processor for rasterization so that the occlusion can be resolved with local data. Sort-last rasterizes each polygon on the processor that performs the polygon's geometry calculations, and then uses pixel by pixel information after the fact to combine all of the processor's rasterization results. The advantages and disadvantages of these approaches are discussed, both in general, and with a specific focus on an efficient implementation on the Princeton Engine.

A major goal of this thesis is to find and extract scalability from the explored communication algorithms, so that as the number of processors increases the rendering performance will increase commensurately. We demonstrate that for some communication approaches, most notably sort-middle, the communication time is linear in the number of polygons and *independent* of the number of processors. Without some care communication can dominate execution time of polygon rendering on large machines. Sort-last algorithms make constant-time communication possible, independent of both the number of polygons and the number of processors, but unfortunately the constant cost is very large.

A novel combination of sort-middle and sort-last communication is proposed and analyzed to address the problem of finding scalable communication algorithms. The algorithm efficiently combines the performance of sort-middle architectures for small numbers of processors and polygons with the scalability of sort-last architectures to create a system with performance *linear* in the number of processors.

The system described in this thesis achieves interactive rendering rates of up to 30 frames per second. To maintain interactivity a sort-middle render was implemented, as scalable solutions such as sort-last proved too expensive to achieve real-time performance. A large set of optimizations are analyzed and implemented to address the scalability problems of sort-middle communication.

This thesis significantly differs from current work on parallel polygon rendering. Contemporary parallel rendering focuses very heavily on multiple-instruction multiple-data (MIMD) architectures with large, fast and expensive networks. We have instead pursued a SIMD architecture with a rather narrow network. Background is provided for software and hardware parallel renderers, both of which have significantly influenced this work.

### 1.1 Background

Polygon rendering systems vary widely in their capabilities beyond just painting polygons on the screen. The most common features found in most of the systems described below include:

**Depth Buffering** A pixel-by-pixel computation of the distance of the polygon from the users eye is stored in a "depth buffer." Polygon are only rendered at the pixels where they are closer to the observer than the previously rendered polygons.

Smooth Shading The color of the polygon is smoothly interpolated between the vertices to give the impression of a smoothly varying surface, rather than a surface made up of flat-shaded planar facets.

**Texture Mapping** The color of the polygon is replaced with an image to increase the detail of the scene. For example, an image can be texture mapped onto a billboard polygon.

More complex capabilities are present in many of the systems and, while technically interesting, are left unaddressed as they don't bear directly on the polygon rendering system described herein.

There have been numerous parallel polygon rendering systems built. I will discuss some of them here, and provide references to the literature. It is significant that most of the work deals either with large VLSI systems, or MIMD architectures with powerful individual nodes, and a rich interconnection network. This thesis bridges the gap between these approaches, merging the very high parallelism of hardware approaches with the flexibility of software approaches.

### 1.1.1 Hardware Approaches

High performance polygon rendering has traditionally been the domain of special purpose hardware solutions, as hardware can readily provide both the parallelism

required and the communication bandwidth necessary to fully exploit the parallelism in polygon rendering. Turner Whitted provides a survey of the 1992 state of the art in hardware graphics architectures in [21].

I will briefly discuss three specific systems here: the PixelFlow architecture from the University of North Carolina, and two architectures from Silicon Graphics, Inc., the IRIS 4D/GTX and the Reality Engine. All of the architectures provide interactive rendering with various degrees of realism.

#### **PixelFlow**

PixelFlow, described in [12] and [13], is a large-scale parallel rendering system based on a sort-last compositing architecture. It provides substantial programmability of the hardware, and at a minimum performs depth buffering, smooth shading and texture mapping of polygons.

PixelFlow is composed of a pipeline of rendering boards. Each rendering board consists of a RISC processor to perform geometry calculation and a 128 × 128 SIMD array of pixel processors that rasterize an entire polygon simultaneously, providing parallelism in the extreme. The polygons database is distributed arbitrarily among the rendering boards to achieve an even load across the processors. After rendering all of its polygons each rendering board has a partial image of the screen, correct only for that subset of the polygons it rendered. The separate partial images of the screen are then composited to generate a single output image via a 33.8 gigabit/second interconnection bus.

PixelFlow implements shading and texture mapping in two special shading boards at the end of the pipeline of rendering boards. Each pixel is thus shaded at most once, eliminating needless shading of non-visible pixels, and the amount of texture memory required of the system is limited to the amount that will provide sufficient bandwidth to texture map full resolution images at update rates.

The sort-last architecture provides performance increases nearly linear in the number of rendering boards and readily admits load balancing. The PixelFlow architec-

ture, when complete, is expected to scale to performance of at least 5 million polygons per second. By comparison the current Silicon Graphics Reality Engine renders slightly more than 1 million polygons per second.

#### IRIS 4D/GTX

The Silicon Graphics IRIS 4D/GTX, described in [2], was first sold in 1989 and is the Princeton Engine's contemporary. The GTX performs smooth shading and depth—buffering of lit polygons and can render over 100,000 triangles a second. The GTX provides no texture mapping support.

Geometry computations are performed by a pipeline of 5 high performance processors which each perform a distinct phase of the geometry computations. The output of the geometry pipeline is fed into a polygon processor which dices polygons into trapezoids with parallel vertical edges. These trapezoids are consumed by an edge processor that generates a set of vertical spans to interpolate to render each polygon. A set of 5 span processors perform interpolation of the vertical spans. Each span processor is further supported by 4 image engines that perform the composition of the pixels with previously rendered polygons and manage the fully distributed frame-buffer. The span processors are interleaved column by column of the screen and the image engines for each span processor are interleaved pixel by pixel. The fine grain interleaved interleaving of the span processors and image engines insure that most primitives will be rasterized in part by all of the image engines.

Communication is implemented by the sort-middle screen-space decomposition performed between the edge processor and the span processors. This choice, while limiting the scalability of the system, avoids the extremely high constant cost of sort-last approaches such as PixelFlow.

#### Reality Engine

The Reality Engine, described in [1], represents the current high—end polygon rendering system from Silicon Graphics. It supports full texture mapping, shading, lighting

and depth buffering of primitives at rates exceeding one million polygons a second.

Logically the Reality Engine is very similar to the architecture of the GTX. The 5-processor geometry pipeline has been replaced by 12 independent RISC processors each implementing a complete version of the pipeline, to which polygons are assigned in a round-robin fashion. A triangle bus provides the sort-middle interconnect between the geometry engines and a set of up to 20 interleaved fragment generators. Each fragment generator outputs shaded and textured fragments to a set of 16 image engines which perform multisample antialiasing of the image, and provide a fully distributed framebuffer. The most significant change from the GTX are the fragment generators, which are the combination of of the span processors and the edge processors.

The texture memory is fully duplicated at each of the 20 fragment generators to provide the high parallel bandwidth required to access textures at full throttle by all fragment generators, and as such the system operates with little performance penalty for texture mapping.

A fully configured Reality Engine consists of over 300 processors and nearly half a gigabyte of memory, and provides the closest analog to the Princeton Engine in raw computational power. Substantial differences in communication bandwidth and the speed of the processors make the comparison far from perfect however, and the Princeton Engine's performance is more comparable to its contemporary, the GTX.

### 1.1.2 Software Approaches

There have been a number of software parallel renderers implemented, both in the interests of realism and/or interactivity. The majority of these renderers have either been implemented on small machines (tens of processors) or on large machine with substantial interconnection. In either case the severity of the communication problem is minimized.

#### **Connection Machine**

Frank Crow et al. implemented a polygonal rendering system on a Connection Machine 2 (CM-2) at Whitney/Demos Productions, as described in [6]. The CM-2 [18] is a massively parallel SIMD computer composed of up to 65,536 bit-serial processors and 2,048 floating-point coprocessors. The nodes are connected in a 2D mesh and also via a 12-dimensional hypercube with 16 processors at each vertex. Each node in the CM-2 has 8KB of memory, for a total main memory size of 512MB.

Crow distributes the framebuffer over the machine with a few pixels per processor. Rendering is performed with a polygon assigned to each processor. All processors render simultaneously and as pixels are generated they are transmitted via the hypercube interconnect to the processor with the appropriate piece of the framebuffer for depth buffering. This is therefore a large–scale implementation of sort–last communication. The issue of the bandwidth this requires from the network is left untouched. It is reasonable to assume that it is not inexpensive on such a large machine. Crow alludes to the problem of collisions between pixels destined for the same processor, but leaves it unresolved.

The use of a SIMD architecture forces all processors to always perform the same operations (on potentially different data). Thus if polygons vary in size all processors will have to wait for the processor with the biggest polygon to finish rasterizing before they proceed to the next polygon. This problem is exacerbated by the 2–D nature of the polygons, which generally breaks the rasterization into a loop over the horizontal "spans" of the polygons, with an inner loop over the pixels in each span. Without care this can result in all processors executing in time proportional to the worst case polygon width. Crow addresses this problem in part by allowing processors to independently advance to the next span of their current polygon every few pixels, but constrains all processors to synchronize at polygon boundaries. Our experience suggests that a substantial amount of time is wasted by this approach.

Crow provides a good overview of the difficulties of adapting the polygon rendering algorithm to a very large SIMD machine, but leaves some critical load balancing issues unresolved, and unfortunately provides no performance numbers.

#### **Princeton Engine**

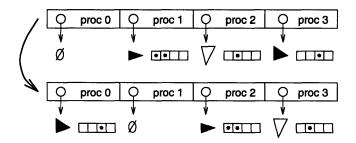

Contemporaneous with this thesis, Scott Whitman implemented a multiple-user polygon renderer on the Princeton Engine. The system described in [20] divides the Princeton Engine among a total of 8 simultaneous users, assigning a group of 128 processors to each user.

Sort-middle communication is used, with some discussion made of the cost of this approach. As in Crow [6], Whitman employs a periodic test during the rasterization of each scan-line to allow processors to independently advance to the next scan-line. He also synchronizes at the polygon level, constraining the algorithm to perform in time proportional to the largest polygon on any processor.

Whitman suggests that his algorithm would attain performance of approximately 200,000 triangles per second per 128 processors on the next generation hardware we discuss in §9.3. This assumes that the system remains devoted to multiple users, so a single user will not attain an additional 200,000 triangles per second for every group of 128 processors assigned to him.

Whitman also provides a good general discussion and background for parallel computer rendering methods in his book [19].

#### Parallel RenderMan

Michael Cox addresses issues of finding scalable parallel algorithms and architectures for rendering, and specifically examines a parallel implementation of RenderMan [4].

Cox implements both a sort-first renderer, as an efficient decomposition of the rendering problem in image space, and a sort-last renderer, as an efficient decomposition in object space, to study the differences in efficiency between these two approaches. Both implementations were on a CM-5 from Thinking Machines, a 512 processor MIMD architecture with a powerful communication network.

The problems of each approach are discussed in detail. Sort-first (and sort-

middle) can suffer from load imbalances as the distribution of polygons varies in image space, and sort-last suffers from extreme communication requirements. Cox addresses these issues with a hybrid algorithm which uses sort-last communication as a back end to load balance to sort-first communication.

#### Distributed Memory MIMD Rendering

Thomas Crocket and Tobias Orloff provide a discussion of parallel rendering on a distributed memory MIMD architecture in [5] with sort-middle communication. Particular attention is paid to load-imbalances due to irregular content distribution over the scene.

They use a row-parallel decomposition of the screen, assigning each processor a group of contiguous rows for which it performs rasterization. The geometry and rasterization calculations are performed in a loop, first performing some geometry calculations and transmitting the results to the other processors, then rasterizing some polygons received from other processors, then performing more geometry, etc. This distributes the communication over the entire time of the algorithm and can result in much better utilization of the communication network by not constraining all of the communication to happen in a burst between geometry and rasterization.

#### **Interactive Parallel Graphics**

David Ellsworth describes an algorithm for interactive graphics on parallel computers in [7]. Ellsworth's algorithm divides the screen into a number of regions greater than the number of processors, and dynamically computes a mapping of regions to processors to achieve good load balancing. The algorithm was implemented on the Touchstone Delta prototype parallel computer with 512 Intel i860 compute nodes interconnected in a 2D mesh.

Polygons are communicated in sort-middle fashion with the caveat that processors are placed into groups. A processor communicates polygons after geometry calculations by bundling all the polygons to be rasterized by a particular group into a large

message and sending them to a "forwarding" processor at that group that then redistributes them locally. This approach amortizes message overhead by creating larger message sizes.

This amortization of the communication network overhead is a powerful idea, and is the central theme of several optimizations explored in this thesis.

### 1.2 Overview

This thesis deals with a number of issues in parallel rendering. A great deal of attention is paid to efficient communication strategies on SIMD rings, and their specific implementation on the Princeton Engine.

Chapter 2 provides an overview of the Princeton Engine architecture which will drive our analysis of sorting methods, and our implementation.

Chapter 3 discusses the uniprocessor polygon rendering pipeline and then extends it to the multiprocessor pipeline. Approaches to the sorting problem are addressed, and issues in extracting efficiency from a parallel SIMD machine are raised.

Chapter 4 examines the scalability of polygon rendering algorithms, by looking at the scalability of the three primary components of rendering: geometry, communication, and rasterization. A general model for the performance of sort-first, sort-middle and sort-last communication on a 1D ring is proposed and used to make broad predictions about the scalability of the sorting algorithms in both the number of polygons and the number of processors. Attention is also paid to the load balancing problems that the choice of sorting algorithm can introduce and their effects on the overall scalability of the renderer. Chapter 4 concludes with justification for the choice of sort-middle communication for the Princeton Engine polygon rendering implementation, despite its lack of scalability.

Chapter 5 proposes and analyzes optimizations for sort-middle communication, both with an analytical model, and with the support of instruction-accurate simulation. The feasibility of very tight user control over the communication network is exploited to provide a set of precisely managed and highly efficient optimizations which more than triple the overall performance from the most naive communication implementation.

Chapter 6 proposes and analyzes a novel communication strategy that marries the efficiency of sort-middle communication for small numbers of polygons and processors with the constant time performance of sort-last communication to obtain a highly scalable algorithm. Cycle by cycle control of the communication channel is used to create a communication structure that while requiring the same amount of bandwidth as sort-last communication achieves nearly a factor of 8 speedup over a typical implementation by amortizing the communication overhead. The VLIW coding of the Princeton Engine allows a full deferred lighting, shading and texture mapping implementation which increases rasterizer efficiency by a factor of more than two.

Chapter 7 details our implementation of polygon rendering on the Princeton Engine. A complete discussion of the efficient handling of the communication channel is made, specifically discussing the queueing of polygons for communication to maintain saturation of the channel, and the use of carefully pipelined pointer indirection to achieve general all-to-all communication with neighbor-to-neighbor communication without any additional copy operations. Specific mechanisms and optimization for the implementation of fast and efficient parallel geometry and rasterization are also discussed.

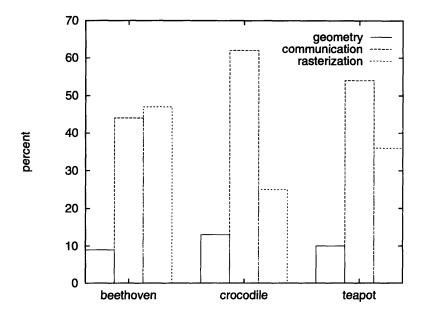

Chapter 8 discusses the performance of our system, and provides an account of where all the instructions go in a single second of execution. Statistics from executions of the system are provided for three sample scenes of varying complexity, along with benchmark figures of the raw throughput of the system for individual geometry, communication, and rasterization operations. The results are compared with the GTX from Silicon Graphics, a contemporary of the Princeton Engine, and with the Magic-1, our next generation hardware.

Chapter 9 discusses our next generation hardware, the Magic-1, currently under test and development. The Magic provides significant increases in communication and

computation support, in addition to a greatly increased clock rate, and is predicted to provide an immensely powerful polygon rendering system. Our estimations for an implementation of a sort—twice rendering system on this architecture are provided, and indicate a system with performance in the millions of polygons, with flexibility far beyond that of current high performance hardware systems.

Chapter 10 summarizes the results of this thesis, and concludes with a discussion of the contributions of this work.

Appendix A discusses the instruction–accurate simulator developed to explore the efficiency of different communication algorithms and the load–balancing issues raised on a highly parallel machine.

## Chapter 2

## Princeton Engine Architecture

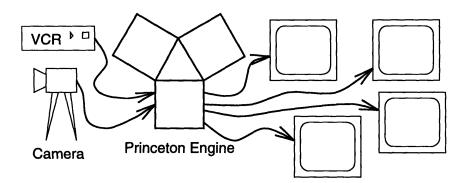

The Princeton Engine [3], a super-computer class parallel machine, was designed and built at the David Sarnoff Research Center in 1988. It consists of between 512 and 2048 SIMD processors connected in a neighbor-to-neighbor ring. The Engine was originally designed purely as a video processor, and its only true input/output paths are video. It accepts two NTSC composite video inputs and produces up to four interlaced or progressive scan component video outputs, as shown in Figure 2-1.

The Princeton Engine is a SIMD architecture, so all processors execute the same instruction stream. Conditional execution of the instruction stream is achieved with a "sleep" state that processors may conditionally enter and remain in until awakened.

Figure 2-1: **Princeton Engine Video I/O:** the Princeton Engine supports 2 simultaneous video inputs and 4 simultaneous outputs.

The instruction stream implicitly executes

```

if wakeup then

asleep = false

execute instruction

if !asleep then

commit result

```

for every instruction. More complex if ... then ... else ... execution can be achieved by first putting some subset of the processors to sleep, executing the then body, toggling the asleep flag, and executing the else body.

The details of the processors, the communication interconnect and the video I/O capabilities are described below. The video I/O structure is particularly critical as it determines what algorithms can be practically implemented on the Princeton Engine.

## 2.1 Processor Organization

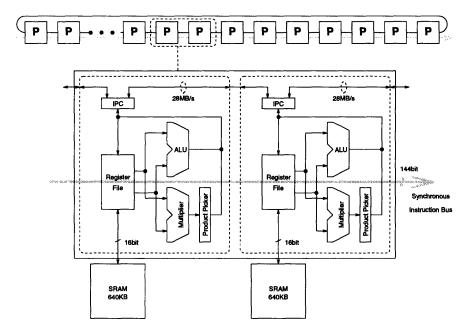

The Princeton Engine, shown schematically in Figure 2-2, is a SIMD linear array of 1024 processors connected in a ring. Each processor is a 16-bit load-store core, with a register file, ALU, a  $16 \times 16$  multiplier and 640 KB of memory.

The  $16 \times 16$  multiplier computes a 32 bit result, and a product picker allows the selection of which 16 bits of the output are used, providing the operation  $c = (a * b)/2^n$ . This allows efficient coding of fixed-point operations. The Princeton Engine was designed to process video in real-time, and as such extended precision integer arithmetic (beyond 16 bits) and floating-point arithmetic delegated to software solutions and are relatively expensive operations. A 32-bit signed integer multiply requires 100 instructions, and a 32-bit signed integer division requires over 400 instructions.

The memory is composed of 2 types: 128KB of fast memory and 512KB of slow memory. Fast memory is accessible in a single clock cycle. Slow memory is divided into 4 banks of 128KB and is accessible in 2 cycles. The compiler places all user

Figure 2-2: **Princeton Engine:** the processors are organized in a 1D ring. The instruction stream is distributed synchronously from the sequencer.

data and variables into fast memory. Any use of the slow memory is by explicit programmer access.

The instruction stream supplied by the sequencer is 144 bits wide. The VLIW (Very Long Instruction Word) coded instruction stream provides parallel control over all of the internal data paths of the processors. The average amount of instruction level parallelism obtained within the processors is between 2 and 3. Unlike typical uniprocessors, the Princeton Engine processors are not pipelined, as the instruction decode has already happened at the sequencer. The parallelism obtained by VLIW on the Princeton Engine is comparably to the parallelism obtained by pipelined execution in a RISC processor, and the 14MHz execution of the processing element is roughly equivalent to 14 RISC MIPS.

The processors are controlled by a central sequencer board which manages the program counter and conditional execution. Each of the 1024 processors operates at 14MHz for an aggregate performance of approximately 14,000 RISC MIPS or 14 billion instructions per second.

## 2.2 Interprocessor Communication

The processors are interconnected via a neighbor-to-neighbor "interprocessor communication" (IPC) bus. Each processor may selectively transmit or receive data on any given instruction, allowing multiple communications to occur simultaneously. There is no shared memory on the Princeton Engine, all communication between processors must via the IPC.

Interprocessor communication (IPC) occurs via a 16-bit data register usable on every cycle, for a bisection (neighbor to neighbor) bandwidth of 28MB/s. The ring can be configured as a shift register with 1024 entries. Each processor has control over one entry in the shift register. After a shift operation each processor's IPC register holds the value of its neighbor's (left or right) IPC register previous to the shift operation. During any given instruction the IPC is shifted left, right or unchanged. The IPC register may be read non-destructively, so once data is placed in the IPC registers it may be shifted and read arbitrarily many times, to distribute a set of values to multiple processors.

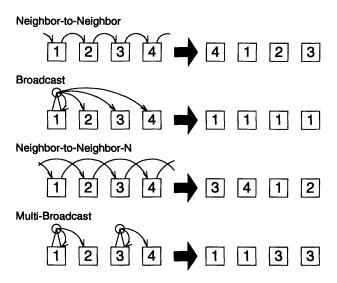

There are several modes of communication supported on the Princeton Engine.

They are represented schematically in Figure 2-3:

Neighbor-to-Neighbor The most natural option. Each processor passes a 16-bit word to either its left or right neighbor. All processors pass simultaneously either to the left or to the right.

**Broadcast** One processor is the broadcaster, and all other processors are receivers.

Neighbor-to-Neighbor-N Each processor passes a single datum to a processor N processors away. All processors do this in parallel, so this is as efficient as neighbor-to-neighbor communication in terms of information density in the ring.

Multi-Broadcast Some subset of the processors are designated broadcasters. Each broadcaster transmits values to all processors, including itself, between itself

Figure 2-3: Communication Options on the Princeton Engine: the right hand side depicts the contents of the communication register on each processor after a single step of the communication method.

and the next broadcaster.

The discussion of communication approaches will ignore the possibility of using broadcast (in either mode) because it requires more instructions than neighbor-to-neighbor to transfer the same amount of data. Consider the transmission of p data around a machine of size n, where each datum is the width of the communication channel. At the start of the communication each processor holds one datum, and at the end of the communication each processor has a copy of every datum. We can count the cycles required for each approach:

| approach             | parallelism | inst/datum   | total inst                                    |

|----------------------|-------------|--------------|-----------------------------------------------|

| neighbor-to-neighbor | n           | $1+2\cdot n$ | $p \cdot (1 + 2 \cdot n)/n \approx 2 \cdot p$ |

| broadcast            | 1           | 7            | $7 \cdot p$                                   |

The neighbor-to-neighbor approach is three to four times faster than broadcasting because it never has to pay the expense of waiting for data to propagate to all of the processors (the propagation delay between neighbors is small). The instructions per datum is  $1 + 2 \cdot n$  instead of  $3 \cdot n$  because each processor loads their datum in parallel

(1 instruction) then performs repeated shifts and non-destructive reads of the communication register. Similar results apply to neighbor-to-neighbor-N communication versus multi-broadcast communication.

## 2.3 Video I/O & Line-Locked Programming

The video I/O structure of the Engine assigns a processor to each column of the output video. Each processor is responsible for supplying all of the output pixels for the column of the display it is assigned to. The addition of an "Output Timing Sequence" (OTS) allows processors to be assigned regions somewhat more arbitrary than a column of the output video.

When the Princeton Engine was originally designed it was conceived of only as a video supercomputer. It was expected that the processing would be virtually identical for every pixel, and thus programs shouldn't operate on frames of video, they should operate on pixels, and every new pixel would constitute a new execution of the program! The paradigm is enforced by resetting the program counter at the beginning of each scanline.

Before the end of the scanline all of the processors must have processed their pixel and placed the result in their video output register. Because the program counter is reset at the beginning of each scanline all programs must insure that their longest execution path is within the scanline "instruction budget" of 910 instructions at 14MHz. This necessarily leads to some obscure coding, as complex operations requiring more than 910 instructions must be decomposed into a sequence of smaller steps that can individually occur within the instruction budget.

### 2.4 Implementation

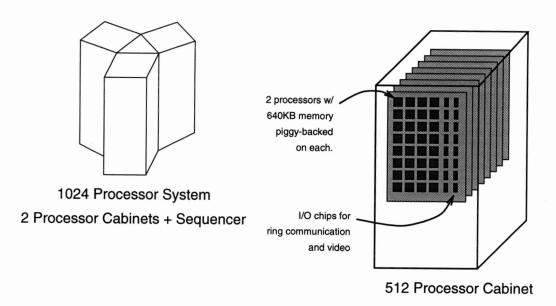

The processors are fabricated in a 1.5 micron CMOS process which allows two processors to be placed on the same die. The physical configuration of the machine is

Figure 2-4: **Princeton Engine:** each of the cabinets shown is approximately 2 feet wide, 3 feet deep and 5 feet high. The processors are cooled by a forced air system.

shown in Figure 2-4. The machine consists of 1 to 4 processor cabinets and a sequencer cabinet. The processor cabinets hold 512 processors each, along with their associated memory. The sequencer cabinet contains the sequencer which provides instructions to the processors, the video input and output hardware, a HiPPi interface, and a dedicated controller card with an ethernet interface.

The sequencer provides the instruction stream to the processors. Serial control flow (procedure calls) is handled by the sequencer. Conditional control flow is performed by evaluating the conditional expression on all the processors in parallel. Processor 0 then transmits its result to the sequencer via the interprocessor communication bus. The sequencer branches conditionally based on the value it sees.

High-level program control is performed via an ethernet connection and a dedicated controller. The controller allows the starting and stopping of the sequencer, and the loading of programs into sequencer memory and data into processor memory. Facilities for non-video input and output are not supported in the video processing mode of operation, so they are not discussed here. Similarly, the HiPPi input/output channel is not compatible with the realtime video processing mode of operation. A piece of the HiPPi implementation, a status register used for flow control, can be

used as a crude data-passing method between the controller and the processors. Data input through this channel is limited to relatively low rates (hundreds of values a second) as there is no handshaking provided.

The video input and output channel are distributed through a mechanism similar to the interprocessor communication register. Over the course of a video scanline the I/O chips sit in the background and shift in 2 composite video inputs and shift out 4 component video outputs. At the start of each scanline the user program can read the video input registers, and before the end of each line time the user program must write the video output registers.

# Chapter 3

# Graphics Pipeline

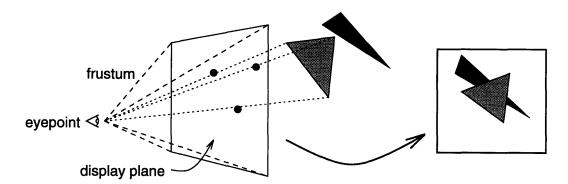

Polygonal rendering uses a synthetic scene composed of polygons to visualize a real scene or the results of computation or any number of other environments. Objects in the virtual space are defined as sets of 3D points and polygons defined with vertices at these points. In the most straightforward application of polygon rendering, these vertices are projected to the display plane (the monitor) via a transformation defined by a synthetic eyepoint and field of view, as shown in Figure 3-1. Subsequently the polygons defined by the set of vertices within the clip volume are rendered. Enhancements to this basic algorithm include occlusion, lighting, shading, and texture mapping.

Per-pixel occlusion insures that the polygons closest to the observer obscure poly-

Figure 3-1: **Synthetic Eyepoint:** a synthetic eyepoint and frustum defines both the set of visible objects and a display plane.

gons further away. Occlusion has been implemented a number of ways, but is most commonly implemented with a depth-buffer. By computing the depth of each vertex of a polygon we can interpolate these depths across the interior pixels of the polygon to compute the depth of any pixel. When we write a pixel to the display device we actually perform a conditional write, only writing the pixel if the surface fragment it represents is "closer" to the eye than any surface already rendered at that pixel.

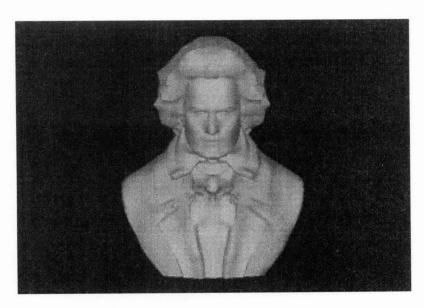

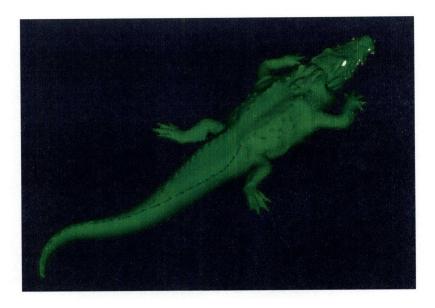

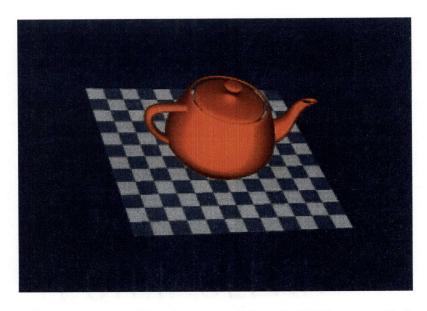

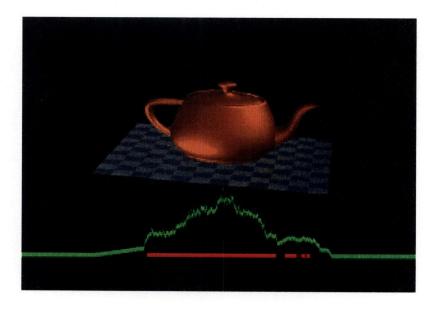

Lighting and shading greatly increase the realism of a scene by providing depth cues via changes in intensity across surfaces. Lighting assumes for any given polygon that it is the only polygon in the scene, so there are no shadows cast by the obstruction of light sources by other scene elements or reflection of light off of other surfaces. These effects are captured in other approaches to rendering such as ray-tracing, and are not generally implemented in polygonal renderers. Shading is performed by applying a lighting model, such as the Phong model [15], to a normal which represents the surface normal of the object being approximated at that point. The lighting model may either be applied at every pixel the polygon covers, by interpolating the vertex normals to determine interior normals, or it may be applied just to the vertex normals of the polygon, and the resulting colors interpolated across the polygon. The former approach (Phong shading) will often yield more accurate results and is free of some artifacts present in the latter approach (Gouraud interpolation) but it more computationally expensive. Figures 3-2, 3-3 and 3-4 are all examples of depth-buffered, Phong-lit, Gouraud-interpolated polygonal scenes.

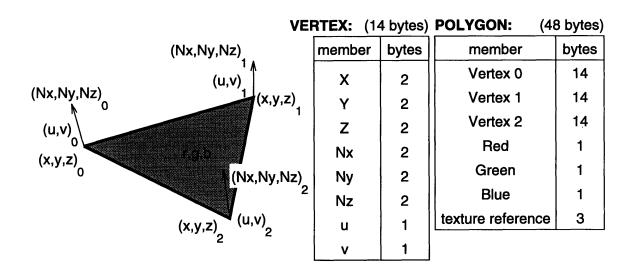

Texture mapping is a further enhancement to polygonal rendering. Instead of just associating a color with each vertex of a polygon, we associate a (u, v) coordinate in an image with each vertex. By careful assignment of these coordinates, we can create a mapping that places an image onto a set of polygons, for example: a picture onto a billboard, carpet onto a floor, even a face onto a head. Texture mapping, in a fashion analogous to shading and depth-buffering, linearly interpolates the texture coordinates at each vertex across the polygon. The color of a particular pixel within the polygon is determined by looking up the pixel in the texture map corresponding

Figure 3-2: Beethoven: a 5,030 polygon model with 4,021 non-culled polygons.

to the current values of u and v. Figure 3-5 shows a sample texture mapped scene along with the corresponding texture map in Figure 3-6.

## 3.1 UniProcessor Pipeline

All of the above is combined into an implementation of a polygonal renderer in a "graphics pipeline". The sequence of operations is a pipeline because they are applied sequentially. The depth-buffer provides order invariance, so the results of one computation (polygon) have no effect on other computations.

The uniprocessor pipeline consists of two stages: geometry and rasterization. The geometry stage transforms a polygon from its 3D representation to screen coordinates, tests visibility, performs clipping and lighting at the vertices, and calculates interpolation coefficients for the parameters of the polygon. The rasterization stage takes the computed results of geometry for a polygon and renders the pixels on the screen.

A more complete description of the uniprocessor pipeline is now presented.

Figure 3-3: Crocodile: a 34,404 polygon model with 25,270 non-culled polygons.

Figure 3-4: **Teapot:** a 9,408 polygon model with 6,294 non-culled polygons.

Figure 3-5: **Texture Mapped Crocodile:** a  $34{,}404$  polygon model with  $\approx 10{,}200$  visible polygons.

Figure 3-6: **Sample Texture Image:** the image of synthetic crocodile skin applied to crocodile.

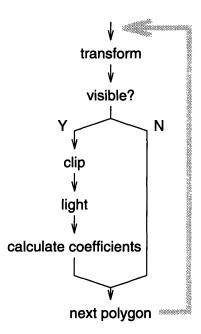

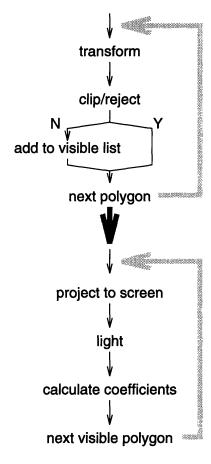

Figure 3-7: Uniprocessor Geometry Pipeline

#### 3.1.1 Geometry

The geometry stage can be formed into a pipeline of operations to be performed, as shown in Figure 3-7 and explained below.

Transform The vertices are projected to the user's point-of-view. This involves translation, so the 3D origin of the points becomes the user's location, and rotation, so that the line of sight of the observer corresponds to looking down the z-axis (by convention) in 3D. This transformation is performed with a matrix multiplication of the form:

$$\begin{bmatrix} x' \\ y' \\ z' \\ 1 \end{bmatrix} = \begin{bmatrix} a & b & c & t_x \\ d & e & f & t_y \\ g & h & i & t_z \\ 0 & 0 & 0 & 1 \end{bmatrix} \cdot \begin{bmatrix} x \\ y \\ z \\ 1 \end{bmatrix}$$

(3.1)

The use of a homogeneous coordinate system allows the translation to be included in the same matrix with the rotation.

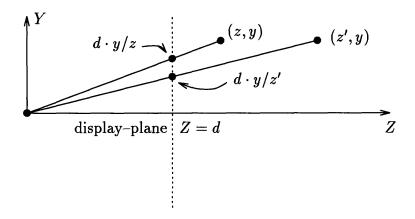

Figure 3-8: **2D Perspective Transformation:** the 2D case is analogous to the 3D case. Here the axes have been labeled to correspond to the standard 3D coordinate system.

The vertex eye-coordinates are now projected to the screen. This introduces the familiar perspective in computer (and natural) images, where distant objects appear smaller than closer objects. The screen coordinates of a vertex,  $(s_x, s_y)$  are related to the transformed 3D coordinates (x', y', z') by:

$$s_x = d\frac{x'}{z'} \tag{3.2}$$

$$s_y = d\frac{y'}{z'} \tag{3.3}$$

The 2D to 1D projection is shown in Figure 3-8. The 3D to 2D projection is identical, just repeated for each coordinate.

Clipping & Rejection Once the polygons are transformed to eye-coordinates they must be clipped against the viewable area. The rays cast from the eye-point of the observer through the four corners of the viewport define a viewing frustum. All polygons outside of this frustum are not visible and need not be rendered. Polygons that intersect the frustum are partially visible, and are intersected with the visible portion of the display plane, or "clipped." Clipping takes a polygon and converts it into a new polygon that is identical within the viewing

frustum, and is bounded by the frustum.

Backface culling culls polygons based on the face of the polygon oriented towards the observer. Each polygon has two faces, and of course you can only see one of the two faces at any time. For example, if we constructed a box out of polygons we could divide the polygon faces into two sets, a set of faces potentially visible for any eyepoint inside the box, and a set of faces potential visible for any eyepoint outside of the box, and the union of these sets is all the faces of all of the polygons. If we know a priori that the viewpoint will never be interior to the box we *never* have to render any of the faces in the interior set. Polygons that are culled because their "interior" face is towards the viewer are said to be "backfacing" and are backface culled.

Lighting Lighting is now applied to the vertex normals. A typical lighting model includes contributions from diffuse (background or ambient) illumination, distant illumination (like the sun) and local point illumination (like a light bulb). Polygons are assigned properties including color (RGB), shininess and specularity which determine how the incident light is reflected. See Foley and van Dam [8] pg. 477 for a description of lighting models.

The normal associated with each vertex may also be transformed, depending on the viewing model. If the model of interaction assumes the viewer is moving around in a fixed space, then the lighting should remain constant, as should the vertex normals used to compute lighting. However, if the model assumes that the object is being manipulated by an observer who is sitting still then the normals but also be transformed. A normal is represented by a vector

$$\begin{bmatrix}

n_x \\

n_y \\

n_z \\

0

\end{bmatrix}$$

(3.4)

and is transformed by the inverse transpose of the transformation matrix.

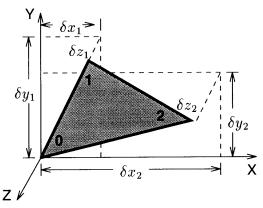

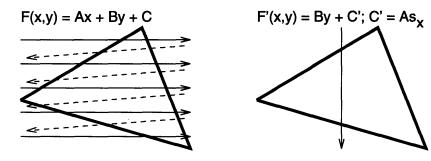

Linear Equation Setup Rasterization is performed by iterating a number of linear equations of the form Ax + By + C. The coefficients of these equations represent the slopes of the values being iterated along the x and y axes in screen space. A typical system interpolates many values, including the color of the pixel, the depth of the pixel, and the texture map coordinates.

The computation of these linear equation coefficients, while straightforward, is time consuming. It requires both accuracy and dynamic range to encapsulate the full range of values of interest. Figure 3-9 shows the form of the computation for the depth. The same equations are evaluated for each component to be interpolated across the polygon.

Due to the similarity of the work performed (lots of arithmetic) and in anticipation of the parallel discussion, I include linear equation setup with the geometry pipeline, but it could also be considered the start of the rasterization stage.

The rasterization stage described next renders the set of visible polygons by iterating the linear equations calculated during the geometry stage.

#### 3.1.2 Rasterization

Rasterization must perform two tasks. It must determine the set of pixels that a polygon overlaps (is potentially visible at) and for each of those pixels it must evaluate the various interpolants associated with the polygon.

The typical uniprocessor software implementation of polygon rasterization analyzes the polygon to be rendered and determines for each horizontal scanline the left-most and right-most edge of the polygon. The algorithm can then evaluate the intersection of the polygon edges with any given scanline and rasterize the pixels within. This algorithm is efficient, as it examines only the pixels within the polygon and it is easy to determine the left and right edges.

Linear equation for an edge from vertex 0 to vertex 1:

$$E(x,y) = Ax + By + C (3.5)$$

$$A = -\delta y_1 \tag{3.6}$$

$$B = \delta x_1 \tag{3.7}$$

$$C = x_0 \cdot y_1 - y_0 \cdot x_1 \tag{3.8}$$

(3.9)

Linear equation for depth:

$$Z(x,y) = Ax + By + C (3.10)$$

$$\Gamma = \delta x_1 \cdot \delta y_2 - \delta y_1 \cdot \delta x_2 \tag{3.11}$$

$$A = (\delta z_1 \cdot \delta y_2 - \delta y_1 \cdot \delta z_2)/\Gamma \tag{3.12}$$

$$B = (\delta x_1 \cdot \delta z_2 - \delta z_1 \cdot \delta x_2)/\Gamma \tag{3.13}$$

$$C = z_0 + A \cdot x_0 + B \cdot y_0 \tag{3.14}$$

(3.15)

Figure 3-9: **Polygon Linear Equations:** The edge equations are unnormalized as only the sign of subsequent evaluations is important. Accurate magnitude is required for the other equations, resulting in more complex expressions for the coefficients.

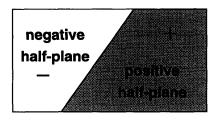

Figure 3-10: **Triangle Definition by Half-Plane Intersection:** a positive and negative half-plane are defined by a line in screen space. The interior of a polygon is all points in the positive half-plane of all the edges. Diagram is after [16].

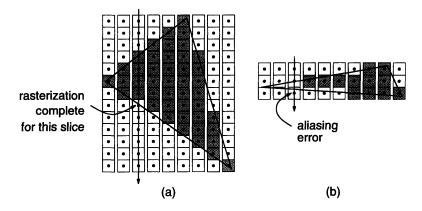

Typical hardware implementations, for example [13], take a different approach. Each polygon can be defined as the intersection of the n semi-finite plains bound by the n edges of the polygon, as explained by Pineda in [16]. We can define the equation of a line in 2D as Ax + By + C = 0 and thus a half-plane is given by  $Ax + By + C \ge 0$ . With the appropriate choice of coefficients we can insure that the equations of the n semi-finite plains will all be positively (or negatively valued) within the polygon. Figure 3-10 depicts this approach.

This provides us with a very cheap test (the evaluation of one linear equation per vertex) to determine if any pixel is inside of a polygon. Furthermore, we can cheaply bound the set of pixels that are potentially interior to the polygon as the set of pixels interior to the bounding box of the polygon. This approach results in examining more pixels then will be rendered, as the bounding box is generally a conservative estimate of the set of pixels in a polygon. For triangles at least half of the pixels examined will be exterior to the polygon. Experimentally this has been determined to be a good tradeoff against the higher computational complexity of span algorithms because SIMD implementations benefit from a simple design with few exceptional cases.

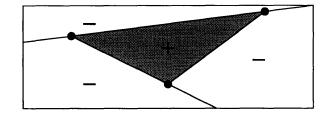

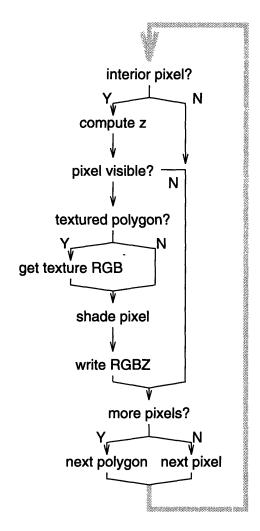

The rasterization process is actually poorly described as a pipeline, because it consists of a series of early—aborts, at least in its serial form. Figure 3-11 shows a typical view of the rasterization process. The next pixel operation takes step horizontally until it reaches the right side of the bounding box, and then takes a vertical step and

Figure 3-11: Uniprocessor Rasterization

returns to taking horizontal steps. The interior pixel test is the simple linear equation test shown in Figure 3-10. Compute Z evaluates the linear equation for depth and the pixel visible test determines if this pixel is closer to the observer than the current pixel in the frame buffer. If so it is then shaded and written to the frame buffer. The procedure for texture mapped polygons is identical, except the pixel that gets shaded is retrieved from a texture map, rather than just being the color of the polygon.

Considerable complexity has been swept under the rug in this view of rasterization. Most significant is the texture mapping operation, which is relatively complex in practice. The simplest way to perform texture mapping is "point sampling". Point sampling takes the color of a texture mapped pixel as the color of the closest texel (texture pixel) to the current interpolated texture coordinates. A more pleasing method uses a weighted combination of the 4 closest texels from the texture map. A yet more complex and pleasing approach is achieved with MIP-Mapping, described by Lance Williams in [22]. All of these methods attempt to correct the inaccuracy of point sampling a transformed image. A mathematically correct resampling of the input image would involve complex filtering and difficult computation. Approximation methods attempt to correct the sampling errors at lower cost, usually with acceptable visual results.

#### 3.1.3 Details

There are a few auxiliary details which accompany the rendering process which have been ignored so far. Most importantly, there is generally a way for the user to interact with the system. A similarly important subject is double-buffering.

The particular input method provided by the system is not important, just some method must exist. These methods vary greatly, from being able to modify the polygon database and view matrix continually and interactively, to simply executing a script of predefined viewpoints.

Double-buffering is used to hide the machinery of polygon rendering. Users are (usually) only interested in the final rendered image, not all the work that goes into

it. To this end, two frame buffers are used. One completed frame buffer is displayed, while the second frame buffer is rendered. When the rasterization of all polygons is complete, the frame buffers are exchanged, usually during the vertical retrace interval of the display, so the images don't flicker distractingly.

## 3.2 MultiProcessor Pipeline

The parallel version of the graphics pipeline differs significantly from the uniprocessor pipeline. There are now n processors working on the rendering problem instead of a single processor, and optimally we would like a factor of n speedup. How do we divide the work among the processors? Given that we have divided the work, how do we execute it in parallel? While these questions appear superficially obvious, they are not. By parallelizing the algorithm we have exposed that it is actually a sorting problem, resolved by the depth-buffer in the uniprocessor system, but presumably resolved in parallel in a multiprocessor implementation.

It is relatively obvious how to partition the geometry work. Instead of giving p polygons to 1 processor, give p/n polygons to each processor, and allow them to proceed in parallel. This should yield a factor of n speedup, which is the most we can hope for. The rasterization stage is less obvious. Do we let each processor rasterize 1/n of the polygons? Do we let each processor rasterize 1/n of the total pixels? When a polygon has to be rasterized do all processors work on it at the same time?

We would also like to divide the work as evenly as possible among the processors. If we put more work on any one processor we have compromised the performance of our system. However, it is not always the case that the same number of polygons on each processor corresponds to the same amount of work, if, for example, the polygons vary in size.

Rasterization is actually a sorting algorithm based on screen location and depth. If we divide the work across multiple processors we must still perform this sorting operation. The addition of communication to the rendering pipeline enables us to resolve the sorting problem and render correct images, that is, the same images a uniprocessor renderer would generate.

Because the rasterization sorting issue has forced us to introduce communication, our first departure from the uniprocessor pipeline, it is natural to start by discussing its parallelization.

#### 3.2.1 Communication

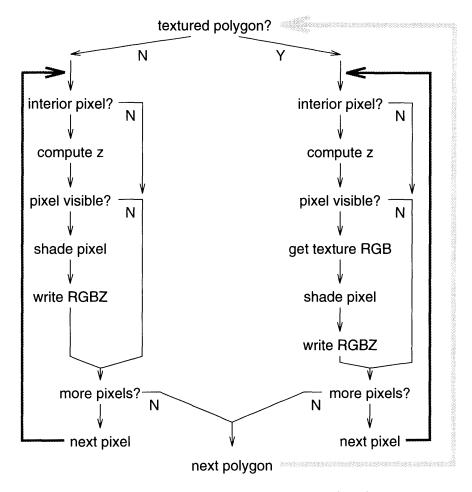

Given that we have to perform communication to produce the final image, we must choose how we parallelize the rasterization. This choice bears heavily on how the image is generated and will determine what communication options are available to us. There are two ways we could divide the rasterization among the processors:

- 1. give each processor a set of pixels to rasterize, or

- 2. give each processor a set of polygons to rasterize.

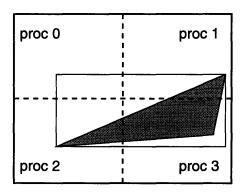

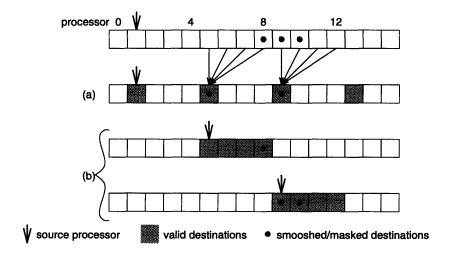

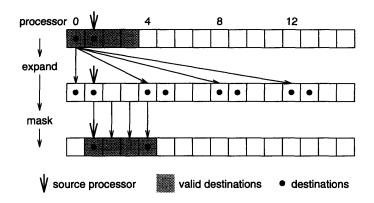

If we choose the first option then the sorting problem is solved by making the pixel sets disjoint, so a single processor has all the information necessary to correctly generate its subset of the pixels. This requires communication before rasterization, so that each processor may be told about all the polygons that intersects its pixel set. These approaches are referred to as "sort-first" and "sort-middle" because the communication occurs either first, before geometry and rasterization, or in the middle, between geometry and rasterization.

If we choose the second option then the polygons rasterized on any given processor will overlap some subset of the display pixels, and there may be polygons on some other processor or processors that overlap some of the same display pixels. So if we parallelize the rasterization by polygons rather than pixels then the sorting problem must be solved after rasterization. This approach is referred to as "sort–last" because the sorting occurs after both rasterization and geometry.

Figure 3-12 shows these communication options schematically. In all cases the communication is shown as an arbitrary interconnection network. Ideally we would

Figure 3-12: **Sort Order:** some possible ways to arrange the polygon rendering process. Figure is after [13].

like this network to be a crossbar with infinite bandwidth, so that the communication stage requires no time to execute. Of course in practice we will never obtain such a communication network.

#### Sort-First

Sort-first performs communication before geometry and rasterization. The screen is diced up into a set of regions and each processor is assigned a region or regions, and rasterizes all of the polygons that intersect its regions. All of the regions are disjoint, so the final image is simply the union of all the regions from all the processors, and no communication in necessary to combine the results of rasterization. The communication stage must give each processor a copy of all the polygons that overlap its screen area. This information can only be determined after the world-space to screen-space transformation is made, so there is generally some non-trivial amount of computation done before the communication is performed.

#### Sort-Middle

Sort-middle also assumes that each processor is rasterizing a unique area of the screen. However, the communication is now done after the geometry stage, so rather than communicating the polygons themselves, we can directly distribute the linear equation coefficients that describe the edges of the polygon on the screen along with the depth, shading, etc.

#### Sort-Last

Sort-last assigns each processor a subset of the polygons to rasterize, rather than a subset of the pixels. As the polygons rasterized on different processors may overlap arbitrarily in the final image, the composition is performed after rasterization. Each processor can perform the geometry and rasterization stage with no communication whatsoever, only communicating once they have generated all of their pixels for the output image.

#### Comparison

These three sorting choices all incur different tradeoffs, and the particular choice of algorithm will depend on both details of the machine (speed, number of processors, etc.) and the size of the data set to be rendered.

Sort-first communication can exploit temporal locality. Generally a viewer will navigate a scene in a smooth and continuous fashion, so the viewpoint changes slowly, and the location of each polygon on the screen changes slowly. If the location of polygons is changing slowly then the change in which polygons each processor will rasterize will be small, and sort-first will require little communication. This is most obvious if the viewer is standing still, in which case the polygons are already correctly sorted from rendering the previous frame to render the current frame. However, sort-first incurs the overhead of duplicated effort in the geometry stage. Every polygon has its geometry computation performed by *all* processors whose rasterization regions it overlaps. For large parallel systems, which will have correspondingly small rasterization

regions, this cost could become relatively high.

Sort-middle communication calculates the geometry only once per polygon and thus will not have the duplication of effort incurred by sort-first. However, sort-middle must communicate the entire polygon database for each rendered frame, which is presumably substantially more expensive than a method which exploits temporal locality.

Sort-last communication traffics in pixels instead of polygons, and has the interesting property that the amount of communication is constant. Each processor will have to communicate no more than a screen's worth of pixels to composite the final image, so as the polygon database grows arbitrarily large sort-last will offer the cheapest communication. Although this constant bound on communication is useful, it is shown later to be a very large amount of communication compared to sort-first and sort-middle for our scenes of interest.

We have laid a framework for the discussion to follow, and, while there are interactions, the actual geometry and rasterization stages are to some extent independent of the communication topology. The communication topology will determine precisely what polygons are computed on what processor for each stage, but will have little effect on the nature of the computation itself. We will defer the actual choice of, and justification for, a communication topology until Chapter 4.

### 3.2.2 Geometry

The geometry calculations consists of five distinct steps:

- transform

- clip/reject

- project to screen coordinates

- light

- linear equation setup

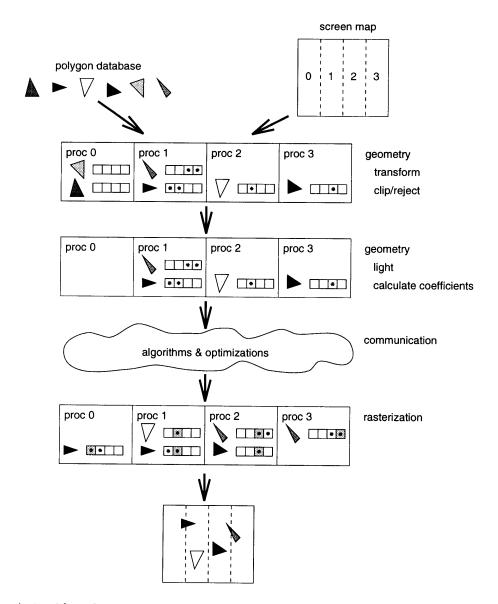

Figure 3-13: **SIMD Geometry Pipeline:** the pipeline is split between clipping and lighting.

Each of these stages has an upper-bound on the amount of work performed per polygon. The calculations to be performed for each polygon, while executing on different data and yielding different results, are identical algebraically. The execution of each processor over its subset of the polygons, whether obtained from the input polygonal database differently, or from the results of sort-first communication, will be identical, and the execution time will be determined by the processor with most polygons to process.

Often after the clip/reject stage a very large number of processors will have discarded their polygon and have nothing to do while the other processors compute. This will achieve poor utilization of the processors and a less than optimal speedup

for the geometry stage. A revised geometry pipeline appropriate for parallel execution is shown in Figure 3-13. By breaking the geometry pipeline into two separate pieces and queueing the work between them we will first perform work proportional to the maximum number of polygons on any processor, then work proportional to the maximum number of visible polygons on any processor. The cost of the second stage of the pipeline per polygon will prove to be substantially higher than the first stage, so if the number of visible polygons is much smaller than the total number of polygons the savings could be substantial. Section 7.1 provides a discussion of this implementation issue.

#### 3.2.3 Rasterization