# Study of Sub-0.5 $\mu m$ SOI-with-Active-Substrate (SOIAS) Technology for Ultra-Low Power Applications

by 1 3/ 3

Isabel Y. Yang

B.S., Massachusettes Institute of Technology (1990)

M.S., Massachusettes Institute of Technology (1993)

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 1996

© Massachusetts Institute of Technology 1996. All rights reserved.

JACOACHUSETTS LISTING E

Author

Department of Electrical Engineering and Computer Science

September, 1996

Certified by

Dimitri A. Antoniadis

Professor of Electrical Engineering

Thesis Supervisor

Accepted by

Frederic R. Morgenthaler

Chairman, Departmental Committee on Graduate Students

# Study of Sub-0.5 $\mu$ m SOI-with-Active-Substrate (SOIAS) Technology for Ultra-Low Power Applications

by

#### Isabel Y. Yang

Submitted to the Department of Electrical Engineering and Computer Science on September, 1996, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

#### Abstract

In this thesis, a novel fully depleted (FD) Silicon-On-Insulator (SOI) based technology was developed for ultra-low power applications. This technology is called Silicon-On-Insulator-with-Active-Substrate (SOIAS). The SOIAS technology, in general, enables the integration in the third dimension of gates and interconnects by using buried under-layers. In this work, the buried under-layer served as a second gate, a back-gate, to the conventional single-gate FD SOI device. The function of the backgate is to modulate the threshold voltage of the normal device. Since supply voltage scaling to 1V and below has been identified as a key approach for energy efficient high performance computing, the threshold voltage needs to be scaled concomitantly in order to maintain high performance levels. However, lowering of the threshold voltage results in high static leakage energy. In order to meet the opposing requirements of high performance and low power, a dynamic threshold voltage control scheme was proposed utilizing the SOIAS technology. This work covers the development of the SOIAS substrate fabrication, material characterization, CMOS device and circuit fabrication which also includes the integration of an x-ray lithography module for scaling into the deep submicrometer regime, device and circuit characterization, and energy evaluation of the SOIAS technology for low power applications.

The technology to fabricate the SOIAS wafers was developed using two different approaches; both approaches take advantages of the already existing technologies developed for SOI and bulk. The first method uses the bond-etch-back (BESOI) process, and the second method is a novel bonded SIMOX process. The process complexity is reduced in the bonded SIMOX approach with very good silicon film thickness uniformity control as compared to the BESOI method. The material quality of the former, however, is slightly inferior to that of the latter. Compared to bulk and conventional SIMOX in terms of electrical properties (e.g. mobility, intrinsic oxide breakdown, and interface state density), the BESOI SOIAS substrates are equal or even superior, and the bonded SIMOX SOIAS wafers are slightly inferior.

The implementation of a CMOS process on SOIAS substrates was demonstrated, and the integration of the x-ray lithography module was successful. A mix and match

scheme was developed and implemented to match the various lithography tools used in this process, and both positive and negative chemically amplified resist processes were optimized for 0.1  $\mu$ m features sizes. Device and simple circuit fabrication was successful. Approximately 3 decades switch in off current and 1.5X increase in drive current was achieved for both NMOS and PMOS at  $V_{DS}$  of 1 V. Independent control of NMOS and PMOS back-gates were verified with 36% change in speed with 250 mV switch in the threshold voltage at 1 V supply voltage. Large dynamic threshold voltage control range was demonstrated, and the threshold voltage design band of 250 mV fits well within this range. Threshold voltage control is not deteriorated for effective channel length scaling down to approximately  $0.2\mu$ m. Quasi-static control of threshold voltage at 20 MHz was verified.

Having demonstrated the technology, a theoretical energy consumption model was developed. This model was used to compare the SOIAS technology against a benchmark convention SOI technology. System and architecture parameters as well as technology design parameters were examined. The dynamic threshold voltage switching scheme is proposed to be implemented at the functional module level (e.g. adder, shifter and multiplier). The SOIAS technology was found to be most suitable for systems which operate in burst-mode such as the microprocessor of an x-server. Significant energy savings is expected for the SOIAS over the SOI technology for event-driven systems. The energy consumption model was also used in conjunction with measured static energy, dynamic energy, and delay data for optimization of threshold and power supply voltages at various system activities. From this analysis, the conclusion was that adaptively adjusting the threshold and supply voltages as the system activity changes can potentially allow energy efficient computation at all times.

Thesis Supervisor: Dimitri A. Antoniadis Title: Professor of Electrical Engineering

Thesis Supervisor: Henry I. Smith Title: Professor of Eletrical Engineering

### Acknowledgments

Initially, the SOIAS project was not funded. With the help of various supporters, I was able to carry through most if not all of the research work. I am very grateful to Lisa Allen of IBIS Corp. for providing us with SIMOX wafers, Charles Goodwin of AT&T for helping with the wafer thinning process, D.P. Mathur of Hughs for providing the localized plasma thinning, and Craig Keast of MIT Lincoln Laboratory for helping with the CMP. I would also like to acknowledge AT&T for providing me with a graduate fellowship, without it I would not have had the freedom to pursue this work.

I was very fortunate to come under the guiding influence of my advisors. From them, I have learned how to be a good investigator, to think scientifically, and that no detail is too small to ignore. They gave me the freedom to pursue my work and establish my individuality, and at the same time offered advice and guidance whenever I needed help. I would like to thank Professor Dimitri Antoniadis for his support, and for imparting some of his infinite wisdom and knowledge to me. I would like to thank Professor Henry Smith for his technical and spiritual support, for his boundless enthusiasm, and for sharing his great love of science. I would also like to thank Professor Anantha Chandrakasan for his tutelage and insights on circuit and system design issues.

I would like to thank Lalitha Parameswaran for her valuable advice on silicon wafer bonding, Paul Tierney, Tim Tyson, Brian Foley, Dan Adams, Dick Westberg, Jim Bishop, Joe DiMaria, Joe Walsh, Bernard Alamariu, Pat Burkhart, Octavio Hurtado, Linus Cordes, and Vicki Diadiuk for their technical support and patience. My special thanks to Jimmy Carter and Mark Mondol for giving me the freedom to do crazy experiments in the NSL.

Through the years I've spent at MIT, I have met and befriended some of the brightest people who came to this fine institution. My thanks goes to: Dr. Lisa Su for her friendship and for those endless philosophical discussions that made life so interesting, Dr. Vincent Wong for his friendship and for being my NSL lab buddy, Dr.

Julie Tsai for being my apartment mate and for remaining my friend afterwards, Dr. Jarvis Jacobs for all the computer support he provided, Drs. Martin Burkhardt and Hang Hu for their help in the NSL, Melanie Sherony for her friendship and for lending a sympathetic ear whenever I needed to let out some steam, Mike Lim and Tim Savas for keeping me amused and up to date on the latest gossip, Euclid Moon and Juan Ferrera for their help in the NSL, and for just being a bunch of nice guys, Andy Wei and Mark Armstrong for their help on various occasions with Naxos, Siva Naren and Anthony Lochtefeld for their participation and interest in the SOIAS project.

I am also grateful to my friends who shared the first half of my journey through MIT and who continued to support me even after they have moved on: Winnie Chan, May Yip, Alice Yee, Frances Lam, Kay Hsu, and Rebecca Kao.

To my parents, I owe everything. A mere "thank you" to acknowledge their sacrifices can hardly do justice to the immense gratitude I feel. I hope that my accomplishments have made them proud. Last, but not least, a big thanks goes to my husband, Bill Chu. I would not have made it this far without his constant support, encouragement and infinite patience. His belief in me never wavered even during the most trying times when I had serious doubts about myself. I hope I will have the opportunity to be his "pillar of strength" as he has been to me. I look forward to the life we will share together.

# Contents

| 1 | Int   | roduct  | ion                                                     | 17 |

|---|-------|---------|---------------------------------------------------------|----|

|   | 1.1   | Thesis  | s Organization                                          | 18 |

| 2 | Bac   | kgrou   | nd                                                      | 20 |

|   | 2.1   | The N   | Need for Low Power                                      | 20 |

|   | 2.2   | Dynai   | mic Threshold Voltage Control Concept                   | 22 |

|   | 2.3   | SOI T   | Cechnology                                              | 23 |

|   |       | 2.3.1   | SOI Dual-gated Devices                                  | 24 |

|   | 2.4   | Comp    | arison of $V_T$ Controllability in Bulk and SOI MOSFETs | 27 |

|   |       | 2.4.1   | Long Channel Device                                     | 27 |

|   |       | 2.4.2   | Short Channel Device                                    | 29 |

|   | 2.5   | SOIAS   | S Device Structure                                      | 33 |

| 3 | Silie | con-Or  | n-Insulator-with-Active-Substrate: SOIAS                | 36 |

|   | 3.1   | Silicon | Direct Bonding                                          | 36 |

|   |       | 3.1.1   | The Bonding Mechanism                                   | 37 |

|   |       | 3.1.2   | Voids                                                   | 40 |

|   |       | 3.1.3   | Bond Strength                                           | 41 |

|   | 3.2   | SOIAS   | S Technology                                            | 43 |

|   |       | 3.2.1   | SOIAS Wafer Fabrication                                 | 44 |

|   |       | 3.2.2   | Bonded Interface Evaluation                             | 47 |

|   |       | 3.2.3   | SOIAS Materials Characterization                        |    |

| 4 | X-r | ay Lithography Integration in CMOS Process            | <b>56</b> |

|---|-----|-------------------------------------------------------|-----------|

|   | 4.1 | Mix-and-Match Scheme                                  | 57        |

|   |     | 4.1.1 Experimental Procedure                          | 58        |

|   |     | 4.1.2 Coarse Features and E-beam Field Marks Transfer | 58        |

|   |     | 4.1.3 E-beam Patterning of Fine Features              | 61        |

|   | 4.2 | X-ray Lithography Exposure and Alignment Procedure    | 63        |

|   | 4.3 | Gate Pattern Transfer Process                         | 70        |

|   |     | 4.3.1 Negative Resist Process of SAL-601              | 70        |

|   |     | 4.3.2 Positive Resist Process of ESCAP-X              | 73        |

|   | 4.4 | Device Results                                        | 75        |

|   |     | 4.4.1 Bulk Devices                                    | 75        |

|   |     | 4.4.2 SOIAS Devices                                   | 79        |

| 5 | SO  | AS CMOS Devices                                       | 81        |

|   | 5.1 | Fabrication                                           | 81        |

|   | 5.2 | Device Measurement Results                            | 86        |

|   | 5.3 | Dynamic Operation                                     | 87        |

|   | 5.4 | SOIAS Circuits                                        | 88        |

| 6 | SO  | AS for Ultra-Low Power Applications                   | 97        |

|   | 6.1 | Energy Consumption Model for SOIAS                    | 97        |

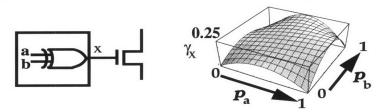

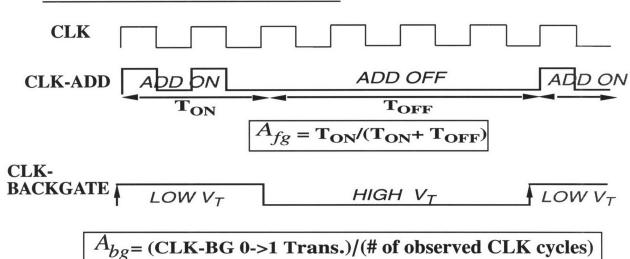

|   |     | 6.1.1 Activity Factor Definitions                     | 100       |

|   |     | 6.1.2 Simulation Criteria                             | 102       |

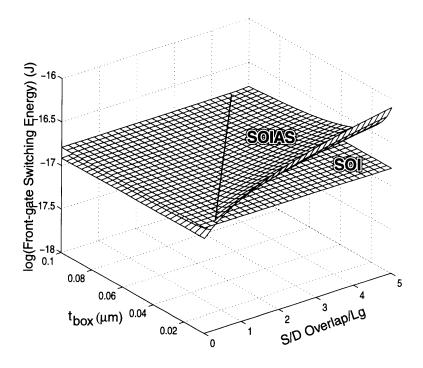

|   | 6.2 | Energy Trade-offs in Technology Design Space          | 103       |

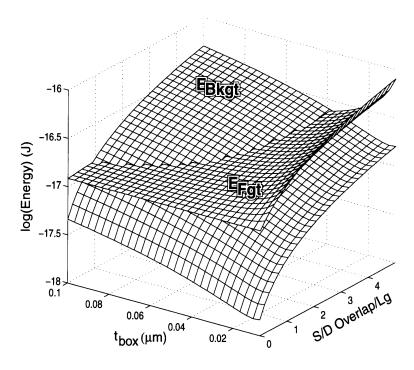

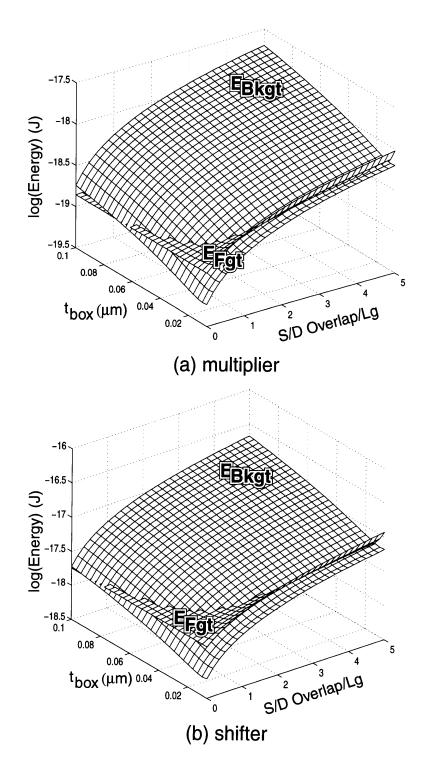

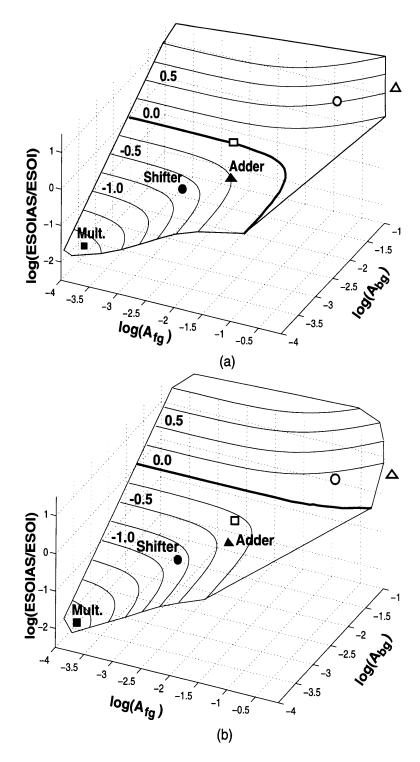

|   | 6.3 | Energy Trade-offs in $A_{bg}$ and $A_{fg}$ Space      | 105       |

| 7 | Ult | ra-Low Voltage Design Space                           | 113       |

|   | 7.1 | Measurement of Energies                               | 114       |

|   | 7.2 | Variable $V_{DD}$ and $V_T$ :                         | 117       |

|   | 7.3 | Dynamic Threshold Voltage Control                     | 120       |

| 8 | Sun | ımarv                                                 | 199       |

# List of Figures

| 2-1 | Electron potential of dual-gated device in the subthreshold region and                            |    |

|-----|---------------------------------------------------------------------------------------------------|----|

|     | strong inversion [11]                                                                             | 26 |

| 2-2 | Measured threshold voltage control by either body bias in bulk or back-                           |    |

|     | gate bias in SOIAS. The open triangles represent a bulk NMOS device                               |    |

|     | with super-steep retrograde (SSR) channel doping; $L_{eff}$ is approxi-                           |    |

|     | mately 0.75 $\mu$ m. The filled triangles represent a single step channel                         |    |

|     | doping device, $L_{eff}$ is approximately 0.7 $\mu m$ . Although the latter has                   |    |

|     | a lower quiescent $V_T$ , the body factor is much smaller than the SSR                            |    |

|     | design. The SOIAS device dynamic $V_T$ range is larger than both of                               |    |

|     | the bulk devices. $\mathcal{L}_{eff}$ of the SOIAS device is approximately 0.4 $\mu \mathrm{m}$ . | 30 |

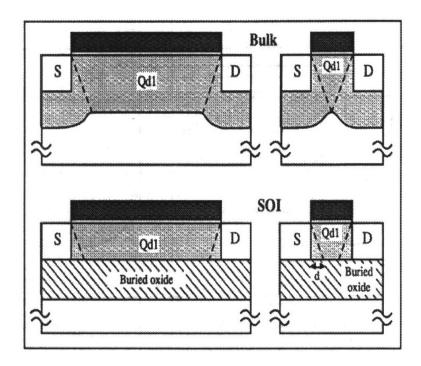

| 2-3 | Charge sharing in bulk and FD SOI devices [23]                                                    | 31 |

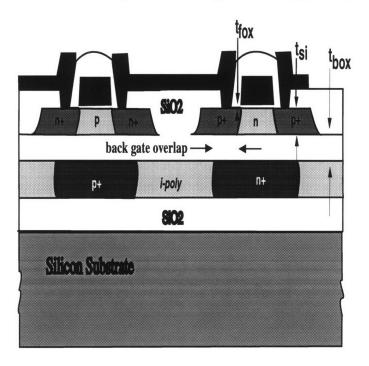

| 2-4 | SOIAS back-gated CMOS device schematic                                                            | 33 |

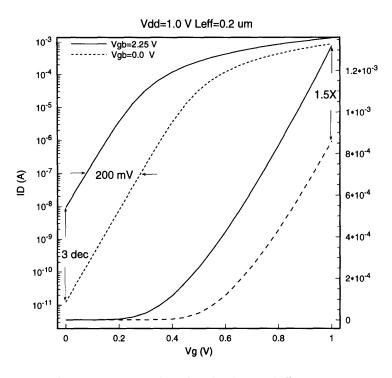

| 2-5 | Simulated subthreshold I-V at different back-gate biases                                          | 34 |

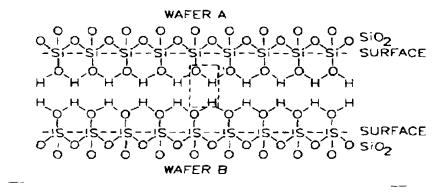

| 3-1 | Hydrogen bond formation between two hydrophilic surfaces [26]                                     | 37 |

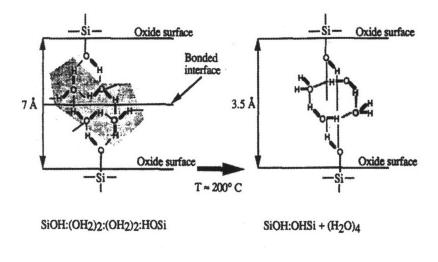

| 3-2 | The bonding mechanism proposed by Stengl et al showing the transi-                                |    |

|     | tion from weak hydrogen bonding to covalent Si-O-Si bonding at two                                |    |

|     | different temperatures [39]                                                                       | 38 |

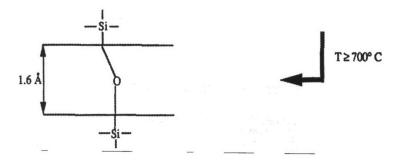

| 3-3 | (a)Fracture strength for SiO <sub>2</sub> to SiO <sub>2</sub> bonding [47]. (b)Fracture strength  |    |

|     | for Si to Si bonding [27]                                                                         | 42 |

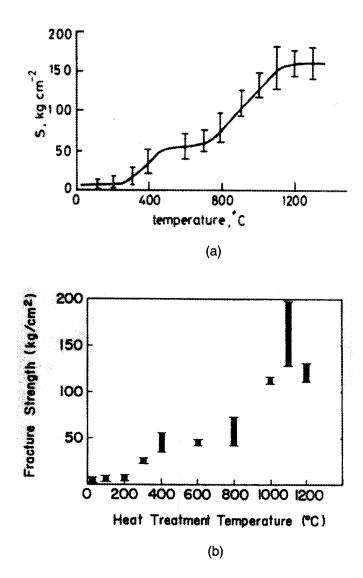

| 3-4 | Surface energy of SiO <sub>2</sub> to SiO <sub>2</sub> bonded interface (open symbols) [36],      |    |

|     | and that of Si to Si bonded interface (filled symbols) [50]                                       | 43 |

|     |                                                                                                   |    |

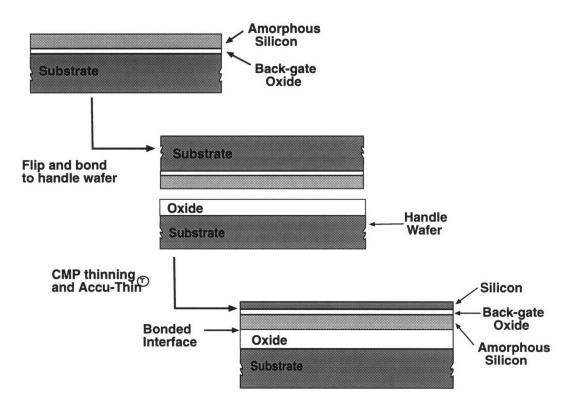

| 3-5  | The bond and etch back (BESOI) process for fabricating SOIAS sub-                    |    |

|------|--------------------------------------------------------------------------------------|----|

|      | strates                                                                              | 45 |

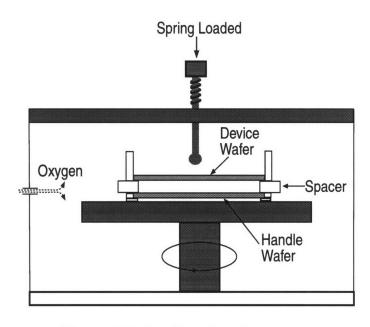

| 3-6  | bonding chamber                                                                      | 46 |

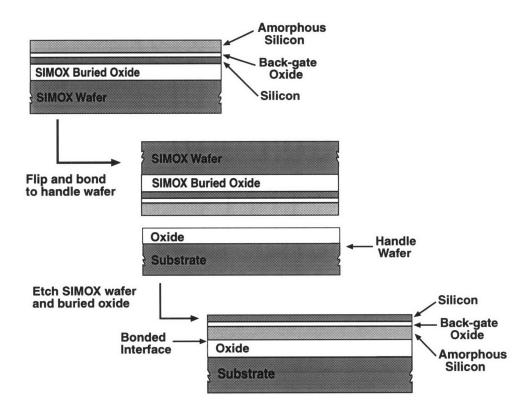

| 3-7  | The bonded SIMOX process for fabricating SOIAS substrates                            | 47 |

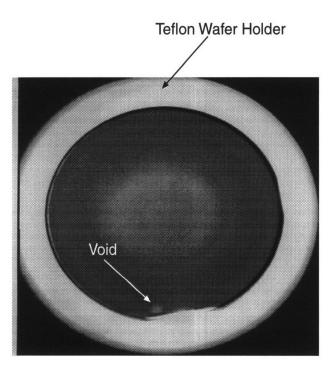

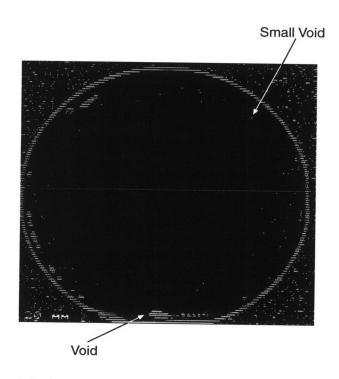

| 3-8  | Infrared image of bonded wafers                                                      | 48 |

| 3-9  | Acoustic microscope image of bonded wafers                                           | 49 |

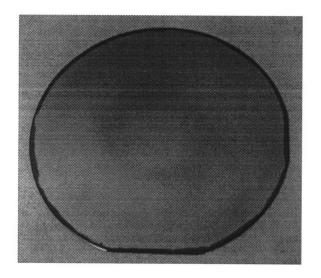

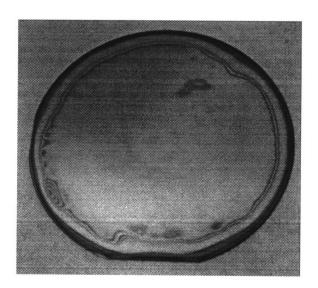

| 3-10 | (a)SOIAS wafer prepared by the bonded SIMOX process. (b)SOIAS                        |    |

|      | wafer prepared by the BESOI method. The absence of fringes indicates                 |    |

|      | the better film thickness uniformity of the bonded SIMOX SOIAS as                    |    |

|      | compared to the BESOI SOIAS                                                          | 50 |

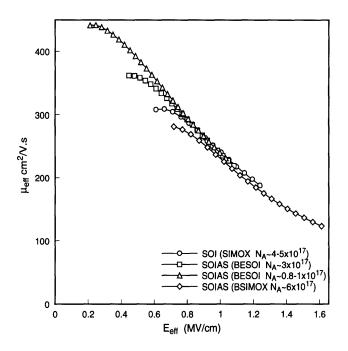

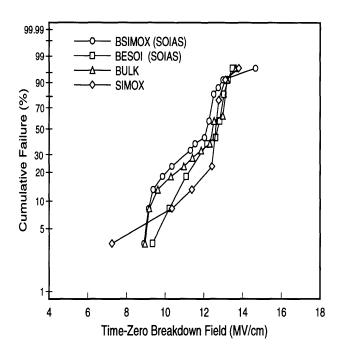

| 3-11 | $Comparison\ of\ effective\ electron\ mobility\ for\ various\ substrate\ materials.$ | 52 |

| 3-12 | Comparison of cumulative percentage failure of 10x10 $\mu m$ transistors             |    |

|      | for different substrates                                                             | 53 |

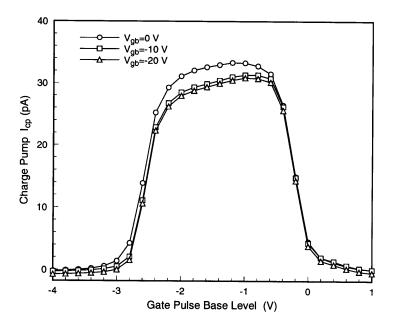

| 3-13 | Charge pumping current as a function of back-gate bias on a SOIAS                    |    |

|      | device                                                                               | 54 |

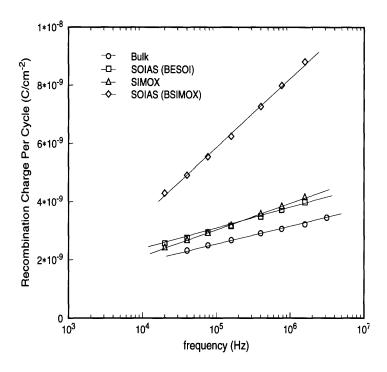

| 3-14 | Recombination charge per cycle as a function of frequency for different              |    |

|      | substrate materials                                                                  | 55 |

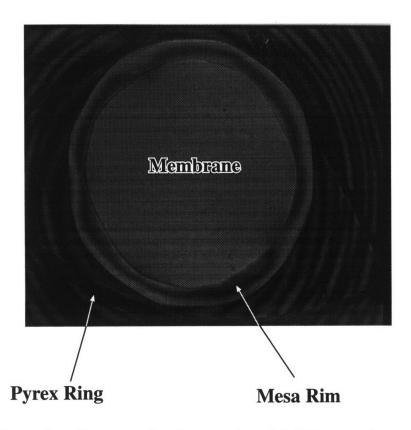

| 4-1  | Fizeau interferogram showing an ultra-flat $SiN_X$ membrane, mesa-style              |    |

|      | x-ray mask                                                                           | 59 |

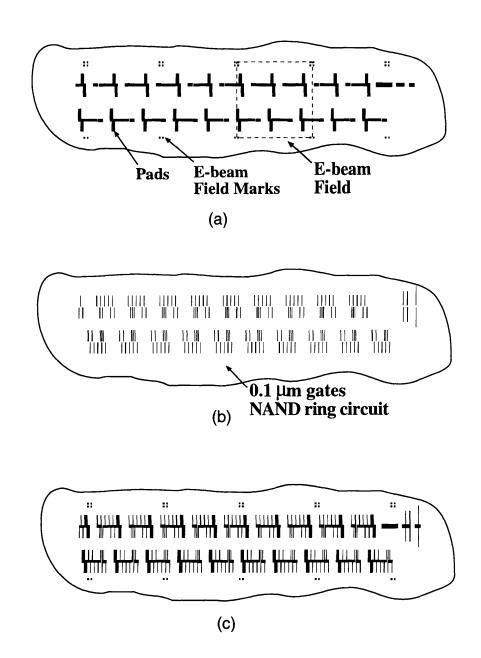

| 4-2  | Process of combining e-beam and optical lithography to produce an x-                 | 00 |

|      | ray mask. (a)Patterning of coarse features and e-beam field alignment                |    |

|      | marks using a stepper.(b)E-beam writing of fine features by aligning                 |    |

|      | to the optically defined field marks. (c) The final pattern on the x-ray             |    |

|      | mask as a result of optical and e-beam lithographies                                 | co |

|      | mask as a result of optical and e-beam indograpmes                                   | 60 |

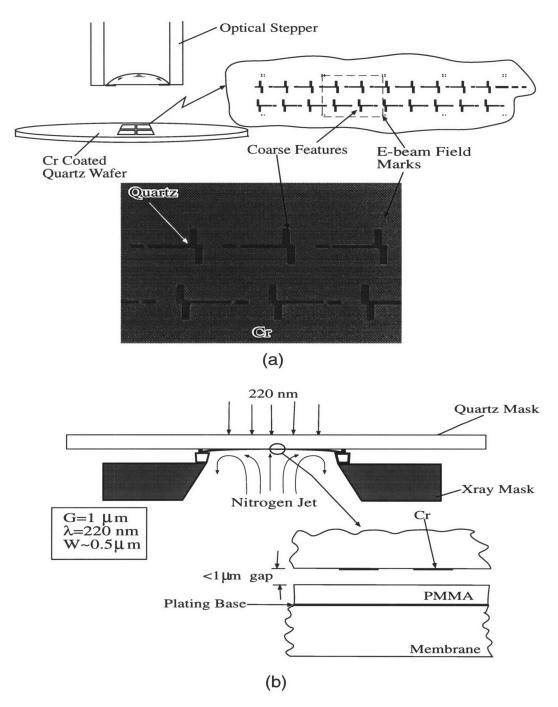

| 4-3 | Quartz water patterning and DUV coarse feature transfer onto x-ray               |    |

|-----|----------------------------------------------------------------------------------|----|

|     | mask. (a)A 10X emulsion mask with coarse features and e-beam field               |    |

|     | marks was stepped down onto a chrome coated quartz wafer. The                    |    |

|     | pattern was then wet etched into chrome. This quartz wafer then                  |    |

|     | serves as the 1X mask for transferring the pattern onto the x-ray mask.          |    |

|     | (b) The DUV transfer process. The x-ray mask is placed on a fixture              |    |

|     | with holes drilled in the underside of the fixture. A jet of nitrogen            |    |

|     | is "blown" through the holes in the fixture forcing the x-ray mask               |    |

|     | membrane to conform to the quartz wafer                                          | 62 |

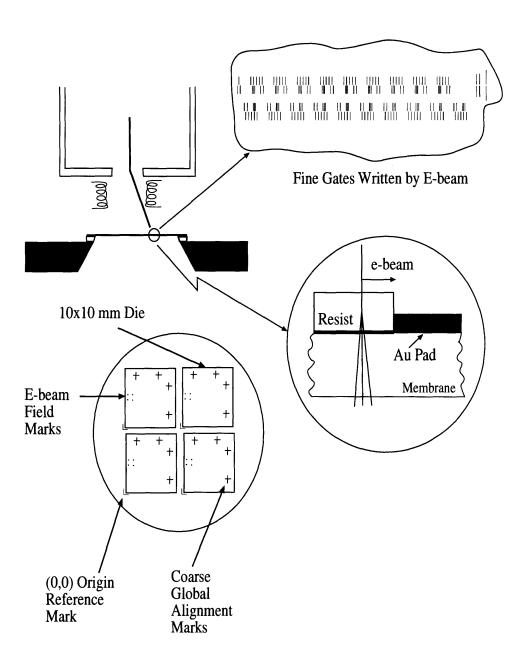

| 4-4 | E-beam writing process for fine gate features                                    | 64 |

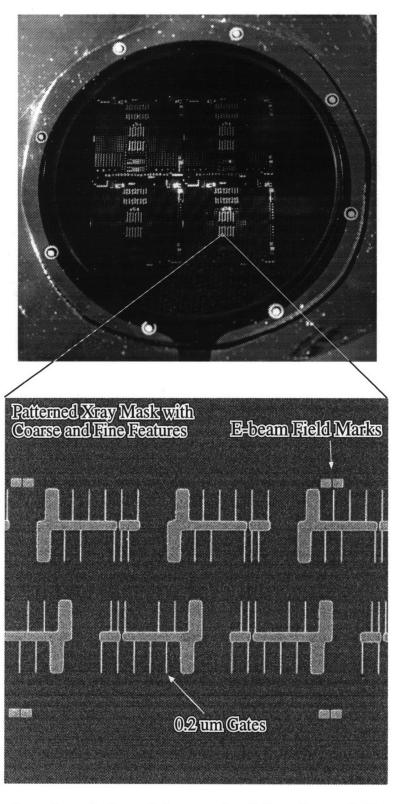

| 4-5 | The completed x-ray mask with coarse features patterned by G-line                |    |

|     | stepper and fine featured patterned by e-beam writing                            | 65 |

| 4-6 | An enlarged view of the completed four die mask (20x20 mm), and                  |    |

|     | e-beam field view of a NAND gate in a NAND ring oscillator. The                  |    |

|     | light scatter (white dots) outside the membrane area are of no concern.          | 66 |

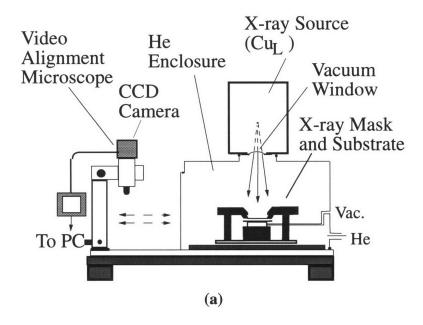

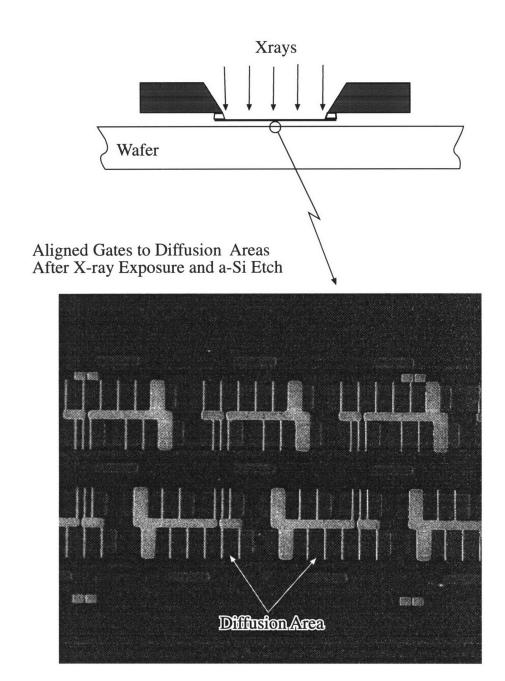

| 4-7 | (a)Schematic of alignment and exposure system. The alignment was                 |    |

|     | done outside of the helium enclosure using the CCD camera and the                |    |

|     | microscope. Once alignment was completed, the stage was rolled on                |    |

|     | ball bearings into the helium enclosure. During exposure, the $\mathrm{Cu}_L$ x- |    |

|     | rays pass through a silicon nitride vacuum window and irradiate the              |    |

|     | mask and wafer. (b)Aligned polysilicon gate on a narrow-width device             |    |

|     | active area.                                                                     | 67 |

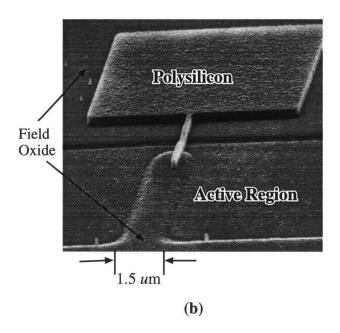

| 4-8 | One e-beam field view of a NAND gate in a NAND ring oscillator after             |    |

|     | the amorphous silicon gate etch                                                  | 69 |

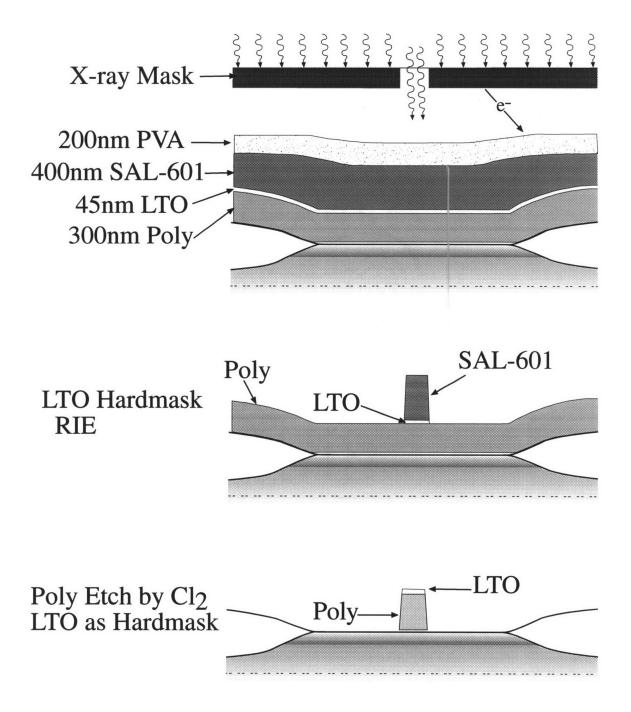

| 4-9 | Process for x-ray exposure using the chemically amplified resist, SAL601,        |    |

|     | and PVA topcoat to prevent the formation of a "skin" layer. The def-             |    |

|     | inition of the polysilicon gate was accomplished in two steps:(1)the             |    |

|     | LTO hard mask was etched in $\mathrm{CHF}_3$ RIE, (2)then the polysilicon was    |    |

|     | etched in pure Cl <sub>2</sub> plasma.                                           | 71 |

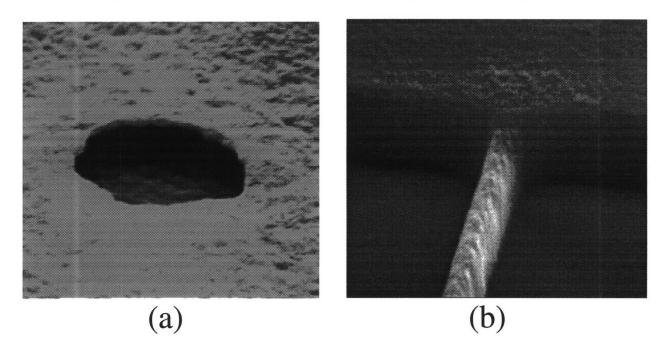

| 4-10 | (a)Sample with crosslinked "skin" layer with the gate pattern. The                 |    |

|------|------------------------------------------------------------------------------------|----|

|      | gate pattern not visible in the SEM, is visible under the optical micro-           |    |

|      | scope. (b)Sample without the "skin" layer                                          | 72 |

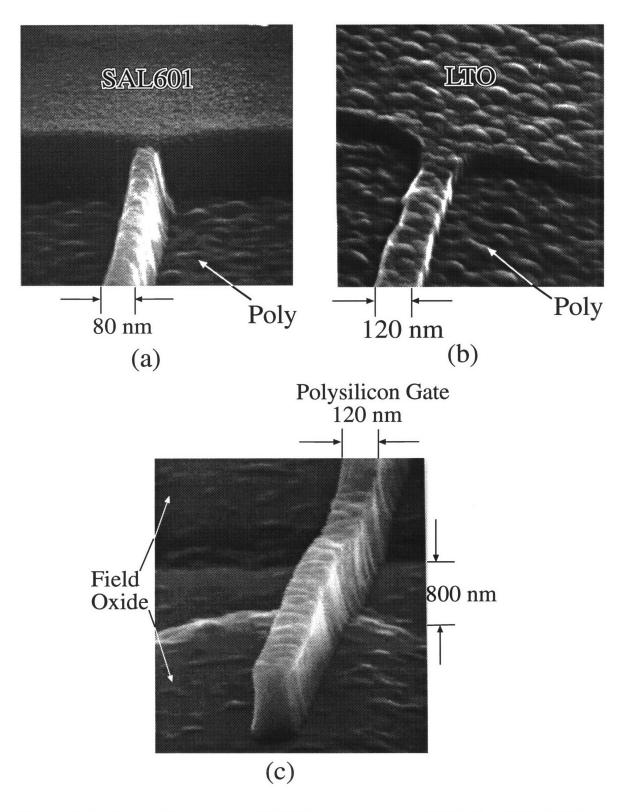

| 4-11 | Dry etching results:(a)SAL601 resist on top of LTO after CHF <sub>3</sub> RIE      |    |

|      | for a 80 nm gate, (b)120 nm gate pattern transferred into the LTO                  |    |

|      | with the SAL601 stripped, (c)polysilicon gate after Cl <sub>2</sub> plasma etching |    |

|      | using LTO as hardmask                                                              | 74 |

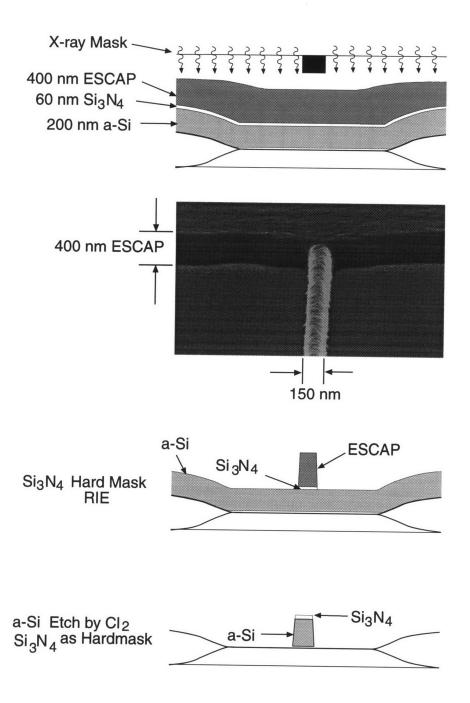

| 4-12 | The gate patterning processing using ESCAP-X resist with nitride hard              |    |

|      | mask                                                                               | 76 |

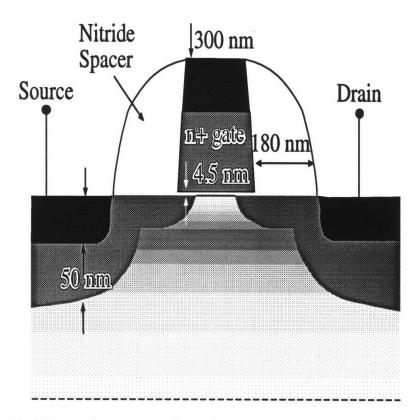

| 4-13 | Schematic cross section of $0.1\mu\mathrm{m}$ channel length nMOSFET. The gate     |    |

|      | oxide thickness was approximately 4.5 nm and the polysilicon thickness             |    |

|      | was 300 nm. The shading in the channel region depicts the retrograde               |    |

|      | doping. The source/drain extension and deep junction depths are $\sim$ 40-         |    |

|      | 50 nm and $\sim$ 120 nm, respectively. The 180 nm thick nitride spacers            |    |

|      | prevented the encroachment of the deep source/drain junctions into                 |    |

|      | the channel region, and $\sim 50$ nm of cobalt silicide was formed on the          |    |

|      | gate and source/drain                                                              | 77 |

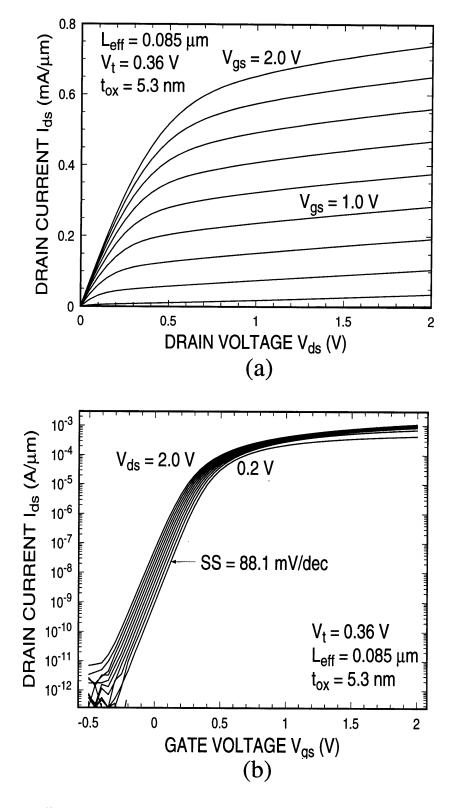

| 4-14 | Device output characteristics:(a)I-V characteristics for $L_{eff}$ =85 nm          |    |

|      | gate length device with threshold voltage of 0.36 V, and gate voltage              |    |

|      | stepped from 0 to 2 V in $0.2$ V increments. (b)Subthreshold charac-               |    |

|      | teristics of the same device.                                                      | 78 |

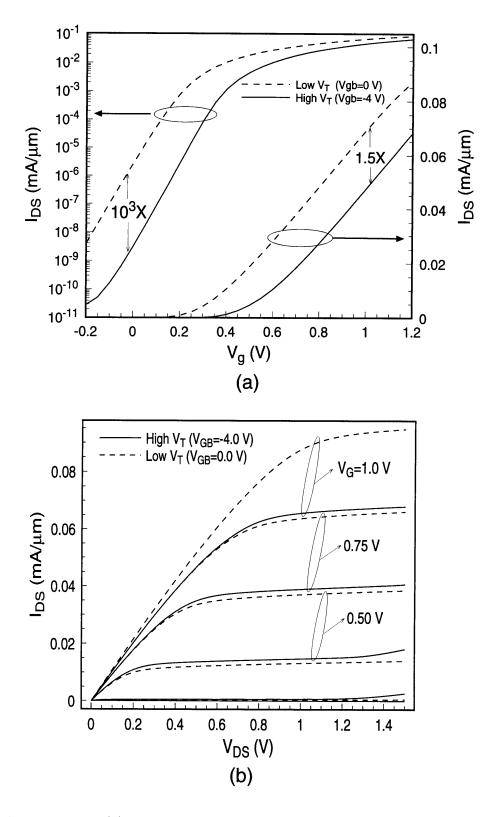

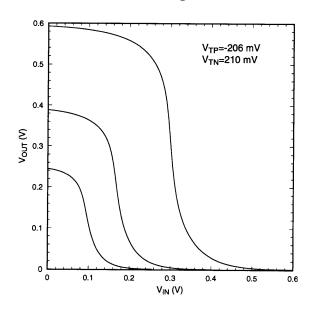

| 4-15 | (a) Subthreshold characteristics of a $0.2\mu\mathrm{m}$ top-gate device showing   |    |

|      | three decade change in the off current with 4 V back-gate bias in idling           |    |

|      | mode with low quiescent $V_T$ . With high quiescent $V_T$ , 1.5x times drive       |    |

|      | current change at VDS of 1.0 V can be observed. (b) I-V characteristics            |    |

|      | of the same device                                                                 | 80 |

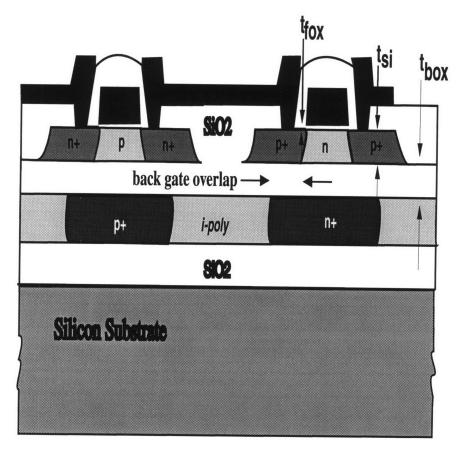

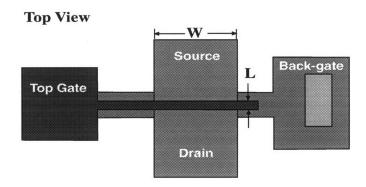

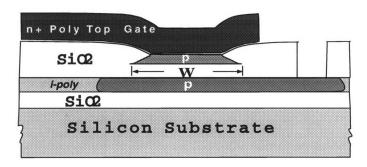

| 5-1  | Device schematic                                                                   | 82 |

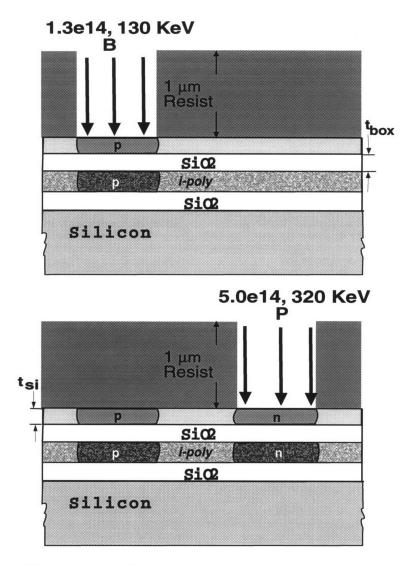

| 5-2  | Two step masking and implant process for the formation of n and p                  |    |

|      | back-gates                                                                         | 83 |

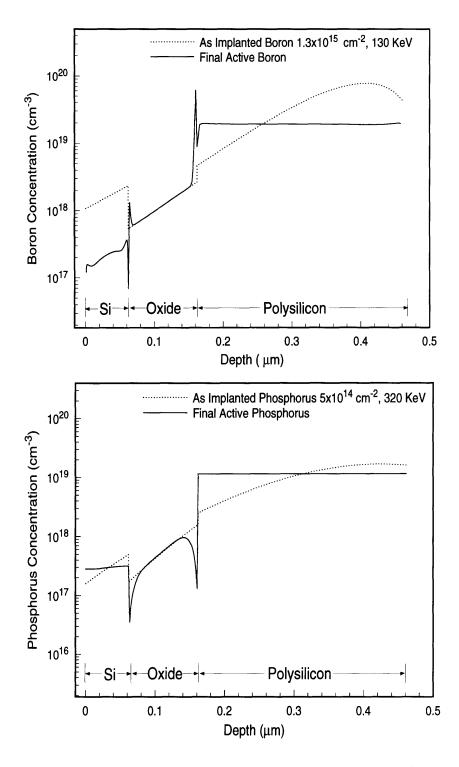

| 5-3  | Suprem3 simulated implant profiles for NMO5 and PMO5 devices and                   |    |

|------|------------------------------------------------------------------------------------|----|

|      | their back-gates. The final active dopant concentration is after all the           |    |

|      | thermals cycles in SOIAS CMOS process                                              | 84 |

| 5-4  | Schematic of back-gate contact cuts                                                | 85 |

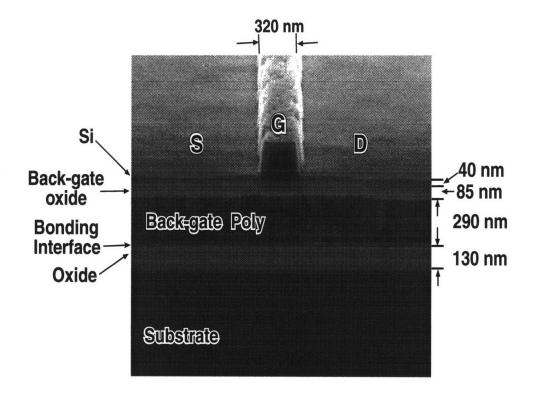

| 5-5  | SEM micrograph of the SOIAS device                                                 | 85 |

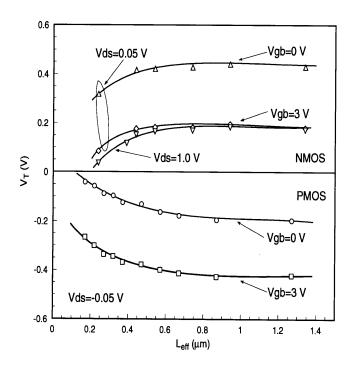

| 5-6  | Measured NMOS device characteristics showing the effects of switching              |    |

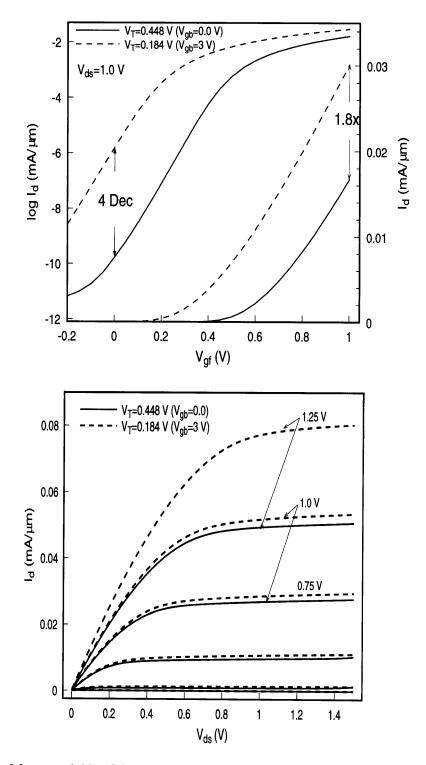

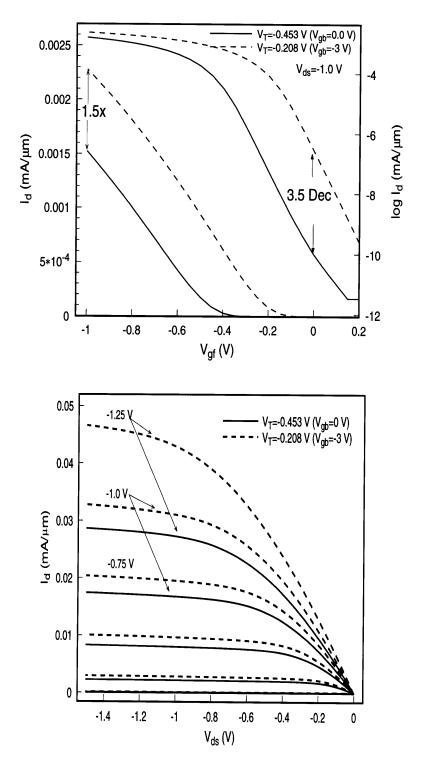

|      | the $V_T$ on the off current and the drive current at $V_{DS}{=}1~V.~.~.~.$        | 89 |

| 5-7  | Measured PMOS device characteristics                                               | 90 |

| 5-8  | Measured threshold voltage tuning range. The x-axis is the quiescent               |    |

|      | ${ m V}_T$ determined by the silicon film thickness and the doping level. The      |    |

|      | y-axis is the tunable $V_T$ set by the back-gate bias; the design range of         |    |

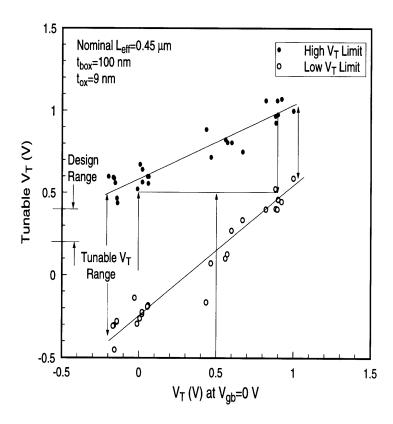

|      | 200 mV switch in $V_T$ fits well within the tuning range                           | 91 |

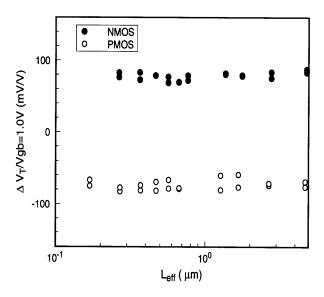

| 5-9  | Measured threshold voltage control as a function of gate length                    | 92 |

| 5-10 | Threshold voltage roll-off as a function of gate length at different back-         |    |

|      | gate biases for NMOS and PMOS                                                      | 92 |

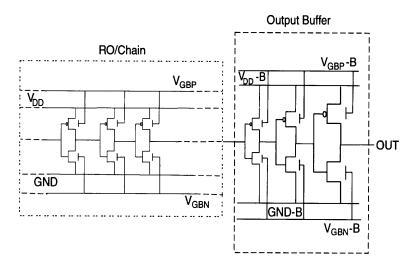

| 5-11 | Schematic of measurement setup for the 101 stage ring oscillators and              |    |

|      | 50 stage inverter chains                                                           | 93 |

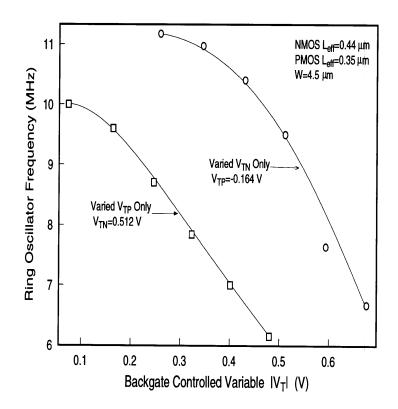

| 5-12 | Measured ring oscillator frequency as a function of independently con-             |    |

|      | trolled $V_T$ through back-gate biasing                                            | 93 |

| 5-13 | Measured 101 stage ring oscillator output frequency as varied by chang-            |    |

|      | ing $V_T$ . A 36% change in the speed is observed for 200 mV change in             |    |

|      | $V_T$ at $V_{DD}$ of 1 V                                                           | 94 |

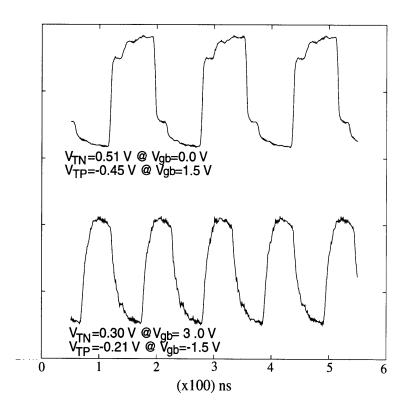

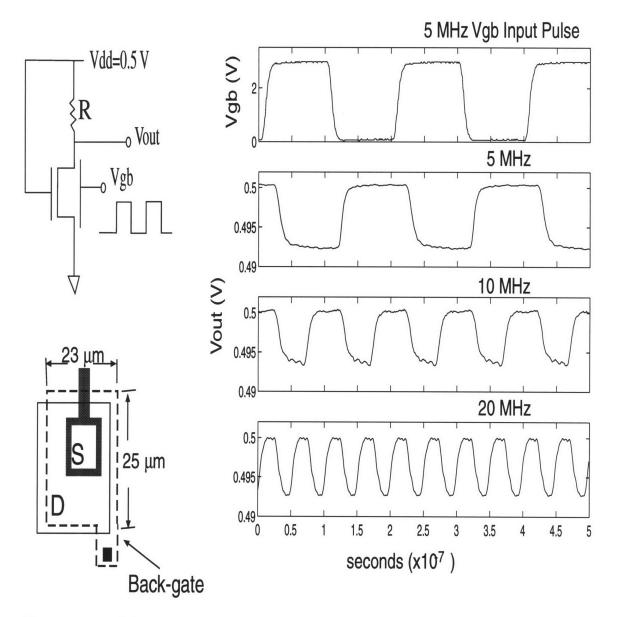

| 5-14 | Schematic showing the measurement setup and device under test for                  |    |

|      | dynamic switching of the back-gate experiment. The $\mathbf{V}_{out}$ at the drain |    |

|      | for three different input frequencies are shown with one example of the            |    |

|      | input pulse on $V_{gb}$ at 5 MHz                                                   | 95 |

| 5-15 | Overlay of dynamic current due to switching of back-gate on DC char-               |    |

|      | acteristics at various static back-gate biases. The points marked X                |    |

|      | represent dynamic measurements at 10 MHz                                           | 96 |

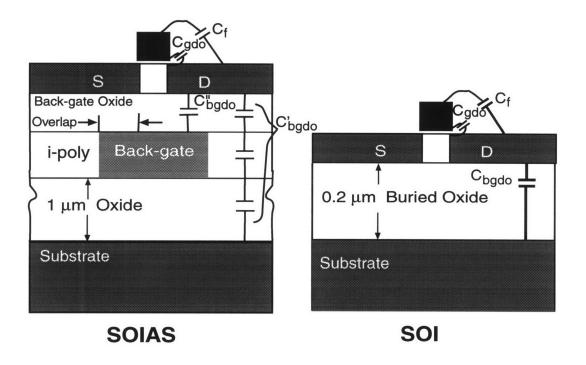

| 6-1  | Capacitances of SOIAS and SOI devices                                              | 99   |

|------|------------------------------------------------------------------------------------|------|

| 6-2  | Schematic illustration of the definitions for the various activities factors       | .101 |

| 6-3  | Comparison of the front-gate dynamic switching energy for SOIAS and                |      |

|      | SOI. The dark line indicates the boundary where the energies are the               |      |

|      | same. When the SOIAS front-gate switching energy becomes greater                   |      |

|      | than that of the SOI, the overlap capacitance contribution becomes                 |      |

|      | significant                                                                        | 104  |

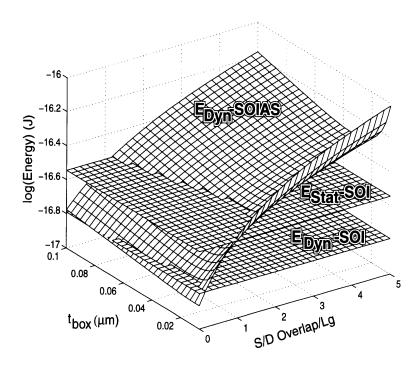

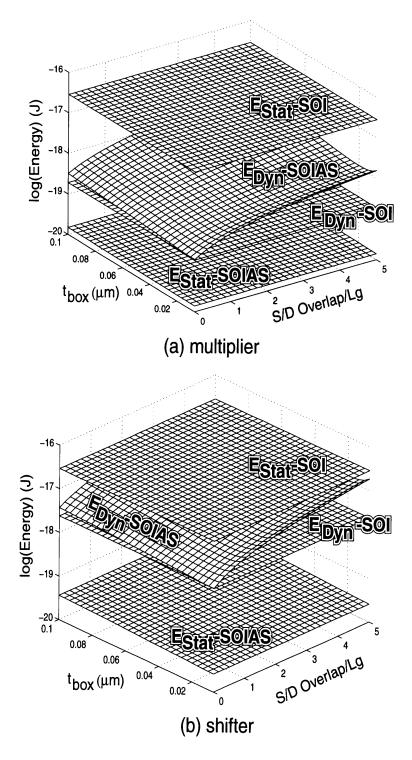

| 6-4  | The front-gate and back-gate dynamic switching energies for the adder.             | 106  |

| 6-5  | The front-gate and back-gate dynamic switching energies for the mul-               |      |

|      | tiplier and shifter                                                                | 108  |

| 6-6  | Comparison of dynamic switching energies (back-gate + front-gate)                  |      |

|      | and the static leakage energy components for the SOIAS and SOI tech-               |      |

|      | nologies. The static leakage for the SOIAS is not shown on the plot                |      |

|      | because it is off the scale.                                                       | 109  |

| 6-7  | Comparison of dynamic switching energies (back-gate + front-gate)                  |      |

|      | and the static leakage energy components for the multiplier and shifter.           | 110  |

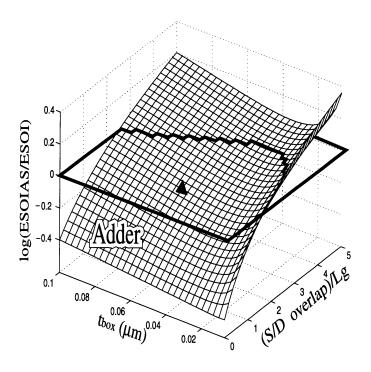

| 6-8  | The adder total energy ratio for SOIAS and SOI. The dark line outlines             |      |

|      | the break-even plane                                                               | 111  |

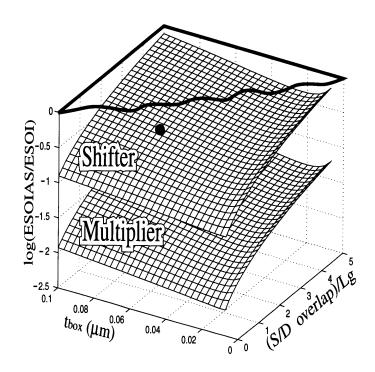

| 6-9  | The multiplier and shifter total energy ratio for SOIAS and SOI. Both              |      |

|      | fall below the break-even plane                                                    | 111  |

| 6-10 | The total energy ratio for SOIAS and SOI with $\chi = 100\%$ (open sym-            |      |

|      | bols) and $\chi = 2\%$ (filled symbols). Squares represent the multiplier; cir-    |      |

|      | cles represent the shifter and triangles represent the adder. Shown are            |      |

|      | two plots for different technology design parameters: (a) $t_{box}$ =50 nm,        |      |

|      | s/d overlap=2L_g=0.5 $\mu \mathrm{m}.$ (b)t_{box}= 50 nm, s/d overlap=0.5L_g=0.125 |      |

|      | $\mu$ m                                                                            | 112  |

| 7-1  | Inverter transfer characteristics                                                  | 114  |

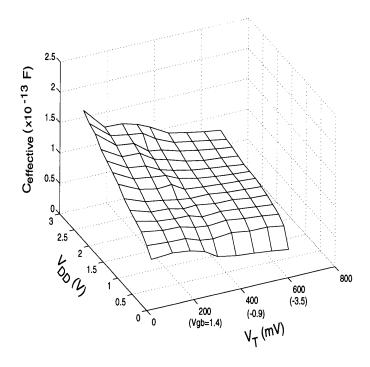

| 7-2  | The measured effective switching capacitance                                       | 115  |

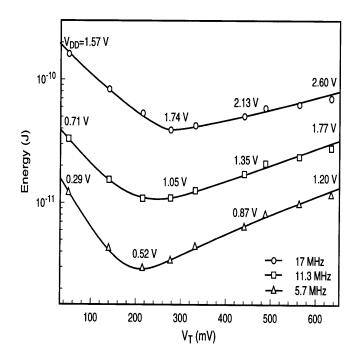

| 7-3 | The measured total energy for 101-stage ring oscillator running at three                |     |

|-----|-----------------------------------------------------------------------------------------|-----|

|     | different frequencies                                                                   | 115 |

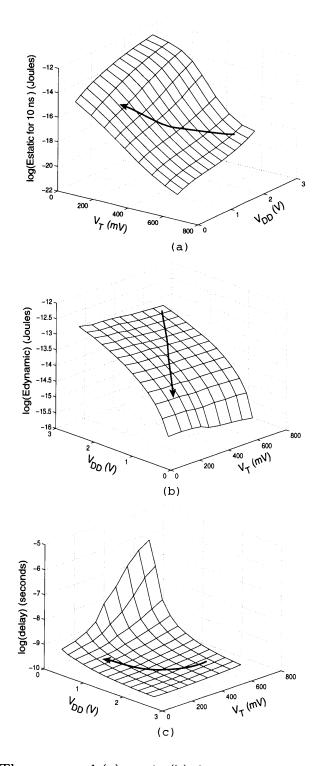

| 7-4 | The measured (a) static (b) dynamic energies, and (c) delay per stage                   |     |

|     | as a function of $V_T$ and $V_{DD}$ . As guides, the arrows indicate the                |     |

|     | direction of $V_{DD}$ and $V_T$ scaling                                                 | 116 |

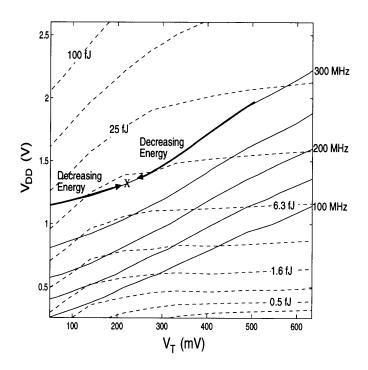

| 7-5 | Energy and performance contours in $V_T$ and $V_{DD}$ space for an adder                |     |

|     | with 0.25 system activity, and the module activity as obtained by pro-                  |     |

|     | filing a SPEC benchmark                                                                 | 118 |

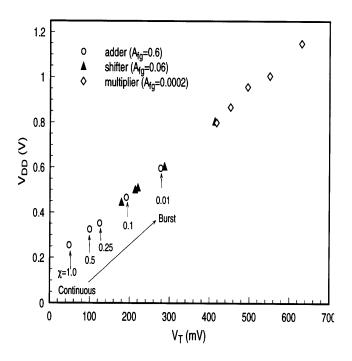

| 7-6 | The optimal $V_T$ and $V_{DD}$ for the adder, shifter and multiplier modules            |     |

|     | with different system activity factors. The module activity factor, $\mathbf{A}_{fg}$ , |     |

|     | for each functional unit was obtained from program profiling of the                     |     |

|     | SPEC benchmark Espresso                                                                 | 119 |

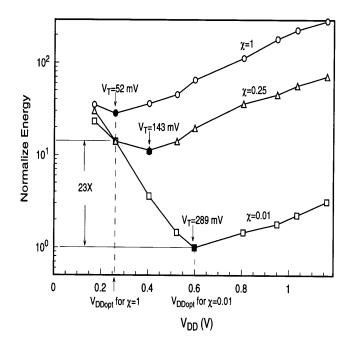

| 7-7 | Comparison of normalized energy versus $\mathbf{V}_{DD}$ for different system ac-       |     |

|     | tivities                                                                                | 119 |

# List of Tables

| 3.1 | Surface roughness comparison for different substrate materials                                        | 51  |

|-----|-------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Average interface state density for different substrate materials                                     | 55  |

| 6.1 | Activity values from profiling the data encryption program (IDEA)                                     | 102 |

| 7.1 | Module activity factor, $\mathbf{A}_{fg}$ , and back-gate activity factor, $\mathbf{A}_{bg}$ obtained |     |

|     | from profiling the SPEC benchmark program                                                             | 121 |

| 7.2 | The optimal $V_T$ and $V_{DD}$ at minimum total energy for some modules                               |     |

|     | as obtained from the energy consumption model and measured static                                     |     |

|     | and dynamic energies for burst-mode, $\chi = 0.01,100$ MHz operation                                  | 121 |

| A.1 | Recipe 110                                                                                            | 141 |

| A.2 | Recipe 114                                                                                            | 141 |

| A.3 | Recipe 226                                                                                            | 142 |

| A.4 | Recipe 230                                                                                            | 142 |

| A.5 | Recipe 10                                                                                             | 142 |

| A.6 | Recipe 15                                                                                             | 142 |

| A.7 | Recipe 20                                                                                             | 143 |

| A.8 | Recipe 32                                                                                             | 143 |

| A.9 | Modified recipe 32 for gate etch                                                                      | 143 |

# Chapter 1

# Introduction

The scope of this thesis spans a wide range. The main focus is placed on technology development with emphasis on application to low power electronics. With the tremendous infrastructure developed for silicon technology, it is unlikely that replacement by a completely different material would occur in the next 10 years. The main technology elements in this thesis, in my opinion, extends the longevity of silicon-based technology by leveraging off the established infrastructure for silicon bulk CMOS. The two main technology elements of this work are:

- Silicon-On-Insulator-with-Active-Substrate (SOIAS) is a variant of the fully depleted (FD) Silicon-On-Insulator (SOI) technology. In general, this technology can be extended to fabricate 3-dimensional structures as opposed to the conventional 2-dimensional planar structures that are prevalent in today's integrated circuits. Specifically, in this work, an additional back-gate is added to the conventional FD SOI MOSFET to electronically modulating the threshold voltage.

- X-ray lithography technology allows scaling of the MOSFET gate dimension into the sub-0.1  $\mu$ m regime. This technology is applicable to both bulk and SOIAS CMOS. Scaling the MOSFET gate is another means of extending the life of silicon technology by squeezing more performance out of the device. In this work, the integration of x-ray lithography into a CMOS process is developed.

From a pragmatic standpoint, a new technology would be of no value unless it

can be implemented in applications that can greatly benefit from such a technology. In this work, the SOIAS technology with electronically variable threshold voltage is evaluated for ultra-low voltage, low power, and high performance systems. This is done using a combination of theoretical, simulation-based, as well as with actual measurement results.

# 1.1 Thesis Organization

In the ensuing chapters, the evolution of the SOIAS technology development, x-ray lithography integration in our CMOS process, and the theoretical evaluations of the applicability of SOIAS to low power systems will be presented in the following order,

- chapter 2 gives a brief background on the requirements for low power and the history of double-gated devices. The basis of the SOIAS device design is also described.

- Chapter 3 focuses on the development of the bonding technology for SOIAS substrates. First a brief history of the theory of silicon fusion bonding is given, followed by the SOIAS substrate preparation process. Finally, the material characterization through electrical measurements are presented.

- Chapter 4 concentrates on the other major technology component of this thesis, which is x-ray lithography for the fabrication of deep submicrometer MOSFETs. The integration of this technology into our CMOS process using a mix-and-match scheme with optical lithography is described, followed by details of the critical resist and dry etching processes. Some device results are presented at the end.

- Chapter 5 presents the measurements on SOIAS devices. First DC static measurement are presented, followed by dynamic measurement results.

- $\bullet$  Chapter 6 presents the theoretical energy dissipation model for SOIAS, and benchmarking against a conventional, constant low  $V_T$  SOI technology.

- Chapter 7 explores the  $V_T$  and  $V_{DD}$  design space for optimal operating points for systems with various activities using measured data in conjunction with the energy model.

- Chapter 8 is the summary and conclusion of this work.

# Chapter 2

# Background

#### 2.1 The Need for Low Power

The rapid emergence of portable wireless electronic systems has spurred researchers to explore various low power optimization techniques at all levels of the hierarchy: architecture, circuit, device and technology. The improvements in battery lifetime, weight, and size, however, does not parallel the explosive commercial growth of portable electronic systems. Therefore, more aggressive power reduction methodologies need to be investigated. Until recently, power consumption considerations in design has always been secondary to performance enhancement. Examples of several strategies adapted for low power design include: (1) switched capacitance reduction, (2) power supply voltage scaling, (3) use of gated clocks, and (4) powering down during long idling periods. The first two methods are at the technology level whereas the latter two are at the circuit and architecture design level. For total reduction in power, all of the strategies should be implemented. Since this thesis is based on technology, focus will be placed on issues related to such (e.g. method 1 and 2). The rationale behind the first two methodologies can be understood by examining the sources of power consumption. For a CMOS technology, there are three main components in the equation for total power dissipation,  $P_{tot}$ :

$$P_{tot} = P_{dyn} + P_{stat} + P_{sc}$$

$$P_{dyn} = \alpha C_{load} V_{dd}^2 f_{clock}$$

$$P_{stat} = I_{Leak} V_{dd}$$

$$P_{sc} = I_{ave} V_{dd}$$

where  $P_{dyn}$  is the dynamic power dissipation. The dynamic power dissipation is due to the switching of the load capacitance,  $C_{load}$ . Therefore, for heavily loaded circuits, the dynamic power dissipation dominates, and it is intuitively obvious that  $C_{load}$  and the power supply voltage,  $V_{dd}$ , should be reduced in order to decrease the total power dissipation without slowing down the clock.  $\alpha$  can best be described as the node switching activity during one clock period, which is strongly dependent on the input signal statistics.  $P_{stat}$  is the power dissipation due to leakage currents in the subthreshold region and reverse bias diode leakage currents for bulk CMOS devices. Finally, the short-circuit power,  $P_{sc}$ , results from both NMOS and PMOS stacked devices being "ON" simultaneously providing a current path from power supply to ground.  $I_{ave}$  is the mean short-circuit current which is strongly dependent on the input and output rise times. The short circuit power can be kept at a low percentage of total power dissipation by balancing the NMOS and the PMOS through transistor sizing assuming the threshold voltages are of the same magnitude.

Capacitance reduction can be accomplished at many levels of design and is fairly straightforward. For example, a Silicon-On-Insulator technology can be used to lower the parasitic node capacitances, and the selection of appropriate logic style and proper transistor sizing can be done at the circuit design level to reduce switched capacitances. Supply voltage scaling is more complex because of the performance/throughput vs power consumption trade-off and is strongly dependent on the application. Supply and threshold voltages must be reduced concomitantly if performance losses cannot be tolerated especially at low  $V_{dd}$  (e.g 1 V and below). However, the price of re-

ducing the threshold voltage is the increased leakage current since the subthreshold slope cannot be scaled. Therefore, an optimum set of supply and threshold voltages exists which balances the dynamic and leakage power dissipations that will result in minimization of total energy. The switching activity,  $\alpha$ , is also a determining factor in finding the optimal threshold and supply voltages. For systems which operate in burst mode or are "event-driven", in which intermittent computations are performed as a result of I/O activity with long periods of inactivity while awaiting I/O, the clock may be stopped completely during inactivity in which case the power consumption should be nearly zero if the leakage power is low, i.e. threshold voltage is high. However, for ultra-low-power applications, the targeted power supply voltages are less than 1 V, and hence the performance will surely suffer. A clever way to address the performance vs power trade-off is to dynamically control the threshold voltage. The granularity of the threshold voltage control depends on the system usage.

# 2.2 Dynamic Threshold Voltage Control Concept

Many system computations are either temporally or spatially localized. Systems that are frequently idle, i.e. doing computation only for a small fraction of the time, operate in burst-mode, and hence exhibit temporal locality. On the other extreme, systems that are active all of the time operate in "continuous" mode, and hence do not exhibit temporal locality. At the same time, a system may only have a fraction of its functional modules active all of the time, such systems exhibit spatial locality. This idea can be applied to lower levels of the hierarchy such as at the logic gate level or the transistor level. One of the widely adapted global strategies for achieving high performance and low power in continuously computing systems (e.g., modules of a video compression system) has been the simultaneous reduction of supply voltage,  $V_{DD}$ , and threshold voltage,  $V_T$ , where the optimal  $V_{DD}$  and  $V_T$  are found for minimum total system energy by trading off dynamic energy for static leakage energy[1, 2, 3]. CMOS-based high performance burst-mode computation systems (e.g. a microprocessor running an X-server or cellular phone which is idling more

than 90% of the time) will suffer high static leakage energy dissipation operating at low  $V_{DD}$  with constant low  $V_T$  even with clocks stopped. For example, even when a user is continuously entering data at the keyboard, the X-server is active, (i.e. doing computation), only 2-3\% of the time [4]. In order to simultaneously achieve high performance during active period and low leakage power during idle period for burstmode computational systems, several schemes of reducing the leakage current have been proposed. The multiple  $V_T$  CMOS design involves using high  $V_T$  transistors to gate the low  $V_T$  functional blocks[5, 6]. Both NMOS and PMOS transistors are needed in order to preserve state. These devices must be made large due to the finite resistance of these transistors. This incurs additional switching energy to switch these devices. Therefore, appropriate sizing of the high  $V_T$  transistors is crucial. Another approach is the dynamic control of  $V_T$  by biasing the bulk-CMOS wells[7]. A triple well technology is required for this scheme. Furthermore, well biasing is complicated by the N-well to P-well junction leakage current as well as source/drain junction to well leakage currents. Both of the above schemes are implemented at the functional module level; for example, in the well biasing scheme, all the transistors in the functional module have the same variable  $V_T$  which is dependent on the well bias.

#### 2.3 SOI Technology

The aforementioned technologies have been mainly proposed for implementation in bulk silicon CMOS. However, the increasing maturity of the SOI technology in the past few years cannot be ignored, especially with the dramatic improvements in material quality. There are two modes of operation for SOI MOSFETs, fully depleted (FD) and partially depleted (PD) channel region (body). In the conventional strongly FD SOI device, the silicon film thickness is usually less than or equal to half of the depletion width of the bulk device. The surface potentials at the front and back interfaces are strongly coupled to each other and capacitively coupled to the front-gate and the substrate through the front-gate oxide and buried oxide, respectively. Therefore,

the potential throughout the silicon film, and hence the charge, is determined by the bias conditions on both the front-gate and the substrate. By replacing the substrate with a back-gate, the device becomes a dual-gated device. The FD design is unique to SOI because the front-gate and back-gate both have control of the charge in the silicon film. In the strongly PD SOI, the back-gate or substrate has no influence on the front surface potential. In the middle regime, the device is nominally PD and can become FD by applying a back-gate bias, thus, coupling of the front and back surface potentials still occurs. In order to implement the dynamic threshold voltage control scheme in SOI, devices must operate in the FD mode.

#### 2.3.1 SOI Dual-gated Devices

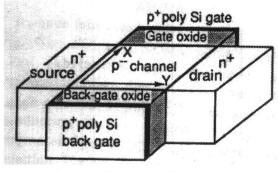

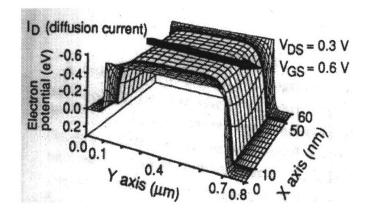

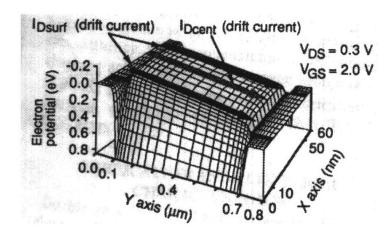

Various researchers have exploited the use of FD SOI in dual-gated devices in which the top and bottom gates are tied and switched together, resulting in enhanced transconductance and reduced short channel effects [8, 9, 10, 11, 12, 13]. Sekigawa et al proposed the earliest dual-gated device with improved  $V_T$  roll-off from analytical calculations [13]. Colinge et al fabricated the "gate-all-around" MOSFET which they have claimed to show more than 2X enhanced transconductance near threshold compared to that of a single-gate device. They attributed this enhancement to "volume inversion" of the silicon film. However, in strong inversion, the enhancement is minimal, i.e. this device acts like two transistors in parallel. This was also confirmed by Venkatesan et al [14]. In the subthreshold region, the potential in the silicon film is more or less flat, i.e. the carriers are more or less evenly distributed in the film. The potential barrier in the film center with respect to the source is lower than in the single gate device, and thus facilitates charge injection from the source, hence more subthreshold current. Furthermore, since the vertical field is small, the carrier in the center of the film does not suffer from surface scattering, and hence may have a higher mobility. Once in strong inversion, the surface potential becomes pinned, and the carriers are predominantly near the surface, and the contribution to total conduction by the carriers in the center of the silicon film is insignificant. This is very nicely shown in the two dimensional plot of the electron potential by Tanaka et al, Figure 2-1,

[11]. Balestra et al also claimed "volume inversion" in their dual-gated MOSFETs through simulation. However, their confirmation through measurements is dubious because their device is not a true dual-gated device. They used the substrate as the second gate and the bias voltage ratio of back to front-gate is 10X to compensate for the oxide thickness difference. In terms of current drive, the dual-gated device does not show any advantage over two single-gated devices unless it operates in the subthreshold region all the time. The main advantage of the dual-gated device is the scalability into the sub-100nm regime [15, 16, 17, 18, 19]. All these devices have the same work function for both top and bottom gates, i.e same polarity gates. Suzuki et al has shown that devices with opposite polarity (n<sup>+</sup>-p<sup>+</sup>) gates scale better than same polarity (p<sup>+</sup>-p<sup>+</sup> or n<sup>+</sup>-n<sup>+</sup>) gates; and the  $V_T$  of the opposite polarity gates devices are in the right range for today's VLSI design requirements due to the work function difference of the top and bottom gates [17, 19]. However, for low voltage operations of the opposite polarity gates devices (\langle 1 V), the bottom gate does not fully "turn on" due to the difference in  $V_T$  of the top and bottom gates. The function of the bottom gate, in this case, is to lower the  $V_T$  of the top-gate device during switching.

An ideal dual-gated device should have its top and bottom gates perfectly aligned. With the same thickness top and bottom gate oxides, misalignment of the bottom gate with the source and drain will greatly increase the parasitic capacitance and degrade the short channel effect immunity [18]. Recently, another group introduced a Dynamic Threshold Voltage MOSFET (DTMOS) in SOI [20]. In this structure, the gate of a PD-SOI MOSFET is tied to the body. Therefore, during switching of the gate, a bias is also applied to the body. As a result, the subthreshold slope reaches the theoretical limit of 60 mV/decade at room temperature, and the threshold voltage appears to be lowered. In order not to incur excessive body current, the gate voltage cannot be higher than 0.6 V. The observed improved subthreshold slope and  $V_T$  lowering are due to the forward biasing of the source-body p-n junction. By the conventional definition of dynamic threshold control, which is the parallel shift of the subthreshold I-V, the DTMOS does not comply.

The fabrication of dual-gated devices is a complex process, and switching the

**Device Schematic**

**Subthreshold Conduction**

Strong Inversion Conduction

Figure 2-1: Electron potential of dual-gated device in the subthreshold region and strong inversion [11].

back-gate every clock cycle also incurs additional energy. In this thesis work, the development of a practical (i.e. easily integrated) technology to implement the dynamic threshold voltage control concept is investigated. This is a FD-SOI-based technology called SOI-with-Active-Substrate (SOIAS). The particular implementation of the SOIAS back-gated devices does not call for switching of the back-gate every clock cycle.  $V_T$  of blocks of devices, i.e. in a module, would be switched similar to the concept of well-biasing in the triple well CMOS.

# 2.4 Comparison of $V_T$ Controllability in Bulk and SOI MOSFETs

#### 2.4.1 Long Channel Device

In bulk CMOS, the threshold voltage is a square root function of the well bias, and the body factor determines the degree of control[21],

$$V_T = V_{FB} + \phi_B + \gamma(\sqrt{V_{sb} + \phi_B})$$

$$\gamma = \frac{\sqrt{2q\epsilon_{Si}N_A}}{C_{ox}}$$

$$\phi_B = 2\frac{kT}{q}ln\frac{N_A}{n_i}$$

$C_{ox}$  is the gate oxide capacitance,  $N_A$  is the channel dopant concentration, q is the electron charge,  $\epsilon_{Si}$  is the silicon dielectric constant, and  $\gamma$ , the body factor, is strongly dependent on the channel doping concentration,

In FD SOI, the threshold voltage depends linearly on the back-gate bias, and the body factor,  $\delta$ , does not depend on channel doping concentration[22],

$$V_{Tf} \simeq V_{Tf}^A - \delta(V_{Gb} - V_{Gb}^A)$$

$$\simeq V_{Tf}^{I} - \delta(V_{Gb} - V_{Gb}^{I})$$

$$V_{Tf}^{A} = V_{FB}^{f} + (1 + \frac{C_{b}}{C_{ox}})2\phi_{B} - \frac{Q_{b}}{2C_{ox}}$$

$$V_{Tf}^{I} = V_{FB}^{f} + 2\phi_{B} - \frac{Q_{b}}{2C_{ox}}$$

$$V_{Gb}^{A} \simeq V_{FB}^{b} - \frac{C_{b}}{C_{box}}2\phi_{B} - \frac{Q_{b}}{2C_{box}}$$

$$V_{Gb}^{I} \simeq V_{FB}^{b} + 2\phi_{B} - \frac{Q_{b}}{2C_{box}}$$

$$\delta = \frac{C_{b}C_{box}}{C_{ox}(C_{b} + C_{box})}$$

where  $C_b = \frac{\epsilon_{Si}}{t_{Si}}$ ,  $C_{box} = \frac{\epsilon_{ox}}{t_{box}}$ .  $Q_b = qN_At_{Si}$  is the bulk charge for fully depleted SOI, and  $V_{FB}$  is the flatband voltage.  $V_{Gb}^A$  and  $V_{Gb}^I$  denote the back biases at the onset of back interface accumulation or inversion, respectively;  $V_{Tf}^A$  and  $V_{Tf}^I$  are the corresponding front-gate threshold voltages, which are pinned after the back interface has reached either accumulation or inversion.

Although the concept of threshold voltage control in bulk and SOIAS are the same, the design trade-offs are different. The reasons for choosing a SOI based technology rather than a bulk technology are manifold. The SOIAS technology has all the advantages of conventional fully depleted SOI, and offers more flexibility. In bulk CMOS, in order to increase the body factor, the channel doping must be increased. However, in doing so, the threshold voltage at zero bias is also increased. Therefore the body factor in bulk is coupled to the threshold voltage. Proper channel and well doping designs may resolve this problem. In the SOIAS technology, since the body factor is not dependent on the channel doping, the threshold voltage at zero bias can be set independently of the body factor. In threshold voltage switching, the SOIAS device back-gate can be switched in either direction to raise or lower the threshold voltage without suffering from junction leakage currents. In bulk, switching from low to high threshold voltages is more desirable than vice versa because the p-n junctions would be forward biased in the latter case resulting in unwanted leakage currents. The physical decoupling of the SOIAS device back-gate allows ample flexibility in its

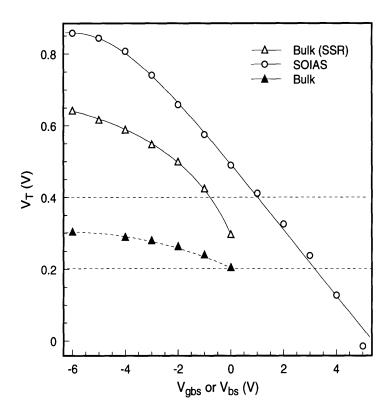

design independent of the top-gate device design. In bulk, the well conductance (i.e. doping) cannot be arbitrarily changed without affecting design parameters of the device. Figure 2-2 illustrates the channel design trade-off of body factor and  $V_T$  in bulk NMOS devices and the large dynamic  $V_T$  range of SOIAS device. In order to achieve a large body factor and low quiescent  $V_T$  in bulk devices, the super-steep retrograde (SSR) channel doping design should be utilized. These bulk devices were measured with a chuck contacting the entire back surface of a wafer which clearly cannot be done in CMOS. In triple-well CMOS, in order to increase the well conductance, a retrograde well design may be necessary. In the SOIAS design, the vertical structure design specifications (e.g.  $t_{ox}$ ,  $t_{si}$ , and  $t_{box}$  would determine the dynamic  $V_T$  range as long as the device is FD.

#### 2.4.2 Short Channel Device

In both the bulk device and SOIAS device, as the gate is scaled into the deep submicrometer regime, unless proper device engineering is employed to reduce the lateral encroachment of the source/drain fields, i.e. short channel effects (SCE), the control of the threshold voltage through the body or the back-gate would decrease. The complex 2-dimensional potential distribution is difficult to treat analytically. For purpose of accuracy, numerical solution of the 2-D Poisson equation should be sought. The charge-sharing concept which most of the analytical models are based provides intuitive understanding of the SCE. Figure 2-3 schematically depicts the charge sharing concept for bulk and SOI devices [23]. The charge, Qd1, in the channel region balances the charge in the top-gate, the source and drain, and the body/backgate. For a long channel device, the top of the trapezoid is L, the length of the gate, and the bottom of the trapezoid is approximately L. The top and bottom gates are assumed to control the charge in the trapezoidal region L. As the device is scaled, the bottom of the trapezoid becomes less than L and control by the body/back-gate also diminishes. The charge Qd1 in the trapezoidal region, under the control of the top-gate and the body/back-gate is also less. As the source and drain are brought closer to the channel region, in order for the top-gate and body/back-gate to maintain

Figure 2-2: Measured threshold voltage control by either body bias in bulk or backgate bias in SOIAS. The open triangles represent a bulk NMOS device with supersteep retrograde (SSR) channel doping;  $L_{eff}$  is approximately 0.75  $\mu$ m. The filled triangles represent a single step channel doping device,  $L_{eff}$  is approximately 0.7  $\mu$ m. Although the latter has a lower quiescent  $V_T$ , the body factor is much smaller than the SSR design. The SOIAS device dynamic  $V_T$  range is larger than both of the bulk devices.  $L_{eff}$  of the SOIAS device is approximately 0.4  $\mu$ m.

Figure 2-3: Charge sharing in bulk and FD SOI devices [23].

proportionately the same control, similar scaling in the vertical dimension must also be implemented. This requires the gate oxide and the source/drain junction be scaled, and the channel doping be increased. Scaling the gate oxide, physically brings the gate closer to the channel region. Increasing the channel doping decreases the depletion into the channel from the source/drain junctions, and decreasing the junction depth reduces the lateral fringing fields from the source/drain. From the charge-sharing concept and using geometrical constructs, the  $V_T$  equation becomes [21]

$$V_T = V_{FB} + \phi_B + \gamma(\sqrt{V_{sb} + \phi_B})(1 - \frac{\alpha\zeta}{L}\sqrt{\phi_B + V_{sb}})$$

$$\zeta = \frac{\sqrt{2\epsilon_{Si}}}{qN_A}$$

where  $\alpha$  is a fitting parameter. As can be seen from the above equation, for short channel devices, there is a linear dependence of  $V_T$  on  $V_{sb}$ . In FD SOI, again from charge-sharing arguments, the  $V_T$  for a FD SOI device, with the back interface depleted, involves replacing  $Q_b$  with  $Q_b(1-d/L)$  [24], where

$$d \simeq \frac{(V_{bi} - \Psi_{sb})}{E_{b(eff)}} \tag{2.1}$$

$V_{bi}$  is the source/drain to channel junction built-in potential, and  $\Psi_{sb}$  is the back interface potential at half way between the source and the drain.  $E_{b(eff)}$  is the effective lateral component of the electric field at the back interface which is given approximately by

$$E_{b(eff)} = [qN_A(V_{bi} - \Psi sb)/2\epsilon_{Si}]^{1/2}$$

$$+ f_a \frac{\epsilon_{ox}}{\epsilon_{Si}} \frac{V_{Gb} - V_{FB}{}^b - \Psi_{sb}}{t_{box}}$$

$$+ f_b \frac{\epsilon_{ox}}{\epsilon_{Si}} \frac{V_{bi} - V_{Gb}{}^b + V_{FB}{}^b}{t_{box}}$$

$\Psi sb$  and  $E_{b(eff)}$  must both be solved iteratively in order to obtain d [24].  $f_a$  and  $f_b$  are fitting parameters. In addition to reducing the front-gate oxide, the back-gate oxide also needs to be reduced in order to maintain the back-gate's control on the charges in the channel, and to reduce the coupling from the source/drain fringing fields, hence larger  $E_{b(eff)}$ , and smaller d. Reducing the silicon film thickness effectively decreases the junction depth. Increasing the silicon film doping also increases the  $E_{b(eff)}$ , i.e. reduces depletion width of the source/drain and channel junction. The downside of having a large body factor in both technologies is that the parasitic source/drain capacitances will increase, the saturation current will decrease, and stacked gates will suffer larger delays. The effects of the drain bias can be included in the above equations using the same charge-sharing arguments for bulk; in FD SOI, however, there is no simple way to incorporate this effect due to the coupling to the back interface, therefore, 2-D numerical simulations is the best way to study these device structures.

#### 2.5 SOIAS Device Structure

The general structure of interest for this work is the back-gated device depicted in Figure 2-4. The top and bottom gates are designed with opposite polarities with the

Figure 2-4: SOIAS back-gated CMOS device schematic.

back-gate having the same polarity as the silicon film. The top and bottom gates are separate and can be switched independently. Therefore, to mimic a dual-gated device, the top and the bottom gates can be tied and swept together. At 1 V or less on  $V_{DD}$ , the back-gate would still function as a threshold voltage modulator of the front-gate. The decision to either implement a dual-gated or back-gated device structure depends on the system usage (burst-mode vs continuously computing), and the bottom gate switching energy vs technology complexity/difficulty trade-offs since a perfectly self-aligned top and bottom gate device is impossible to achieve with technologies that exist to date. In choosing the device design parameters for the SOIAS devices, the emphasis was placed on the maximum process latitude which will yield devices that meet the  $V_T$  and off current requirements at 1 V supply voltage. Figure 2-5 shows an example of such a device from MINIMOS simulation. The specifications for this device is 3-4 decades change in off current at  $V_{DD}$  of 1 V, corresponding to 200 mV of switch

Figure 2-5: Simulated subthreshold I-V at different back-gate biases.

in  $V_T$ . The design parameters are 7 nm front-gate oxide, 40 nm silicon film thickness, 80 nm back-gate oxide thickness. The thick back-gate oxide allows maximum latitude in the formation of the back-gate since source/drain overlap capacitance is small in comparison to the switching capacitance of the front-gate. The silicon film is as thin as practically achievable to maximize the control of the back-gate on the front-gate  $V_T$ . The devices fabricated in this work are designed around these specifications and device parameters. For scaling into the sub-0.2  $\mu$ m regime, the vertical structure ( $t_{ox}$ ,  $t_{Si}$ , and  $t_{box}$ ) must be redesigned to achieve the same threshold voltage control and minimize SCE.

Since the SOIAS device operates in the FD mode, some of the issues associated with the design of FD SOI devices are still present while others are ameliorated by the ability to control the threshold voltage, and to operate at lower supply voltages. One of the key challenges in properly designing the conventional SOI FD devices is obtaining a reasonable threshold voltage in very thin FD films. Especially when designing in the deep submicrometer regime, the tradeoffs of the silicon film thickness, channel doping, and buried oxide thickness needs to be carefully evaluated. Conven-

tionally, the FD SOI has 200-400 nm of buried oxide, and very thin silicon film (40-60 nm). The SOIAS device requires the buried oxide thickness to be reduced to less than 100 nm, and the silicon to approximately 40 nm, and thus reduces the short channel effects, as well as increases the the back-gate control on the front-gate threshold voltage. Since the threshold voltage of the SOIAS device can be precisely controlled electronically, the requirements on the channel doping can be relaxed as long as the film is fully depleted. The large series resistance problem associated with thin silicon films without a good silicide still exist. The reduction of the supply voltage to 1 V or below also avoids the problem of large field-induced drain breakdown.

# Chapter 3

Silicon-On-Insulator-with-Active-

Substrate:

**SOIAS**

# 3.1 Silicon Direct Bonding

Silicon direct bonding or fusion bonding, as the name implies, is the joining together of two silicon wafers (with or without oxide) at room temperature without the aid of an high electric field or gluing agent, and subsequently annealing at high temperatures to seal the bond. Although this concept has been around for quite some time, with the first patent filed in 1966 [25], the demand for SOI material was insignificant at that time. Then in 1985, Lasky et al [26] demonstrated the fabrication of NMOS SOI devices using the bonding and etch-back methodology which spurred a flurry of research and development. Since then, much work has been published which contributed to the understanding of the bonding mechanism and interface quality characterization. Any two very flat and smooth surfaces when brought into contact form a weak bond. The materials of the two surfaces can be metal, semiconductor, insulator, or any combination of these [26, 27, 28, 29, 30]. Once the two surfaces are in contact, a "contact wave" spreads across the entire area from the point of

Figure 3-1: Hydrogen bond formation between two hydrophilic surfaces [26].

contact. The speed of the "contact wave" depends on the flatness of the wafers, the smoothness of the surfaces, and the chemical treatment of the surfaces prior to bonding. The surfaces of these wafers are usually chemically treated to render them either hydrophilic or hydrophobic. The type of bond formed and the bond strength at room temperature depend on the chemical surface treatment. The bond strength after annealing depends on the annealing temperature. The bonding mechanism and bond strength evaluation has been studied extensively. An excellent review paper on this topic can be found in reference [31].

### 3.1.1 The Bonding Mechanism

The wafer surface can be rendered hydrophilic through various treatments. Typically cleaning with heated hydrogen peroxide based solution (e.g. RCA [32] clean or pirahna clean (H<sub>2</sub>SO<sub>4</sub>:H<sub>2</sub>O<sub>2</sub>)) would yield hydrophilic surfaces. Some groups had tried treatment with hot nitric acid (HNO<sub>3</sub>) after the above mentioned cleaning procedures to enhance the hydrophilicity of the surface [33, 34]. For hydrophilic surfaces, the bonding at room temperature is predominately caused by hydrogen bonds between hydroxyl groups and water molecules adsorbed on the surfaces when exposed to air[26], see Figure 3-1. Van der Waals forces between the atoms and the adsorbed molecules also exist [35]. These bonds are electrostatic and relatively weak. The bond strength improvement with annealing temperature is believed to occur in three different regimes with different mechanisms. The temperature boundary is by no means

clearly defined. When the room temperature bonded wafers are annealed at low temperatures (100-200°C), enhanced mobility of the adsorbed molecules is believed to cause more bonds to bridge the gap between the two surfaces, and hence strengthen the bond [36]. For annealing in the 300 °C range, a chemical bonding reaction occurs which replaces the weak electrostatic bonds with covalent Si-O-Si bonds according to the following reaction [26, 36, 37]:

$$Si - OH + OH - Si \rightarrow H_2O + Si - O - Si$$

(3.1)

Abe *et al* believed that the temperature at which the above reaction occurs is around 600 °C [38]. Stengl *et al* proposed a two step mechanism for the formation of the Si-O-Si bonds as depicted in Figure 3-2[39].

Figure 3-2: The bonding mechanism proposed by Stengl *et al* showing the transition from weak hydrogen bonding to covalent Si-O-Si bonding at two different temperatures [39].

These authors proposed that at temperatures above 200 °C, the adsorbed water molecules aggregate into clusters of four molecules, thus reducing the gap between the wafers. At temperatures equal to or above 700 °C, the water molecules diffuse away leaving the Si-O-Si bonds [39]. After the formation of the Si-O-Si bonds, annealing in the temperature range from approximately 600-1100 °C strengthens the bond more because the bonded area increases due to elastic deformation of the wafer around the peripheries of unbonded areas (e.g. a particle) [36]. At even higher temperatures (i.e. ) 1100 °C), the viscous flow of the oxide fills in the microvoids, and the bond strength depends on the mass transport phenomenon, i.e. length of the anneal [36, 40].

Non-hydrophilic surfaces can also be bonded [41, 34, 42, 43, 44]. Spontaneous bonding usually does not occur on these surfaces, but with slight force the wafers can be bonded at room temperature. The hydrophobic silicon wafers are usually dipped in dilute HF prior to bonding. The bonding mechanism for hydrophobic surfaces still remains, for the most part, a mystery. Bengtsson and Engstrom proposed that after treatment in dilute  $HF(\sim 2\%)$ , the surface is predominately terminated by hydrogen atoms; however, the subsequent rinse in deionized water and exposure to air increases the density of hydroxyl groups on the wafer surface, although the surface remains hydrophobic [42]. This may be a possible explanation of adhesion between two hydrophobic surfaces. Himi et al used a similar explanation with highly concentrated HF (~ 49%). For treatment in highly concentrated HF, the surface is predominately terminated with fluorine atoms ( $\sim 37\%$ ). Dipping such a wafer in deionized water will result in replacement of the fluorine atoms with OH groups. They believed that although the amount of OH groups for such a surface is less than the hydrophilic surface, it is enough to form the initial bond at room temperature [43]. Of course, the Van Der Waals forces always exist in both cases, and can also aid in the initial room temperature bonding. Therefore, a hydrophilic surface is not necessary for successful bonding. The bond strength after annealing at high temperatures for the hydrophobic surfaces is stronger than the hydrophilic case. This is due to the epitaxial bonding at the interfaces that is free of oxide [43].

### **3.1.2** Voids

Achieving wafer bonding that is free of voids is an extremely challenging task. There are two category of voids; extrinsic voids and intrinsic voids. Extrinsic voids are those resulting from particulates on the wafer surfaces, local contamination, surface roughness, non-flat surfaces, or gas trapped in pockets when two or more "contact waves" are generated simultaneously at the mating of the two surfaces at room temperature. These type of voids are present at the time of room temperature bonding and would remain after the high temperature anneals. In order to reduce the extrinsic voids, wafer cleaning prior to bonding is critical, and bonding in a cleanroom environment is required. Wafer bowing tend to introduce voids due to multiple points of contact when the wafers are pressed together. Extreme wafer bowing prevents bonding altogether. This problem is more apparent in cases where stressed film layers are deposited on the wafer. Intrinsic voids are only present in silicon to silicon bonding with both hydrophilic and hydrophobic surfaces at intermediate annealing temperatures ( $\sim 200-800^{\circ}C$ ). These voids can be observed after annealing at these temperatures following room temperature void-free bonding. Above 1000 °C, the voids disappear. There is no consensus on the origin of these voids. One explanation proposed was that the voids are formed from the release of water molecules during the Si-O-Si bond formation reaction [27, 39]. The belief is that, at elevated temperatures, the water in the voids would oxidize the silicon. Another group claimed that hydrocarbon contamination of the wafer surface is the cause of these temperature dependent voids [45, 46]. This theory is in part supported by the observation that HF treated wafers has more intrinsic voids compared to those without the HF treatment [45, 34]. At high enough annealing temperatures, either the hydrocarbons decompose into smaller groups and the gas in the voids migrates to the edge of the wafer, or diffuse into the wafer. The total effect may be a combination of the two theories. The biggest mystery, however, is the absence of intrinsic voids at these intermediate temperatures for bonding silicon to an oxidized wafer or quartz. Abe et al has shown that at least 20 nm of silicon dioxide is needed on one of the wafers to

produce void-free bonded pairs with annealing in the intermediate temperature range [28]. The same observation was made for bonding silicon to sapphire [28]. One explanation may be that whatever is trapped at the interface, be it water or hydrocarbon groups, can readily diffuse into the oxide at lower annealing temperatures. Annealing at lower temperatures is attractive for bonding a wide variety of materials, especially for metals used in interconnects. Recently, successful bonding of cobalt silicide and tungsten has been demonstrated at annealing temperatures below 900 °C [29, 30]. This author believes this will be the trend of wafer bonding in the future.

### 3.1.3 Bond Strength

The methods derived for evaluation of bonding strength are destructive and semiquantitative. Two widely used methods are the measurements of fracture strength and surface energy [27, 36, 47, 48]. The fracture strength technique is a direct measurement of the bond strength and involves physical separation either at the bond interface, which yields the true bond quality, or fracture in one of the bonded wafers which implies that the bond strength is equivalent to or greater than the fracture strength of the substrate. Usually a strong adhesive is used to glue "handles" to the bonded wafers, and a force perpendicular to the bonded interface is applied to pull the wafers apart or until fracture. Figure 3-3 shows the measured fracture strength for silicon to silicon bonding and oxide to oxide bonding as a function of annealing temperature [27, 47].

The surface energy measurement technique was developed by Maszara et al [36] based on the theory of crack propagation in a cleaved bulk sample developed by Gillis and Gilman [49]. The surface energy measurement technique involves the insertion of a blade of a certain thickness at the bonding interface, and the length of the crack is the distance from the edge of the wafer where the blade was inserted to the point where the wafers still remained bonded. The surface energy is inversely proportional to this length [36]. Figure 3-4 shows the measured surface energy as a function of annealing temperature for silicon to silicon and oxide to oxide bonding [36, 50]. All these figures show a similar trend with three fairly distinct regions which is consistent

Figure 3-3: (a) Fracture strength for SiO<sub>2</sub> to SiO<sub>2</sub> bonding [47]. (b) Fracture strength for Si to Si bonding [27].

with the explanations given above for the bonding mechanisms at different annealing temperatures. The surface energy for silicon to silicon bonding seems to be a lot higher than oxide to oxide bonding which is contradictory to the direct fracture strength measurement. Since the loading force for these two measurements are different, perpendicular to the bonded interface for the fracture strength measurement and parallel for the surface energy measurement, a direct translation of surface energy to fracture strength may not be straightforward.

Figure 3-4: Surface energy of SiO<sub>2</sub> to SiO<sub>2</sub> bonded interface (open symbols) [36], and that of Si to Si bonded interface (filled symbols) [50].

### 3.2 SOIAS Technology

The development of the Silicon-On-Insulator-with-Active-Substrate (SOIAS) technology was guided by the understanding of the silicon bonding mechanism as presented in the previous sections. In conventional silicon fusion bonding, the bonded wafers usually do not contain more than two layers of thin films. The concept of SOIAS technology can be taken to many levels of complexity. The fundamental idea behind this technology is to add one or more conductive under-layers beneath the buried oxide of a SOI structure. Such layers can serve as buried interconnects or gates or both, i.e. enabling integration in the third dimension. The fabrication of SOIAS structures leverages off many of the technologies developed for bulk and SOI CMOS processes (e.g. CMP and wafer bonding). There are several options and var-

ious degrees in which the buried layer or layers can be rendered conductive. In one extreme, the buried layer can be a refractory metal such as tungsten, or silicides of such metals which can withstand subsequent high temperature processing. In this case, the buried conductive layer must be pre-patterned prior to bonding, and a dielectric must be deposited and planarized. This bonding process is more complicated and challenging. In the other extreme, a blanket insulating/semi-insulating layer (e.g.. intrinsic amorphous/polycrystalline silicon) can be used, and selective areas of the buried layer can be made conductive by ion implantation with dopants. This work focuses on the development of the latter approach.

### 3.2.1 SOIAS Wafer Fabrication