## Strategies for Manufacturing Low Volume Semiconductor Products in a High Volume Manufacturing Environment

by

Robert L. Scholtz III B.S. Mechanical Engineering, Purdue University, 1995

Submitted to the MIT Department of Mechanical Engineering and to the Sloan School of Management in partial fulfillment of the requirements for the Degrees of

Master of Science in Mechanical Engineering and Master of Business Administration

at the Massachusetts Institute of Technology June 2002

© Massachusetts Institute of Technology, 2002, All rights reserved

| Signature of Aut | thor                                     |                                                                    |

|------------------|------------------------------------------|--------------------------------------------------------------------|

|                  |                                          | Department of Mechanical Engineering<br>Sloan School of Management |

|                  |                                          | May 10, 2002                                                       |

| Certified by     |                                          |                                                                    |

|                  |                                          | Jesús A. del Alamo                                                 |

|                  |                                          | Professor of Electrical Engineering                                |

|                  |                                          | Thesis Supervisor                                                  |

| Certified by     |                                          |                                                                    |

|                  |                                          | U Stephen C. Graves                                                |

|                  | Leaders                                  | for Manufacturing Professor of Management and Engineering          |

|                  |                                          | Thesis Supervisor                                                  |

| Certified by     |                                          |                                                                    |

| •                |                                          | Stanley B. Gershwin                                                |

|                  | Seni                                     | or Research Scientist, Department of Mechanical Engineering        |

|                  |                                          | Thesis Reader                                                      |

| Accepted by      |                                          |                                                                    |

|                  |                                          | Ain A. Sonin                                                       |

|                  |                                          | Chairman, Department Committee on Graduate Students                |

|                  |                                          | Department of Mechanical Engineering                               |

| Accepted by      |                                          |                                                                    |

| Accepted by      |                                          | Margaret Andrews                                                   |

| ~                |                                          | Executive Director of Master's Program                             |

|                  | MASSACHUSETTS INSTITUTE<br>OF TECHNOLOGY | Sloan School of Management                                         |

|                  |                                          |                                                                    |

|                  | JUN 2 4 2002                             | BARKER                                                             |

|                  |                                          |                                                                    |

|                  | LIBRARIES                                |                                                                    |

## Strategies for Manufacturing Low Volume Semiconductor Products in a High Volume Manufacturing Environment

by

Robert L. Scholtz III

Submitted to the MIT Department of Mechanical Engineering and to the Sloan School of Management on May 10, 2002 in partial fulfillment of the requirements for the Degrees of Master of Science in Mechanical Engineering and

Master of Business Administration

# ABSTRACT

The rapid growth of the digital communications market has prompted several large semiconductor manufacturers, including Intel Corporation, to begin the design and manufacture of communication ICs. The communications ICs are currently produced in much lower volumes than products such as microprocessors and memory. These low-volume products have been reported to cause operational problems, such as excessive cost, slow throughput time, and low yield when manufactured in semiconductor fabs designed for high volume manufacturing.

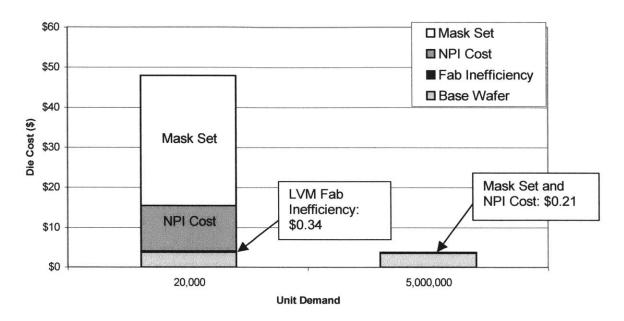

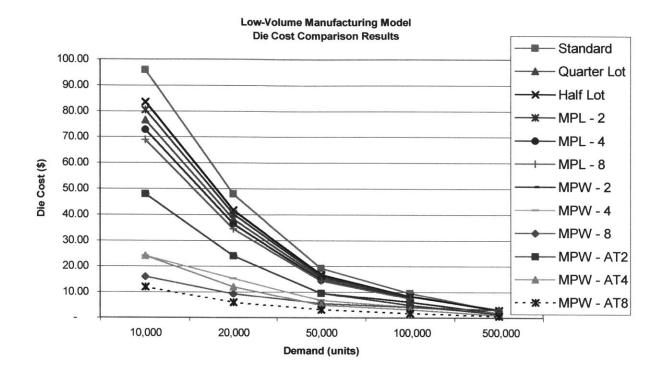

This thesis examines the operational problems caused by the manufacture of low-volume semiconductor products and explores potential improvements. A financial model was developed to compare the cost of manufacturing low-volume products using several different strategies in existing high-volume fabs. The model results demonstrated that mask set cost, a fixed cost, becomes a very large component of total production cost as the product volume is reduced. Further, this model identified multi-product wafers, a scheme of fabricating several products on a single wafer, as a strategy with potential for savings up to approximately 75% of the manufacturing cost of low-volume products.

A second financial model was developed to consider more detailed aspects of fabricating products on multi-product wafers. This model considered the sensitivity of the potential cost savings to changes in demand and changes to the design of multi-product wafers. This model also demonstrated that significant savings are possible with the multi-product wafer strategy, especially if the products are carefully matched (by die size and demand) with other products on the multi-product wafer.

Finally, a brief organizational study was conducted to analyze the implementation of a multi-product wafer manufacturing process for the production of low-volume CMOS ICs at Intel Corporation.

| Thesis Supervisors: | Jesus del Alamo<br>Professor of Electrical Engineering   |  |

|---------------------|----------------------------------------------------------|--|

|                     | Stephen Graves<br>Professor of Management                |  |

| Thesis Reader:      | Stanley Gershwin<br>Department of Mechanical Engineering |  |

## **Acknowledgements**

Dedicated to my wife, Jennifer

I would like to thank my internship supervisor, Brian Kelly, for his advice and support throughout my study of low-volume manufacturing strategies. I would also like to thank Todd Kinkade for joining me in developing the models presented here, Dave Fanger for his technical advice, Chris Richard for his manufacturing strategy advice, and Intel's MPS working group for welcoming me and allowing me to contribute to its charter.

I would like to thank my thesis supervisors Steve Graves and Jesus del Alamo, and my thesis reader Stan Gershwin, for their patient guidance and support as this project has evolved.

I would also like to thank my LFM colleague, Bob Kelly, for many helpful discussions about Intel and its manufacturing processes.

Finally, I would like to thank the Leaders for Manufacturing Program and Intel Corporation for making this work possible.

# **Table of Contents**

| ABSTRACT                                                                       | 3         |

|--------------------------------------------------------------------------------|-----------|

| Acknowledgements                                                               | 4         |

| Table of Contents                                                              |           |

|                                                                                |           |

| Chapter 1: A transition to low-volume IC manufacturing                         | 7         |

| 1.1 The Problem                                                                | 8         |

| 1.2 Sources of potential solutions                                             |           |

| 1.3 Thesis Structure                                                           | .12       |

|                                                                                | 14        |

| Chapter 2: Low-volume IC manufacturing                                         |           |

| 2.1 Technical challenges of low-volume IC manufacturing                        |           |

| 2.1.1 Photolithography                                                         |           |

| 2.1.2 Chemical Mechanical Polishing                                            |           |

| 2.1.3 Thins Films                                                              |           |

| 2.1.4 Sorting                                                                  |           |

| 2.1.5 Other processes.                                                         |           |

| 2.1.6 New Product Introductions                                                |           |

| 2.2 Existing examples of low-volume IC manufacturing                           | 10        |

| 2.2.1 "Shuttles" for prototypes and low-volume products                        | ·19<br>   |

| 2.2.2 Intel's low-volume fabs                                                  |           |

| 2.2.3 Mini-fab – Ericsson                                                      |           |

| 2.2.4 Work cell layout                                                         |           |

| 2.3 Alternatives for low-volume IC manufacturing                               |           |

| 2.3.1 Multi-product wafers                                                     |           |

| 2.3.2 Multi-product lots                                                       | .21<br>20 |

| 2.3.3 Reduced NPI effort                                                       |           |

| 2.3.4 Small lot size<br>2.4 Conclusions                                        |           |

| 2.4 Conclusions                                                                | . 29      |

| Chapter 3: Financial analysis of potential low-volume manufacturing strategies | 30        |

| 3.1 Development of a financial model                                           | .30       |

| 3.1.1 Calculation of the wafer quantity requirement                            | .31       |

| 3.1.2 Tailoring the wafer requirement to each LVM strategy                     |           |

| 3.1.3 Wafer cost components                                                    |           |

| 3.1.4 Mask set cost                                                            |           |

| 3.1.5 Die cost calculation                                                     |           |

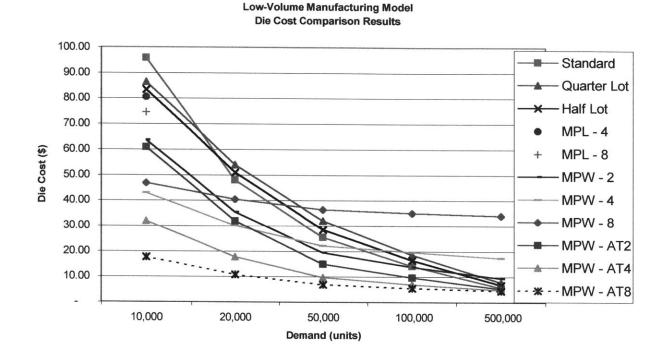

| 3.2 Low-Volume Manufacturing Cost Model results                                |           |

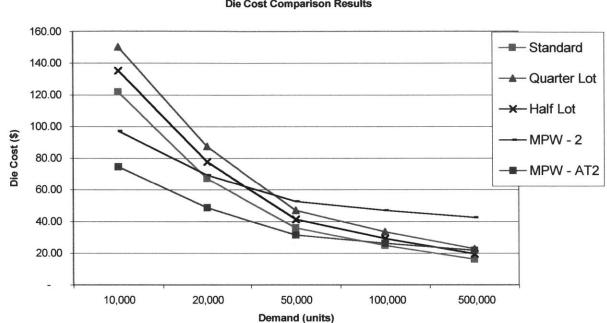

| 3.2.1 Die cost comparisons with increasing die size                            | .47       |

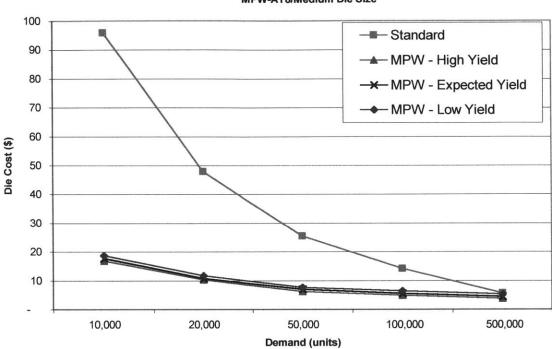

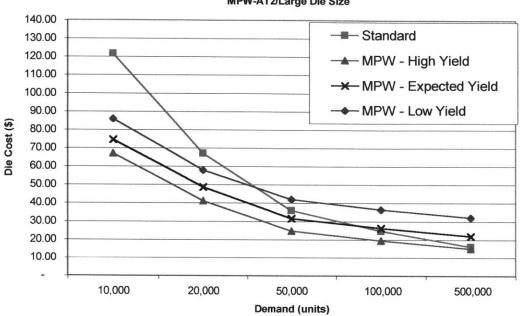

| 3.2.2 Impact of die yield on manufacturing strategy                            | .51       |

| 3.2.3 Impact of New Product Introductions (NPIs) on wafer cost                 | .53       |

| 3.3 Mapping the lowest cost LVM strategies                                     | .54       |

| 3.4 Conclusions                                                                | .56       |

| Chapter 4: Development and results of the Multi-product Wafer Cost Model | 57 |

|--------------------------------------------------------------------------|----|

| 4.1 MPW Cost Model calculations                                          |    |

| 4.1.1 Modeling an MPW with multiple die sizes                            |    |

| 4.1.2 Optimization of die ratio                                          |    |

| 4.1.3 Total cost calculation                                             |    |

| 4.2 Results of the MPW Cost Model                                        | 62 |

| 4.2.1 Sample MPW Cost Model results                                      |    |

| 4.2.2 MPW sensitivity to demand changes                                  |    |

| 4.3 MPW Cost Model conclusions                                           |    |

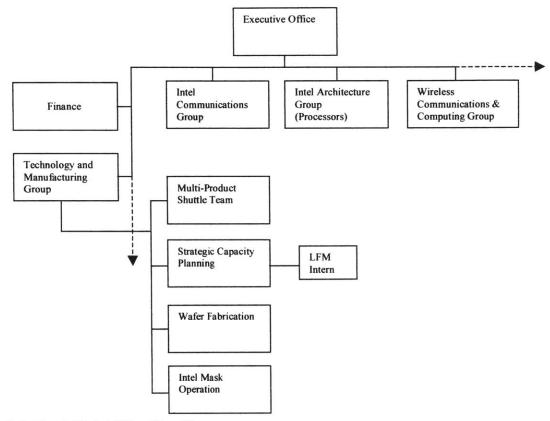

| Chapter 5: Organizational Challenges of Implementing MPWs                | 69 |

| 5.1 Background of the MPS Working Group                                  |    |

| 5.2 Strategic design lens                                                |    |

| 5.2 Surger design lens                                                   |    |

| 5.4 Cultural lens                                                        |    |

| 5.5 Conclusions                                                          |    |

|                                                                          |    |

| Chapter 6: Conclusions and recommendations for further research          | 75 |

| Appendix A: List of Acronyms                                             | 78 |

| Appendix B: Low-Volume Cost Model results                                | 79 |

| Comparison of low-volume manufacturing strategies' die costs             | 79 |

| Yield impact on MPW die cost                                             |    |

| References                                                               | 82 |

# Chapter 1: A transition to low-volume IC manufacturing

As the market for personal computers has matured in the past decade, the growth rate of the microprocessor business has slowed considerably. Microprocessor manufacturers, who have become accustomed to strong "double-digit" growth, are being forced to look beyond the processor to find attractive growth opportunities.

Over the past few years, Intel Corporation has been entering the communications markets such as Ethernet and wireless in an attempt to find markets for ICs with high-expected growth. Table 1.1 compares the expected growth and size of the PC market and a few communications equipment markets. While the communications markets are currently relatively miniscule, the growth potential is remarkable.

| Market              | Annual Growth Rate | 2002 Projected Market Size |  |

|---------------------|--------------------|----------------------------|--|

|                     |                    | (\$-million)               |  |

| Personal Computers  | -10 - 10%          | 190,000                    |  |

| 10 Gigabit Ethernet | 221%               | 714                        |  |

| Metro Ethernet      | 48%                | 155                        |  |

| Network Processors  | 120%               | 194                        |  |

Table 1.1: Forecast annual growth of selected worldwide technology markets, 2000 - 2006

Source: Daiwoo Securities[1], InfoTech Trends[2]

BusinessWeek Magazine reported that Intel has pumped more than \$10 billion into 34 acquisitions over the past three years. These deals were expected by CEO Craig Barrett to enable business units such as the Communications Group and the Wireless Communications and Computing Group to grow 50% annually [3].

One of the results of these acquisitions has been the creation of a diverse product line that includes both high-value, low-volume components and lower-value, high-volume components. The products are currently produced by a combination of internal and externally subcontracted manufacturing, with much of the external manufacturing at subcontracted semiconductor foundries being a legacy from the manufacturing strategies of the original acquisitions.

A key strategy with the new businesses is to bring the manufacturing of many of the new products into Intel's fabs. Intel management believes it can achieve several benefits by bringing the manufacturing in house. The new products can benefit from Intel's logic technology, which is considered to be superior to the logic performance offered by the foundries. Additionally, the products are produced with greater confidentiality, thus protecting the intellectual property from competitor's eyes for a longer period. Further, internal manufacturing would simplify the supply chain by reducing the number of suppliers that must be managed.

## 1.1 The Problem

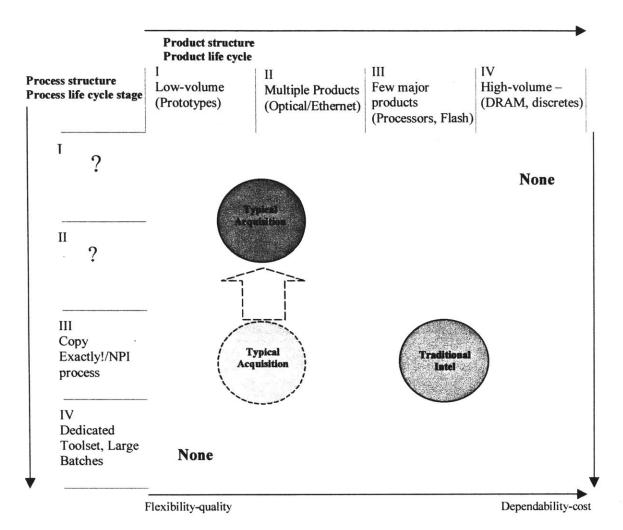

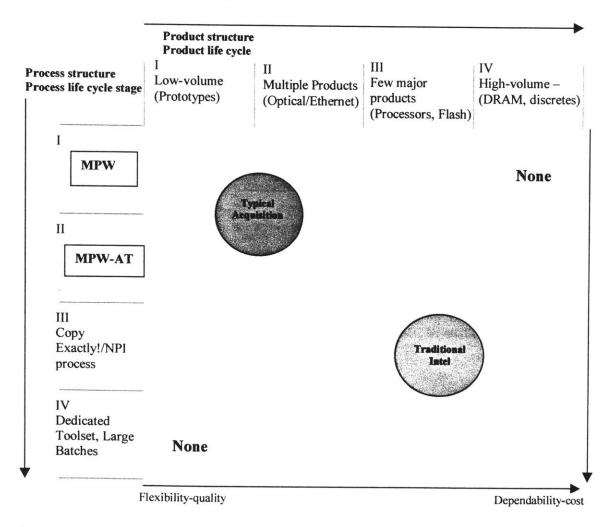

The shift of the product portfolio to lower volume, high mix products without a change to the manufacturing strategy will potentially cause significant delays and unnecessarily high costs in the production of these products. The product-process matrix as proposed by Hayes and Wheelwright demonstrates that the manufacturing process should match the product being produced. Ideally, the products map into the diagonal of the proposed product-process matrix [4]. This product-process matrix is shown in Figure 1.1.

Figure 1.1: The Product-Process matrix adapted to semiconductor manufacturing [4]

Intel has created a manufacturing system that is tailored to the needs of the products it has traditionally manufactured. Those products, primarily microprocessors and flash memory chips, are produced in volumes of millions of units per year and are represented by the "Traditional Intel" circle in the above figure. The production of such high-volume components requires that the manufacturing process be focused on repeatability and high yield. The combination of Intel's Copy Exactly! (CE!) Methodology and New Product Introduction (NPI) process has done just that. Intel's CE! Methodology is the process by which new manufacturing processes are transferred from a development fab to a multiple high-volume manufacturing (HVM) fabs [5]. This rigorous process ensures that identical products can be produced at multiple fabs and that

high yields are achieved quickly during the ramp to high-volume production. The NPI process optimizes the parameters of the manufacturing process to each product. This process enables Intel to achieve high yields, which we will see is a strong lever in reducing manufacturing costs of low-volume products.

Intel's recent entry into communications markets has added new product categories to the product portfolio. The "Typical Acquisition" circle on the product-process matrix of Figure 1 represents these product categories. One can see that these lower volume products, if manufactured with the current process, fall off of the diagonal in which the process is well matched to the process. As suggested by the product-process matrix, it is not ideal to blindly push low-volume products into the same process used by Intel's high-volume products. Ideally, these low-volume products should have a manufacturing process tailored to their specific needs, thus bringing the products into the ideal diagonal of the product-process matrix. But what process should be used? And can Intel's fabs accommodate a fabrication methodology specific to low-volume products? These are some of the questions that this thesis will attempt to address. To begin to explore these questions, the problems of running low-volume components in the existing fabs are described below.

Problems with low-volume products produced in high-volume fabs are caused both by the physical limits of the manufacturing process and the incentives created by management to govern the process. The primary problems are as follows:

**High setup costs per wafer** – The high mix of products inherent with low-volume production means that more setups will have to be conducted in the fab. Since the manufacturing process is optimized for each product, the tools must be set to different parameters for each product change. Making matters worse, the low-volume wafers cannot spread this setup across a large number of wafers.

More New Product Introductions (NPIs) – An NPI is the time-consuming and laborintensive procedure of optimizing the manufacturing process for each new product. The procedure is designed to maximize the yield of the new product. Low-volume products

suffer two negative effects from NPIs. First, the cost of the additional labor and the lost fab tool time is not spread over millions of units, so the cost per die is high. Second, the low-volumes prevent yield enhancements from significantly improving the manufacturing costs. Yield improvements do not significantly reduce the manufacturing capacity required because so few wafers are manufactured. Thus, a large improvement in yield would only create a relatively small reduction in wafers required.

Slow tool run rates – Low-volume products cause some of the tools to run slower because of the increased inspection required to assure good quality in the early stages of a product's life. High-volume products are able to rely on statistical samples to reduce the number of inspections required by each lot.

**Slow throughput time** – The combination of the above problems increases the time required for a product to be manufactured in the fab. But this is not all. The incentives used to motivate the workforce and management include metrics such as tool utilization, which are made worse by the aforementioned effects. So, the low-volume products receive a lower priority, which causes them to sit idle in the fab while the higher volume products move through rapidly.

**Poor yield** – Product yield is often improved over time as learning occurs. With lowvolume products, the production run is too short to implement improvements to the process that may improve yield. While it may not make sense to expend the effort to improve the yield of some low-volume products, any low yield numbers tend to raise red flags in the Intel culture where profitability has been tied to yield for many years.

**Opportunity Cost** – Because many of the problems listed here effectively reduce the capacity of the fab, the opportunity cost of other products that could have been run may become an issue. The fab capacities are typically constrained during the ramp of a new process technology, so any "wasted" tool time is a lost opportunity to produce another product. Due to its complexity, the opportunity cost was considered beyond the scope of this thesis and will not be explored further.

## 1.2 Sources of potential solutions

This thesis explores and compares the potential of several strategies for manufacturing lowvolume microelectronic products in the context of a high-volume IC manufacturer. Potential solutions to the problem of manufacturing low-volume products were collected from a variety of sources. Intel's process and industrial engineers were asked for ideas to improve the current process to accommodate low-volume products. A comparison of the major wafer foundries' processes for manufacturing prototypes was conducted. Other literature suggesting alternative methods of manufacturing semiconductors were also considered by the author.

Some constraints were placed on the range of potential solutions considered to enable Intel to continue its manufacturing process development cycle while manufacturing low-volume products. Thus, the scope of this thesis was limited to the products that can be manufactured in Intel's existing CMOS logic fabs. It was assumed here that the process technologies used by these low-volume communication products would be identical to or relatively minor revisions of the process technologies used to produce microprocessors. It was also assumed that the total combined volume of Intel's low-volume products is too low to justify the development and construction of a fab designed solely for the purpose of manufacturing low-volume wafers.

## 1.3 Thesis Structure

This thesis is divided into six chapters plus an Appendix. Chapter 2 delves into the technical challenges of producing low-volume products and considers several solutions to these problems. Chapter 3 discusses the development and results of a model used to evaluate various manufacturing strategies for low-volume products. The model, known as the Low-Volume Manufacturing (LVM) Cost Model, enables the user to determine the best manufacturing strategy (of those considered) for a given product. This chapter identified a process called "Multi-Product Wafers" to have potential for significant cost savings. Chapter 4 takes the cost modeling a step further with a more detailed focus on multi-product wafers. Chapter 5 steps

away from the technical issues and considers the organizational challenges that will accompany the implementation of the multi-product wafer strategy for producing low-volume products. Finally, Chapter 6 revisits the Hayes-Wheelwright product-process matrix, summarizes this thesis, and considers topics for further research.

# **Chapter 2: Low-volume IC manufacturing**

As mentioned in Chapter 1 there are many problems that occur in an IC fab when low-volume products are introduced. The introduction of low-volume products into a high-volume wafer fab has different impacts on the various functional areas. The effect is most pronounced in the photolithography area, but other areas are also impacted. This chapter will explore the most dramatic effects low-volume products have on fabs, then will investigate what has been done in the past with low-volume semiconductor product manufacturing. This will allow us to synthesize low-volume manufacturing strategy options for further investigation in this thesis.

## 2.1 Technical challenges of low-volume IC manufacturing

This section explores the challenges that low-volume products present to the operation of a highvolume semiconductor fabrication facility, or fab. The low-volume products not only affect the performance of the different tools used in IC production, but also some processes such as the New Product Introduction process.

## 2.1.1 Photolithography

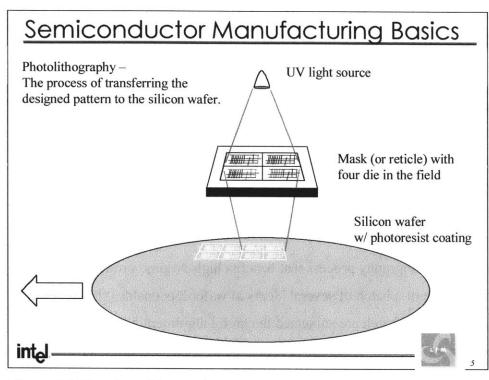

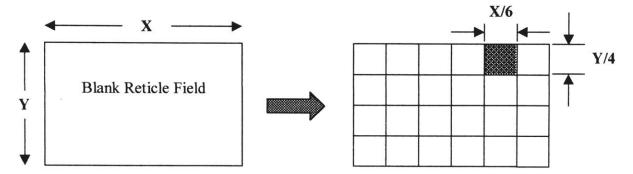

Photolithography is the process of transferring circuit patterns to the silicon wafers. These patterns act as masks to allow ion implantation or etching to be performed on narrowly designated areas of the wafer. The photolithography tools, known as steppers, are the most expensive tools in a fab. Because of this, the steppers are typically the bottlenecks in the fabrication process. As the bottleneck, any wasted time on the stepper is lost fab capacity. Thus fab incentive systems are designed to maximize the stepper utilization. The steppers are designed to rapidly and accurately project patterns on individual wafers. A simple diagram of the photolithography stepping process is shown in Figure 2.1.

Figure 2.1 The photolithography process

Low-volume production runs have three primary effects on the photolithography area. These effects are: 1) more setups, 2) slower run rates, and 3) more mask sets<sup>1</sup> are required. The increased setup time and slower run rates reduce the production capacity of the fab by reducing the number of wafers per hour that can be patterned. Because a new mask set is required for each product, a portfolio of many low-volume products can significantly increase the capital expense and fixed costs.

The setup time is a function of two processes that typically occur during a changeover to a different product. First, the reticle<sup>2</sup> must be changed and aligned. The steppers typically have an automated magazine that holds several reticles to speed up the process. Once the reticle is changed, it must be carefully aligned to ensure that the pattern that will be printed on the wafer

<sup>&</sup>lt;sup>1</sup> A mask set is a set of patterns, typically chromium patterns on a quartz glass window, that are projected onto the silicon wafer surface with UV light. Each mask, also known as a reticle, is analogous to a "negative" of a photograph. Since each layer of the semiconductor manufacturing process requires a unique reticle, a mask set is typically comprised of 20 to 30 reticles.

<sup>&</sup>lt;sup>2</sup> See footnote 1 (above)

will be in focus and correctly positioned relative to the previous and subsequent layers. The reticle change and alignment process causes a down time on the order of five minutes.

One part of the photolithography process is the curing of the photoresist<sup>3</sup>, which is conducted in an oven. Different products may require a different photoresist recipe, which can require different oven temperatures. An oven temperature change requires a period of roughly 30 minutes to achieve stability. Thus, product changes can create significant delays in the photolithography area.

An interesting feature of the lithography process that benefits high-volume products is that learning during the processing of a batch of several identical wafer lots enables the stepping rate to increase. The early wafers in a batch are subjected to careful alignment and mid- and post-process checks. However, as a statistical sample is collected, fewer checks are conducted and the wafer lots progress significantly faster (on the order of 20 - 30 % faster run rate).

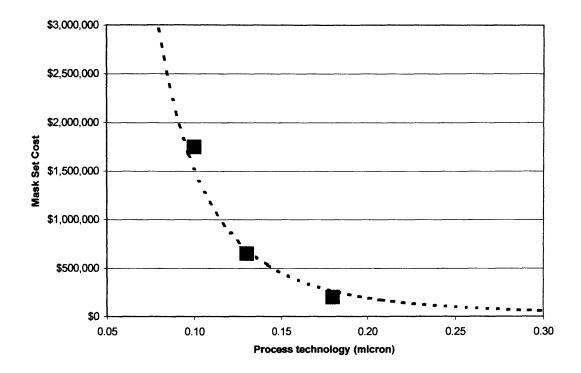

The mask sets used to transfer circuit designs to the wafer, become a proportionately greater expense for low-volume products. Because a new mask set is required for every product, low-volume products cannot spread the associated mask costs across the sale of millions of units. Further, the cost of producing mask sets has been increasing as process technologies use finer and finer line widths. These smaller feature sizes in the semiconductor design require more expensive electron-beam equipment and phase shift coatings to produce the mask set. For example, a recent article published in the Semiconductor Business News reported the cost of a mask set for a 0.13-micron design runs about \$650,000. The cost of a mask set for 0.10 micron design is expected to rise to \$1.5 to \$2 million. [6]

## 2.1.2 Chemical Mechanical Polishing

The chemical mechanical polishing (CMP) process is used to planarize the surface of a wafer after layers of material have been added during the fabrication process. This process is

<sup>&</sup>lt;sup>3</sup> Photoresist is the light sensitive coating that enables the circuit pattern to be transferred to the surface of the silicon wafer.

performed by pressing the wafer against a rotating pad in the presence of chemically activated, abrasive slurry. The combination of chemical and mechanical material removal enables a nearly perfect flat surface to be created. The resulting smooth surface allows the photolithography steps to achieve a more precise focus, resulting in better yield and finer line width capability[6].

------

The CMP tools see a loss in productivity with low-volume products primarily due to the additional setups that are required. However, the loss of productivity depends on the tool type and product mix. Some CMP tools that have multiple spindles (and can run several wafers at a time) are able to process wafers to different specifications simultaneously. In other cases, the tool must be completely cleared of one product before another can begin its processing.

The effectiveness of CMP process is also dependent on learning from wafers fabricated during and after the NPI process. The material removal rate is partially a function of the pattern density of the product being polished. Because the pattern density varies from product to product, the optimal CMP tool settings differ for various products. Low-volume products, with fewer wafers required, cannot spread the cost of this learning across as many products.

Later in this thesis, we will see that CMP may cause problems with wafers with multiple products fabricated on them. The steep gradients of pattern density caused by placing different products in close proximity make the process difficult to optimize for maximum yield.

## 2.1.3 Thins Films

The thin films tools deposit very thin layers of metal or dielectric material on the wafers. These tools are chemical reactors that typically use a process known as chemical vapor deposition (CVD). Low-volume products have a relatively small but measurable impact on the productivity of the thin films tools. This impact is simply due to the additional setups required with low-volume products.

## 2.1.4 Sorting

The sort area of the fab tests the individual dies on a wafer for functionality and speed. This knowledge enables several decisions to be made. It enables the fab manager to understand the process capability independent of the packaging process. It also allows defective dies to be discarded prior to the packaging step.

Sort requires expensive probing tools to measure test structures on the wafer. Every product requires a corresponding probe card that has tiny pins that contact the die in the appropriate contact pads. These probe cards are a capital expense requiring tens of thousands of dollars per product. Very low-volume products typically skip the sort step, at the expense of packaging nonfunctional die.

#### 2.1.5 Other processes

The other processes in the wafer fab, such as etch and ion implant are not as affected by lowvolume products. These tools either have small setup times or run products in small batches regardless of the total number of wafers coming through the area. Additionally, these tools comprise a smaller percentage of the total fab capital spending than the tools described in sections 2.1.1 through 2.1.4. Thus a small increase in setup time will have an even smaller impact on overall spending.

## 2.1.6 New Product Introductions

New Product Introductions (NPIs) consume vast amounts of tool, operator, and engineering time. Every time a new product is launched in a fab, the process is optimized for that product. There are baseline tool settings for each process, but Intel has found that product yields can be significantly improved by choosing the best settings for each product. For example, the CMP results are largely affected by the density of features on a product. Several wafers of a new product may run through the CMP process with different polish times for each. The wafers are then inspected to determine which setting provides the best planarization without excess material

removal. This process of selecting the best settings for an NPI can take several hours for each step in the semiconductor manufacturing process. Adding the setup times for every layer results in a delay on the order of weeks.

-----

The high cost of setups for NPIs is not a problem for a fab that only runs a few stable products. The NPI cost is spread across many wafers, and the yield improvement justifies the cost. As some fabs start manufacturing low-volume "custom" products, the cost and lost productivity due to the NPI process will become a more significant impact to wafer cost. For low-volume products, the cost of the NPI may not be worth the yield improvement that it drives.

## 2.2 Existing examples of low-volume IC manufacturing

Several companies, including Intel have manufactured low-volume products in their fabs. A few low-volume manufacturing strategies have been proposed, but most fabs seem to treat low-volume products as "second class" and give priority to high-volume products. This section is intended to look at a cross-section of some of the strategies that have been used to manufacture low-volume chips that may apply to the low-volume communication chips on Intel's product roadmap. Each strategy has various costs and benefits depending on the manufacturing situation.

## 2.2.1 "Shuttles" for prototypes and low-volume products

The so-called "shuttle" methodology has been effectively implemented by the semiconductor foundries to support the prototyping needs of fabless chip design houses. Shuttles are multi-product wafers (MPWs) on which the products of several customers are jointly fabricated, thus allowing the customers to share the mask set and other fixed costs. The shuttle programs are run in an analogous fashion to a shuttle bus. The foundries publish a schedule of the "departure dates" for a wafer lot to begin the fabrication process for a specific manufacturing process technology. Each process technology typically has shuttle departure schedules that range from weekly to quarterly departures, depending on the demand. For each shuttle, the mask set is divided into a number of seats of fixed size and price. Customers are offered the purchase one or more seats prior to the departure date. Then, the customers must submit their chip designs for

the shuttle by the departure date. The shuttles do not wait for late customers to ensure the satisfaction of the customers who submitted their designs on schedule. Thus, a late passenger simply waits for the next shuttle. Once the components are fabricated, the wafers are diced and packaged, and then the appropriate units are sent to each customer.

An example of a well-implemented shuttle program is Taiwan Semiconductor Manufacturing Company's (TSMC's) CyberShuttle program. The CyberShuttle program has a schedule including 16 different process technologies with an aggregate of over 100 shuttles per year. A typical shuttle run from TSMC will provide the customer with forty packaged units, with additional units available at extra cost. The TSMC program is focused on providing prototypes at relatively low cost and fast turnaround time. However, the program does not provide support for production parts. Thus once an acceptable prototype has been obtained, the product goes into production using standard high-volume manufacturing methods. [8]

The shuttle process provides several benefits to both the supplier and customer. The customers are able to share the high fixed cost of the mask set, resulting in significant savings over a dedicated product run. The lower cost enables the designers to try several iterations of a product before finalizing a design. The frequent departures of shuttles support the ability to try multiple iterations and allow flexibility in scheduling product launches. The foundry benefits by allowing potential customers to "sample" its service for relatively low cost and by selling the shuttle seats at a higher price than a corresponding seat price on a regular production wafer. In the fab, many of the potential low-volume runs are consolidated into fewer standard runs. This helps bring the average batch size up, which results in higher tool utilization and lower wafer costs.

Shuttles also have some challenges associated with them. Because the shuttles typically have many different products "on-board", the process cannot be optimized for any single product, and the yields may be lower than production parts. Also, since different customers own the products on a single prototyping wafer and intellectual property must be protected, TSMC cannot provide whole wafers to any customers. While the designers can get functional information from the packaged units, there are often tests that the designers would like to perform while the dies are still part of a whole wafer. By committing that the shuttles will leave on time, TSMC is taking

some risk that the shuttle will not be filled. Since the cost of a shuttle wafer is the same whether there are ten passengers or a single passenger, TSMC could end up subsidizing under-subscribed shuttles. Of course, once the demand for prototypes is well known, the pricing and schedules can be set to accommodate demand variability risk.

The success of the shuttle programs at the foundries suggests that the MPW concept is worth exploring for low-volume manufacturing.

## 2.2.2 Intel's low-volume fabs

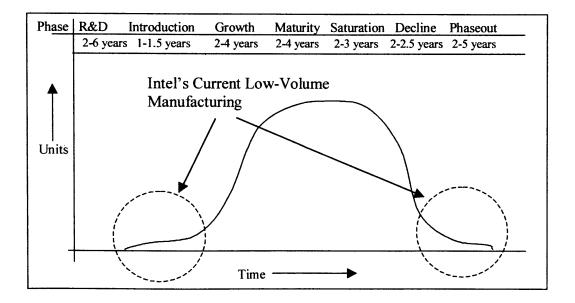

Intel does have some fabs that produce low-volume products. However, these fabs tend to produce products that are at the start or the tail of the product lifecycle as depicted in Figure 2.2. The location of the products on the product lifecycle has an important impact on the manufacturing strategy used. The primary method of dealing with low volumes is to make low-volume products wait in queue until there is enough demand requiring several production lots or until the deadline is fast approaching.

Figure 2.2: The Intel product lifecycle [9]

The first type of Intel fab that frequently runs low-volume products is the Technology Development fab, or TD fab. During the introduction phase of a new logic CMOS product or process, the manufacturing process is being refined in the TD fabs for transfer to Intel's highvolume fabs. The anticipation of transferring the process to other fabs combined with Intel's Copy Exactly! methodology forces the low-volume TD fabs to operate like high-volume fabs. Thus, there is an attempt to maintain large batch sizes when possible, and single-lot products have to wait. [4]

The second type of Intel fab that produces low-volume products is one that produces products that are being phased out. These products are typically produced on an old process technology and are concentrated to a single fab. This concentration creates a wide diversity of products and demand requirements in that fab. However, one benefit of this situation is that the fab can be more flexible in its operation and scheduling of production since the products and processes are guaranteed not to be transferred to other fabs. The Copy Exactly! methodology does not necessarily apply at the tail of the lifecycle.

The low-volume manufacturing process at the end of a process's life cycle is somewhat constrained by the tools used in the fab. The manufacturing processes at the tail are still virtually the same as they were during high-volume manufacturing, so the tools are reused as the process demand shrinks. Because the tools and mask sets are already bought and paid for, it does not make sense to purchase and qualify new low-volume tools for the tail of the product. Excess tools are disposed of or upgraded for use with new process technologies.

The primary process for improving the efficiency of running low-volume products at the end of the life-cycle is to delay production of small batches until there is justification to run a larger batch. Unfortunately, this results in many small lots waiting in queue until the delivery dates approach, and then the lots must be expedited through the fab. Once the lots are completed, significant finished goods inventory must be held which is an additional expense.

Overall, the current methods of manufacturing low-volume products at Intel are not compatible with the requirements for new low-volume communications products. The tradeoff with these

methods is to sacrifice throughput time in order to reduce wafer cost. In the communications sector, this is unacceptable.

-----

-----

## 2.2.3 Mini-fab – Ericsson

One option for the production of low-volume products is to separate them completely from the high-volume production fabs. However, a drawback of this approach is that a minimum toolset is required to manufacture the wafers. That is, at least one of each type of tool (stepper, implant, polish, etc.) is required. This is only a problem if there are not enough low-volume products to use a significant portion of the fab capacity. Once established, the low-volume fab can focus primarily on reducing setup times due to frequent change-overs, rather than yield or tool utilization.

Ericsson, the telecom and cell phone company based in Sweden, opened what it calls a "minifab" in 1994. This fab had an output of only 10,000 wafers per year compared to approximately 300,000 wafers per year at an Intel plant. The Ericsson mini-fab was designed to enable fast design cycle times for custom ASICs (Application Specific Integrated Circuits). While Ericsson did not have the competency or desire to manage the mass production of high-volume chips, the mini-fab enabled Ericsson to develop prototypes, and produce small production runs without revealing its circuit designs to an outside contractor [10].

Ericsson considered the mini-fab to be a strategic asset. Prior to the construction of the mini-fab, Ericsson was dependent on external foundries for both manufacturing knowledge and manufacturing capacity. The mini-fab, which was designed through a partnership with Texas Instruments, enabled Ericsson to build knowledge in the semiconductor processing area. The fab may have made Ericsson more competitive in the marketplace by improving its design capability and manufacturing flexibility, but was not implemented to reduce manufacturing costs, a key goal of this thesis. Intel already has an abundance of opportunities to learn about CMOS wafer processing, thus building a separate fab for new low-volume products does not appear to be an economical option.

## 2.2.4 Work cell layout

The use of a cellular arrangement of tools for semiconductor manufacturing has been suggested in the manufacturing system design literature as an alternative to the traditional job shop layout of wafer fabs [11]. This cellular tool arrangement has proven to be successful in automotive and aerospace machining applications. The manufacturing cell brings the various tools needed to manufacture a wafer into close proximity in the order of the process steps. The primary benefits of a cellular manufacturing arrangement are that transport times would be nearly eliminated, and single wafer processing could be enabled. Single wafer processing would have the effects of reducing the quantity of WIP<sup>4</sup> in the system and the total throughput time. Such a cellular fab would employ small tools that have only small capacity. However, it is not clear how the traditional re-entrant flow, in which a wafer visits a particular tool multiple times during the semiconductor fabrication process, would be accommodated. Presumably, an entire tool set, including low-capacity and highly accurate photolithography steppers, would be purchased for every layer in a process. The cellular arrangement of the semiconductor manufacturing tools is not compatible with Intel's high-volume fab designs, so it was not considered further in this thesis.

## 2.3 Alternatives for low-volume IC manufacturing

Intel's plans to produce low-volume products hinge on the desire to use standard Intel process technologies (logic CMOS) with minor modifications to those processes. This desire is created by two factors. First, the capacity required to produce the low-volume products is small compared to Intel's processor and flash memory products. Thus, there is a general consensus that a new fab is not needed to accommodate the low-volume products. Rather, the extra capacity required can be "built in" to the requirements for new process technologies. Second, the development of a process technology is a time consuming and expensive endeavor that is specific to the tools used for production. Redeveloping a process for low-volume tools would require a significant investment that has yet to be justified.

<sup>&</sup>lt;sup>4</sup> Work in Process

Based on the initial desire to produce Intel's low-volume products in Intel's high-volume manufacturing fabs, the following options for low-volume manufacturing were generated through brainstorming and discussions with industrial engineers. It should be noted that many of the strategies could be used simultaneously, but for simplicity they will be discussed separately.

## 2.3.1 Multi-product wafers

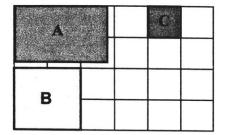

Multi-product wafers, as the name indicates, are wafers that have more that one product fabricated on them. The foundries introduced the use of multi-product wafers with their shuttle programs for prototypes, such as the CyberShuttle program at TSMC. Multi-product wafers have some limitations, but also some very significant cost benefits.

The benefits of using a multi-product wafer for product manufacturing include sharing mask set costs, sharing tool setup times, and potentially sharing wafer costs. The mask sets are continually increasing in cost as the process technologies require finer and finer line widths. By placing several products on the mask set, the cost could be shared by those products. In the fab, the multi-product wafer would only drive a single NPI effort. Thus the setup time per product could be driven down substantially. Finally, it may be possible to share wafer costs between products that have less than a single lot (a lot is a box of 25 wafers) of demand.

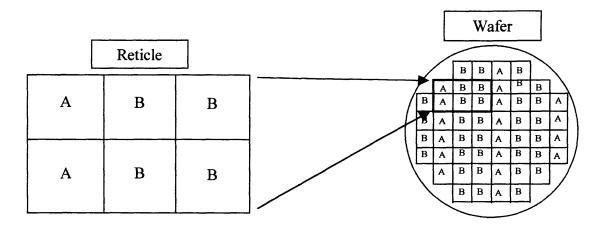

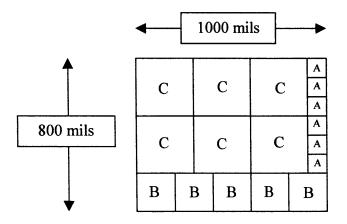

Multi-product wafers also come with several challenges. Some of the challenges include dealing with product mix that is fixed once the masks are created, potentially lower yields, ensuring pattern density uniformity for the polish step, and increased coordination between designers. The fixed product mix is caused by the fact that once a mask set is created, it cannot be changed. For example, consider a mask set that creates patterns for two of hypothetical product "A" and four of product "B" as illustrated in Figure 2.2. The mask set will only produce the products in the 2:4 ratio regardless of what the market desires. If for some unforeseen reason, the "A" products are a hit, but the "B" products falter, up to two thirds of the silicon may be wasted producing the "A" products.

Figure 2.2: Sample MPW reticle (mask) and wafer layouts

There is also some concern that the multi-product wafers will cause an unacceptable decline in die yield. Because the fabrication processes will not be optimized on a product level, as is currently done with dedicated wafers, the yield may drop to levels that outweigh the savings. The primary cause of the yield concerns is the CMP step of the wafer fabrication process. Because various products have different features, the resulting designs have different pattern densities. The issue with having various pattern densities on a wafer is that the polish step is not as effective and cannot be controlled as well. The result of polishing a wafer with die of different densities is like sanding a knotty board. The board (wafer) is dished out in the soft areas, and bulged where there are knots (highly dense components). The density problem can be somewhat alleviated by introducing dummy structures into the designs of less dense chips. The dummy structures ideally have no impact on the circuit performance while raising the pattern density to a common level. However, depending on the design, the dummy structures may consume valuable silicon area.

The physical die size of the products slated for MPW manufacturing has impact on the design of MPWs. The dies must be able to fit within the available area of the reticle field. Thus, the size of the reticle field places a constraint on the number of different products that can be manufactured on an MPW. We will see the effects of this constraint in Chapters 3 and 4.

The sharing of wafers with MPWs would require the use of packaging equipment that can cut, pick, and sort different sized chips from a single wafer. Intel's wafer saws cannot currently cut different sized products from a single wafer. This limitation would cause a significant amount of wasted silicon, since only a single product would be cut from each MPW. Laser saws that have the capability to cut out different-sized dies are currently available on the market, but have not been integrated into Intel's packaging process. The decision of whether to purchase and integrate a new packaging technology will depend on the relative value of the potentially wasted silicon and the laser saw technology. The financial implications of this will be explored further in Chapter 3.

Finally, MPWs require coordination and synchronization of product launches. The products to be produced on an MPW must go to market at nearly the same time to prevent one product from delaying the launch of another. This may create significant challenges since one design group may not have the resources to launch multiple products simultaneously, and separate design groups would have to coordinate their product launches. However, if a "critical mass" of new product launches is obtained, the coordination become much easier. If there is a constant stream of new products to be launched, there will be enough products that can be relatively easily grouped together without attempting to change the product launch schedule.

## 2.3.2 Multi-product lots

The concept of multi-product lots (MPLs) was created to find a way to reduce the setup times inherent in running many low-volume products in a high-volume fab. The theory is that mask sets are not shared but the process setups and NPIs are shared. Essentially the process is made generic for a group of products. Operationally, this strategy would be identical to the multi-product wafer strategy except at the photolithography stage. At the lithography bay in the fab, a standard 25 wafer lot would begin its processing of the first product until, say, eight wafers were completed. At that point, the reticle (or mask) would be changed and the exposure of the second product would continue.

Figure 2.3: A multi-product lot with three products

The primary cost increase is lower utilization of the photolithography tools due to the reticle change time. There would also be potential CMP and yield problems, because the tool settings would not be optimized for each product. This strategy would also require wafer level tracking (as opposed to the current lot level tracking) to know which wafers in a lot belong to which group. The multi-product lot idea would only be useful in the case of products that have a volume requirement that is less than a full lot. If a full lot or more is required, it simply does not make sense to add a reticle change to the photolithography process.

## 2.3.3 Reduced NPI effort

When a new product is introduced, the engineers go through a standard procedure of tailoring the manufacturing process parameters to that product. The procedure (known as an NPI) enables the fab to run the product at the highest yield possible. An NPI involves running up to three wafers through a process step, then sending them to metrology for analysis. The remainder of the lot waits for the results to return and the tools to be adjusted before further processing. The waiting and setup times can amount to several hours of lost tool productivity and increased cycle time at each process step. Presumably, the cost savings from higher yield outweighs the overhead of performing the NPI. However, in the context of low-volume products with fewer wafers being processed there may not be enough savings due to yield to justify a full NPI yield improvement effort. This strategy would have to be developed through engineering and experimentation to determine the yield improvement per hour of tool and engineering time spent. Then the appropriate yield target would be estimated by balancing the NPI cost with the cost of wasted silicon, based on the forecast demand for the product.

## 2.3.4 Small lot size

One option for processing low-volume products that does not dramatically change the way a fab operates is to run smaller wafer lots. Typically, products are run in lots of 25 wafers. Some low-volume products are not expected to require a full wafer lot to satisfy the entire lifetime demand! Thus, running a whole lot wastes wafers. Additionally, running smaller lots can have the advantage of lower WIP and faster cycle times. The main drawback of running smaller lots is that the tool setup times are spread over fewer wafers so the tool utilization is much worse than that observed with high-volume manufacturing.

\_\_\_\_\_

## 2.4 Conclusions

In this chapter, we have explored various options for manufacturing low-volume products. Most of the current methods of manufacturing low-volume products were eliminated due to incompatibility with Intel's high-volume fabs. The remaining strategies, multi-product wafers, multi-product lots, reduced NPI effort, and small lot sizes, will be compared in more detail in the following chapter.

# Chapter 3: Financial analysis of potential low-volume manufacturing strategies

In Chapter 2, several of the options for manufacturing low-volume products were discussed. However, the discussion alone does not help select an appropriate strategy. As a reminder, the goals of choosing the best strategy are to manufacture low-volume products at low cost, with fast throughput times, and high flexibility. In this chapter, the costs of the potential low-volume manufacturing strategies will be compared using a financial model, referred to as the Low-Volume Manufacturing Cost Model (LVM Cost Model). First, the development of the model will be discussed in general. Next, the tailoring of the model to the specific manufacturing strategies will be shown. Finally, the results of the model are displayed and compared.

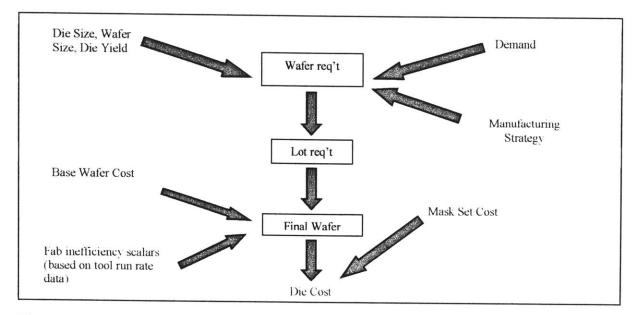

## 3.1 Development of a financial model

The model developed here was intended to capture the total cost of producing a common product with different manufacturing strategies. The LVM Cost Model is organized as shown in Figure 3.1. First, the quantity of wafers required is calculated from the forecast demand and the combination of expected factory parameters (e.g. die size, wafer size, and die yield) and the specific manufacturing strategy to be used (e.g. Standard, Multi-product Wafer, Multi-product Lot, etc.). Once determined, the wafer quantity is converted to the number of required lots.

Next the wafer cost is determined. The final wafer cost can vary based on the number of lots run together in a chain, or cascade. Also, the first two lots or a product's lifecycle are burdened with the cost of the NPI.

The final wafer cost is converted to "cost per die" by dividing by the number of dies per wafer. The mask set cost is also divided among the total lifecycle die produced with that mask. The sum of these two costs gives us a final Die Cost that can be used to compare the different manufacturing strategies for products with various die sizes and demand forecasts. Sections 3.1.1 through 3.1.3 describe the equations used to model the die cost. These sections are organized to follow the model roadmap depicted in Figure 3.1. Section 3.1.1 describes the calculation of the wafer requirement parameters used by all of the manufacturing strategies, including the calculation of "lot requirement". Section 3.1.2 describes the calculations specific to the individual manufacturing strategies considered in the model. Finally, Section 3.1.3 describes the equations used to calculate the final wafer cost and die cost.

Figure 3.1: Roadmap of the Low-Volume Manufacturing Cost Model

## 3.1.1 Calculation of the wafer quantity requirement

The number of wafers required to satisfy demand is a function of product die size and factory parameters such as yield and wafer size. For simplicity, the demand forecasts for the products to be modeled were lumped into a single time period. This simplification eliminated the need to calculate inventory held between periods.

### **Die size**

Die size is the size of a single chip. Typical die sizes vary from 100 mils x 100 mils to about 500 mils x 500 mils. The units of measurement of the dies are "mils", or thousandths of an inch. The die size determines how many die will fit on a wafer. Clearly, a product with large dies will require more wafers than a product with small dies to satisfy a particular unit demand. For this

initial, Low-Volume Manufacturing Cost model, the dies were assumed to be square. This constraint will be relaxed in a more refined model presented in Chapter 4.

## Gross die per wafer

The size of the wafer has an obvious impact on the number of die that can be produced on the wafer. The number of whole die printed on a wafer, called Gross Die per Wafer is calculated by,

Eq. 3.1 GrossD/W =

$$\frac{\pi \times (WaferDiameter/2)^2}{A}$$

- EdgeEffectCorrection

where, *WaferDiameter* is the diameter of the raw silicon wafer, and *A* is the die area. The examples presented in this thesis assume a 300mm wafer diameter. The value, *EdgeEffectCorrection*, is empirically obtained based on die size and wafer size that accounts for the loss of partially fabricated dies that overlap the edge of the wafer because the dies are square in shape and the wafers are round in shape. The edge effect is most significant for smaller wafers and large die.

### Line yield

Line yield, or wafer yield, is the ratio of good wafers after completing all of the process steps to the total wafers started. A small percentage of wafers are broken during handling or are processed incorrectly and must be scrapped. The line yield is typically quite high in modern factories, so it is assumed to be 100% in the LVM Cost Model.

#### **Die yield**

Die yield is the ratio of good dies to total dies fabricated on a wafer. Defects caused by particles or scratches on the wafer surface cause some dies to be non-functional upon completion of the fabrication process. Since the defects on a wafer are assumed to be randomly distributed across a wafer, products with large die are more likely to encounter a killer defect. Thus, large dies suffer poorer die yields than small dies.

The model uses a proprietary die yield calculation, so a similar calculation derived from the famous Murphy yield model [12] is presented here. The die yield can be characterized by the

following equation in which the defect density is approximated by the gamma distribution function:

\_\_\_\_\_

Eq. 3.2

$$Y_{die} = \frac{Y_0}{(1 + D_0 A / \alpha)^{\alpha}}$$

where,  $Y_0$  is the linear yield function constant which reflects that portions of the wafer area result in zero yield despite the absence of point defects.  $D_0$  is the mean defect density, which represents the number of killer defects per unit area. The clustering parameter,  $\alpha$ , accounts for the tendency of defects to cluster on the wafer. The parameters  $Y_0$ ,  $D_0$  and  $\alpha$ , must be determined experimentally or empirically, and they will depend on the wafer size, the process technology being used, and the cleanliness of the fab.

Table 3.2 demonstrates the effect of die size and defect density. In this example,  $Y_0$  and  $\alpha$  are held constant at values of 0.90 and 15, respectively. The defect density was varied for three different die sizes. It is seen that small die generally have a higher die yield than large die and are much less affected by increases in defect density.

Table 3.2: Sample Calculation of die yield with varying die size and defect density

|                   | -                           | Y <sub>die</sub>     |         |                      |

|-------------------|-----------------------------|----------------------|---------|----------------------|

| Die Dimensions    | Die Area (cm <sup>2</sup> ) | D <sub>0</sub> =0.10 | D₀=0.25 | D <sub>0</sub> =0.40 |

| 100 mil x 100 mil | 0.06                        | 89%                  | 89%     | 88%                  |

| 300 mil x 300 mil | 0.58                        | 85%                  | 78%     | 71%                  |

| 500 mil x 500 mil | 1.61                        | 77%                  | 60%     | 48%                  |

Note:  $Y_0 = 0.90$  and  $\alpha = 15$  in this example.

## Die per wafer

The die yield and gross die per wafer are used to calculate the number of good die per wafer. This is given by:

Eq. 3.3  $D/W = GrossD/W \times Y_{die}$

Now that we have the number of dies that a single wafer yields, we are nearly ready to calculate the total number of wafers required to satisfy a given quantity of demand. However, the next section will show that the number of wafers required may also depend on the strategy used to manufacture those wafers.

## 3.1.2 Tailoring the wafer requirement to each LVM strategy

The various manufacturing strategies have an effect on the number of wafers required. The different methods of combining products into common lots or on multi-product wafers cause unique changes in the calculations. The calculations that are unique to the individual manufacturing strategies are described in this section.

#### Standard

The standard manufacturing strategy assumes that there is only one product produced per lot and there are 25 wafers in each lot. This is the standard method of running high-volume products at Intel and is used as a baseline for comparison with the low-volume manufacturing strategies. The whole number of wafers required to satisfy the total lifecycle demand of the product is calculated by:

Eq. 3.4 WaferRequirement =

$$\frac{Demand}{D/W}$$

It follows that the number of lots required to satisfy demand is represented by:

Eq. 3.5

$$LotRequirement = \frac{WaferRequirement}{Wafers/Lot}$$

where, *Wafers/Lot* is the number of wafers in a box, typically 25. Both the wafer requirement and lot requirement values were forced to be integers, so the values are rounded up to the next whole number.

## Small lot size

The first low-volume manufacturing strategy considered was small lot sizes. The lot size is the number of wafers that move together through the fab in a single box. The option of using smaller lot sizes can potentially reduce waste by producing fewer wafers in the case of extremely low demand where fewer than one lot of wafers will satisfy a product's lifetime demand. Small lot sizes were modeled by simply reducing the constant *Wafers/Lot* in Equation 3.5.

. ... . ...

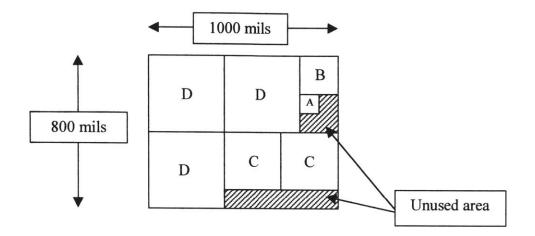

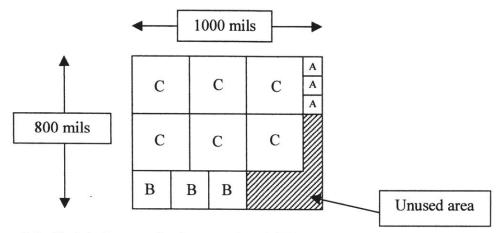

## **Multi-product wafers**

A more complicated low-volume manufacturing strategy to model is the multi-product wafer. For this initial model, two simplifying assumptions were made. First, the model assumes all of the products of an MPW have the same die size. Second, the model assumes that the products have the same total demand. These assumptions, while not very realistic, enabled the model to quickly assess the potential of using MPW as an LVM strategy. A more detailed model, described in Chapter 4 will eliminate these assumptions.

Multi-product wafers were considered in two types. The first type assumes that only one product is harvested from each wafer. For example, in the case of a four-product MPW only one of the products is assembled into packages and tested while the other three are simply discarded. This may occur due to difficulties in dicing wafers with nonstandard scribe lines or difficulties in logistics. There is a clear tradeoff in this model since much of the silicon is wasted. The more products that are fabricated on an MPW, the more silicon is wasted, but the mask set cost and NPI and setup cost are spread over more products as well. Thus, the number of products placed on the MPW must be balanced with the relative cost between wafers and mask sets. The number of wafers required with the "MPW" strategy is given by:

Eq. 3.6 WaferRequirement<sub>MPW</sub> =

$$\frac{Demand}{D/W_{MPW}} \times (\#products/wafer)^2$$

where  $D/W_{MPW}$  is the number of good die per wafer for a MPW and #*products/wafer* is the number of different products fabricated on an MPW. *Demand* is the quantity of dies required for each individual product.

The term, *#products/wafer*, appears squared in Equation 3.6 because:

- 1. Each additional product reduces the number of dies per product on each wafer

- 2. Only one product is packaged from each wafer

The second type of MPW assumes that all products on the MPW are packaged and tested. This eliminates the problem of wasting silicon when many products are placed on an MPW. Because this is considered a special case of the MPW it was designated the "MPW-AT" strategy. As discussed in Section 2.3.1, this MPW-AT strategy requires more advanced wafer sawing techniques than are currently used at Intel and, if implemented, would require additional tool purchases and process development.

The number of wafers required to satisfy demand when the MPW-AT strategy is used and all products are packaged for each wafer is given by:

Eq. 3.7

$$WaferRequirement_{MPW-AT} = \frac{Demand}{D/W_{MPW}} \times (\#products/wafer)$$

where, MPW-AT denotes that the MPW strategy is used with all products *Assembled and Tested*, or packaged. Here we see that *#products/wafer* is not squared, thus fewer wafers are needed if all products can be packaged from each wafer as is shown below.

Both of the MPW strategies were considered with 2, 4 and 8 products per wafer. Additionally, the MPWs were modeled with a worse die yield, because the manufacturing processes cannot be optimized for each specific product on an MPW. This was accomplished by incrementing the defect density when calculating wafer requirements for the MPW and MPW-AT strategies.

#### **Multi-product lots**

Multi-product lots (MPLs) were modeled in a similar method to the MPWs. To review, an MPL is a lot of wafers with different products fabricated on different wafers of that lot. The process

technology is the same for each product so setup times are shared. However, unique mask sets are required for each product so mask set cost cannot be shared.

Again, a simplifying assumption was made that the products on an MPL are the same die size and have the same unit demand. With MPLs there is no problem separating the different products because each product is on its own wafer. However, the MPLs may have a lower yield than wafers run with standard production techniques since the setup procedures are shared between the various products. So, the manufacturing processes cannot be optimized for a specific product on an MPL. The number of wafers required to satisfy demand when the MPL strategy is given by:

Eq. 3.8 WaferRequirement<sub>MPL</sub> =

$$\frac{Demand}{D/W_{MPL}} \times (\# products/lot)$$

where *#products/lot* is the number of different products fabricated in an MPL. Again, *Demand* is the quantity of dies required for each individual product.

### 3.1.3 Wafer cost components

As discussed in Chapter 2, many tools become less efficient when small batches are run due to setup times and test requirements. The financial model will try to capture the sensitivity of capital cost to the number of lots required for each product.

#### **Base wafer cost**

The wafer costs used in the model were based on what Intel Finance calls the "Yielded Wafer Cost", which includes labor, capital, overhead, and raw materials. This measure of cost is calculated on a routine basis to estimate the wafer costs of each process technology over time. The estimates are based on the total expected expenses divided by the total expected wafers. Thus, the wafers produced during the ramp phase of production are extremely expensive because there are relatively few wafers being produced while an entire fab is depreciated. Later in the process lifecycle, the wafer cost declines as the depreciation is spread across many more wafers. A processed silicon wafer can cost anywhere from several hundred dollars to tens of thousands

37

of dollars depending on the process technology and position on the lifecycle. Typical wafer costs are broken down as shown in Table 3.1.

Table 3.1: Typical Wafer Cost Breakdown, 2001 [13]

| 48% |

|-----|

| 32% |

| 10% |

| 10% |

|     |

The largest expense, depreciation, includes the expenses of both the fabs and the tools. Because depreciation constitutes such a large portion of wafer cost, it is easy to see why there is an emphasis on tool utilization. The second highest expense, raw materials, is the cost of the raw silicon wafers, chemicals, and gasses required to manufacture ICs. Direct labor and overhead account for the remainder of the base wafer cost.

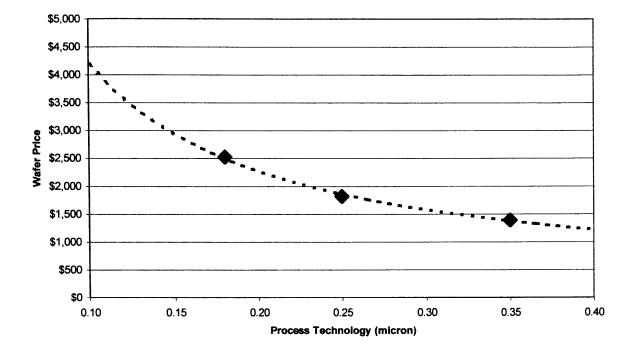

To give a representative example of base wafer costs, the third quarter 2001 average prices of wafers produced by foundries are shown below in Figure 3.2. The higher prices for process technologies with smaller feature sizes reflect the higher cost of new processing tools.

Figure 3.2: Q3 2001 average foundry wafer prices by CMOS process technology [14].

#### Fab tool utilization

In order to maximize the fab tool utilization, fab managers attempt to reduce the number of changeovers by running several consecutive lots of each product. These consecutive lots are known as a "cascade". The typical cascade size for high-volume products is four lots, or 100 wafers. However, some low-volume products may require only a single lot of wafers (or less) to meet the forecast lifetime demand. These low-volume products cause a proportionally higher amount of tool down time. Because the tool depreciation is the largest portion of the wafer cost, lost tool run time has the potential to dramatically increase wafer cost. This potential increase in wafer cost is not currently accounted for at a product level by Intel's finance department. The current accounting method spreads the cost of the extra capacity requirement across all of the wafers processed per time period. However, some Intel employees fear the addition of many low-volume products could cause enough of a productivity drop that the high-volume product managers would want a wafer cost based on productivity measured at the product level.

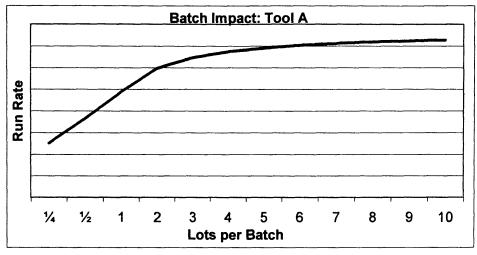

To model the fab efficiency loss caused by low-volume products, real data for representative tools was collected with the help of various industrial engineers. A typical tool efficiency curve is represented in Figure 3.4. The efficiency improves rapidly as the cascade size increases, but eventually diminishing returns slow the potential improvement.

Figure 3.4: Sample fab tool efficiency curve.

To account for this in the model, tool efficiency curves were collected for those tools that suffer the most impact from low-volume manufacturing as described in Chapter 2, then converted into "tool inefficiency" factors as follows:

Eq. 3.9

$$e_{tnc} = \frac{rr_{nc}}{rr_{n4}}$$

where,  $rr_{nc}$  is the run rate (in wafers per hour) for tool n with cascade size c. A baseline cascade size of four lots was used in this equation, and the inefficiency factors were calculated for 1/4, 1/2, 1, 2, 3, and 4 lot cascades. Thus, a typical product with cascade size of four lots will have an inefficiency factor of "1". A low-volume product with fewer lots in a cascade will an inefficiency factor greater than "1".

These tool inefficiency factors were used in conjunction with the weighted cost of each tool type to create a composite fab inefficiency factor for each cascade size. The weighted cost of each tool was determined by:

Eq. 3.10

$$w_{tn} = \frac{cost_n}{\sum_{i=1}^n cost_i}$$

Where,  $cost_n$  is the cost of tool number n.

It follows that the overall fab inefficiency factor for cascade size c, is calculated as follows:

Eq. 3.11

$$ef_c = w_{t1} \times e_{t1c} + w_{t2} \times e_{t2c} + \dots + w_{tn} \times e_{tnc}$$

To demonstrate the calculation of the tool inefficiency factors, suppose we want to find the fab inefficiency factor for a cascade size of two lots. First we must collect the run rates for the tools at the cascade sizes of both the proposed two lots and the standard four lots. In this example, we will consider four hypothetical tool types designated by letters A, B, C, and D.

For Tool A, suppose the run rates for two-lot and four-lot cascades are  $rr_{A2}=20$  wafers/hour and  $rr_{A4}=30$  wafers/hour, respectively. Thus, the tool inefficiency factor,  $e_{tA2}=30/20=1.5$  because tool A requires 1.5 times the processing time per wafer when processing two-lot batches compared to the baseline of four-lot batches of wafers. If cost of tool A capacity is \$5 million and the entire toolset cost is \$10 million, then the weighted tool cost,  $w_{tA}=$ \$5million/\$10 million = 0.5. Using these calculations for the rest of the tools we can construct Table 3.2.

| Tool | rr <sub>n2</sub> | rr <sub>n4</sub> | Tool                       | Tool Cost | Tool Cost |

|------|------------------|------------------|----------------------------|-----------|-----------|

|      | (wafers/hour)    | (wafers/hour)    | (wafers/hour) Inefficiency |           | Weighting |

|      |                  |                  | Factor                     |           |           |

| A    | 20               | 30               | 1.5                        | 5.0       | 0.5       |

| В    | 30               | 33               | 1.1                        | 2.0       | 0.2       |

| C    | 15               | 30               | 2.0                        | 1.5       | 0.15      |

| D    | 10               | 12               | 1.2                        | 1.5       | 0.15      |

Table 3.2 Sample tool cost weighting calculation

Using Equation 3.11 we find that the fab inefficiency factor for a cascade size of two lots is then:

$$ef_2 = (1.5 \times 0.5) + (1.1 \times 0.2) + (2.0 \times 0.15) + (1.2 \times 0.15) = 1.45$$

The fab inefficiency factor can then be used to charge low-volume products for the extra fab and tool time they consume. Based on conversations with industrial engineers, an estimate was made that direct labor costs would only increase by half the amount depreciation increases. Thus, the depreciation and direct labor components of base wafer cost are multiplied by the fab inefficiency factors to obtain a final wafer cost as follows:

Eq. 3.12

$$wc_f = ef_c \times wc_d + wc_rm + \{[(ef_c - 1)/2] + 1\} \times wc_{dl} + wc_o$$

where,  $e_{f_c}$  is the fab inefficiency factor for cascade size c, wc<sub>d</sub> is depreciation portion of base wafer cost,  $wc_{rm}$  is the raw material portion of base wafer cost,  $wc_{dl}$  is the direct labor portion of base wafer cost,  $wc_o$  is the overhead portion of base wafer cost.

An illustration of the final wafer cost calculation using a representative wafer cost of \$3000 (for a four-lot cascade) is shown here. First, the wafer cost must be broken into its components using the values from Table 3.1. The resulting wafer cost components are as follows:

$wc_{d} = \$3000 \times 0.48 = \$1440$   $wc_{rm} = \$3000 \times 0.32 = \$960$   $wc_{dl} = \$3000 \times 0.10 = \$300$  $wc_{o} = \$3000 \times 0.10 = \$300$