## Micro-cleaved Ridge Lasers for Optoelectronic Integration on Silicon

by

Joseph J. Rumpler II

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy in Electrical Engineering

### at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2008

© Massachusetts Institute of Technology 2008. All rights reserved.

.

· · · · ·

## Micro-cleaved Ridge Lasers for Optoelectronic Integration on Silicon

by

Joseph J. Rumpler II

Submitted to the Department of Electrical Engineering and Computer Science on February 29, 2008, in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

#### Abstract

This thesis addresses one of the last hurdles to optoelectronic integration on silicon, namely the incorporation of room-temperature, electrically-pumped edge-emitting laser diodes. To this end, thin ( $^{6} \mu$ m) InP-based multiple quantum well (MQW) ridge laser platelets emitting at a wavelength of 1550 nm have been manufactured and integrated by metal-to-metal bonding onto silicon substrates.

These laser platelets can be thought of as freestanding optoelectronic building blocks that can be integrated as desired on diverse substrates. These blocks are fully processed lasers, with both top side and bottom side electrical contacts. The thinness of these optoelectronic building blocks and the precision with which their dimensions are defined are conducive to assembling them in dielectric recesses on a substrate, such as silicon, as part of an end-fire coupled, coaxial alignment optoelectronic integration strategy. They are assembled by a micro-scale pick and place technique that allows the blocks to be picked up individually and placed as desired on any substrate. Integration is accomplished by metal-to-metal solder bonding.

To enable the manufacture of these laser blocks, a novel micro-cleaving process technology has been developed. This novel micro-cleaving process is used to simultaneously obtain both smooth end laser facets and precisely defined laser cavity lengths. As a proof of concept, this process has been shown to achieve nominal cavity lengths of  $300 \ \mu m +/- 1.25 \ \mu m$ . It is believed that this micro-cleaving process could be used in the future to make thin platelet lasers having much shorter cavity lengths and with better than 1.25  $\mu m$  length precision.

For the 300  $\mu$ m long, 6  $\mu$ m thin, micro-cleaved ridge platelet lasers integrated onto silicon substrates, continuous-wave lasing at temperatures as high as 55 °C and pulsed lasing at temperatures to at least 80 °C have been achieved. These lasers have output powers as high as 26.8 mW (at T = 10.3 °C), differential efficiencies as high as 81% (at T = 10.3 °C), and threshold currents as low as 18 mA (at T = 10.3 °C). The characteristic temperatures,  $T_0$  and  $T_1$ , of the lasers on silicon were measured to be 43 K and 85 K, respectively.

To put the performance of these integrated micro-cleaved ridge lasers on silicon

in perspective, conventionally cleaved multiple quantum well (MQW) ridge lasers on their native InP substrate were also fabricated and tested. The thin micro-cleaved ridge platelet lasers integrated onto silicon outperformed the conventional lasers on InP in terms of thermal characteristics (maximum operating temperature,  $T_0$ , and  $T_1$ ), output power, and differential efficiency.

The structure of this thesis is as follows. First, the motivation for this work and the historical evolution of the optoelectronics field are briefly described. Next, the various optoelectronic integration techniques that have been pursued over the years and their limits are presented. The novel fabrication processes developed to manufacture these platelet lasers is then described in detail. Specifics on the characterization methods and measurement results of both the micro-cleaved ridge lasers on silicon and the conventionally cleaved ridge lasers on native InP substrates are presented. A technique, Magnetically Assisted Statistical Assembly, that could be potentially used to scale the integration technology to ultra-high densities of optoelectronic components is then theoretically described. Finally, the thesis concludes with a comparison with other state of the art results in the literature and proposes further directions for this research effort.

Thesis Supervisor: Clifton G. Fonstad, Jr. Title: Professor

### Acknowledgments

As I complete this chapter of my life, there are a great number of people I would like to thank. First, I would like to thank Professor Fonstad whose interesting projects on the topic of Optoelectronic Integration lured me here about seven years ago as a new graduate student.

I want to thank everyone in Professor Fonstad's research group. Not only have I enjoyed working with you all, I have enjoyed hanging out with you. To James Perkins and Ed Barkley, thanks for the great times. From our nearly daily social meetings in the office to our long hours spent in the lab to our sometimes even longer hours spent in the gym, I have had a truly awesome time spending time with you guys. There are a ridiculous number of inside jokes I will carry with me the rest of my life. Thanks to Diana Cheng for being so patient and understanding during this last term here when I was really swamped with trying to wrap up the thesis and passing off a lot of my experience with MASA to her. Thanks to Shaya Famenini, Mindy Teo, and Vivian Lei for always being friendly faces around Building 13. I want to thank Professor Sheila Prasad for making building 13 an enjoyable place to work. I will miss stopping by your office and catching up. I want to thank Henry Choy for showing me the ropes my first few years here.

I want to thank the members of my thesis committee, Professor Rajeev Ram and Professor Tayo Akinwande. I really appreciated the comments and insight you provided on my work.

I want to thank the folks out at Lincoln Lab, especially Jason Plant, Reuel Swint, and Paul Juodawlkis. Jason's willingness to help me with the ICP semiconductor etching was awesome. This was a huge enabler for the project.

I want to thank the folks over at MTL, namely Kurt Broderick, and Dennis Ward, who seemed to always go way out of their way to get the equipment back up and running when I really needed it. Thank you so much. I want to thank Bob Bicchieri, Eric Lim, and Dave Terry for their help over the years.

I want to thank the CMSE, especially Tim McClure, who always was there to

answer my questions on the P10 and Carl Zeiss Axioskop tools that I made use of so much in my work.

To all the people I've borrowed equipment from over the years, such as Professor Kolodziejski and Dr. Gale Petrich, who let me use part of their laser testing setup. I want to thank Professor Ram again for letting me borrow equipment, such as the all-important TEC controller, that made all of the temperature analysis of my laser diodes possible.

I want to thank the folks associated with the 6.152J course. Over the years, I became a veteran TA of this course. Along the way I met some great people, namely Professor Tayo Akinwande, Professor Marty Schmidt, Professor Caroline Ross, Dr. Bob O'Handley, Li-Wen Wang, and Scott Poesse. I have had a blast and really thank you for the opportunity you gave me.

There are lots of friends around campus who have made my stay at MIT truly outstanding. As I am running against the clock to finish the thesis, I am reluctant to name everyone for fear of leaving off someone who has played an important role. One person I really have to mention by name is David Berns whose friendship gained during classes and working on "The Fund" is something I will remember the rest of my life.

Last but certainly not least I want to thank my family (my parents, Joe and JoAnn, my sisters, Jan and Jill and their families, and my brothers, Jim and Jason, and Kaiser) for all of their love and support. I also want to thank my Grandma Loretta and my Aunts and Uncles for their support. I want to thank my girlfriend Vivian Lei, who has been fundamental in me getting all this done. I also want to thank Cindy Ho, Vivian's Mom, for her well wishes and support. Getting a Ph.D., as I have learned, is a long journey with many ups and many downs. It helps so much when you have such great people in your life, making sure you keep the right perspective. Thank you so much for your support. I love you very much.

# Contents

| 1 | Mo  | tivatio | n for Optoelectronic Integration                               | 25 |

|---|-----|---------|----------------------------------------------------------------|----|

|   | 1.1 | Introd  | luction - Examples of Optoelectronic Products and their Impact | 25 |

|   | 1.2 | Histor  | rical Evolution of the Optoelectronic Integration Effort       | 29 |

|   | 1.3 | Mode    | rn Optoelectronic Integration Effort                           | 34 |

|   |     | 1.3.1   | Last Mile of the Optical Network                               | 34 |

|   |     | 1.3.2   | Chip-to-Chip and On-chip Optical Interconnects                 | 37 |

|   | 1.4 | Overv   | riew of Thesis                                                 | 41 |

|   | 1.5 | Lab F   | acilities                                                      | 42 |

| 2 | Арј | proach  | es aimed at Optoelectronic Integration                         | 43 |

|   | 2.1 | Key I   | Deliverables of an Integration Strategy                        | 43 |

|   | 2.2 | Mono    | lithic Integration Strategies                                  | 44 |

|   |     | 2.2.1   | Monolithic Optoelectronic Integration in Silicon               | 45 |

|   |     | 2.2.2   | Monolithic Optoelectronic Integration in Gallium Arsenide and  |    |

|   |     |         | Indium Phosphide                                               | 46 |

|   | 2.3 | Hybri   | d Integration Strategies                                       | 49 |

|   |     | 2.3.1   | Flip-chip Bonding                                              | 50 |

|   |     | 2.3.2   | Direct Epitaxy                                                 | 52 |

|   |     | 2.3.3   | Wafer Bonding                                                  | 53 |

|   |     | 2.3.4   | Fluidic Assembly Techniques                                    | 54 |

|   | 2.4 | Our A   | approach and the Rationale Behind It                           | 58 |

.

| 3 | Edg  | e-Emi   | tting Lasers for Integration with Low Loss Dielectric Wave     | g-  |

|---|------|---------|----------------------------------------------------------------|-----|

|   | uide | es      |                                                                | 61  |

|   | 3.1  | Silicon | n, a Platform for Hybrid Optoelectronic Integration            | 62  |

|   | 3.2  | Introd  | uction to our Proposed Edge-Emitting Laser - Dielectric Waveg- |     |

|   |      | uide S  | ystem                                                          | 66  |

|   |      | 3.2.1   | Competing Approach in the Literature                           | 70  |

|   |      | 3.2.2   | Dielectric Waveguides Basic Structure                          | 72  |

|   |      | 3.2.3   | Edge-Emitting Laser Basic Structure and Operation              | 73  |

|   | 3.3  | Appro   | aches to Create Accurately Dimensioned Lasers With Highly Re-  |     |

|   |      | flectiv | e Optical Facets                                               | 76  |

|   |      | 3.3.1   | Cleaved Facet Lasers                                           | 76  |

|   |      | 3.3.2   | Etched Facet Lasers                                            | 76  |

|   |      | 3.3.3   | Micro-Cleaved Facet Lasers                                     | 77  |

|   | 3.4  | Our N   | lovel Micro-Cleaving Approach                                  | 78  |

| 4 | Edg  | ge-Emi  | tting Laser Process Development                                | 87  |

|   | 4.1  | Starti  | ng Semiconductor Material                                      | 87  |

|   | 4.2  | Conve   | entionally Cleaved Ridge Laser Process Development             | 90  |

|   |      | 4.2.1   | Front-Side Device Processing                                   | 90  |

|   |      | 4.2.2   | Back-Side Device Processing                                    | 101 |

|   | 4.3  | Micro   | -Cleaved Ridge Laser Process Development                       | 106 |

|   |      | 4.3.1   | Front-Side Processing                                          | 107 |

|   |      | 4.3.2   | Back-Side Processing                                           | 115 |

|   | 4.4  | Manip   | oulation and Bonding of Micro-Cleaved Platelets                | 132 |

|   |      | 4.4.1   | Assembling InP-based Ridge Waveguide Platelets in Dielectric   |     |

|   |      |         | Recesses on a Silicon Substrate                                | 133 |

|   |      | 4.4.2   | Assembling InP-based Ridge Laser Platelets on Metallized Sil-  |     |

|   |      |         | icon Substrates for Device Characterization                    | 136 |

| 5 | Mi   | cro-Cle | eaved Ridge Laser Characterization                             | 139 |

|   | 5.1  | Micro   | -Cleave Precision Characterization                             | 140 |

|              | 5.2  | Ridge   | Laser Optical and Electrical Characterization             | 146       |

|--------------|------|---------|-----------------------------------------------------------|-----------|

|              |      | 5.2.1   | Conventionally Cleaved Ridge Laser                        | 147       |

|              |      | 5.2.2   | Micro-Cleaved Ridge Laser                                 | 161       |

|              |      | 5.2.3   | Comparison of the Micro-Cleaved Ridge Lasers              | 169       |

| 6            | Ena  | bling   | Higher Density Integration - Magnetically Assisted Statis | <b>S-</b> |

|              | tica | l Asse  | mbly                                                      | 181       |

|              | 6.1  | Magn    | etically Assisted Statistical Assembly                    | 181       |

|              |      | 6.1.1   | Properties of the Ferromagnetic Films used in MASA        | 183       |

|              |      | 6.1.2   | Theory Underlying the MASA Technique                      | 184       |

|              | 6.2  | Deriva  | ation of Magnetic Field Expressions                       | 188       |

|              |      | 6.2.1   | Hard Magnetic Film with Perpendicular Anisotropy          | 188       |

|              |      | 6.2.2   | Hard Magnetic Film with In-Plane Anisotropy               | 190       |

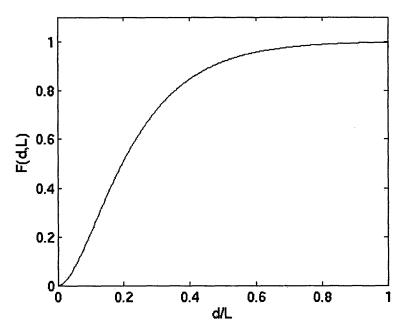

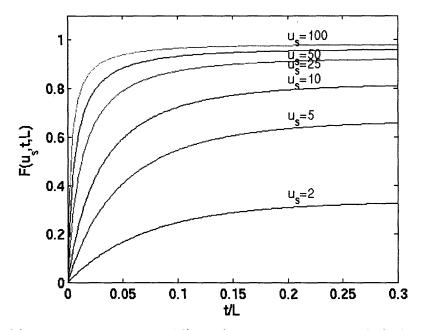

|              | 6.3  | Deriva  | ation of the Magnetic Retention Force Expression          | 191       |

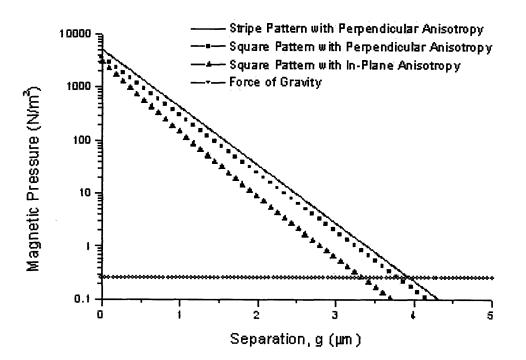

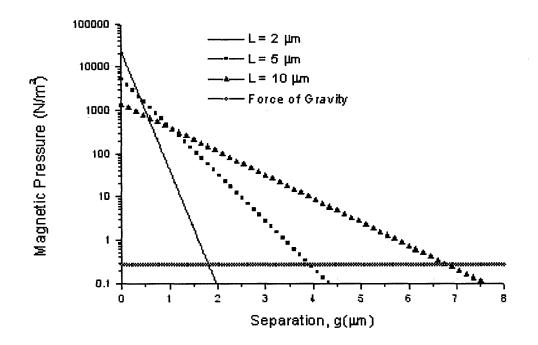

|              |      | 6.3.1   | Magnetic Force Density Dependencies                       | 195       |

|              |      | 6.3.2   | Magnetic Force Verification                               | 198       |

| 7            | Cor  | cludir  | ng Remarks                                                | 199       |

|              | 7.1  | Alterr  | native Approaches to Achieving III-V Lasers on Silicon    | 199       |

|              | 7.2  | Futur   | e Directions                                              | 205       |

| A            | Cor  | ventio  | onally Cleaved Ridge Laser Process Flow                   | 209       |

| В            | Mic  | ro-clea | aved Ridge Laser Process Flow                             | 213       |

| $\mathbf{C}$ | Pro  | cess R  | lecipes                                                   | 219       |

|              | C.1  | Lithog  | graphy Process Recipes                                    | 219       |

|              | C.2  | Etchir  | ng Process Recipes                                        | 221       |

|              |      | C.2.1   | Reactive Ion Etching                                      | 221       |

|              |      | C.2.2   | Sputter Etching                                           | 223       |

|              |      | C.2.3   | Wet Etching                                               | 223       |

|              | C.3  | Depos   | ition Processes                                           | 226       |

|   |     | C.3.1                    | Plasma Enhanced Chemical Vapor Deposition (PECVD) $\ldots$                                            | 226               |

|---|-----|--------------------------|-------------------------------------------------------------------------------------------------------|-------------------|

|   |     | C.3.2                    | Sputter Deposition                                                                                    | 226               |

|   |     | C.3.3                    | Electron-Beam Deposition                                                                              | 228               |

|   |     | C.3.4                    | Electrodeposition                                                                                     | 229               |

|   | C.4 | Photo                    | mask Making Process                                                                                   | 230               |

|   |     |                          |                                                                                                       |                   |

| _ | ~ ~ |                          |                                                                                                       |                   |

| D | Mag | gnetic                   | Retention Force Theoretical Model                                                                     | 231               |

| D |     |                          | <b>Retention Force Theoretical Model</b><br>Magnetic Film with Perpendicularly Oriented Magnetization |                   |

| D |     | Hard                     |                                                                                                       | 231               |

| D |     | Hard D.1.1               | Magnetic Film with Perpendicularly Oriented Magnetization                                             | 231<br>231        |

| D | D.1 | Hard 1<br>D.1.1<br>D.1.2 | Magnetic Film with Perpendicularly Oriented Magnetization<br>Array of Squares Pattern                 | 231<br>231<br>234 |

List of Tables

# List of Figures

.

| 1-1 | a.) A typical pulse oximeter [53] b.) Absorption spectrum of fully         |    |

|-----|----------------------------------------------------------------------------|----|

|     | oxygenated hemoglobin and non-oxygenated hemoglobin[32]                    | 26 |

| 1-2 | Historical transatlantic undersea network capacity [20]                    | 28 |

| 1-3 | Functional schematic of a basic WDM network where four wavelengths         |    |

|     | are multiplexed on a single fiber, travel a long distance and then are     |    |

|     | demultiplexed[28]                                                          | 30 |

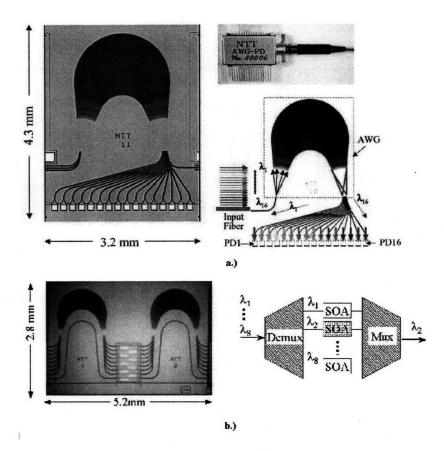

| 1-4 | a.) Schematics and picture of a 16 channel AWG integrated with 16          |    |

|     | photodetectors, b.) Schematic and picture of a monolithically inte-        |    |

|     | grated AWG mux, demux, and semiconductor optical amplifier (SOA)           |    |

|     | array[59]                                                                  | 31 |

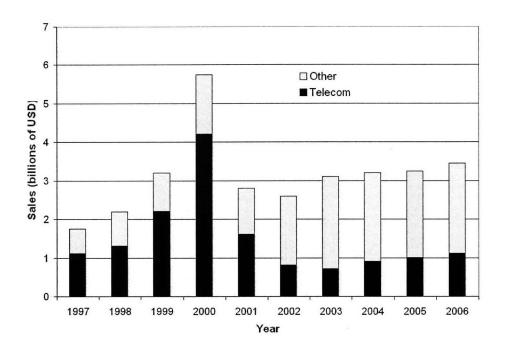

| 1-5 | Historical laser-diode and telecom laser-diode market from 1997 up         |    |

|     | through 2006[79]                                                           | 32 |

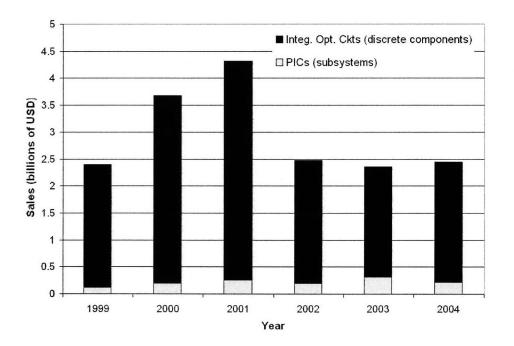

| 1-6 | Historical photonic integrated circuit subsystem and discrete compo-       |    |

|     | nents markets from 1999 up through 2006 [4, 5]. $\ldots$ $\ldots$ $\ldots$ | 32 |

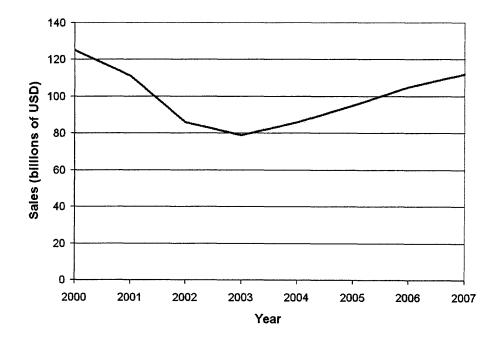

| 1-7 | Historical telecommunication equipment sales [11]                          | 33 |

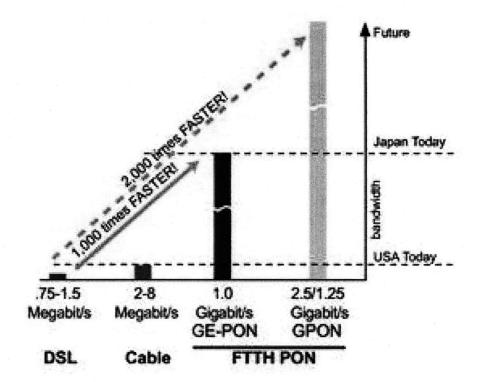

| 1-8 | Bandwidth comparison between DSL, cable modem, and FTTH tech-              |    |

|     | nologies. Note DSL, cable, and FTTH GE-PON (Passive Optical Net-           |    |

|     | work) are in volume deployment; whereas, the FTTH GPON is still in         |    |

|     | development[74]                                                            | 35 |

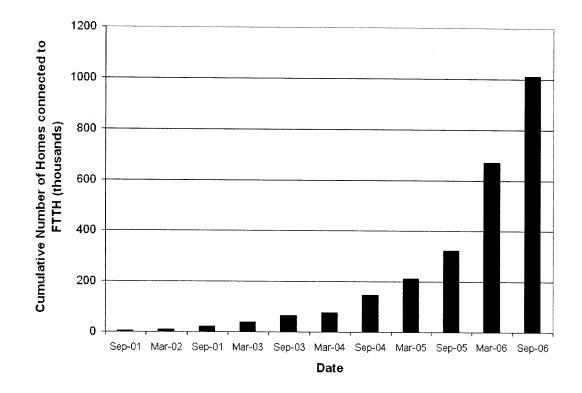

| 1-9 | Cumulative number of homes in North America connected to FTTH              |    |

|     | [57]                                                                       | 36 |

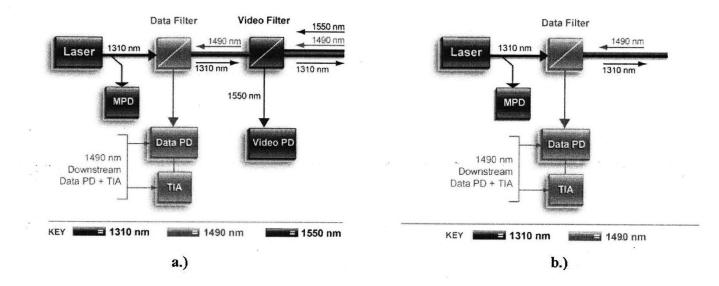

| 1-10 | Schematic of a.) FTTH triplexer, b.) FTTH diplexer. Note, PD                                    |    |

|------|-------------------------------------------------------------------------------------------------|----|

|      | = photodetector, $MPD$ = monitor photodetector, and $TIA$ = tran-                               |    |

|      | simpedance amplifier[91]                                                                        | 37 |

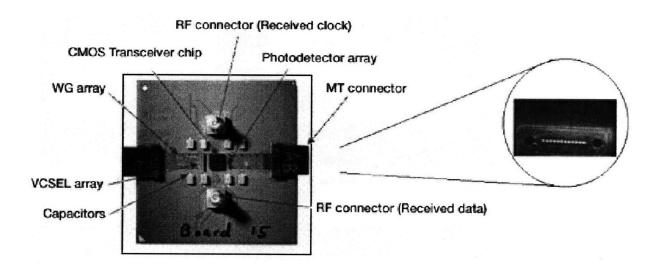

| 1-11 | Intel chip-to-chip optical interconnect prototype [95]                                          | 38 |

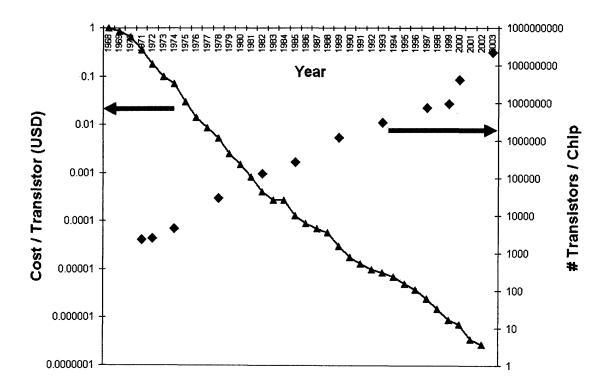

| 1-12 | Number of transistors integrated on a single chip and the related cost                          |    |

|      | per transistor[31]                                                                              | 39 |

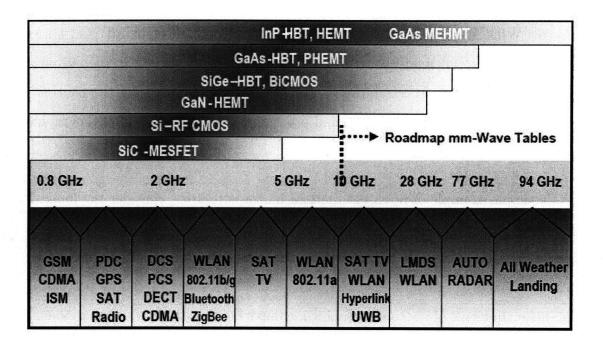

| 2-1  | 2006 International technology roadmap for semiconductors, radio fre-                            |    |

|      | quency and analog/mixed-signal technologies for wireless communica-                             |    |

|      | tions working group[6]. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 47 |

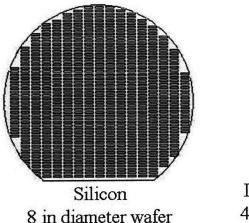

| 2-2  | Typical substrate sizes used in industry for silicon, indium phosphide                          |    |

|      | and gallium arsenide                                                                            | 49 |

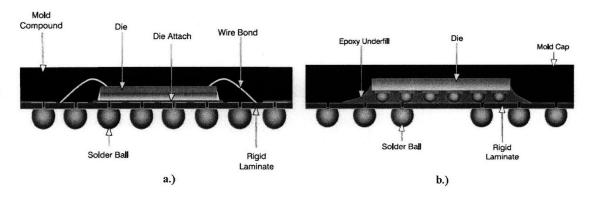

| 2-3  | Hybrid integration techniques a.) Wire bonding b.) Flip-chip bonding[82].                       | 50 |

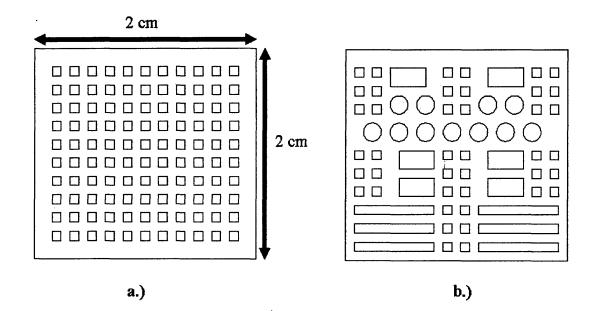

| 2-4  | Demonstration of flip-chip bonding limits: a.) Homogeneous array of                             |    |

|      | devices to be integrated. b.) Inhomogeneous array of devices to be                              |    |

|      | integrated                                                                                      | 51 |

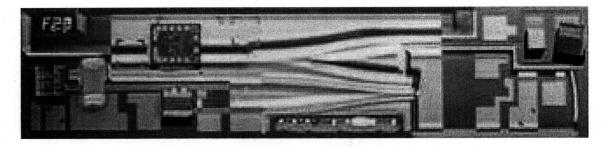

| 2-5  | Top-down picture of a triplexer product manufactured by Enablence                               |    |

|      | Technologies using flip-chip bonding techniques. A FTTH triplexer, as                           |    |

|      | described in Chapter 1, has multiple photodetectors, one at 1490 nm                             |    |

|      | and the other at 1550 nm, as well as a 1310 nm laser and electronics [85].                      | 52 |

| 2-6  | Fluidic self-assembly (FSA) schematic[94].                                                      | 55 |

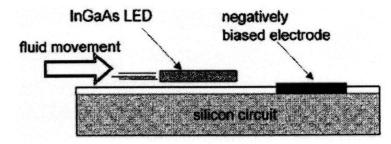

| 2-7  | Electric field directed assembly (EFDA) schematic [29]                                          | 57 |

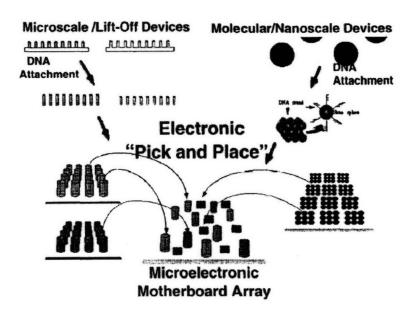

| 2-8  | DNA assisted assembly schematic[27]                                                             | 57 |

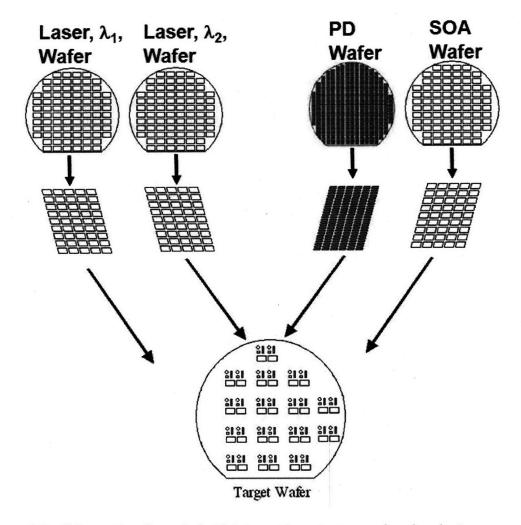

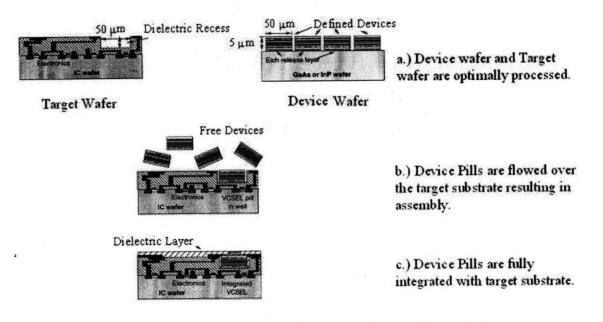

| 2-9  | Schematic of our hybrid integration strategy whereby devices are op-                            |    |

|      | timally processed on their own substrates, tested, and removed from                             |    |

|      | these substrates and assembled on a target substrate                                            | 59 |

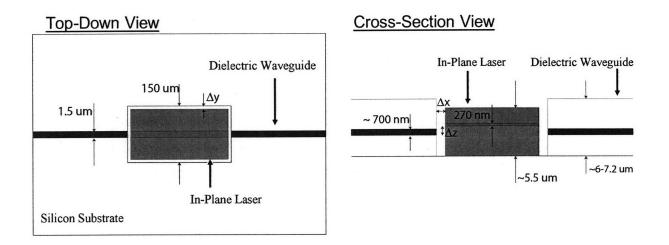

| 3-1  | Top-down and cross-sectional schematics showing the integration of a                            |    |

|      | edge-emitting laser with a dielectric waveguide on silicon                                      | 67 |

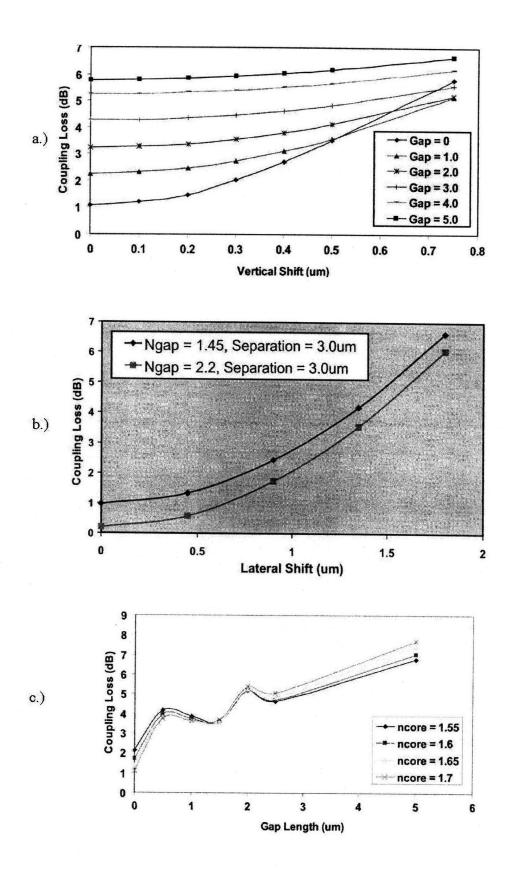

| 3-2  | Simulation work carried out by Dr. Edward Barkley on the coupling                   |    |

|------|-------------------------------------------------------------------------------------|----|

|      | loss as a function of a.) vertical offset, $\Delta z$ , b.) lateral offset (related |    |

|      | to $\Delta y$ ), and c.) gap spacing, $\Delta x$ . [15]                             | 68 |

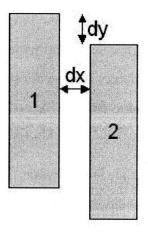

| 3-3  | Arrangement of two evanescently coupled waveguides, labelled 1 and 2.               | 70 |

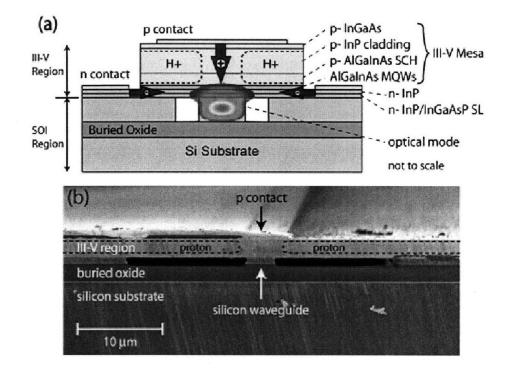

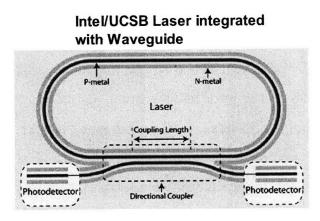

| 3-4  | a.) Schematic and b.) SEM showing the Intel-UCSB approach of inte-                  |    |

|      | grating an edge-emitting laser with a dielectric waveguide on silicon[33].          | 71 |

| 3-5  | Schematic of the dielectric waveguide with $SiO_xN_y$ core and $SiO_2$              |    |

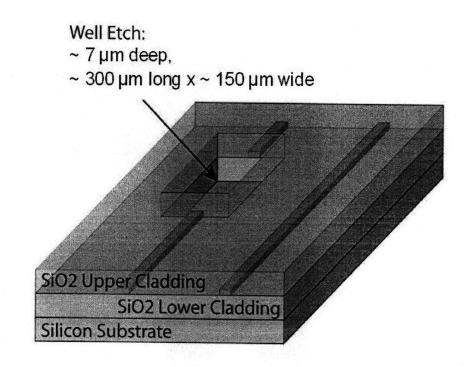

|      | cladding as well as the dielectric recess. [15]                                     | 72 |

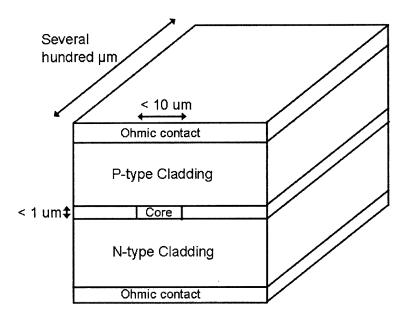

| 3-6  | Simple schematic of an edge-emitting laser with five essential layers               | 73 |

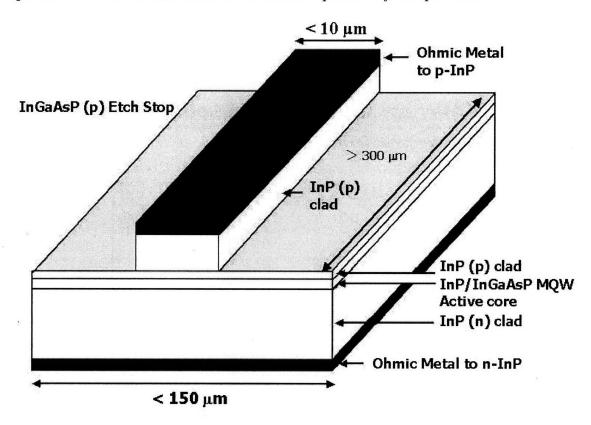

| 3-7  | Schematic showing the basic structure of a edge-emitting laser                      | 74 |

| 3-8  | a.) Schematic showing the two general techniques, roller break and                  |    |

|      | 3-point bending, used in the Loomis Industries automated cleaving                   |    |

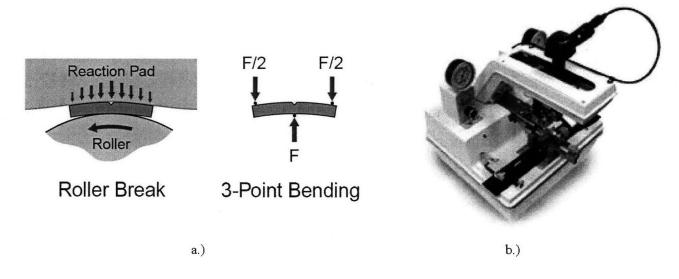

|      | process LSD-100 tool. b.) The LSD-100 tool. [39] $\ldots$ $\ldots$                  | 77 |

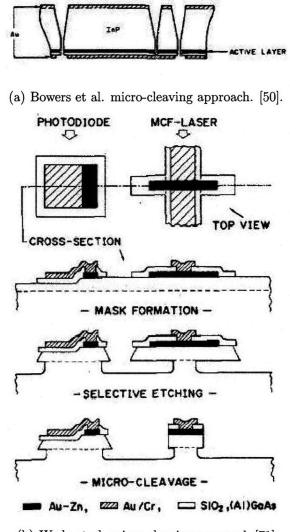

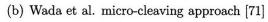

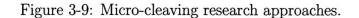

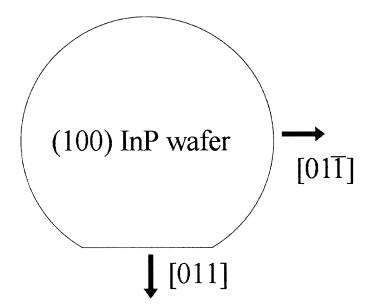

| 3-9  | Micro-cleaving research approaches.                                                 | 79 |

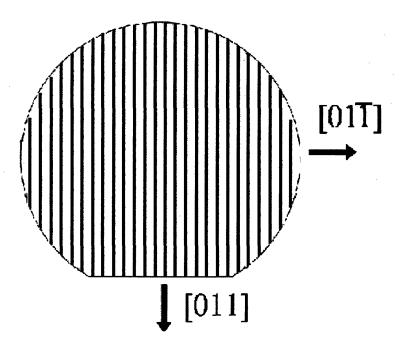

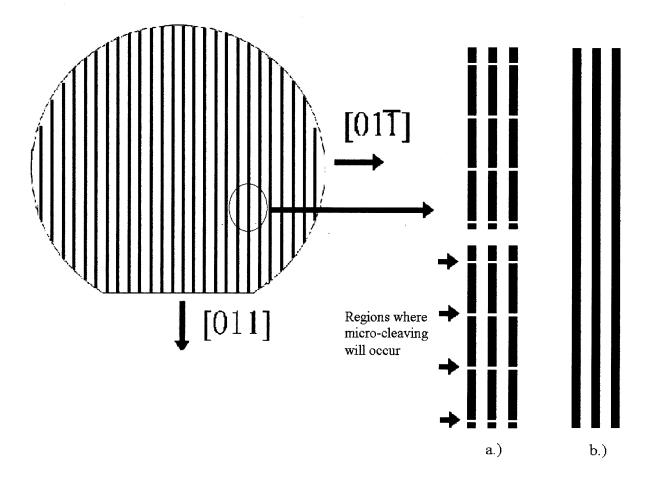

| 3-10 | Schematic showing a $(100)$ InP wafer and the associated cleavage planes            | 81 |

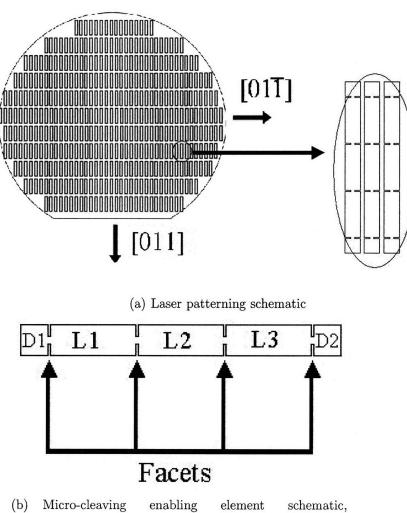

| 3-11 | Micro-cleave enabling elements                                                      | 82 |

| 3-12 | Array of bars formed on the front-side of a InP substrate upon which                |    |

|      | a InP/InGaAsP epitaxial structure has been grown                                    | 83 |

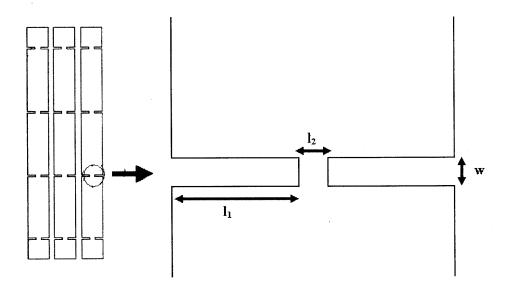

| 3-13 | Schematic of the micro-cleave enabling bar pattern.                                 | 84 |

| 3-14 | Aspect Ratio Dependent Etching in notch region                                      | 85 |

| 3-15 | Schematic of the micro-cleave enabling bar pattern with detail of the               |    |

|      | semiconductor ridge and ridge metal ohmic contact                                   | 86 |

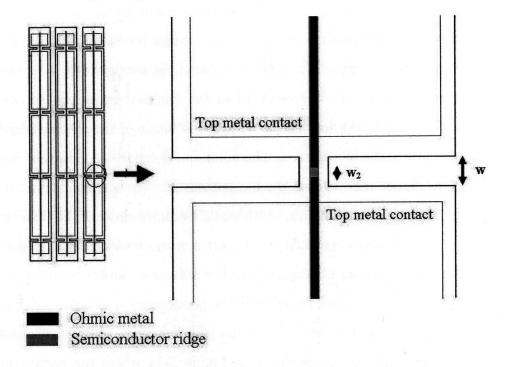

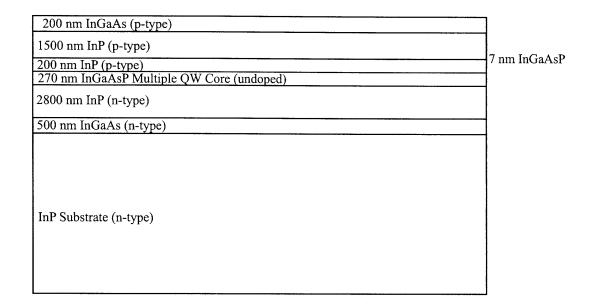

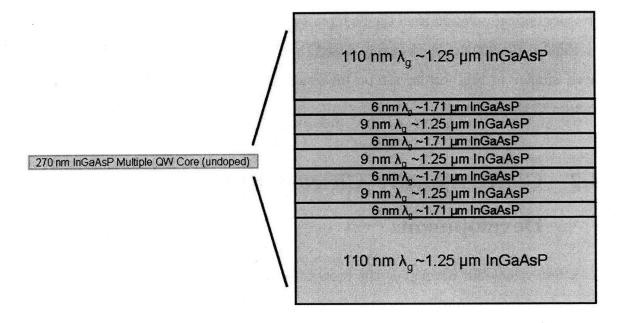

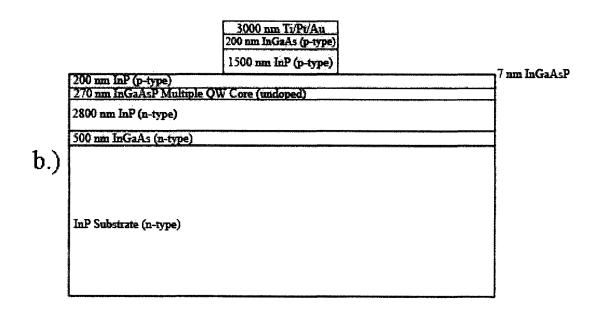

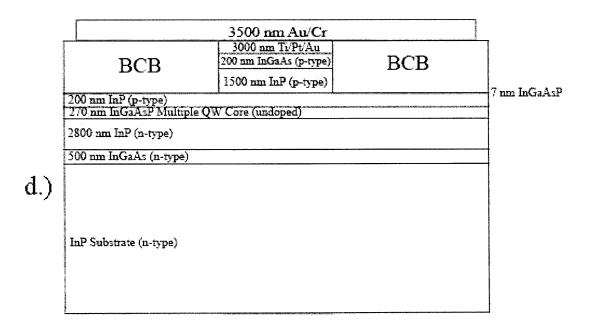

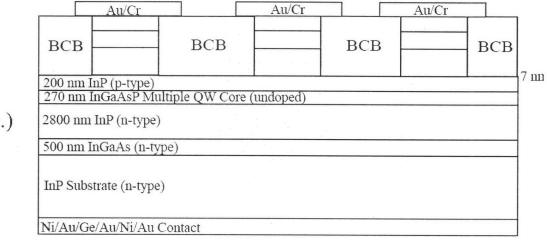

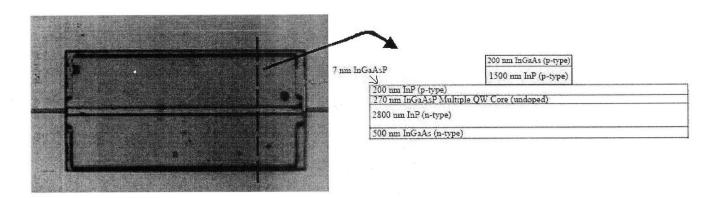

| 4-1  | Cross-sectional schematic of the 1550 nm laser structure grown on InP.              | 88 |

| 4-2  | Cross-sectional schematic of the 270 nm thick active region of the 1550             |    |

|      | nm laser epitaxial InP wafer                                                        | 89 |

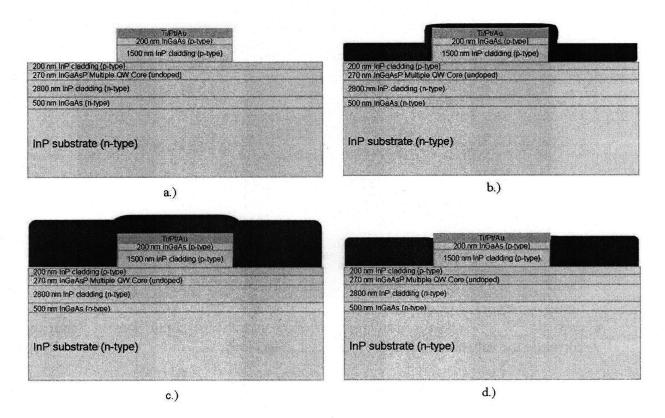

| 4-3  | Conventionally cleaved ridge laser front-side process flow schematic:               |    |

|      | a.) Top ohmic contact formation through b.) Semiconductor ridge                     |    |

|      | formation.                                                                          | 91 |

|      |                                                                                     |    |

| 4-3  | Conventionally cleaved ridge laser front-side process flow schematic            |     |

|------|---------------------------------------------------------------------------------|-----|

|      | continued: c.) Dielectric layer deposition and planarization through            |     |

|      | d.) Top large area contact formation.                                           | 92  |

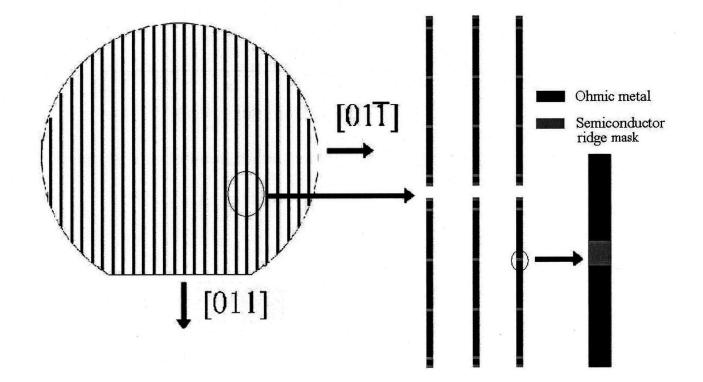

| 4-4  | Schematic showing the alignment of the metal ohmic contact ridge                |     |

|      | pattern to the cleavage planes of the InP wafer.                                | 93  |

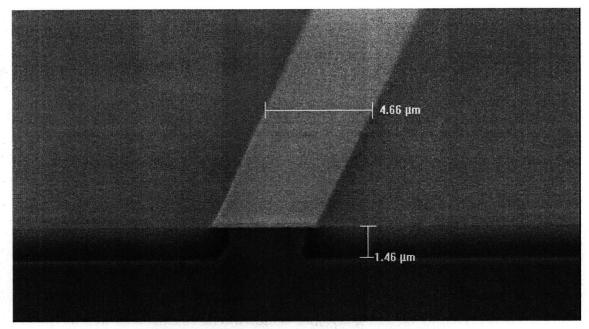

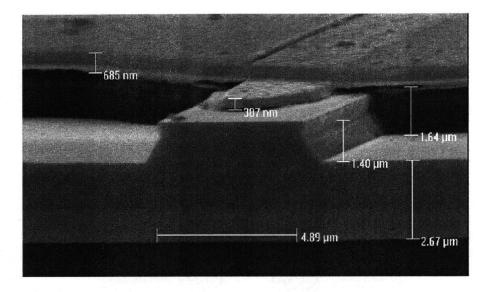

| 4-5  | Scanning electron micrograph of an unannealed ohmic contact metal               |     |

|      | to semiconductor ridge after the semiconductor ridge etch.                      | 95  |

| 4-6  | Schematic of the dielectric layer deposition and planarization proce-           |     |

|      | dure: a.) Starting sample, b.) First coat of Cyclotene and cure, c.)            |     |

|      | Second coat of Cyclotene and cure, d.) Cyclotene etch-back.                     | 96  |

| 4-7  | Scanning electron micrographs of ridge lasers after the BCB planariza-          |     |

|      | tion and etch-back process.                                                     | 98  |

| 4-8  | Scanning electron micrographs of ridge lasers after the top large area          |     |

|      | electrical contact formation. Note that the nodules visible on the metal        |     |

|      | are likely a result of contamination that occurred due to the high pres-        |     |

|      | sure of several $\mu$ Torr during deposition                                    | 100 |

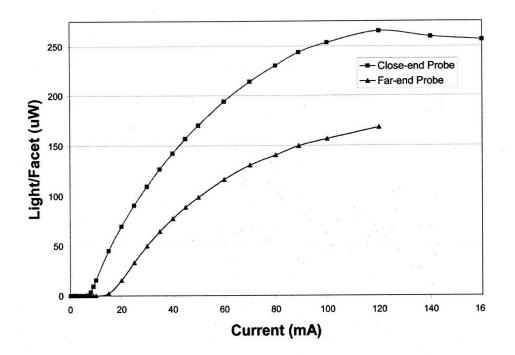

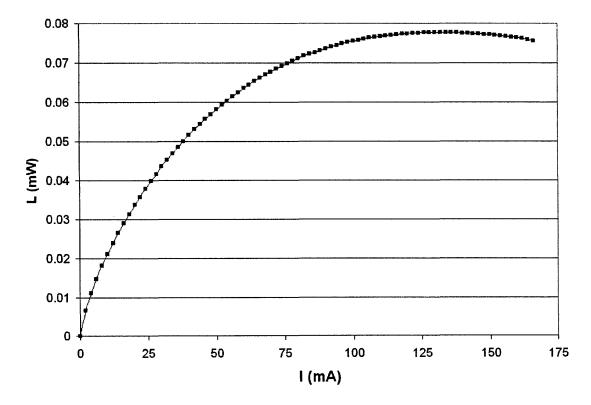

| 4-9  | Experimental L-I characteristic of the edge-emitting laser, with 9 $\mu{\rm m}$ |     |

|      | wide semiconductor ridge, probed at two distinct points on the ohmic            |     |

|      | ridge contact.                                                                  | 101 |

| 4-10 | Conventionally cleaved edge-emitting laser back-side schematic process          |     |

|      | flow: a.) Front-side protective coat, b.) Substrate mounting. Contin-           |     |

|      | ued on next page.                                                               | 102 |

| 4-10 | Conventionally cleaved edge-emitting laser backside schematic process           |     |

|      | flow continued: c.) Substrate thinning, d.) Backside ohmic contact              |     |

|      | formation. Continued on next page                                               | 103 |

| 4-10 | Conventionally cleaved edge-emitting laser backside schematic process           |     |

|      | flow continued: e.) Schematic cross-section of three finished devices,          |     |

|      | f.) Top-down photograph of three finished devices                               | 104 |

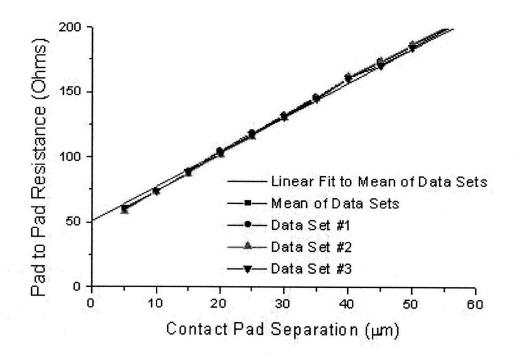

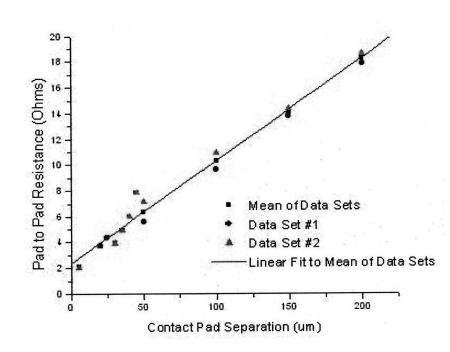

| 4-11 | TLM of a Ni/Au/Ge/Au/Ni/Au contact to a 350 $\mu$ m thick n-type InP            |     |

|      | substrate                                                                       | 106 |

| 4-12 | Schematic showing how the metal ohmic contact ridge pattern is aligned<br>to the cleavage planes of the InP wafer: a.) Micro-cleaved ridge laser |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | process, b.) Conventionally cleaved ridge laser process                                                                                          | 107 |

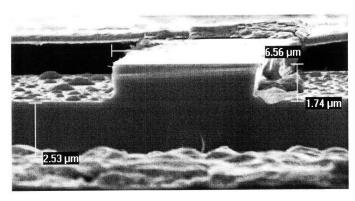

| 4-13 | Scanning electron micrographs showing micro-cleaved devices where                                                                                |     |

|      | a.) the ohmic contact metal was continuous across multiple devices,                                                                              |     |

|      | b.) the ohmic contact metal was discontinuous in the notch regions                                                                               |     |

|      | between devices                                                                                                                                  | 108 |

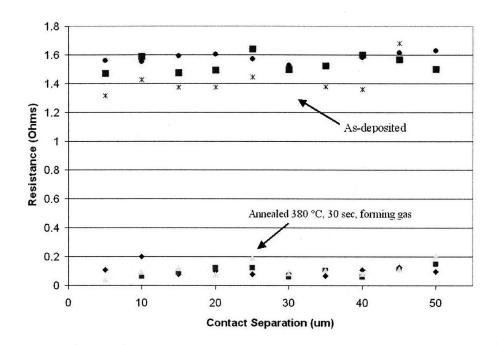

| 4-14 | TLM of an annealed Ti/Pt/Au contact deposited on a 500 nm thick                                                                                  |     |

|      | p-type InGaAs layer.                                                                                                                             | 109 |

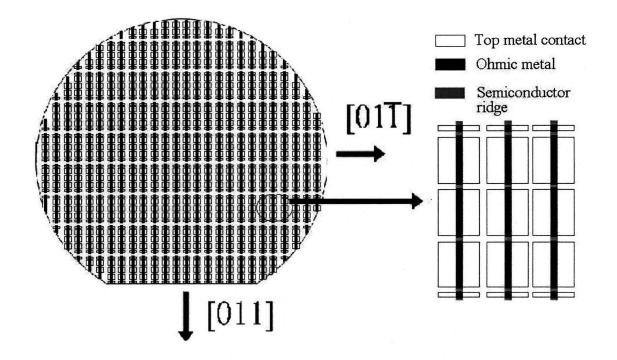

| 4-15 | Schematic showing the semiconductor ridge pattern aligned over the                                                                               |     |

|      | ohmic contact                                                                                                                                    | 110 |

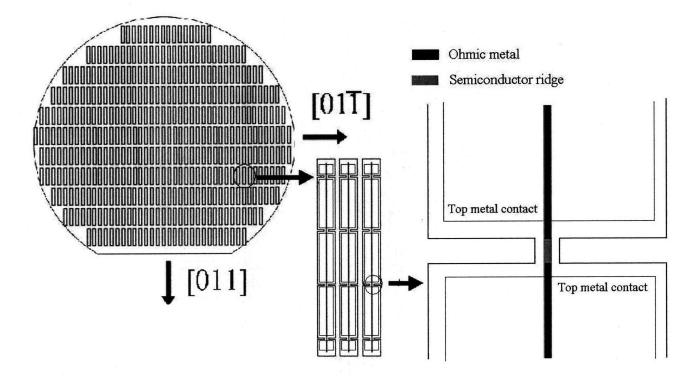

| 4-16 | Schematic detailing how the top large area electrical contact is aligned                                                                         |     |

|      | over the ohmic ridge contact.                                                                                                                    | 111 |

| 4-17 | Schematic showing the alignment of the micro-cleave bar pattern to                                                                               |     |

|      | the semiconductor ridge, the ohmic metal ridge contact, and the top                                                                              |     |

|      | large area electrical contact.                                                                                                                   | 112 |

| 4-18 | Schematic cross-section of the device a.) prior to dry etching, b.) after                                                                        |     |

|      | dry etching and $SiO_2$ hardmask removal                                                                                                         | 114 |

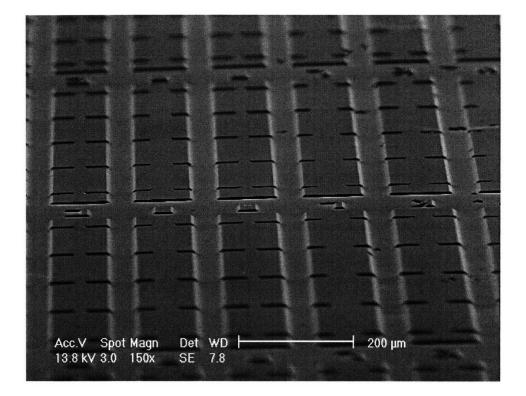

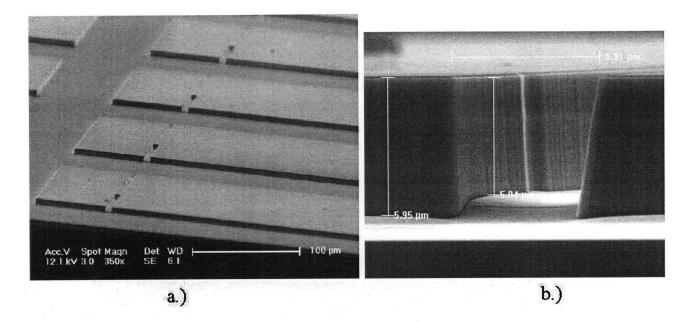

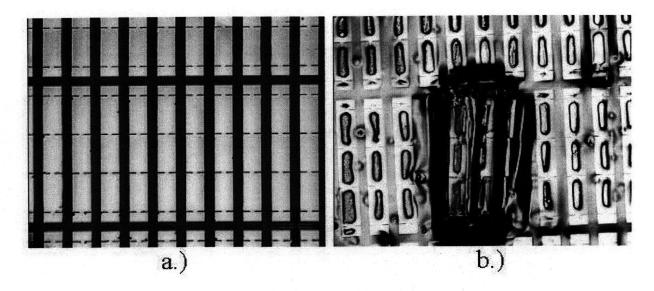

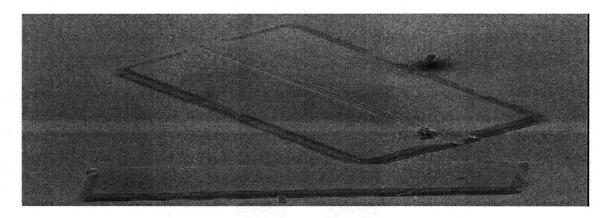

| 4-19 | Scanning electron micrographs of: a.) An array of micro-cleave en-                                                                               |     |

|      | abling bar patterns formed by ICP dry etching on the front-side of                                                                               |     |

|      | an InP substrate, and b.) Zoomed-in SEM of one notch. Note, these                                                                                |     |

|      | images are of etches on dummy InP material and not the actual laser                                                                              |     |

|      | epitaxial material                                                                                                                               | 115 |

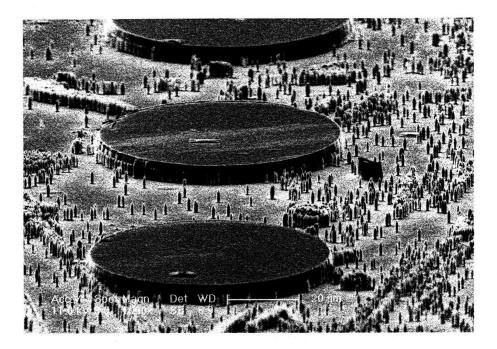

| 4-20 | Scanning electron micrograph of an array of circular InP-based diodes                                                                            |     |

|      | patterned by reactive ion etching using a methane/hydrogen chemistry.                                                                            | 116 |

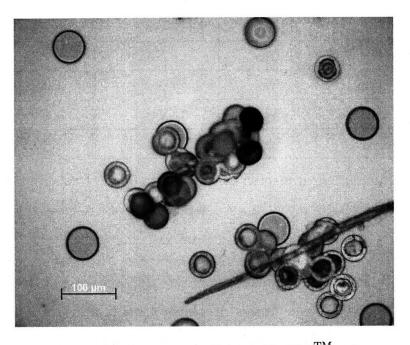

| 4-21 | Pictorial results of the Brewer Science $\operatorname{ProTek}^{\operatorname{TM}}$ polymer process where                                        |     |

|      | arrays of heterostructure diode pills clumped together.                                                                                          | 118 |

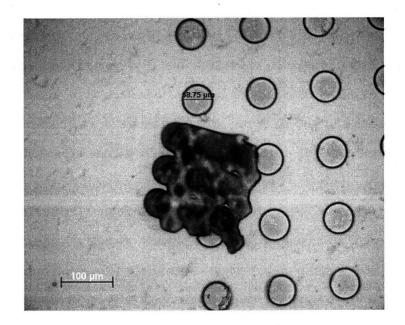

| 4-22 | Pictorial results of Apiezon <sup>®</sup> wax process where arrays of heterostruc-                                                               |     |

|      | ture diode pills clumped together.                                                                                                               | 118 |

.

| 4-23 Pictorial results of the Apiezon® wax/photoresist process a.) Post-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| substrate removal, b.) Post back-side photolithography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 119               |

| 4-24 Pictorial results of the WaferBOND <sup>TM</sup> process post back-side metal-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

| lization and lift-off processing, a.) Zoomed-out image, b.) Zoomed-in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |

| image. Note that there appears to be some residue in the notch re-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                   |

| gions. What looks like residue is, in fact, InGaAs. Since this thin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                   |

| InGaAs layer aids the ohmic contact formation, it is etched off only                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

| after the liftoff process is complete. This way the ohmic metallization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| is used as a self-aligned etch mask.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 120               |

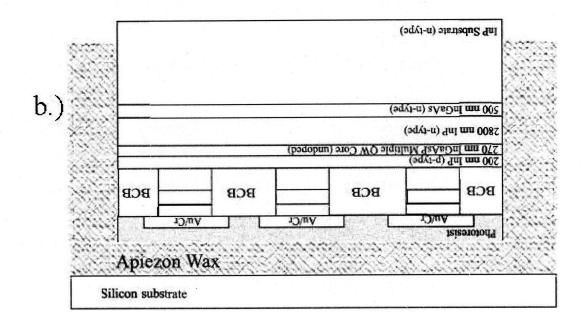

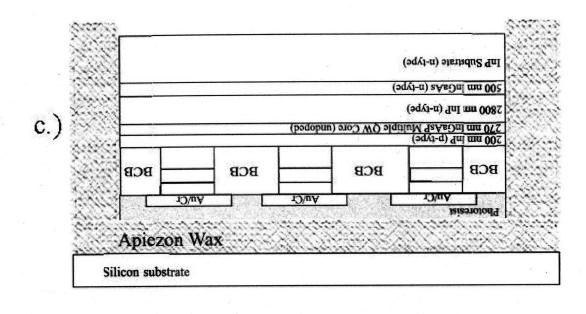

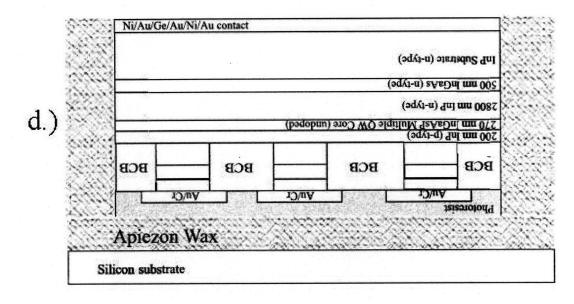

| 4-25 Cross-sectional schematics of ridge lasers during the back-side process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 121               |

| 4-26 Cross-sectional schematics of ridge lasers during the back-side process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                   |

| continued.  .  .  .  .  .  .  .  .  .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 122               |

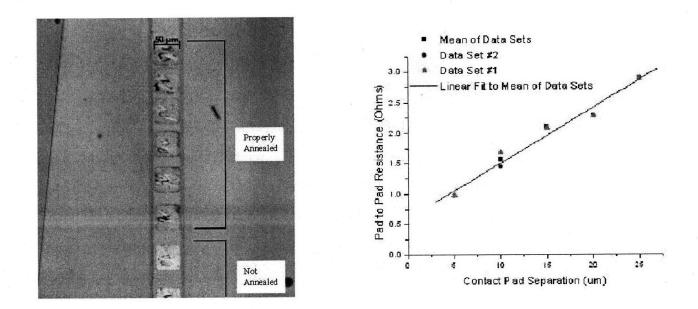

| 4-27 TLM of an as-deposited Ni/Au/Ge/Au/Ni/Au contact deposited on a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

| 500 nm thick n-type InGaAs layer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 124               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

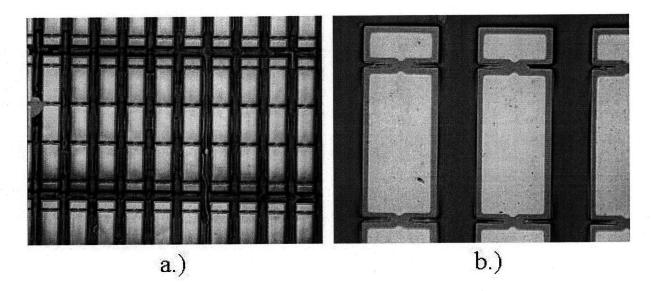

| 4-28 a.) Photo of contact pattern on InGaAs showing the importance of a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| 4-28 a.) Photo of contact pattern on InGaAs showing the importance of a flat surface when annealing or activating the contacts. b.) TLM of an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                   |

| flat surface when annealing or activating the contacts. b.) TLM of an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 124               |

| flat surface when annealing or activating the contacts. b.) TLM of an annealed Ni/Au/Ge/Au/Ni/Au contact deposited on a 500 nm thick                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                   |

| flat surface when annealing or activating the contacts. b.) TLM of an annealed Ni/Au/Ge/Au/Ni/Au contact deposited on a 500 nm thick n-type InGaAs layer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                   |

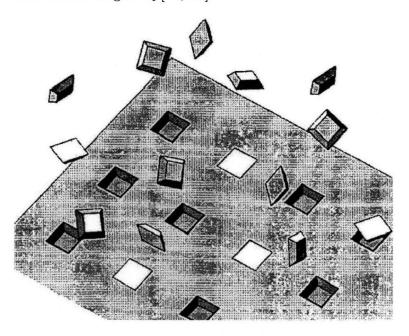

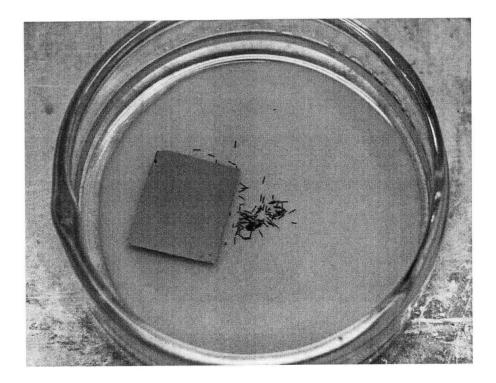

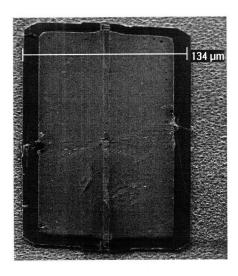

| <ul> <li>flat surface when annealing or activating the contacts. b.) TLM of an annealed Ni/Au/Ge/Au/Ni/Au contact deposited on a 500 nm thick n-type InGaAs layer.</li> <li>4-29 Pictorial results of the laser bars released in solution.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                | 125               |

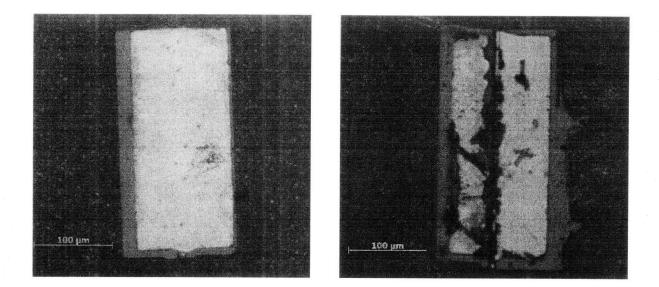

| <ul> <li>flat surface when annealing or activating the contacts. b.) TLM of an annealed Ni/Au/Ge/Au/Ni/Au contact deposited on a 500 nm thick n-type InGaAs layer.</li> <li>4-29 Pictorial results of the laser bars released in solution.</li> <li>4-30 Top-down image of typical micro-cleaved ridge laser before and after</li> </ul>                                                                                                                                                                                                                                                                                                                             | 125<br>126        |

| <ul> <li>flat surface when annealing or activating the contacts. b.) TLM of an annealed Ni/Au/Ge/Au/Ni/Au contact deposited on a 500 nm thick n-type InGaAs layer.</li> <li>4-29 Pictorial results of the laser bars released in solution.</li> <li>4-30 Top-down image of typical micro-cleaved ridge laser before and after electrical probing.</li> </ul>                                                                                                                                                                                                                                                                                                         | 125<br>126        |

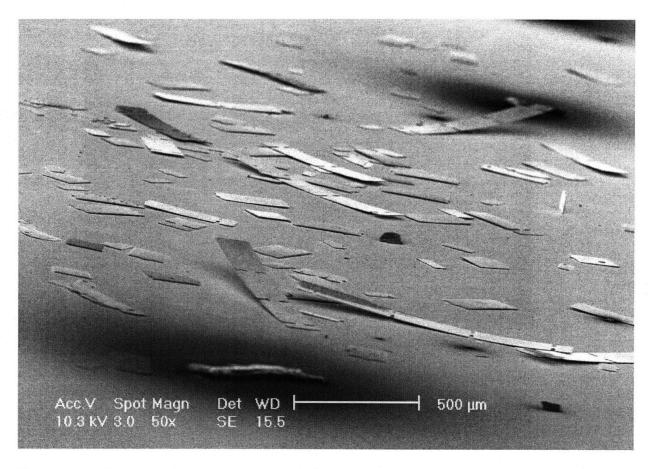

| <ul> <li>flat surface when annealing or activating the contacts. b.) TLM of an annealed Ni/Au/Ge/Au/Ni/Au contact deposited on a 500 nm thick n-type InGaAs layer.</li> <li>4-29 Pictorial results of the laser bars released in solution.</li> <li>4-30 Top-down image of typical micro-cleaved ridge laser before and after electrical probing.</li> <li>4-31 Scanning electron micrograph of a large quantity of micro-cleaved lasers</li> </ul>                                                                                                                                                                                                                  | 125<br>126        |

| <ul> <li>flat surface when annealing or activating the contacts. b.) TLM of an annealed Ni/Au/Ge/Au/Ni/Au contact deposited on a 500 nm thick n-type InGaAs layer.</li> <li>4-29 Pictorial results of the laser bars released in solution.</li> <li>4-30 Top-down image of typical micro-cleaved ridge laser before and after electrical probing.</li> <li>4-31 Scanning electron micrograph of a large quantity of micro-cleaved lasers micro-cleaved dummy devices, as well as long uncleaved bars.</li> </ul>                                                                                                                                                     | 125<br>126        |

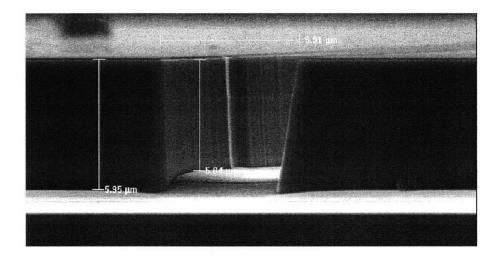

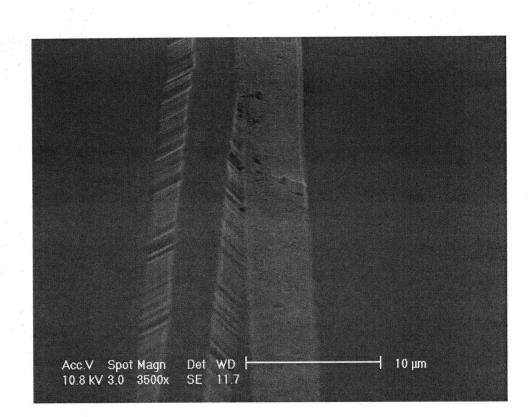

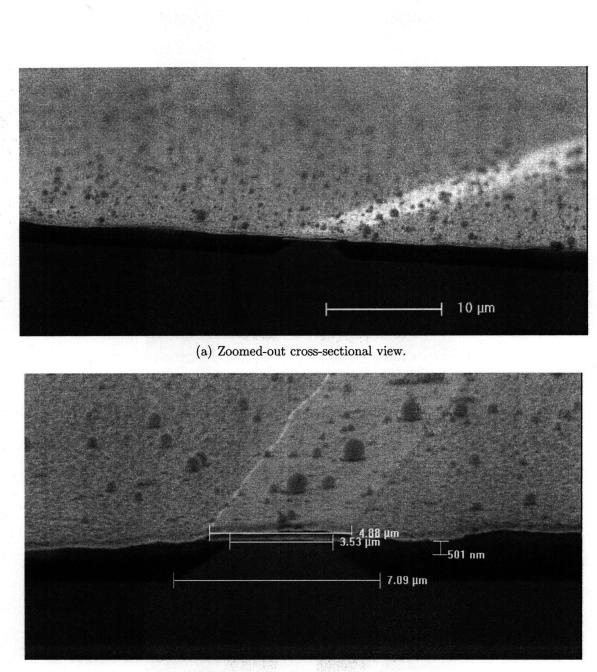

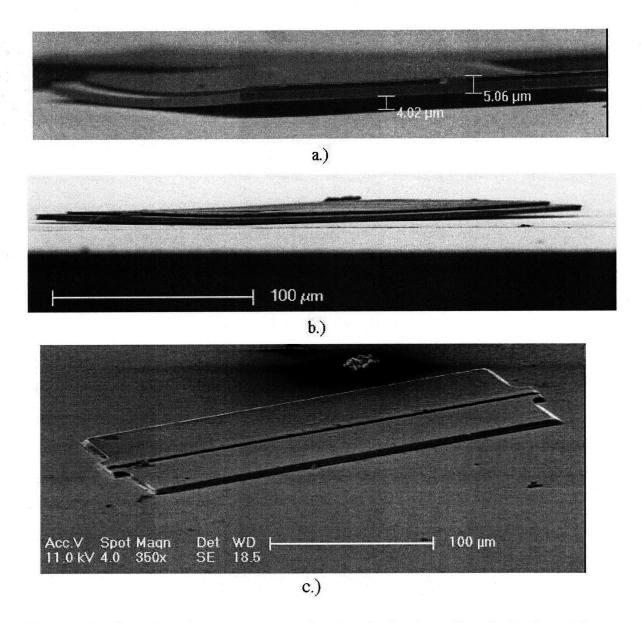

| <ul> <li>flat surface when annealing or activating the contacts. b.) TLM of an annealed Ni/Au/Ge/Au/Ni/Au contact deposited on a 500 nm thick n-type InGaAs layer.</li> <li>4-29 Pictorial results of the laser bars released in solution.</li> <li>4-30 Top-down image of typical micro-cleaved ridge laser before and after electrical probing.</li> <li>4-31 Scanning electron micrograph of a large quantity of micro-cleaved lasers micro-cleaved dummy devices, as well as long uncleaved bars.</li> <li>4-32 Scanning electron micrographs of a typical facet achieved with the</li> </ul>                                                                    | 125<br>126<br>127 |

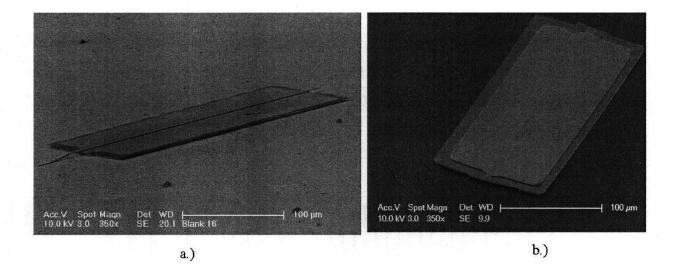

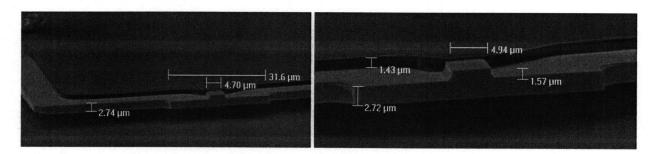

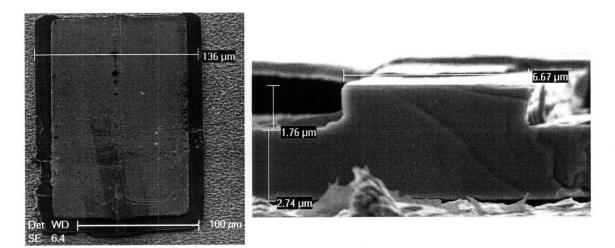

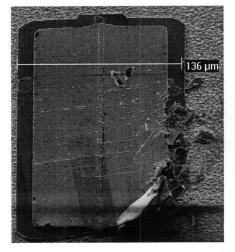

| <ul> <li>flat surface when annealing or activating the contacts. b.) TLM of an annealed Ni/Au/Ge/Au/Ni/Au contact deposited on a 500 nm thick n-type InGaAs layer.</li> <li>4-29 Pictorial results of the laser bars released in solution.</li> <li>4-30 Top-down image of typical micro-cleaved ridge laser before and after electrical probing.</li> <li>4-31 Scanning electron micrograph of a large quantity of micro-cleaved lasers micro-cleaved dummy devices, as well as long uncleaved bars.</li> <li>4-32 Scanning electron micrographs of a typical facet achieved with the micro-cleaving process, a.) zoomed-out image, b.) zoomed-in image.</li> </ul> | 125<br>126<br>127 |

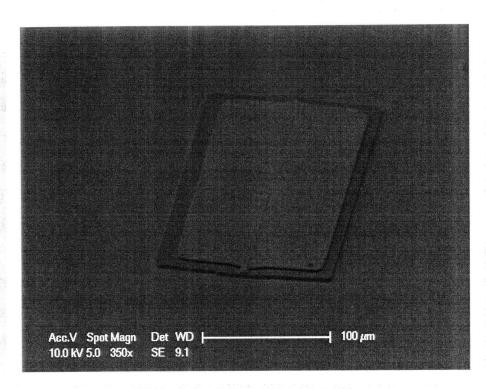

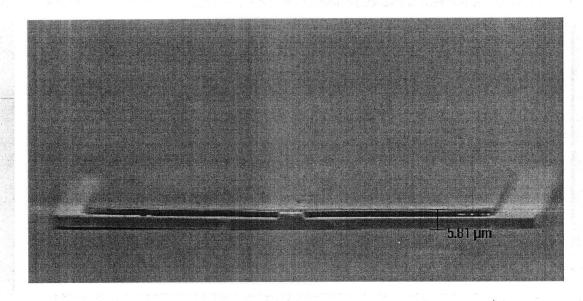

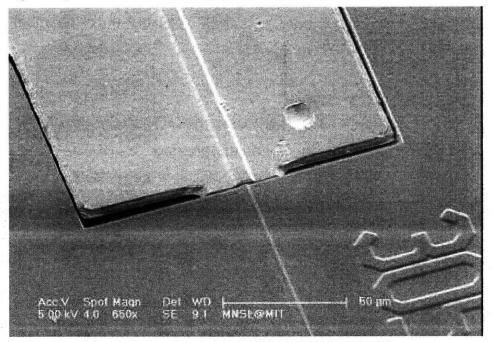

| 4-35       | Scanning electron micrographs of: a.) A micro-cleaved platelet with                                               |      |

|------------|-------------------------------------------------------------------------------------------------------------------|------|

|            | front-side planarization and large area metal layers, but no back-side                                            |      |

|            | metal, b.) A micro-cleaved platelet with front-side planarization and                                             |      |

|            | large area metal layers, and back-side metal layers, c.) A micro-cleaved                                          |      |

|            | platelet with no front-side planarization and large area metal layers,                                            |      |

|            | and no back-side metal layers either.                                                                             | 130  |

| 4-36       | Scanning electron micrograph of a laser bars indium bonded down on                                                |      |

|            | a silicon substrate.                                                                                              | 131  |

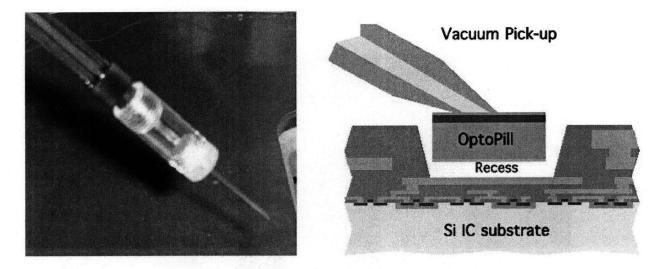

| 4-37       | Picture and schematic of the micro-pipette tool used to pick up and                                               |      |

|            | move individual platelets.                                                                                        | 132  |

| 4-38       | Picture and cross-sectional schematic of an InP-based micro-cleaved                                               |      |

|            | ridge waveguide platelet.                                                                                         | 134  |

| 4-39       | Picture of two InP-based micro-cleaved ridge waveguides assembled in                                              |      |

|            | dielectric recesses on a silicon substrate.                                                                       | 134  |

| 4-40       | Images of micro-cleaved ridge waveguides assembled in dielectric re-                                              |      |

|            | cesses on a silicon substrate.                                                                                    | 135  |

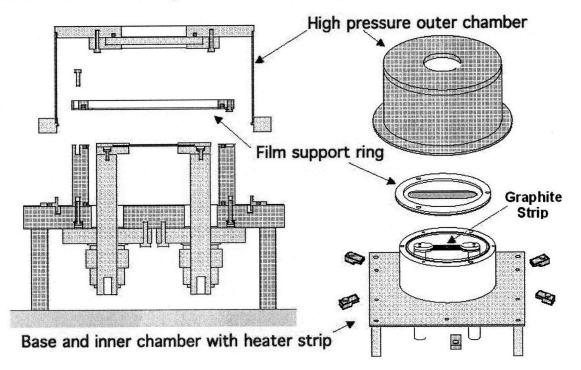

| 4-41       | Schematic of the bonding chamber used.                                                                            | 136  |

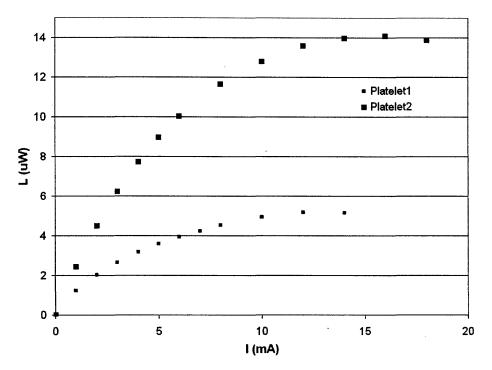

| 4-42       | Light output characteristics of unbonded and poorly bonded micro-                                                 |      |

|            | cleaved ridge platelets on silicon.                                                                               | 138  |

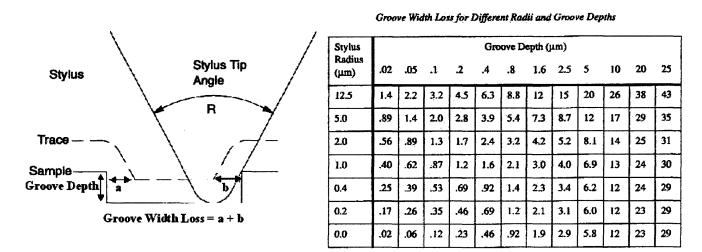

| 5-1        | Schematic and table detailing the effect of models at the status                                                  |      |

| 0-1        | Schematic and table detailing the effect of profilometer stylus radius<br>on the lateral measurement accuracy[83] | 141  |

| <b>F</b> 0 |                                                                                                                   | 141  |

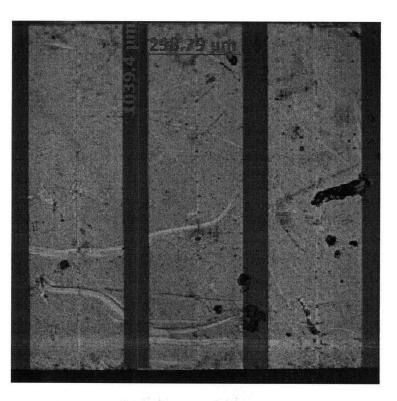

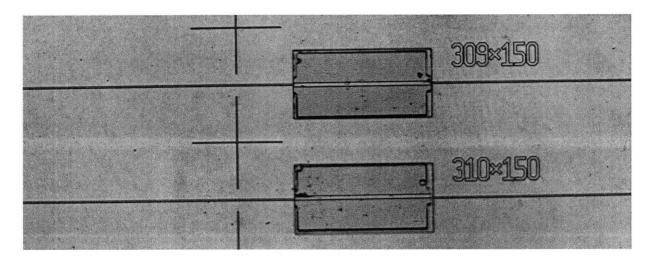

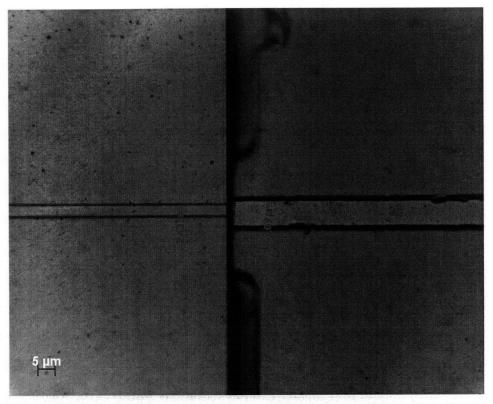

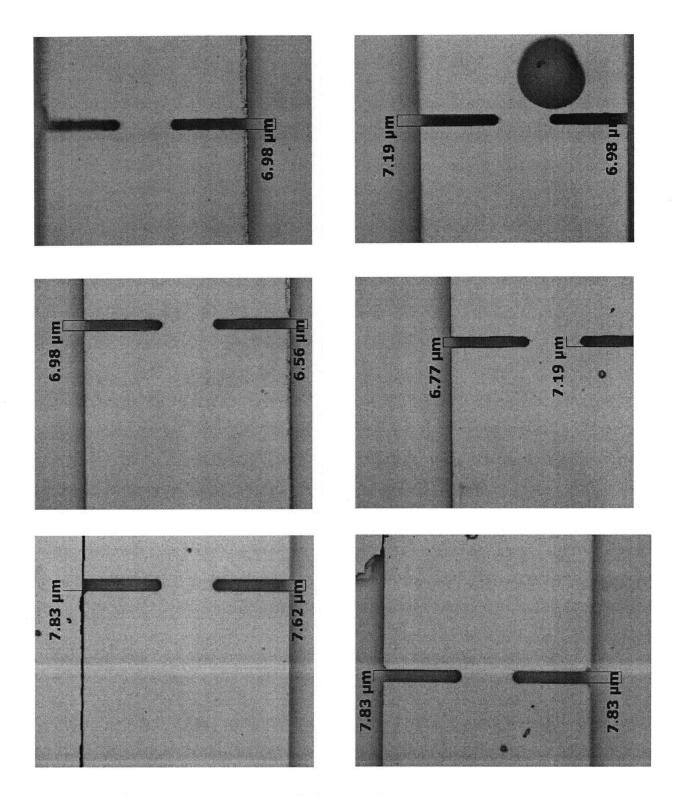

| 5-2        | Pictures taken with the Carl Zeiss Axioskop microscope system of a                                                | 1.40 |

|            | number of notches from one given sample.                                                                          | 143  |

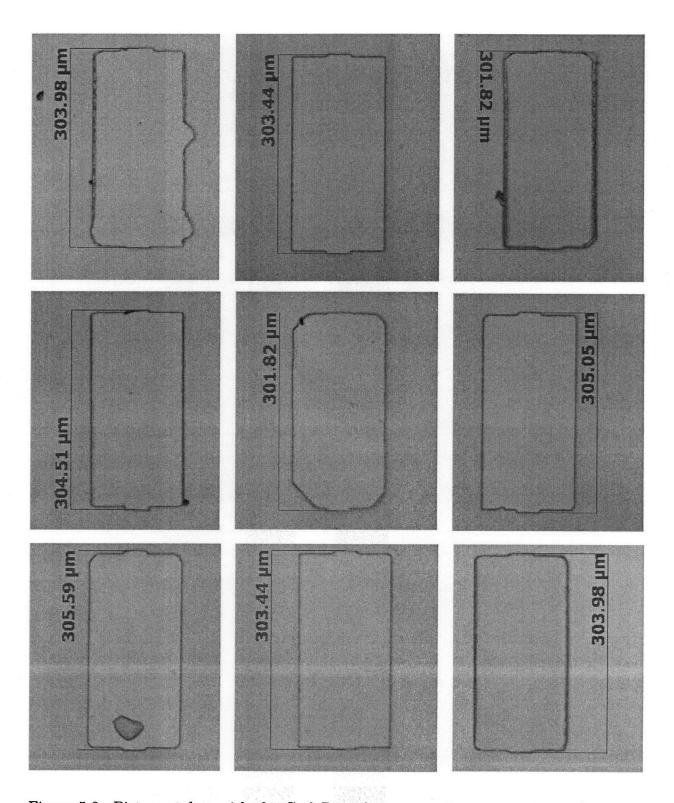

| 5-3        | Pictures taken with the Carl Zeiss Axioscope microscope system of a                                               |      |

|            | number of micro-cleaved platelets from one given sample                                                           | 144  |

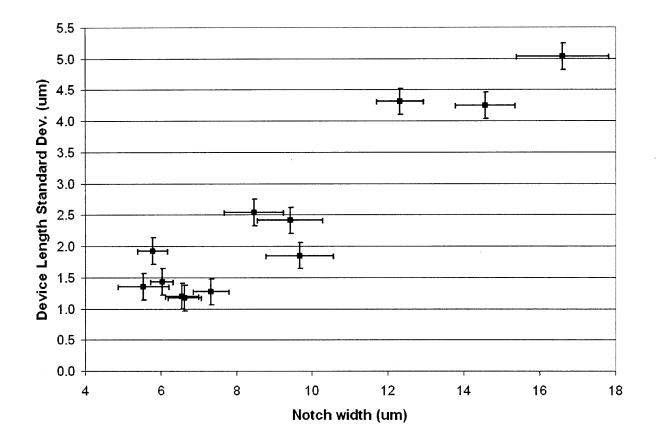

| 5-4        | Experimental results of the micro-cleave process device length variabil-                                          |      |

|            | ity as a function of notch width                                                                                  | 145  |

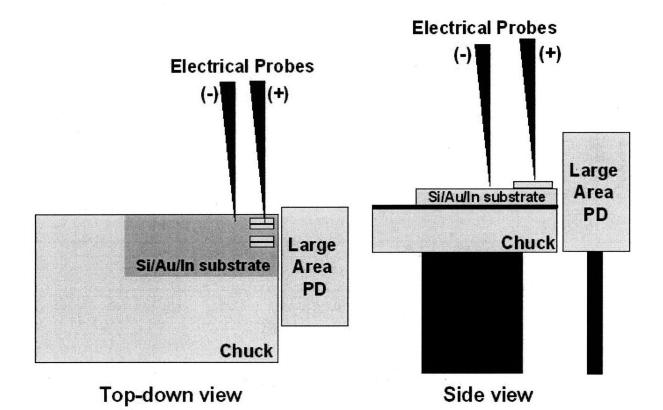

| 5-5        | Test setup for the ridge laser light output characterization                                                      | 147  |

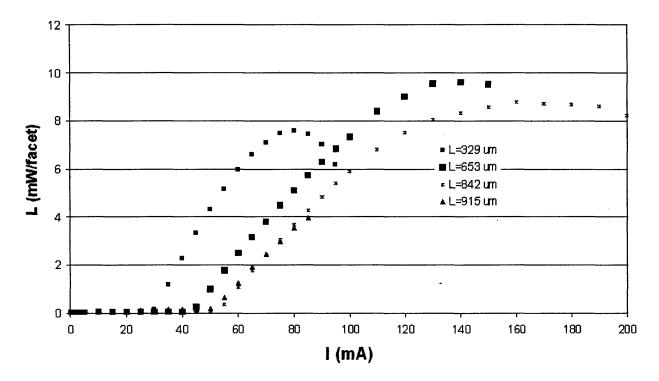

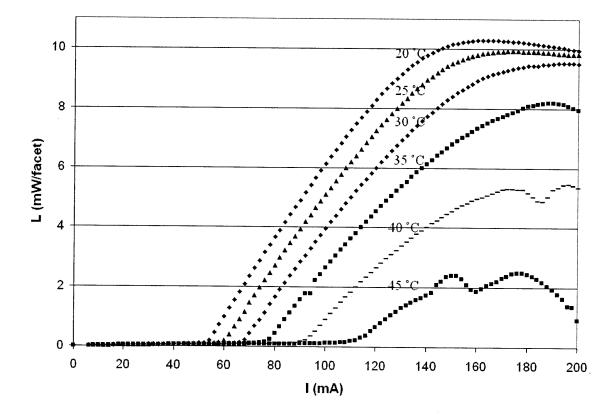

| 5-6  | Experimental light output characteristics of CC ridge lasers (6.8 $\mu$ m               |         |

|------|-----------------------------------------------------------------------------------------|---------|

|      | wide ridge) of various cavity lengths measured at room temperature                      |         |

|      | and under continuous-wave conditions.                                                   | 148     |

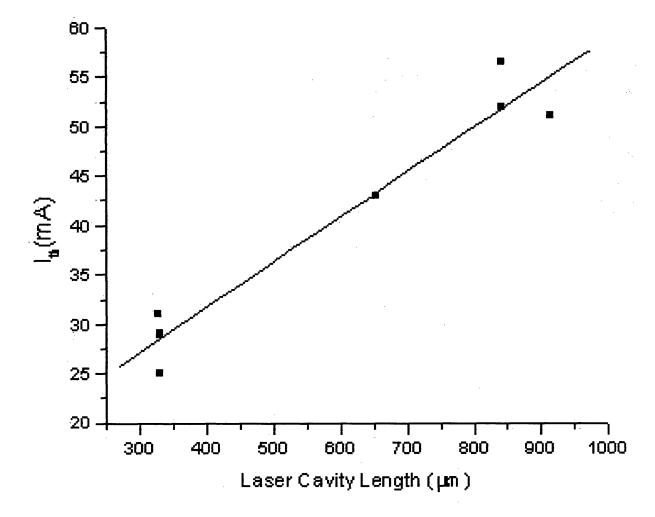

| 5-7  | Threshold current as a function of laser cavity length for CC ridge                     |         |

|      | lasers (6.8 $\mu$ m wide ridge) measured at room temperature and under                  |         |

|      | continuous-wave conditions.                                                             | 149     |

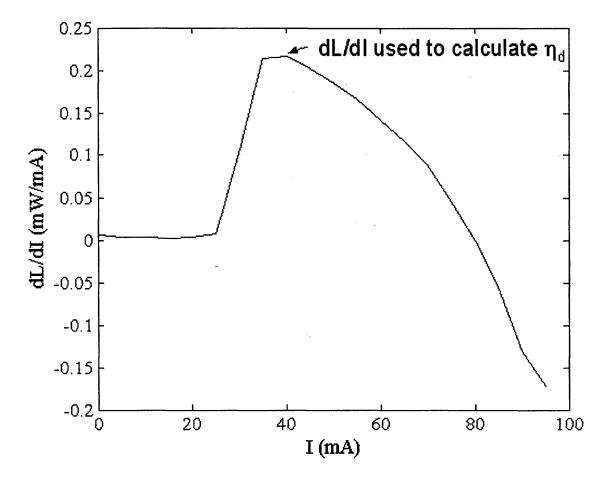

| 5-8  | dL/dI vs. I characteristic for a CC ridge laser (6.8 $\mu m$ wide ridge, 328.5          |         |

|      | $\mu$ m long device) measured at room temperature and under continuous-                 |         |

|      | wave conditions.                                                                        | 150     |

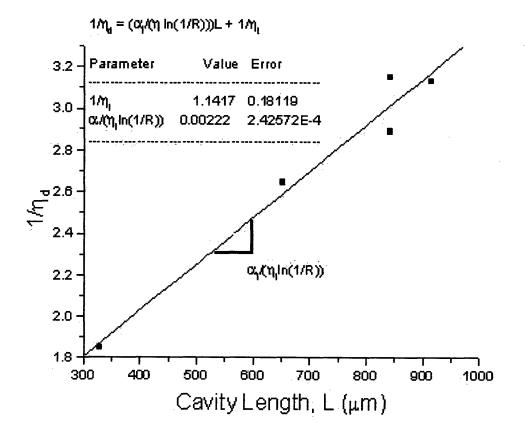

| 5-9  | Inverse of the maximum differential efficiency as a function of laser                   |         |

|      | cavity length for CC ridge lasers (6.8 $\mu$ m wide ridge) measured at                  |         |

|      | room temperature and under continuous-wave conditions. Extracted                        |         |

|      | parameters are $\eta_i = 87.6\%$ , and $\alpha_i/\ln(1/R) = 19.4 \ cm^{-1}$ .           | 151     |

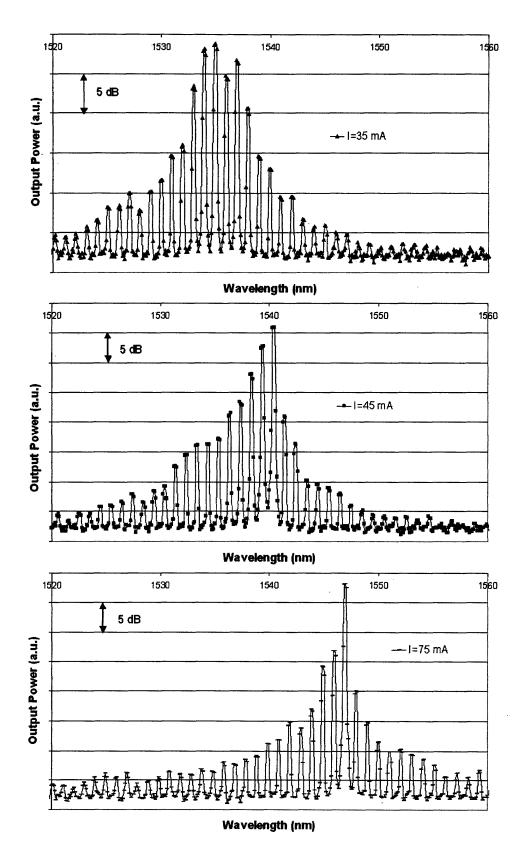

| 5-10 | Optical output spectrum of a CC ridge laser with length = 328.5 $\mu \mathrm{m}$        |         |

|      | and ridge width of 6.8 $\mu$ m measured at room temperature and under                   |         |

|      | continuous-wave conditions.                                                             | 153     |

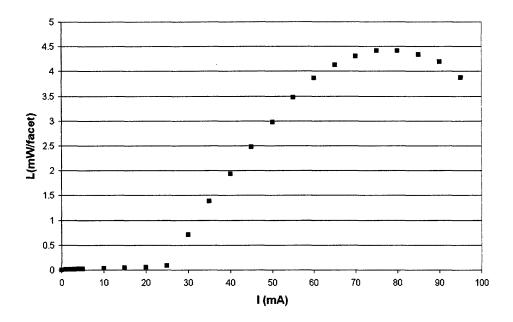

| 5-11 | Light output characteristic of a CC ridge laser with length = 328.5 $\mu \rm{m}$        |         |

|      | and ridge width of 6.8 $\mu$ m measured at room temperature and under                   | ·       |

|      | continuous-wave conditions. This output spectrum corresponding to                       |         |

|      | this laser is shown in Figure 5                                                         | 154     |

| 5-12 | Light output characteristic as a function of stage temperature for an                   |         |

|      | 1170 $\mu m$ long, 6.8 $\mu m$ wide CC ridge laser (CC1) measured under                 |         |

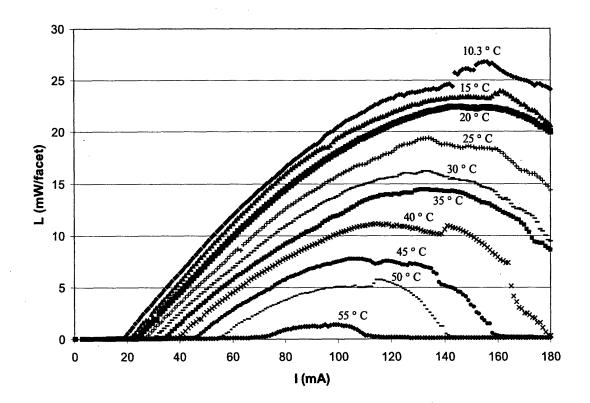

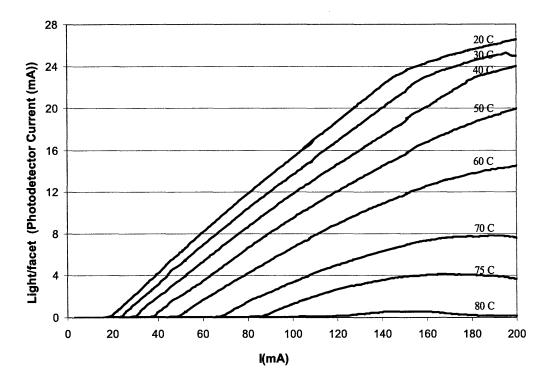

|      | continuous-wave conditions.                                                             | 155     |

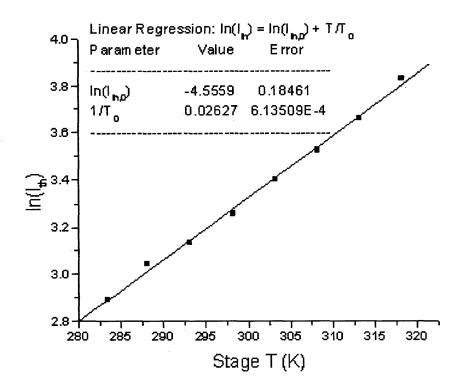

| 5-13 | ln(Threshold current) as a function of stage temperature for a continuous               | -       |

|      | wave tested conventionally-cleaved ridge laser (CC1). $\ldots$                          | 156     |

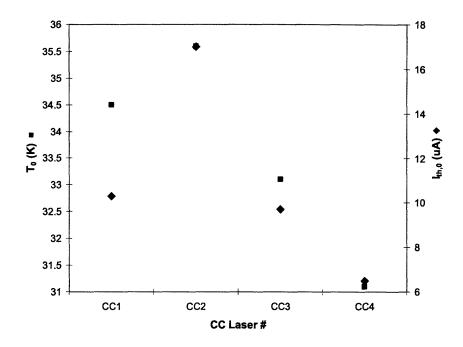

| 5-14 | Characteristic temperatures, $T_0$ , and the 0 K threshold currents, $I_{th,0}$ ,       |         |

|      | of four conventionally cleaved ridge lasers tested under continuous-wave                |         |

|      | conditions                                                                              | 157     |

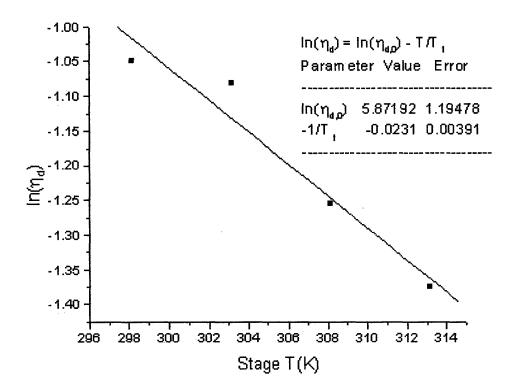

| 5-15 | $\ln(\text{differential efficiency})$ as a function of stage temperature for a conventi | onally- |

|      | cleaved ridge laser (CC1) tested under continuous-wave conditions.                      | 158     |

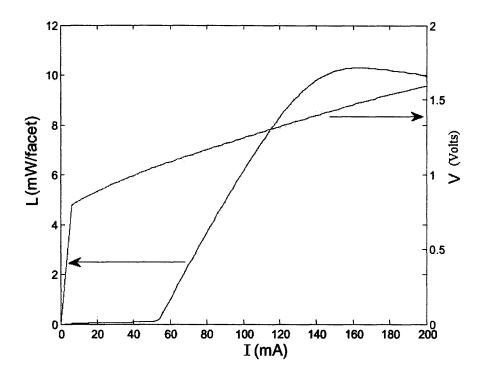

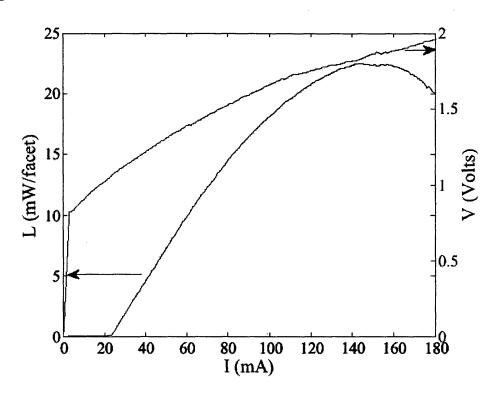

| 5-16 | Light output and current-voltage characteristics for a ridge laser (CC1)                                                                        |     |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | measured at a stage temperature of 20 $^{\circ}\mathrm{C}$ and under continuous-wave                                                            |     |

|      | conditions                                                                                                                                      | 159 |

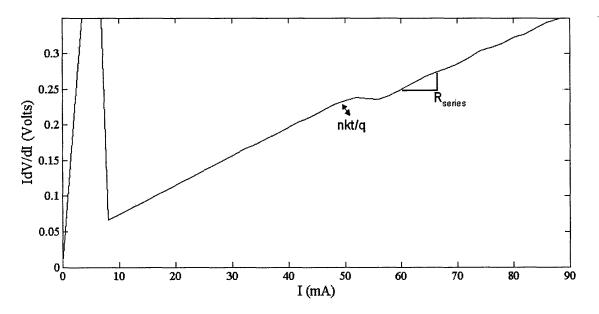

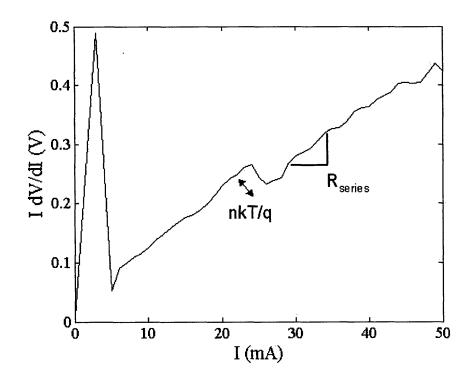

| 5-17 | IdV/dI vs. I for a CC ridge laser (CC1) measured at room temperature                                                                            |     |

|      | and under continuous-wave conditions.                                                                                                           | 160 |

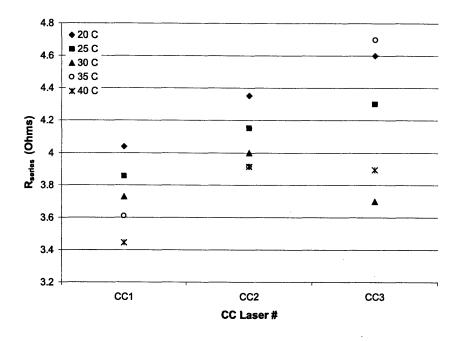

| 5-18 | Diode forward series resistance as a function of stage temperature for                                                                          |     |

|      | three different conventionally cleaved ridge lasers, CC1, CC2, and CC3.                                                                         | 161 |

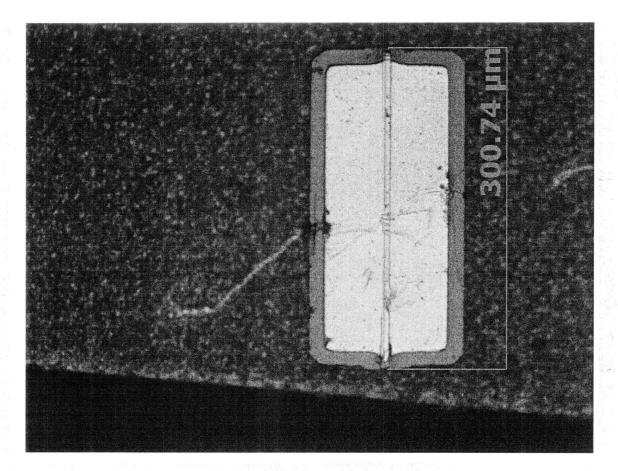

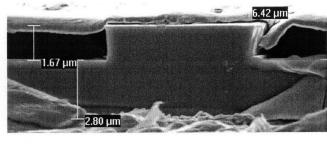

| 5-19 | Top-down photograph of micro-cleaved ridge laser (MC6) bonded on                                                                                |     |

|      | silicon                                                                                                                                         | 162 |

| 5-20 | Light output characteristic for micro-cleaved ridge laser (MC6) on sil-                                                                         |     |

|      | icon as a function of stage temperature and under continuous-wave                                                                               |     |

|      | conditions                                                                                                                                      | 163 |

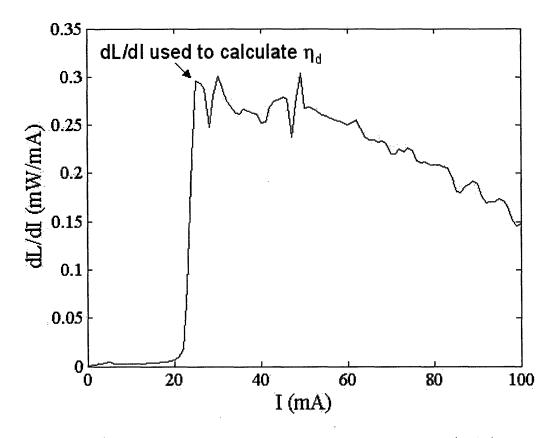

| 5-21 | dL/dI vs. I characteristic for a micro-cleaved ridge laser (MC6) mea-                                                                           |     |

|      | sured at a stage temperature of 20 $^{\circ}\mathrm{C}$ and under continuous-wave con-                                                          |     |

|      | ditions                                                                                                                                         | 164 |

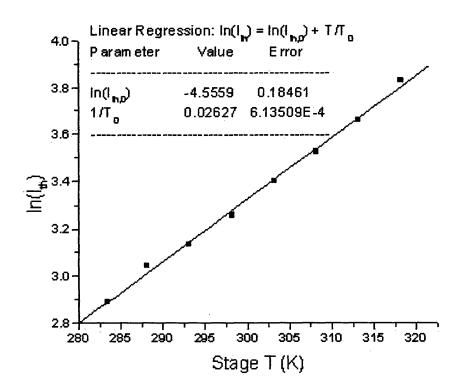

| 5-22 | $\ln(\text{Threshold current})$ as a function of stage temperature for a continuous-                                                            |     |

|      | wave tested micro-cleaved ridge laser (MC6)                                                                                                     | 165 |

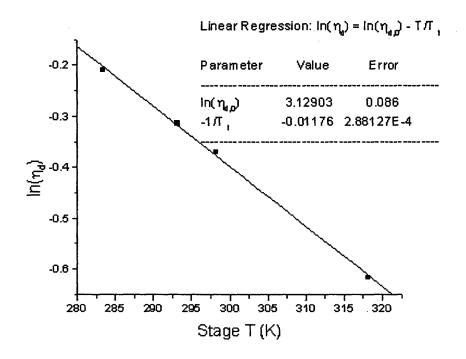

| 5-23 | $\ln(\text{differential efficiency})$ as a function of stage temperature for a micro-                                                           |     |

|      | cleaved ridge laser (MC6) tested under continuous-wave conditions. $% \left( {{\rm{AC6}}} \right)$ .                                            | 165 |

| 5-24 | Light output characteristic for micro-cleaved ridge laser (MC6) on sil-                                                                         |     |

|      | icon as a function of stage temperature and under pulse conditions. $% \left( {{{\left[ {{{\left[ {{\left[ {\left[ {{\left[ {{\left[ {{\left[ $ | 166 |

| 5-25 | Light output and current-voltage characteristics for a micro-cleaved                                                                            |     |

|      | ridge laser (MC6) measured at a stage temperature of 20 $^{\circ}\mathrm{C}$ and under                                                          |     |

|      | continuous-wave conditions.                                                                                                                     | 167 |

| 5-26 | IdV/dI vs. I for a micro-cleaved ridge laser (MC6) on silicon measured                                                                          |     |

|      | at a stage temperature of 20 $^{\circ}\mathrm{C}$ and under continuous-wave conditions.                                                         | 168 |

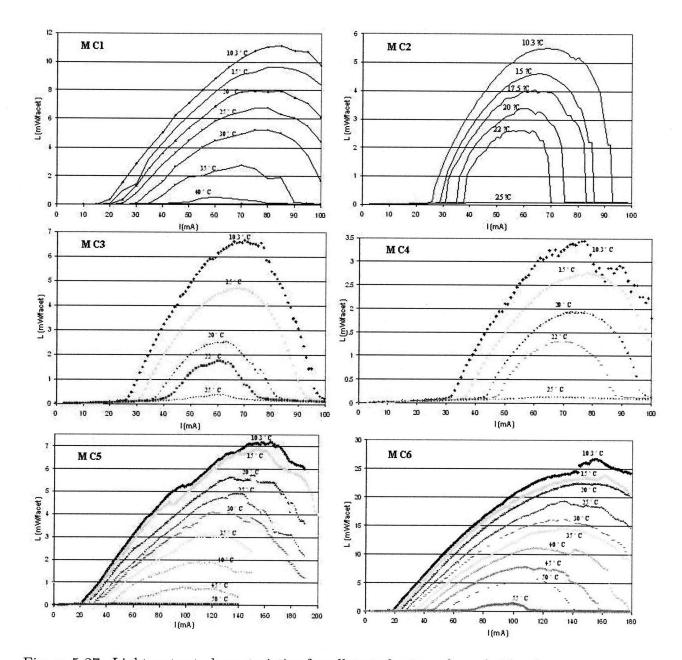

| 5-27 | Light output characteristics for all tested micro-cleaved ridge lasers                                                                          |     |

|      | as a function of stage temperature measured under continuous-wave                                                                               |     |

|      | conditions                                                                                                                                      | 170 |

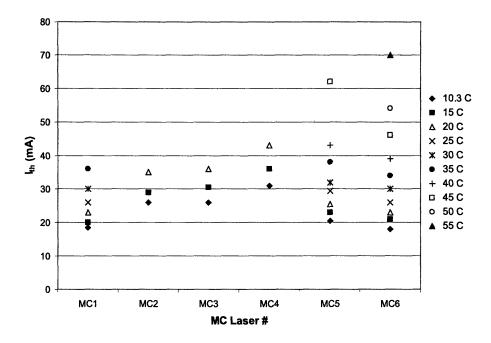

| 5-28 | Threshold current, $I_{th}$ , as a function of stage temperature extracted        |     |

|------|-----------------------------------------------------------------------------------|-----|

|      | from continuous-wave measurements of six micro-cleaved ridge lasers               |     |

|      | on silicon.                                                                       | 171 |

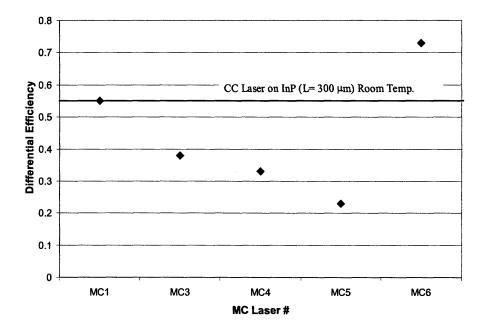

| 5-29 | Differential efficiency, $\eta_d$ , at a stage temperature of 20 °C extracted     |     |

|      | from continuous-wave measurements of micro-cleaved ridge lasers on                |     |

|      | silicon                                                                           | 171 |

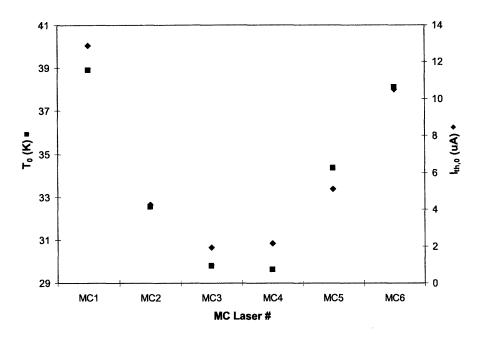

| 5-30 | Characteristic temperatures, $T_0$ , and and the 0 K threshold currents,          |     |

|      | $I_{th,0}$ , extracted from continuous-wave measurements of six micro-cleaved     |     |

|      | ridge lasers on silicon.                                                          | 172 |

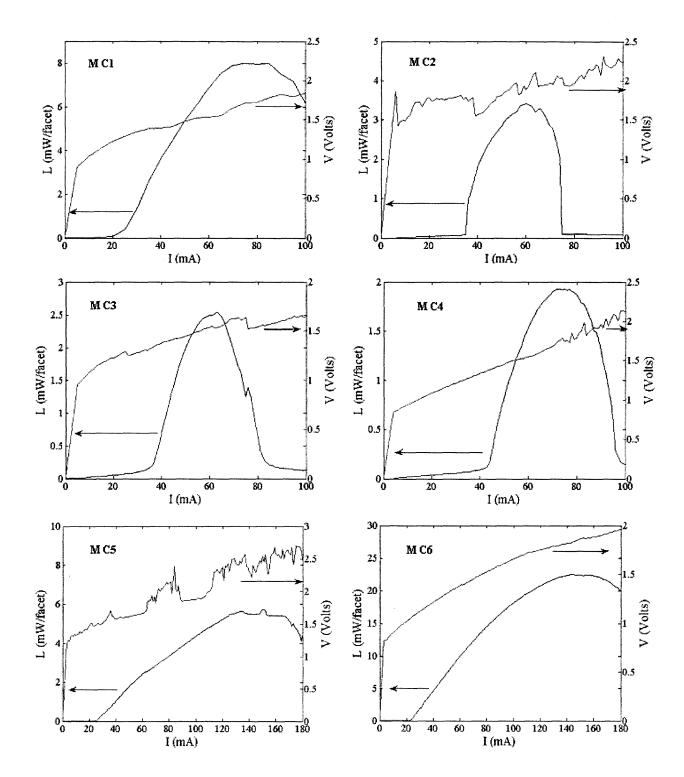

| 5-31 | Light output and current-voltage characteristics for all micro-cleaved            |     |

|      | ridge lasers measured at a stage temperature of 20 °C and under                   |     |

|      | continuous-wave conditions.                                                       | 173 |

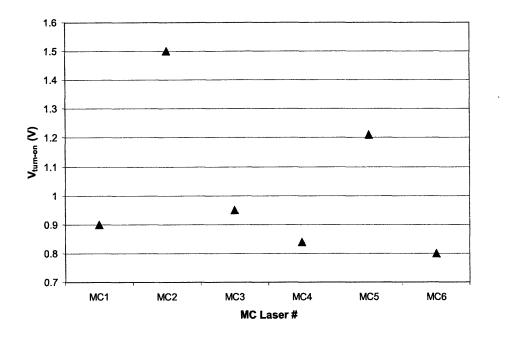

| 5-32 | Turn-on voltages for for all micro-cleaved ridge lasers measured at a             |     |

|      | stage temperature of 20 $^{\circ}\mathrm{C}$ and under continuous-wave conditions | 174 |

| 5-33 | Laser diode series resistance for for all micro-cleaved ridge lasers mea-         |     |

|      | sured at a stage temperature of 20 °C and under continuous-wave con-              |     |

|      | ditions                                                                           | 174 |

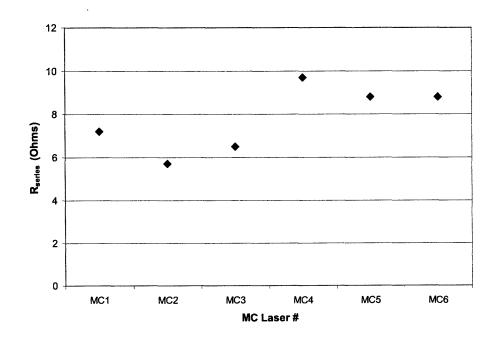

| 5-34 | Step height of ridge to planarization layer following the BCB etch-back           |     |

|      | process. Note that the data point taken at 2700 $\mu \mathrm{m}$ from the sample  |     |

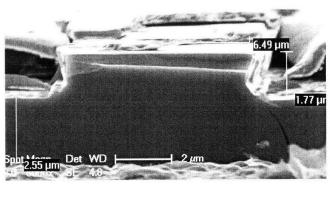

|      | center is 900 $\mu$ m from the sample edge                                        | 176 |

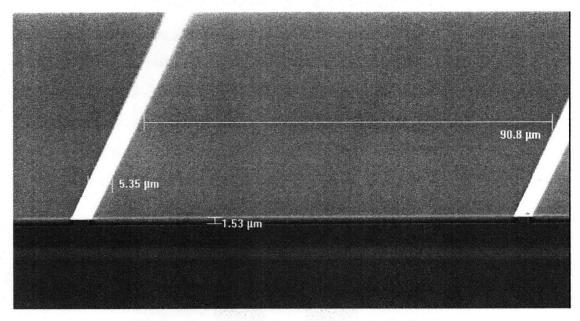

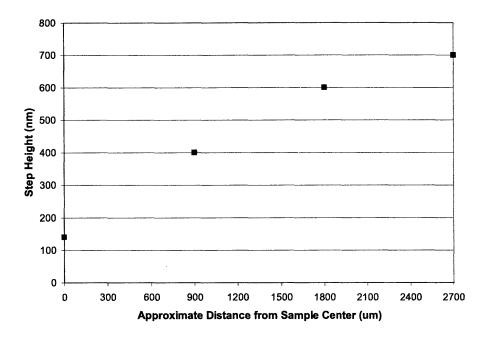

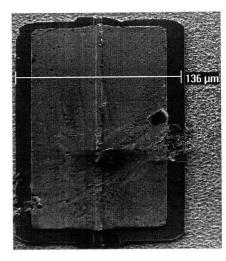

| 5-35 | Scanning electron micrographs (SEM) of the cross section of a ridge               |     |

|      | laser after the top large area contact formation process                          | 177 |

| 5-36 | SEMs of micro-cleaved ridge lasers on silicon (MC3, MC4)                          | 178 |

| 5-37 | SEMs of micro-cleaved ridge lasers on silicon (MC5, MC6)                          | 179 |

| 6-1  | Magnetically assisted statistical assembly technique                              | 182 |

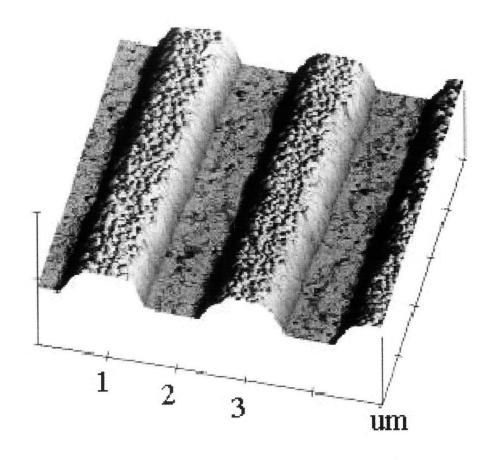

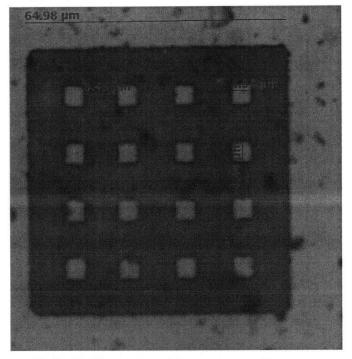

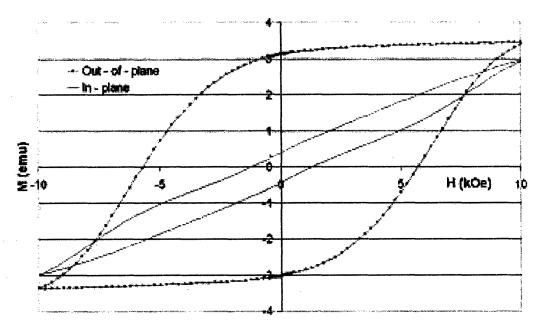

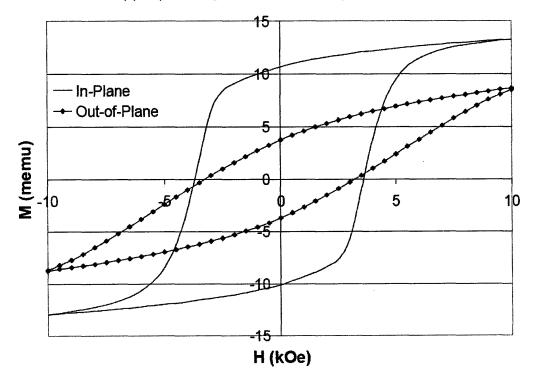

| 6-2  | Patterned hard magnetic films.                                                    | 185 |

| 6-3  | Magnetization vs. Applied Magnetic Field for patterned hard magnetic              |     |

| 0-0  | films.                                                                            | 186 |

|      | IIIIIIS                                                                           |     |

| 6-4                      | Schematic of the system under consideration for the magnetic force                                                                       |                          |

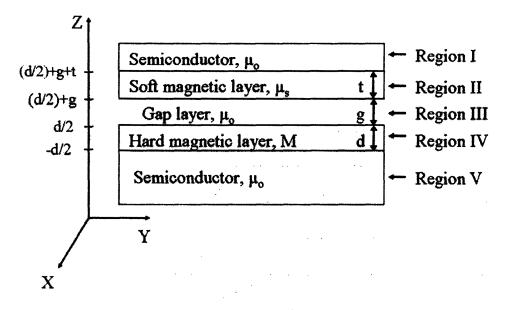

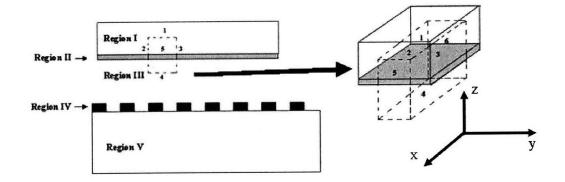

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

|                          | modeling[1]                                                                                                                              | 187                      |

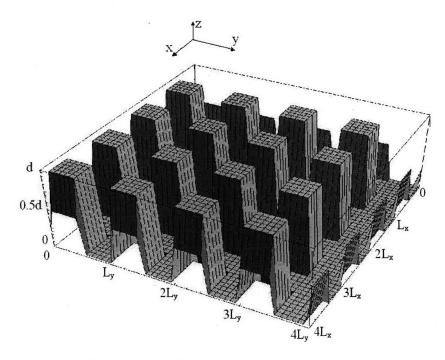

| 6-5                      | Graphical representations of the hard magnetic material patterns                                                                         | 189                      |

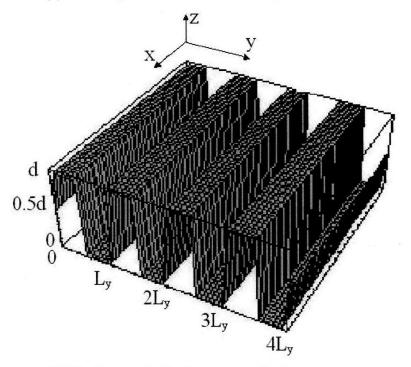

| 6-6                      | Schematic depicting the surface chosen to evaluate the force integral,                                                                   |                          |

|                          | where the six faces of this volume are labeled 1, 2, 3, 4, 5, and 6                                                                      | 192                      |

| 6-7                      | Magnetic retention forces for the various magnetization orientations                                                                     |                          |

|                          | and pattern geometries assuming $L_x = L_y = 5 \ \mu \text{m}, M_r = 1000 \ \text{emu}/cm^3$ ,                                           |                          |

|                          | $\mu_s = 50, d = t = 0.25 \ \mu m. \dots \dots$                                    | 195                      |

| 6-8                      | Dependence of the force expression on hard and soft magnetic film                                                                        |                          |

|                          | thickness.                                                                                                                               | 197                      |

| 6-9                      | Magnetic retention force for the array of stripes pattern with perpen-                                                                   |                          |

|                          | dicular anisotropy as a function of pattern period                                                                                       | 198                      |

|                          |                                                                                                                                          |                          |

| 7-1                      | Schematic detailing the comparative size of the Intel/UCSB Racetrack                                                                     |                          |

| 7-1                      | Schematic detailing the comparative size of the Intel/UCSB Racetrack laser and the MIT laser integrated with a dielectric waveguide[12]. | 204                      |

| 7-1                      | Schematic detailing the comparative size of the Intel/UCSB Racetrack laser and the MIT laser integrated with a dielectric waveguide[12]  | 204                      |

| 7-1<br>A-1               |                                                                                                                                          | 204<br>209               |

|                          | laser and the MIT laser integrated with a dielectric waveguide [12]                                                                      |                          |

| A-1                      | laser and the MIT laser integrated with a dielectric waveguide[12]                                                                       | 209                      |

| A-1<br>A-2               | laser and the MIT laser integrated with a dielectric waveguide[12]                                                                       | 209<br>210               |

| A-1<br>A-2<br>A-3        | laser and the MIT laser integrated with a dielectric waveguide[12]                                                                       | 209<br>210<br>211        |

| A-1<br>A-2<br>A-3<br>B-1 | laser and the MIT laser integrated with a dielectric waveguide[12]                                                                       | 209<br>210<br>211<br>214 |

## Chapter 1

# Motivation for Optoelectronic Integration

# 1.1 Introduction - Examples of Optoelectronic Products and their Impact

From the ways in which we communicate, to the ways our health is monitored, to the ways we are entertained, optoelectronic devices are becoming more pervasive in society. To provide the reader with some detail on the growing impact of optoelectronics on society, a couple of applications in the medical field and the field of communications strongly impacted by optoelectronic products will now be discussed.

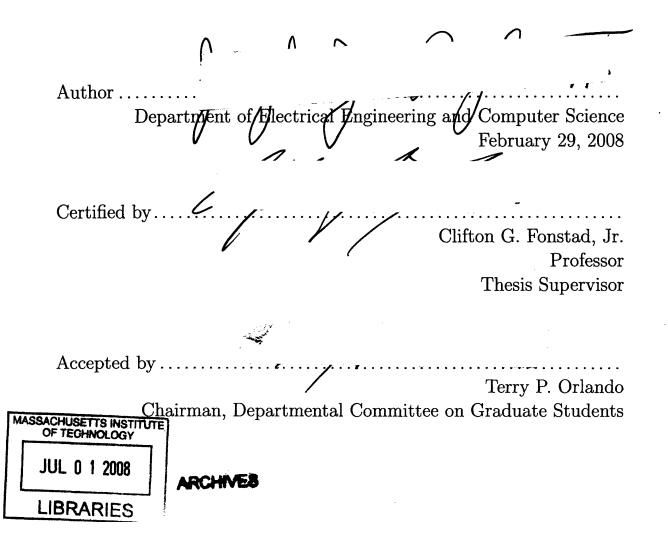

In the medical field, doctors can now non-invasively monitor the oxygen level in a patient's bloodstream by using an optoelectronic instrument, known as a pulse oximeter. Operationally, when this device is placed on a patient's finger, toe, or ear lobe, light emitting diodes (LEDs) shine light that is either transmitted through or is absorbed by the blood. On the opposite end of the emitter array, a photodetector array measures the light that is transmitted. The amount of light transmitted depends on the amount of oxygen present in the blood.<sup>1</sup> Taking only a matter of seconds, this

<sup>&</sup>lt;sup>1</sup>In its simplest form, the measurement utilizes two wavelengths of light, red (i.e., wavelength around 650 nm) and infrared (i.e., wavelength around 900 nm). Hemoglobin with significant oxygen content absorbs more at infrared wavelengths than at red wavelengths as is shown in Figure 1-1.

non-invasive measurement allows medical professionals to continuously monitor the oxygen level in a patient's bloodstream. This fast accurate measurement is vital to the health of the patient since oxygen deprivation can result in brain damage within a few minutes. Before the commercialization of these devices, detecting the amount of oxygen in the bloodstream was a time consuming (i.e., tens of minutes) and painfully invasive process.

Non-invasive blood glucose monitoring for diabetics is another application in the medical field in which researchers are working to commercialize optoelectronic products.<sup>2</sup> The impact that such a device could have is far reaching as several hundred million people suffering from diabetes are at present resigned to drawing blood several times a day to measure their blood glucose level[62].

Figure 1-1: a.) A typical pulse oximeter [53] b.) Absorption spectrum of fully oxygenated hemoglobin and non-oxygenated hemoglobin[32].

Although the impact of optoelectronic devices on the medical field is impressive, it is arguable that optoelectronics has had its most significant impact in the field of communications, especially in long distance communications. In particular, the long distance undersea telecommunications network, which includes the link between Europe and North America, demonstrates how the development of several optoelectronic devices can revolutionize a field.

$<sup>^{2}</sup>$ Several companies, including VeraLight, Inc., are working to create non-invasive blood glucose monitors using optoelectronic devices.

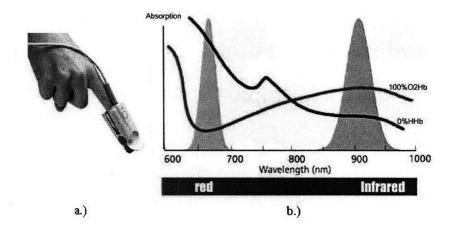

There was a time when the undersea communication networks consisted of long spans of electrical coaxial cable with intermittently spaced electrical signal regenerators. However, near the end of the 1970s, the practical capacity (i.e., bits of information transmitted per second) limits of the the electrical network began to be approached. The problem with the electrical undersea network, as is the potential problem with all electrical interconnect networks, was that electrical interconnects have several frequency dependent parasitic impedances (i.e., resistances, capacitances, and inductances) which can degrade the transmitted signal. Specifically, the transmission capability for an electrical interconnect is limited by either skin effect<sup>3</sup> loss as the signal transmission frequency is increased or resistive loss as the interconnect gets too long [67].