# A Formal Framework for Specification-Based Embedded Real-Time System Engineering

by

### Martin Ouimet

B.S.E., Princeton University (1998) S.M., Massachusetts Institute of Technology (2004)

Submitted to the Department of Aeronautics and Astronautics in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2008

| © Massachusetts Institute of Technology 2008. All rights reserved.              |

|---------------------------------------------------------------------------------|

| Author                                                                          |

| Department of Aeronautics and Astronautics                                      |

| May 23rd, 2008                                                                  |

| Certified by                                                                    |

| I. Kristina Lundqvist                                                           |

| Professor, Mälardalen University                                                |

| Thesis Advisor                                                                  |

| Certified by                                                                    |

| Professor, Massachusetts Institute of Technology                                |

| Doctoral Committee Chair                                                        |

| Accepted by                                                                     |

| Chairman, Department Committee on Graduate Students OF TECHNOLOGY  AUG 0 1 2008 |

**LIBRARIES**

| Certified by                                                                                   |

|------------------------------------------------------------------------------------------------|

| Nancy A. Lynch Professor, Massachusetts Institute of Technology Thesis Supervisor              |

| Certified by  Heidi C. Perry  Director, The Charles Stark Draper Laboratory  Thesis Supervisor |

| Certified by                                                                                   |

4

•

# A Formal Framework for Specification-Based Embedded Real-Time System Engineering

by

### Martin Ouimet

Submitted to the Department of Aeronautics and Astronautics on May 23rd, 2008, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

### Abstract

The increasing size and complexity of modern software-intensive systems present novel challenges when engineering high-integrity artifacts within aggressive budgetary constraints. Among these challenges, ensuring confidence in the engineered system, through validation and verification activities, represents the high cost item on many projects. The expensive nature of engineering high-integrity systems using traditional approaches can be partly attributed to the lack of analysis facilities during the early phases of the lifecycle, causing the validation and verification activities to begin too late in the engineering lifecycle. Other challenges include the management of complexity, opportunities for reuse without compromising confidence, and the ability to trace system features across lifecycle phases. The use of models as a specification mechanism provides an approach to mitigate complexity through abstraction. Furthermore, if the specification approach has formal underpinnings, the use of models can be leveraged to automate engineering activities such as formal analysis and test case generation. The research presented in this thesis proposes an engineering framework which addresses the high cost of validation and verification activities through specification-based system engineering. More specifically, the framework provides an integrated approach to embedded real-time system engineering which incorporates specification, simulation, formal verification, and test-case generation. The framework aggregates the state-of-the-art in individual software engineering disciplines to provide an end-to-end approach to embedded real-time system engineering. The key aspects of the framework include:

• A novel specification language, the Timed Abstract State Machine (TASM) language, which extends the theory of Abstract State Machines (ASM). The TASM language is a literate formal specification language which can be applied and multiple levels of abstraction and which can express the three key aspects of embedded real-time systems – function, time, and resources.

• Automated verification capabilities achieved through the integration of mature analysis engines, namely the Uppaal tool suite and the SAT4J SAT solver. The verification capabilities provided by the framework include completeness and consistency verification, model checking, execution time analysis, and resource consumption analysis.

• Bi-directional traceability of model features across levels of abstraction and lifecycle phases. Traceability is achieved syntactically through archetypical refinement types; each refinement type provides correctness criteria, which, if met, guarantee semantic integrity through the refinement.

Automated test case generation capabilities for unit testing, integration testing, and regression testing. Unit test cases are generated to achieve TASM specification coverage through the rule coverage criterion. Integration test case generation is achieved through the hierarchical composition of unit test cases. Regression test case generation is achieved by leveraging the bi-directional traceability of model features.

The framework is implemented into an integrated tool suite, the TASM toolset, which incorporates the Uppaal tool suite and the SAT4J SAT solver. The toolset and framework are evaluated through experimentation on three industrial case studies – an automated manufacturing system, a "drive-by-wire" system used at a major automotive manufacturer, and a scripting environment used on the International Space Station.

Thesis Supervisor: I. Kristina Lundqvist Title: Professor, Mälardalen University

Thesis Supervisor: R. John Hansman

Title: Professor, Massachusetts Institute of Technology

Thesis Supervisor: Nancy A. Lynch

Title: Professor, Massachusetts Institute of Technology

Thesis Supervisor: Heidi C. Perry

Title: Director, The Charles Stark Draper Laboratory

Thesis Supervisor: Nicholas Roy

Title: Professor, Massachusetts Institute of Technology

## Acknowledgments

First and foremost, I would like to thank my advisor and thesis supervisor, Professor Kristina Lundqvist, for providing me with the guidance and with all the resources that I needed to succeed. I have a tremendous amount of admiration and respect for Professor Lundqvist as an intellectual leader, as a mentor, and as a friend. I would also like to thank Professor John Hansman for accepting the role of doctoral committee chair toward the end of my studies. Other members of my committee also deserve praise - Professor Nancy Lynch, Professor Nicholas Roy, and Heidi Perry - for taking time out of their busy schedules to guide me through the PhD process. Your time and feedback was invaluable. Professor Daniel Jackson also deserves mention due to his involvement in the general examination process.

On a research note, I would like to acknowledge JK Srinivasan, Professor Mikael Nolin, Professor Egon Börger, Gustaff Naeser, Yuri Gurevich, David Wang, Guillaume Berteau, and Matthieu Quenot, who have contributed directly and indirectly to the research included in this thesis. Furthermore, the Charles Stark Draper Laboratory deserves a special mention, since it has provided the funding for the project. Special thanks go out to Lauren Kessler and Heidi Perry who were instrumental to make this project a reality. I would also like to recognize Professor Charles Coleman for giving me the opportunity to explore various areas and for encouraging me to satisfy my intellectual curiosity.

On a personal note, I would like to give special consideration to my dear friends, who have withstood my intermittent emotional outbursts and my constant state of flux. Nicolas Dulac deserves special mention for being such a great friend. Michel Duranceau was also there when I needed him the most, even while 350 miles away. Étienne Parent was an awesome roommate and a true friend. Bart East and Jason Smyczek remained supportive, even though I wasn't always keeping in touch. Thank you to the East family and to the Duranceau family for continuing to be wonderful people. Yves Boussemart was always a source of positive attitude and occasional memorable incidents. Thank you to other friends - MV, TM, MAC, CG, HH, JL, LO,

NP, DW, CL, EP, JP, CL, MF, ... The MIT hockey team provided much needed entertainment and good times during my first years at MIT. The music crew also played an important role in my intellectual and emotional development - Rusty Scott, Victoria Chang, Elaine Kwon, Mark Kroll, Curtis Hughes, Mark Harvey, Tony Savarino, and Yoko Miwa. I would also like to recognize the wonderful ladies of the Boston area and beyond who, on various occasions, provided much needed emotional support and fantastic companionship to discover the wonderful nightlife of Boston and beyond. At the forefront, Wendy and Stella greatly contributed to my general well-being. WX, SJ, JQ, NT, MT, YJH, SSC, JC, AC, RC, V, LR, SD, CY, MM, MN, ... thanks for putting up with me, you are all awesome. Another thank you goes out to the fantasy baseball crew of New Jersey and Laval and to the fantasy hockey crowd of Montréal. The "Semi-Pro" crew, led by my uncle Michel, also deserves a wink.

Finally, a special "thank you" goes to my family who, at times, seemed more worried than my advisor about whether or not I would complete the PhD program. I have always maintained that if I could have half the heart of my father and half the courage of my mother, I would be extremely proud of who I am. Hopefully, I will get there some day. Thank you Gérard and Denise, you mean more to me than I can convey in a few lines. Thank you also to my brother, Patrick, my sister-in-law Annie, and their two sons Félix and Renaud. Your continuous support and distractions continue to be indispensable. Thank you also to my cousins Daniel and Richard. I promise that some day we will finally make it to Fenway Park. I am blessed to have a large extended family who is always radiant. Since they are too numerous to mention, I will not single them out individually; but kisses and firm handshakes go out to all the aunts, uncles, and cousins on both sides of my family.

Dear mom and dad, although I will probably never stop being a student in the figurative sense, I am convinced that the next time an acquaintance asks you what your younger son does for a living, you will be extremely happy that you will no longer have to answer "student". Warm regards to all who helped make this a reality. With love,

Martin

### Remerciements

D'abord et avant out, j'aimerais remercier mon superviseur et ma directrice de thèse, le Professeur Kristina Lundqvist, qui m'a guidé dans ma recherche et qui m'a fourni toutes les ressources nécessaires pour assurer mon succès. J'ai énormément d'admiration et de respect pour le Professeur Lundqvist en tant que modèle intellectuel, en tant que conseillère, and en tant qu'amie. Je voudrais aussi remercier le Professeur John Hansman, qui a accepté le rôle de chaire du comité d'évaluation durant la fin de mes études. Je me dois aussi de mentionner les autres membres de mon comité le Professeur Nancy Lynch, le Professeur Nicholas Roy, et Heidi Perry. Merci d'avoir pris le temps et d'avoir eu la patience pour me guider à bon port. Vos efforts et votre attention ont été grandement appréciés. Le Professeur Daniel Jackson mérite également mes remerciements dû à sa participation à l'examen général.

Du côté de la recherche, je voudrais créditer JK Srinivasan, le Professeur Mikael Nolin, le Professeur Egon Börger, Gustaff Naeser, Yuri Gurevich, David Wang, Guillaume Berteau, et Mathieu Quenot, qui ont tous contribué a la recherche inclue dans cette thèse. De plus, le Charles Stark Draper Laboratory obtient une mention spéciale, puisqu'il a subventionné ma recherche au cours de mes études au doctorat. Un gros merci à Lauren Kessler et à Heidi Perry pour leur dévouement. Je voudrais aussi remercier le Professeur Charles Coleman qui m'a donné l'opportunité d'explorer mes intérêts à ma guise et qui m'a encouragé à satisfaire ma curiosité intellectuelle.

Du côté personnel, j'aimerais offrir ma profonde gratitude a mes chers amis, qui, à un moment ou un autre, ont tous dû subir les répercussions de mes sautes d'humeur et de mon incertitude constante. Nicolas Dulac a été de loin mon meilleur ami et compagnon spirituel à Boston. Même s'il était à 350 miles de Boston, mon meilleur ami de longue date, Michel Duranceau, a toujours su être là pour me remonter le moral. Étienne Parent a été un ami exemplaire avec qui j'ai pu chialer plus souvent qu'à mon tour. Bart East et Jason Smyczek ont su apporter leur support, même si je n'ai pas toujours été aussi communicatif que j'aurais dû l'être. Un gros merci à la famille East et à la famille Duranceau qui continuent d'être des gens extrêmement chaleureux.

Yves Boussemart a toujours été une source d'énergie positive et d'occasionnels incidents mémorables. Merci aux autres amis - MV, TM, MAC, CG, HH, JL, LO, NP, CL², EP, JP, DMW, ... J'ai également découvert la musique lors de mon séjour aux études - Rusty Scott, Victoria Chang, Elaine Kwon, Mark Kroll, Curtis Hughes, Mark Harvey, Tony Savarino, et Yoko Miwa - merci d'avoir été une source d'inspiration, merci de votre enseignement, et merci de votre encouragement. Je voudrais aussi mentionner ces divines demoiselles de Boston et d'ailleurs, qui ont su enflammer plus d'une soirée, tout en apportant un support émotionnel indispensable et une complicité remarquable, et avec lesquelles j'ai pu découvrir différents restos et bistrots de Boston et d'ailleurs. En tête de liste, Wendy et Stella ont grandement contribué a mon bien être. WX, SJ, JQ, NT, MT, YJH, SSC, JC, AC, RC, V, LR, SD, CY, MM, MN, ... merci de m'avoir toléré, vous êtes sublimes. Je tiens aussi à remercier la gang du pool de baseball du New Jersey et les gangs des pools de hockey et de baseball de Laval. Clin d'oeil aussi a la gang du "Semi-Pro", avec mon oncle Michel en tête.

Finalement, j'offre un remerciement spécial a ma famille, qui m'a supporté moralement et financièrement tout au long de mes études. J'ai toujours cru que si j'avais la moitié du coeur de mon père et la moitié du courage de ma mère, je serais très fier de l'homme que je suis devenu. J'espère y arriver un jour. Merci Gérard et Denise, vous êtes plus importants pour moi que je ne puisse le témoigner en quelques lignes. Merci aussi à mon frère Patrick, à ma belle-soeur Annie, et à mes deux neveux Félix et Renaud. Merci aussi á mes cousins Daniel et Richard. Je vous promets qu'on ira au Fenway Park éventuellement. Je me compte très chanceux d'être membre d'une grande famille étendue. Malheureusement, ils sont trop nombreux pour être nommés individuellement; tout de même, j'offre baisers et poignées de mains viriles à toutes mes tantes, à tous mes oncles, et à tous mes cousins et cousines. Chers môman et pôpa, même si je ne cesserai probablement jamais d'être un étudiant au sens figuré, je suis convaincu que la prochaine fois où une connaissance vous demandera ce que votre plus jeune fils fait dans la vie, vous serez très fiers de ne plus avoir à répondre "étudiant". Merci à tous ceux et celles qui ont contribué à mon succès. Avec amour,

Martin

# Contents

| 1 Introduction |     |                                                                 |    |  |  |

|----------------|-----|-----------------------------------------------------------------|----|--|--|

|                | 1.1 | Motivations                                                     | 27 |  |  |

|                | 1.2 | Thesis Contributions                                            | 28 |  |  |

|                | 1.3 | Relevant Publications                                           | 29 |  |  |

|                | 1.4 | Thesis Outline                                                  | 30 |  |  |

|                | 1.5 | Chapter Structure                                               | 33 |  |  |

|                | 1.6 | Notational Conventions                                          | 34 |  |  |

|                | 1.7 | Segue into Chapter 2                                            | 34 |  |  |

| 2              | Bac | kground Information                                             | 35 |  |  |

|                | 2.1 | Real-Time Embedded Systems                                      | 35 |  |  |

|                |     | 2.1.1 The Nature of Time in Real-Time Systems                   | 39 |  |  |

|                | 2.2 | Systems Engineering                                             | 41 |  |  |

|                | 2.3 | Software Engineering                                            | 42 |  |  |

|                | 2.4 | Formal Methods                                                  | 45 |  |  |

|                | 2.5 | Model-Based Software Engineering                                | 46 |  |  |

|                | 2.6 | Modeling Languages                                              | 48 |  |  |

|                |     | 2.6.1 The Time Paradox: Incorporating Time in High Level Models | 50 |  |  |

|                | 2.7 | Analysis Engines                                                | 54 |  |  |

|                |     | 2.7.1 Model Checkers                                            | 54 |  |  |

|                |     | 2.7.2 <i>SAT</i> Solvers                                        | 56 |  |  |

|                | 2.8 | Case Studies                                                    | 57 |  |  |

|                |     | 2.8.1 The Production Cell                                       | 58 |  |  |

|   |      | 2.8.2  | Electronic Throttle Controller                       | 65  |

|---|------|--------|------------------------------------------------------|-----|

|   |      | 2.8.3  | Timeliner Script Executor                            | 70  |

|   |      | 2.8.4  | Motivations for the Case Studies                     | 74  |

|   | 2.9  | Segue  | into Chapter 3                                       | 75  |

| 3 | Frai | mewor  | k Overview                                           | 77  |

|   | 3.1  | Introd | uction                                               | 77  |

|   | 3.2  | Relate | d Work                                               | 78  |

|   | 3.3  | Capab  | vilities                                             | 81  |

|   |      | 3.3.1  | Modeling and Simulation                              | 82  |

|   |      | 3.3.2  | Static Analysis                                      | 83  |

|   |      | 3.3.3  | Bi-Directional Traceability                          | 84  |

|   |      | 3.3.4  | Test Case Generation                                 | 85  |

|   | 3.4  | Tool A | Architecture                                         | 86  |

|   |      | 3.4.1  | Front-End Components                                 | 87  |

|   |      | 3.4.2  | Back-End Components                                  | 89  |

|   |      | 3.4.3  | 3rd Party Engines                                    | 90  |

|   | 3.5  | Segue  | into Chapter 4                                       | 90  |

| 4 | The  | Time   | d Abstract State Machine Specification Language      | 93  |

|   | 4.1  | Relate | ed Work                                              | 93  |

|   | ,    | 4.1.1  | Usability of Specification Languages                 | 94  |

|   |      | 4.1.2  | Abstract State Machines                              | 95  |

|   |      | 4.1.3  | The TASM Language                                    | 101 |

|   |      | 4.1.4  | Other Specification Formalisms                       | 102 |

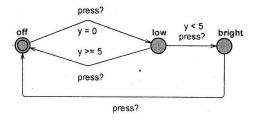

|   |      | 4.1.5  | Light Switch Example                                 | 104 |

|   | 4.2  | The T  | Fimed Abstract State Machine (TASM) Language: Syntax | 106 |

|   |      | 4.2.1  | Basic ASM Specification                              | 106 |

|   |      | 4.2.2  | Light Switch Example Version 1                       | 109 |

|   |      | 4.2.3  | Time                                                 | 111 |

|   |      | 4.2.4  | Resources                                            | 112 |

|   |      | 4.2.5    | Light Switch Example Version 2                         | 113 |

|---|------|----------|--------------------------------------------------------|-----|

|   |      | 4.2.6    | Hierarchical Composition                               | 113 |

|   |      | 4.2.7    | Light Switch Example Version 3                         | 116 |

|   |      | 4.2.8    | Parallel Composition                                   | 117 |

|   |      | 4.2.9    | Light Switch Example Version 4                         | 118 |

|   | 4.3  | The T    | imed Abstract State Machine (TASM) Language: Semantics | 118 |

|   |      | 4.3.1    | Update Set                                             | 121 |

|   |      | 4.3.2    | Time                                                   | 121 |

|   |      | 4.3.3    | Resources                                              | 122 |

|   |      | 4.3.4    | Light Switch Example Version 2 Revisited               | 124 |

|   |      | 4.3.5    | Hierarchical Composition                               | 125 |

|   |      | 4.3.6    | Light Switch Example Version 3 Revisited               | 129 |

|   |      | 4.3.7    | Hierarchical Composition and Expressivity              | 131 |

|   |      | 4.3.8    | Parallel Composition                                   | 135 |

|   |      | 4.3.9    | Light Switch Example Version 4 Revisited               | 139 |

|   |      | 4.3.10   | Summary and Other Extensions                           | 141 |

|   | 4.4  | Relation | on to Timed ASM                                        | 146 |

|   | 4.5  | Segue    | into Chapter 5                                         | 149 |

| 5 | Stat | tic Ana  | alysis                                                 | 151 |

|   | 5.1  | Functi   | onal Analysis: Completeness and Consistency            | 151 |

|   |      | 5.1.1    | Related Work                                           | 153 |

|   |      | 5.1.2    | Completeness                                           | 154 |

|   |      | 5.1.3    | Consistency                                            | 157 |

|   |      | 5.1.4    | Mapping to SAT                                         | 160 |

|   |      | 5.1.5    | Example                                                | 161 |

|   | 5.2  | Functi   | onal Analysis: Model Checking                          | 165 |

|   |      | 5.2.1    | Mapping to UPPAAL                                      | 166 |

|   |      | 5.2.2    | Example                                                | 167 |

|   | 5.3  | Execu    | tion Time Analysis                                     | 168 |

|   |            | 5.3.1   | Related Work                    | 170 |

|---|------------|---------|---------------------------------|-----|

|   |            | 5.3.2   | Iterative Bounded Liveness      | 171 |

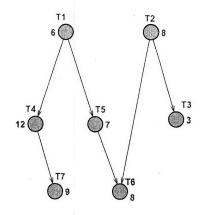

|   |            | 5.3.3   | Example: The Scheduling Problem | 177 |

|   | 5.4        | Resou   | rce Consumption Analysis        | 182 |

|   |            | 5.4.1   | Related Work                    | 182 |

|   |            | 5.4.2   | Approach                        | 183 |

|   |            | 5.4.3   | Example                         | 186 |

|   | 5.5        | Segue   | into Chapter 6                  | 187 |

| 6 | Bi₋I       | Directi | onal Traceability               | 189 |

| U | 6.1        |         | ed Work                         |     |

|   | 0.1        | 6.1.1   | Syntactic Change Management     |     |

|   |            | 6.1.2   | •                               |     |

|   | 6.2        |         | Refinement Theory               |     |

|   | 0.2        | 6.2.1   | Types of Definements            |     |

|   |            | 6.2.2   | Types of Refinements            |     |

|   | <i>C</i> 0 |         | Correctness Criteria            |     |

|   | 6.3        |         | ple                             |     |

|   | 6.4        | Segue   | into Chapter 7                  | 220 |

| 7 | Tes        | t Case  | Generation                      | 221 |

|   | 7.1        | Relate  | ed Work                         | 221 |

|   |            | 7.1.1   | Coverage Criteria               | 223 |

|   |            | 7.1.2   | Abstract State Machines         | 224 |

|   | 7.2        | Test (  | Case Generation Concepts        | 224 |

|   |            | 7.2.1   | Definitions                     | 225 |

|   |            | 7.2.2   | Operations on Templates         | 227 |

|   |            | 7.2.3   | Machines and Test Suites        | 230 |

|   | 7.3        | Unit '  | Test Case Generation            | 231 |

|   |            | 7.3.1   | Complexity Analysis             | 233 |

|   |            | 7.3.2   | Example                         | 234 |

|   | 7.4        | Integr  | ration Test Case Generation     | 235 |

|   |     | 7.4.1  | Hierarchical Composition            |

|---|-----|--------|-------------------------------------|

|   |     | 7.4.2  | Complexity Analysis                 |

|   |     | 7.4.3  | Example                             |

|   | 7.5 | Comp   | lete Test Case Generation Algorithm |

|   |     | 7.5.1  | Test Sequences                      |

|   | 7.6 | Regres | ssion Test Case Generation          |

|   |     | 7.6.1  | Refinement Types                    |

|   |     | 7.6.2  | Test Case Execution                 |

|   |     | 7.6.3  | Complexity Analysis                 |

|   |     | 7.6.4  | Example                             |

|   | 7.7 | Segue  | into Chapter 8                      |

| 8 | Cas | e Stud | lies 257                            |

|   | 8.1 | Produ  | ction Cell                          |

|   |     | 8.1.1  | Model                               |

|   |     | 8.1.2  | Functional Analysis                 |

|   |     | 8.1.3  | Execution Time Analysis             |

|   | •   | 8.1.4  | Resource Usage Analysis             |

|   |     | 8.1.5  | Test Case Generation                |

|   |     | 8.1.6  | Discussion                          |

|   | 8.2 | Electr | onic Throttle Controller:           |

|   |     | High I | Level Model                         |

|   |     | 8.2.1  | Model                               |

|   |     | 8.2.2  | Functional Analysis                 |

|   |     | 8.2.3  | Test Case Generation                |

|   |     | 8.2.4  | Discussion                          |

|   | 8.3 | Electr | onic Throttle Controller:           |

|   |     | Taskir | ng Model                            |

|   |     | 8.3.1  | Model                               |

|   |     | 8.3.2  | Functional Analysis                 |

|   |     | 8.3.3   | Execution Time Analysis       | 311 |

|---|-----|---------|-------------------------------|-----|

|   |     | 8.3.4   | Test Case Generation          | 312 |

|   |     | 8.3.5   | Discussion                    | 312 |

|   | 8.4 | Electro | onic Throttle Controller:     |     |

|   |     | Low L   | evel Model                    | 314 |

|   |     | 8.4.1   | Model                         | 315 |

|   |     | 8.4.2   | Traceability                  | 325 |

|   |     | 8.4.3   | Functional Analysis           | 328 |

|   |     | 8.4.4   | Execution Time Analysis       | 332 |

|   |     | 8.4.5   | Resource Consumption Analysis | 335 |

|   |     | 8.4.6   | Test Case Generation          | 337 |

|   |     | 8.4.7   | Discussion                    | 339 |

|   | 8.5 | The T   | 'imeliner Script Executor:    |     |

|   |     | Plant   | Control System                | 341 |

|   |     | 8.5.1   | Model                         | 343 |

|   |     | 8.5.2   | Functional Analysis           | 355 |

|   |     | 8.5.3   | Execution Time Analysis       | 358 |

|   |     | 8.5.4   | Test Case Generation          | 361 |

|   |     | 8.5.5   | Discussion                    | 362 |

|   | 8.6 | Segue   | into Chapter 9                | 363 |

| _ | ~   |         |                               |     |

| 9 |     | clusio  |                               | 365 |

|   | 9.1 |         | •                             | 365 |

|   | 9.2 |         |                               | 368 |

|   |     | 9.2.1   | 8 8                           | 368 |

|   |     | 9.2.2   | <b>V</b>                      | 370 |

|   |     | 9.2.3   |                               | 371 |

|   |     | 9.2.4   |                               | 372 |

|   |     | 9.2.5   | y .                           | 373 |

|   |     | 9.2.6   | Overall Limitations           | 375 |

|   |     | 9.2.7  | Lessons Learned                     | 376 |

|---|-----|--------|-------------------------------------|-----|

|   | 9.3 | Oppor  | rtunities for Future Research       | 377 |

|   |     | 9.3.1  | Language Extensions                 | 377 |

|   |     | 9.3.2  | Framework Features                  | 378 |

|   |     | 9.3.3  | Analysis Engines                    | 379 |

|   | 9.4 | Closin | g Thoughts                          | 382 |

|   | 9.5 | Segue  | into the Appendices                 | 382 |

| A | TAS | SM La  | nguage Reference                    | 383 |

|   | A.1 | TASM   | I Objects                           | 383 |

|   |     | A.1.1  | Specification                       | 383 |

|   |     | A.1.2  | Project                             | 384 |

|   |     | A.1.3  | Environment                         | 384 |

|   |     | A.1.4  | Main Machine Template               | 384 |

|   |     | A.1.5  | Function Machine                    | 385 |

|   |     | A.1.6  | Sub Machine                         | 385 |

|   |     | A.1.7  | Configuration                       | 386 |

|   | A.2 | Syntax | x                                   | 386 |

|   |     | A.2.1  | Notational Conventions              | 386 |

|   |     | A.2.2  | Names                               | 387 |

|   |     | A.2.3  | Types                               | 387 |

|   |     | A.2.4  | Arithmetic Operators                | 389 |

|   |     | A.2.5  | Logical Operators                   | 390 |

|   |     | A.2.6  | Context-Free Grammar                | 391 |

|   | A.3 | Seman  | tics                                | 400 |

|   |     | A.3.1  | Operator Precedence                 | 401 |

|   |     | A.3.2  | Calling Convention                  | 401 |

|   |     | A.3.3  | Types                               | 403 |

|   |     | A.3.4  | Relation to Abstract State Machines | 403 |

|   |     | A.3.5  | Sugaring/Desugaring                 | 404 |

|              |      | A.3.6   | Resource definitions                       | 404 |

|--------------|------|---------|--------------------------------------------|-----|

|              |      | A.3.7   | Type definitions                           | 404 |

|              |      | A.3.8   | Variables                                  | 405 |

|              |      | A.3.9   | Rules                                      | 405 |

|              |      | A.3.10  | Execution Semantics                        | 407 |

| В            | Tran | nslatin | g TASM Models to $SAT$                     | 409 |

|              | B.1  | Prelim  | inaries                                    | 409 |

|              | B.2  | Transl  | ation Algorithm                            | 410 |

|              |      | B.2.1   | Function Machines                          | 410 |

|              |      | B.2.2   | Boolean and User-Defined Datatypes         | 411 |

|              |      | B.2.3   | Integer Datatypes                          | 414 |

|              |      | B.2.4   | Constraints with Symbolic Right-Hand Sides | 417 |

|              |      | B.2.5   | Complete Translation Algorithm             | 417 |

|              | В.3  | Analys  | sis                                        | 418 |

|              |      | B.3.1   | Limitations                                | 418 |

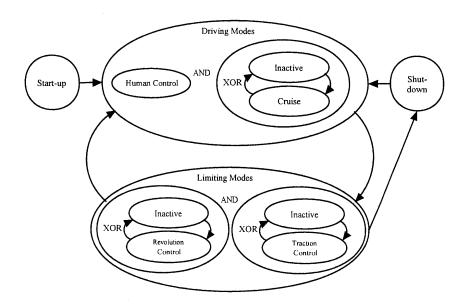

|              |      | B.3.2   | Complexity Analysis                        | 419 |

|              |      | B.3.3   | Intractability                             | 420 |

| $\mathbf{C}$ | Trai | nslatin | g TASM Models to Uppaal 's Timed Automata  | 423 |

|              | C.1  | Prelim  | ninaries                                   | 423 |

|              | C.2  | Transl  | ation Algorithm                            | 425 |

|              |      | C.2.1   | Variables and Datatypes                    | 425 |

|              |      | C.2.2   | Machines and Rules                         | 426 |

|              |      | C.2.3   | Complete Translation Algorithm             | 430 |

|              | C.3  | Exam    | ple                                        | 431 |

| D            | Pro  | ductio  | n Cell TASM Model                          | 435 |

|              | D.1  | Enviro  | onment                                     | 437 |

|              | D.2  | Main    | Machines                                   | 439 |

|              | DЗ   | Funct   | ion Machines                               | 444 |

|              | D.4  | Sub M   | Iachines                        | 445 |

|--------------|------|---------|---------------------------------|-----|

| $\mathbf{E}$ | Elec | ctronic | Throttle Controller TASM Model  | 457 |

|              | E.1  | High I  | Level Model                     | 457 |

|              |      | E.1.1   | Environment                     | 459 |

|              |      | E.1.2   | Main Machines                   | 461 |

|              |      | E.1.3   | Function Machines               | 466 |

|              |      | E.1.4   | Sub Machines                    | 470 |

|              | E.2  | Taskin  | ng Model                        | 475 |

|              |      | E.2.1   | Environment                     | 476 |

|              |      | E.2.2   | Main Machines                   | 477 |

|              |      | E.2.3   | Function Machines               | 480 |

|              |      | E.2.4   | Sub Machines                    | 481 |

|              | E.3  | Low L   | evel Model                      | 486 |

|              |      | E.3.1   | Environment                     | 488 |

|              |      | E.3.2   | Main Machines                   | 491 |

|              |      | E.3.3   | Function Machines               | 497 |

|              |      | E.3.4   | Sub Machines                    | 499 |

| $\mathbf{F}$ | Tim  | eliner  | Plant Control System TASM Model | 501 |

|              | F.1  | Enviro  | onment                          | 503 |

|              | F.2  | Main 1  | Machines                        | 505 |

|              | F.3  | Functi  | on Machines                     | 509 |

|              | F1   | Sub M   | Jachines                        | 500 |

# List of Figures

| 2-1  | High level view of a mostly periodic reactive real-time system | 37  |

|------|----------------------------------------------------------------|-----|

| 2-2  | Delay in system responding to an event of interest             | 38  |

| 2-3  | Systems engineering process [19]                               | 42  |

| 2-4  | V software lifecycle model [242]                               | 44  |

| 2-5  | Timed automaton describing the behavior of a lamp [24]         | 49  |

| 2-6  | Sample task graph                                              | 51  |

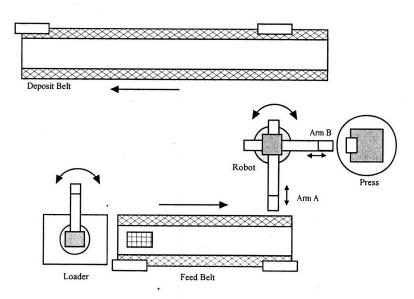

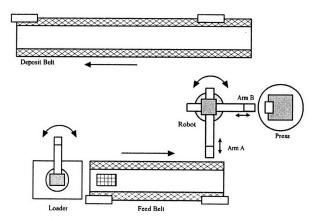

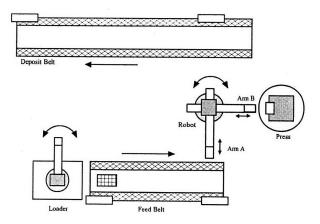

| 2-7  | Top view of the production cell                                | 59  |

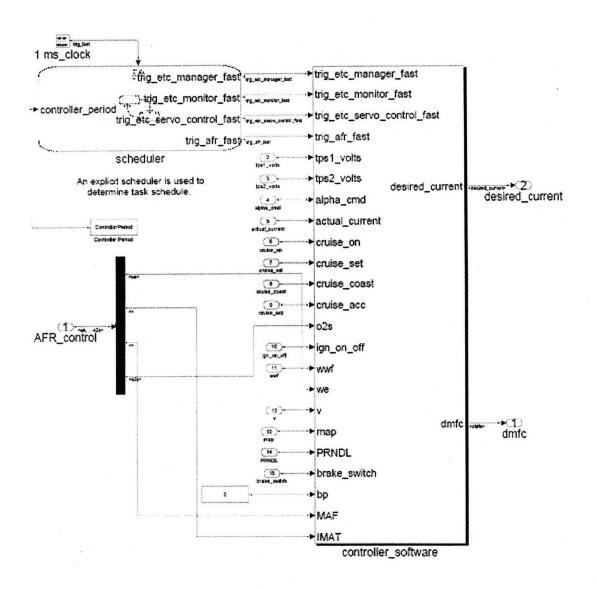

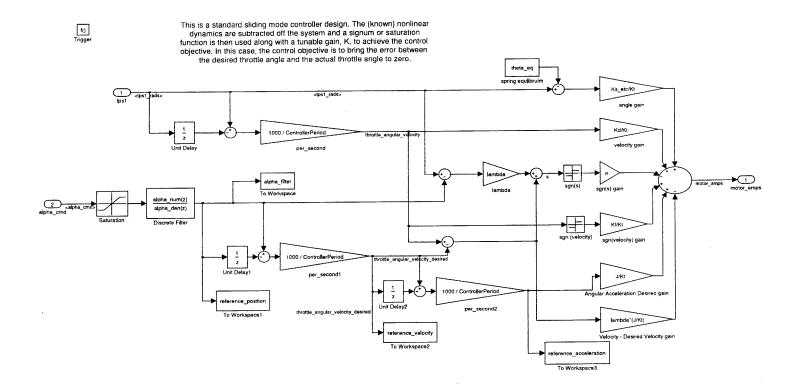

| 2-8  | High level Simulink model of the ETC                           | 67  |

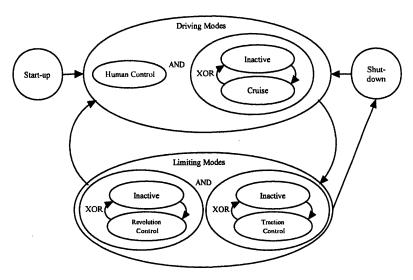

| 2-9  | ETC modes                                                      | 68  |

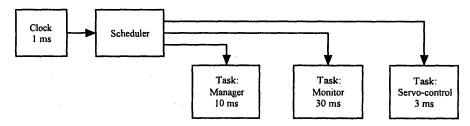

| 2-10 | ETC tasks and scheduler                                        | 69  |

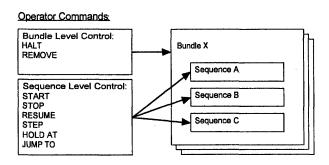

| 2-11 | Timeliner script organization [61]                             | 72  |

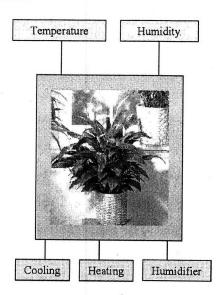

| 2-12 | Timeliner plant application                                    | 74  |

| 3-1  | Architecture of the TASM toolset                               | 87  |

| 4-1  | Light switch example                                           | 105 |

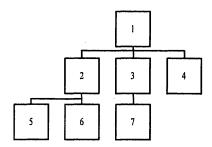

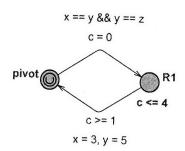

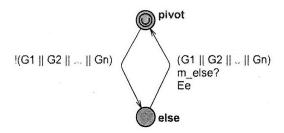

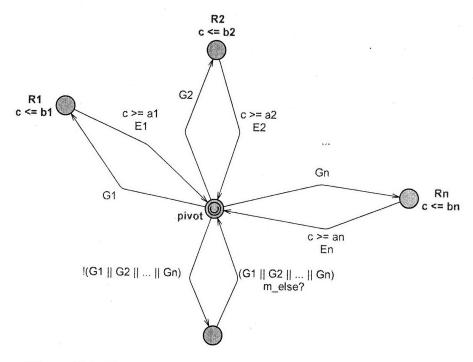

| 4-2  | Hierarchical composition                                       | 129 |

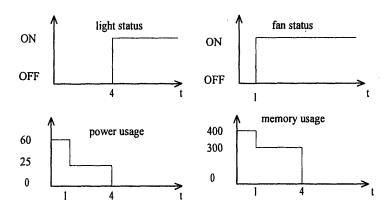

| 4-3  | Time history of variable values and resource consumption       | 141 |

| 5-1  | Timed automaton for Listing 5.1                                | 168 |

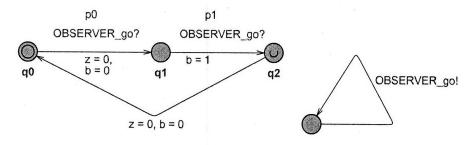

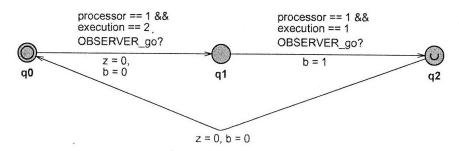

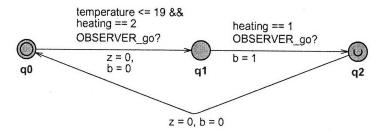

| 5-2  | Observer automaton                                             | 175 |

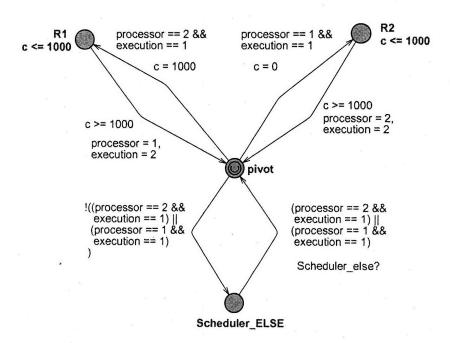

| 5-3  | Task graph                                                     | 178 |

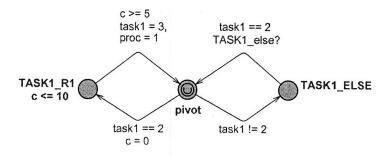

| 5-4  | Timed automaton for the TASK1 main machine                     | 180 |

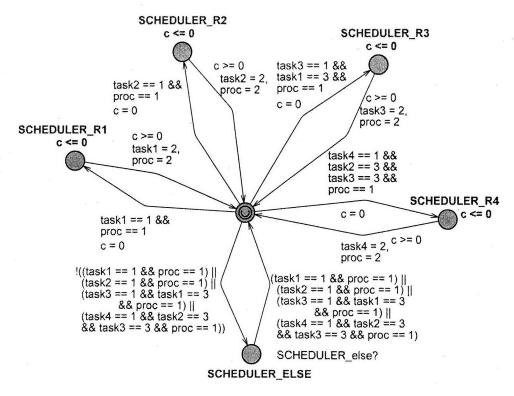

| 5-5  | Timed automaton for the SCHEDULER main machine                 | 181 |

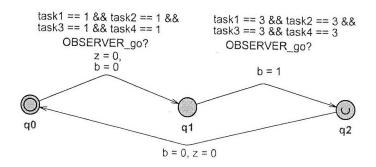

| 5-6  | Observer automaton to analyze schedulability                                  | 182 |

|------|-------------------------------------------------------------------------------|-----|

| 8-1  | Top view of the production cell                                               | 258 |

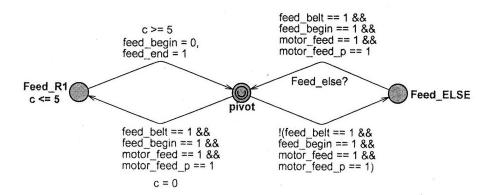

| 8-2  | Timed automaton for the feed main machine                                     | 278 |

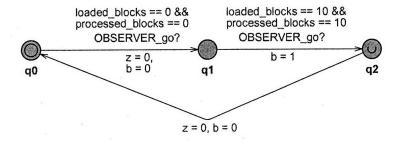

| 8-3  | Observer automaton to verify the time needed to process $10 \text{ blocks}$ . | 281 |

| 8-4  | ETC modes                                                                     | 288 |

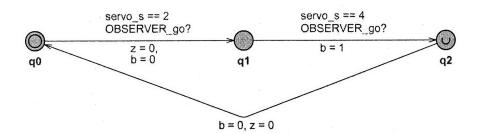

| 8-5  | Observer automaton to verify the execution time of the servo task $$ .        | 311 |

| 8-6  | Simulink sliding mode controller to calculate driver throttle current .       | 326 |

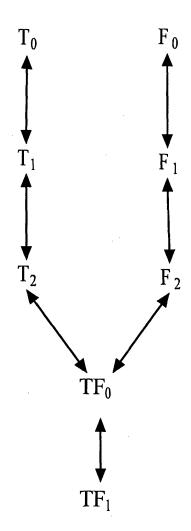

| 8-7  | Traceability between different versions of the ETC model                      | 327 |

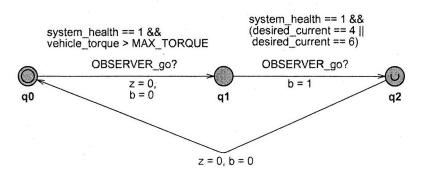

| 8-8  | Observer automaton to measure the end-to-end latency of the ETC for           |     |

|      | the vehicle torque being over the critical threshold                          | 333 |

| 8-9  | Automaton for the Scheduler main machine                                      | 354 |

| 8-10 | Observer automaton to measure the execution time of one pass of Time-         |     |

|      | liner                                                                         | 358 |

| 8-11 | Observer automaton to measure the end-to-end latency of Timeliner             |     |

|      | for a temperature drop                                                        | 360 |

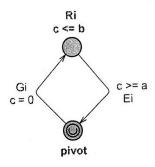

| C-1  | Timed automaton for rule $R_i$ of Equation 2                                  | 427 |

| C-2  | Timed automaton for Listing C.1                                               | 428 |

| C-3  | Timed automaton for the "Else rule" and the "t := next" annotation            | 429 |

| C-4  | Timed automaton for a TASM machine with $n$ rules                             | 430 |

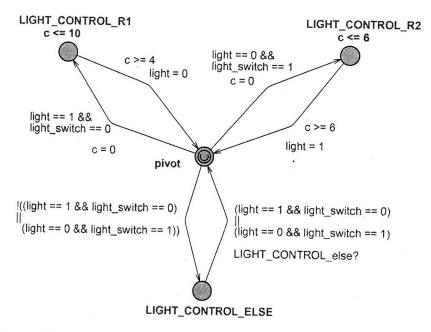

| C-5  | Timed automaton for the LIGHT_CONTROL machine                                 | 432 |

| C-6  | Timed automaton to enforce the urgent channel for the else rule of            |     |

|      | machine LIGHT_CONTROL                                                         | 432 |

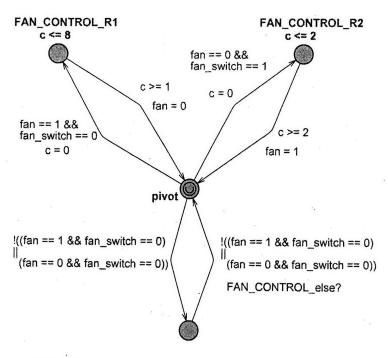

| C-7  | Timed automaton for the FAN_CONTROL machine                                   | 433 |

| C-8  | Timed automaton to enforce the urgent channel for the else rule of            |     |

|      | machine FAN_CONTROL                                                           | 433 |

| D-1  | Top view of the production cell                                               | 435 |

# List of Tables

| 2.1 | Examples of sources of explicit quantitative time                       | 40  |

|-----|-------------------------------------------------------------------------|-----|

| 2.2 | List of actuators used in the production cell system                    | 60  |

| 2.3 | Behavior of actuators based on polarity                                 | 61  |

| 2.4 | List of sensors used in the production cell system                      | 61  |

| 2.5 | Durative actions                                                        | 62  |

| 3.1 | Comparison of the proposed framework with other frameworks for em-      |     |

|     | bedded real-time systems engineering                                    | 82  |

| 4.1 | Comparison of the features of the TASM language with other languages    |     |

|     | for embedded real-time system specification                             | 105 |

| 4.2 | Update set combination operators                                        | 141 |

| 5.1 | Maximum resource usage                                                  | 187 |

| 5.2 | Minimum resource usage                                                  | 187 |

| 6.1 | Truth table to verify the correctness criteria for the rule expansion   |     |

|     | refinement between rule $R_1$ and rules $S_{11}$ and $S_{12}$           | 215 |

| 6.2 | Truth table to verify correctness the criteria for the rule expansion   |     |

|     | refinement between rule $P_1$ and rules $D_1$ , $D_2$ , and $D_3$       | 218 |

| 7.1 | Pre and post state for sample test case template for Listing 7.1        | 229 |

| 7.2 | Coverage test case corresponding to the template of Table 7.1 $ \dots $ | 230 |

| 7.3 | Template test suite for the machine of Listing 7.3                      | 235 |

| 7.4 | Template test suite for the machine of Listing 7.5                      | 240 |

| 7.5  | Template test suite for the machine of Listing 7.6                    | 242 |

|------|-----------------------------------------------------------------------|-----|

| 7.6  | Template test suite for the machine of Listing 7.7                    | 243 |

| 7.7  | Test suite template for the machine of Listing 7.10                   | 254 |

| 7.8  | Test suite template for the machine of Listing 7.7                    | 255 |

| 7.9  | List of test cases that need to be executed to cover the refinement   | 256 |

| 8.1  | List of main machines used in the production cell model               | 259 |

| 8.2  | Number of rules for flattened main machines                           | 277 |

| 8.3  | Completeness analysis results for the production cell model           | 279 |

| 8.4  | Consistency analysis results for the production cell model            | 280 |

| 8.5  | Resource consumption analysis results for the production cell         | 283 |

| 8.6  | Test case generation results for the production cell model            | 284 |

| 8.7  | Sample test case template from the test suite for the Controller main |     |

|      | machine                                                               | 285 |

| 8.8  | Number of rules for flattened main machines for the high level ETC    |     |

|      | $model \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$       | 298 |

| 8.9  | Completeness analysis results for the ETC high level model            | 300 |

| 8.10 | Consistency analysis results for the ETC high level model             | 301 |

| 8.11 | Test case generation results for the ETC high level model             | 303 |

| 8.12 | Sample test case template from the test suite for the CONTROLLER      |     |

|      | main machine                                                          | 303 |

| 8.13 | Execution time for floating point operations for a PowerPC 405 (in    |     |

|      | clock cycles)                                                         | 305 |

| 8.14 | Timing properties for the ETC tasks                                   | 305 |

| 8.15 | Number of rules for flattened main machines                           | 309 |

| 8.16 | Completeness analysis results for the ETC tasking model               | 310 |

| 8.17 | Consistency analysis results for the ETC tasking model                | 310 |

| 8.18 | Test case generation results for the ETC tasking model                | 312 |

| 8.19 | Sample test case template from the test suite for the $SCHEDULER$     |     |

|      | main machine                                                          | 313 |

| 8.20 | Truth table for the step expansion refinement between rule $R_1$ of model   |     |

|------|-----------------------------------------------------------------------------|-----|

|      | $\mathcal{T}_0$ and rules $R_{11}$ and $R_{12}$ of model $\mathcal{T}_1$    | 317 |

| 8.21 | Resource usage estimates for the ETC low level model                        | 325 |

| 8.22 | Number of rules for flattened main machines                                 | 330 |

| 8.23 | Completeness analysis results for the ETC low level model                   | 331 |

| 8.24 | Consistency analysis results for the ETC low level model                    | 332 |

| 8.25 | End-to-end latency analysis results for the ETC low level model             | 335 |

| 8.26 | Resource usage analysis results for the ETC low level model                 | 336 |

| 8.27 | Test case generation results for the ETC low level model (part 1)           | 337 |

| 8.28 | Test case generation results for the ETC low level model (part 2) $$        | 338 |

| 8.29 | Sample test case template from the test suite for the TASKS main            |     |

|      | machine                                                                     | 339 |

| 8.30 | Duration of transitions (in $\mu s$ ) between labels of Listing 8.25        | 345 |

| 8.31 | Duration of transitions (in $\mu s$ ) between labels of Listing 8.26        | 345 |

| 8.32 | Completeness analysis results for the Timeliner plant control system .      | 357 |

| 8.33 | Consistency analysis results for the Timeliner plant control system         | 357 |

| 8.34 | Execution time analysis results for the WCET of one pass of Timeliner       | 359 |

| 8.35 | Execution time analysis results for the BCET of one pass of Timeliner       | 359 |

| 8.36 | End-to-end latency analysis results for the plant control system            | 361 |

| 8.37 | Test case generation results for the plant control system                   | 362 |

| 8.38 | Sample test case template from the test suite for the <i>Timeliner</i> main |     |

|      | machine                                                                     | 362 |

| A.1  | Reserved keywords                                                           | 388 |

| A.2  | Operators                                                                   | 392 |

| A.3  | Operator precedence                                                         | 402 |

| C.1  | Datatype translations                                                       | 426 |

| D.1  | List of machines used in the production cell model                          | 436 |

| E.1  | List of machines used in the high level ETC model                           | 458 |

| E.2 | List of machines used in the tasking model of the ETC             | 475 |

|-----|-------------------------------------------------------------------|-----|

| E.3 | List of machines used in the low level ETC model (part 1)         | 486 |

| E.4 | List of machines used in the low level ETC model (part 2)         | 487 |

| F.1 | List of machines used in the Timeliner plant control system model | 502 |

# Chapter 1

# Introduction

This chapter serves as an "executive summary" of the work presented in this thesis. The chapter contains information about the motivations for the presented research, the contributions of the research, the list of presentations, posters, technical reports and refereed publications related to the research, and the roadmap of the thesis. Each chapter in the thesis follows a template structure, as explained in Section 1.5.

### 1.1 Motivations

In modern society, software systems can be found everywhere, including in airplanes, in automobiles, and in consumer electronics. The proliferation of software increases the dependency on the correct functioning of software and yields a new set of challenges in the engineering of software-intensive systems. The growing size and complexity of modern software systems exacerbates the difficulty of delivering reliable systems within aggressive budgetary constraints. In various engineering disciplines, the use of models has proven a viable approach to mitigate complexity through abstraction [40]. However the use of models in the engineering of software is a relatively novel approach to building software systems. The use of models not only helps to control complexity, but if the models have formal underpinnings, the models can be used to automate certain engineering activities such as verification and test case generation.

The research presented in this thesis seeks to address five key challenges in the engineering of embedded real-time systems:

- The high complexity of modern software systems, by providing a model-based approach to software-intensive system engineering.

- The high cost of Verification and Validation (V & V) activities by leveraging the use of models to automate engineering activities.

- The challenges in using formal methods in an engineering context by providing a novel literate specification language and abstracting verification details in a push-button approach.

- The lack of integration between disparate models by providing bi-directional traceability across levels of abstraction.

- The lack of integration of the state-of-the art in individual disciplines by providing an overarching engineering framework.

These five challenges form the base motivation for the research presented in this thesis. These challenges are addressed individually in subsequent chapters. In addressing these challenges, the research presented in this thesis makes a number of research contributions in various areas. These contributions are outlined in the following section.

### 1.2 Thesis Contributions

The research presented in this thesis makes five key contributions to address the challenges enumerated in the previous section:

• A new specification language for embedded real-time systems, the Timed Abstract State Machine (TASM) language, which extends the theory of Abstract State Machines (ASM). The TASM language integrates the specification of functional and non-functional properties – function, time, and resources.

- A set of verification procedures for automated analysis of models, using generally

available analysis engines. The procedures include the analysis of completeness

and consistency, the analysis of execution time, and the analysis of resource

consumption.

- An approach to traceability of system models that incorporates syntactic change and semantic integrity.

- A generic and extensible approach to automatically generate test cases for unit testing, integration testing, and regression testing.

- An integrated framework for modeling, simulation, verification, and test-case generation for embedded real-time systems.

- An integrated toolset implementing the capabilities of the framework.

### 1.3 Relevant Publications

The research presented in this thesis has led to presentations and poster sessions presented at the "Real-Time System Symposium (RTSS)" in December 2006 [189], at the "ARTIST Workshop on Tool Platforms for Embedded System Modeling, Analysis and Validation" of the "Computer-Aided Verification Conference (CAV)" in July 2007 [196], at the "Real-Time in Sweden Conference (RTiS)" in August 2007 [197], and at the "Asia-Pacific Software Engineering Conference (APSEC)" in December 2007 [204].

The presented research has also yielded a number of Technical Reports released through the Embedded Systems Laboratory (ESL) at the Massachusetts Institute of Technology [190, 195, 201, 202, 206]. A reference manual for the Timed Abstract State Machine (TASM) language [185], as well as a user guide for the TASM toolset [186] are also available through the Embedded Systems Laboratory [88].

The Timed Abstract State Machine language was presented to the real-time system community at the "Real-Time and Network Systems Conference (RTNS)" in

March 2007 [199] and to the ASM community at the "Abstract State Machines Workshop (ASM)" in June 2007 [198]. A journal article about the TASM language is set to appear in Volume 14 of the Journal of Universal Computer Science (JUCS) in July 2008 [205]. A critical look on how time is treated in modeling languages, motivating the TASM approach to modeling time, was presented at the "Modeling in Software Engineering (MiSE) Workshop" of the "International Conference on Software Engineering (ICSE)" in May 2007 [194].

The case study involving the Electronic Throttle Controller (ETC) was presented at the "Critical System Development using Modeling Languages Workshop (CSDUML)" of the "Model Driven Engineering Languages and Systems Conference (MoDELS)" in October 2006 [187] and was selected as one of two best papers to appear in Volume 4364 of Lecture Notes in Computer Science (LNCS) entitled "Models in Software Engineering" [188]. The analysis of TASM models using a SAT Solver was presented at the "Model-Based Testing Workshop (MBT)" of the "European Joint Conferences on Theory and Practice of Software (ETAPS)" in May 2007 [192] and appears in Volume 190 of "Electronics Notes in Theoretical Computer Science (ENTCS)" [193]. The TASM toolset was presented at the "Computer-Aided Verification Conference (CAV)" in July 2007 [200].

An overview of the framework will be presented at the "International Symposium on Quality Engineering for Embedded Systems (QEES)" [203], a symposium held jointly with the "European Conference on Model Driven Architecture Foundations and Applications (ECMDA)", in June 2008. A follow-up article will be submitted to the journal entitled "Software Tools for Technology Transfer".

## 1.4 Thesis Outline

This section provides an overview of the content of each chapter contained in this thesis.

### • Chapter 1: Introduction

This Chapter provides an "executive summary" of the thesis and should be read before other chapters.

### • Chapter 2: Background Information

This chapter provides background information necessary to understand the material contained in the research. This chapter covers a wide range of topics such as information about real-time systems, software engineering, and descriptions of the analysis engines used to implement the framework. The reader is invited to browse sections of this chapter as needed.

### • Chapter 3: Framework Overview

This chapter provides an overview of the capabilities of the framework as well as the tool architecture used in the implementation of the framework.

# • Chapter 4: The Timed Abstract State Machine Specification Language

This chapter describes the Timed Abstract State Machine (TASM) Language, its syntax, semantics, and modeling facilities, including how time and resources are treated, hierarchical composition, and parallel composition. Throughout the chapter, illustrative examples are provided to depict the concepts as they are introduced.

### • Chapter 5: Static Analysis

This chapter presents the types of analysis that can be performed in the framework. The analysis procedures include completeness and consistency analysis, execution time analysis, and resource consumption analysis. This chapter also contains illustrative examples to demonstrate the analysis algorithms. The implementation of the analysis facilities, performed in the TASM toolset, are also described.

#### • Chapter 6: Bi-Directional Traceability

This chapter explains the bi-directional traceability capabilities of the proposed framework. The approach to traceability establishes a relationship between two or more TASM models and combines syntactic change management with notions of semantic equivalence for the models.

### • Chapter 7: Test Case Generation

This chapter presents the automated test case generation capabilities of the framework for unit, integration, and regression test case generation. The regression test case generation strategy uses the traceability approach described in Chapter 6. Examples and implementation details are also presented.

### • Chapter 8: Case Studies

This chapter contains the results of the three case studies used to evaluate the research presented in this thesis – the production cell case study, an Electronic Throttle Controller (ETC), and the Timeliner Script Executor. The case studies are introduced in Section 2.8 but the models and analysis results are presented in Chapter 8. The complete TASM models for each case study are provided in the appendices.

### • Chapter 9: Conclusion

This chapter provides a critical evaluation of the presented research, draws conclusions for the thesis, and describes directions for possible future developments of the research.

#### Appendix A: TASM Language Reference

This appendix contains the concepts involved with the implementation of the TASM language in the TASM toolset. These concepts include the complete Context-Free Grammar (CFG) for the TASM language and various implementation topics such as operator precedence and typing.

### • Appendix B: Translating TASM Models to SAT

This appendix contains the details of the mapping from the TASM language to SAT, for the purpose of static analysis, as explained in Chapter 5, and for test case generation, as explained in Chapter 7.

### • Appendix C: Translating TASM Models to UPPAAL

This appendix contains the complete mapping from the TASM language to UPPAAL, for the purpose of timing analysis, as explained in Section 5.3. The mapping to UPPAAL is also used for model checking of functional properties.

### • Appendix D: Production Cell TASM Model

This appendix contains the complete TASM model for the production cell case study, explained in Section 2.8.1 and studied in Section 8.1.

### • Appendix E: Electronic Throttle Controller TASM Model

This appendix contains the complete TASM model for the electronic throttle controller for the case study, explained in Section 2.8.2 and studied in Section 8.2, in Section 8.3, and in Section 8.4.

### • Appendix F: Timeliner Plant Simulator TASM Model

This appendix contains the complete TASM model for the Timeliner case study involving the plant control system, explained in Section 2.8.3 and studied in Section 8.5.

## 1.5 Chapter Structure

Individual chapters in this thesis follow a common template. At the beginning of each chapter a paragraph explains the information contained in the chapter. The last section of each chapter is named "Segue into Chapter N" and provides a brief summary of the information provided in the current chapter and how it leads to the following chapter. All chapters follow this template except for the appendices. Unlike the thesis chapters, individual appendices do not follow a common pattern. However,

the first paragraph of each appendix contains a brief description of its content. The content of the appendices is summarized in Section 1.4. Appendices do not follow a linear progression and serve as a reference that can be read in any order.

### 1.6 Notational Conventions

In order to enhance the readability of the thesis, special fonts are used to clarify meaning in certain situations:

- *Italic font* is used for definitions and when referring to abstract syntax, such as the names of machines or the names of rules.

- Teletype font is used when referring directly to the concrete syntax of a model, such as a variable.

- "Quotation marks" are used to emphasize blocks of text that should be grouped together.

Furthermore, the listings for models expressed in the Timed Abstract State Machine (TASM) language are expressed in teletype font.

## 1.7 Segue into Chapter 2

This chapter presented an "executive summary" of the content of the thesis. The following chapters expand on this summary. The next chapter, Chapter 2, provides background information about the topics covered throughout the thesis.

# Chapter 2

# **Background Information**

This chapter presents background information related to the concepts explained in the following chapters. The information contained in this chapter includes details about the types of systems targeted by the presented research, details about how the current work integrates into software engineering practice, information about the analysis engines used in the framework, and descriptions of the case studies used to evaluate the presented framework.

## 2.1 Real-Time Embedded Systems

The primary goal of a computer system is to provide value, as defined by a user of the system, by performing a set of functions. More specifically, a computer system must provide a *correct* response (output) based on a given stimulus (input). The concept of *correctness* is comprised of multiple facets such as functional correctness and nonfunctional correctness. The *functional correctness* of a computer system is defined through a set of *requirements* that the input-output behavior of the system must satisfy [85]. The requirements describing the functional correctness of a computer system can be described through *safety properties*, that is, statements about behavior that *should never occur*, and *liveness properties*, that is, statements about behavior that *should eventually occur* [30]. All functional behavior of computer systems can be described in terms of safety and liveness properties [154].

While functional correctness is a critical aspect of all computer systems, certain types of systems also require that non-functional aspects of the system, such as timing behavior, conform to stringent correctness criteria. The research presented in this work addresses the engineering of embedded real-time systems, a class of systems where non-functional properties are central to the system's value. More specifically, embedded real-time systems represent a special class of computer systems where time plays a critical role in the correctness of the system. In a real-time system, the system must not only produce a correct answer, but must also do so in an adequately bounded amount of time [58]. The amount of time under which the system must produce a response is termed a deadline. If a real-time system provides an answer after a deadline has elapsed, the system is said to have missed a deadline. With regards to correctness, the implications of missing a deadline depends on the type of system. Real-time systems fall into two categories – hard real-time systems, where missing a deadline is unacceptable, and *soft* real-time systems, where missing a deadline may be acceptable under certain circumstances, depending on performance requirements [155]. Nevertheless, time plays a critical role in defining the correctness of a real-time system since a correct answer provided too late can be as erroneous as providing an incorrect answer [49]. The timing analysis provided by the framework does not make assumptions about whether the system being analyzed is hard or soft. The framework provides generic timing analysis to determine the best and worst case timing behavior, and it is up to the system behavior to decide whether the analysis results are acceptable for the system being engineered.

In practice, real-time systems are also typically reactive, meaning that they do not terminate, but are in continuous interaction with the environment, until the system is switched off. Reactive systems are different than transformational system, where the system terminates after producing an answer. In a reactive real-time system, the timing correctness of the system is defined as the absence of missed deadlines while taking into account the continuous interaction of the system with its environment. The types of systems targeted by the proposed framework are of the mostly periodic nature [164], meaning that they operate in a continuous loop that samples

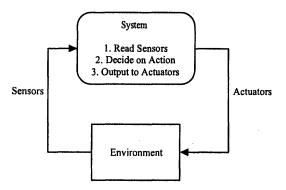

the environment through sensors, makes a decision on what action the system should take based on the sensor values, and affects the environment by executing the action through an actuator. A sample loop for the systems targeted by the proposed framework is shown in Figure 2-1. It is important to note that which steps of the loop are executed at each iteration is implementation dependent. As will be described in the electronic throttle controller case study, the sampling of the state through sensors could be done at a lower frequency than, for example, the frequency of deciding on the action to be taken by the controller.

Figure 2-1: High level view of a mostly periodic reactive real-time system

In traditional real-time system theory, the concept of a deadline refers to the Worst-Case Execution Time (WCET) [89] also sometimes called the worst-case computation time, that is, the maximum time that can elapse when an individual task or an individual process executes [58]. In this research, the traditional WCET definition is made more general to include system properties. In the remainder of this work, the term WCET is used to denote the maximum amount of time that can elapse when the system completes a path between two states. The definition used in this thesis also stipulates that such a path can consist of any two states. In this definition, the notion of state can include both the state of the engineering artifact such as the program counter and values of system variables, and, the value of environment variables. This definition is more general than the traditional definition and can capture important concepts such as end-to-end latency all the while being able to express the traditional definition. End-to-end latency refers to the longest reaction time of a system to an environment stimulus, taking into account system properties such as environment

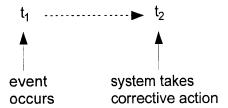

interaction, task interference, and delay in response. For example, in the loop of Figure 2-1, the value of an environment variable could change while the system is deciding on which action to take. Depending on the frequency of sensor readings, a significant delay could result in the system taking a corrective action since there could be a delay before the change is detected. Figure 2-2 shows a symbolic view of the time that can elapse between an event occurring and the system taking a corrective action. The verification problem to ensure that there are no missed deadlines can be summarized as:

$$dt = t_2 - t_1 \leq Required Deadline$$

The response latency, dt, refers to how much time elapses between the event and the response. The proposed framework provides necessary facilities to calculate the maximum value of dt, for any event and action modeled. The Required Deadline is system-dependent and is provided by the performance requirements. It is also the responsibility of the system designer to decide on which course of action to take if the designed system does not meet the required deadline. The proposed system provides only the necessary modeling and analysis facilities. Additional definitions related to execution time are given in Section 5.3.

Figure 2-2: Delay in system responding to an event of interest

Most real-time systems also fall into the category of embedded systems. *Embedded* systems represent a special class of real-time systems where the software system is not stand-alone, but is part of a larger system and must work with other components to achieve the system's goals [155]. Vehicle controllers, such as automotive electronics

and avionics, are typical examples of embedded real-time systems. In an embedded system, resources such as communication bandwidth and memory are typically limited and must be shared across multiple components. Consequently, the correctness of an embedded real-time system is also dependent on the resource usage being adequately bounded. In summary, for an embedded real-time computer system, the correctness of the system is defined in terms of three key aspects – functional correctness, timing behavior, and resource usage. These three aspects form the fundamental motivation of the modeling and analysis capabilities provided by the proposed framework.

## 2.1.1 The Nature of Time in Real-Time Systems

Since time plays an important role in defining the correctness of a real-time system, it is paramount to understand the role of time in the systems of interest. On a general and global level, the time axis is a monotonic function that is used to order events linearly according to some concept of progression [101]. A large body of research has been devoted to establish that a computer system satisfies a correct ordering of events [49]. This correct ordering of events, also called qualitative time, refers to the ordering of events with respect to one another and is not concerned with the temporal distance between events [212]. For example, in the well-known Simple Mail Transfer Protocol (SMTP), an acknowledgement message (ACK) shall not be received before a synchronization request (SYN) has been emitted. In other words, an ACK must occur after a SYN and never before. However, in real-time systems, timing correctness does not depend only on the ordering of events, but also depends on the numerical distance between events, a concept called quantitative time [155]. For example, in the SMTP protocol, after a SYN has been emitted, a timer is typically started while waiting for the ACK. If, after a prespecified amount of time, the ACK has not been received, the SYN sender might assume that the SYN request was lost. In such a situation, the precise amount of time between the SYN and the ACK is of particular importance, in addition to the messages occurring in the correct order.

Quantitative time appears in real-time system problems either explicitly or implicitly. Examples of where quantitative time appears explicitly include performance

| Source       | Example                         |  |  |

|--------------|---------------------------------|--|--|

| Requirements | The data in the operator        |  |  |

|              | console shall be refreshed 10   |  |  |

|              | times per second                |  |  |

| Physics      | It takes approximately 5 sec-   |  |  |

|              | onds for a projectile shot      |  |  |

|              | straight up in the air at a ve- |  |  |

|              | locity of 50 m/s to come to     |  |  |

|              | rest at its apogee              |  |  |

| Components   | Pressure sensors can put        |  |  |

|              | data on the system bus at a     |  |  |

|              | rate of 10Hz                    |  |  |

Table 2.1: Examples of sources of explicit quantitative time

requirements, local clocks, timeouts, scheduling, the physics of the problem, and constraints of the components of the system. Examples of explicit instances of quantitative time are shown in Table 2.1. Examples where time appears implicitly, as a side-effect, include software execution time and hardware execution time. Listing 2.1 shows a brief example of software code, written in the Timeliner scripting language [61], borrowed from the Timeliner case study. The code represents a sequence used to maintain cabin temperature between 20 and 25 Celsius degrees [238]. In order to determine how long this snippet of Timeliner code takes to execute, many other questions need to be answered. For example, the execution time of the script depends on:

- The properties of the execution platform

- The semantics of the language

- The assumptions on the behavior of the environment

Once the code has been written and the system is implemented, these concerns can typically be addressed to a satisfactory degree of confidence. For example, in [62], precise timing measurements of each statement of the Timeliner language have been measured through laboratory experiments for a specific execution environment. However, determining these execution times a priori remains a challenging endeavor.

Listing 2.1 Sequence TEMP\_MONITOR [238]

```

SEQUENCE TEMP_MONITOR

EVERY 1

IF TEMPERATURE >= 26 THEN

SET TRYING_TO_COOL_SYSTEM TO TRUE

COMMAND COOLING, NEW_STATE=>ON

WHEN TEMPERATURE <= 22

SET TRYING_TO_COOL_SYSTEM TO FALSE

COMMAND COOLING, NEW_STATE=>OFF

END WHEN

END IF

IF TEMPERATURE <= 19 THEN

COMMAND HEATING, NEW_STATE=>ON

WHEN TEMPERATURE >= 22

COMMAND HEATING, NEW_STATE=>OFF

END WHEN

END IF

END EVERY

CLOSE SEQUENCE

```

Even for software and hardware execution, time can also appear implicitly and explicitly. For example, the code in Listing 2.1 contains one explicit timing statement, the "EVERY 1" statement. This statement tells the runtime system that the sequence shall execute at most once per second. Other examples of explicit timing statements include the statements sleep and wait, which are present in many programming languages such as C++ and Java [239]. In real-time system engineering, the explicit sources of quantitative time, outside of software and hardware, define the timing constraints of the system that is to be built. One of the goals of real-time system engineering is to build a system which meets these constraints.

# 2.2 Systems Engineering

Systems Engineering is the aggregation of multiple elements to perform functions that could not be performed by the elements alone [152]. Systems engineering is an overarching discipline which includes aspects bridging people, documentation, software, hardware, and other domains. Systems engineering efforts seek to develop processes, tools, and techniques to ensure that a given engineering artifact satisfies all parties involved throughout the lifetime of a system. In Section 2.1, the types of systems targeted by the presented framework were presented, alongside definitions of the correctness of these systems. The goal of the systems engineering efforts go beyond the

correctness aspects described in Section 2.1 and include concepts related to the stakeholders, potential risks, safety concerns, and other factors affecting the engineering, delivery, and operation of the system [166]. The goal of this section is to situate the applicability of the presented framework in the wider sphere of systems engineering.

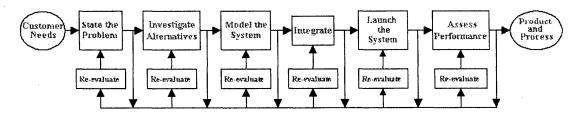

Figure 2-3 shows the steps of a generic systems engineering process defined in [19]. The framework presented in this research is applicable in the software and digital hardware engineering facets of real-time systems, during the modeling phases and the integration phases depicted in Figure 2-3.

Figure 2-3: Systems engineering process [19]

The proposed framework assumes the existence of requirements on the functional, time, and resource aspects of the system. The engineering of software and digital hardware for an embedded system, such as the engineering of an avionics system, will be performed in parallel with other systems engineering activities such as requirements analysis and vehicle design. In the following section, software engineering principles are reviewed as motivations for the presented framework.

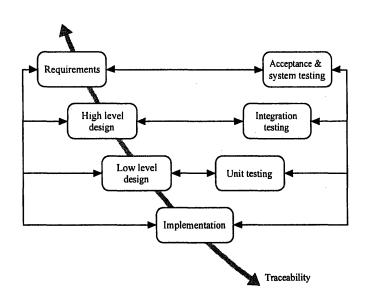

# 2.3 Software Engineering

Software engineering is the set of techniques, processes, and tools used to develop computer systems [242]. Typically, software engineering is divided into lifecycle phases that traditionally include requirements engineering, design, implementation, testing, and maintenance [255]. These different phases are carried out in sequence, with a certain amount of overlap depending on the lifecycle model that is used [253]. Validation and Verification (V & V) activities are defined as the process of establishing confidence into the correctness of the system. More specifically, validation refers to