# Compiling for Parallel Multithreaded Computation on Symmetric Multiprocessors

by

#### Andrew Shaw

S.B., Massachusetts Institute of Technology, Cambridge, MA, 1989 S.M., Massachusetts Institute of Technology, Cambridge, MA, 1993

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electrical Engineering and Computer Science

at the

Massachusetts Institute of Technology

January, 1998

© Massachusetts Institute of Technology 1998

| Signature of Author |          |                                 |                      |

|---------------------|----------|---------------------------------|----------------------|

|                     | Departme | ent of Electrical Engineering a | and Computer Science |

|                     | -        | 1                               | January 22, 1998     |

| Certified by        |          |                                 | A 2.1                |

|                     | V        | Dunfacean of Computer Sai       | Arvind               |

|                     |          | Professor of Computer Sci       | Thesis Supervisor    |

|                     |          |                                 |                      |

| Accepted by         |          |                                 |                      |

| 1 7                 |          |                                 | Arthur C. Smith      |

714.0

LIBRAPHES

Chairman, Committee on Graduate Students

# Compiling for Parallel Multithreaded Computation on Symmetric Multiprocessors

by

#### Andrew Shaw

Submitted to the Department of Electrical Engineering and Computer Science on January 22, 1998

in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering and Computer Science

#### **Abstract**

Shared-memory symmetric multiprocessors (SMP's) based on conventional microprocessors are by far the most common parallel architecture today, and will continue to be so for the forseeable future. This thesis describes techniques to compile and schedule Id-S, a dialect of the implicitly parallel language Id, for execution on SMP's.

We show that previous implementations of Id for conventional microprocessors incurred an overhead of at least 40-300% over an efficient sequential implementation of Id-S. We break down this overhead into various presence-tag checking and scheduling overheads. Given this overhead, we conclude that a fine-grained, element-wise synchronizing implementation of Id is not suitable for use on small-scale SMP's.

We then describe a parallelization technique for Id-S that discovers both DAG and loop parallelism. Our parallelization exploits Id-S's single-assignment semantics for data structures. We show that for many programs, our technique can discover ample parallelism, without need for Id's traditional non-strict, fine-grained, producer-consumer semantics. Because our parallelization eliminates the need for presence-tag checking and creates coarser-grained units of work, the parallelized codes only incur a small overhead versus sequential execution.

Finally, we describe code-generation and scheduling techniques which produce efficient parallel executables which we run on a Sun Ultra HPC 5000 SMP. We compare speedups of parallelized Id-S codes using two different schedulers: an SPMD scheduler, and a more general multithreaded scheduler. We describe the advantages and disadvantages of each scheduler, and quantify the limitations in speedups for each scheduler which are due to parallelization, code generation, and scheduling.

Thesis Supervisor: Arvind

Title: Professor of Computer Science and Engineering

#### Acknowledgements

It is an honor and a privilege to have been a member of the Computation Structures Group (CSG) at the MIT Laboratory for Computer Science. From the "old" generation, I'd like to thank Steve Heller, Ken Traub, and Greg Papadopoulos, who brought me into CSG. From the "next" generation, I'd like to thank Boon Ang, Derek Chiou, and Alex Caro for all of the battles we've fought together all these years. Thanks also to Xiaowei Shen for many late-night talks in the lab, and James Hoe and Mike Ehrlich for teaching me a little about hardware. Thanks to Shail Aditya for many long discussions about dataflow, functional languages, and advice about surviving grad school.

R. Paul Johnson and Andy Boughton have taken good care of us, through thick and thin. I have relied on your help and friendship too many times to count. Thank you.

I would like to thank my advisor, Arvind, who is often exasperatingly uncompromising, but who has taught me to think clearly, to focus on fundamentals and first principles, and to build a strong foundation for my arguments and ideas. I am proud to have been one of your students.

I'm very grateful to my readers, Rishiyur Nikhil and Saman Amarasinghe, who both read my thesis carefully, asked penetrating questions, pointed out holes and ambiguities, and helped me wrestle it into shape.

The work in this thesis was motivated by ideas from two research projects: TAM and Cilk. From the Berkeley TAM project, David Culler, Klaus Schauser, Seth Goldstein, and Thorsten von Eiken bridged the gap between dataflow and conventional architectures, and laid the groundwork for the partitioning and code generation approach used in this thesis. From Cilk and its predecessor, PCM, Yuli Zhou, Michael Halbherr and Chris Joerg showed me the importance of scheduling; my early code to implement Cilk on SMP's was the basis of the compiler used in this thesis. Special thanks to Chris Joerg, whose questions eventually led me to the work in this thesis, and who directly or indirectly helped me solve some of the hard problems, and who encouraged me in my work when I needed it.

I'd like to thank my family – my sister Nini, and my parents Julie Yueh-ho and Chong-Kuang Shaw who have supported me throughout my years at MIT. Everything I have, I owe to you.

Finally, thanks to my wife Atsuko, who brought true happiness to my life – your optimism and patience have pulled me through, and I am so lucky to have shared these years with you. I am also happy to have shared my final year at MIT with my daughter Marie, whose energy and thirst for knowledge inspire me anew.

# **Contents**

| 1 | Intr | oductio | n                                                 | 19 |

|---|------|---------|---------------------------------------------------|----|

|   | 1.1  | Paralle | lism and efficiency                               | 21 |

|   |      | 1.1.1   | Overheads in previous Id implementations          | 21 |

|   |      | 1.1.2   | Analysis of parallelism/efficiency tradeoff       | 22 |

|   | 1.2  | Structu | ared versus unstructured parallelism              | 23 |

|   |      | 1.2.1   | Exposing parallelism                              | 24 |

|   |      | 1.2.2   | Parallel execution model: SPMD vs. multithreading | 25 |

|   | 1.3  | Thesis  | contributions                                     | 26 |

|   |      | 1.3.1   | New language semantics                            | 26 |

|   |      | 1.3.2   | New compiler parallelization and code-generation  | 27 |

|   |      | 1.3.3   | Parallelism and efficiency tradeoff               | 27 |

|   |      | 1.3.4   | Parallelizing Id-S                                | 28 |

|   |      | 1.3.5   | Parallel code generation and run-time system      | 28 |

|   |      | 1.3.6   | Parallel performance                              | 28 |

|   |      | 1.3.7   | Issues not addressed in this thesis               | 29 |

|   | 1.4  | Relate  | d work                                            | 30 |

|   |      | 1.4.1   | Direct ancestors to this research                 | 30 |

|   |      | 1.4.2   | Related hardware                                  | 32 |

|   |      | 1.4.3   | Related languages                                 | 32 |

|   |      | 1.4.4   | Related compilers                                 | 32 |

|   |      | 1.4.5   | Related multithreading run-time systems           | 32 |

|   | 1.5  | Outlin  | e of thesis                                       | 33 |

| 2 | Syst | em Ove  | erview                                                 | 35 |

|---|------|---------|--------------------------------------------------------|----|

|   | 2.1  | Multit  | hreaded execution model                                | 35 |

|   | 2.2  | Id lang | guage and compilers                                    | 37 |

|   |      | 2.2.1   | Performance impact of Id language features             | 39 |

|   |      | 2.2.2   | Sequential Id compiler as baseline                     | 39 |

|   |      | 2.2.3   | Compiler generated threaded code                       | 40 |

|   | 2.3  | Run-ti  | me system                                              | 41 |

|   | 2.4  | Develo  | opment hacks that made this study possible             | 43 |

|   |      | 2.4.1   | Reusing code                                           | 43 |

|   |      | 2.4.2   | Rapid prototyping                                      | 43 |

|   |      | 2.4.3   | Test suites and automatic regression testing           | 44 |

|   |      | 2.4.4   | Generating C and gcc extensions                        | 44 |

|   |      | 2.4.5   | Graph viewer                                           | 44 |

|   |      | 2.4.6   | Linker implemented in Perl                             | 45 |

| 3 | Fine | Graine  | ed Id Overheads                                        | 47 |

|   | 3.1  | Metho   | dology                                                 | 47 |

|   |      | 3.1.1   | Performance compared to strict TAM                     | 48 |

|   |      | 3.1.2   | SimICS Spare simulator                                 | 49 |

|   |      | 3.1.3   | Relationship between run-time and instruction counts   | 49 |

|   | 3.2  | Presen  | ce tag checking overhead                               | 51 |

|   |      | 3.2.1   | Presence tag checking scheme                           | 51 |

|   |      | 3.2.2   | Presence check performance results                     | 52 |

|   | 3.3  | Thread  | ling overheads                                         | 53 |

|   |      | 3.3.1   | Bookkeeping for threading overheads                    | 54 |

|   |      | 3.3.2   | Threading overhead performance results                 | 55 |

|   | 3.4  | Overhe  | ead summary and coarser-grained multithreading         | 56 |

|   | 3.5  | Related | d work                                                 | 57 |

|   |      | 3.5.1   | Software based fine-grain synchronization              | 57 |

|   |      | 3.5.2   | TAM                                                    | 58 |

|   |      | 3.5.3   | Software distributed shared memory systems             | 58 |

|   | 3.6  | Conclu  | sion: fine-grain parallelism too expensive in software | 59 |

| 4 | Para | allelizin | g Id-S                                                                     | 61  |

|---|------|-----------|----------------------------------------------------------------------------|-----|

|   | 4.1  | Simple    | parallelization example                                                    | 62  |

|   | 4.2  | Comm      | entary on parallelization                                                  | 63  |

|   |      | 4.2.1     | Role of single-assignment semantics                                        | 64  |

|   |      | 4.2.2     | No index analysis                                                          | 64  |

|   |      | 4.2.3     | Whole program analysis                                                     | 64  |

|   |      | 4.2.4     | Extension to loop parallelization                                          | 65  |

|   |      | 4.2.5     | Parallelization is decoupled from scheduling                               | 65  |

|   | 4.3  | Appro     | ach to parallelization                                                     | 66  |

|   |      | 4.3.1     | Parallelization example 2                                                  | 67  |

|   |      | 4.3.2     | Stage 1: find local mod and ref sets                                       | 68  |

|   |      | 4.3.3     | Stage 2: find interprocedural mod and ref sets                             | 72  |

|   |      | 4.3.4     | Stage 3: find procedure argument aliases                                   | 74  |

|   |      | 4.3.5     | Stage 4: find return value aliases                                         | 76  |

|   |      | 4.3.6     | Stage 5: incorporate interprocedural mod/ref and alias information locally | 77  |

|   |      | 4.3.7     | Stage 6: add data structure dependences                                    | 79  |

|   |      | 4.3.8     | Stage 7: characterizing loop induction variables                           | 81  |

|   |      | 4.3.9     | Stage 8: marking parallel loops                                            | 83  |

|   | 4.4  | Limita    | tions and improvements to the parallelization                              | 85  |

|   |      | 4.4.1     | False dependencies due to $\top$                                           | 85  |

|   |      | 4.4.2     | False dependencies due conservative object labelling                       | 85  |

|   |      | 4.4.3     | Room for improvement in index analysis                                     | 86  |

|   | 4.5  | Paralle   | elization results                                                          | 86  |

|   |      | 4.5.1     | Methodology for measuring idealized parallelism                            | 87  |

|   |      | 4.5.2     | Parallelism in structured codes                                            | 89  |

|   |      | 4.5.3     | Parallelism in unstructured codes                                          | 92  |

|   |      | 4.5.4     | Effect of single-assignment semantics                                      | 95  |

|   | 4.6  | Interac   | ction of DAG and loop parallelism                                          | 98  |

|   |      | 4.6.1     | Example to illustrate DAG and loop parallelism interaction                 | 98  |

|   |      | 4.6.2     | Analyzing DAG and loop parallelism interaction for FFT                     | 100 |

|   | 47   | Id-S n    | arallelization conclusions                                                 | 103 |

| 5 | Cod | le Gene | ration                                                                                 | 105 |

|---|-----|---------|----------------------------------------------------------------------------------------|-----|

|   | 5.1 | Partiti | oning                                                                                  | 106 |

|   |     | 5.1.1   | Pre-partitioning                                                                       | 108 |

|   |     | 5.1.2   | Partitioning algorithm                                                                 | 108 |

|   |     | 5.1.3   | Peephole fixups                                                                        | 109 |

|   | 5.2 | Calling | g convention                                                                           | 110 |

|   | 5.3 | Join sy | ynchronization                                                                         | 113 |

|   |     | 5.3.1   | Join counters and local work queue                                                     | 113 |

|   |     | 5.3.2   | Control optimizations for join synchronizations                                        | 114 |

|   |     | 5.3.3   | Optimizing for binary joins                                                            | 115 |

|   |     | 5.3.4   | Join synchronization overhead                                                          | 115 |

|   | 5.4 | Paralle | el Loop Code                                                                           | 117 |

|   |     | 5.4.1   | Parallel loop calling convention                                                       | 117 |

|   |     | 5.4.2   | Loop chunking protocol                                                                 | 119 |

|   |     | 5.4.3   | Work estimation                                                                        | 120 |

|   |     | 5.4.4   | Cumulative overheads from calling convention, join synchronization, and parallel loops | 121 |

| 6 | Run | -Time S | System                                                                                 | 125 |

|   | 6.1 | Messa   | ge passing layer                                                                       | 126 |

|   | 6.2 | Work s  | stealing policy                                                                        | 128 |

|   |     | 6.2.1   | Return and receive stubs                                                               | 128 |

|   |     | 6.2.2   | Stealing loop iterations                                                               | 130 |

|   | 6.3 | SPMD    | scheduling                                                                             | 130 |

|   | 6.4 | Perform | mance and speedups                                                                     | 131 |

|   |     | 6.4.1   | Speedups limited by lack of parallelism                                                | 132 |

|   |     | 6.4.2   | Speedups limited by code generation                                                    | 135 |

|   |     | 6.4.3   | Run-time system overheads                                                              | 135 |

|   |     | 6.4.4   | Load imbalances                                                                        | 135 |

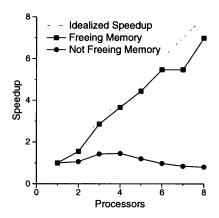

|   |     | 6.4.5   | Effects of the memory system and freeing memory                                        | 136 |

|   | 6.5 | Multith | preaded versus SPMD scheduling                                                         | 137 |

| 7                                                           | Con | Conclusions                                                                                                                                                                |                                                                                                      |     |  |  |

|-------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----|--|--|

|                                                             | 7.1 |                                                                                                                                                                            | rictness isn't used to write more expressive programs and non-strictness adds too execution overhead | 139 |  |  |

| 7.2 Sequential single-assignment simplifies parallelization |     |                                                                                                                                                                            |                                                                                                      | 140 |  |  |

|                                                             | 7.3 | 7.3 Generating efficient multithreaded parallel code for SMP's                                                                                                             |                                                                                                      | 140 |  |  |

|                                                             | 7.4 | 7.4 Multithreaded scheduling can be as efficient as SPMD scheduling for structured codes, while handling DAG parallelism and unbalanced loop parallelism better than SPMD. |                                                                                                      |     |  |  |

|                                                             | 7.5 | 5 Memory management increases single-processor performance and increases speedups .                                                                                        |                                                                                                      |     |  |  |

|                                                             | 7.6 | 7.6 Future work                                                                                                                                                            |                                                                                                      | 142 |  |  |

|                                                             |     | 7.6.1                                                                                                                                                                      | Parallelizing conventional languages                                                                 | 142 |  |  |

|                                                             |     | 7.6.2                                                                                                                                                                      | Integration with software distributed shared memory                                                  | 143 |  |  |

|                                                             |     | 7.6.3                                                                                                                                                                      | Single-chip SMP as an alternative to wider superscalars and VLIW's                                   | 143 |  |  |

# **List of Figures**

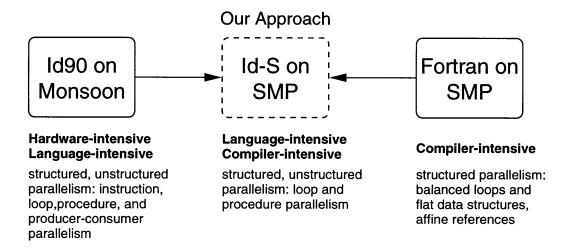

| 1.1 | Our approach straddles two previous approaches to parallel computing: Id on Monsoon and Fortran on SMP's, attempting to take advantage of the strengths of each                                                                                                                                                                                                               | 20 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

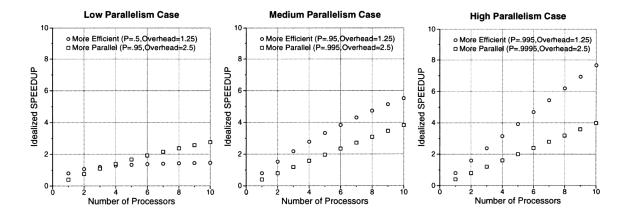

| 1.2 | Assuming $P$ is the fraction of a code which can be parallelized, and Overhead is the ratio of run-time versus sequential execution, these graphs show the speedups under two scenarios assuming the parallel part of the code speeds up perfectly. In general, efficiency is more important than parallelism for small numbers of processors, except when parallelism is low | 22 |

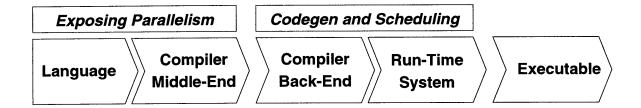

| 1.3 | In exploiting structured and unstructured parallelism, there are two main, somewhat decoupled components: (1) exposing parallelism and (2) code generation and scheduling. We attack the first with a combination of language support and compiler analysis, and we handle the second with methods for efficient code generation and scheduling                               | 23 |

| 1.4 | Id-S is the fastest implementation of Id to date, and comparable in performance to C or Fortran.                                                                                                                                                                                                                                                                              | 27 |

| 1.5 | The Id97 system has dataflow roots but has moved towards implementation on more conventional architectures                                                                                                                                                                                                                                                                    | 30 |

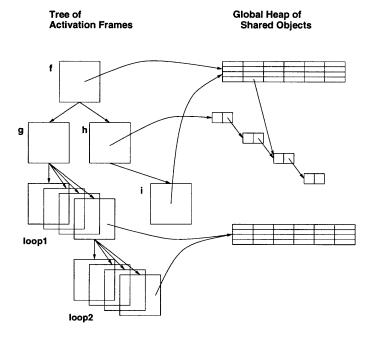

| 2.1 | In the multithreaded execution model, procedure activations may execute in parallel, as may loop activations. Activation frames are analogous to stack frames, and all the procedure and loop activations may reference global heap objects                                                                                                                                   | 36 |

| 2.2 | The three Id compilers: fine-grained, sequential and parallel                                                                                                                                                                                                                                                                                                                 | 38 |

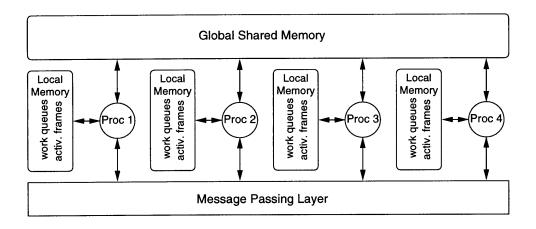

| 2.3 | Run-time system structure                                                                                                                                                                                                                                                                                                                                                     | 41 |

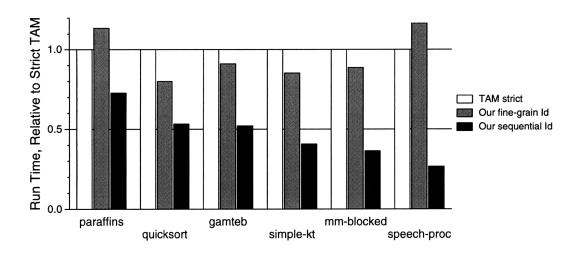

| 3.1 | Normalized run-time of fine-grain and sequential Id-S compilers compared to the strict TAM compiler running on a Sparc 10                                                                                                                                                                                                                                                     | 48 |

| 3.2 | Program input sizes                                                                                                                                                                                                                                                                                                                                                           | 48 |

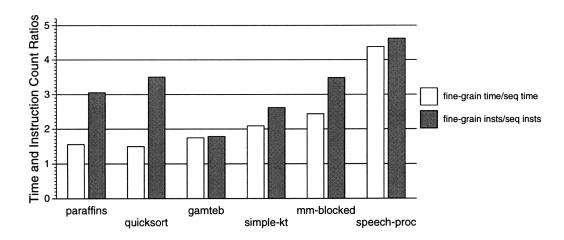

| 3.3 | Execution time ratios compared to instruction count ratios. Much of the additional execution time for the strict versions is accounted for by additional instructions executed, although some of the additional instructions are masked by poor cache locality                                                                                                                | 50 |

| 3.4 | Although the ratio of instructions between the fine-grained and sequential versions is between 2 and 5, the total difference in data cache misses between the versions is not as great – for codes with have a naturally high cache miss rate, a big reduction in instructions will not have as big a reduction in time because much of the time is spent handling            |    |

|     | cache misses.                                                                                                                                                                                                                                                                                                                                                                 | 50 |

| 3.5  | The presence tags for a structure reside at negative offsets from the structure base, and are initialized to be empty. Each tag is a byte wide, to make reading and writing the tags cheaper                                                                         | 51 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

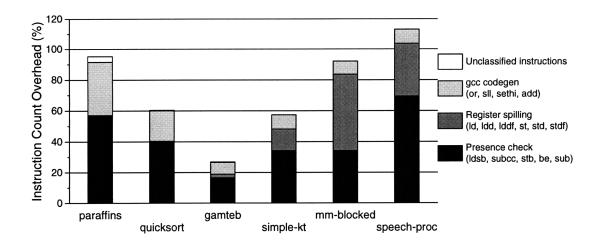

| 3.6  | Presence tag overhead, classified into three main sources – instructions used in the presence check, instructions coming from register spilling, and instructions introduced by poor code generation by gcc                                                          | 52 |

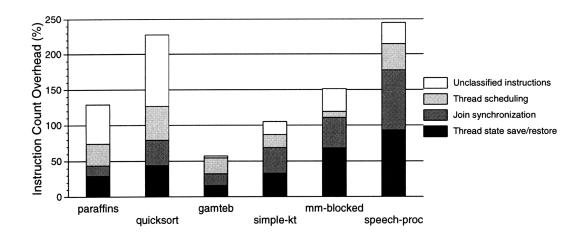

| 3.7  |                                                                                                                                                                                                                                                                      |    |

|      | Threading overhead of strict version, relative to (non-tag-checking) sequential version.                                                                                                                                                                             | 55 |

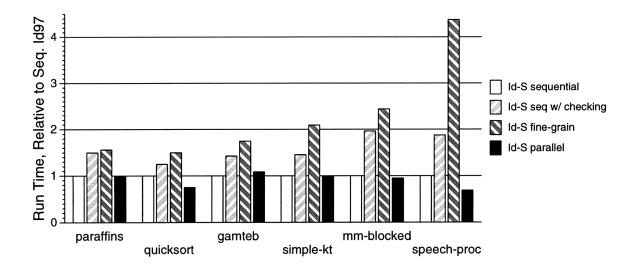

| 3.8  | Run-time on a Sparc 10 performance of sequential, sequential with checking, fine-grained multithreading and parallel multithreading without element-wise synchronization.                                                                                            | 56 |

| 4.1  | In this code fragment, the calls to foo and bar within baz can occur in parallel, because there is no data dependency between the calls to foo and bar                                                                                                               | 62 |

| 4.2  | Compiler parallelization stages and line counts of each stage, including comments and debugging code. The compiler was written in Lisp, increasing code density, but the                                                                                             |    |

|      | compiler stages are still extremely short and simple                                                                                                                                                                                                                 | 66 |

| 4.3  | Example program to calculate $\sum_{i=1}^{n} fib(n)$ , where $fib(n)$ is the $nth$ fibonacci number.                                                                                                                                                                 | 68 |

| 4.4  | Desugaring of make_fibtree and sumtree providing a unique variable name to each object                                                                                                                                                                               | 69 |

| 4.5  | After Stage 1, all of the reads, writes and procedure calls are labelled with the object or objects which they reference. Each object is labelled with its source                                                                                                    | 70 |

| 4.6  | The direct mod and ref sets of each procedure are only to objects which are ⊤, procedure arguments, or return values of calls − references to objects allocated within the procedure are not visible externally. In our fibtree example, the direct mod and ref sets |    |

|      | are all to procedure arguments.                                                                                                                                                                                                                                      | 72 |

| 4.7  | Procedure for propagating mod/ref information interprocedurally                                                                                                                                                                                                      | 72 |

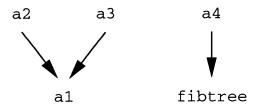

| 4.8  | Binding multi-graph for fibtree example. We know from Stage 1 that a1 is written, so we determine that a2 and a3 are also written. We know from Stage 1 that fibtree is read,                                                                                        |    |

|      | so we determine that a4 is also read                                                                                                                                                                                                                                 | 73 |

| 4.9  | Procedure for resolving aliases from procedure arguments                                                                                                                                                                                                             | 74 |

| 4.10 | Procedure for resolving aliases from return values                                                                                                                                                                                                                   | 77 |

| 4.11 | Incorporating interprocedural information locally                                                                                                                                                                                                                    | 78 |

| 4.12 | In Stage 5, we augment each of the calls with the objects which are potentially read and written, and propagate this information through conditionals and loops, and back through the call tree, if necessary.                                                       | 78 |

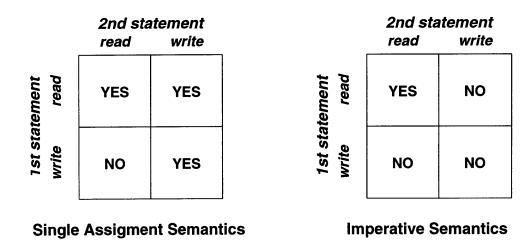

| 4.13 | Dependence matrices which determine when nodes can execute in parallel. Single-assignment semantics allow more nodes to be executed in parallel than imperative se-                                                                                                  | 70 |

|      | mantics                                                                                                                                                                                                                                                              | 79 |

| 4.14 | In Stage 6, we decide whether to add dependencies between references, using the dependence matrix for single-assignment semantics                                                                                                                                    | 80 |

| 4.15 | In Stage 7, we characterize all loop induction variables as being either <i>constant-incrementing</i> reduction, or other. Loops which have any induction variables which are classified as                                                                          | 7, |

|      | other we do not parallelize                                                                                                                                                                                                                                          | 82 |

| 4.16 | In Stage 8, we first check if there are any loop carried dependences due to induction variables, and then we check whether there is any intersection between the mod and ref sets of the loop. If there are no loop carried dependences in the induction variables and the intersection of the mod and ref sets is the empty set, then we can parallelize the loop | 84  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

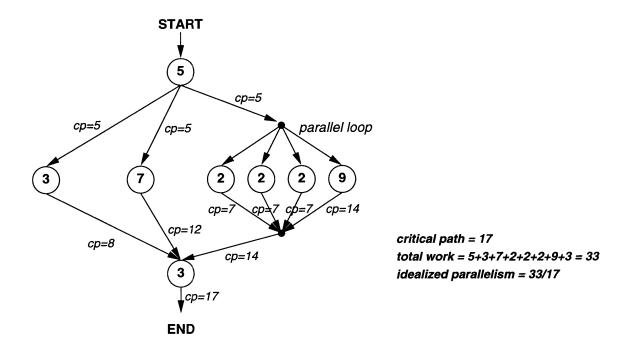

| 4.17 | Example of idealized parallelism calculation. The critical path and total work is calculated, and the idealized parallelism is the ratio of the total work to critical path                                                                                                                                                                                        | 87  |

| 4.18 | Idealized parallelism for structured codes, showing the effects of DAG parallelism, loop parallelism, and both types of parallelism.                                                                                                                                                                                                                               | 89  |

| 4.19 | Idealized parallelism for unstructured codes                                                                                                                                                                                                                                                                                                                       | 92  |

| 4.20 | Idealized parallelism assuming imperative and single-assignment semantics. Single-assignment has a greater effect on structured codes – for unstructured codes, the functional style of programming forced by single-assignment semantics is more important.                                                                                                       | 96  |

| 4.21 | Example program to illustrate interaction of DAG and loop parallelism. The function slow_seq_function is very slow, performs no side effects, and takes a constant amount of time                                                                                                                                                                                  | 99  |

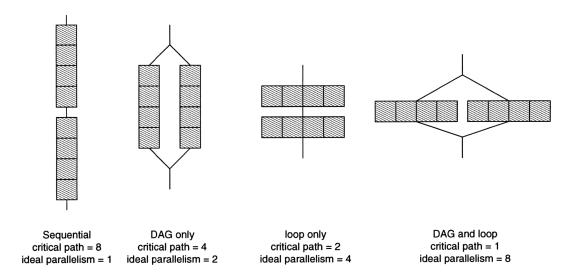

| 4.22 | The parallelism of two_par_loops under different assumptions about parallelization. Exploiting both DAG and loop parallelism is better than exploiting just one or the other.                                                                                                                                                                                      | 100 |

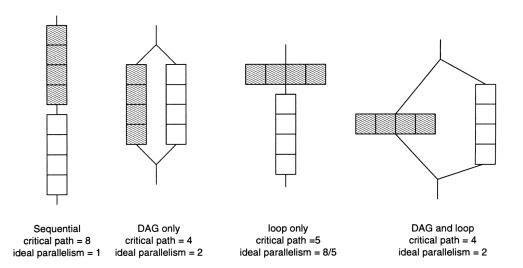

| 4.23 | The parallelism of one_par_one_seq under different assumptions about parallelization. The shaded loop is parallelizable, whereas the unshaded loop is unparallelizable. Exploiting both DAG and loop does not provide any incremental improvement over just DAG parallelism, because the critical path does not change                                             | 101 |

| 4.24 | The FFT program illustrates the effect of exponential total parallelism in comparison to individual DAG and loop parallelism. The "Total Work", "Critical Path" and "Ideal Parallelism" data are collected by instrumenting the FFT program and running under different problem sizes                                                                              | 102 |

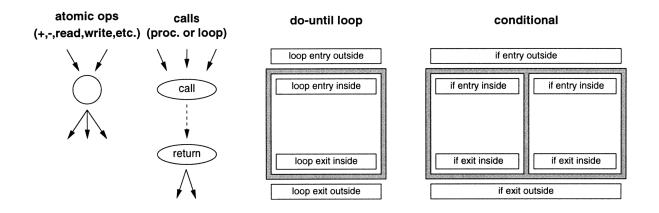

| 5.1  | Dataflow graph nodes                                                                                                                                                                                                                                                                                                                                               | 107 |

| 5.2  | Pre-partitioning to make encapsulators atomic                                                                                                                                                                                                                                                                                                                      | 108 |

| 5.3  | Separation Constraint Partitioning                                                                                                                                                                                                                                                                                                                                 | 109 |

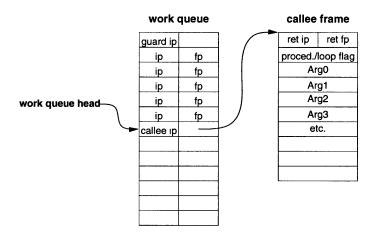

| 5.4  | The calling convention pushes procedure calls onto the main work queue, in ip/fp continuations. The fp points to a frame, which contains the procedure arguments, as well as the return continuation, and a flag to tell whether the frame is associated with a pro-                                                                                               | 110 |

| 5.5  | cedure call or parallel loop call                                                                                                                                                                                                                                                                                                                                  | 110 |

| 5.6  | Join counter assignment.                                                                                                                                                                                                                                                                                                                                           | 114 |

| 5.7  | Join synchronization typically occurs less often than procedure calls, and is only frequent for programs which make a lot of procedure calls. Many of the join synchronizations can be optimized into binary immediate joins, and join synchronization does not                                                                                                    | 116 |

|      | add significant code generation overhead                                                                                                                                                                                                                                                                                                                           | 116 |

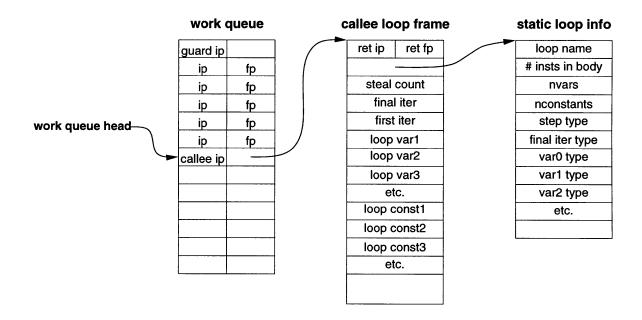

| 5.8  | Parallel loop calling convention                                                                                                                                                                                                                                                                                 | 118 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.9  | The loop chunking protocol is used to "strip mine" loop iterations and reduce the overhead of parallel loop execution, while exposing loop parallelism.                                                                                                                                                          | 119 |

| 5.10 | Simple minded algorithm to set the parallel loop chunk                                                                                                                                                                                                                                                           | 120 |

| 5.11 | Cumulative overheads from the calling convention, join synchronization and parallel loops for the structured codes. The rightmost bars are our starting points in parallel execution                                                                                                                             | 122 |

| 5.12 | Cumulative overheads from the calling convention, join synchronization and parallel loops for the unstructured codes. The rightmost bars are our starting points in parallel execution                                                                                                                           | 123 |

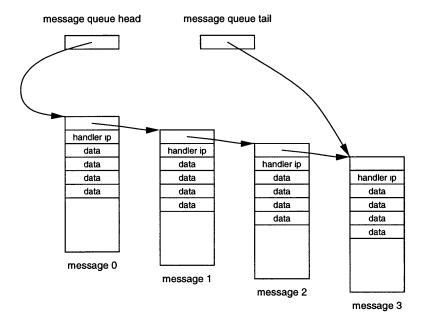

| 6.1  | The structure of the active-message passing layer on shared memory. Each processor has a message queue head, tail and lock, all of which reside in shared memory. Messages are linked fixed-sized blocks of shared memory                                                                                        | 126 |

| 6.2  | Polling overheads shown by running identical parallel-ready codes with polling and without polling on one processor. Polling is done before every procedure entry or loop chunk execution. Polling does not show a significant overhead, except for procedure-call intensive codes such as fib, nqueens and tree | 127 |

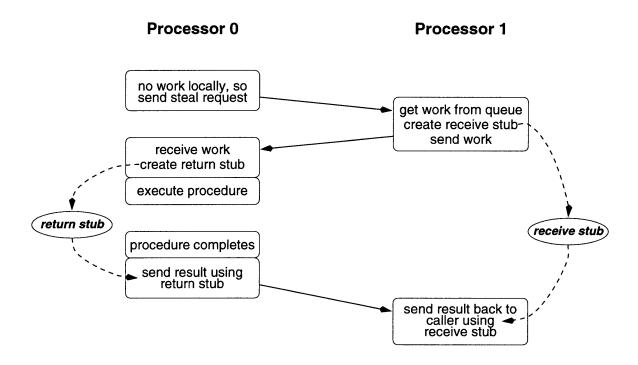

| 6.3  | The basic steal protocol – idle processors send requests to random processor for work. If the request is satisfied, the idle processor executes the work, and when done, sends back the result.                                                                                                                  | 129 |

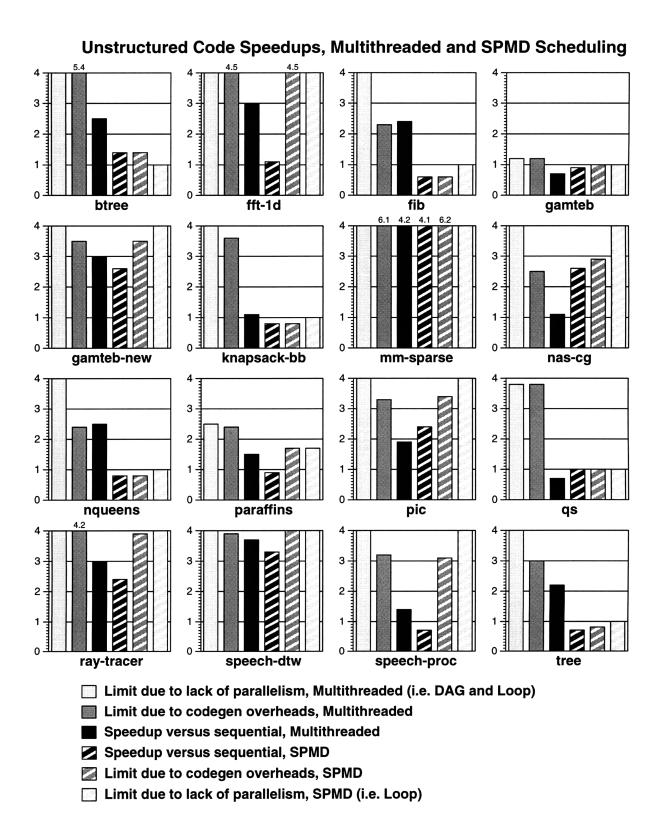

| 6.4  | Speedups on 4 processors for structured applications under work-stealing multithreaded and SPMD scheduling. The outer bars show the limitations due to lack of parallelism and code generation overheads                                                                                                         | 133 |

| 6.5  | Speedups on 4 processors for structured applications under work-stealing multithreaded and SPMD scheduling. The outer bars show the limitations due to lack of parallelism and code generation overheads                                                                                                         | 134 |

| 6.6  | Speedups for "warshall 400" when freeing memory and not freeing memory, running under the SPMD scheduler. Note that the sequential times for this were 37.7 seconds when freeing memory and 55.2 when not freeing memory.                                                                                        | 136 |

|      |                                                                                                                                                                                                                                                                                                                  |     |

### Chapter 1

### Introduction

After decades of research and years of turmoil in industry, parallel computers have finally entered the mainstream in the form of relatively cheap, small-scale, shared-memory Symmetric Multiprocessors (SMP's). Every major computer manufacturer is now making and selling SMP's, but despite this proliferation of hardware, users cannot easily exploit this parallelism except for a subset of well-structured "scientific" applications and relatively coarse-grained throughput applications such as database servers and Web servers.

In this thesis, we describe an approach to exploiting parallelism on SMP's which has several advantages over previous approaches to parallel computing:

- It runs on stock hardware using a stock operating system.

- The programmer writes in a sequential style, leaving parallelization, work partitioning, synchronization, communication and scheduling to the compiler and run-time system.

- It handles both *structured* and *unstructured* parallelism, which requires solving problems at two different levels:

- 1. Discovering both structured and unstructured parallelism in sequential programs.

- 2. Scheduling possibly unstructured work on the processors with good load balance and low overhead.

This work bridges the gap between two very different approaches to parallel computing: Id90 on Monsoon and Fortran on SMP's. The Id90/Monsoon approach [62] [43] exposes implicit parallelism at the language level while requiring extensive hardware support for fine-grained synchronization and communication. Every level of parallelism is exploited, including instruction, procedure, loop, and

Figure 1.1: Our approach straddles two previous approaches to parallel computing: Id on Monsoon and Fortran on SMP's, attempting to take advantage of the strengths of each.

producer-consumer parallelism. The Id90/Monsoon approach can support both structured and unstructured parallelism at a significant cost in hardware and re-coding of applications. However, to the first degree, the programmer does not need to concern himself with explicit parallelization, work partitioning, synchronization, communication or scheduling.

The Fortran/SMP approach, exemplified by the SUIF [6] compiler, can take advantage of stock hardware and OS's for parallelizing many existing Fortran codes without programmer intervention. This approach exploits coarse-grained loop parallelism, where data structure accesses within the loop are affine functions over the iteration space and work is relatively well-balanced across the loop iterations. We call such parallelism *structured parallelism*. The Fortran/SMP approach emphasizes compiler analysis and transformations to parallelize codes and discover coarse-grained parallelism, while taking a semi-static approach to work scheduling and distribution.

Our approach, as shown in Figure 1.1, attempts to exploit structured and unstructured parallelism on stock hardware. We compile Id-S, a variant of the Id90 language, and perform interprocedural data dependence analysis to determine when we can exploit procedure parallelism and loop parallelism. Our analysis is greatly aided by the Id-S semantics, which require that each data structure element be written to at most once, thereby eliminating anti- and output- dependences at the source level. We then generate code which is scheduled dynamically on the SMP processors. A combination of compiler and run-time system support allows us to obtain a coarse-grain of parallelism at run-time. We have been able to compile almost all Id90 programs with minor changes, showing speedups on most codes.

#### 1.1 Parallelism and efficiency

Our work builds on previous efforts to compile Id90 for conventional microprocessors, including TAM [25] [32] [72], P-RISC [56], and pHluid [18]. Our approach differs from those previous efforts in that we have changed the Id language semantics and opted to forgo fine-grained producer-consumer synchronization in order to improve the *efficiency* of the language implementation. *In effect, we are trading off parallelism for efficiency* – this tradeoff is necessary because we do not have hardware support for producer-consumer synchronization and we are targeting small machines.

#### 1.1.1 Overheads in previous Id implementations

The only published parallel speedup data for an Id implementation targeted for "conventional" (i.e. non-dataflow) architectures are for TAM [72] running on the CM-5. These data include a linear speedup of 16 on 64 processors for the Simple benchmark. The linear speedup indicates that there was enough parallelism exposed to execute on 64 processors.

A further examination of the data from [72] reveals that the speedup numbers are relative to the same parallel executable running on 1 processor of the CM-5. However, this parallel executable is more than twice as slow as the same program compiled under the same TAM compiler for single-processor execution (as opposed to a 1-processor execution of a parallel-ready code), because of overheads introduced for real parallel execution – these overheads include support for remote memory references and parallel work distribution. In Chapter 3, we show that even the single-processor TAM implementation is twice as slow as it might be because of its support for fine-grained synchronization and scheduling.

In all, the linear speedup of 16 on 64 processors is actually a linear speedup of less than 4 when compared to an efficient sequential implementation. In effect, the program is slowed down by a factor of 16, and then run on 64 processors to get a factor of 4 overall speedup.

This is an extreme case, but the parallelism/efficiency tradeoff is a serious issue when considering implementation alternatives. Running on a relatively small SMP, we certainly cannot afford a factor of 16 overhead, even if it promises us abundant parallelism, but as the simple analysis in the next section shows, we probably cannot afford even a more realistic overhead of 2.5, except when there is relatively little parallelism to be exposed.

Figure 1.2: Assuming P is the fraction of a code which can be parallelized, and Overhead is the ratio of run-time versus sequential execution, these graphs show the speedups under two scenarios assuming the parallel part of the code speeds up perfectly. In general, efficiency is more important than parallelism for small numbers of processors, except when parallelism is low.

#### 1.1.2 Analysis of parallelism/efficiency tradeoff

With a small number of processors and high synchronization overheads, additional parallelism may not make up for a loss in efficiency. Figure 1.2 shows speedups under a very simple analytical model. Let us assume that a code runs in time T in an efficient sequential implementation. In order to enable the code to run in parallel, assume there is an overhead factor OV such that a parallelized code running on one processor takes time  $T \times OV$ . Assume that the code consists of a perfectly parallelizable fraction P and a sequential fraction (1 - P). The total run-time of a code running on n processors is then  $T \times OV \times ((1 - P) + P/n)$ , and the speedup on n processors is:

$$\mathrm{Speedup} = \frac{1}{OV \times ((1-P) + P/n)}$$

We then plug in values of OV and P to compare the speedups of a more efficient (OV = 1.25, P = .5, .95, .995) and a more parallel (OV = 2.5, P = .95, .995, .9995) version, where the more parallel version has a sequential section which is 10 times smaller than the more efficient version (i.e. has 10 times more parallelism). The factor of 2.5 overhead is a very conservative estimate of the fine-grained overhead introduced by a TAM-style Id implementation – this is analyzed in greater depth in Chapter 3.

The graphs show that for a small number of processors ( $\leq 10$ ), the additional parallelism of the high overhead scenario does not make up for the additional overhead, except in the case of low parallelism, and then, only for more than 4 processors.

Figure 1.3: In exploiting structured and unstructured parallelism, there are two main, somewhat decoupled components: (1) exposing parallelism and (2) code generation and scheduling. We attack the first with a combination of language support and compiler analysis, and we handle the second with methods for efficient code generation and scheduling.

Of course, the tradeoffs depend significantly on the actual overhead parameters, and the difference in exploitable parallelism. In some cases the difference in overhead may be greater or smaller, and the difference in parallelism may be greater or smaller, but Figure 1.2 gives an intuitive feeling for the tradeoffs we are considering.

The overhead parameters we chose fit closely with the analysis in Chapter 3 comparing the more parallel Id90 with the more efficient Id-S. The parallelism regime in which we operate (i.e. low, medium or high) depends upon the effectiveness of our parallelization analysis and the characteristics of the codes we are considering. If the parallelization yields enough exploitable parallelism that we are operating in the medium or high range, then any additional parallelism we could have exploited with a more fine-grained approach would not be not necessary.

#### 1.2 Structured versus unstructured parallelism

In our system, we would like to exploit structured as well as unstructured parallelism. Structured parallelism is loop parallelism where data structure accesses are affine functions of the iteration space, and where work is relatively well balanced across the loop iterations. Unstructured parallelism is all other parallelism, including procedure parallelism, and whole loop parallelism (e.g. two separate loops executing in parallel) – in unstructured parallelism, work may be unbalanced and the granularity of work may be unknown at compile time, or even by the programmer. We are not concerned with instruction-level parallelism, and leave that to the individual superscalar microprocessors in the SMP.

Exploiting parallelism requires solving two separate problems: (1) exposing parallelism and (2) code generation and scheduling. As shown in Figure 1.3, we address the first problem with the language

and compiler middle-end and the second problem with the compiler back-end and run-time system. The two problems are decoupled to the extent that different strategies for attacking them can be mixed and matched.

#### 1.2.1 Exposing parallelism

Traditional Fortran loop parallelizing compilers expose parallelism using a combination of ad hoc nested loop data dependence analyses [48] [86] and interprocedural "region-based" and linear-inequality driven analyses and transformations [13] [65] [6] [38]. These approaches can work well for very structured Fortran programs where most of the work lies in nested loops, and where accesses to large, flat, static data structures in the loops are affine functions of the iteration space.

However, these Fortran techniques do not work as well for programs which have less structured accesses to data structures – for example, where most work does not lie in loops, or where accesses are not affine, or where nested data structures such as lists, trees and other non-array structures are used. Most of the research in unstructured parallelization has focused on pointer analysis in the context of C programs [84], but this work has had only limited success, largely due to the difficulty of handling C's very low-level semantics.

We take the approach of requiring some language support by having the user to program in a style which gives the compiler more information about data dependences. Because Id-S is a single-assignment language (i.e. each data structure element can only be written once), the compiler does not need to check for anti- or output- dependences, which can obscure some parallelism. Furthermore, the single-assignment semantics forces the user to use dynamic heap allocation, which allows the compiler to further distinguish between structure accesses, exposing more parallelism.

The net result is that we can use a very simple interprocedural data dependence analysis to find both loop and procedure parallelism. Fortran techniques would still be useful for a few loops that our approach cannot analyze, but our simple technique finds most of the loops Fortran techniques would find, and can also handle some loops with non-affine accesses or accesses to nested data structures, which Fortran techniques typically cannot handle. In general, our simple analysis is good enough that we have not bothered to implement the Fortran techniques.

The middle-end of the compiler is also responsible for giving a rough determination of when parallelism is worth exposing, and passing along this information to the back-end code generation phases. We describe some simple, effective techniques to avoid exposing too much fine-grained parallelism. The work-estimation phase is not as important as it would be in other systems because we have taken great care in the code generation and run-time system to minimize synchronization and parallel bookkeeping overheads, and to increase work granularity at run-time.

#### 1.2.2 Parallel execution model: SPMD vs. multithreading

Although traditional Fortran parallelizing loop compilers originally targeted vector supercomputers, more recent Fortran compilers [6] have targeted non-vector SMP's. These Fortran compilers generate mostly sequential code with parallelized outer loop iterations scheduled evenly across the processors. In this thesis, we call this execution model the *Single Program Multiple Data* (SPMD) execution model. SPMD works well for structured programs because work resides mostly in loops, and is well-balanced across loop iterations. Additionally, compiler-driven loop and data transformations can improve the locality of data references under SPMD execution [85].

The SPMD model has several drawbacks – it cannot effectively handle unbalanced loops, procedural parallelism, or nested parallel loops because loop iterations are distributed evenly across the processors, and only one level of loop parallelism is exploited. In contrast, the *multithreaded* execution model allows different processors to execute different procedure or loop activations, dynamically spawning, scheduling and synchronizing work. The multithreaded model is more general than the SPMD model, but may incur more overhead due to dynamic scheduling and synchronization, and poorer memory locality.

We use the terms "SPMD" and "multithreaded" very loosely – both terms can be used to describe a wide variety of execution models. Furthermore, we show that SPMD and multithreaded execution are two points on a continuum of execution models. We compile Id-S for *both* SPMD and multithreaded parallel execution, and compare their performance. For some highly structured applications, a more static, SPMD approach yields better performance, whereas for other, less structured, less loop-dominant applications, a more dynamic, multithreaded approach yields better performance.

In this thesis, we show how to structure multithreaded execution so that it can be performed efficiently, while being competitive with SPMD execution for many codes. Implementing multithreading efficiently requires efficient code generation techniques and adaptive, lightweight scheduling mechanisms.

#### 1.3 Thesis contributions

In this thesis, we focus on implementing a parallel software system to exploit symmetric multiprocessors. Almost all parallel computers today are SMP's, and SMP's are becoming cheaper and more common on the low-end, and larger and more powerful on the high-end. SMP's provide shared memory support directly in hardware, easing the burden on the programmer and compiler. However, SMP's do not provide any hardware support for fine-grained synchronization or scheduling. Synchronization is usually performed through relatively heavyweight locks to shared memory locations, and scheduling must be done completely in software. Consequently, the granularity of parallelism must be coarse enough to overcome the overheads incurred for synchronization and scheduling.

The organization of the software is the key to exploiting parallelism effectively on SMP's. We describe an approach which includes language, compiler and run-time system working in concert to expose and exploit parallelism efficiently.

#### 1.3.1 New language semantics

We introduce a variant of the Id90 language, which we call Id-S. Id-S has a sequential evaluation order like C or Fortran and single-assignment semantics like Id90. Id-S is not functional: data structures can be allocated, and reads and writes can be performed on the structures as in imperative languages, except that each structure element can only be written once. Id-S's sequential semantics do not preclude an implementation which exploits producer-consumer parallelism, and all legal Id-S programs are also legal Id90 programs which will execute, terminate and provide the same results if implemented on previous Id90 systems, including Monsoon.

We changed the Id semantics to provide a sequential evaluation order because the fine-grained, implicitly parallel dataflow semantics of Id90 are difficult to implement efficiently on non-dataflow hardware, and as we discussed in Section 1.1, the parallelism exposed by Id90 would not make up for the overhead incurred. The sequential semantics also give more information to the compiler about dependences caused by reads and writes.

We chose to compile Id-S rather than C or Fortran because the single-assignment semantics allowed us to both simplify parallelization analysis for structured loops, and also handle unstructured codes which would be difficult or impossible to parallelize under imperative semantics.

| Performance comparison (seconds on SparcStation 10) |            |                 |      |           |  |

|-----------------------------------------------------|------------|-----------------|------|-----------|--|

|                                                     | Input Size | strict TAM Id90 | Id-S | C/FORTRAN |  |

| Gamteb                                              | 40,000     | 169.5           | 88.3 |           |  |

| MMT                                                 | 500        | 61.0            | 22.2 | 19.8      |  |

| Paraffins                                           | 19         | 2.2             | 1.6  |           |  |

| Quicksort                                           | 10,000     | 1.5             | 0.8  | 0.6       |  |

| Simple                                              | 1 1 100    | 2.7             | 1.1  | 1.0       |  |

| Speech                                              | 10240 30   | 0.6             | 0.16 | 0.12      |  |

Figure 1.4: Id-S is the fastest implementation of Id to date, and comparable in performance to C or Fortran.

Surprisingly, we found that almost all existing Id90 programs could be converted to Id-S programs, simply by reordering bindings within blocks. Almost all of the Id90 programs we found which we could not convert to Id-S were toy programs designed explicitly to exploit Id90's non-strict, implicitly parallel dataflow semantics.

#### 1.3.2 New compiler parallelization and code-generation

The core of our research is built around a new Id compiler can work with varying language semantics, exploiting different levels of parallelization, and using different code-generation strategies.

Id-S's sequential evaluation order allows us to generate more efficient code for conventional micro-processors than for Id90, while the single-assignment semantics allows us to perform more parallelization than for Fortran or C. Our sequential implementation of Id-S is the fastest implementation of Id to date, with performance competitive with sequential Fortran or C. Figure 1.4 shows our performance relative to strict TAM Id90 and C or Fortran – the TAM performance numbers are from [72]. Identical Id programs were compiled for TAM and Id-S, and similar (or more efficient) algorithms were used for the C and Fortran programs. No C or Fortran programs using the same algorithms were available for Gamteb or paraffins. More details about the input sizes and structure of the programs are given in Sections 3.1 and 4.5.

#### 1.3.3 Parallelism and efficiency tradeoff

Using our sequential Id-S implementation as a baseline, we perform a detailed evaluation of the overheads in the state-of-the-art implementations of Id90 for conventional microprocessors. Our results show where improvements could be made in implementations with element-wise data structure synchronization, but also lead us to conclude that such an implementation would have overheads which are too high to overcome any benefits from additional parallelism.

#### 1.3.4 Parallelizing Id-S

We give an algorithm for parallelizing Id-S which is based on existing interprocedural data dependence analyses. These analyses yield more results for Id-S than they do for imperative languages because of Id-S's single-assignment semantics and frequent heap allocations.

We instrument our compiled code to provide us with ideal parallelism numbers to give us an idea of how effective our parallelization is, and where it is weak. The ideal parallelism numbers allow us to separate the effectiveness of the parallelization from the details of the code generation and scheduling.

By disabling or modifying certain parallelization analyses, we also show the separate effects of procedure and loop parallelism, and how much parallelism we could discover if we do not assume single-assignment semantics.

#### 1.3.5 Parallel code generation and run-time system

We describe our code generation schemas which are tightly linked with the run-time system. We show some control-flow style optimizations performed to make hooks into the run-time system cheaper.

We describe the structure of the run-time system, which increases work granularity at run-time using lazy work-stealing techniques. Our run-time system also handles loop and procedure parallelism uniformly, thereby simplifying our run-time system entry-points. Some simple compile-time work-estimation is performed to eliminate fine-grained parallelism which cannot be profitably exploited.

#### 1.3.6 Parallel performance

Finally, we give performance numbers on an 8-processor Sun Microsystems Ultra HPC 5000 SMP, and analyze sources of lost performance on benchmarks which do not achieve perfect speedup. The potential sources of overhead we examine include:

• Parallel overheads due to code generation – although we attempt to keep overheads due to code generation down as much as possible, we still have some overhead compared to sequential execution.

- Insufficient parallelism some codes do not parallelize well, because of limitations of the compiler. Some codes simply do not have much parallelism to exploit.

- Run-time system overheads run-time system overheads include time to distribute work and synchronize on returning work. Run-time system overheads typically show up for codes which have a small work granularity and/or low parallelism. SPMD scheduling typically has less overhead than multithreaded scheduling, although for many codes, the difference is insignificant.

- Load balance for some codes, a simple SPMD scheduling leads to load imbalance, whereas multithreading scheduling can handle more

- Memory system limitations certain codes are fundamentally limited by the main memory bandwidth of the SMP. Some codes will not show good speedup unless heap memory is reclaimed because of poor cache behavior and memory bandwidth limitations.

We show some speedups for almost every code we ran, validating our approach.<sup>1</sup> Performance could be improved on the compiler side by improving code generation and parallelization. On the run-time system side, it could be improved by better (more robust) scheduling policies and a tighter implementation.

#### 1.3.7 Issues not addressed in this thesis

Many issues remain unaddressed in this thesis because of a lack of time and resources. In a production Id system, garbage collection or some other form of automatic memory management [44] would be necessary to avoid running out of heap memory. Our system currently places this burden on the programmer, which is both tedious and error-prone. The effect of garbage collection on parallelism and performance might be somewhat different from our results.

Fortran techniques would be useful both for parallelizing loops which cannot be handled by our system, and for restructuring to improve usage of the memory hierarchy. Currently, we perform no locality optimizations in the compiler or run-time system. Many locality transformations are orthogonal to scheduling, and could provide improvements for multithreaded execution as well as SPMD execution.

Our compiler depends upon interprocedural analysis for parallelization. Currently, this is implemented by compiling the entire program at once, but interprocedural analysis can also be performed with separate compilation by maintaining some file information in a database, or by pushing some of the compilation to the linking phase.

$<sup>^1</sup>$ The Id-S benchmarks that we used to evaluate the language, compiler and run-time system can be retrieved at http://www.csg.lcs.mit.edu/~shaw-phd-id.tar.gz.

| Year      | System             | Researchers and References                                   |

|-----------|--------------------|--------------------------------------------------------------|

| 1987      | Id / TTDA          | Arvind, Nikhil, Iannucci, Traub, etc. [9] [10]               |

| 1989      | Id / Monsoon       | Papadopoulos and Culler [62], Hicks, Chiou, Ang, Arvind [43] |

| 1988-1995 | Id partitioning    | Traub [81] [82], Schauser [72], Coorg [22]                   |

| 1991      | Id / TAM           | Culler, Goldstein, Schauser, von Eiken [25] [32]             |

| 1992      | Id/P-RISC          | Nikhil [56]                                                  |

| 1992      | EM-C/EM-4          | Sato, Sakai, etc. [66] [68]                                  |

| 1993      | Id / StarT-88110MP | Carnevali, Shaw [55]                                         |

| 1994      | Cilk / CM-5        | Zhou, Halbherr, Joerg, etc. [37]                             |

| 1994      | Id/pHluid          | Chiou, Nikhil [18]                                           |

| 1997      | Id97 / SMP's       | This Work                                                    |

Figure 1.5: The Id97 system has dataflow roots but has moved towards implementation on more conventional architectures.

We only show performance results for relatively small ( $\leq$  8 processor) systems – for larger systems, locality, synchronization and communication become more of a concern, and the techniques we use may have to be modified or augmented.

#### 1.4 Related work

The direct roots to the approach in this thesis have a long history, dating back to dataflow architectures and implicitly parallel functional programming languages. The general direction of this work has been from functional languages and heavy architectural support towards more conventional languages running on standard commercial hardware.

#### 1.4.1 Direct ancestors to this research

Figure 1.5 shows some of the systems which are direct ancestors to the Id97 system. The original implementation of Id was on the Tagged-Token Dataflow Architecture (TTDA) [9] [10] [80], which was a simulated dataflow architecture. Each TTDA instruction synchronized on the arrival of its input values, and direct support for element-wise data structure synchronization existed in the form of I-structure boards.

Monsoon [62] was the direct successor of TTDA, and was realized in hardware. Monsoon had a explicit token matching store, and introduced the notion of activation frames as a synchronization namespace and temporary storage. Monsoon also had direct support for I-structures.

Ken Traub [81] developed the early theory of compiling the non-strict Id language into sequential threads to be executed on more conventional von Neumann architectures. The TAM compiler [25] [32] actually implemented some simple partitioning algorithms, and compiled Id for conventional microprocessors. Over the course of a few years, partitioning algorithms for non-strict Id improved with contributions from Traub [82], Klaus Schauser [72] and Satyan Coorg [22]

The P-RISC effort [56] was a combination of partitioning compiling technology and a few machine instructions to create a "Parallel RISC" instruction set. This eventually led to the StarT-88110MP machine, which was to be based on a modified Motorola 88110 processor. Derek Chiou and Rishiyur Nikhil continued on a P-RISC implementation of Id with the pHluid compiler [18], which was targeted towards sequential workstations and clusters of workstations.

I spent a year in Japan working on the EM-4 [66] project at the Electrotechnical Laboratory. EM-4 was a hybrid dataflow / von Neumann architecture, programmed using EM-C [68], a dialect of C with support for explicit threading and synchronization. This work bridged some of the gap for me between dataflow and von Neumann machines.

In 1994, Yuli Zhou developed a C pre-processor which he used to write explicitly parallel C programs for the CM-5 in a system which eventually became Cilk [37]. He and Michael Halbherr rediscovered the fact that much of the overhead of multithreading was actually in run-time scheduling, and that lazy task stealing could significantly lower communications and synchronization overhead, even for the CM-5 which had very expensive communication and no explicit support for fine-grained synchronization. Lazy work stealing was originally exploited in the Multilisp system [40] and a similar idea was exploited in lazy task creation [52] on Alewife [2].

The work in this thesis grew out of my frustrations with explicitly parallel languages, and the success of lazy work stealing in Cilk to reduce multithreading overheads. Although EM-C and Cilk were efficient, they were very difficult to use because parallelization and synchronization were left to the programmer. Id gave a much nicer programming model to the user, and had shown ample parallelism for a variety of applications, but seemed to incur too much overhead on conventional microprocessors. I had written the first SMP implementation of Cilk, and I knew work stealing could eliminate some of the overheads in scheduling Id programs. I began work to find the the overheads of implementing Id on SMP's which resulted in this thesis.

#### 1.4.2 Related hardware

The underlying multithreaded execution model we implement in software has its roots in multithreaded hardware, including dataflow machines such as Monsoon [62], EM-4 [66], Sigma-1 [45] and the Manchester Machine [36]. Very similar in spirit to the dataflow machines are the HEP [76] and Tera [4]. Alewife [2] and the J-Machine [58] also provide support for multithreaded execution, although these machines are closer to conventional sequential machines.

#### 1.4.3 Related languages

Sisal is a strict functional language [17] which has been compiled for parallel execution on a number of platforms, including sequential workstations, vector supercomputers, and SMP's [67]. Id97 differs from Sisal in that Id97 is not functional – empty objects can be allocated and reads and writes can occur to those objects. Cilk [16], EM-C [68], and Cid [57] are explicitly parallel dialects of C which have a multithreaded implementation.

#### 1.4.4 Related compilers

The data dependence analysis for the Id97 compiler is inspired by Fortran loop parallelization techniques [48] [86] [13] [65]. Recent work by the SUIF project has extended this loop parallelization to including loops containing function calls, and loop restructuring for memory locality [6] [38]. The interprocedural analysis necessary for parallelizing Id97 is based on Banning's interprocedural alias analysis [15], and Cooper and Kennedy's advances [19] [20] on Banning's original algorithms.

#### 1.4.5 Related multithreading run-time systems

The thread representation and scheduling work is a direct descendant of TAM [25], P-RISC [56] [18], and Cilk [37] [16] [46]. It is also closely related to Lazy Task Creation [52] and Lazy Threads [35] [34]. Lightweight thread representations and scheduling techniques have also been implemented in C-style thread libraries such as Filaments [29] [30] and other threads packages [47] [53] [21].

#### 1.5 Outline of thesis