## **KIRCHOFF'S VOLTAGE LAW**

**Kirchoff's Voltage Law:** Around any loop:  $\sum_i V_i = 0$ (KVL)

Faraday's Law:

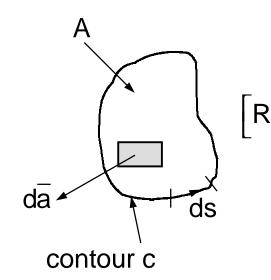

$\nabla \times \overline{\mathsf{E}} = -\partial \overline{\mathsf{B}} / \partial t \quad [\text{differential form}]$ Integral form is:  $\oint_{\mathsf{C}} \overline{\mathsf{E}} \bullet d\overline{\mathsf{s}} = -\frac{\mathsf{d}}{\mathsf{d}t} \int_{\mathsf{A}} \overline{\mathsf{B}} \bullet d\overline{\mathsf{a}}$ [Recall Stoke's Theorem:  $\int_{\mathsf{A}} (\nabla \times \overline{\mathsf{G}}) \bullet \hat{\mathsf{n}} d\mathsf{a} = \oint_{\mathsf{C}} \overline{\mathsf{G}} \bullet \overline{\mathsf{d}}\mathsf{s}$ ]

If  $d\overline{B}/dt = 0$  in A, then Kirchoff's voltage law must be satisfied

More generally:

KVL assumes all magnetic energy is stored inside circuit elements

## **KIRCHOFF'S VOLTAGE LAW (2)**

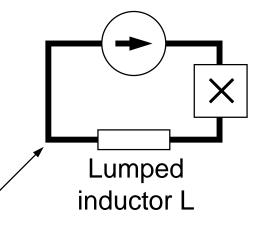

**Undefined Circuit:**

i(t) = cos  $\omega t$  $A = \frac{d}{dt} \int_A \overline{B} \cdot d\overline{a} \neq 0 \Rightarrow \text{ voltage!}$

### **Defined Circuit:**

We assume voltage drops occur only across elements, and ignore H fields generated by currents through them.

We use small loops, thick wires, and high-impedance lumped elements

"parasitic inductance"

## **KIRCHOFF'S CURRENT LAW (KCL)**

**Kirchoff's Current Law:**  $\sum_{i} I_{i} = 0$  = Total current into any node (KCL)  $\nabla \times \overline{H} = \overline{J} + \partial \overline{D} / \partial t$  [differential form] **Ampere's Law:**  $\nabla \bullet (\nabla \times \overline{H}) = \nabla \bullet (\overline{J} + \partial \overline{D} / \partial t) = 0$  $= \nabla \bullet \overline{J} + \partial (\nabla \bullet \overline{D})/\partial t$  $= \nabla \bullet \overline{J} + \partial \rho / \partial t$  $\nabla \bullet \overline{J} = -\partial \rho / \partial t$  = 0 at each node **Conservation of Charge:** Recall Gauss's Divergence Theorem:  $\int_{V} (\nabla \bullet \overline{G}) dv = \int_{S} \overline{G} \bullet \overline{da}$ **Current Law follows from:**  $\int_{S} \overline{J} \cdot d\overline{a} = \sum_{i} I_{i} = 0$  da

More generally:

KCL assumes nodes and wires store no charge  $(\partial \rho / \partial t = 0)$ , or that all electric energy is stored inside circuit elements

"parasitic capacitance"

### **SOLVING CIRCUITS**

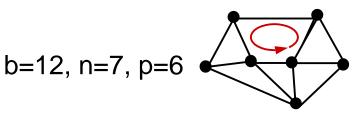

### **Generic Circuit Topology:**

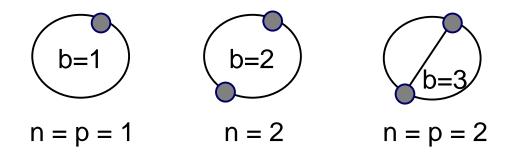

Assume b branches, n nodes, and p unique loops

We can show b = n + p - 1.

Every time we add a branch, the number of nodes or loops (meshes) increases by one.

Voltage sources are branches characterized by  $v = V_o$ Current sources are branches characterized by  $i = I_o$

# **SOLVING CIRCUITS (2)**

Number of Unknowns: Number of unknowns is 2b (v,i for each branch)

**Number of Equations:**

We have one device equation for each branch relating or specifying v and i

We also have n - 1 independent node equations (KCL) and p loop equations (KVL), for a total of:

b + (n-1) + p = 2b equations = number of unknowns

(Recall b = n + p - 1)

Given initial conditions and all sources we can solve the equations analytically for simple circuits, or by simulation for any circuit.

(Non-unique exceptions: indeterminate flip-flop or chaotic circuits)

## SIMPLE CIRCUIT ELEMENTS, R AND C

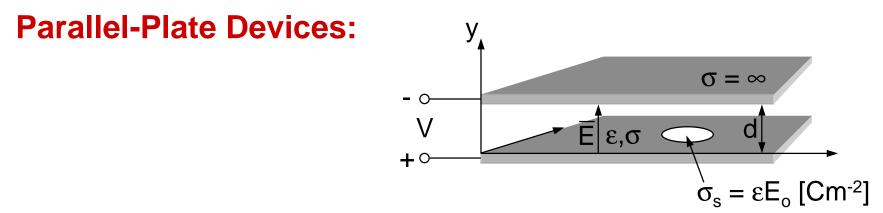

### **Electrostatics:**

In general:Everywhere $\nabla \times \overline{E} = 0$ , $\nabla \bullet \overline{E} = \rho/\epsilon$ At conductor $\hat{n} \bullet \overline{E} = \sigma_S / \epsilon$ , $\overline{E} / / = 0$ Between conductors, $\nabla \bullet \overline{E} = \rho/\epsilon = 0$

### **Field Solution:**

$\overline{E}=\hat{y}E_{0}$  for rectangular geometry here  $\sigma_{s}=\epsilon E_{0}$

### **SIMPLE CAPACITOR**

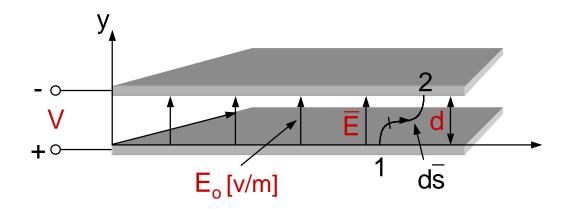

### **Relating Fields to Potentials:**

In general, absolute potential  $\Phi = 0$  at infinity, by definition

## **SIMPLE CAPACITOR (2)**

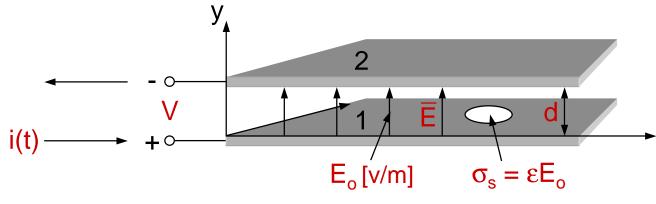

### **Capacitor Charge Q:**

We define:

$$Q = \int_A \sigma_s da = A \epsilon E_0 = A \epsilon V/d$$

We also define:

### **Capacitance C:**

Therefore:

We know:

Therefore:

$$C = A\epsilon/d$$

$$q(t) = \int_{-\infty}^{t} i(t)dt = Cv(t)$$

$$v(t) = (1/C) \int_{-\infty}^{t} i(t)dt$$

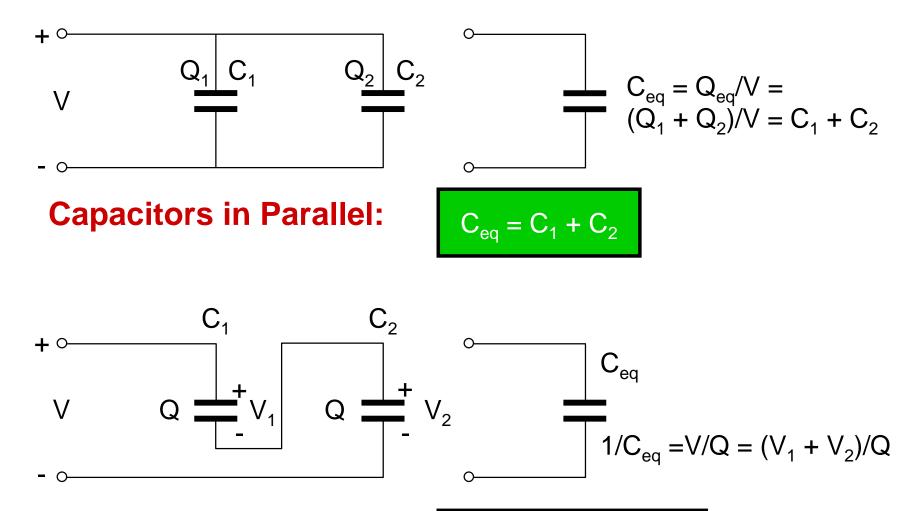

### **CAPACITORS IN SERIES AND PARALLEL**

**Capacitor in Series:**

$$1/C_{eq} = 1/C_1 + 1/C_2$$

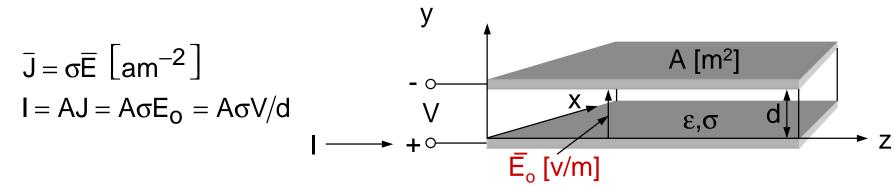

### SIMPLE RESISTORS

#### **Conductance** $\sigma$ :

Resistance R: $R = V/I = d/A\sigma$ Resistors in Series: $R_{eq} = R_1 + R_2$  $R_{eq} = (V_1 + V_2)/I$ Resistors in Parallel: $1/R_{eq} = 1/R_1 + 1/R_2$  $1/R_{eq} = (I_1 + I_2)/V$

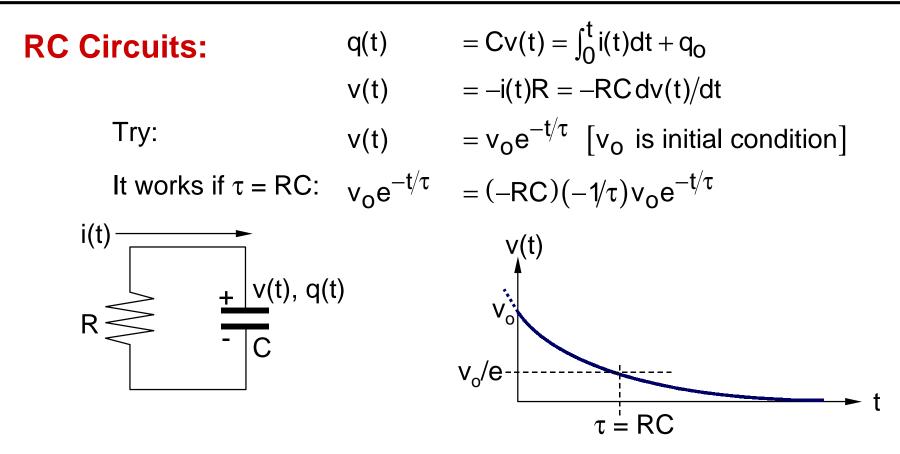

## **CHARGE RELAXATION**

#### **Dielectric Relaxation:**

$$R = d/A\sigma, C = \in A/d$$

$\tau = RC = \varepsilon/\sigma$  seconds "Relaxation time constant"

independent of geometry