# Fast Thread Communication and Synchronization Mechanisms for a Scalable Single Chip Multiprocessor

by

### Stephen William Keckler

B.S. Electrical Engineering, Stanford University, 1990 S.M. Computer Science, Massachusetts Institute of Technology, 1992

Submitted to the Department of Electrical Engineering and Computer Science In Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electrical Engineering and Computer Science

at the

Massachusetts Institute of Technology June 1998

©1998 Massachusetts Institute of Technology. All rights reserved.

| Signature of Author |                                                                                                                              |

|---------------------|------------------------------------------------------------------------------------------------------------------------------|

|                     | Department of Electrical Engineering and Computer Science May 18, 1998                                                       |

| Certified by        | Dr. William J. Dally Professor of Electrical Engineering and Computer Science Thesis Supervisor                              |

| Accepted by         |                                                                                                                              |

| C. SHOFOCIA         | Dr. Arthur C. Smith<br>Chairman, Committee on Graduate Students<br>Department of Electrical Engineering and Computer Science |

| JUL 231938          | Eng                                                                                                                          |

LIBRARIES

# Fast Thread Communication and Synchronization Mechanisms for a Scalable Single Chip Multiprocessor

by

Stephen William Keckler

Submitted to the

Department of Electrical Engineering and Computer Science

on May 18, 1998, in partial fulfillment of

the requirements for the Degree of Doctor of Philosophy in

Electrical Engineering and Computer Science

#### Abstract

Much of the improvement in computer performance over the last twenty years has come from faster transistors and architectural advances that increase parallelism. Smaller feature sizes have decreased the transistor switching time but at the same time increased the resistance of interconnect wires, resulting in slower signal transmission in on-chip wiring. Since future chips will have more silicon area and include more execution units, a much larger demand for parallelism is emerging. However, the increased significance of wire delay will require monolithic components, such as processors and caches, to be small and that the communication wires connecting them be short.

Computer systems typically exploit concurrency using either instruction level parallelism (ILP) or coarse-grain parallel threads running on a multiprocessor. This thesis proposes mechanisms for exploiting on-chip parallelism at a fine grain to bridge the gap between ILP and coarse-grain multiprocessing. Fast interprocessor communication and synchronization enables the use of tasks with run lengths as small as 10 cycles. At the same time, these interaction mechanisms are less susceptible than conventional microprocessor designs to longer wire delays imminent in future silicon process technologies. As fine-grain parallelism is orthogonal to ILP and coarse-grain threads, it complements both methods and provides an opportunity for greater speedup.

This thesis presents the architecture and implementation of the MIT Multi-ALU Processor (MAP), a 5 million transistor custom VLSI microprocessor chip. The MAP architecture incorporates 9 function units, split into 3 independent processors. The processors communicate via interprocessor register writes and synchronize using a hardware barrier instruction. These integrated mechanisms allow threads to communicate 10 times faster and synchronize 60 times faster than using a shared on-chip cache. The fast interprocessor interaction enables the MAP to exploit both instruction-level parallelism and fine-grain thread level parallelism. On a suite of applications, speedups of 1.2–2.4 are achieved using fine-grain threads on a 3-processor MAP chip.

Thesis Supervisor: Dr. William J. Dally

Title: Professor of Electrical Engineering and Computer Science

## Acknowledgments

It is good to have an end to journey toward, but it is the journey that matters in the end.

- Ursula K. LeGuin

And quite a journey it has been. I am deeply indebted to my guide, mentor, and thesis advisor, Professor William J. Dally. From the day I arrived at MIT, Bill has treated me as a colleague and a partner. He has taught me the value of both breadth and depth in conducting systems research and impressed upon me that in order to make a significant contribution, one needs to span many technological levels. Bill always had the knack to ask the hard questions that inspired me to look at a problem in a new way or to continue to dig deeper. His willingness to give me leadership responsibilities taught me valuable lessons in both research and project management. Thanks also to my thesis readers at MIT, Professors John Guttag and Frans Kaashoek.

The M-Machine project was truly a collaborative effort, and without the cooperation of the design team, the chip would not have come together. Many thanks to the other members of the MAP processor design team: Andrew Chang, Whay Lee, and Nick Carter. In addition, I want to acknowledge the efforts Urban Jangren and his team at Cadence Spectrum Design, who were our industrial parters in this venture. Without their support and collaboration, this MAP chip would never have gotten much past the circuit design. I also had the pleasure of working with some very talented undergraduate and masters students including Jeff Bowers, Dan Hartman, Keith Klayman, and Albert Ma. On the software side, thanks go to Daniel Maskit, Yevgeny Gurevich, and Andy Shultz for their efforts on the M-Machine compiler and runtime system.

Great thanks go to my many friends throughout my graduate career, including three I want to mention by name. To Don Yeung, for being an awesome housemate and co-commiserator for many years. To chief yogurthead Stuart Fiske, for dragging me out of the office and making my move to California easier. And to my officemate Scott Rixner, for being the perfect foil for so many jokes and keeping the office environment amusing at so many levels.

Last, but certainly not least, many thanks go to my parents, Bill and Joyce Keckler. They have provided a tremendous amount of emotional, intellectual, and recreational support. Thanks also go to Mom for brushing up on her computer science skills so that she was willing and able to help edit my thesis. Finally, I thank them both for learning not to ask the question: "When are you going to graduate?".

The research in this thesis has been supported by the Department of Defense through a National Defense Science and Engineering Graduate Fellowship, by an Intel Graduate Fellowship, and by the Defense Advanced Research Projects Agency monitored by the Air Force Electronic Systems Division under contract F19628-92-C-0045.

# Contents

| 1 | Intr | roduction 14                        |

|---|------|-------------------------------------|

|   | 1.1  | Technology Trends                   |

|   | 1.2  | The Parallelism Gap                 |

|   | 1.3  | The MIT M-Machine                   |

|   | 1.4  | Contributions                       |

|   | 1.5  | Background                          |

|   | 1.6  | Thesis Roadmap                      |

| 2 | M-I  | Machine Overview 29                 |

|   | 2.1  | The MAP Chip Architecture           |

|   |      | 2.1.1 MAP Execution Clusters        |

|   |      | 2.1.2 Memory System                 |

|   |      | 2.1.3 Global Configuration Space    |

|   |      | 2.1.4 On-Chip Switches              |

|   |      | 2.1.5 Communication Subsystem       |

|   |      | 2.1.6 Exceptions                    |

|   |      | 2.1.7 Events                        |

|   |      | 2.1.8 Summary                       |

|   | 2.2  | MAP Implementation                  |

|   | 2.3  | Design Methodology                  |

|   | 2.4  | Evolution of the MAP Design         |

|   | 2.5  | Scalability of the MAP Architecture |

|   | 2.6  | Lessons from the Implementation     |

| 3 | MA   | AP Chip Pipeline Design 54          |

|   | 3.1  | Pipeline Components                 |

|   |      | 3.1.1 Instruction Fetch             |

|   |      | 3.1.2 Register Read                 |

|   |      | 3.1.3 Synchronization               |

|   |      | 3.1.4 Execution Units               |

|   |      | 3.1.5 Write Back                    |

|   | 3.2  | Data Synchronization                |

|   | 3.3  | Multithreading                      |

|   |      | 3.3.1 Pipeline Overhead             |

|   |      | 3.3.2 Thread Selection              |

|   | 3.4 | Pipeline Mechanisms for Intercluster Interaction |

|---|-----|--------------------------------------------------|

|   |     | 3.4.1 Register Synchronization                   |

|   |     | 3.4.2 Cluster Barrier                            |

|   | 3.5 | Summary                                          |

| 4 | On- | chip Interaction Mechanisms 70                   |

| 4 | 4.1 | Experimental Evaluation Tools                    |

|   | 4.2 | Communication                                    |

|   |     | 4.2.1 Communication Mechanisms                   |

|   |     | 4.2.2 Communication Costs                        |

|   | 4.3 | Synchronization                                  |

|   | 1.0 | 4.3.1 Memory Synchronization                     |

|   |     | 4.3.2 Instruction Synchronization                |

|   |     | 4.3.3 Synchronization Costs                      |

|   | 4.4 | Thread Creation                                  |

|   |     | 4.4.1 New Threads                                |

|   |     | 4.4.2 Waiting Threads                            |

|   |     | 4.4.3 Invocation Costs                           |

|   | 4.5 | Summary                                          |

|   |     | ·                                                |

| 5 |     | truction-Level Parallelism 89                    |

|   | 5.1 | Limits of ILP                                    |

|   | 5.2 | Instruction-Level Parallelism on the MAP chip    |

|   |     | 5.2.1 Loosely Coupled Execution Streams          |

|   |     | 5.2.2 Comparison to Superscalar                  |

|   |     | 5.2.3 Comparison to VLIW                         |

|   | 5.3 | Evaluation of Loose Coupling                     |

|   |     | 5.3.1 Synthetic Benchmark                        |

|   |     | 5.3.2 Application Kernels                        |

|   | 5.4 | Summary                                          |

| 6 | Thr | read-Level Parallelism 103                       |

|   | 6.1 | Parallel Procedure Call                          |

|   | 6.2 | Synthetic Benchmark Study                        |

|   |     | 6.2.1 Granularity                                |

|   |     | 6.2.2 Argument Count                             |

|   | 6.3 | Parallel Applications                            |

|   | 6.4 | Inner-Loop Parallelism                           |

|   |     | 6.4.1 Task Granularity                           |

|   |     | 6.4.2 Communication Comparison                   |

|   | 6.5 | Outer-Loop Parallelism                           |

|   |     | 6.5.1 Task Granularity                           |

|   |     | 6.5.2 Synchronization Comparison                 |

|   | 6.6 | Summary                                          |

| 7 | M-N | Machine Project Retrospective 124                |

|   | 7.1  | Processor Coupling                         |

|---|------|--------------------------------------------|

|   |      | 7.1.1 SZ Stage Placement                   |

|   |      | 7.1.2 Cluster Synchronization              |

|   |      | 7.1.3 Remote Scoreboard Invalidation       |

|   | 7.2  | Register Limitations                       |

|   | 7.3  | Simulation Environment                     |

|   | 7.4  | Project Complexity                         |

| 8 | Con  | aclusion 131                               |

|   | 8.1  | MAP Chip Summary                           |

|   | 8.2  | Architectures for Future Chips             |

|   | 8.3  | Software Support                           |

| A | ΜA   | P Instruction Set Architecture 139         |

|   |      | Operation Fields                           |

|   |      | Integer Operations                         |

|   |      | A.2.1 Arithmetic Operations                |

|   |      | A.2.2 Byte Manipulation                    |

|   |      | A.2.3 Comparison Operations                |

|   |      | A.2.4 Data Movement                        |

|   |      | A.2.5 Control Flow Operations              |

|   |      | A.2.6 Address Calculation                  |

|   |      | A.2.7 Immediate Operations                 |

|   |      | A.2.8 Configuration Space Operations       |

|   |      | A.2.9 Communication Operations             |

|   | A.3  | Memory Operations                          |

|   | 11.0 | A.3.1 Standard Memory Access               |

|   |      | A.3.2 Synchronizing Operations             |

|   |      | A.3.3 Address Calculation                  |

|   |      | A.3.4 Special Memory Operations            |

|   |      | A.3.5 Thread Management Operations         |

|   |      | A.3.6 Arithmetic Operations                |

|   | A.4  | Floating-point Operations                  |

|   |      | A.4.1 Floating-point Arithmetic Operations |

|   |      | A.4.2 Integer Arithmetic Operations        |

|   |      | A.4.3 Data Movement                        |

|   |      | A.4.4 Data Conversion                      |

|   |      | A.4.5 Comparison Operations                |

|   |      | A.4.6 Immediate Operations                 |

|   |      | A.4.7 Communication Operations             |

| В | Gra  | phs of Application Results 147             |

| _ |      | Inner-Loop Parallelism                     |

|   | B.2  | Outer-Loop Parallelism                     |

|   |      | •                                          |

# List of Figures

| 1.1 | Timeline of microprocessor performance and clock rate improvements                 | $\epsilon$ |

|-----|------------------------------------------------------------------------------------|------------|

| 1.2 | Scaling of transistor and wire delays                                              | 7          |

| 1.3 | Impact of wire delay on corner-to-corner communication latency across a chip 1     | 7          |

| 1.4 | Schematic diagram of superscalar and VLIW architectures                            | 8          |

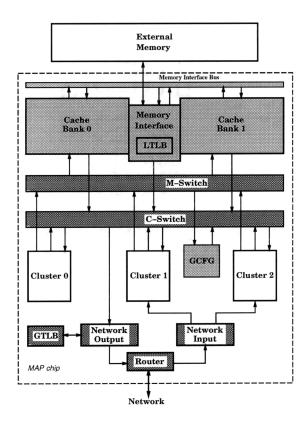

| 2.1 | Block diagram of the MAP architecture                                              | C          |

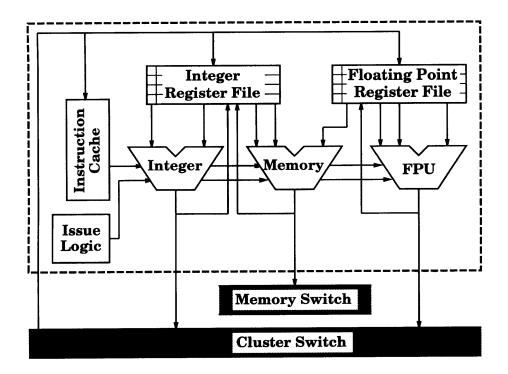

| 2.2 | The components of a MAP cluster                                                    | 1          |

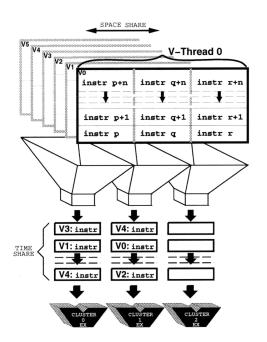

| 2.3 | Multicluster and multithreaded parallelism on the MAP                              | 4          |

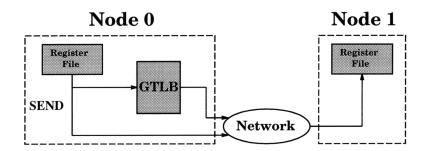

| 2.4 | Register-register send instruction between two MAP chips 3                         | 8          |

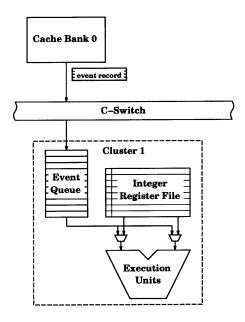

| 2.5 | Writing an event record into the event queue                                       | 1          |

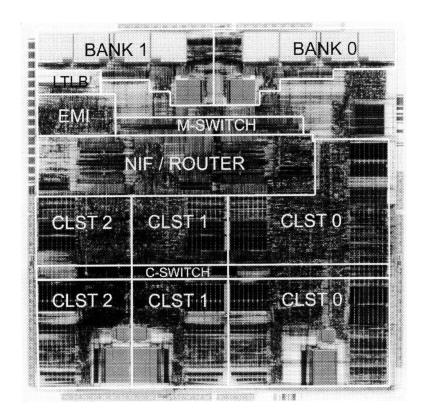

| 2.6 | Preliminary plot of the MAP chip                                                   |            |

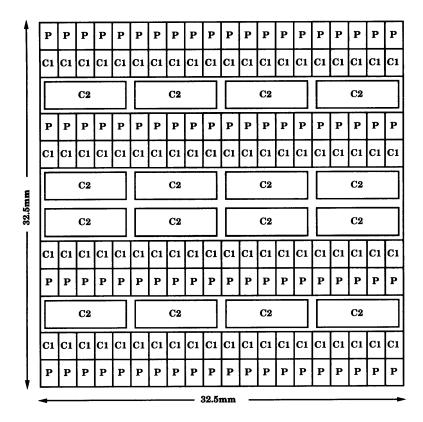

| 2.7 | Modified MAP architecture scaled for $0.1\mu\mathrm{m}$ CMOS technology 4          | 6          |

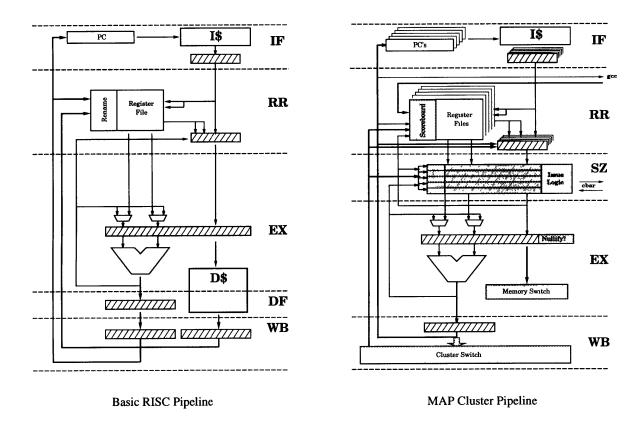

| 3.1 | Comparison of basic RISC and MAP pipelines                                         | 5          |

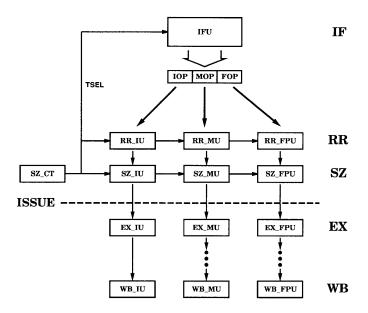

| 3.2 | Block diagram of all cluster pipeline modules                                      | 6          |

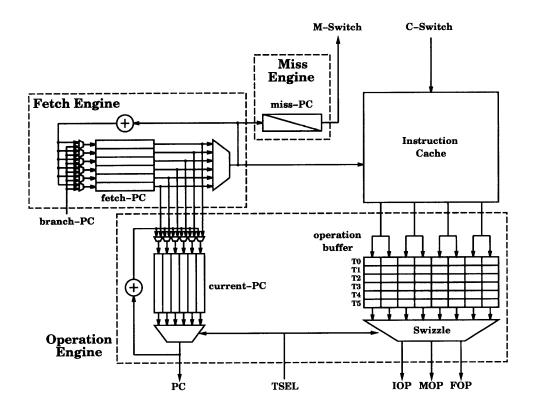

| 3.3 | The MAP Instruction Fetch Unit                                                     | 7          |

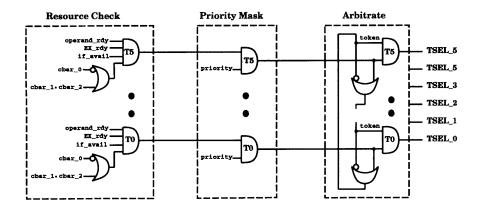

| 3.4 | MAP synchronization stage                                                          | 1          |

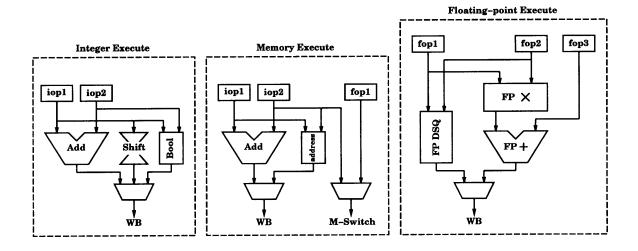

| 3.5 | MAP execution units                                                                | 3          |

| 3.6 | Data synchronization and delivery in the MAP pipeline 6                            |            |

| 3.7 | Cluster barrier state machine                                                      | 8          |

| 4.1 | A remote register write via the Cluster Switch                                     |            |

| 4.2 | Technology scaling of communication mechanisms                                     |            |

| 4.3 | Barrier instruction spanning all three clusters                                    |            |

| 4.4 | Technology scaling of barrier synchronization                                      |            |

| 4.5 | Program fragment to fork a thread into Cluster 1 using memory mapped registers . 8 |            |

| 4.6 | Program fragment to fork a thread into Cluster 1 using an hfork instruction 8      |            |

| 4.7 | Program fragment that uses memory to fork into a waiting thread                    |            |

| 4.8 | Program fragment that uses registers to fork into a waiting thread                 |            |

| 4.9 | Components of thread invocation and return                                         | 6          |

| 5.1 | Dependence graph for the inner loop of dot product                                 |            |

| 5.2 | Assembly code for 4-point relaxation on 2 MAP clusters                             |            |

| 5.3 | Optimized assembly code for 4-point relaxation on 2 MAP clusters 9                 |            |

| 5.4 | The effect of overlapping memory latencies                                         | 7          |

| 5.5 | Sequential memory access program                                                   | ۶          |

| 5.6        | Overlapped memory access program                                                     |

|------------|--------------------------------------------------------------------------------------|

| 5.7        | The effect of slip among instruction streams                                         |

| 5.8        | ILP cycle breakdown for MG-core and CG-core                                          |

| 6.1        | Parallel procedure call fork and join                                                |

| 6.2        | Slave standby handler for parallel procedure call                                    |

| 6.3        | Synthetic benchmark pseudocode                                                       |

| 6.4        | Synthetic benchmark granularity measurements                                         |

| 6.5        | Effect of granularity on execution time for fixed problem size                       |

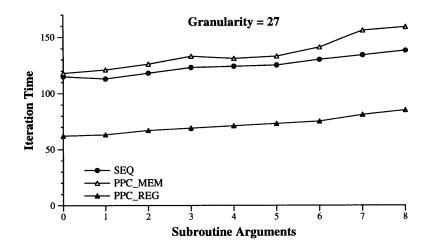

| 6.6        | Effect of increased number of arguments on execution time                            |

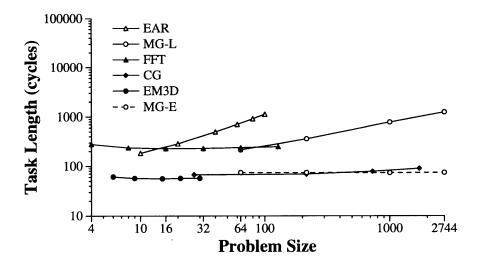

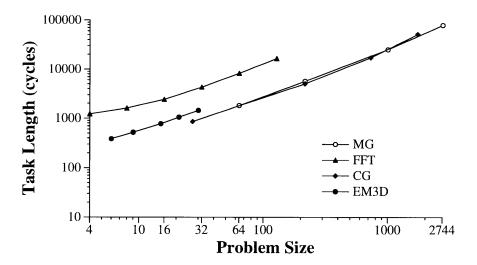

| 6.7        | Inner-loop task length versus problem size                                           |

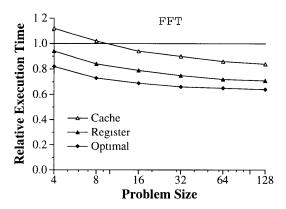

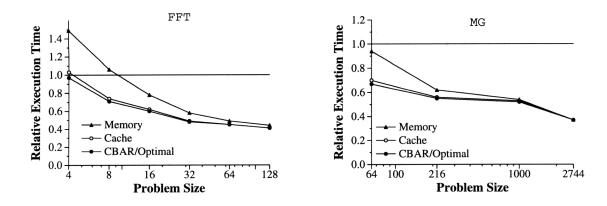

| 6.8        | Normalized execution time versus problem size for Inner-Loop FFT                     |

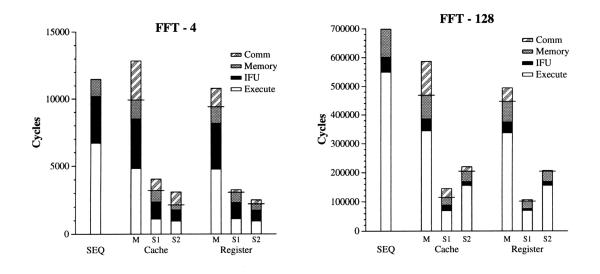

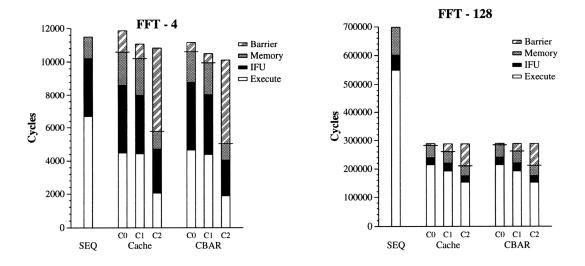

| 6.9        | Cycle breakdown of execution time for Inner-Loop FFT                                 |

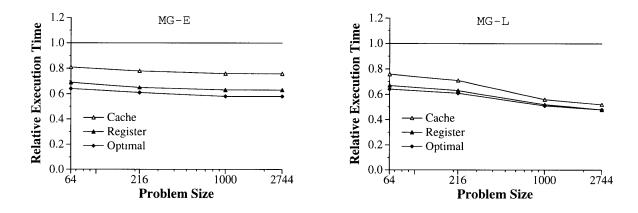

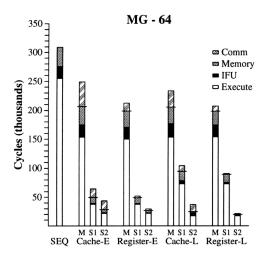

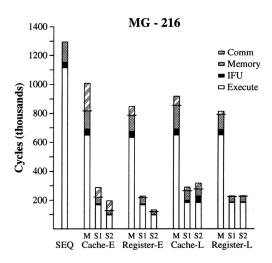

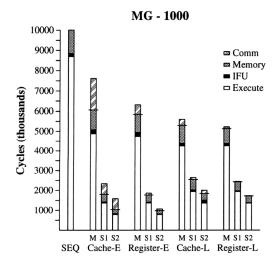

|            | Normalized execution time versus problem size for Inner-Loop Multigrid 116           |

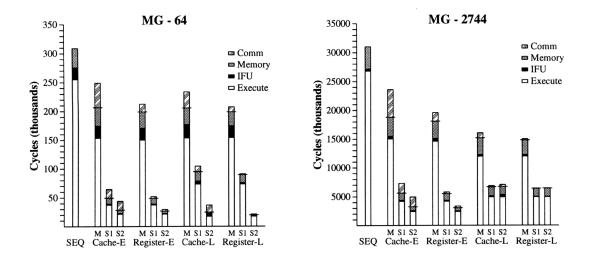

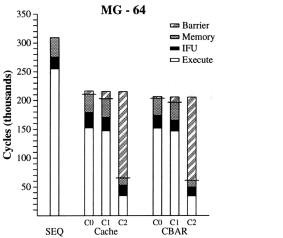

|            | Cycle breakdown of execution time for Inner-Loop Multigrid                           |

|            | Outer-Loop task length versus problem size                                           |

| 6.13       | Normalized execution time versus problem size for Outer-Loop FFT and Multigrid . 119 |

|            | Cycle breakdown of Outer-Loop FFT                                                    |

| 6.15       | Cycle breakdown of Outer-Loop Multigrid                                              |

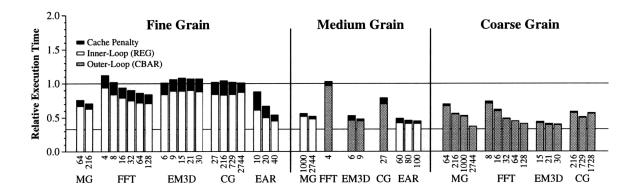

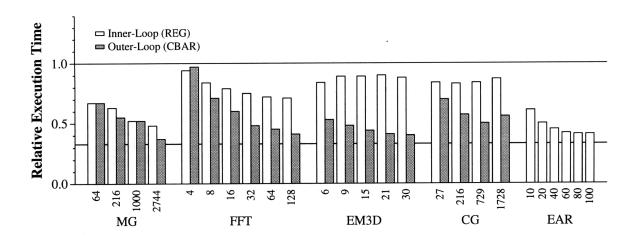

| 6.16       | Execution time and cache penalties for Inner and Outer-Loop applications 121         |

| 6.17       | Comparison of Inner versus Outer-Loop parallelizations                               |

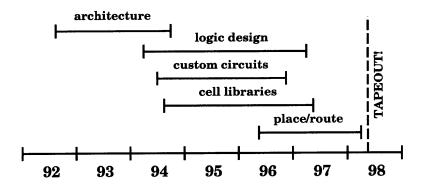

| 7.1        | Chronology of the MAP chip design                                                    |

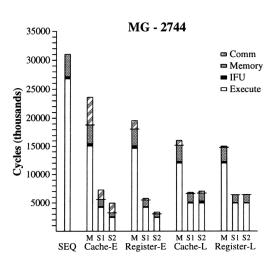

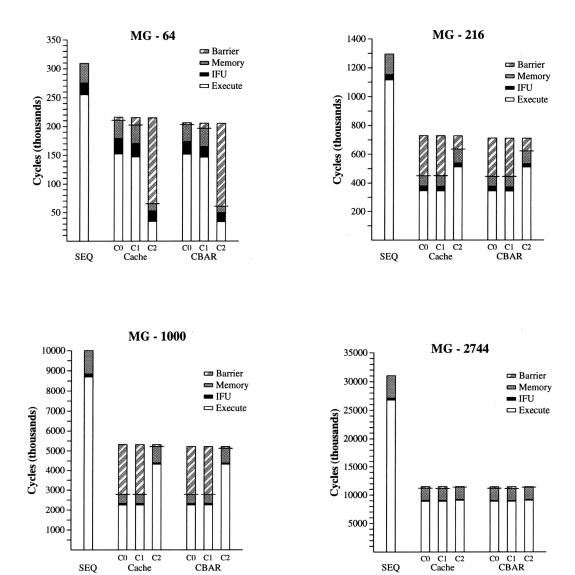

| B.1        | MG cycle breakdown using inner-loop parallelism                                      |

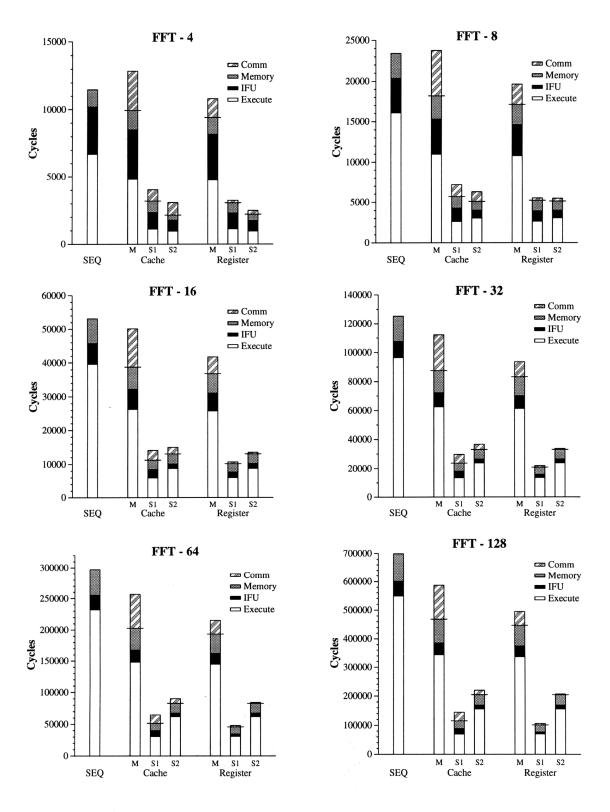

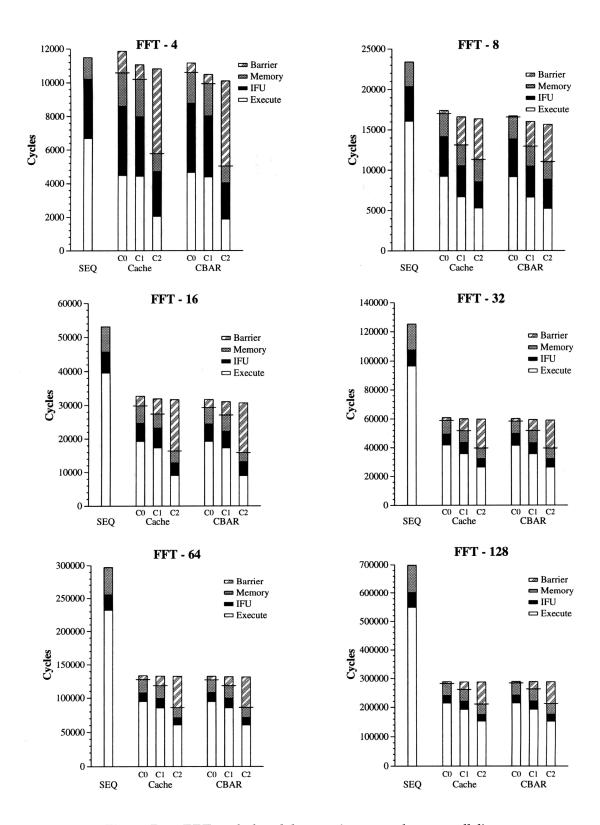

| <b>B.2</b> | FFT cycle breakdown using inner-loop parallelism                                     |

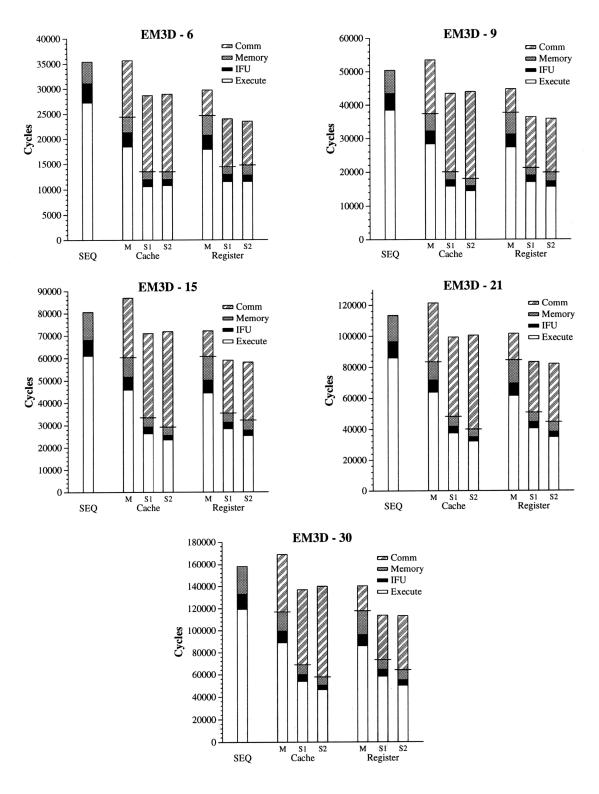

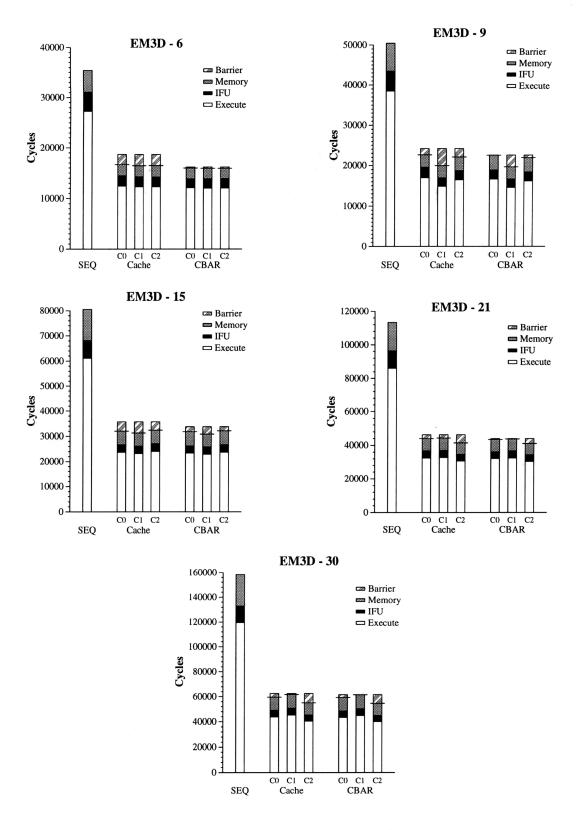

| <b>B.3</b> | EM3D cycle breakdown using inner-loop parallelism                                    |

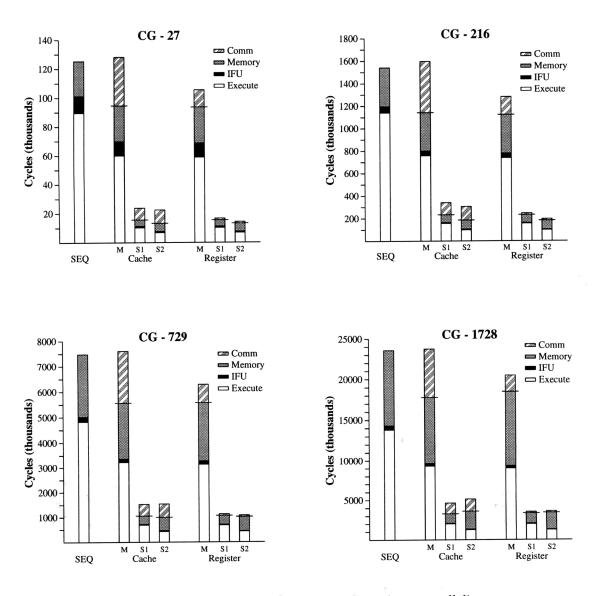

| <b>B.4</b> | CG cycle breakdown using inner-loop parallelism                                      |

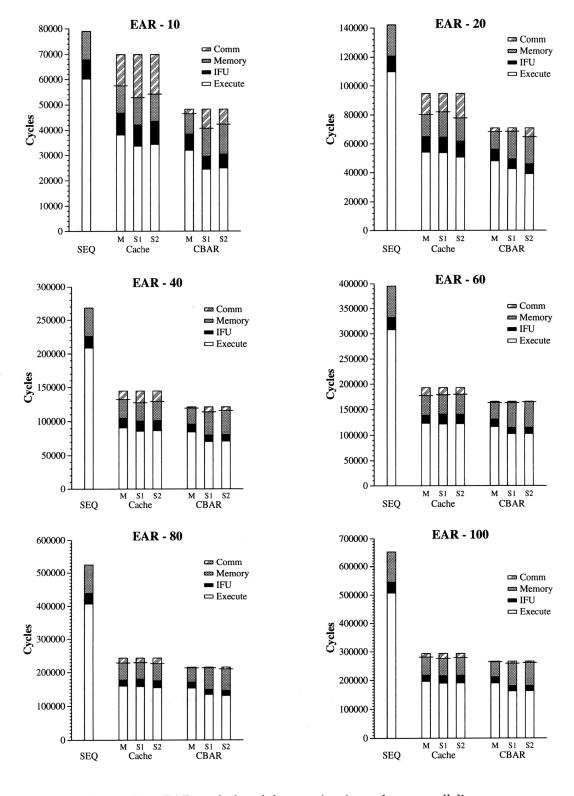

| B.5        | EAR cycle breakdown using inner-loop parallelism                                     |

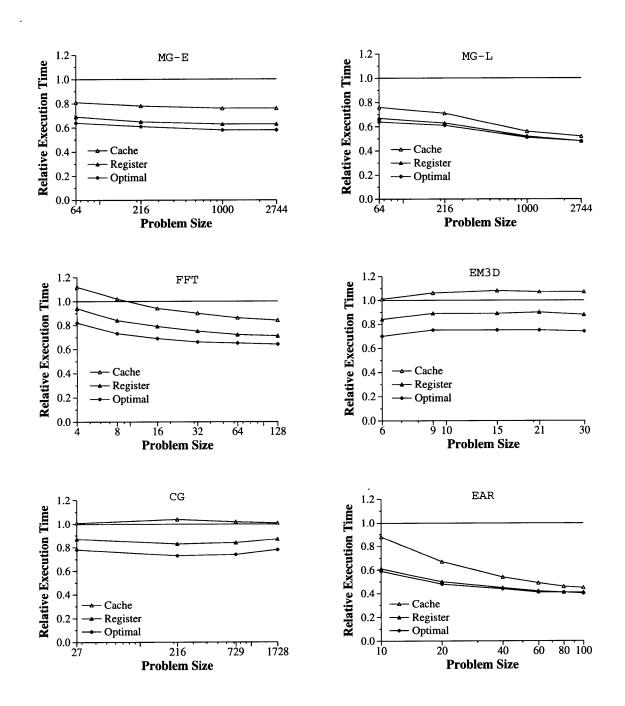

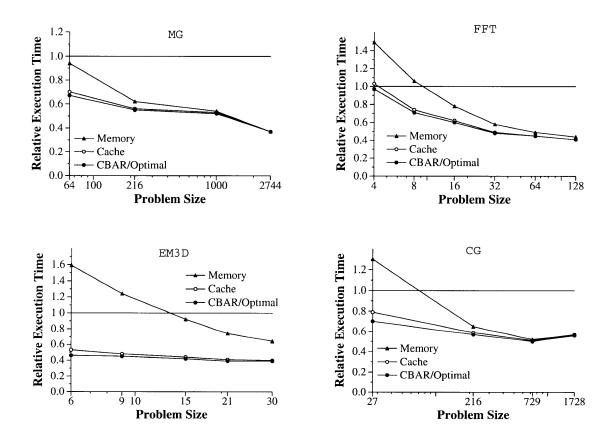

| B.6        | Summary of inner-loop execution times                                                |

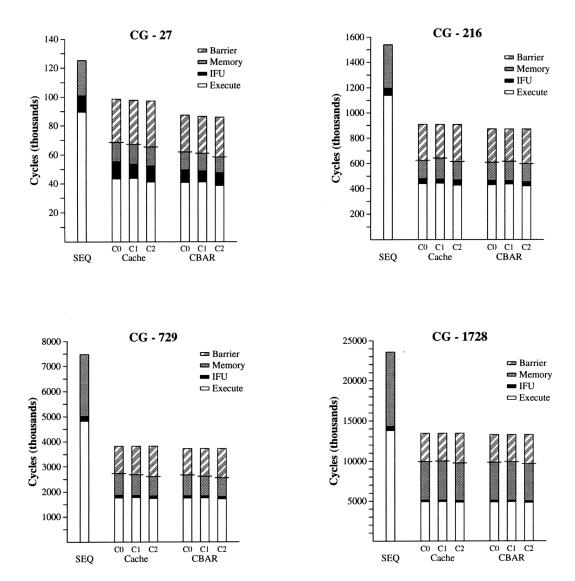

| B.7        | MG cycle breakdown using outer-loop parallelism                                      |

| B.8        | FFT cycle breakdown using outer-loop parallelism                                     |

| B.9        | EM3D cycle breakdown using outer-loop parallelism                                    |

|            | CG cycle breakdown using outer-loop parallelism                                      |

| B.11       | Summary of outer-loop execution times                                                |

# List of Tables

| 1.1 | Interaction latencies of recent parallel computers            | 19      |

|-----|---------------------------------------------------------------|---------|

| 1.2 | Comparison of communication and synchronization mechanisms    | $2^{2}$ |

| 2.1 | Designated uses of the MAP's six thread slots                 | 42      |

| 2.2 | MAP chip pin usage                                            | 44      |

| 2.3 | Area costs for the components of the MAP chip                 |         |

| 2.4 | Area costs for original MAP architecture                      |         |

| 3.1 | Encoding for instruction compression                          | 58      |

| 4.1 | Communication latencies between threads on different clusters | 73      |

| 4.2 | Barrier latency                                               | 79      |

| 4.3 | Thread invocation overhead                                    |         |

| 5.1 | Intercluster interactions in MG-core and CG-core              | 00      |

| 6.1 | Synthetic benchmark execution models                          | 07      |

| 6.2 | Application benchmark summary                                 | 11      |

| A.1 | Instruction packing to eliminate NOPs                         | 40      |

| A.2 | Predicates used to conditionally execute each instruction.    | 41      |

# Chapter 1

## Introduction

Over the last 20 years, the computer industry has become accustomed to a doubling of microprocessor performance every 18 months. This exponential growth is due to improvements in silicon process technology which has produced both faster clock rates and enabled architectural innovations that have improved performance. Smaller feature sizes have decreased the transistor switching time but at the same time increased the resistance of interconnect wires, resulting in slower signal transmission in on-chip wiring. Technology has already reached a point in which VLSI designers must take wire delay into account for high-speed chips.

In order to get faster performance from computer systems, architects have turned to parallelism at two extremes of granularity: instruction-level parallelism (ILP) and coarse-thread parallelism. Very long instruction word (VLIW) and superscalar processors exploit ILP with a grain size of a single instruction, while multiprocessors extract parallelism from coarse threads with a granularity of many thousands of instructions. Instruction-level and coarse-thread parallelism both have their limits. ILP in applications is restricted by control flow and data dependencies [Wal91]. For multicomputers, there is limited coarse thread parallelism at small problem sizes and in many applications.

This thesis focuses on mechanisms that enable more parallelism to be exploited on-chip without negatively affecting the clock rates of future technologies. The architectural innovations incorporate multiple processors on a chip that are linked with fast synchronization and communication mechanisms. Threads running on different on-chip processors communicate by writing into each other's register files. They synchronize by blocking on a register that is the target of a remote write

or by executing a fast barrier instruction. In addition to exploiting instruction-level parallelism, these mechanisms enable a new type of fine-grain thread level parallelism.

The fast communication and synchronization primitives are incorporated into the Multi-ALU processor (MAP) chip, which is a part of the MIT M-Machine. This thesis describes how these mechanisms are integrated into a processor pipeline and presents their implementation in a 5-million transistor custom microprocessor designed at MIT. Through simulation studies, the register-register communication and barrier synchronization instruction are shown to be significantly faster than their counterparts that use only the local on-chip cache. Using a set of real applications, the integrated interaction mechanisms of the MAP chip enable speedups of up to 2.4 times on 3 on-chip processors using fine-grain threads with run lengths of less than 300 cycles.

### 1.1 Technology Trends

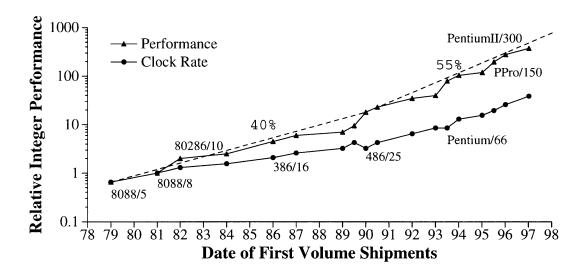

Advances in semiconductor technology over the last twenty years have resulted in dramatic performance and density improvements. Gate delays have dropped substantially, increasing microprocessor clock rates from less than 1MHz to more than 500MHz. Architectural innovations such as pipelining, caching, and dynamic instruction scheduling have also helped push the performance of microprocessors. Figure 1.1 plots the performance of the family of Intel microprocessors over the last 20 years [Gwe95]. The diagram shows both integer performance and clock rate normalized to an 8MHz 8088 microprocessor released in 1981. Based on its past history, the computer industry and its customers have come to expect exponential performance improvements of 55% per year, with about half of the improvement coming from increased clock rate, and the rest coming from architectural advances that increase parallelism. In order to continue to get additional performance each year, future microprocessors must employ architectures that do not slow the clock.

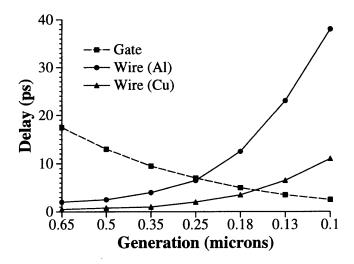

Technology scaling is now having a profound effect on both gate and wire delay. Figure 1.2 shows the absolute delay for both transistors and on-chip wires over several generations of silicon process technologies [Sem97, Boh96]. Due to reduced transistor channel lengths, transistor switching delays are decreasing at a rate of 25% per generation. However, scaling is less kind to interconnect as the RC wire delay is doubling every generation. As wires get smaller, their cross-sectional area decreases, resulting in higher wire resistance. In addition, the wires are closer together, contributing to higher coupling capacitance between wires in the same layer. Lower resistance

Figure 1.1: Relative performance of the Intel x86 family of microprocessors from 1979–1998, normalized to the 8MHz 8088 of 1981. The total performance improved 55% per during the 1990s, with the clock speed accounting for about half of the speedup.

wires such as copper, in conjunction with lower dielectric insulators would reduce the RC product at each generation, but would merely delay the inevitable impact on long wires.

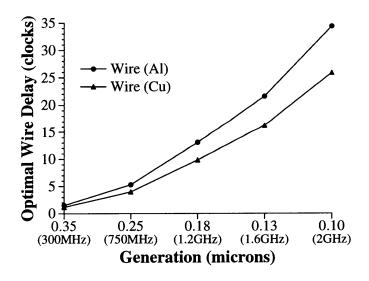

Figure 1.3 shows the effect of technology scaling by plotting the delay in clock cycles to transmit a signal on a wire between two opposite corners of a chip. The computed propagation latency assumes optimal placement of repeaters in order to minimize the effect of RC delay. Nonetheless, the combination of increased wire resistance, repeater delay, faster clock rates, and larger chips results in more than 26 cycles to transmit a bit from corner to corner in a  $0.1\mu m$ , 2GHz process. On-chip communication latency is no longer uniform and independent of distance. As a result, computer architects are faced with constraints limiting wire lengths in order to achieve high clock rates.

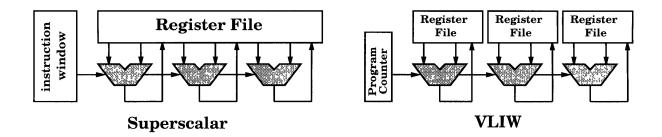

Today's microprocessor architectures, however, are on an evolutionary path that requires global communication, as shown in Figure 1.4. Superscalar microprocessors can be characterized as having both global control and global data. Centralized instruction issue logic examines an instruction window to determine which instructions can be executed simultaneously. The concurrent instructions are then delivered to the execution units which may be distributed throughout the chip. In an attempt to reduce the complexity of the issue logic, a global register file is typically used to

Figure 1.2: Absolute delay of transistors and wires over a several generations of silicon process technologies. The gate delay is decreasing at 25% per generation, while RC wire delay is doubling every generation.

Figure 1.3: Communication latency from chip corner-to-corner using optimal repeater placement. The latency is expressed in terms of the number of clock cycles at the clock rate of the designated process generation. Corner-to-corner delay is increasing dramatically due to slower wires, faster clocks, and larger chips.

Figure 1.4: Block diagram for two modern microprocessor organizations. Superscalar architectures dynamically schedule instruction level parallelism from a central instruction window and typically employ a global register file. VLIW processors statically schedule instructions in a compiler, and can more readily use local register files.

hold the data for all of the execution units. As the number of execution units increases, the wire lengths between centralized components (the issue logic and the register file) and the distributed execution units will increase. In a  $0.1\mu m$  process using copper interconnect, a signal can travel approximately 2.5mm in one 2GHz clock cycle. Thus to run at full speed, a superscalar processor in this technology must locate all execution units within one clock cycle of the instruction scheduling logic or pipeline more deeply between the scheduling logic and the execution units. Since a circular area of silicon with 2.5mm radius occupies less than 2% of the area of a 32.5mm square chip, it is clear that a single chip uniprocessor using a centralized dynamic scheduling discipline will not be efficient. Other factors will also limit the scalability of superscalar processors. The complexity of the issue logic is proportional to the product of the instruction window size and the number of execution units. In addition, the size of the register file grows quadratically with the number of register file ports, which can become large with increasing numbers of execution units.

Very long instruction word (VLIW) architectures have been built for supercomputer applications [CNO+88] and are being used in digital signal processors. In a VLIW, a programmer or compiler discovers instruction level parallelism and statically schedules the code across a series of execution units. The register files can be partitioned and placed close to an execution unit with the compiler scheduling the communication among them. The static scheduling and distributed data solves some of the constraints of superscalar architectures. However, a VLIW still has only a single program counter, and branch targets must be broadcast to all execution units.

Today's architectures that require frequent global communication are not well-matched with the

|                                   |                   |                    | Late                  | ncy    |

|-----------------------------------|-------------------|--------------------|-----------------------|--------|

| Machine                           | Clock Frequency   | Interaction        | time                  | cycles |

| Berkeley NOW [MVCA97]             | 167MHz            | round trip message | $21.6 \mu \mathrm{s}$ | 3600   |

| Intel Paragon [CLMY96]            | $50\mathrm{MHz}$  | round trip message | $19.9 \mu \mathrm{s}$ | 995    |

| Meiko CS-2 [CLMY96]               | $66\mathrm{MHz}$  | round trip message | $20.3 \mu \mathrm{s}$ | 1340   |

| SGI Origin [LL97]                 | 195MHz            | remote memory read | 540ns                 | 105    |

| Sun Ultra [CPWG97]                | $250\mathrm{MHz}$ | remote memory read | 550ns                 | 138    |

| Hal Mercury [WGH <sup>+</sup> 97] | $200\mathrm{MHz}$ | remote memory read | $1.1 \mu \mathrm{s}$  | 220    |

Table 1.1: Interaction latencies of recent parallel computers.

technology of the near future. Instead, future architectures must exploit physical locality on-chip to keep wires short. Incorporating multiple processors on a chip that can communicate efficiently with one another via processor registers is well suited to these emerging technological constraints. By doing this, the MIT MAP chip keeps all control and most communication local to each processor, enhancing locality and diminishing the effects of slow wires. Global communication is abstracted out of the local processor design and can be optimized or pipelined independently. Compared to alternative methods of controlling large numbers of execution units, register-coupled processors offer both simple implementation and attractive speedups.

## 1.2 The Parallelism Gap

Conventional computer systems exploit parallelism at two extremes. Instruction-level parallelism comes from instructions in a single stream that can be executed concurrently. During scheduling, each instruction can be considered its own task, and communication between instructions typically takes place through data registers. In order to effectively exploit ILP, the communication must be fast (1–2 cycles) and have essentially no overhead.

At the other end of the spectrum are coarse grained parallel computers, with interactions requiring 100s of cycles ( $\geq 1\mu s$ ) on conventional multiprocessors, and 1000s of cycles ( $\geq 10\mu s$ ) on multicomputers. Table 1.1 details interaction latencies for some recent commercial and research machines. The Berkeley, Intel, and Meiko results include all components of a round trip message. The SGI, Sun, and Hal numbers include only the latency of performing a remote read that can

be completely satisfied in hardware by a remote memory module. Communication between two threads running in parallel on separate processors will take much longer. In either case, exploiting parallelism on machines with such long interaction latencies requires very coarse–grain threads with infrequent communication and synchronization. Consequently, coarse-thread parallelism typically comes from outer loops of applications that are identified by hand or using a loop-parallelizing compiler.

The difference between ultra-fine instruction-level and coarse multiprocessor parallelism exposes a parallelism gap. This gap will continue to widen as microprocessor clock rates are increasing faster than multiprocessor interconnection network latency. The fast communication and synchronization mechanisms of the MAP chip can be used to bridge the parallelism gap between ILP and coarse—threads. Fine—grain threads which communicate and synchronize frequently can run on-chip and exploit parallelism that is not available with multiprocessor communication latencies. Because of the long interaction latencies between processors, typical multiprocessors require applications with large data sets in order to achieve significant parallel speedup. In fact, most reports of parallel speedup includes increasing the size of the applications data set as more processors are used.

However, the programs that people run every day are not large scientific applications. Many applications, such as electronic circuit simulation, have small data sets, large computation requirements, and ample concurrency. Unfortunately, simulation of a relatively small circuit that may require four hours on a uniprocessor is not likely to get faster on a conventional multiprocessor. Parallelizing this application will require partitioning of the data set across the processors. The overhead from slow multiprocessor communication mechanisms will overwhelm any benefit from fine-grain concurrency. With sufficiently fast communication and synchronization between processors, the models of the different transistors can be evaluated concurrently which will enable significant speedup even on small problem sizes. Inner-loops of applications are also prime targets for fine-grain threads. This inner-loop parallelism is orthogonal to coarse-thread parallelism and ILP, and can be used in concert with conventional methods to achieve faster performance. Since future chips will have more silicon area and include more execution units, a much larger demand for parallelism is emerging. At the same time, the increased significance of wire delay will require monolithic components, such as processors and caches, to be small and that the communication wires connecting them to be short. By using efficient mechanisms for communication and syn-

chronization, programs can exploit fine-grain concurrency in the parallelism gap and allow parallel processing techniques to be applied to many important small applications.

#### 1.3 The MIT M-Machine

The MIT M-Machine is designed to exploit parallelism at all granularity levels. The M-Machine consists of a collection Multi-ALU processor (MAP) chips connected via an integrated network interface and a 2-dimensional network. Each MAP chip has 3 clusters of execution units that communicate with one another through registers using an on-chip communication switch. Each cluster has three execution units, two register files, and a local instruction cache. Instruction level parallelism can be exploited within a cluster and across the clusters using register–register communication. Fine-grain threads can exploit inner loop parallelism on-chip, with the independent clusters communicating and synchronizing using the integrated interaction mechanisms of the MAP chip. Coarse grain threads are spread across multiple M-Machine nodes to exploit outer-loop parallelism.

The MAP chip, which is the focus of this thesis, is itself a prototype for future microprocessor designs. While the baseline MAP chip design contains three processors, this particular implementation, unlike current microprocessors, is scalable. The architecture of the MAP chip mitigates the effect of the long wire delays present in current and future silicon process technologies by partitioning the execution units into independent processor clusters. Three execution units are included in a cluster so that all local wires can easily be driven in a small fraction of the clock cycle. Long global wires are necessary to connect the clusters and the cache banks in the memory system. Each of these components operates independently from one another and can tolerate multiple cycles of communication latency. The computation power in the MAP chip can be scaled in two dimensions. Limited scalability is achieved by incorporating additional execution units into each cluster, subject to the local wiring latency constraints. A greater degree of scalability comes from increasing the number of processor clusters. The number of clusters is restricted by the silicon area on a chip and the scalability of the communication mechanisms between clusters. With three processors on the MAP chip, a simple crossbar communication system is sufficient. A more scalable communication substrate that exploits physical locality can enable more clusters built on a single chip without requiring long wires between remote clusters. Multiprocessor network topologies, such as meshes and

|                                                  | MAP Chip          | J-Machine<br>[NWD93] | Alewife<br>[ABC <sup>+</sup> 95, LA94] |                  | Monsoon<br>[PC90] |

|--------------------------------------------------|-------------------|----------------------|----------------------------------------|------------------|-------------------|

| Communication: Form Packet size Latency          | register-register | messages             | shared memory                          | messages         | dataflow tokens   |

|                                                  | 1 word            | >2 words             | 4 words                                | >2 words         | 1 token           |

|                                                  | 1 cycle           | 11 cycles            | 38 cycles                              | 42 cycles        | 8 cycles          |

| Synchronization: Data Form Barrier Form Overhead | scoreboard        | message dispatch     | spin lock                              | message dispatch | data arrival      |

|                                                  | cbar instruction  | messages             | spin locks                             | messages         | N/A               |

|                                                  | 1 cycle           | 55 cycles            | 64 cycles                              | 128 cycles       | N/A               |

Table 1.2: Comparison of communication and synchronization mechanisms.

trees, could certainly be used to extend the scalability of a single-chip implementation. Regardless of the configuration of the processors, the key to the scaling the execution resources on a single chip is to exploit locality.

The contributions of the MAP chip architecture come not only from the partitioning of execution units into clusters, but also from the mechanisms employed to interact among them. The MAP chip integrates communication and synchronization mechanisms into the core of each processing element which results in drastically lower latencies than available even in other experimental fine-grain parallel computers. Table 1.2 compares the on-chip communication and synchronization mechanisms of the MAP chip to those of other experimental parallel computers. The communication between different MAP processors takes place through registers, as an instruction on one processor can write into the register file of another processor with a latency of one cycle. The J-Machine integrates a network interface very closely with the processor and allows a user program to send messages directly from the contents of a register file. Two adjacent processors can communicate in 11 cycles including instruction and network interface overhead on both ends. The Alewife shared memory multiprocessor integrates hardware support for both shared memory and message passing communication between processors. Fetching data that resides in a remote cache line requires 38 cycles, while message communication between two processors requires 42 cycles.

For synchronization, the MAP chip introduces two novel instructions: empty and cbar. The empty instruction can modify a MAP cluster's register scoreboard which is used for data synchronization. Instructions that need data from remote processors wait in a synchronization pipeline stage. When a remote register write completes, the scoreboard bit for the designated register is

marked full, enabling execution of any instruction that is waiting for the value. A scoreboard entry is marked full automatically when registers are written and is emptied manually using a user-level empty instruction. Data synchronization on message passing systems such as the J-Machine or Alewife typically takes place when the message arrives at a remote processor. The dispatch of code that handles the message can signal to the thread that is waiting for the value. In a shared memory machine, data synchronization is enforced using spin locks in memory. For control synchronization, the MAP chip implements a barrier instruction (cbar) which enables threads on all three processors to synchronize with only one cycle of overhead. Barrier synchronization on message passing machines, even only two processors, requires many more cycles to complete (55 cycles for the J-Machine and 128 cycles on Alewife). Shared memory barriers which are implemented using locks in memory can also be expensive, requiring 64 cycles to synchronize two Alewife processors. With its integrated mechanisms and on-chip interactions, the MAP chip can communicate and synchronize more than an order of magnitude faster than previous fine-grain parallel machines. This provides the opportunity to exploit forms of parallelism that have been previously unavailable.

In many ways, the MAP chip's mechanisms are similar to those found in a dataflow machine. The Monsoon dataflow computer was built to process dataflow tokens, which typically consist of a single instruction. When a token fires, it computes a result and transmits it to other tokens that are waiting to use that result as an operand. When the operand arrives, it can immediately enable a token for execution. Data is delivered directly from one instruction to another on different processing elements, and individual instructions stall until all of their operands arrive. The MAP chip's register communication and synchronization are analogous to the communication between computation tokens in Monsoon. Using these mechanisms, the MAP chip can provide extremely fast interprocessor communication to conventional programs and allow them to exploit parallelism at a finer granularity than ever before.

The experimental methodology used to evaluate the MAP chip includes both simulation and implementation. A highly accurate simulator is used to investigate the performance of the architecture and in particular the communication and synchronization mechanisms. The MAP chip project is also somewhat unique among academic architecture research in that it verifies the feasibility of the architecture through silicon implementation. The MAP prototype is a 5 million transistor custom VLSI chip implemented in a  $0.5\mu m$  CMOS technology. All of the logic and circuit design

of the MAP chip is complete, and tapeout is anticipated for May 1998. Further investigations on the hardware prototype will follow when the chips are tested and incorporated into a 16 processor M-Machine system in Autumn 1998. Building the prototype is extremely valuable because it allows us to "close the loop" by examining not only the performance of the proposed mechanisms, but also the design complexity and area cost in a real piece of silicon. Furthermore, it validates the assumptions made during high level simulation and provides the designers with valuable insight for future projects.

#### 1.4 Contributions

The primary contributions of this research are:

- A scalable microprocessor architecture and implementation that partitions execution units into independent clusters to mitigate the effects of the emerging wire delay constraints of present and future silicon process technologies.

- Direct register-register transfers between on-chip processors for single-cycle communication between threads.

- A register scoreboard to enforce local and remote data synchronization that is updated by register writes but is also under software control. An empty instruction allows a user to manually invalidate registers.

- A fast barrier instruction (cbar) that enables threads on different on-chip processors to synchronize their instruction streams with only one cycle of overhead.

- An experimental evaluation of fine and coarse-grain parallelism, quantifying the benefit of using integrated register communication and synchronization mechanisms instead of a locally shared cache.

- A custom VLSI chip that demonstrates the physical feasibility of the mechanisms. The logic

design of the chip shows how a register scoreboard and a synchronization pipeline stage unify

data synchronization for arithmetic, memory, and communication instructions, and how the

hardware structures can be incorporated into a microprocessor pipeline.

1.5. BACKGROUND 25

• A design, implementation, and physical evaluation of zero-cycle multithreading, which combines both instruction and thread level parallelism to interleave instructions from multiple threads over a common set of execution units.

## 1.5 Background

Computer systems designers have exploited parallelism to help improve application performance. However, the nature of the parallelism that can be exploited is dictated largely by the overhead to communicate and synchronize among the parallel components. The study of synchronization cost performed by Chen, Su, and Yew [CSY90] explored a spectrum of granularities including instruction, statement, and loop level parallelism. They found that statement oriented parallelism was far more sensitive to synchronization overhead than loop level parallelism. However, even with substantial synchronization overhead the statement level parallelism still yielded 4 to 20 times speedup over sequential. This study suggests that the amount of fine-thread parallelism available in applications is considerably greater than what we have exploited so far using simple approaches to parallelization, and that it scales well beyond three processors. It also shows that to extract this parallelism requires very low-overhead synchronization.

Previous architectures and machines have exploited parallelism at a large grain size, typically using loops, because they did not have sufficiently low latency communication mechanisms. However, some architectures have integrated fine—grain mechanisms into their computation engines to enable faster interactions among parallel threads.

Register Communication: The Cray X-MP implemented two central vector processing units with a bank of shared address, scalar data, and semaphore registers that could be accessed by either processor [RR87]. These registers were typically used for self scheduling of loops. The registers were not general purpose and values were copied to a processor's local register set prior to using the data. The CMU iWarp employed a form of register–register communication between processors to enable systolic communication and computation [BCC+90, PSW91]. Communication channels were established between processors, and words could be sent to a remote communication unit through the channel. At the receiver, a communication unit copied the data into a register visible by a computation unit.

Multithreaded Systems: Architectures that support fine-grain threads in a multiprocessor typically implement fast thread creation and dispatch mechanisms. The \*T architecture, whose threads are in the range of 15 instructions, implements fork, join, and next instructions that interact with a memory task queue and a synchronization coprocessor to allow threads on different processors to communicate with one another [NPA92].

Like the MAP chip, the Tera Computer System [ACC<sup>+</sup>90] also exploits fine-grain threads using a multithreaded multiprocessor architecture. In a Tera machine, interaction between threads takes place only through memory, and full-empty bits are provided on each memory location to enable fast synchronization. In addition, Tera's architecture penalizes single threaded code by providing no support for data locality, and by a hardware scheduling policy which prohibits a single thread from using the execution resources on every cycle.

On-chip Thread Parallelism: The Hydra and Simultaneous Multithreading (SMT) architectures aim to scale on-chip parallelism beyond the limits of ILP. The Hydra architecture explores the design tradeoffs of building a single-chip multiprocessor, focusing on the memory system [NHO96]. Coarse grained tasks execute independently and communicate via a level-1 or level-2 cache. SMT adds multithreading to a traditional superscalar to exploit both instruction and thread-level parallelism [TEL95]. Execution resources are dynamically assigned to different threads, and instructions from them may execute simultaneously. Both Hydra and SMT provide only memory-based mechanisms for communication and synchronization between threads and are thus limited to threads that can tolerate longer communication latencies. The work in this thesis is complementary to these projects in that register-based mechanisms could easily be incorporated into these architectures, extending the granularity of parallelism they are able to exploit.

The Multiscalar architecture attempts to deduce fine—grain parallelism at runtime [SBV95]. Basic blocks of the program are assigned dynamically to different execution units, while hardware is responsible for enforcing the data dependencies among the blocks. Communication takes place via a unidirectional ring to which each thread can read or write. This promising approach to extracting speculative fine-thread parallelism is well matched to implementation using register-based mechanisms in lieu of the special hardware suggested in [SBV95].

1.6. THESIS ROADMAP 27

### 1.6 Thesis Roadmap

This thesis focuses on communication and synchronization mechanisms that are used to exploit both instruction level and fine-thread parallelism across multiple processors within the MAP chip. Chapter 2 describes the architecture of the MAP processor, including the organization of execution units, the memory system, and the network interface. This chapter also details the physical implementation of MAP architecture in a 5 million transistor custom VLSI chip using a  $0.7\mu m$  drawn process. An area analysis of the components of the MAP chip show that an implementation of a MAP processor with all of the architecture's floating-point units and more on-chip memory capacity and bandwidth could easily be built using a  $0.35\mu m$  process.

Chapter 3 details the cluster pipeline of the MAP chip, including the bypassing and instruction issue mechanisms that enable fast cluster interaction. This chapter presents a new synchronization pipeline stage that determines when a thread can execute its next instruction, based on the instruction's data requirements and the availability of execution resources. In addition, the synchronization stage dynamically interleaves instructions from multiple threads on a cycle-by-cycle basis to tolerate instruction, memory and communication latencies.

In order to determine the benefit of the MAP's on-chip interprocessor communication and synchronization mechanisms, a simulation study using the Verilog logic design of the MAP chip was performed. This study, detailed in Chapter 4, shows that a remote thread can be created in 11 cycles, and that two threads can communicate or synchronize in a single cycle. Communication is 10 times faster and synchronization is 60 times faster than using only an on-chip cache.

Chapter 5 describes how the register communication and synchronization mechanisms can be used to exploit instruction-level parallelism across the independent MAP processors. Hand scheduling of procedures that contain ILP splits the code into independent streams that execute simultaneously on separate clusters. Synchronizing explicitly when communication is necessary is shown to be competitive with the implicit synchronization of a VLIW.

The boundaries of the parallelism gap are explored in Chapter 6. A suite of applications is characterized by parallelizing their inner and outer loops to quantify the benefits of the MAP's mechanisms over using just a shared on-chip cache. On the fine-grain parallelism that is found in the inner loops, the MAP's mechanisms provide speedups of up to 2.4 times using 3 on-chip processors, while communicating through memory yields less speedup and sometimes slowdown. On

coarser grain outer-loop parallelism, processor interactions are infrequent enough that the MAP's barrier instruction provides little performance improvement.

Chapter 7 discusses some of the lessons learned from the MAP design and implementation, including the value of controlling complexity. Finally, Chapter 8 contains the conclusions of this work and outlines future research.

## Chapter 2

# M-Machine Overview

The M-Machine is intended to exploit parallelism at all levels and to extract more parallelism from problems of fixed size, rather than requiring enormous problems to achieve peak performance. The M-Machine consists of a collection of computing nodes interconnected by a bidirectional 2-D mesh network [FKD+95]. Each six-chip node contains a Multi-ALU (MAP) chip and 1 MWord (8 MBytes) of synchronous DRAM (SDRAM) with error correction (ECC). Three clusters of execution units are implemented on each MAP chip, and mechanisms are employed to enable fast communication and synchronization between them. This enables the on-chip execution units to interact frequently and exploit both instruction and thread-level parallelism. The MAP chip also includes a network interface and router that are integrated into the execution unit pipeline. The bandwidth from the processor core to the local synchronous DRAM (SDRAM) and to each network channel is balanced at 8 bytes per processor cycle. The low latency and high bandwidth network interface and router allows threads on different MAP chips to communicate efficiently. To connect to peripheral devices, the MAP chip includes a dedicated I/O bus. In the M-Machine, I/O devices may be connected to either every node or a subset of nodes, such as those on an edge of the mesh.

This chapter focuses on the architecture and implementation of the MAP chip. Section 2.1 describes the components of the MAP chip, including the processing, memory, and communication subsystems. Sections 2.2 through 2.4 discuss the physical implementation of the MAP chip and how the design was modified to meet the on-chip area constraints. Section 2.5 analyzes the scalability of the MAP chip for future process generations. Finally, Section 2.6 concludes with some interesting lessons about conducting a project such as this in an academic environment.

Figure 2.1: Block diagram of the MAP architecture.

## 2.1 The MAP Chip Architecture

As shown in the block diagram of Figure 2.1, a MAP chip consists of four major subsystems: processing clusters, communication switches, memory banks units, and a network unit. The processing subsystem contains three execution clusters, each of which is an independent processor. A cluster includes an instruction cache, two register files, and three execution units. The memory subsystem is composed of a shared unified cache organized into two banks so that it can process two memory requests simultaneously. The Global Configuration Space (GCFG) controller enables the control registers of the MAP to be accessed via memory operations. Two crossbar switches interconnect these components. Clusters make memory requests to the appropriate bank of the interleaved cache over the 142-bit wide (51 address bits, 66 data bits, 25 control bits)  $3\times2$  M-Switch. The 88-bit wide (66 data bits, 22 control bits)  $7\times3$  C-Switch is used for inter-cluster communication and to return data from the memory system. Both switches support up to three transfers per

Figure 2.2: A MAP cluster consists of 3 execution units, 2 register files, an instruction cache and ports onto the memory and cluster switches.

cycle; each cluster may send and receive one transfer per cycle. The network subsystem contains the network interface units and a router. A cluster can communicate with another MAP chip by injecting a message directly into the router, which automatically delivers the message to the destination using the routers on intermediate MAP chips.

#### 2.1.1 MAP Execution Clusters

Each of the three MAP clusters is an independent 64-bit pipelined processor with a local 4KB instruction cache. Figure 2.2 shows a block diagram of a cluster, including three execution units, two register files, and interfaces to the global switches. The integer unit executes arithmetic, logical, shift, and comparison operations. The memory unit executes load and store operations to memory, as well as most of the integer unit operations, excepts shifts and compares. The floating-point unit includes a 4 stage multiply-add pipeline and an iterative divide/square-root unit. It executes all floating-point operations, as well as integer multiply and integer divide.

The integer and floating-point register files each contains six banks of 16 registers. The integer register banks share four read ports and three write ports that are read and written independently by both the integer and memory units. The floating-point register banks are accessed through four read ports and two write ports. The floating-point unit reads three operands (for multiplyaccumulate) and writes one result to the floating-point register file. The memory unit also reads one operand from the floating-point register file for floating-point store operations. The additional write port on each register file allows the Cluster Switch to update registers without interfering with local writes. Integer register 0 ( $i\theta$ ) and floating-point register 0 ( $f\theta$ ), are both hard wired to the value zero, while integer register 1 (i1) is mapped to the program counter. Both the integer and floating-point units can write results to remote register files via the Cluster Switch. The Cluster Switch is also used to move data between the integer and floating-point register files on the same cluster. The memory unit sends its load and store instructions to the shared on-chip cache using its port to the Memory Switch. Misses in the instruction cache generate load operations that go to the unified cache as well. In addition to the data registers, a cluster also has six banks of 16 one-bit condition code (CC) registers. These registers hold results of comparison operations and are used for conditional branches and predicated execution of instructions. Of the 16 condition code registers, 8 are reserved for local access while the other 8 are global and can be written by remote clusters.

Each MAP instruction may contain 1, 2, or 3 operations, with one operation for each execution unit. Operations are scheduled statically by a compiler and packed into instruction words. The MAP's instruction scheduling hardware does not reorder instructions. Operations in a single instruction must issue together but may complete out of order. Synchronization between instructions must take place through hardware enforced data dependencies in order to prevent write-after-write hazards to the register file. Load and store operations to the memory system that issue from a given cluster will access the memory system and complete in order. Every operation may be conditionally executed depending on the one-bit value of one of the condition code registers.

Concurrency is exploited within a cluster using multithreading. Up to six instruction streams may be simultaneously loaded in the processor pipeline, each residing in its own *thread slot* consisting of a set of pipeline registers and private portions of the register files. Each thread can access one bank of the integer, floating-point, and condition code register files. The instruction streams

are called V-Threads, as instructions from them drop vertically into a common set of execution resources on a cluster. Instructions from different V-Threads are interleaved over the execution units on a cycle-by-cycle basis. If one thread is waiting for a result from a previous instruction, another thread may use the execution units instead. Consecutive instructions entering the execution pipeline may be from distinct V-Threads, or they may be from the same V-Thread. This flexible interleaving allows the MAP to exploit multithreaded parallelism and to mask variable pipeline, memory, and communication delays. The pipeline design required to implement this multithreading is discussed further in Chapter 3.

The MAP also supports concurrency by executing threads in parallel across its arithmetic clusters. Threads executing on different clusters are known as H-Threads since they can enter their own execution pipelines horizontally and concurrently. H-Threads that occupy the same thread slot number on different clusters are members of the same V-Thread. To facilitate closer interaction between clusters, H-Threads within the same V-Thread may communicate and synchronize with one another by writing into each other's register files. Two threads that reside in different V-Threads can communicate with one another through memory. Because memory operations issued by threads on separate clusters may complete out-of-order, synchronization through registers, a cluster barrier, or on a memory location is necessary to coordinate memory communication between clusters.

The combination of multiple clusters and fast interactions among them can be used to support multiple execution models, including instruction, thread, and loop level parallelism. Because of the integrated register communication, the MAP chip can exploit fine-grain thread level parallelism that would be infeasible on a traditional multiprocessor.

To exploit instruction-level parallelism, the compiler can schedule an instruction across all three clusters using H-Threads from the same V-Thread. The compiler must insert explicit register-based synchronization operations or use the cluster barrier instruction to enforce instruction ordering between H-Threads. Unlike the lock-step execution of traditional VLIW machines, H-Thread synchronization occurs only as required by data or resource dependencies. While explicit synchronization incurs some overhead, it allows H-Threads to slip relative to one other in order to accommodate variable—latency operations such as memory accesses. These intercluster communication synchronization and communication mechanisms are examined in more detail in Chapter 4.

The partitioning of V-Threads and H-Threads across the clusters is shown in Figure 2.3. The

Figure 2.3: Multiple V-Threads are interleaved dynamically over the cluster resources. Each V-Thread consists of 3 H-Threads which execute on different clusters.

state for each of the six V-Threads (V0-V5) is stored in the pipeline registers and register files in each cluster. One H-Thread from each V-Thread resides on each cluster and consists of a sequence of 3-wide instructions containing integer, memory, and floating-point operations. As shown for cluster 0, the instructions from each V-Thread are dynamically interleaved over the execution units, so that an instruction from V3 can follow one from V1 without any pipeline stalls. A cluster's execution resources are time-shared by those V-Threads that are executing. Each cluster is independently controlled, and instructions from the same V-Thread need not be executed simultaneously on all clusters. The parallel clusters and multithreading at each cluster allow the execution resources to exploit both instruction and thread-level parallelism and achieve high utilization of the function units.

#### 2.1.2 Memory System

The MAP's memory system is designed to provide high bandwidth and low latency access to the on-chip cache and off-chip memory. As illustrated in Figure 2.1, the 32KB unified cache is organized

as two word-interleaved 16KB banks which permits references to consecutive addresses to proceed in parallel. On a memory reference, a virtual address is used to access the cache directly and no virtual to physical translation is required. However, since all processes reside in the same global virtual address space, the cache will never contain any aliases. Each cache line consists of 8 words (64 bytes). The external memory interface includes virtual memory support and a synchronous DRAM (SDRAM) controller to manage the off-chip memory. The SDRAM controller exploits the pipeline and page modes of the external memory and performs single error correction and double error detection on the memory transfers.

Each cache bank receives memory operations from the clusters via the Memory Switch. For a load operation that hits in the cache, the data is immediately returned to the requesting cluster on the Cluster Switch. Operations that miss in the cache are delivered to the external memory interface (EMI), which accesses the local translation lookaside buffer (LTLB) to find a virtual to physical translation for the requesting address. If a translation is found, the EMI accesses the SDRAM, returns the data to the requesting cluster through the Cluster Switch, and inserts the line containing the data into the cache. If a translation is not found, an LTLB miss event is triggered and handled in software on cluster 0. Physical page frames and virtual pages are 4 Kbytes (64 8-word cache blocks) in length. Cache hits have a 3 cycle latency including both Memory and Cluster Switch traversal. Cache misses require 8-15 cycles to resolve, depending on whether the SDRAM can be accessed in page or pipeline mode. The memory system implements uncached load instructions which allow data to be accessed without polluting the cache. In addition, it implements two block buffers which serve as both a victim cache and a write buffer when a cache block is evicted [Jou90].

In memory, each MAP word is composed of a 64-bit data value, one synchronization bit, and one pointer bit. The synchronization bit is used to implement fine-grain memory synchronization on a word-by-word basis. A pair of special load and store operations specify a precondition and a postcondition. If the precondition matches the synchronization bit, the bit is set to the postcondition and the load or store completes normally. Two possible outcomes exists if the precondition test fails. If the memory operation is unfaulting, then the programmer is notified in a condition code register that the operation failed. The program can then retry the operation and spin if necessary. If the memory operation is faulting, the request is placed in a hardware queue and nothing

is returned to the program. A software handler can later retry the memory operation or cause the user program to block.

The pointer bit is used to provide data and code protection in a single global virtual address space through guarded pointers [CKD94]. Guarded pointers implement a light-weight capability system that organizes the global address space into segments which must be accessed with unforgeable pointers. Paging manages the relocation of data in physical memory within the virtual address space. The protection and paging mechanisms are independent so that data integrity may be preserved on variable-size segments of memory. Segmentation checks are performed in the cluster during address calculation. When a memory operation executes, the permission of the pointer is examined to determine if the operation is legal. If the check determines that a memory operation is illegal, a cluster's memory unit triggers an exception. Data is controlled on a segment-by-segment basis which can prevent protected data from being read, and read-only segments from being written. These mechanisms of guarded pointers enable multiple protection domains to be resident in the processor simultaneously, and allow an individual thread to change its addressing environment very inexpensively

The memory system also includes support for sharing data across multiple MAP chips. Each LTLB and page table entry includes two block-status bits for each cache line in the page (128 bits total). These bits encode four possible cache line states, including Read-only, Read-write, Dirty, and Invalid. Copies of a cache line may reside simultaneously on different M-Machine nodes, and the block-status bits are used to help keep the data coherent. For example, a write to a Read-only cache line will trap to a software routine which can then retrieve an exclusive copy of the line by sending a message to the home node of the data. Remote data can be cached locally in both the on-chip cache and local memory. A more complete description and evaluation of the hardware and software support for shared memory on the M-Machine can be found in [Car98].

#### 2.1.3 Global Configuration Space

The Global Configuration Space (GCFG) controller enables a program to access the MAP chip's internal registers and control state. These locations are mapped into the configuration address space, which is separate from the virtual and physical memory address spaces. GCFG requests are accepted from the Memory Switch and results are returned via the Cluster Switch. Centralized

state, such as the global cycle counter, the performance monitoring controllers and counters, the thread status bits, and the I/O interface are located within the GCFG controller.

The GCFG controller communicates with local configuration space controllers to access other state that is distributed throughout the MAP chip. In each cluster, all of the registers and score-boards can be read and written via configuration space. To read a remote cluster's register, a load is performed to the appropriate configuration space location. Upon receiving it, the GCFG controller forwards it over the Cluster Switch to the local configuration space (LCFG) controller in the target cluster. The LCFG controller accesses the register by injecting a synthetic operation into the pipeline that delivers the data to the requesting cluster using the Cluster Switch. In this fashion, threads can be started, stopped, and swapped in and out by using a sequence of load and store operations. Since remote access using the GCFG is somewhat slow, it is not intended to be used intensively by application programs. However, some thread control instructions are made available to the user. Both the hfork and hexit instructions, which allow a thread to be created and destroyed, are interpreted as GCFG store operations. In response to one of these requests, the GCFG performs a series of transactions that update the appropriate registers in both the GCFG state and the cluster. This serves as a shortcut for creating and terminating threads, allowing faster thread interaction with less overhead.

#### 2.1.4 On-Chip Switches

The Memory and Cluster Switches connect the different asynchronously executing components of the MAP chip. The Memory Switch allows clusters to make memory requests to both of the on-chip cache banks as well as the Global Configuration Space controller. The Memory Switch has 3 input ports, one for each cluster, and 2 output ports, one for each cache bank; the GCFG controller shares an output port with Bank 1. In each cluster, both the memory unit and the instruction fetch unit compete for the Memory Switch port, using a round-robin arbitration scheme.

The Cluster Switch is used to return requested data from the memory system to the clusters, to allow clusters to communicate with one another using register-register transfers, and to transfer the contents of outgoing messages from the registers of the sending cluster to the network output unit. Most Cluster Switch transactions include only a single word, but a burst mode is used to transfer atomically a stream of words from the cluster to the network interface for send instructions.

Figure 2.4: The MAP send instruction transfers data from the register file on one M-Machine node to the register file of another.

Arbitration is performed among the seven requesters to determine which requests will be satisfied. External Memory Interface (EMI) requests have the highest priority, followed by the Global Configuration Space controller. At the next tier, round robin arbitration selects between the two cache banks. At the lowest level, a round robin strategy selects among the three clusters. Since all data returned from the memory system is ultimately in response to cluster based memory requests, placing the clusters at the lowest priority for the Cluster Switch provides natural backpressure to the execution units. Thus a cluster's execution units will stall if previous switch transactions are clogging the Cluster Switch.

#### 2.1.5 Communication Subsystem

In order to reduce the latency to communicate between different MAP chips, the M-Machine provides a fast, protected, user-level message passing substrate [LDK<sup>+</sup>98]. Each MAP chip includes a highly integrated network interface and a 2-dimensional mesh router. As shown in Figure 2.4, messages are composed in a thread's general registers and launched atomically with a user-level send instruction. A state machine sequences the message contents over the Cluster Switch to the network output unit (NETOUT). The NETOUT injects the message into the network using a port into the router located on-chip. The message is routed to its destination using the routers on other MAP chips that lie along the message's path. When the message arrives at its destination, it is queued in a hardware FIFO that is mapped to a register in an H-Thread belonging to the system V-Thread (V-Thread 5). A system-level message handler removes the message contents

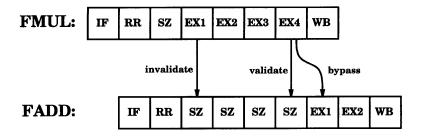

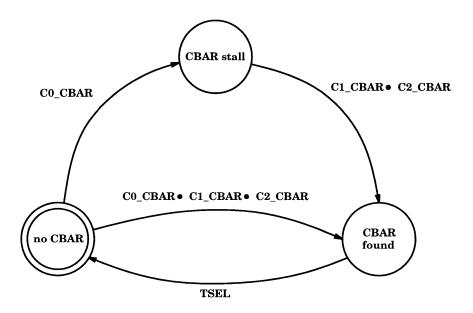

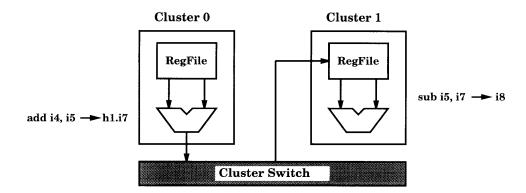

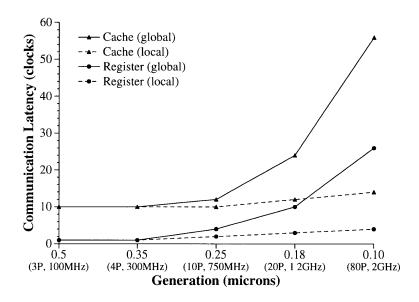

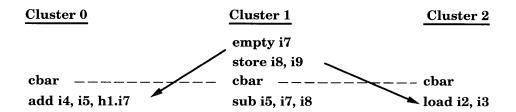

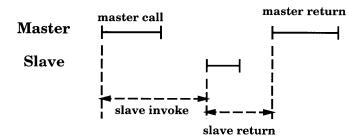

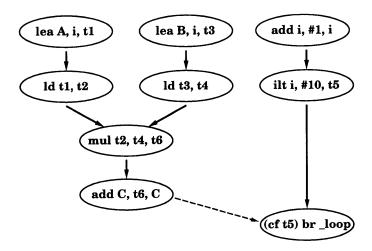

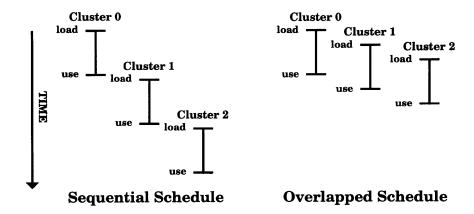

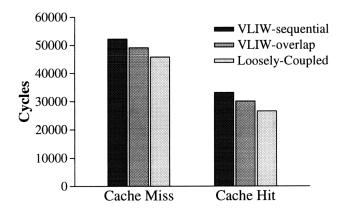

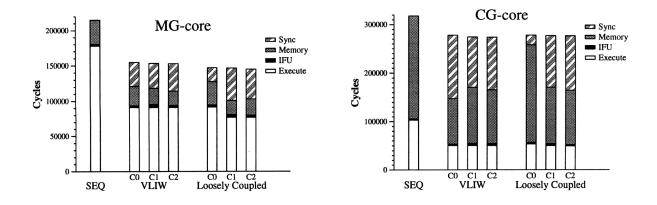

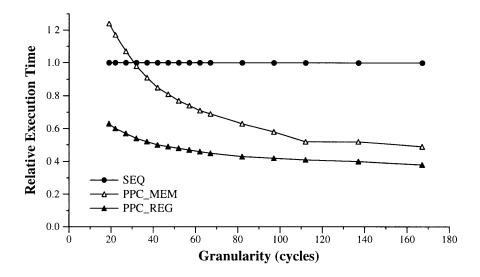

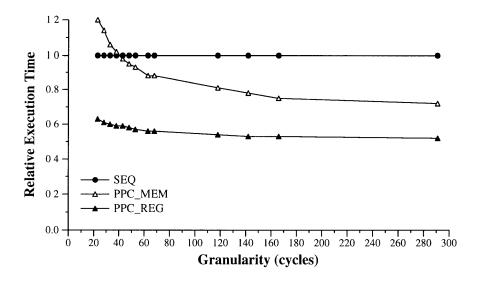

from queue, and performs the required action. Two network priorities are provided, one each for requests and replies. Messages are routed in dimension order using up to four virtual channels. The router connects MAP chips together using 36 pins for each of the 4 physical channels. The network operates at twice the clock frequency as the MAP core so that one 64-bit word can be sent every cycle. Adjacent MAP chips communicate using a bidirectional signalling discipline, in which they both can simultaneously transmit and receive data on the same wire [DLD93].