### MIT Open Access Articles

A Simple Semiempirical Short-Channel MOSFET Current-Voltage Model Continuous Across All Regions of Operation and Employing Only Physical Parameters

The MIT Faculty has made this article openly available. *Please share* how this access benefits you. Your story matters.

**Citation:** CDF Collaboration et al. "Search for High-Mass Resonances Decaying to Dimuons at CDF." Physical Review Letters 102.9 (2009): 091805. © 2009 IEEE

**As Published:** http://dx.doi.org/10.1109/ted.2009.2024022

Publisher: Institute of Electrical and Electronics Engineers

Persistent URL: http://hdl.handle.net/1721.1/52366

**Version:** Final published version: final published article, as it appeared in a journal, conference proceedings, or other formally published context

**Terms of Use:** Article is made available in accordance with the publisher's policy and may be subject to US copyright law. Please refer to the publisher's site for terms of use.

# A Simple Semiempirical Short-Channel MOSFET Current-Voltage Model Continuous Across All Regions of Operation and Employing Only Physical Parameters

Ali Khakifirooz, Member, IEEE, Osama M. Nayfeh, Member, IEEE, and Dimitri Antoniadis, Fellow, IEEE

Abstract—A simple semiempirical model  $I_D(V_{GS}, V_{DS})$  for short-channel MOSFETs applicable in all regions of device operation is presented. The model is based on the so-called "top-ofthe-barrier-transport" model, and we refer to it as the "virtual source" (VS) model. The simplicity of the model comes from the fact that only ten parameters are used. Of these parameters, six are directly obtainable from standard device measurements: 1) gate capacitance in strong inversion conditions (typically at maximum voltage  $V_{GS} = V_{dd}$ ); 2) subthreshold swing; 3) drain-induced barrier lowering (DIBL) coefficient; 4) current in weak inversion (typically  $I_{\rm off}$  at  $V_{GS}=0$  V) and at high  $V_{DS};$  5) total resistance at  $V_{DS}=0~{

m V}$  and  $V_{GS}=V_{dd}$  and 6), effective channel length. Three fitted physical parameters are as follows: 1) carrier low-field effective mobility; 2) parasitic source/drain resistance, 3) the saturation region carrier velocity at the so-called virtual source. Lastly, a constrained saturation-transition-region empirical parameter is also fitted. The modeled current versus voltage characteristics and their derivatives are continuous from weak to strong inversion and from the linear to saturation regimes of operation. Remarkable agreement with published state-of-the-art planar short-channel strained devices is demonstrated using physically meaningful values of the fitted physical parameters. Moreover, the model allows for good physical insight in device performance properties, such as extraction of the VSV, which is a parameter of critical technological importance that allows for continued MOSFET performance scaling. The simplicity of the model and the fact that it only uses physically meaningful parameters provides an easy way for technology benchmarking and performance projection.

Index Terms—CMOS scaling, inversion charge density, MOSFET compact modeling, virtual source velocity.

#### I. INTRODUCTION

OSFET compact modeling has been the subject of a vast amount of technical literature, and models of various degrees of complexity and accuracy exist. Conceptually, compact

Manuscript received October 13, 2008; revised April 27, 2009. Current version published July 22, 2009. This work was supported by the Semiconductor Research Corporation Focus Center Research Program under the Center for Materials, Structures and Devices. The review of this paper was arranged by Editor R. Huang

- A. Khakifirooz was with Microsystems Technology Laboratory, Massachusetts Institute of Technology, Cambridge, MA 02139 USA. He is now with IBM Research at Albany Nanotech, Albany, NY 12203 USA (e-mail: khaki@us.ibm.com).

- O. M. Nayfeh and D. Antoniadis are with the Microsystems Technology Laboratories, Massachusetts Institute of Technology, Cambridge, MA 02138 USA

- Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TED.2009.2024022

models can be considered to consist of a multilevel hierarchy. At the first level are the carrier charge and transport models, in which some parameters are represented by second-level models of geometry-dependent electrostatics and even by third-level models that capture layout dependencies. While the majority of compact models are concerned with computer-aided-design applications and with accurate and detailed fittings to device characteristics over a range of geometry and layout features, the model presented in this paper belongs strictly to the first level with the goal of providing a simple and intuitive understanding of the underlying carrier transport in modern short-channel planar MOSFETs with the capability, for example, of extracting the virtual source carrier velocity. The "new" semiempirical model describes the short-channel MOSFET current versus voltage characteristics and is valid in all regions of operation, with continuity of both current and its derivatives. To demonstrate the model, this paper also presents some example fittings to state-of-the-art MOSFETs. The model is very simple and reasonably accurate and is based on the physics of shortchannel device transport with only physical quantities that are either known, e.g., gate length, or are easily obtainable from standard output and transfer characteristics. While much of the parameter reduction in this model compared to standard compact models comes primarily from the fact that this is only a first level model, still, by adopting a rather simple physical concept as its basis, even at this level, the model has inherent simplicity and requires few fitting parameters. The key value of the model is that it allows extraction of the so-called virtual-source carrier velocity, which is a parameter of great technological importance [1] that cannot be obtained via direct measurement. Moreover, the fact that the model is based only on a limited number of physically meaningful parameters allows for easy technology benchmarking and performance projection [1]. The term "new" here is used with some hesitation because, practically, all ideas used in the model have been discussed in one form or another in the vast topical literature, but to the best of our knowledge, they have never been combined in the way done in this paper. For reasons that will become obvious in Section II, we refer to this model as the virtual source (VS) model.

#### II. VS MODEL IN SATURATION

In the "charge-sheet approximation," the drain current normalized by width  $(I_D/W)$  of a MOSFET can be described by

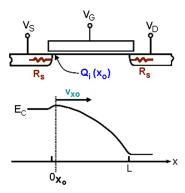

Fig. 1. Virtual source point  $x_0$  in the channel of a modern short-channel MOSFET. The carrier charge and velocity, used in (1) and through this work, are defined at this point (at the peak of the conduction band profile).

the product of the local charge areal density times the local carrier velocity anywhere in the channel. It is particularly useful to write this expression at the location of the "virtual source," i.e., at the location of the top of the energy barrier  $(x=x_o)$  between the source and channel (see Fig. 1) because the channel charge density there  $Q_{ix_o}$ , is easiest to model [2], [3], i.e.,

$$I_D/W = Q_{ix_o} v_{x_o}. (1)$$

For short-channel devices, the virtual source velocity,  $v_{x_0}$  is related to the so-called unidirectional thermal velocity, or ballistic velocity  $v_{\theta}$ , as has been discussed at length elsewhere [2], [3]. It turns out, as will be shown later in this paper by direct comparison with measured data in the literature, that  $v_{x_o}$  is weakly dependent on either  $V_{GS}$  or  $V_{DS}$ , provided that the device is biased in saturation (in either strong or weak inversion). In fact, it has been shown that in the saturation regime, the ballistic velocity and the inversion charge density at the virtual source [except for drain-induced barrier lowering (DIBL) dependence] are independent of  $V_{DS}$  [3]. It is further demonstrated that even at the nonballistic regime inversion charge density at the top of the barrier  $Q_{ix_o}$  and carrier velocity at this point  $v_{x_o}$  are almost independent of  $V_{DS}$  if the device operates in the saturation region. On the other hand, while the ballistic velocity increases monotonically with  $V_{GS}$  [3], Monte Carlo simulations demonstrate that the virtual source velocity is almost constant at high  $V_{GS}$  [1] since carrier scattering also increases with the gate voltage.

Note that instead of using the ballistic velocity along with the backscattering coefficient to describe the  $I_D$ – $V_{GS}$  characteristics in saturation, as done, for example, in [3], we opt to use the average velocity of carriers at the virtual source  $v_{x_o}$  to avoid the complication caused by exact dependencies of the backscattering coefficient on device parameters and bias, and the ambiguity of the  $k_BT$  layer.

The virtual-source charge density can be approximated quite closely by the new empirical function in (2). This expression allows for a continuous expression for the inversion charge density at the virtual source from weak to strong inversion. The form of the expression (i.e., without the new  $\alpha$  term in the exponential) was first proposed by Wright [4] as follows:

$$Q_{ix_o} = C_{inv} n\phi_t \ln \left( 1 + \exp \frac{V'_{GS} - (V_T - \alpha\phi_t F_f)}{n\phi_t} \right)$$

(2)

where  $C_{\rm inv}$  is the effective gate-to-channel capacitance per unit area in strong inversion,  $\phi_t$  is the thermal voltage  $(k_BT/q), V'_{GS}$  is the internal gate–source voltage, i.e., corrected for the voltage drop on the source resistance  $R_S$  and is given by  $V'_{GS} = V_{GS} - I_DR_S$ , n is the subthreshold coefficient, which is related to the so-called "subthreshold swing" by  $S = n\phi_t \ln 10$ , and

$$V_T = V_{T0} - \delta V'_{DS} \tag{3}$$

where  $V_{T0}$  is the strong-inversion threshold voltage at  $V_{DS}=0,\ V'_{DS}$  accounts for the voltage drop on both  $R_S$  and  $R_D$  (drain resistance) as  $V'_{DS}=V_{DS}-I_D(R_S+R_D)$ , and  $\delta$  is the DIBL coefficient in V/V. Note that DIBL is the only term that introduces dependency of  $Q_{ix_o}$  on  $V_{DS}$ . The term following  $V_T$  in (2) allows for the requirement of different values of threshold voltage (better stated as "reference voltage") in strong and weak inversion, as discussed at length in the literature, e.g., [5]–[7]. It was found empirically in this work that a shift of  $V_T$  by 3.5 $\phi_t$  is a very good approximation, and hence,  $\alpha=3.5$  in (2) is used in this work. The following "inversion transition" function  $F_f$  is a Fermi function that allows for a smooth transition between the two values of reference voltage and is centered at the point halfway between them:

$$F_f = \frac{1}{1 + \exp\left(\frac{V'_{GS} - (V_T - \alpha\phi_t/2)}{\alpha\phi_t}\right)}.$$

(4)

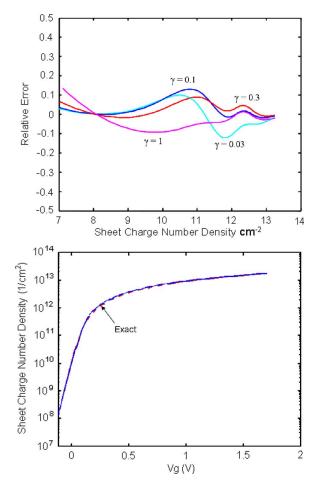

Fig. 2 compares the approximate solution of (2) with  $\alpha=3.5$  to the exact solution from a 1-D Poisson solution (e.g., [7]) under the sheet-charge approximation and assuming nondegenerate conditions for different values of the body factor:  $\gamma=\sqrt{2q\varepsilon_{\rm Si}N}/C_g$ . As can be seen in the figure, the approximation in (2) produces an error less than 15% over seven orders of magnitude of channel-charge number-density up to a maximum of  $2.5\times10^{13}~{\rm cm}^{-2}$ , which is a sufficient range for most MOSFET applications. Moreover, note that the error in the strong-inversion region is below 5% for more technologically reasonable values of body factor in the range of  $0.1-1~{\rm V}^{1/2}$ . It was found that the errors remained nearly unchanged with temperatures over a wide range, e.g., form  $-20~{\rm ^{\circ}C}$  to  $100~{\rm ^{\circ}C}$ .

Of course, the virtual source charge density of a shortchannel device can only be derived from a 2-D Poisson solution. In the 2-D case, the subthreshold swing is dictated by a combination of doping and geometrical electrostatics. However, the overall shape of the charge versus  $V_{GS}$  characteristics does not change, and comparisons with 2-D device simulations, including degenerate conditions (not shown here), indicate that (2)–(4) still yield a good approximation to the charge density with errors no larger than that shown in Fig. 2. All that is required is that  $C_{inv}$  at maximum  $V_{GS}$ , n, and the value of the charge  $Q_{ix_0}$  at a particular value of  $V_{GS}$  in weak inversion be all matched to the theoretically calculated (or simulated) charge. Note that matching these three parameters to data uniquely determines the value of  $V_T$ . Similarly, it was found by comparisons to theoretical calculations that included the inversion layer quantum-mechanical effect [8] and reasonable amounts of poly depletion [8] that (2)–(4) are still an excellent approximation, provided the above three parameters are matched.

Fig. 2. (a) Relative error of the approximate solution for charge using (2) with  $\alpha = 3.5$  as compared to 1-D Poisson solution under the charge-sheet approximation. For comparison, the value of  $V_{T0}$  was fitted to match the value of  $V_{GS}$  at a charge density of  $10^8~{\rm cm}^{-2}$  in the exact and approximate solutions. The subthreshold swing was calculated from the classical expression  $n = 1 + \gamma/2\sqrt{2\phi_F}$ .  $C_g$  was matched to the theoretically calculated value at  $V_{GS}=1.2~{

m V}$ , which was set to 1.9  $\mu{

m F/cm^2}$  in the theoretical calculation while the body factor  $\gamma$  (in  $V^{1/2}$ ), was varied by changing doping from  $10^{16}$  to  $10^{19}~{\rm cm}^{-3}$ . (b) Model versus exact charge solution for "worst case" approximation for  $\gamma = 0.03$ .

#### III. NONSATURATION

To account for the nonsaturation region, the velocity  $v_{x_0}$  in (1) is multiplied by a "saturation function"  $F_s$ , which increases smoothly from 0, at  $V_{DS}^{\prime}=$  0, to 1, at  $V_{DS}^{\prime}>V_{DSAT},$  where  $V_{D{\rm SAT}}$  is the saturation voltage. Equation (1) is then generalized to (5), given as follows, which is valid over all regions of operation:

$$I_D/W = Q_{ix_o} v_{x_o} F_s \tag{5}$$

$$I_{D}/W = Q_{ix_{o}} v_{x_{o}} F_{s}$$

(5)

$$F_{s} = \frac{V'_{DS}/V_{DSAT}}{\left(1 + (V'_{DS}/V_{DSAT})^{\beta}\right)^{1/\beta}}.$$

(6)

This  $F_s$  function is akin to the carrier velocity saturation function used elsewhere [9], [10], but here, it serves to empirically reproduce the nonsaturation behavior of the I-V characteristics. At  $V_{DS} = 0$ ,  $F_s$  is 0, while it becomes equal to 1 for  $V_{DS}'\gg V_{D{\rm SAT}}$  and, hence, allows the full value of  $v_{x_0}$  in (5). In principle,  $\beta$  is a saturation-transition-region fitting parameter,

but it was generally found in this work that excellent fits to measured modern MOSFET data, as will be discussed later, can be obtained with  $\beta = 1.8$  for nFETs and  $\beta = 1.4$  for pFETs. It is interesting to note that typical values of  $\beta$  when (6) has been used to model carrier velocity saturation are 2 for electrons and 1 for holes [10], [11].

Returning to (6), it is noted that the derivative of this equation with respect to  $V_{DS}^{\prime}$  at  $V_{DS}^{\prime}=0$  is  $1/V_{D\mathrm{SAT}},$  irrespective of the value of  $\beta$ , and therefore, we have

$$\frac{1}{W} \frac{\partial I_D}{\partial V'_{DS}} \bigg|_{V_{DS} = 0} \cong \frac{Q_{ix_o}(V_{DS} = 0)v_{x_o}}{V_{DSAT}} \equiv \frac{1}{WR_{C\min}}. \quad (7)$$

Here, the approximate sign is used because of the assumption that the  ${\cal V}_{DS}$  dependency of both  $v_{x_o}$  and  $Q'_{ix_o}$  is negligible.  $WR_{C \min}$  is the width-normalized resistance of the channel at  $V_{DS} = 0$  (in ohm centimeters), where it has its minimum value for any given value of  $V_{GS}$ , i.e.,

$$WR_{C\min} = \frac{L_C}{Q_{ix_00}\mu} \tag{8}$$

where  $L_C = L_G - 2L_{ov}$  is the effective channel length obtained from the gate length, accounting for source and drain overlap  $(L_{ov})$ ,  $\mu$  is the channel carrier effective mobility at  $V_{DS} = 0$  V, which, of course, is a function of  $V_{GS}$  but is assumed constant to the first order, and  $Q_{ix_0} \equiv Q'_{ix_0} (V_{DS} = 0)$ is defined for convenience. Using (8) in (7) determines the value of  $V_{DSAT} = V_{DSATs}$  in strong inversion, which is independent of  $\beta$  and only dependent on physical parameters, i.e.,

$$V_{DSATs} = \frac{v_{x_o} L_C}{\mu}.$$

(9)

To properly account for saturation in weak inversion,  $V_{DSAT}$  in (6) in that region should be equal to  $\phi_t$ . While this is an approximation because  $F_s$  is not exactly equal to  $1 - \exp(-V_{DS}/\phi_t)$ as it should be in weak inversion, the resulting error is less than about 10% for a range of  $\beta$  values from 1.4 to 2.5 (not shown). Finally, to allow a smooth transition between the strong- and weak-inversion values of the saturation voltage, a generalized form of the saturation voltage is introduced by employing again the inversion transition function  $F_f$ , defined by (4), as follows:

$$V_{DSAT} = V_{DSATs}(1 - F_f) + \phi_t F_f. \tag{10}$$

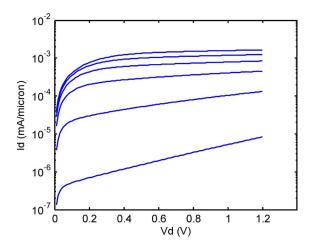

It can easily be seen from (4) that  $F_f$  in strong inversion tends to zero, while in weak inversion, it tends to unity, and thus,  $V_{DSAT}$  correspondingly varies smoothly from  $V_{DSATs}$  to  $\phi_t$ . Fig. 3 exemplifies the behavior of the model over the complete range of operation of a MOSFET. The smooth transition of the saturation voltage from weak inversion to strong inversion is clearly evident.

It should be emphasized that (6) and (10) are heuristic. It can be easily shown from (1), (8), and (9) that  $V_{DSATs}$  is approximately equal to the value of  $V_{DS}$  where the current through the resistor  $R_{C \min}$  is equal to the saturation current, i.e., it is determined by the intercept of the  $1/WR_{C\min}$  and  $Q_{ix_0}v_{x_0}$  loci in the  $I_D/W$  versus  $V_{DS}$  plane. While this is appealing, it is not physically rigorous. In addition, the form of

Fig. 3. Model output characteristics as in Fig. 4(a) in a semilog plot to illustrate the continuity of the model from weak to strong inversion and from linear to saturation regions.

(6) is not fully physically justified, even though it is borrowed from the velocity saturation expression [9], [10]—it is not justifiable to assume that the lateral electric field is given by  $V_{DS}/L_C$  under all conditions in strong inversion, as actually implied by (6). Nevertheless, as can be seen in Section IV, the fitting of the VS model to real device data is very good and comes with physically justifiable parameters.

#### IV. APPROXIMATE EVALUATION OF THE MODEL

It is clear from the fact that the internal voltages  $V_{GS}'$  and  $V_{DS}'$  are required in (5) and (6) that explicit solution of the model equations requires iterations in order to obtain self-consistent values of  $V_{GS}' = V_{GS} - I_D R_S$  and  $V_{DS}' = V_{DS} - I_D (R_S + R_D)$ . However, iterations can be avoided with relatively little loss of accuracy by simply replacing the internal voltages in (2)–(5) by the applied external ones, namely,  $V_{GS}$  and  $V_{DS}$ , while replacing the virtual-source velocity in (5) by the effective velocity v, which is given by:

$$v = \left(F_f + \frac{1 - F_f}{1 + WR_S C_g (1 + 2\delta) v_{x_o}}\right) v_{x_o}.$$

(11)

As in the case of (10), the Fermi function  $F_f$ , which is given in (4), allows for a smooth transition of v from a value of  $v_{x_o}$  in weak inversion  $(F_f \sim 1)$ , where there is no degradation due to the presence of  $R_S$ , to the value that is appropriately degraded in strong inversion  $(F_f \sim 0)$ . The derivation of the second term in the right-hand side of (11) for the case of operation only in the strong-inversion region and, therefore, for  $F_f = 0$  has been discussed in [12] and [13]. In addition,  $R_S + R_D$  must be added explicitly to the right-hand side of (8) so that the correct total resistance at  $V_{DS} = 0$  V can be obtained. Then, the strong-inversion saturation voltage becomes

$$V_{DSATs} = (R_S + R_D)WQ_{ix_o0}v + \frac{vL_C}{\mu}.$$

(12)

Finally, it is found that for this implicit solution, the  $\beta$  factor in the saturation function  $F_s$  [see (6)] should be set to approximately 2.5 for nFETs and 2.0 pFETs. The model implementa-

tion in this approximate form is entirely closed form, which is useful for some applications, but in Section V, only the exact explicit solution given by (1)–(10) is used.

## V. COMPARISON OF THE MODEL TO DATA AND DISCUSSION

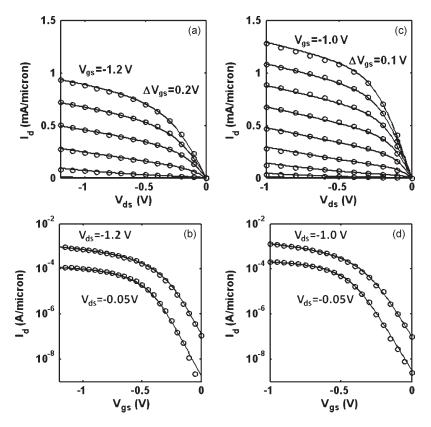

Example fits to device data of a modern uniaxially strained 65- and 32-nm node technologies [14], [15] are shown in Figs. 4 and 5. As can be seen, the model description of the data is very good over a broad range and of bias values, and over two different technologies, i.e., with poly-SiON and high-k metalgate stacks. Table I shows the device parameters that can be considered as given for this model, i.e.,  $C_{\rm inv}$ ,  $I_{\rm off}(V_{GS},V_{DS})$ , S,  $\delta$ , and  $L_G$ . Since the data come from the literature, a value for  $L_{\rm ov}=5$  nm had to be assumed—the same for both technologies. This assumption does affect somewhat the extracted value of  $\mu$ , as will be discussed next. The extracted parameters are  $v_{x_o}$ ,  $WR_S$ ,  $\mu$ , and  $\beta$ . As can be seen from the table, the extracted values are physically reasonable and come with the correct trend between the two technologies.

The methodology for fitting can be accomplished manually with little iteration, although standard optimization methods can also be used. First, the capacitance  $C_{\text{inv}}$  is set to the strong-inversion value measured at  $V_{GS} = V_{dd}$ , which is typically reported. Second, the subthreshold swing parameter n,  $I_{\rm off}$  (typically at  $V_{GS}=0$  V and  $V_{DS}=V_{dd}$ ), and the DIBL coefficient  $\delta$  are obtained directly from the measured transfer characteristics of the device. Naturally, in order to match the calculated  $I_{\rm off}$  to the measured value, an initial guess for  $v_{x_o}$ is required; a good starting value is  $v_{x_0} = 10^7$  cm/s, and it is then refined as described later. Note that this process sets the value of  $V_T$  and establishes the correct electrostatic behavior of the device. Third, from the  $I_D$  versus  $V_{DS}$  output curve for  $V_{GS} = V_{dd}$ , the total resistance  $2R_S + R_{C \min}$  is obtained from the slope  $dI_D/dV_{DS}|_{V_{DS}=0}$  at  $V_{DS}=0$  V—it can typically be assumed that  $R_S = R_D$  for symmetric devices. At this point, an assumption about  $L_C$  and  $\mu$  is required in order to isolate and extract  $R_S$ . A good typical value for  $L_{\rm ov}$  is  $\sim 0.15 \times$  the nominal short-channel  $L_G$ , and  $\mu \sim$  $200-300 \text{ cm}^2/\text{V} \cdot \text{s}$  for electrons and  $\mu \sim 100-250 \text{ cm}^2/\text{V} \cdot \text{s}$ for holes in strained Si. Finally, the velocity  $v_{x_0}$  is adjusted by comparing model results in saturation with measured data at  $V_{DS} = V_{dd}$  and at various  $V_{GS}$  values. The model is quite constrained, and therefore, relatively minor adjustments of the initial parameter values are typically required or are, indeed, possible. Typically, in nominal short-channel devices, the parasitic resistance dominates at the highest value of  $V_{GS}$ , and therefore, errors in the assumptions for  $L_{\rm ov}$  and  $\mu$  are not very critical for the extraction of  $R_S$ , which, in turn, is critical for obtaining an accurate value for  $v_{x_0}$ . With some experience and good engineering judgment, very reasonable physical parameters can be obtained, as can be seen in Figs. 4 and 5 and Table I; it should be noted that these particular MOSFETs exhibit the lowest values of  $R_S$  in the authors' experience, but they are well within the physical range for well-engineered devices. Furthermore, although the values of carrier velocity may appear high, it should be noted that the devices have

Fig. 4. Comparison of model current (lines) with data (circles). (a) and (b) For a 65-nm technology uniaxially strained nFET technology with poly-SiON gate stack [13] and gate length  $L_G=35$  nm. (c) and (d) For a 32-nm technology uniaxially strained nFET with a metal-gate high-k stack [14] and gate length  $L_G=32$  nm. Device parameters are given in Table I.

Fig. 5. Comparison of model current (lines) with data (circles). (a) and (b) For a 65-nm technology uniaxially strained pFET technology with poly-SiON gate stack [13] and gate length  $L_g=35$  nm. (c) and (d) For a 32-nm technology uniaxially strained nFET with a metal-gate high-k stack [Intel IeDM 08] and gate length  $L_g=32$  nm. Device parameters are given in Table I.

|                                           | 65-nm | 32-nm | 65-nm | 32-nm |

|-------------------------------------------|-------|-------|-------|-------|

|                                           | CMOS  | CMOS  | CMOS  | CMOS  |

|                                           | nFET  | nFET  | pFET  | pFET  |

| $C_{inv}$ [ $\mu$ F/cm <sup>2</sup> ]     | 1.83  | 2.65  | 1.70  | 2.60  |

| $L_G$ [nm]                                | 35    | 32    | 35    | 32    |

| $L_{ov}$ [nm]                             | 5     | 5     | 5     | 5     |

| S [V/decade]                              | 0.10  | 0.098 | 0.095 | 0.095 |

| δ [V/V]                                   | 0.12  | 0.13  | 0.155 | 0.145 |

| $I_{off}(V_{GS}=0, V_{dd})$ [nA/ $\mu$ m] | 120   | 100   | 135   | 100   |

| $V_{dd}$ [V]                              | 1.2   | 1.0   | 1.2   | 1.0   |

|                                           |       |       |       |       |

| $v_{xo} [10^7 \text{ cm/s}]$              | 1.4   | 1.35  | 0.85  | 1.03  |

| $WR_S$ [ $\Omega$ . $\mu$ m]              | 75    | 80    | 130   | 80    |

| $\mu$ [cm <sup>2</sup> /V.s]              | 250   | 250   | 140   | 210   |

| $\beta$                                   | 1.8   | 1.8   | 1.5   | 1.7   |

TABLE I MOSFET DEVICE PARAMETERS

been shown to be nonballistic; the thermal velocity (ballistic limit) in these uniaxially strained devices has been shown theoretically to be significantly increased compared to relaxed Si values [1].

The quality of agreement shown in Figs. 4 and 5 was found to hold over numerous devices from the literature as well as experimental devices in the authors' laboratory. Interestingly, the model produces good agreement even with non-MOSFET FETs, such as 50-nm-gate-length InGaAs HEMTs [16] using the same parameter  $\beta$  as for Si nFETs but with suitably increased electron mobility and velocity, as expected for III–V channel materials.

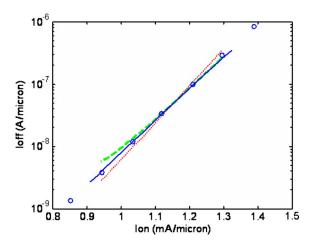

As discussed in Section I, the VS model in this paper was developed primarily in order to allow for simple and largely unequivocal characterization of the historical evolution of virtual source carrier velocity in Si-CMOS FETs operating in the saturation region and to permit extrapolation of future requirements, e.g., as done by Khakifirooz and Antoniadis [17], [18]. Nevertheless, it is rather remarkable that this minimalist model describes very well the I-V behavior of modern MOSFETs over their full range of operation and with only few physical parameters, which, moreover, are held constant. Of course, the model is not predictive in the sense that it requires the electrostatics ( $C_{inv}$ , S,  $\delta$ , and  $I_{off}$ —i.e.,  $V_T$ ) and virtual source carrier velocity and mobility as input parameters either from measurements or device simulations, or simply from educated guesses about future device structures and materials. On the other hand, if gate-length dependence of the electrostatics is available, the model can help in understanding the significance of the effects of the key MOSFET parameters and their variations over a range for gate lengths. As an example, Fig. 6 shows the VS model "predicted"  $I_{\rm off}(V_{GS}=0~{

m V},V_{DS}=1.2~{

m V})$  versus  $I_{\rm on}(V_{GS}=0.2~{

m V})$ 1.2 V,  $V_{DS} = 1.2$  V) for the nFET technology in Fig. 4 [14]. The calculations were made by varying  $L_G$  in the model from 30 to 65 nm. For these calculations, the variation of  $V_{T_{\rm sat}}$ and  $V_{T_{\mathrm{lin}}}$  (the typical constant-current threshold voltages at  $V_{DS} = 1.0 \text{ V}$  and 0.05 V, respectively) versus  $L_G$  in [14, Fig. 3] was used to reproduce the DIBL parameter  $\delta(L_G)$  and  $V_{T0}$ versus  $L_G$  dependence in the model. Note that for  $V_{T0}$  only the variation with  $L_G$  was used from the data because the

Fig. 6. Modeled versus measured  $I_{\rm off}(V_{GS}=0~{\rm V},V_{DS}=1.2~{\rm V})$  versus  $I_{\rm on}(V_{GS}=1.2~{\rm V},V_{DS}=1.2~{\rm V})$  for the nFET technology in Fig. 3. Data from [13] are depicted by points. For details of the model-calculated lines, refer to the text.

definitions of  $V_{T0}$  here, and  $V_{T_{\text{lin}}}$  in that paper are different. As can be seen in the figure, even with no other  $L_G$  parameter dependences in the model, the calculated  $I_{\rm on}$  versus  $I_{\rm off}$ (dashes) is in good agreement with the data. Next, since some increase of S with decreasing length can be expected even for these evidently very well engineered devices, a linear  $S(L_G)$  dependency on  $\delta(L_G)$  was assumed (empirically) as follows:  $S(L_G) = S(35 \text{ nm}) + (0.1 \text{ V/dec})(\delta(L_G)(\delta(35 \text{ nm})).$ The result is depicted in the dotted line. Finally, a good match to the data is achieved (solid line) by assuming a linear variation of  $v_{x_o}(L_G)$  as follows:  $v_{x_o}(L_G) = v_{x_o}(35 \text{ nm}) +$  $(10^7 \text{ cm/s})(\delta(L_G) - \delta(35 \text{ nm}))$ . This form of dependency of velocity for short-channel MOSFETs has been shown in the literature [19], [20], and the coefficient here is quite reasonable. Of course, it cannot be claimed here that the modeled velocity dependency on DIBL is physically correct because the  $S(L_G)$ dependency via DIBL was assumed empirically—the data are not available in the literature. On the other hand,  $S(L_G)$  is often available from measurements, and if so, then the  $v_{x_o}(L_G)$ would have real physical significance, for example, in quantifying the effectiveness of strain engineering in a particular technology.

#### VI. CONCLUSION

A minimalist MOSFET model that describes the  $I{-}V$  behavior of short-channel MOSFETs over the complete region of operation has been developed. In addition to physical parameters that are easily obtained from measurements, a minimum set of physically meaningful parameters, all assumed constant over the region of operation, is included, and a methodology for extracting them from data has been presented. The model is suitable for analyzing the effect of variation of these parameters and for technology road-mapping exercises. In addition, the model can form the basis of a compact model for circuit simulation with the addition of models relating its parameters to physical device dimensions and/or layout properties.

#### ACKNOWLEDGMENT

The authors would like to thank Prof. Y. Tsividis and Prof. M. Lundstrom for the useful discussions.

#### REFERENCES

- [1] A. Khakifirooz and D. A. Antoniadis, "Transistor performance scaling: The role of virtual source velocity and its mobility dependence," in *IEDM Tech. Dig.*, 2006, pp. 667–670.

- [2] M. S. Lundstrom, "Elementary scattering theory of the Si MOSFET," IEEE Electron Device Lett., vol. 18, no. 7, pp. 361–363, Jul. 1997.

- [3] M. S. Lundstrom and Z. Ren, "Essential physics of carrier transport in nanoscale MOSFETs," *IEEE Trans. Electron Devices*, vol. 49, no. 1, pp. 133–141, Jan. 2002.

- [4] G. T. Wright, "Threshold modelling of MOSFETs for CAD of CMOS-VLSI," *Electron Lett.*, vol. 21, no. 6, pp. 223–224, Mar. 1985.

- [5] Y. Cheng, M.-C. Jeng, Z. Liu, J. Huang, M. Chan, K. Chen, P. K. Ko, and C. Hu, "A physical and scalable *I–V* model in BSIM3v3 for analog/digital circuit simulation," *IEEE Trans. Electron Devices*, vol. 44, no. 2, pp. 277–287, Feb. 1997.

- [6] N. Arora, MOSFET Models for VLSI Circuit Simulation: Theory and Practice. New York: Springer-Verlag, 1997.

- [7] Y. Tsividis, Operation and Modeling of the MOS Transistor, 2nd ed. New York: McGraw-Hill, 1999.

- [8] Y. Taur and T. H. Ning, Fundamentals of Modern VLSI Devices. New York: Cambridge Univ. Press, 1998.

- [9] D. M. Caughey and R. E. Thomas, "Carrier mobilities in silicon empirically related to doping and field," *Proc. IEEE*, vol. 55, no. 12, pp. 2192–2193, Dec. 1967.

- [10] J. A. Cooper and D. F. Nelson, "High-field drift velocity of electrons at the Si-SiO<sub>2</sub> interface as determined by a time-of-flight technique," *J. Appl. Phys.*, vol. 54, no. 3, pp. 1445–1456, Mar. 1983.

[11] R. W. Coen and R. S. Muller, "Velocity of surface carriers in inversion lay-

- [11] R. W. Coen and R. S. Muller, "Velocity of surface carriers in inversion layers on silicon," *Solid State Electron.*, vol. 23, no. 1, pp. 35–40, Jan. 1980.

- [12] D. A. Antoniadis, I. Åberg, C. N. Chleirigh, O. M. Nayfeh, A. Khakifirooz, and J. L. Hoyt, "Continuous MOSFET performance increase with device scaling: The role of strain and channel material innovation," *IBM J. Res. Develop.*, vol. 50, no. 4/5, pp. 363–376, Jul. 2006.

- [13] A. Khakifirooz and D. A. Antoniadis, "The future of high-performance CMOS: Trends and requirements," in *Proc. Eur. Solid State Device Res. Conf.*, 2008, pp. 30–37.

- [14] S. Tyagi, C. Auth, P. Bai, G. Curello, H. Deshpande, S. Gannavaram, O. Golonzka, R. Heussner, R. James, C. Kenyon, S.-H. Lee, N. Lindert, M. Liu, R. Nagisetty, S. Natarajan, C. Parker, J. Sebastian, B. Sell, S. Sivakumar, A. St. Amour, and K. Tone, "An advanced low power, high performance, strained channel 65 nm technology," in *IEDM Tech. Dig.*, 2005, pp. 1070–1072.

- [15] S. Natarajan, M. Armstrong, M. Bost, R. Brain, M. Brazier, C.-H. Chang, V. Chikarmane, M. Childs, H. Deshpande, K. Dev, G. Ding, T. Ghani, O. Golonzka, W. Han, J. He, R. Heussner, R. James, I. Jin, C. Kenyon, S. Klopcic, S.-H. Lee, M. Liu, S. Lodha, B. McFadden, A. Murthy, L. Neiberg, J. Neirynck, P. Packan, S. Pae, C. Parker, C. Pelto, L. Pipes, J. Sebastian, J. Seiple, B. Sell, S. Sivakumar, B. Song, K. Tone, T. Troeger, C. Weber, M. Yang, A. Yeoh, and K. Zhang, "A 32 nm logic technology featuring 2nd generation high-κ+ metal gate transistors, enhanced chan-

- nel strain and 0.171  $\mu$ m<sup>2</sup> SRAM cell size in a 291 Mb array," in *IEDM Tech. Dig.*, 2008, pp. 1–3.

- [16] D.-H. Kim and J. A. del Alamo, "Lateral and vertical scaling of In<sub>0.7</sub>Ga<sub>0.3</sub>As HEMT for post-Si-CMOS logic applications," *IEEE Trans. Electron Devices*, vol. 55, no. 10, pp. 2546–2553, Oct. 2008.

- [17] A. Khakifirooz and D. A. Antoniadis, "MOSFET performance scaling—Part I: Historical trends," *IEEE Trans. Electron Devices*, vol. 55, no. 6, pp. 1391–1400, Jun. 2008.

- [18] A. Khakifirooz and D. A. Antoniadis, "MOSFET performance scaling—Part II: Future directions," *IEEE Trans. Electron Devices*, vol. 55, no. 6, pp. 1401–1408, Jun. 2008.

- [19] H. Hu, J. B. Jacobs, L. T. Su, and D. A. Antoniadis, "A study of deep-submicron MOSFET scaling based on experiment and simulation," *IEEE Trans. Electron Devices*, vol. 42, no. 4, pp. 669–677, Apr. 1995.

[20] A. Lochtefeld and D. A. Antoniadis, "On experimental determination of

- [20] A. Lochtefeld and D. A. Antoniadis, "On experimental determination of carrier velocity in deeply scaled NMOS: How close to the thermal limit?" *IEEE Electron Device Lett.*, vol. 22, no. 2, pp. 95–97, Feb. 2001.

**Ali Khakifirooz** (M'08) received the B.Sc. and M.Sc. degrees from the University of Tehran, Tehran, Iran, in 1997 and 1999, respectively, and the Ph.D. degree from the Massachusetts Institute of Technology (MIT), Cambridge, in 2007, all in electrical engineering.

From 1997 to 2001, he was with the Thin Films Research Laboratory, University of Tehran, where he was engaged in low-temperature fabrication of polysilicon thin-film transistors on flexible substrates. From 2001 to 2008, has was with the Mi-

crosystems Technology Laboratories, MIT, where he studied carrier transport in deeply scaled MOSFETs and worked on the fabrication and characterization of germanium-channel transistors. In May 2008, he joined IBM Research at Albany Nanotech, Albany, NY, where he is working on exploratory device design for 22-nm node and beyond. He has authored or coauthored more than 50 technical papers.

**Osama M. Nayfeh** (M'09) received the B.S. degree in electrical and computer engineering from the University of Illinois at Urbana-Champaign in 2002 and the Ph.D. degree in electrical engineering and computer science from the Massachusetts Institute of Technology (MIT), Cambridge, in 2008. His thesis investigated nonvolatile memory devices using colloidal silicon nanoparticles.

He is currently a Postdoctoral Researcher with MIT, where his research focuses on novel nanoelectronic devices for advanced computation and mem-

ory applications. He is the author or coauthor of 19 technical articles and has given several research presentations at academic, governmental, and industrial locations.

Dr. Nayfeh is a member of the IEEE, Materials Research Society and Sigma Xi. He was the recipient of the Intel Fellowship in 2007 for his work on nanotechnology-based devices.

**Dimitri Antoniadis** (M'79–SM'83–F'90) was born in Athens, Greece. He received the B.S. degree in physics from the National University of Athens, Athens, Greece, in 1970, and the Ph.D. degree in electrical engineering from Stanford University, Stanford, CA, in 1976.

He has been with the Microsystems Technology Laboratories, Massachusetts Institute of Technology (MIT), Cambridge, since 1978, where he is the Ray and Maria Stata Chair in Electrical Engineering. He is the Director of the multiuniversity Focus Research

Center for Materials Structures and Devices centered at MIT. He is the author or coauthor of more than 200 technical papers. His present research focuses on the physics and technology of extreme submicrometer Si, silicon-on-insulator, and Si/SiGe MOSFETs.

Dr. Antoniadis is a member of the National Academy of Engineering and the recipient of several professional awards.