### STANDARDIZING AND IMPROVING TEST WAFER PROCESSES: INVENTORY OPTIMIZATION AND A DAYS OF INVENTORY PULL SYSTEM

By David W. Johnson OF TECHNOLOGY

JUN 16 2009

LIBRARIES

B.S. 2001 Mechanical Engineering Rensselaer Polytechnic Institute

| Submitted to the MIT Sloan School of Management and the Department of Mechanical Engineer | ing |

|-------------------------------------------------------------------------------------------|-----|

| in Partial Fulfillment of the Requirements for the Degrees of                             |     |

Master of Business Administration AND Master of Science in Mechanical Engineering In conjunction with the Leaders for Manufacturing Program at the Massachusetts Institute of Technology June 2009 ARCHIVES © 2009 Massachusetts Institute of Technology. All rights reserved. Signature of Author \_\_\_\_\_. May 8, 2009 Mechanical Engineering, MIT Sloan School of Management Certified by \_\_\_\_\_\_ Deborah Nightingale, Thesis Supervisor Professor of the Practice, Aeronautics & Astronautics and Engineering Systems Division Certified by Stephen Graves, Thesis Supervisor Abraham Siegel Professor of Management, MIX Sloan School of Management Certified by David Hardt, Thesis Reader Ralph E. and Eloise F. Cross Professor of Mechanical Engineering Accepted by \_\_\_\_\_ / 😂 -David Hardt Ralph E. and Eloise F. Cross Professor of Mechanical Engineering Accepted by \_\_\_\_\_ E Debbie Berechman Executive Director of MBA Program, MIT Sloan School of Management

This page has been intentionally left blank.

### Standardizing and Improving Test Wafer Processes: Inventory Optimization and a Days of Inventory (DOI) Pull System

by

### David W. Johnson

Submitted to the MIT Sloan School of Management and the Department of Mechanical Engineering on May 8, 2009 in Partial Fulfillment of the Requirements for the Degrees of Master of Business Administration and Master of Science in Mechanical Engineering

# Abstract

#### Summary:

Over the past few years, the Intel Fab-17 facility has aggressively pursued lean methodology to reduce the manufacturing costs associated with its aging 200mm diameter wafer process. One area ripe with improvement opportunities is the processes supplying and managing Test Wafers, which are non-production wafers used to verify production tools and operations.

With four test wafer types, hundreds of different sequences of operations (defined as routes), and varying consumption trends, thousands of decisions must be made daily to ensure Test Wafers are available on time and with the proper base characteristics. To further illustrate the magnitude and importance of Test Wafer systems, roughly the same number of Test Wafers are introduced each time period into the fab as production wafers.

Through direct observation and process mapping techniques, I identified two system level projects, each containing enormous cost and performance improvements to the entire facility.

### Project One: Reallocating excess inventory

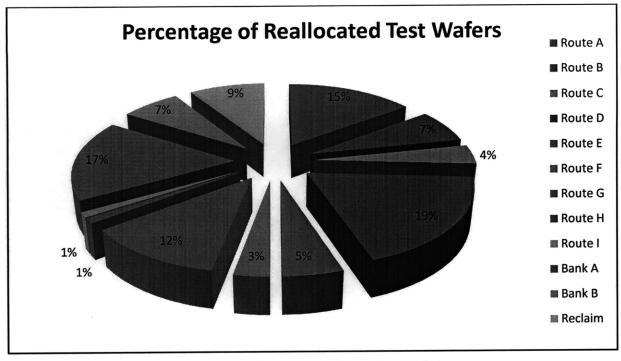

In analyzing the Test Wafer inventory quantity and consumption rates in primary stockroom, I noticed that certain routes had excess inventory while others were deficient, thus leading to significantly more expensive Test Wafers types to be used instead. In order to maximize realized cost savings, I developed a linear optimization program which distributed excess Test Wafer inventory to areas of need. Different re-allocation costs, initial material specifications, and forecasted consumption needs constrained the quantity and location for this redistribution.

Per the optimization program's recommendations, I led a team to re-allocate the largest excess Test Wafer inventory area to twelve different locations. The savings for this project correspond to over a year's worth of test wafer inventory now available for these routes and banks.

### Project Two: Determining supply decisions from a Days of Inventory (DOI) metric

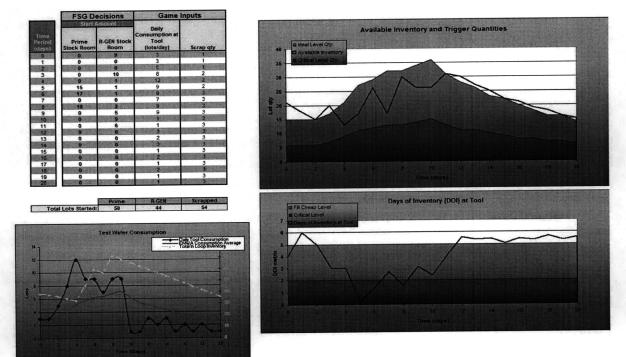

The previous process for supplying Test Wafers into the fab was complicated, lacked standardization, required significant human intervention, and led to tool performance impacts despite high operating costs. To address these issues, I designed, developed, and implemented a

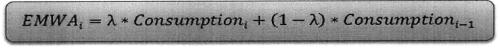

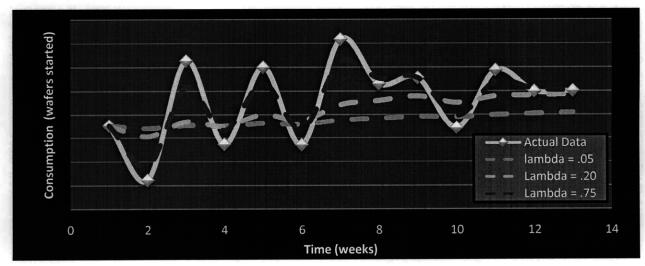

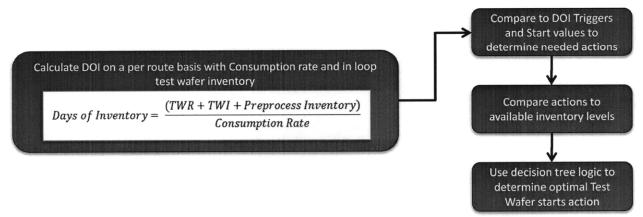

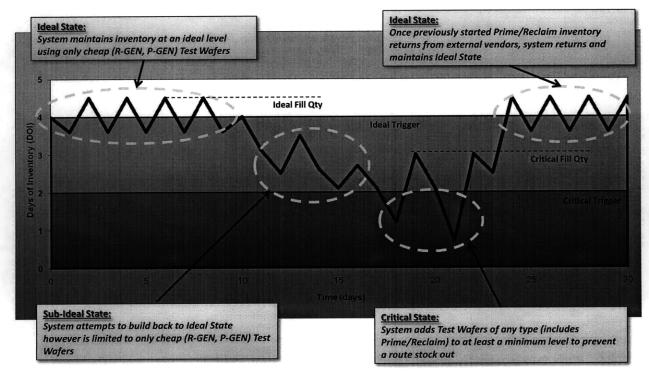

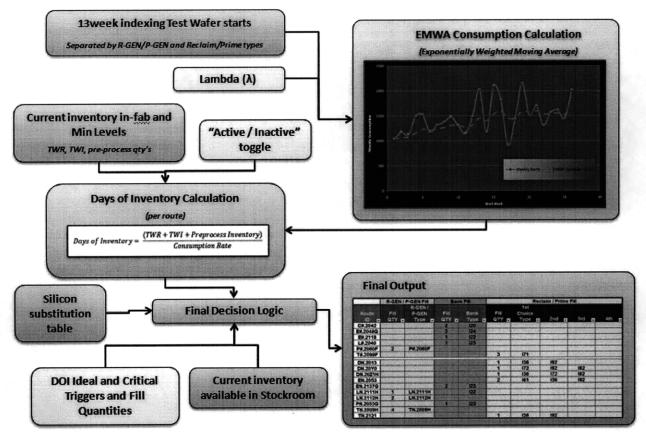

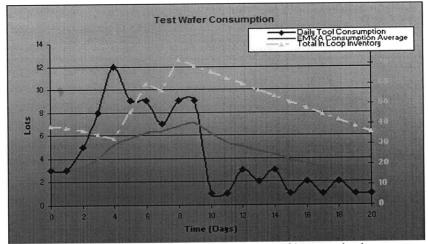

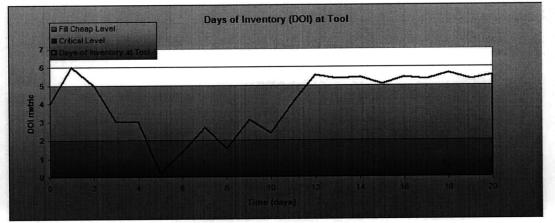

program which prioritized and calculated thousands of test wafer decisions based upon a Days of Inventory (DOI) metric. By prioritizing actions based on the time until stock out, cost-effective decisions were made while ensuring Test Wafers are available at a tool when needed. The program forecasted short term consumption using an Exponentially Weighted Moving Average (EMWA) and pulled real-time inventory and available Test Wafer material to support the calculations and decision logic.

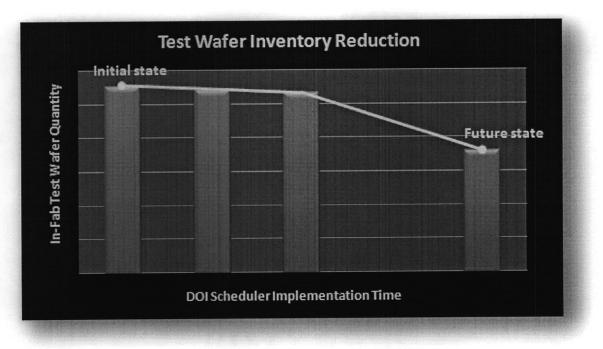

After a successful fab-wide pilot, the "DOI Scheduler" program has now replaced the previous test wafer supply process. As a result, internal fab test wafer inventory will decrease by approximately 35% (as of March 2009, inventory has dropped by 15% and continues downward), Test Wafer availability will improve by approximately75%, and 4 to 5hrs a week of labor resources have been saved. Equally important, the prior non-standard process is now standardized, enabling future Test Wafer improvement projects and allowing root cause analysis on previously unsolvable problems.

This page has been intentionally left blank.

----

# TABLE OF CONTENTS

| Ab   | stract       |                                                      |          |

|------|--------------|------------------------------------------------------|----------|

| Tał  | ole of Cont  | ents                                                 | 6        |

| List | t of Figures | 5                                                    | 8        |

| List | t of Tables  |                                                      |          |

| Dis  | claimer      |                                                      | 11       |

| Acl  | knowledgm    | ients                                                |          |

| Ab   | out the Ău   | thor                                                 |          |

|      |              |                                                      |          |

| 1    | Introducti   | on and Overview                                      |          |

| I    |              | ne Problem: General                                  |          |

|      |              | he Problem: Overview of Fab-17 Specific              |          |

|      | 1.2.1        | Problem 1: Inventory location                        |          |

|      |              | Problem 2: Starting Test Wafers                      |          |

|      |              | ypotheses                                            |          |

|      | 1.3 11       | -                                                    | 18       |

|      | 1.3.1        | ,                                                    |          |

|      |              | esearch Methodology                                  |          |

| 2    |              | nd and Current State                                 |          |

| Ζ    |              | hat is a Test Wafer?                                 |          |

|      |              | peration and Route Descriptions                      |          |

|      | 2.2 O        | est Wafers and Fab-17                                | 23       |

|      |              | Primary Stockroom                                    |          |

|      | 2.3.1        | Fab Starts Group (FSG)                               | 2+<br>25 |

|      | 2.3.2        | Test Wafer routes                                    |          |

|      | 2.3.3        | Prime and Reclaim Silicon Vendors                    |          |

|      | 2.3.4        | R-GEN and P-GEN Silicon Vendors                      |          |

|      | 2.3.5        |                                                      |          |

|      | 2.3.6        | Scrap                                                |          |

|      | 2.4 Fa       | b-17 Organization<br>"Broken" State                  | 29       |

|      |              | Managing Test Wafer Inventory                        |          |

|      |              | Starting Test Wafers into the Fab                    |          |

|      | 2.5.2        | Starting Test Waters into the Fab                    |          |

|      |              | irect Observation and Establishing the Current State |          |

|      | 2.6.1        | Measurement of Human Behaviors                       |          |

|      | 2.6.2        | Measurement of Test Wafer Consumption                |          |

|      | 2.6.3        | Measurement of Test Wafer Costs and Performance      |          |

| 3    | Literature   | Review                                               |          |

|      | 3.1 Jo       | urnals and Industry Papers                           |          |

|      |              | blic Intel Specific Documentations                   |          |

|      | 3.3 A        | cademic and Other Publications                       | 40       |

n en anderskaren er anderskille Billetin -

|    | 3.4      | LFM Theses                                                             | 40 |

|----|----------|------------------------------------------------------------------------|----|

| 4  | Researc  | h Analysis: Project 1 – Reallocating excess inventory                  | 41 |

|    | 4.1      | Overview: Excess and Inadequate Inventory Levels                       | 41 |

|    | 4.2      | Optimization Model Background Data                                     | 41 |

|    | 4.3      | Optimization Model Algorithm                                           | 42 |

|    |          | Organizational Issues                                                  |    |

| 5  | Researc  | h Analysis: Project 2 – Determining supply decisions from a DOI metric | 45 |

|    |          | Overview: Using a DOI metric for pulling Test Wafer starts             |    |

|    |          | DOI Scheduler Program Inputs                                           |    |

|    | 5.3      | DOI Scheduler Model Discussion                                         |    |

|    | 5.3.     |                                                                        |    |

|    | 5.3.     | 0                                                                      |    |

|    | 5.3.     | 0                                                                      |    |

|    | 5.3.     |                                                                        |    |

|    | 5.4      | Implementation Issues                                                  |    |

|    | 5.4.     |                                                                        |    |

|    | 5.4.     | 0                                                                      |    |

| 6  |          | s and Discussion                                                       |    |

|    |          | Description of findings: Project 1                                     |    |

|    |          | Description of findings: Project 2                                     |    |

|    | 6.2.     |                                                                        |    |

|    | 6.2.     |                                                                        |    |

|    |          | General Implications for Other Industries                              |    |

|    | 6.4      | Future Work                                                            | 70 |

| Re | ferences |                                                                        | 72 |

|    |          |                                                                        |    |

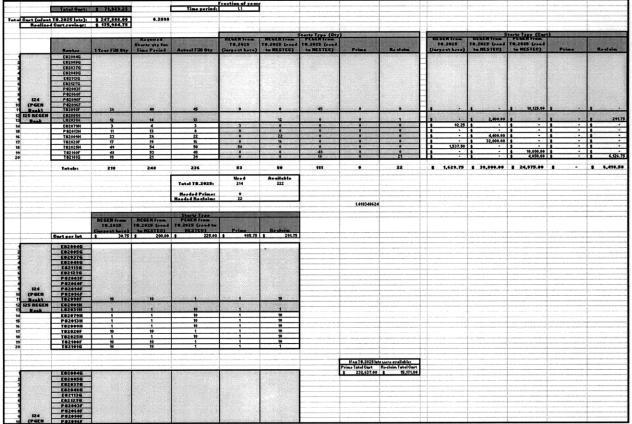

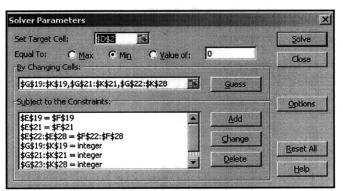

| Ap | pendix I | A: Reallocation Optimization Model Interface                           | 74 |

| Ap | pendix I | 3: Common Excel Formulas Used in DOI Scheduler                         | 75 |

|    |          | 2: DOI Scheduler – Fill Quantity Logic                                 |    |

|    |          | D: DOI Scheduler – Available Inventory Logic                           |    |

|    |          | E: DOI Scheduler – Final Action Logic                                  |    |

|    |          | 5: DOI Scheduler – Starts Display Logic                                |    |

|    |          | G: DOI Scheduler – Output Display Tabs                                 |    |

|    |          | H: DOI Scheduler Education Series                                      |    |

|    |          | : DOI Scheduler Game                                                   |    |

| Ap | pendix J | : Detailed Literature Review                                           |    |

-----

# LIST OF FIGURES

| Figure 1: Histogram of DOI per route corresponding to the Min Level triggers                        | ; |

|-----------------------------------------------------------------------------------------------------|---|

| Figure 2: Test Wafer type and cost summary                                                          |   |

| Figure 3: General route block diagram                                                               |   |

| Figure 4: Test Wafer material flow block diagram24                                                  |   |

| Figure 5: Fixed to route and bank inventory systems                                                 |   |

| Figure 6: Test Wafer lifecycle                                                                      | ) |

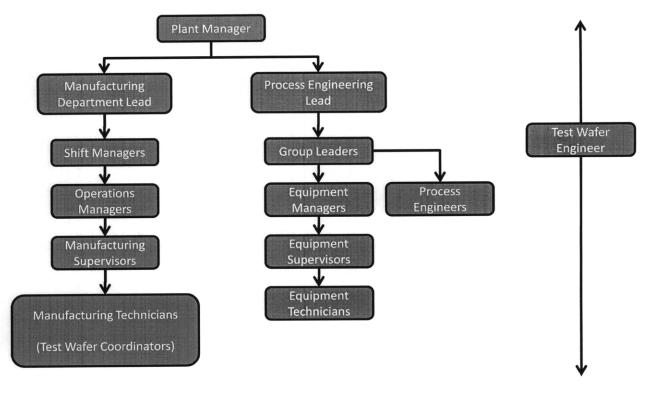

| Figure 7: Fab-17 organization structure                                                             | ) |

| Figure 8: Example route Test Wafer consumption EWMA                                                 | ) |

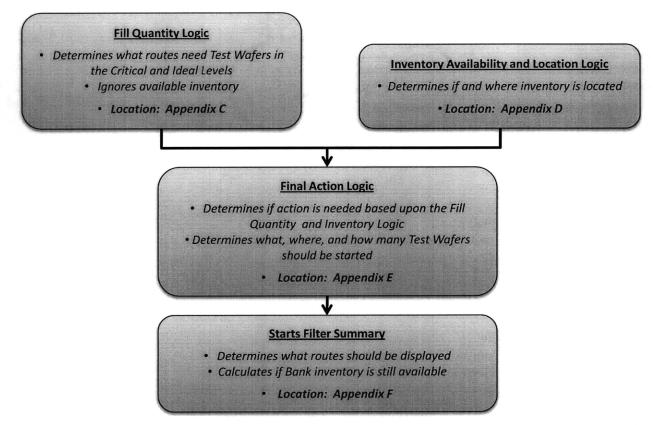

| Figure 9: DOI Scheduler program block diagram overview45                                            | > |

| Figure 10: Example route DOI trigger methodology description48                                      |   |

| Figure 11: DOI Scheduler program algorithm51                                                        |   |

| Figure 12: DOI Scheduler program logic categories                                                   | 2 |

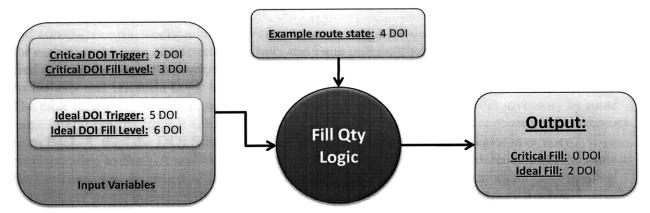

| Figure 13: Fill Quantity Logic example 1: Current route DOI is less than Ideal DOI Trigger53        | 5 |

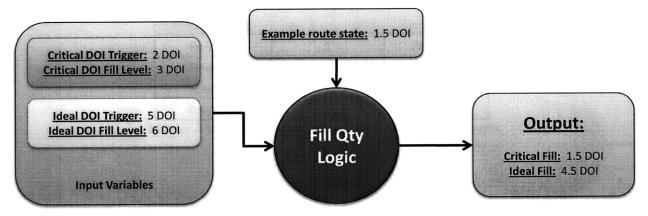

| Figure 14: Fill Quantity Logic example 2: Current route DOI is less than Ideal and Critical DOI     |   |

| Trigger                                                                                             |   |

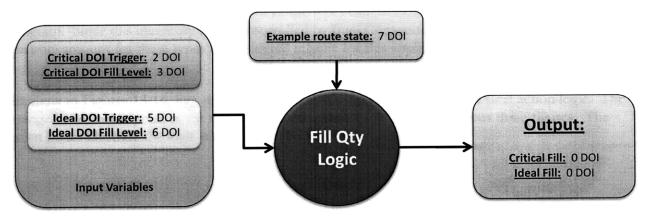

| Figure 15: Fill Quantity Logic example 3: Current route DOI greater than Ideal DOI Trigger53        | 5 |

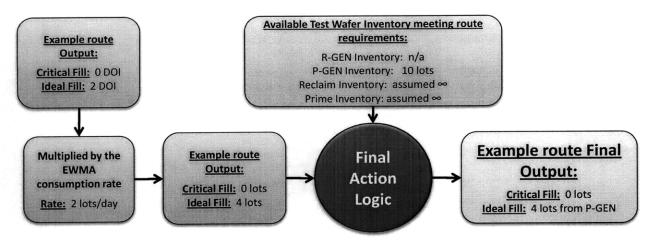

| Figure 16: Final Action Logic example 1: Ideal Fill with available cheap Test Wafer inventory55     | > |

| Figure 17: Final Action Logic example 2: Ideal Fill with a partial available cheap Test Wafer       |   |

| inventory55                                                                                         | 5 |

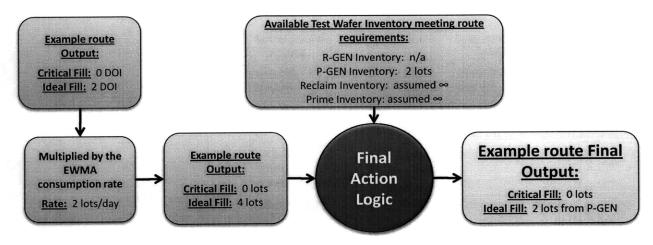

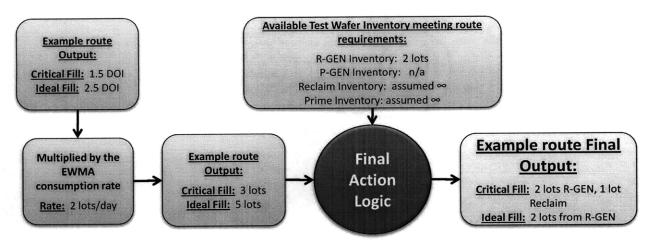

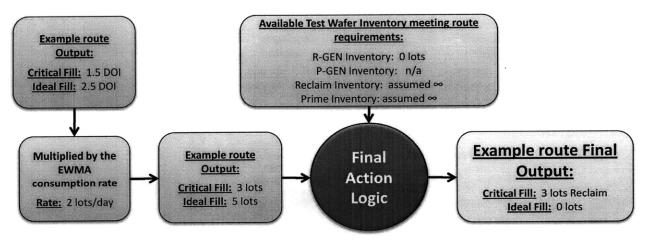

| Figure 18: Final Action Logic example 3: Critical and Ideal Fill with partial available cheap Test  |   |

| Wafer inventory                                                                                     | Ś |

| Figure 19: Final Action Logic example 4: Critical and Ideal Fill with no cheap Test Wafer inventory |   |

| available                                                                                           | 5 |

| Figure 20: Example DOI Scheduler final output screen                                                | 1 |

| Figure 21: Project 1 results summary: Reallocated Test Wafer inventory quantity and location62      |   |

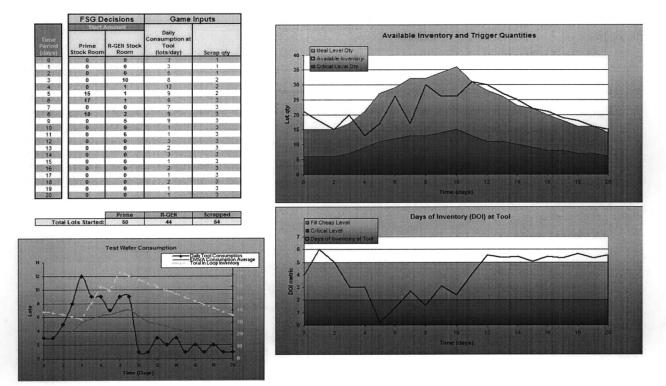

| Figure 22: DOI Scheduler program simulation overview                                                | ŀ |

| Figure 23: Input parameters for simulation example scenario65                                       | ; |

| Figure 24: Simulation example consumption and inventory levels                                      |   |

| Figure 25: Simulation example inventory DOI graph                                                   |   |

| Figure 26: Simulation example lot quantity graph                                                    |   |

| Figure 27: Histogram showing Test Wafer DOI inventory levels per route                              | 3 |

| Figure 28: In-fab Test Wafer inventory reduction                                                    |   |

| Figure 29: Example screenshot of the Reallocation Optimization interface74                          | ł |

| Figure 30: Solver Parameter screenshot                                                              | ł |

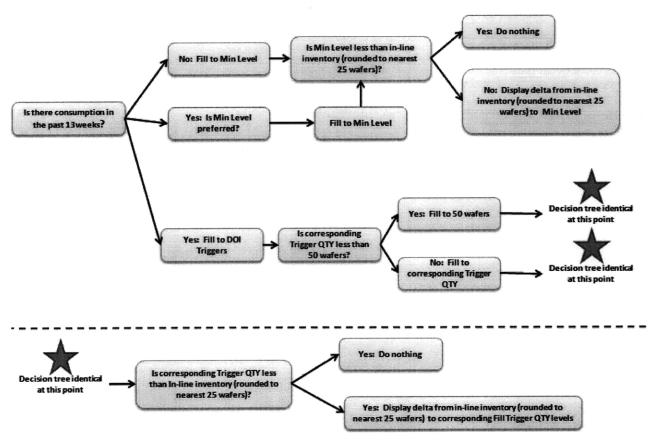

| Figure 31: DOI Scheduler - fill quantity decision tree70                                            |   |

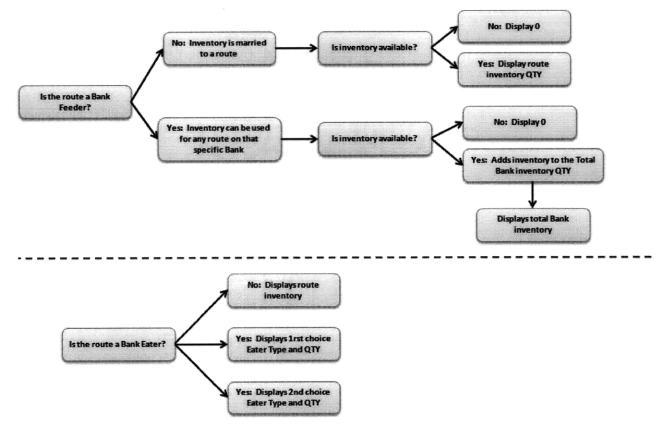

| Figure 32: DOI Scheduler - available stockroom inventory decision tree77                            | 7 |

| Figure 33: DOI Scheduler - final Test Wafer action decision tree                                    | 3 |

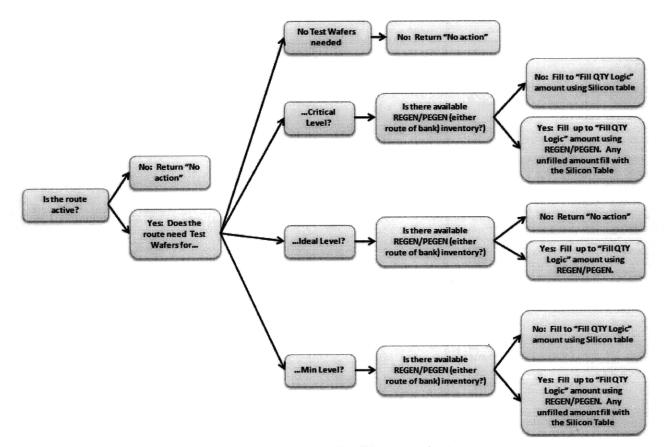

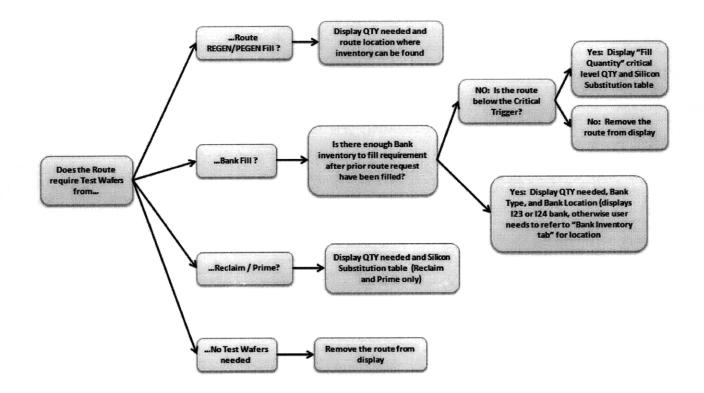

| Figure 34: DOI Scheduler - final output display decision tree                                       | ) |

| Figure 35: DOI Scheduler final output: Bank inventory summary example80                             | ) |

| Figure 36: DOI Scheduler final output: DOI calculations and logic summary example80                 |   |

| Figure 37: DOI Scheduler final output: configuration control example                                | l |

| Figure 38: DOI Scheduler Class - Introduction slide                                                 | 2 |

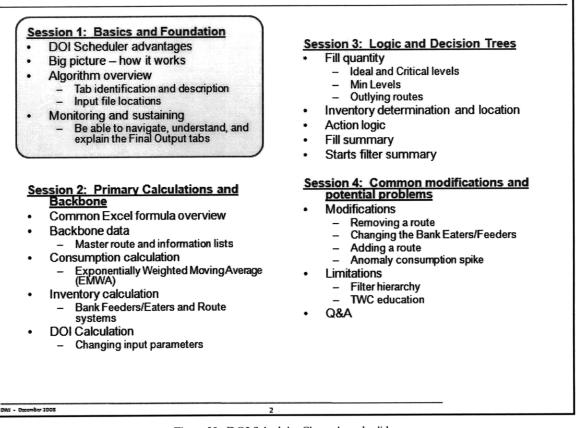

| Figure 39: DOI Scheduler Class: Agenda slide                                                        | 3 |

| Figure 40: DOI board game                                                                           |   |

- - ----

| Figure 41: DOI Excel simulation supporting | g the DOI board game85 |

|--------------------------------------------|------------------------|

|--------------------------------------------|------------------------|

# LIST OF TABLES

| Table 2: Test Wafer types21Table 3: Example route sequence of operations23Table 4: Advantages/Disadvantages for inventory held married to a particular route24Table 5: Advantages/Disadvantages for inventory held in a bank system25Table 6: Example silicon substitution table.26Table 7: R-GEN and P-GEN sorting types28Table 8: Organization jobs and description31Table 9: Min level starts process problem summary33Table 10: Human element observation summary35Table 11: Measurement of Test Wafer performance summary table38Table 12: Project 1 background data and measurements42Table 13: DOI Scheduler input data47Table 15: Available Inventory and Logic bank and route inventory location example54Table 16: DOI Scheduler program summary results table63Table 17: Fab-17 future work summary71Table 18: Commonly used Excel formulas75 | Table 1: ' | Test Wafer base characteristics                                           | 21 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------------|----|

| Table 4: Advantages/Disadvantages for inventory held married to a particular route24Table 5: Advantages/Disadvantages for inventory held in a bank system25Table 6: Example silicon substitution table.26Table 7: R-GEN and P-GEN sorting types28Table 8: Organization jobs and description31Table 9: Min level starts process problem summary33Table 10: Human element observation summary35Table 11: Measurement of Test Wafer performance summary table38Table 12: Project 1 background data and measurements42Table 13: DOI Scheduler input data47Table 14: DOI Scheduler input variables47Table 15: Available Inventory and Logic bank and route inventory location example54Table 16: DOI Scheduler program summary results table63Table 17: Fab-17 future work summary71                                                                          | Table 2: ' | Test Wafer types                                                          | 21 |

| Table 5: Advantages/Disadvantages for inventory held in a bank system25Table 6: Example silicon substitution table.26Table 7: R-GEN and P-GEN sorting types28Table 8: Organization jobs and description31Table 9: Min level starts process problem summary33Table 10: Human element observation summary35Table 11: Measurement of Test Wafer performance summary table38Table 12: Project 1 background data and measurements42Table 13: DOI Scheduler input data47Table 14: DOI Scheduler input variables47Table 15: Available Inventory and Logic bank and route inventory location example54Table 16: DOI Scheduler program summary results table63Table 17: Fab-17 future work summary71                                                                                                                                                              | Table 3: 1 | Example route sequence of operations                                      | 23 |

| Table 6: Example silicon substitution table26Table 7: R-GEN and P-GEN sorting types.28Table 8: Organization jobs and description.31Table 9: Min level starts process problem summary.33Table 10: Human element observation summary.35Table 11: Measurement of Test Wafer performance summary table.38Table 12: Project 1 background data and measurements.42Table 13: DOI Scheduler input data.47Table 14: DOI Scheduler input variables.47Table 15: Available Inventory and Logic bank and route inventory location example.54Table 16: DOI Scheduler program summary results table.63Table 17: Fab-17 future work summary.71                                                                                                                                                                                                                           | Table 4:   | Advantages/Disadvantages for inventory held married to a particular route | 24 |

| Table 7: R-GEN and P-GEN sorting types28Table 8: Organization jobs and description31Table 9: Min level starts process problem summary33Table 10: Human element observation summary35Table 11: Measurement of Test Wafer performance summary table38Table 12: Project 1 background data and measurements42Table 13: DOI Scheduler input data47Table 14: DOI Scheduler input variables47Table 15: Available Inventory and Logic bank and route inventory location example54Table 16: DOI Scheduler program summary results table63Table 17: Fab-17 future work summary71                                                                                                                                                                                                                                                                                   | Table 5: 1 | Advantages/Disadvantages for inventory held in a bank system              | 25 |

| Table 8: Organization jobs and description31Table 9: Min level starts process problem summary33Table 10: Human element observation summary35Table 11: Measurement of Test Wafer performance summary table38Table 12: Project 1 background data and measurements42Table 13: DOI Scheduler input data47Table 14: DOI Scheduler input variables47Table 15: Available Inventory and Logic bank and route inventory location example54Table 16: DOI Scheduler program summary results table63Table 17: Fab-17 future work summary71                                                                                                                                                                                                                                                                                                                           | Table 6: 1 | Example silicon substitution table                                        | 26 |

| Table 9: Min level starts process problem summary33Table 10: Human element observation summary35Table 11: Measurement of Test Wafer performance summary table38Table 12: Project 1 background data and measurements42Table 13: DOI Scheduler input data47Table 14: DOI Scheduler input variables47Table 15: Available Inventory and Logic bank and route inventory location example54Table 16: DOI Scheduler program summary results table63Table 17: Fab-17 future work summary71                                                                                                                                                                                                                                                                                                                                                                       |            |                                                                           |    |

| Table 10: Human element observation summary35Table 11: Measurement of Test Wafer performance summary table38Table 12: Project 1 background data and measurements42Table 13: DOI Scheduler input data47Table 14: DOI Scheduler input variables47Table 15: Available Inventory and Logic bank and route inventory location example54Table 16: DOI Scheduler program summary results table63Table 17: Fab-17 future work summary71                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 8: 0 | Organization jobs and description                                         | 31 |

| Table 11: Measurement of Test Wafer performance summary table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 9: 1 | Min level starts process problem summary                                  |    |

| Table 12: Project 1 background data and measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Table 10:  | Human element observation summary                                         | 35 |

| Table 13: DOI Scheduler input data47Table 14: DOI Scheduler input variables47Table 15: Available Inventory and Logic bank and route inventory location example54Table 16: DOI Scheduler program summary results table63Table 17: Fab-17 future work summary71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |            |                                                                           |    |

| Table 13: DOI Scheduler input data47Table 14: DOI Scheduler input variables47Table 15: Available Inventory and Logic bank and route inventory location example54Table 16: DOI Scheduler program summary results table63Table 17: Fab-17 future work summary71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 12:  | Project 1 background data and measurements                                | 42 |

| Table 15: Available Inventory and Logic bank and route inventory location example                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |            |                                                                           |    |

| Table 16: DOI Scheduler program summary results table63Table 17: Fab-17 future work summary71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Table 14:  | DOI Scheduler input variables                                             | 47 |

| Table 17: Fab-17 future work summary    71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |            |                                                                           |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 16:  | DOI Scheduler program summary results table                               | 63 |

| Table 18: Commonly used Excel formulas    75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Table 17:  | Fab-17 future work summary                                                | 71 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 18:  | Commonly used Excel formulas                                              | 75 |

# DISCLAIMER

This document has been reviewed and approved by the Intel Corporation. In order to protect Intel, sensitive material has been omitted or replaced with representative data. Aspects such as cost savings and production details are not included for this reason. Ratios and other non-specific metrics are used to quantify results for the reader while not violating Intel's confidentiality.

### Acknowledgments

### "Somewhere, something incredible is waiting to be known..." Dr. Carl Sagan

The successes presented in this thesis were made possible by the Massachusetts Institute of Technology, specifically the Leaders For Manufacturing (LFM) program. I would like to thank Don Rosenfield, LFM Program Director, for accepting me into this program on two separate occasions thus enabling this opportunity. I would also like to extend my appreciation to fellow classmates Drew Corum, Maria Mentzer, and Dan Schoerner as our shared experiences and hardships have taught me more than any class.

Special thanks go to the Intel Corporation and Fab-17 for their support and creation of such a momentous project. Specifically, Kevin O'Malley and Richard Kearns provided fantastic mentorship and trust in my abilities and hypotheses. Additionally, the members of the FPS Cost Team, Leo Ramirez, Patti Slaughter, Sherry Letendre, and many others played integral roles in the development and implementation of the projects presented here. Without their help, these accomplishments would never have been achieved.

My thesis advisors Professor Stephen Graves and Professor Deborah Nightingale provided the perfect amount of oversight and recommendations throughout this experience. I am grateful for all their assistance and auspices.

Additionally, I want to thank my family. They have always encouraged me to follow my dreams and to shoot for the stars. I can only laugh when I think of my grandmother's wise words when I began the thesis writing process. "Don't be foolish; keep it short and concise, nobody cares that much anyway."<sup>1</sup>

Lastly, and most importantly, I sincerely thank my wonderful fiancée, Alison, who has endured two challenging years of student loans, homework-caused unavailability, and piles of unorganized case studies and textbooks. She has continued to support me even when all rational thought says otherwise, to which I am forever indebted. I solemnly promise to refrain for anymore educational exploits which prevent a sustainable monetary income. I love you.

<sup>&</sup>lt;sup>1</sup> The irony of thesis length and contradiction to Clella's advice was quickly noted as the thesis continued to grow with seemingly no end in sight.

# About the Author

Often considered idealistic and in constant pursuit of "half full glasses," David Johnson left a rewarding career designing mechanical space systems at the Jet Propulsion Laboratory, NASA to follow his passion of helping people on a larger scale. Consistent with his logical and problem solving strengths, the Leaders for Manufacturing program offered an unmatched opportunity to hone business and technical acumen on the backbone of strong leadership skills. Post graduation, David looks forward to channeling his energy towards efforts in sustainability and environmental conservation.

David is an avid outdoorsman and can frequently be found either participating in or conjuring the next great adventure with his friends. Nothing brings him greater tranquility than a strong cup of coffee served thick and black shared with his fiancée, dog, and a gorgeous sunrise over snow-capped mountains or ocean waves breaking under a slight offshore breeze.

# GLOSSARY

**<u>A3 Document:</u>** A single page (A3 sized piece of paper or 85."×11" as more typical in USA standards) document which describes the current state, problem statement, hypothesis, and anticipated results. These are used to clearly visualize problem statements and results.

**Bank:** A group of Test Wafer inventory from multiple routes batched together by identical base characteristics.

**Bank Eaters:** Routes who require Test Wafers with the same base characteristics as grouped in a Test Wafer Bank. These routes will pull Test Wafers from this bank as need and availability determine.

**Bank Feeders:** Routes who's cleaned Test Wafers from R-GEN or P-GEN vendors are grouped together by their identical characteristics in the stock room, in a Test Wafer Bank.

**Days of Inventory (DOI):** A metric measuring inventory in terms of time until stock out. It is defined as the inventory quantity divided by the consumption rate in units per day.

**Fab-17:** The name of Intel Corporation's Hudson, MA manufacturing facility where this thesis project was completed. Each manufacturing facility has a particular name and operate as separate facilities although the processes used are interchangeable for each product line. This commonality is referred to the "virtual factory" concept.

**Fab Starts Group (FSG):** The group responsible for determining what, where, and when Test Wafers should be released into the fab. Additionally, FSG is responsible for moving Test Wafer lots from outside of the clean room to the first operation.<sup>2</sup>

Kaizan: A lean manufacturing term used to identify a focused improvement event on a particular problem or issue.

**Learning Card:** A single page document used to visually display an improvement hypothesis and test conditions. These are posted in the area of improvement and contain areas for feedback and comments. Once approval from all relevant stakeholders has been obtained and the hypothesis is validated, the improvement is incorporated into the standard work process.

**Lot:** A group of 25 wafers held together by a lot box. All operations and processes are standardized around these lot boxes in a 200mm wafer diameter facility.

**Operation:** A specific activity, movement, or process used to change Test Wafer properties or transfer to the next operations.

**PROC:** The acronym used for "processing." This term is used when wafer lots are moved from one operation to another.

**Route:** A specific sequence of operations linking all movements, pre-process activities, verification/validation steps, and removal course.

<sup>&</sup>lt;sup>2</sup> Only Test Wafer specific activities are mentioned. For simplicity, production wafer activities are ignored for this thesis.

**SWARM:** An Intel lean manufacturing term used to identify a group of individuals proactively searching for improvement opportunities often in a particular area or discipline.

**Test Wafer:** a non-production silicon wafer used for validation and verification purposes of various tools and processes. Multiple types of Test Wafers exist with different base characteristics as required by the tool and validation or verification process. The following four types of Test Wafer exist.

<u>Test Wafer – R-GEN</u>: A used Test Wafer sent to a vendor to be cleaned or recycled using chemical etching techniques to remove any surface materials and expose the bare silicon.

<u>Test Wafer – P-GEN</u>: A REGEN Test Wafer with an added polish step after the chemical etching to ensure a flat surface finish.

<u>Test Wafer - Reclaim</u>: A used Test Wafer sent to a vendor for more extreme cleaning or recycling operations. First, a chemical etch removed any surface material. Next, a series of grinding, lapping, and polishing operations commences leaving the bare silicon surface at the expense of greater material loss.

Test Wafer - Prime: A new silicon wafer designated to be used for Test Wafer purposes

**Wafer Cost:** The cost to manufacture a single wafer populated with chips. Each wafer is divided into numerous chips. As wafer diameter increases, the number of chips per wafer increases by a square factor drastically decreasing the Chip Cost for a single wafer. For this reason, an increase in wafer diameter is preferred in terms of an economy of scale argument.

**<u>Recipe</u>**: A specific set of cleaning operations (mostly chemical etch operations) used by R-GEN and P-GEN vendors to return a used Test Wafer back to its bare state.

# 1 Introduction and Overview

The Intel Corporation is renowned for not only the design of sophisticated semi-conductor chipsets but also the efficient and cost effective manufacturing of such. In order to ensure high quality production, an extensive system of verifications, preventative maintenance, and validations are constantly conducted throughout the manufacturing line. To minimize the risk on high value production wafers, these test operations are run and monitored through the use of Test Wafers, wafers which are designated for non-production purposes.

Fab-17 in Hudson, Massachusetts is a 200mm diameter wafer facility manufacturing Intel products for over ten years. Historically, this facility has started more Test Wafers than production wafers manufactured for a given time period; this being consistent with industry standards. Due to the large usage volume and inherent cost per wafer, Test Wafers have always been a major contributor to the overall cost per production wafer.

This thesis provides a detailed description of two system level Test Wafer improvement hypotheses and their results at Fab-17. Chapter 1 outlines the problem and hypotheses. Chapter 2 contains the background and description of Test Wafers and the existing management systems. Chapter 3 provides a literature review addressing similar issues from industry and academia. Chapters 4 and 5 present the research analysis and approach for each improvement project. Lastly, Chapters 6 concludes with the results and thesis findings. This format was chosen to best inform the reader of the thesis projects in an efficient and effective fashion while providing great detail for those more interested and/or committed.

### 1.1 The Problem: General

The challenges and rewards associated with inventory management and supply from a general perspective are no different than that of Test Wafers. Cost savings obtained from optimal inventory quantities, minimizing holding costs, ensuring material availability, etc. can be extremely significant on the functioning of an organization and/or product delivery. Understanding how inventory and material supply systems behave will allow for the development of supporting systems ensuring low cost while improving and maintaining system performance. Whether with Test Wafers at Fab-17 or any other inventory material, these same root problems exist.

### 1.2 The Problem: Overview of Fab-17 Specific

Through a month of direct observations, numerous problems associated with system level Test Wafer inventory management continued to occur. Largely, a lack of standardization in Test Wafer processes led to wasteful operations, quality and process stability issues, enormous amounts of "human glue" and manual intervention, and the inability to easily and properly complete root cause analysis on many problems. Given the available time and resources for this research, two main problems were identified and attacked. The following two sections elaborate on the details with these problems.

It is important to note the significance of cost reduction and process improvement initiatives at Fab-17. With newer Intel sites transitioning to the larger, more cost effective 300mm and 450mm wafer architecture, Fab-17 must continue to drive wafer cost lower to maintain a competitive edge within the Intel network. Ultimately, the wafer cost metric is a deciding factor on the longevity of the plant. Fear of closing Fab-17 motivates many employees to embrace lean methodology and continuous improvement projects that reduce cost and cycle time, and improve quality and yield. Lastly, the problem statements and hypotheses in this section are discussed prior to a sufficient background description of Test Wafers and their systems and processes at Fab-17. Any confusion regarding these aspects will be clarified in detail in Chapter 2.

# 1.2.1 Problem 1: Inventory location

A single stockroom located external to the manufacturing clean room manages all Test Wafer inventory. An external vendor provides the workforce to run the shipping/receiving and storage service; all inventory is owned by Intel once it arrives.

For most routes R-GEN and P-GEN Test Wafers are preferred as their cost is significantly less than a Prime or Reclaimed Test Wafer. Through observation, some routes contained seemingly large quantities of cheaper, recycled Test Wafer inventory (R-GEN and P-GEN Test Wafers, whereas other routes had little or small amounts of inventory. It became apparent that the preferred Test Wafer inventory of similar base characteristics was not optimally distributed across the different routes.

In order to better understand the discrepancy between route Test Wafer quantities, the consumption and scrap rates for each route were multiplied with the inventory levels to obtain the time duration until Test Wafer inventory would be depleted for each route.

For a one route, over 30 years of inventory had accumulated, while many other routes were either dry or days away from a stock out scenario. The cost impacts for the routes with inadequate inventory levels were significant; without the cheaper Test Wafers, Intel would need to start Prime or Reclaimed Test Wafers at a cost of approximately an order of magnitude greater. With hundreds of Test Wafer lots being affected, the cost impact was enormous.

Additionally, due to cleanliness issues, Test Wafer lots have a shelf life of roughly one year. Over this time particulates and/or surface oxidation occurs requiring the recycling and cleaning process to be repeated. Preferably, Test Wafer inventory would be used prior to this deadline as to avoid unnecessary re-cleaning costs.

# 1.2.2 Problem 2: Starting Test Wafers

Fab-17 maintains an inventory of Test Wafers within the fab for each route. The process for determining which Test Wafer types, what quantity, to which routes, and at what time was decided from a non-standard, highly labor intensive process located at the entrance of the fab. A program monitored the available quantity of Test Wafers in the fab for each route and flagged a notification when the actual quantity dropped below a fixed minimum level. Due to an environment highly sensitive to costs, the technicians responsible for communicating the Test Wafer order starting location to the stockroom would often not follow the program's recommendations unless a cheap Test Wafer availabile in the stockroom. This behavior drove non-standard operations. To ensure Test Wafer availability, other technicians on the floor would need to communicate their needs adding unnecessary work. This "human glue" also led to frequent Test Wafer stock outs on the various routes.

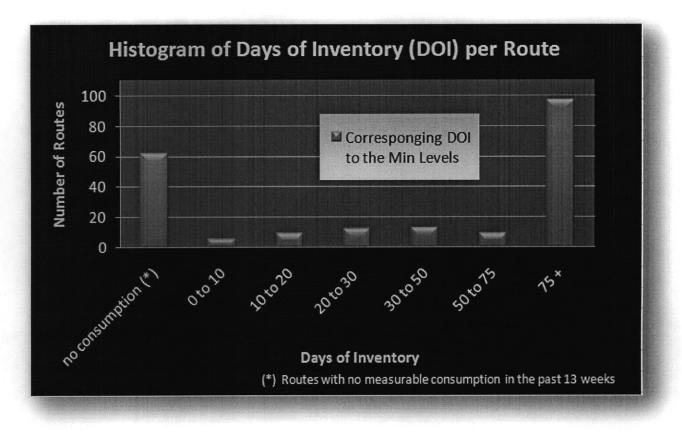

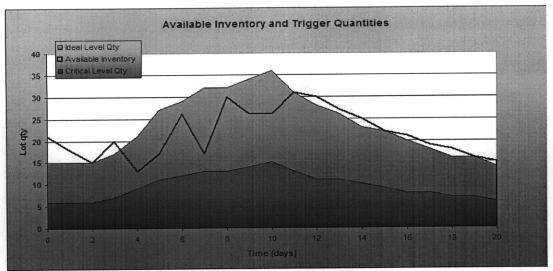

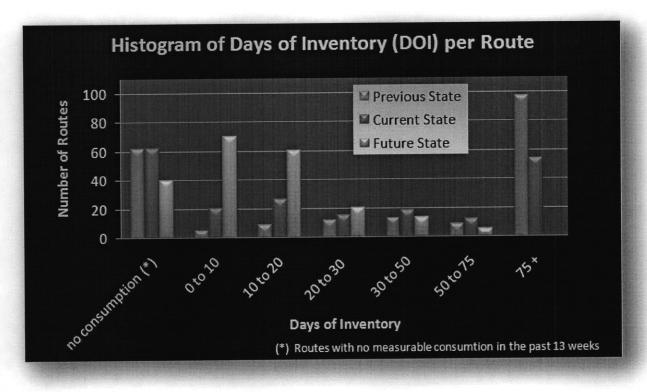

Additionally, the minimum trigger levels were established many years ago and in most cases were no longer appropriate. Using a calculated consumption rate for each route, roughly half of the minimum levels corresponded to over 75 days of inventory. This excess impacted holding and opportunity costs, and increased the number of shelf-life violations, which resulted in rejecting Test Wafers. The histogram in Figure 1 illustrates the corresponding days of inventory to the total number of routes.

Figure 1: Histogram of DOI per route corresponding to the Min Level triggers

The non-standard process also led to an inability to complete root cause analysis on stock out causes or other Test Wafer starts decisions. On many occasions, a route would have a Test Wafer availability issue and the cause would be impossible to deduce often leading to repeat issues without correction.

In summary, the lack of standardization, required human intervention, non-optimal trigger levels all led to an extremely complicated system which performed only with technician heroics and high costs. Very few individuals understood all aspects leaving the Test Wafer starts process at a precarious position if any one of those individuals was sick or moved to different responsibilities.

### 1.3 Hypotheses

Two hypotheses were developed to attack each problem described above. By utilizing lean principles in the problem assessment and improvement approach, significant savings in inventory management and costs were anticipated while improving Test Wafer availability and fab performance.

### 1.3.1 Project 1 - Reallocating excess inventory

If excess Test Wafer inventory is optimally reallocated to starved routes/banks adhering to its base characteristics and requirements, then a total savings equivalent to a year's worth of inventory for

those affected routes/banks will be observed. Enormous cost savings will be obtained from the monetary difference between starting the cheaper R-GEN or P-GEN Test Wafers instead of the expensive Prime or Reclaim wafers.<sup>3</sup>

# 1.3.2 Project 2 – Determining supply decisions from a DOI metric

If Test Wafer type, quantity, and location are optimally started based upon the prioritization of routes under a Days of Inventory (DOI) metric, then a robust standard process can be established simplifying work and eliminating human connections while decreasing in-fab Test Wafer inventory levels and improving Test Wafer availability. The DOI metric incorporates the consumption rate of Test Wafers into the metric. This rate would otherwise be communicated through non-value add connections. This approach is the foundation for process standardization allowing for root cause analysis and the foundation for future Test Wafer improvement projects.

## 1.4 Research Methodology

The research and implementation of the thesis projects occurred through the utilization of lean principles. Initially process and value stream mapping techniques, direct observation, and DMAIC (Design, Measure, Analysis, Improve, Control) strategies were used to establish and understand the current state. One of the largest challenges for this project was determining how to measure Test Wafer performance. Interacting with on-floor technicians and systems experts in all disciplines helped with ascertaining what information was available or easily obtained. Kaizan and SWARM events helped quickly identify key issues and built relationships with principal stakeholders helping ensure future implementation successes. A multi-disciplinary team focused on cost savings was also established which provided a great forum to educate and receive feedback throughout all departments. The details from this initial investigation will be discussed in detail in Chapter 2.

A comprehensive literature review augmented the hands-on research portion. Industry publications, prior LFM theses, and educational textbooks were used to understand inventory management related to Test Wafers. These findings will be summarized in Chapter 3.

Once the project analysis was completed, pilot programs were launched through the use of Learning Cards and A3 Documents. These tools help document and test the hypotheses. Under the approach of "small and rapid improvements," quick modifications were made ultimately leading to successful improvements.<sup>4</sup> The approach for each project will be explained in Chapters 4 and 5 with the results described in Chapter 6.

<sup>&</sup>lt;sup>3</sup> The exact monetary savings cannot be published but a estimate based upon public knowledge is provided in Section 5.

<sup>&</sup>lt;sup>4</sup> Quotation taken from commonly used Lean terminology

# 2 Background and Current State

Understanding the immensely complex systems associated with Test Wafers has been the great challenge associated with this thesis.<sup>5</sup> As with any project, lasting and measurable improvements cannot occur without first understanding how the Test Wafer environment at Fab-17 operates. This section will attempt to provide a thorough background on the different types of Test Wafers, their usage and consumption, and the systems and processes used. Test Wafers have historically been treated as the "black sheep" of the fab; they are largely ignored and un-glorified until needed. At that point, they are a necessity despite being non-value add. For this reason, resources have not historically been allocated to improve and maintain effective Test Wafer operations. In studying this section the reader will invariably question many of the processes. From the perspective of this thesis, the reader should focus on understanding the state leading up to the specific hypothesis instead of developing new improvement hypotheses for the next LFM intern.

### 2.1 What is a Test Wafer?

Test Wafers are silicon wafers of the same properties as production wafers with the exception of being designated for verification and validation purposes only. Test Wafers are run in conjunction with maintenance activities, scheduled checks, out of specification operations, etc. Since the cost of scrapping a production wafer is large, due mainly to the number and length of the operations needed to get to the final product, Test Wafers are consumed at a large rate. For a semiconductor manufacturing facility with similar processes and age as Fab-17, the number of Test Wafers started is 1-3 times the number of production wafers started.<sup>6</sup> A few examples of different operations and routes where they are used are the following.

- Verifying the thickness of a deposition layer

- Checking the number of particles in a particular machine

- Running non-production dummy wafers to ensure steady state on an operation

For each route, there are restrictions on the Test Wafer characteristics. These characteristics are based on the process history, base material conditions, and the recycling approaches. The details of the types of routes will be discussed in section 2.2.

In addition, Test Wafers can be recycled and reused numerous times based upon the required Test Wafer characteristics for a specific route. In looking at the example of verifying the thickness of a deposition layer, the important characteristics may be the Test Wafer's thickness and flatness. Other concerns such as copper contamination are carefully controlled. The major input characteristics which distinguish each Test Wafer type are listed in Table 1.

<sup>&</sup>lt;sup>5</sup> Note that in many cases "... immensely complex systems..." could be referred to as "... unnecessarily complex systems..."

<sup>&</sup>lt;sup>6</sup> As determined from internet searches and discussions with numerous individuals familiar with semiconductor manufacturing. The reason for this phenomenon deals with the high cost of scrapping parts in semiconductor manufacturing, particularly near the end of the manufacturing cycle. More Test Wafers (or framed as more cost) is added before running production wafers to minimize part defects.

| Characteristic            | Description / Significance                                               |

|---------------------------|--------------------------------------------------------------------------|

| Resistance                | - Measured in Ohm-cm and deals with capacitance and adherence            |

|                           | measurements                                                             |

| Particles and cleanliness | - Measured by the size of particles per specific area. Often multiple    |

|                           | tiers are used to separate the number of allowable particles by size and |

|                           | distribution density                                                     |

| Flatness / Thickness      | - Physical characteristic parameters critical for many operations        |

| Copper Contamination      | - Important to note that once a Test Wafer has been exposed to any       |

|                           | type of Copper it is considered contaminated. A copper contamination     |

|                           | is extremely difficult to contain and clean. If a contaminated Test      |

|                           | Wafer exposes a tool, then the tool may contaminate every subsequent     |

|                           | wafer which is run. The copper contamination is then spread              |

|                           | throughout the fab. Extreme caution is taken to prevent this from        |

|                           | happening.                                                               |

| Doping type               | - Adding impurities into the silicon changes the behavior of the silicon |

| 1 0 71                    | by varying the number of valence electrons. Changing this                |

|                           | conductance varies the silicon's ability to act as a conductor or        |

|                           | insulator.                                                               |

Table 1: Test Wafer base characteristics

In addition to the base characteristics, Test Wafers are classified into four types as shown in Table 2.

| Туре                      | Description                                                                 |  |  |  |

|---------------------------|-----------------------------------------------------------------------------|--|--|--|

| R-GEN                     | A recycled or cleaned Test Wafer where chemical etching procedures are      |  |  |  |

|                           | used to remove any deposition layers until only the bare silicon remains.   |  |  |  |

| P-GEN                     | A R-GEN cleaning operation but with an additional polish step to ensure     |  |  |  |

|                           | surface flatness                                                            |  |  |  |

| Reclaim                   | Along with a chemical etch procedure, a grind, lap, and polish operation is |  |  |  |

|                           | added to ensure that any surface imperfections are removed. Since a         |  |  |  |

|                           | relatively large amount of material is removed, wafers can only be          |  |  |  |

|                           | Reclaimed three times before they are too thin for safe use. At that point  |  |  |  |

|                           | they are scrapped.                                                          |  |  |  |

| Prime                     | A virgin or new silicon wafer                                               |  |  |  |

| Table 2: Test Wafer types |                                                                             |  |  |  |

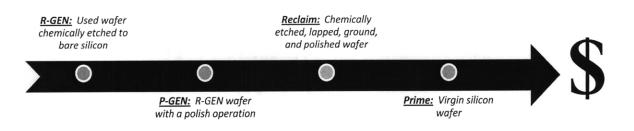

The four types outlined above are ranked in ascending cost. For the R-GEN, P-GEN, and Reclaim Test Wafers, the additional operations are the source of the cost increase. Prime Test Wafers are most expensive due to their virgin or unused status. Depending on the base silicon characteristics, a Prime Test Wafer may be an order of magnitude more expensive than the cheapest R-GEN Test Wafer. Different material structure differentiates Prime Test Wafers. Over time through the recycling and cleaning processes, their geometric characteristics change which affects route restriction compliance. This cost hierarchy is summarized in Figure 2.

Figure 2: Test Wafer type and cost summary

### 2.2 Operation and Route Descriptions

Along with understating the details of what a Test Wafer is, it is critical to have a good comprehension of usage nomenclature and processes. Fab-17 manufacturing occurs in a class 10 (ISO equivalent 4) clean room.<sup>7</sup> In the production line, each tool and associated activity is distinguished by a particular operation and operation number. In order to fabricate a production wafer, a large number of operations are run in sequence each adding or subtracting material until a finished product is complete. Test Wafers may run any number of these operations; however, many Test Wafer specific operations also exist since Test Wafers are used for verification, cleaning, and/or validation activities separate from the production sequence.

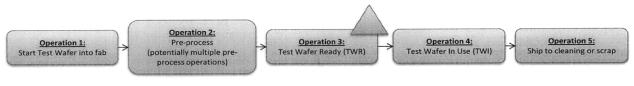

A route is defined as a particular sequence of operations beginning with the starting operation of releasing Test Wafers into the fab. The subsequent operations are pre-process operations, operations which prepare the Test Wafer for whatever verification or validation purpose it was intended for. These pre-process operations may be additional cleaning, adding deposition layers, etc. Once the pre-process operations are complete, Test Wafers enter a "Test Wafer Ready" (TWR) operation. This is a holding operation where specific route inventory is held awaiting usage. Once needed, Test Wafers enter a "Test Wafer In Use" (TWI) operation. At this operation Test Wafers are used for their verification or validation purpose. Once this operation is completed Test Wafers are placed in exit operations. These are used to send the Test Wafers to be either recycled/cleaned or scrapped. The block diagram and example sequence in Figure 3 and Table 3 illustrates this process. Bar codes and scanners are used to "proc" the Test Wafers from one operation to the next.

Figure 3: General route block diagram

<sup>&</sup>lt;sup>7</sup> Class 10 deals with the particle levels in a specific volume. By definition, a class 10 space has 10 particles greater than 0.5microns per cubic foot. As reference, normal living conditions are at class 1,000,000 (one million particles greater than 0.5microns per cubic foot)

| Sequence | Operation Number | Operation Description                |

|----------|------------------|--------------------------------------|

| 1        | 9001             | Starts Test Wafer lot into the fab   |

| 2        | 9050             | Pre-process step 1                   |

| 3        | 7130             | Pre-process step 2                   |

| 4        | 3520             | Pre-process step 3                   |

| 5        | 8550             | Test Wafer Ready (TWR)               |

| 6        | 8560             | Test Wafer In Use (TWI)              |

| 7        | 1210             | Send to external vendor for cleaning |

Table 3: Example route sequence of operations<sup>8</sup>

To help quantify the complexity of the Test Wafer operations and routes, there are over 200 different routes. These are needed to ensure that all tools and activities needed to manufacture production wafers are behaving properly. Each of these routes has specific Test Wafer requirements, consumption rates, and lead times. Minimizing the variability of each route is a difficult challenge.

Lastly, in a 200mm diameter wafer facility, all wafers are transported in groups of 25 wafers. One group of wafers is called a lot. Lot boxes are designed to transport 25 wafers as well as interface with transportation equipment and tools. Test Wafer deliveries occur in multiples of 25 wafers for this reason. Only a full lot box can be "proc'ed" to the next operation.

### 2.3 Test Wafers and Fab-17

Fab-17 is a 200mm wafer facility; meaning all tools and machines are designed for the manufacturing of semi-conductors on a 200mm diameter silicon wafer. Over the past few years Fab-17 has pursued aggressive lean education programs to reduce cycle time, improve quality, and reduce operating costs. Since the majority of Intel's factories are 300mm facilities and the next generation of 450mm facilities is in design, the importance of reducing wafer costs is that much more critical. Fab-17 is at a precarious position in that the cost to upgrade the current facility is greater than building a new "greenfield" site.<sup>9</sup> Rumors of plant closure have help drive improvement projects and a culture focused on reducing its costs.

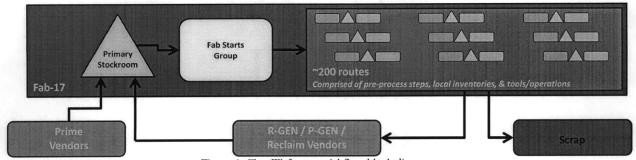

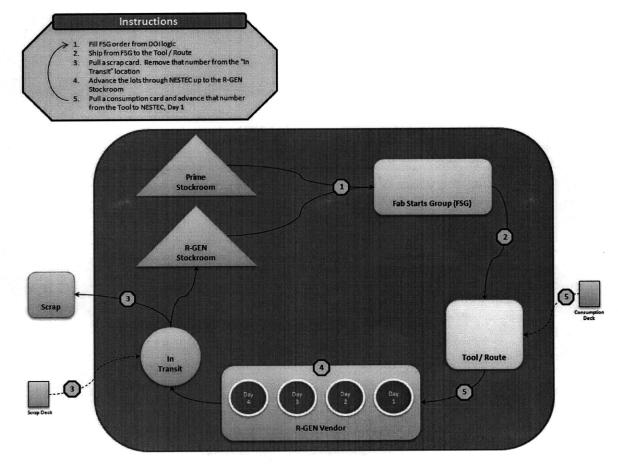

Figure 4 illustrates Test Wafer material flow at Fab-17. Each block will be elaborated in sections 2.3.1 through 2.3.6.

<sup>&</sup>lt;sup>8</sup> All operation numbers are false placeholders

<sup>9</sup> Greenfield: a new site on land previously undeveloped

Figure 4: Test Wafer material flow block diagram

### 2.3.1 Primary Stockroom

Test Wafer inventory is received and stored in the Primary Stockroom outside of the manufacturing clean room. Each Test Wafer lot is individually bagged to minimize the risk of contamination and cleanliness issues. All four types of Test Wafers are held here. For Prime and Reclaim wafers, their quantities are controlled by a forecasting group within Intel. They are grouped together by their base characteristics. Any route which can accept those base characteristics can pull from that Test Wafer batch if inventory is available.

R-GEN and P-GEN Test Wafers are handled in one of two different approaches. The specific routes determine which approach they would prefer; this decision is primarily based upon risk to the tool.<sup>10</sup>

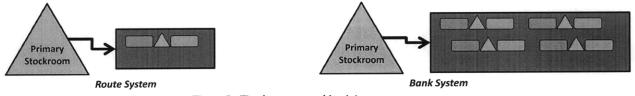

1. **Inventory held married to a particular route:** With this approach, all Test Wafers which leave the fab for R-GEN or P-GEN cleaning procedures are returned to their original route. The primary advantages and disadvantages of this system are summarized in Table 4.

| Advantage                                                                                                                                                                                               | Disadvantage                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| - Control of Test Wafers exposing the route<br>to potential contamination. The risk of a<br>Test Wafer from a different route with<br>contamination or with conflicting base<br>characteristics is low. | - The consumption/usage variability is<br>accommodated on each individual route.<br>This drives a need for larger safety stock<br>inventory levels |

| - The Test Wafers are effectively "owned"<br>by the route. Measuring Test Wafer usage<br>and costs are much easier.                                                                                     |                                                                                                                                                    |

Table 4: Advantages/Disadvantages for inventory held married to a particular route

<sup>&</sup>lt;sup>10</sup> Oftentimes, risk is a perceived risk instead of actual risk. Although a culture of improvement is present many route owners are risk adverse and will take more conservative approaches to change

2. Inventory from multiple routes are lumped together in a "bank"<sup>11</sup>: With a bank system, Test Wafers returning from R-GEN and P-GEN cleaning procedures with identical base characteristics are lumped together. This single Test Wafer group is called a bank. Any route which can use Test Wafers with those base characteristics can pull from that particular bank. Routes which feed or supply Test Wafers to a bank are called "feeders." Routes which pull or eat Test Wafers from a bank are called "eaters." Not all banks have the same feeders and eaters. Some routes only feed to a bank while others only eat from a bank based upon route Test Wafer requirements. The primary advantages and disadvantages of this system are captured in Table 5.

| Advantage                                                                                                                                                                                                                        | Disadvantage                                                                                                                                                                             |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| - Individual route consumption/usage<br>variability can be aggregated. This decreases<br>the overall variability and allows for a total<br>smaller safety stock inventory while<br>maintaining the same Test Wafer availability. | - Verifying and ensuring that all Test Wafers<br>in a bank meet the base characteristics is<br>extremely important. Proper quality control<br>and trust in the bank system is paramount. |  |

| - Decreases the overall Test Wafer costs for<br>the routes feeding from the bank as<br>additional cheaper Test Wafers are available.                                                                                             | - Directly tracing costs back to a particular route (cost accounting) is challenging                                                                                                     |  |

Table 5: Advantages/Disadvantages for inventory held in a bank system

Figure 5 shows a pictorial representation of the route and bank Test Wafer inventory management systems. The Primary Stockroom triangle represents a particular route or bank Test Wafer inventory group. The green box represents the fab with either a single or numerous routes (routes depicted with boxes/triangles for pre-process, TWR, and TWI steps). Further below, Figure 5 elaborates on these inventory management concepts.

Figure 5: Fixed to route and bank inventory systems

### 2.3.2 Fab Starts Group (FSG)

The Fab Stars Group (FSG) is responsible for determining what, where, and when Test Wafers should be released into the fab. They are also responsible for physically moving Test Wafer lots from outside of the clean room and "PROC'ing" them into the first operation. It is at this point that previously unassigned Test Wafer lots become associated with a particular route. Lastly, FSG is also responsible for shipping used Test Wafers outside of the fab. In summary, FSG is the intermediary between the Primary Stockroom and the fab routes.

<sup>&</sup>lt;sup>11</sup> Note that all bank Test Wafers are of the R-GEN or P-GEN type

FSG is not only a group of technicians but also a location. The technicians complete their responsibilities in a special area which has an airlock allowing transfers to and from the clean room area. Various other tools and equipment are located in this area to help assist with initial Test Wafer checks and lot box identification.

Numerous computers linked to the Intel network have programs which provide information and complete calculations to assist FSG in making the Test Wafer starts decisions. Every shift, FSG must determine the following Test Wafer actions.

- 1. Which routes need Test Wafers

- 2. How many Test Wafers are needed

- 3. What type of Test Wafers should be used

Previously, a program based upon minimum quantity levels per route was used to trigger which routes and how many Test Wafers were needed. This program and the behaviors leading to problems will be discussed fully in section 2.5.2. Project 2 of this thesis addresses these issues.

The type of Test Wafer that should be used is determined by the route owner and is documented in a substitution table. The substitution table is formatted in ascending cost order; the cheapest Test Wafer type meeting the route's base characteristics is preferred first while the most expensive is prioritized last. Often the silicon substitution table order is R-GEN or P-GEN, Reclaim, and then Prime silicon Test Wafers but is ultimately determined by the route's requirements.

Table 6 contains an example silicon substitution preference for five example routes. The text in the "1rst Choice" through "5<sup>th</sup> Choice" columns corresponds to a particular Test Wafer type with the specified base characteristics. The "Route," Bank," and "Reclaim" text in the boxes correspond to example Test Wafer inventory of that particular characteristic.

|         | Silicon Substitution Preferences |           |           |         |         |

|---------|----------------------------------|-----------|-----------|---------|---------|

|         | 1rst Choice                      | 2nd       | 3rd       | 4rth    | 5th     |

| Route-1 | <b>R-GEN Route-1</b>             | Reclaim-A | Reclaim-B | Prime-A |         |

| Route-2 | Bank-A                           | Reclaim-C | Prime-B   | Prime-C | Prime-D |

| Route-3 | P-GEN Route-3                    | Prime-A   |           |         |         |

| Route-4 | Reclaim-A                        | Prime-A   |           |         |         |

| Route-5 | Prime-B                          |           |           |         |         |

Table 6: Example silicon substitution table.

Once FSG has determined that a particular route needs Test Wafers, they then check for availability in the Stockroom. In theory, they should start the number of Test Wafer lots required using the cheapest Test Wafer type available.<sup>12</sup> This may be a combination of different Test Wafer types.

<sup>&</sup>lt;sup>12</sup> Actual practice will be discussed in section 2.5.2

### 2.3.3 Test Wafer routes

Once Test Wafer lots are released into the fab, many routes have pre-process operations used to prepare the Test Wafer to whatever state is necessary for their action operation (TWI). The number of pre-process steps and the type of activity at each operation determine the length of time needed for pre-processing before the Test Wafer is ready for use (TWR).

In order to buffer consumption spikes and accommodate this pre-process and delivery lead time, individual routes hold inventory at the TWR operation.<sup>13</sup> The quantity of Test Wafers held in this operation is different for each route. The size of inventory buffer is fixed by the route owner. When the quantity of Test Wafers drops below this value, the system signals FSG to start additional lots.<sup>14</sup>

To minimize the length of time needed to get to the TWR operation, the technicians often need to track down the location of their Test Wafers and communicate their importance to the pre-process tool technicians. Since Test Wafers are seen as non-value add and do not count in area metrics, many technicians will purposely choose to run production wafers instead. The pre-process length variability is large, at times up to a week before a Test Wafer lot arrives at TWR. This "human glue" or human intervention is necessary to keep the system running, albeit at high labor resource and complicated work expense.