# Material Selection and Nanofabrication Techniques for Electronic Photonic Integrated Circuits

by

Charles W. Holzwarth III

B.S. Material Science and Engineering University of Illinois Urbana-Champaign, 2004

Submitted to the Department of Materials Science and Engineering in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Materials Science and Engineering at the

Massachusetts Institute of Technology

**ARCHIVES**

June 2009

JUL 2 8 2009

LIBRARIES

© 2009 Massachusetts Institute of Technology All right reserved

| Signature of Author | •        |          |           |           | and Engineering<br>April 28, 2009                  |

|---------------------|----------|----------|-----------|-----------|----------------------------------------------------|

| Certified by        |          | /<br>Pro | ofessor ( | of Electr | Henry I. Smith ical Engineering nesis Supervisor   |

| Certified by        |          |          |           |           |                                                    |

| ,                   | Professo | or of Ce | ramics    | and Elec  | Harry L. Tuller ctronic Materials nesis Supervisor |

| Accepted by         |          |          |           |           |                                                    |

|                     |          |          |           |           | Christine Ortiz aduate Students                    |

#### Material Selection and Nanofabrication Techniques for Electronic Photonic Integrated Circuits

by

Charles W. Holzwarth III

Submitted to the Department of Materials Science and Engineering on April 28, 2009 in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Materials Science and Engineering

#### **ABSTRACT**

Electronic-photonic integrated circuits have the potential to circumvent many of the performance bottlenecks of electronics. To achieve the full benefits of integrating photonics with electronics it is generally believed that wavelength-division multiplexing is needed; requiring an integrated optical device capable of multiplexing/demultiplexing operations. One such device is a bank of microring-resonator filters with precisely spaced resonant frequencies.

In this work, a fabrication strategy based on scanning-electron-beam lithography (SEBL) is presented for precisely controlling the resonant frequency of microring-resonator filters. Using this strategy it is possible to achieve dimensional control, on the tens-of-picometer scale, as required for microring-resonator filter banks. To correct for resonant-frequency errors present after fabrication, two forms of postfabrication tuning, one dynamic and one static, are demonstrated. It is also shown that hydrogen silsesquioxane (HSQ) can be converted into a high-quality overcladding for photonic devices by optimizing the annealing process. Finally, a postfabrication technique of localized substrate removal is presented, enabling the integration of photonics with CMOS electronics.

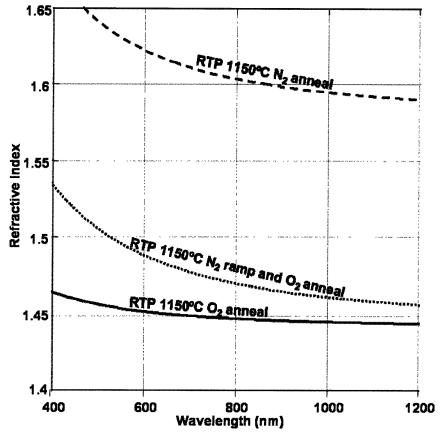

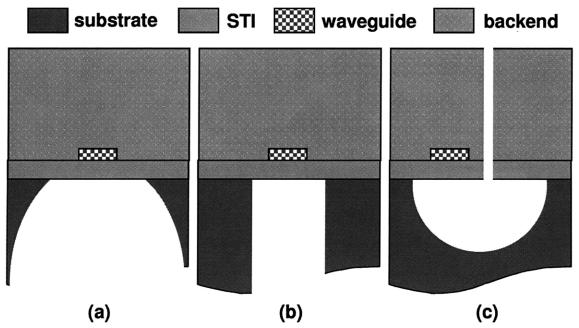

Second-order microring-resonator filter banks were fabricated using SiN<sub>x</sub> and Si as the high-index core materials. By controlling the electron-beam-exposure dose it is possible to change the average microring-waveguide width to a precision better than 75 pm, despite the 6 nm SEBL address grid. Using postfabrication tuning the remaining resonant-frequency errors can be reduced to less than 1 GHz. By annealing HSQ in a an O<sub>2</sub> atmosphere using rapid thermal processing, it is possible to create thick overcladding layers that have essentially the same optical properties as SiO<sub>2</sub> with the excellent gap-filling and planarization properties of HSQ. Using XeF<sub>2</sub> to locally etch an underlying Si substrate, waveguides with a propagation loss of ~10 dB/cm were fabricated out of polysilicon deposited on 50 nm of SiO<sub>2</sub>.

Thesis Supervisor: Henry I. Smith

Title: Professor of Electrical Engineering

Thesis Supervisor: Harry L. Tuller

Title: Professor of Ceramics and Electronic Materials

### **Table of Contents**

| Chapter 1 Introduction                                               | 18       |

|----------------------------------------------------------------------|----------|

| PART I Microring-Resonators Filters and Filter Banks                 | 22       |

| Chapter 2 Background                                                 | 23       |

| 2.1 Electronic-Photonic Integrated Circuits                          | 23       |

| 2.1.1 Ultra-Fast Analog-to-Digital Converter                         | 26       |

| 2.1.2 Many-Core Processor-to-DRAM Networks                           | 29       |

| 2.2 Microring Resonator Optical Filters                              | 31       |

| 2.2.1 General Operation                                              | 31       |

| 2.2.2 Material Selection and Fabrication Challenges                  | 34       |

| Chapter 3 Fabrication of Microring Resonators                        | 36       |

| 3.1 Introduction                                                     | 36       |

| 3.2 Silicon-Rich Silicon Nitride Filters                             | 37       |

| 3.2.1 SiN <sub>x</sub> Filter Fabrication with PMMA                  | 40       |

| 3.2.2 Reactive-Ion Etching Optimization                              | 42       |

| 3.3 Silicon Filters                                                  | 43       |

| 3.3.1 Silicide Formation                                             | 45       |

| 3.3.2 Si Filter Fabrication with HSQ                                 | 48       |

| 3.4 Exposure Optimization                                            | 50       |

| 3.4.1 Roughness Minimization                                         | 51       |

| 3.4.2 Absolute Dimensional Control and Pattern Fidelity              | 54       |

| 3.5 Conclusion                                                       | 58       |

| Chapter 4 Lithographic Resonant Frequency Control of Microring Resor | nators59 |

| 4.1 Introduction                                                     | 59       |

| 4.2 Dose Modulation                                                  | 62       |

| 4.2.1 Binary Model                                                   | 64       |

| 4.2.2 String Propagation Method                                      | 66       |

| 4.3 Calibration Experiments                                          | 60       |

| 4.4 Scale-Up                                             | 74  |

|----------------------------------------------------------|-----|

| 4.5 Conclusion                                           | 76  |

| Chapter 5 Postfabrication Trimming                       | 77  |

| 5.1 Introduction                                         | 77  |

| 5.2 Dynamic Tuning with Microheaters                     | 79  |

| 5.2.1 Heater Fabrication                                 | 80  |

| 5.2.2 Tuning Performance                                 | 82  |

| 5.3 Static Tuning with Electron-Beam Curing              | 84  |

| 5.4 Conclusion                                           | 88  |

| Chapter 6 Microring-Resonator Filter Banks               | 89  |

| 6.1 Introduction                                         | 89  |

| 6.2 Device Architecture                                  | 90  |

| 6.2.1 Filter Design                                      | 91  |

| 6.2.2 Material Selection                                 | 93  |

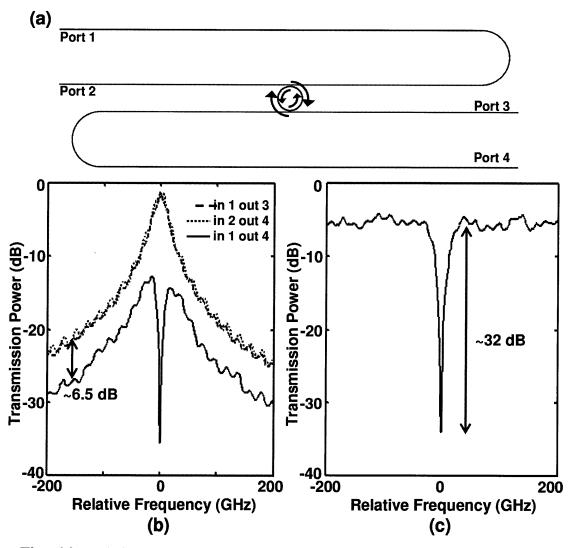

| 6.2.3 Counter-Propagating-Mode Design                    | 95  |

| 6.3 SiN <sub>x</sub> Filter Banks                        | 98  |

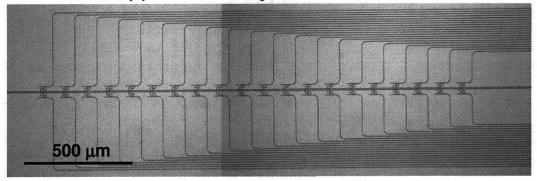

| 6.3.1 Eight-Channel Filter Bank                          | 99  |

| 6.3.2 Twenty-Channel Filter Bank                         | 102 |

| 6.3.3 Thermally Corrected Filter Bank                    | 104 |

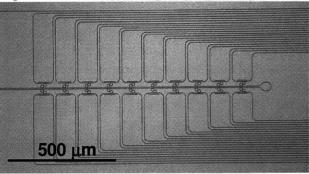

| 6.4 Si Filter Banks                                      | 105 |

| 6.5 Conclusion                                           | 108 |

| PART II Supporting Technologies for Integration          | 109 |

| Chapter 7 Optimized Hydrogen Silsesquioxane Overcladding | 110 |

| 7.1 Introduction                                         | 110 |

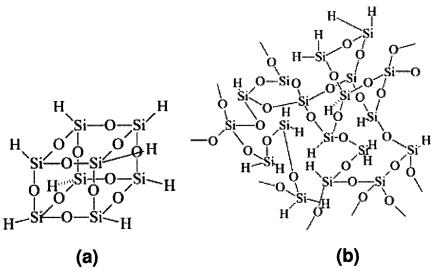

| 7.2 Converting HSQ to SiO <sub>2</sub>                   | 113 |

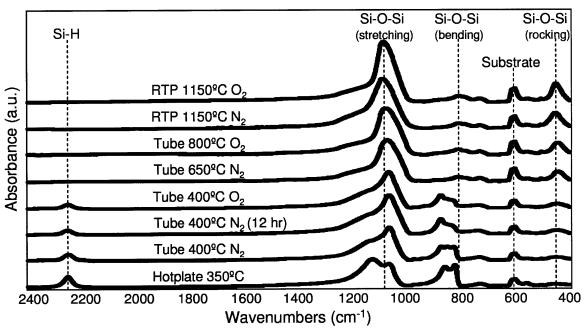

| 7.2.1 Thermal Annealing                                  | 113 |

| 7.2.2 Measured Material Properties                       | 117 |

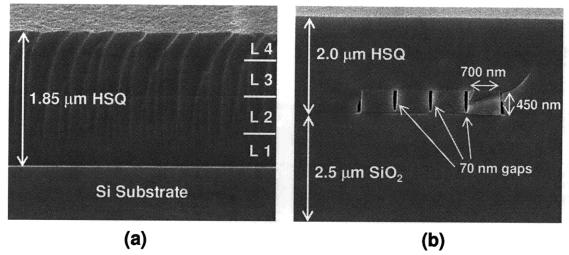

| 7.2.3 Creating Thick Layers                        | 120 |

|----------------------------------------------------|-----|

| 7.2.4 Gap-Filling, Planarization, and Optical Loss | 124 |

| 7.3 Conclusion                                     | 126 |

| Chapter 8 Localized Substrate Removal              | 128 |

| 8.1 Introduction                                   | 128 |

| 8.2 Localized Substrate Removal                    | 131 |

| 8.2.1 XeF <sub>2</sub> Etching                     | 132 |

| 8.2.2 Fabrication Process                          | 134 |

| 8.2.3 Measured Poly-Silicon Loss                   | 137 |

| 8.3 Creating Waveguides in a CMOS Line             | 138 |

| 8.3.1 Transparent Fabrication                      | 139 |

| 8.3.2 Post-Processing.                             | 140 |

| 8.4 Conclusion.                                    | 141 |

| Chapter 9 Conclusion                               | 143 |

| 9.1 Summary of Accomplishments                     | 143 |

| 9.2 Future Work                                    | 144 |

| Appendix A Loss Measurement Methods                | 146 |

| Bibliography                                       | 149 |

## **List of Figures**

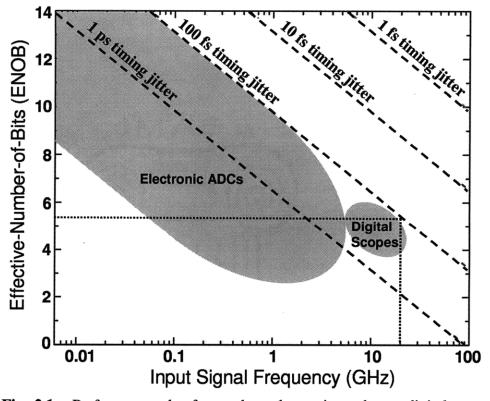

| Fig. 2.1  | Performance plot for electronic analog-to-digital converters                                               | 26 |

|-----------|------------------------------------------------------------------------------------------------------------|----|

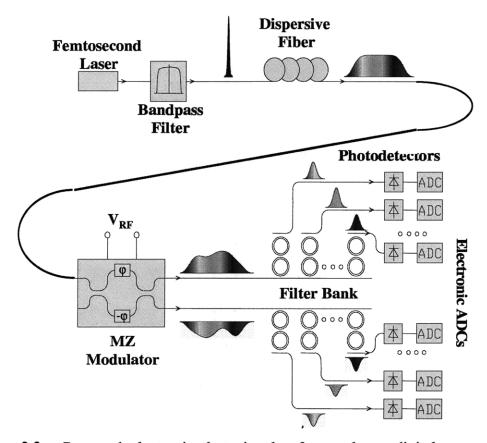

| Fig. 2.2  | Proposed electronic-photonic analog-to-digital converter                                                   | 28 |

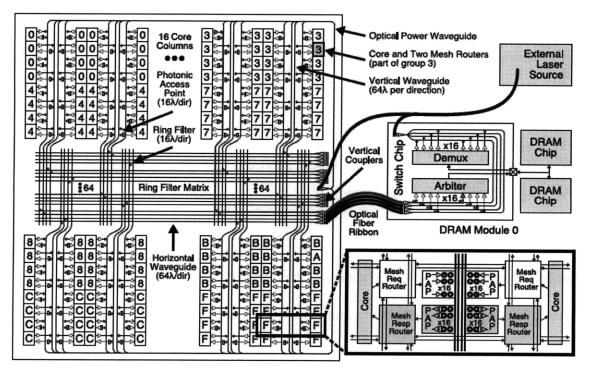

| Fig. 2.3  | Proposed photonic manycore-to-DRAM network                                                                 | 30 |

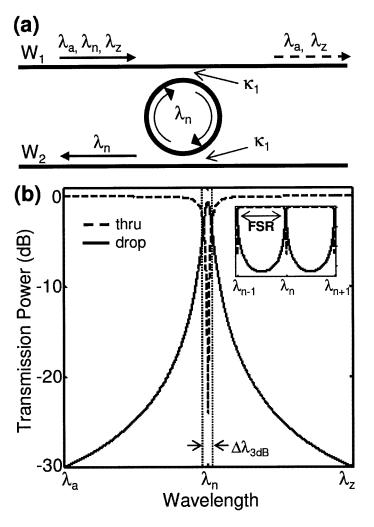

| Fig. 2.4  | Schematic and simulated transmission response of a first-order microring-resonator filter                  | 32 |

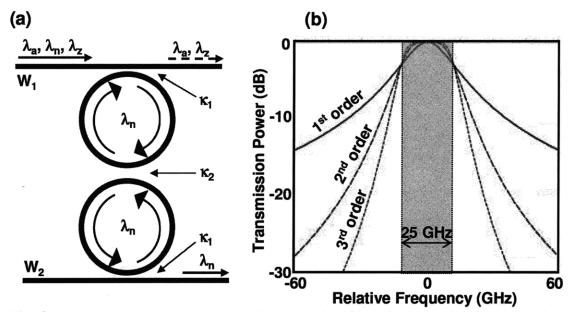

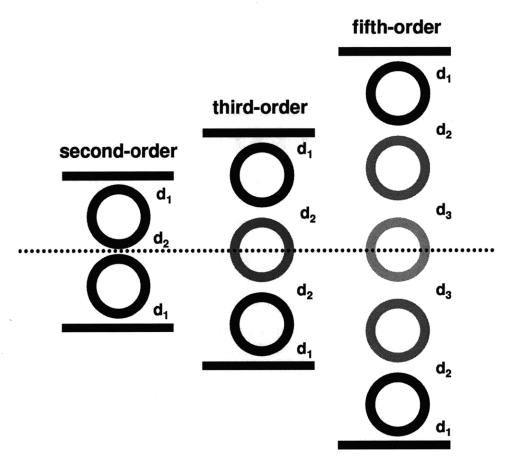

| Fig. 2.5  | Schematic of second-order filter and simulated transmission responses for higher-order filters             | 34 |

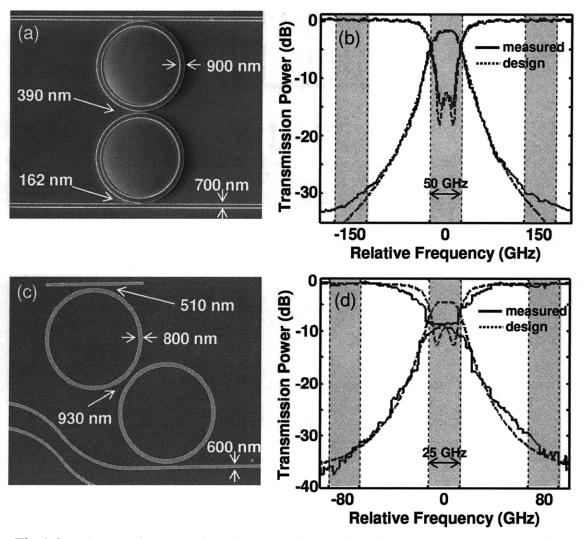

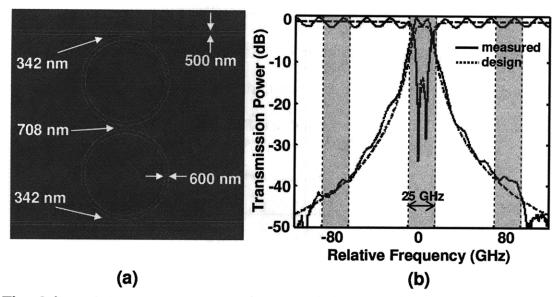

| Fig. 3.1  | Top-view micrograph, measured and simulated transmission response of second-order SiN <sub>x</sub> filters | 38 |

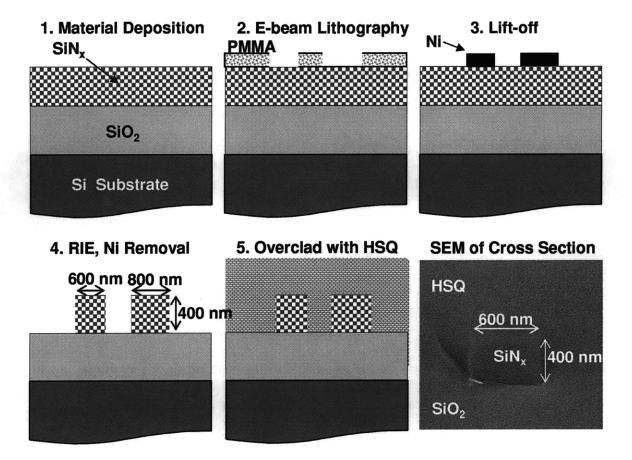

| Fig. 3.2  | Fabrication process for SiN <sub>x</sub> filters                                                           | 40 |

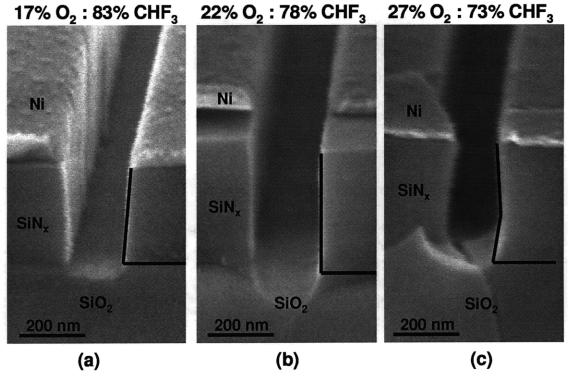

| Fig. 3.3  | Effects of RIE O <sub>2</sub> concentration on sidewall profile                                            | 43 |

| Fig. 3.4  | Top-view micrograph, measured and simulated transmission response of second-order Si filters               | 45 |

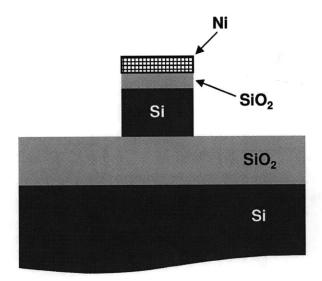

| Fig. 3.5  | Cross-section diagram of Si waveguide after RIE                                                            | 46 |

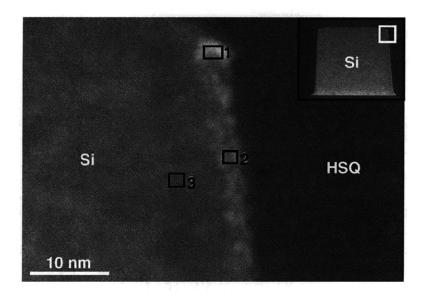

| Fig. 3.6  | Cross-section STEM and EDS spectrum of Pd silicide on the Si waveguide sidewall                            | 48 |

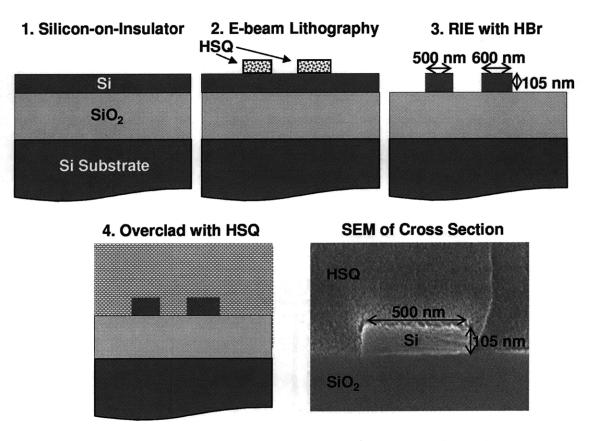

| Fig. 3.7  | Fabrication process for Si filters                                                                         | 49 |

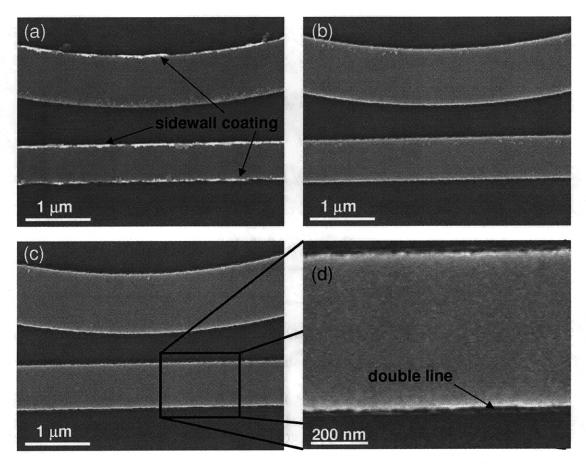

| Fig. 3.8  | Micrographs of the Ni hardmask roughness for various exposure doses                                        | 52 |

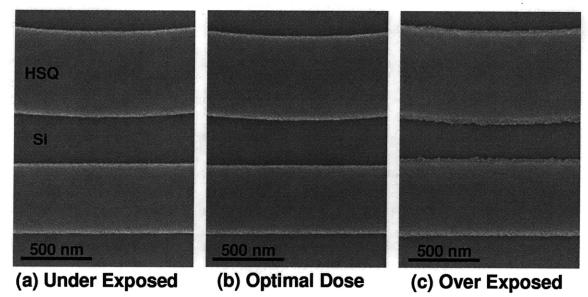

| Fig. 3.9  | Micrographs of HSQ for various exposure doses                                                              | 53 |

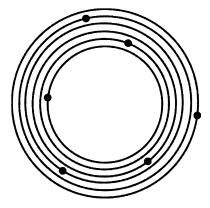

| Fig. 3.10 | Schematic of optimal SEBL writing strategy for microrings                                                  | 56 |

| Fig. 3.11 | Plot of the location dependent frequency mismatch in second-order filters due to intrafield distortions    | 58 |

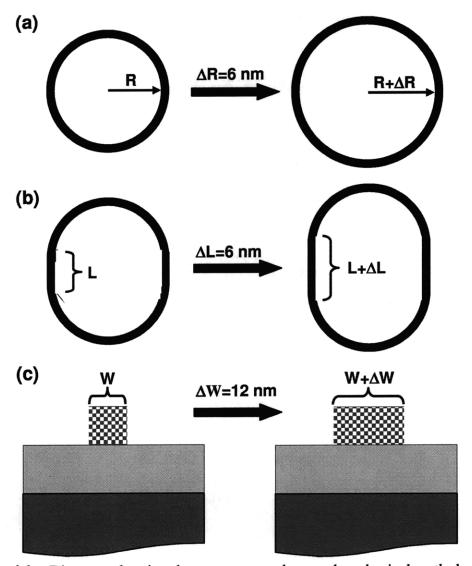

| Fig. 4.1  | Ways to shift a microrings resonant frequency though dimensional changes in the SEBL layout                | 61 |

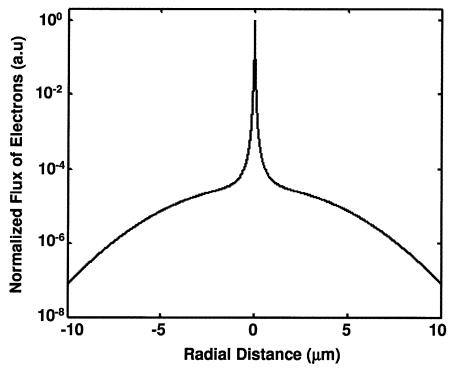

| Fig. 4.2  | Point-spread function for Raith 150                                                                        | 63 |

| Fig. 4.3 | Dose profile cross-section of microring resonator65                                                   |

|----------|-------------------------------------------------------------------------------------------------------|

| Fig. 4.4 | Simulated resonant frequency dependence on exposure dose using binary model                           |

| Fig. 4.5 | String propagation method for resist development simulations67                                        |

| Fig. 4.6 | Simulated resonant frequency dependence on exposure dose using the string propagation method          |

| Fig. 4.7 | SEBL layout for frequency calibration experiments70                                                   |

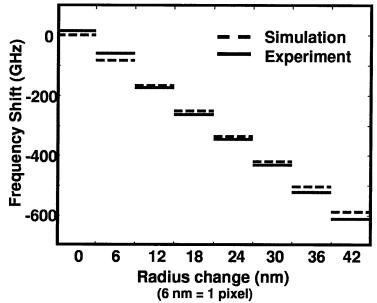

| Fig. 4.8 | Resonant frequency change for input change in radius71                                                |

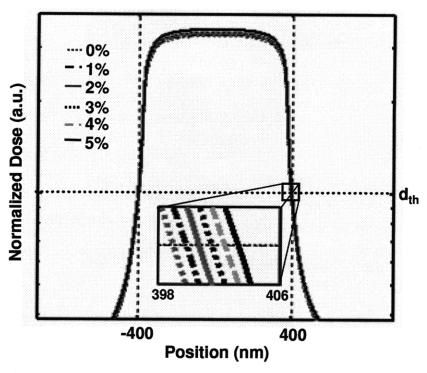

| Fig. 4.9 | Experimental results of resonant frequency dependence on exposure dose compared to simulation results |

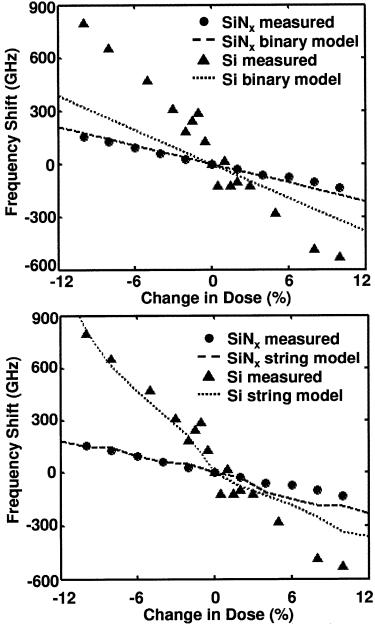

| Fig. 5.1 | Change in intrinsic Q with heater location80                                                          |

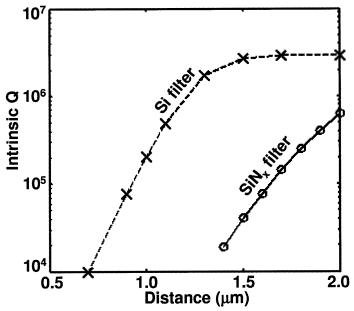

| Fig. 5.2 | Image of packaged thermally-tunable photonic chip81                                                   |

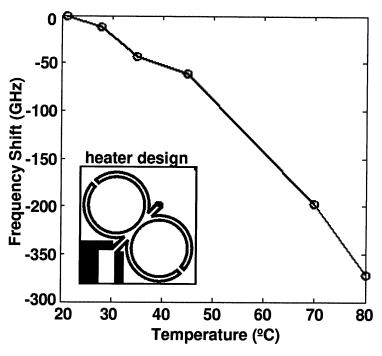

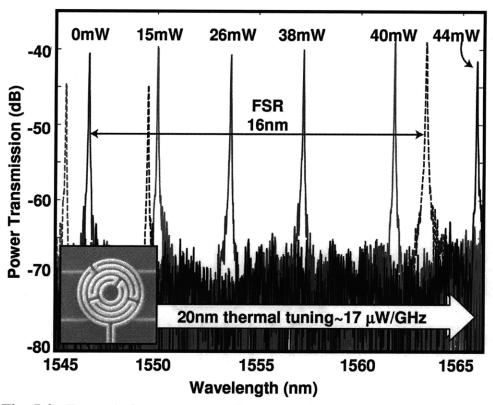

| Fig. 5.3 | Tuning efficiency of SiN <sub>x</sub> filters83                                                       |

| Fig. 5.4 | Tuning range of Si filters84                                                                          |

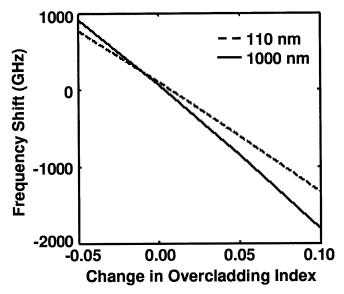

| Fig. 5.5 | Simulated frequency shift with change in overcladding index86                                         |

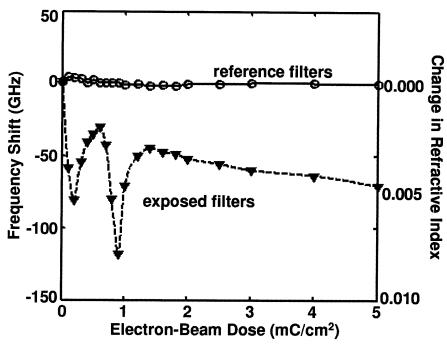

| Fig. 5.6 | Frequency shift versus electron-beam curing dose87                                                    |

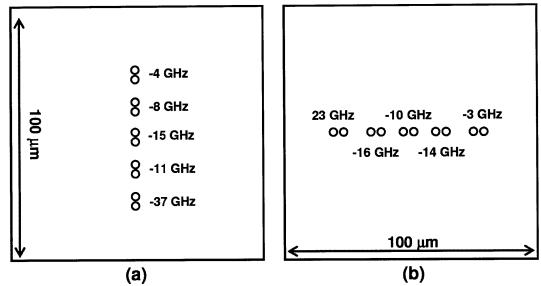

| Fig. 6.1 | Frequency shifts due to proximity effects and CIFS92                                                  |

| Fig. 6.2 | Filter bank layouts for standard and contra-propagating mode designs                                  |

| Fig. 6.3 | Crosstalk between contra-propagating modes in a microring resonator filter                            |

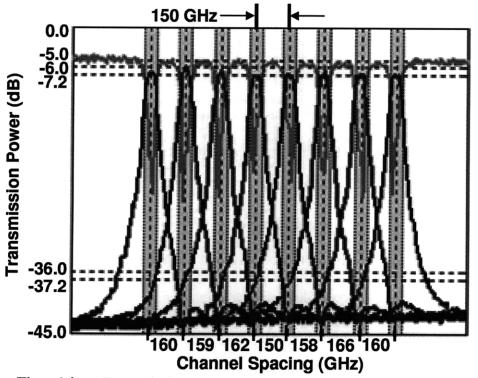

| Fig. 6.4 | Transmission response for an eight-channel filter bank using air-clad SiN <sub>x</sub> filters        |

| Fig. 6.5 | Transmission response for a twenty-channel filter bank using oxide-clad SiN <sub>x</sub> filters      |

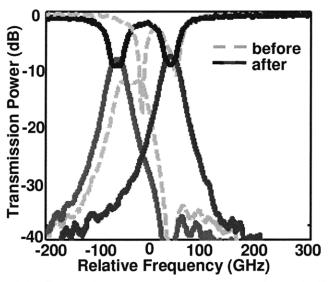

| Fig. 6.6 | Transmission response of a two-channel filter bank before and after using thermal tuning              |

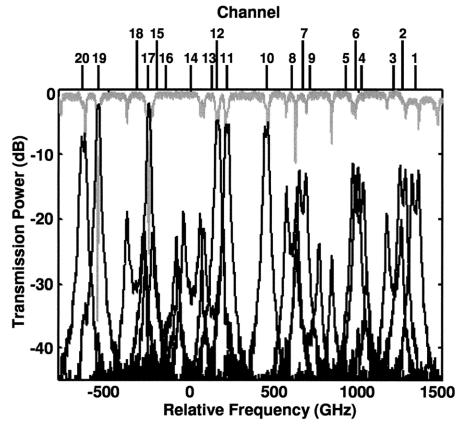

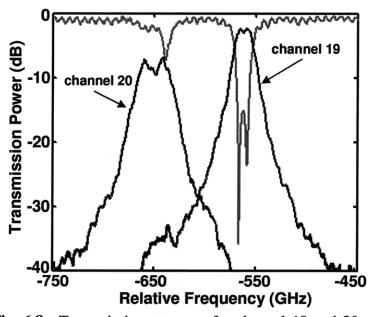

| Fig. 6.7 | Transmission response for a twenty-channel Si filter bank106                                          |

| Fig. 6.8  | Transmission response of two channels of a twenty-channel Si filter bank                                             |

|-----------|----------------------------------------------------------------------------------------------------------------------|

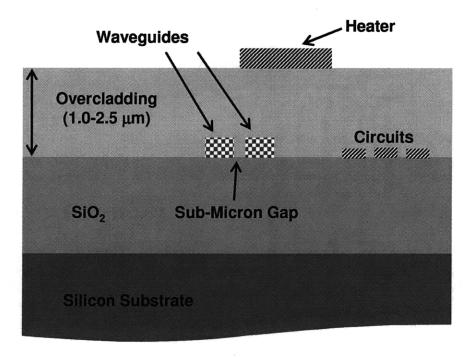

| Fig. 7.1  | Schematic of the role of an overcladding material111                                                                 |

| Fig. 7.2  | Cage and network structure of HSQ114                                                                                 |

| Fig. 7.3  | Chromatic dispersion of HSQ samples annealed at high temperatures119                                                 |

| Fig. 7.4  | FTIR measures of HSQ samples for different final anneals120                                                          |

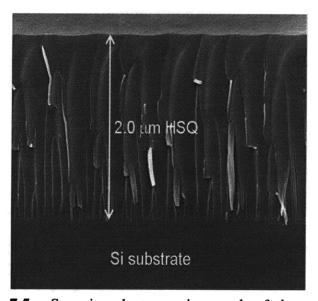

| Fig. 7.5  | Micrograph showing 2.0 μm thick HSQ film122                                                                          |

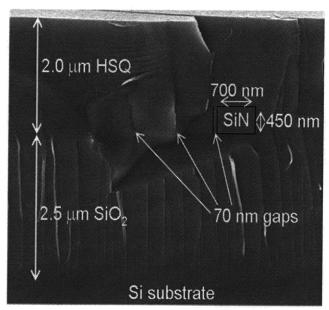

| Fig. 7.6  | Micrograph demonstrating gap-filling and planarization properties of optimal HSQ annealing process                   |

| Fig. 7.7  | Cross-section micrograph of optimized HSQ film after decretive HF etch                                               |

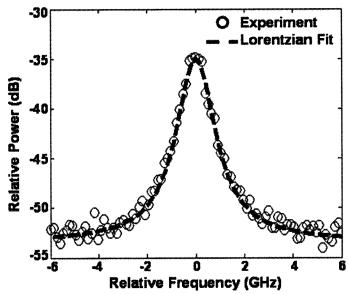

| Fig. 7.8  | Transmission response of a high-Q ring overclad with optimized HSQ                                                   |

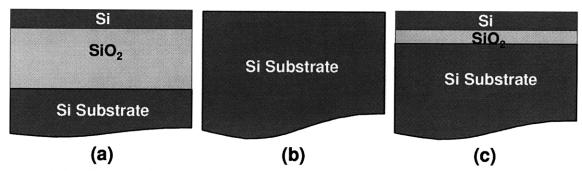

| Fig. 8.1  | Cross-sectional diagram of common starting wafers for photonics and VLSI                                             |

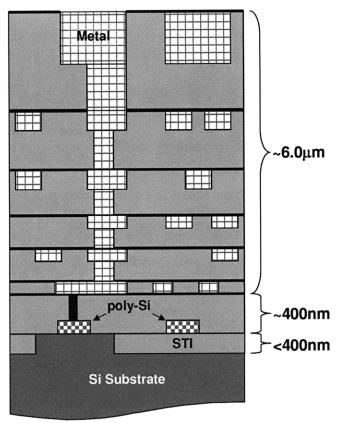

| Fig. 8.2  | Schematic cross-section of a high-performance CMOS chip130                                                           |

| Fig. 8.3  | Diagram showing the integration of photonics on a CMOS chip130                                                       |

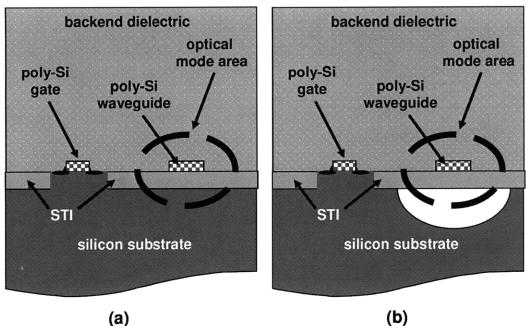

| Fig. 8.4  | Possible ways to achieve localized substrate removal                                                                 |

| Fig. 8.5  | Chemical process for etching Si with XeF <sub>2</sub> 132                                                            |

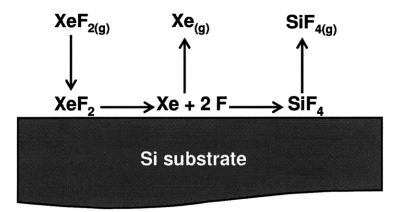

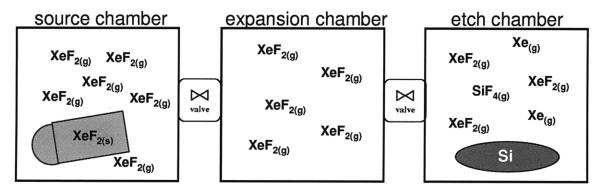

| Fig. 8.6  | Schematic for three chamber XeF <sub>2</sub> etching system133                                                       |

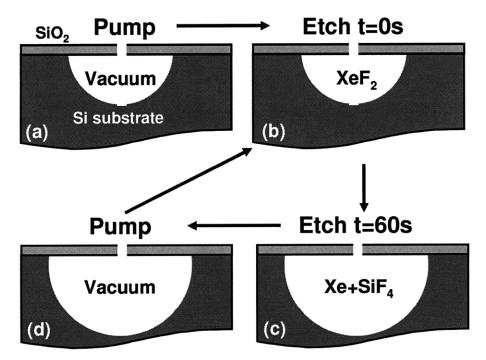

| Fig. 8.7  | Pump-etch-pump method for achieving large undercuts                                                                  |

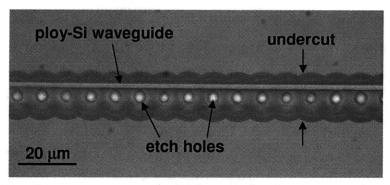

| Fig. 8.8  | Optical micrograph of poly-Si waveguide with locally removed substrate                                               |

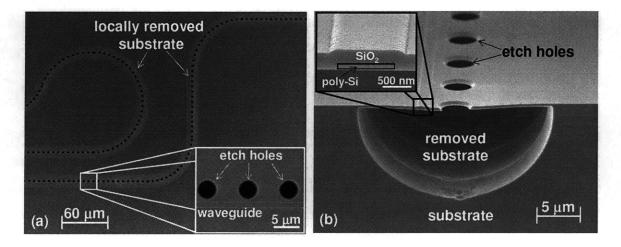

| Fig. 8.9  | Top-view and cross-section micrograph of poly-Si waveguide with locally removed substrate                            |

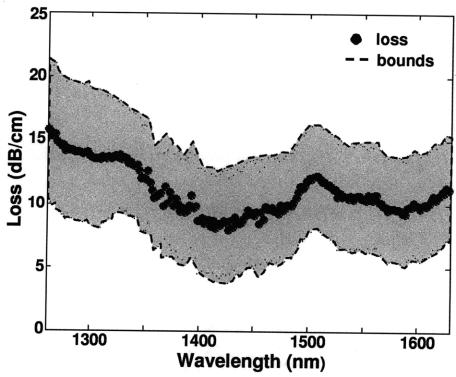

| Fig. 8.10 | Measure propagation loss for poly-Si waveguides fabricated using XeF <sub>2</sub> to locally remove the substrate137 |

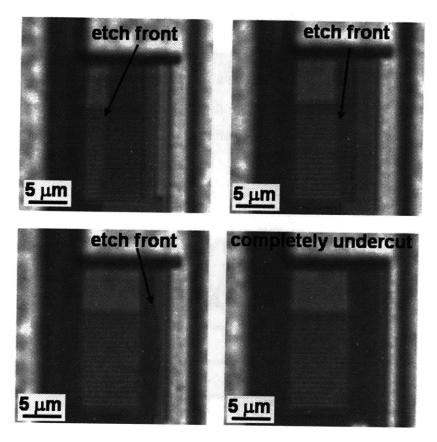

| Fig. 8.11 | Micrographs showing the Si undercut etch front propagating under a vertical coupler                                  |

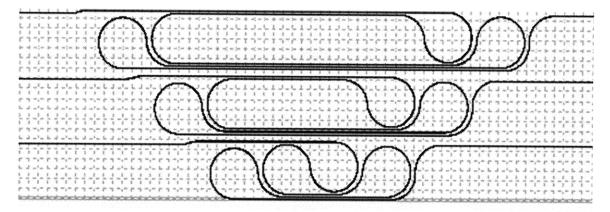

| Fig. A.1 | Paperclip layout for loss measurements                                   | 47 |

|----------|--------------------------------------------------------------------------|----|

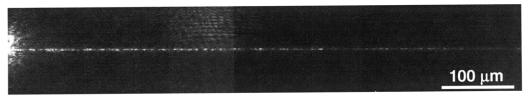

|          | Photography of light scattering from a waveguide taken with an IR camera | 48 |

### **List of Tables**

| Table 3.1 | Measured roughness and propagation loss of different metallic hardmasks | 47   |

|-----------|-------------------------------------------------------------------------|------|

| Table 3.2 | Dimensional accuracy of filters parameters                              | 55   |

| Table 4.1 | Resonant frequency dependence for dimensional changes                   | 60   |

| Table 4.2 | Frequency dependence on radius and dose from experiments                | 70   |

| Table 6.1 | Material and filter bank properties for selected CMOS materials         | 93   |

| Table 7.1 | Refractive indexes and film shrinkage of HSQ for different anneals      | 118  |

| Table 7.2 | HSQ film thickness first observed to crack for different anneals        | .122 |

### **List of Acronyms**

3D: Three-dimensional

ADC: Analog-to-digital converter

CIFS: Coupling-induced frequency shifts

CMOS: Complementary metal-oxide-semiconductor

ENOB: Effective number of bits

EPIC: Electronic-photonic integrated circuit

FDTD: Finite-difference-time-domain

FSR: Free spectral range

HIC: High index contrast

HSQ: Hydrogen silsesquioxane

IC: Integrated circuit

LER: Line-edge roughness

LPCVD: Low-pressure chemical-vapor deposition

PECVD: Plasma-enhanced chemical-vapor deposition

PMMA: Poly-methyl-methacrylate

Q: Quality factor

RIE: Reactive-ion etching

SEBL: Scanning-electron-beam lithography

SOI: Silicon-on-insulator

WDM: Wavelength-division multiplexing

### Acknowledgements

I would like to first thank all of my collaborators, which are too many to name individually. I would like to especially thank Milos A. Popovic and Anatoly Khilo for providing me with exceptional optical designs over the years. I would also like to thank Marcus Dahlem and Peter T. Rakich for their help with the optical characterization. I believe much of the research successes presented in this thesis is due to the superb level of teamwork between the design, fabrication and characterization groups.

I would like to thank the members of the NanoSructures Laboratory (NSL). The NSL is composed of a first-class group of graduate students, postdocs, and research scientists, whose expertise covers the complete field of nanofabrication. Most importantly I would like to thank the founder of the NSL and my primary thesis advisor Prof. Henry I. Smith. He has been truly exceptional in his role as my advisor, giving me immense freedom to explore interesting avenues of research, while at the same time guiding my ideas with his breadth of nanofabrication knowledge. I would also like to thank Tymon Barwicz, who took the time to train me in many of the aspects of fabricating microring-resonator filters. If it was not for the ground work he began during his thesis work, I would not have been able to achieve the results in my thesis in a reasonable time period. Finally, I would like to thank two of the unsung heroes of my research Jim Daley and Mark Mondol, whose hard work keeps the NSL and Scanning-Electron-Beam Lithography Facility up and running.

I would also like to thank Franz X. Kaertner, from whom I have learned many details about integrated optical systems and femtosecond lasers during our weekly EPIC meetings.

Lastly, I would like to thank my friends, family and my wife. They have been a constant source of support throughout my entire graduate career.

### **Chapter 1**

#### Introduction

Since the fabrication of the first electronic integrated-circuit (IC) there has been a constant drive to make ICs faster, smaller, cheaper, and more energy efficient. This was famously stated in the paper by Gordon E. Moore in 1965 where he predicted the number of components in an integrated circuit, and the density at minimum cost per transistor, would double approximately every two years [1]. This prediction became known as Moore's Law, and although it originally applied to the density of transistors in an IC it is now often used to describe the doubling of computing power every two years. Until recently, this trend has mainly relied on the shrinking or scaling of the transistor size, which enables an increase in speed and density. Some ICs, such as processors, are closing in on the fundamental limits of size scaling, where currently the transistor gate length is ~20 nm [2]. This is forcing processor manufacturers to move to a multicore platform, allowing them to maintain this doubling of computer performance through parallelism. However, this approach has its limitations due to the core-to-DRAM and core-to-core data transfer rate bottlenecks [3]. For other systems, such as high-speed analog-to-digital converters, improving speed through dimensional scaling is not sufficient to improve performance. Currently, the sampling resolution of electronic Chapter 1 Introduction

analog-to-digital converters is limited by the timing jitter of the electronic clock, not the speed of the individual transistors [4]. These two examples demonstrate that dimensional scaling is no longer the answer for achieving higher performance ICs; a new solution is called for.

One such solution is to integrate photonic devices with electronic devices. The history of the telecommunications industry makes is evident that this is not a far-fetched idea. Telecommunication, a word derived from the Greek prefix tele- meaning "far off" and the Latin communicare meaning "to share", describes the transmission of signals over long distances for the sake of communication. From 1837, when the electric telegraph was invented, until the late 1980s the telecommunications infrastructure was dominated by electronic cables. The laying of the first fiber-optic transatlantic cable in 1988 changed this, causing the rapid replacement of long-haul electric cables with fiber optics, taking advantage of their enormous increase in data capacity [5]. This increase in data capacity can also be used to solve the data-transfer bottleneck in multicore processors by replacing some of the electronics with photonics. Also, by integrating photonics with electronics one can take advantage of ultra-low-noise optical sources. For example, the timing jitter of a femtosecond laser is more than two orders of magnitude lower than current state-of-the-art on-chip electronic oscillators. Jitter currently limits the performance of ultra-fast analog-to-digital converters [6]. These are just two examples of the many ways photonics can be combined with electronics in a synergistic manner to form an electronic-photonic integrated circuit (EPIC) that surpasses current performance limitations of electronic ICs.

Chapter 1 Introduction

Although certain photonic devices are already being used heavily in telecommunication systems, they can not be easily integrated with electronic ICs. This is because the photonic devices used in telecommunication are relatively large, low-index-contrast discrete components that are made using materials and fabrication methods that are not CMOS compatible. To monolithically integrate photonics with electronic ICs, a switch from the low-index-contrast and III-V material systems of the telecommunications industry to a high-index-contrast (HIC) CMOS-compatible material system must be made. This would enable a decrease in size, with the added benefit of using CMOS compatible fabrication tools. For seamless integration it is also important to develop a fabrication process for integrated photonics that involves minimal customization of the IC fabrication process.

The switch from low-index-contrast to HIC materials is not trivial. Both the design and fabrication challenges increase rapidly as the index contrast increases. The analytic design tools developed for low-index-contrast photonics do not work adequately for HIC devices, requiring the use of rigorous three-dimensional finite-difference time-domain simulations [7]. Likewise, the fabrication challenges for HIC photonic devices are immense. The propagation loss from sidewall roughness scales with the index contrast squared, requiring ultra-smooth sidewalls for HIC devices. Also, for resonant structures such as microring filters, dimensional precision on the nanometer to tens of picometer level is essential for optimal performance. There are also challenges in integrating HIC photonics with electronics since photonic devices require a thick (>1  $\mu$ m) low-index undercladding layer, which is currently prohibited in high-performance ICs due to thermal constraints.

In this thesis, I address some of the challenges in fabricating CMOS-compatible photonic devices and integrating them with current IC process flows. The main focus will be on the basic architecture and fabrication of filter banks consisting of optical microring-resonators, thought by many to be the basic building block of integrated photonic systems. This will include material selection, means of achieving resonant frequency control without post-fabrication tuning, and post-fabrication tuning methods. Also, a novel fabrication method will be presented that enables the transparent integration of photonic devices with electronic ICs.

This thesis is separated into two main parts. Part I will focus on the fabrication of microring-resonator filter banks that can be used as multiplex/demultiplex devices for EPIC systems. To achieve the resonant-frequency-spacing precision required for these devices, dimensional control on the *tens of picometer scale is required*, which we demonstrate using a novel scanning-electron-beam lithography (SEBL) technique. Also presented, are two forms of post-fabrication tuning, one dynamic and one static, to correct any resonant frequency errors in the filter bank. Using these methods some of the most advanced microring resonator filters and filter banks have been fabricated.

Part II focuses on supporting techniques for the fabrication of EPICs. This includes an optimized annealing technique that allows the use of a spin-on glass to form a high quality overcladding layer for photonic devices. Another supporting technology is a postfabrication technique of localized substrate removal to enable the seamless integration of photonic devices with electronics in a commercial CMOS line.

### **PART I**

# Microring-Resonators Filters and

### Filter Banks

### Chapter 2

### **Background**

#### 2.1 ELECTRONIC-PHOTONIC INTEGRATED CIRCUITS

Advances in HIC photonics have enabled increasingly complex EPICs to be designed and fabricated. Examples of these circuits include: ultrafast analog-to-digital converters, optical interconnects for multicore processors, and fiber-optic transceivers [3,6,8]. The photonic components that comprise EPICs typically fall into one of four categories; waveguides, modulators, filters, and detectors (assuming that the light source will not be integrated monolithically). The goal of EPICs is to integrate these basic photonic building blocks with electronic circuits in a synergistic manner to achieve better performance than in current electronic ICs.

Waveguides are the most basic photonic component, and are used to transport light from one point to another. All other photonic structures are comprised of waveguides in one way or another. The most important characteristic of a waveguides is its propagation loss. The loss consists of a material-dependent term (material absorption) and a fabrication-dependent term (typically scattering from sidewall roughness). Propagation loss will determine the overall efficiency of a photonic device, and for most systems should be 3 dB/cm or less. Other important characteristics are index contrast and the confinement factor of the optical mode. These properties determine the minimum

radius of curvature a waveguide can have before incurring excess bending loss. This is important because the minimum bending radius will ultimately determine how densely photonic devices can be integrated.

The next photonic component, optical modulators, have the role of transforming electrical signals into optical signals. This is typically done by changing either the phase or the magnitude of light. Broadband modulators (> 100 GHz) are typically based on a Mach-Zehnder interferometer and use either carrier injection or heating to change the optical path length between the two arms [9]. This changes the interference at the output of the modulator resulting in an amplitude change. Narrowband modulators (<100 GHz), on the other hand, are typically based on resonant structures such as microrings [10]. Here again, either carrier injection or heating is used to change the optical path length of the device. This results in a change in the resonant frequency, allowing one to modulate the magnitude of the signal. The two important figures of merit for a modulator are the speed at which it can modulate, and the energy consumed per bit. Carrier-injection-based modulators are both faster and more energy efficient then thermal ones so they are preferred [11].

Optical filters are used to separate signals carried on different wavelengths. It is generally agreed that in order to maximize the value of integrating photonics with electronics, wavelength-division multiplexing (WDM), (transporting multiple optical signals through a single waveguide on different wavelengths) must be used [12]. This creates the need for filters to separate the signals (demultiplex) and combine them (multiplex). This filtering function can be achieved using a bank of microring resonators that have resonant frequencies corresponding to the wavelengths of the various signals.

In HIC material systems, such as silicon-on insulator, these microring resonators can have radii as small as  $1.5 \, \mu m$ , making them ideal for integration [13].

The fourth basic photonic building block, detectors, transform optical signals into electrical signals. Detectors are photodiodes made from Ge, SiGe, and ion implanted Si [14,15,16]. The photodiode material is chosen so that it can efficiently absorb the incoming photon, resulting in the excitation of electron-hole pairs. This creates a photocurrent that is dependent on the flux of the incoming light. A few important characteristics of photodiodes are their detection efficiency and speed. Detection efficiency relates the number of incoming photons to the resulting photocurrent. The speed of a photodiode depends on the how quickly the excited electron-hole pairs can exit the photodiode.

These basic photonic building blocks, when combined with an external light source (laser) and integrated with electronic circuits can, overcome performance bottlenecks that limits analogous electronics-only systems. Two systems that provide a great example of the possible synergy between photonics and electronics are an electron-photonic ultra-fast analog-to-digital converter and an optical many-core processor-to-DRAM network. Both systems address current limitations in integrated electronic circuits by replacing certain parts of the system with photonics, resulting in an increase in performance of more than an order of magnitude. By monolithically integrating photonics with electronics this large performance increase can be achieved without an associated large increase in cost.

#### 2.1.1 Ultra-Fast Analog-to-Digital Converters

With advances in CMOS technologies and parallel-computing architecture, teraflop processor systems are now a reality [17]. The true benefits of these systems can not be fully realized at present due to the limitations of analog-to-digital converters (ADC). The effective number-of-bits (ENOB) versus input signal frequency for existing ADCs, shown in Fig. 2.1, clearly illustrates how the performance of electronic ADCs are fundamentally limited by the timing jitter of the electronic clocking circuits, and the jitter performance of electronic oscillators. State-of-the-art on-chip electronic oscillators currently have a timing jitter of ~100 fs, limiting the sampling resolution of a 20 GHz

**Fig. 2.1:** Performance plot for modern electronic analog-to-digital converters showing how the 100 fs timing jitter of electronic circuits limits the resolution achievable for a given signal frequency

analog signal to ~5 ENOB. To increase the sampling resolution to > 6 ENOB for microwave signals a different low-timing-jitter source most be used, such as a femtosecond laser.

Femtosecond lasers have been shown to be very-low-noise sources, with timing jitter of ~10 fs or below [6,18]. The timing jitter of electronic oscillators, dominated by thermal noise (kT), is proportional to the square of the oscillation period ( $T_0$ ) (Eq. 2.1). This period is on the order of ~100 ps for a ~10 GHz microwave signal. In contrast, the dominant source of timing jitter for mode-locked femtosecond lasers is quantum noise ( $\hbar\omega_c$ ) and is proportional to the square of the pulse width ( $\tau$ ), which is on the order of ~100 fs (Eq. 2.2). This six order of magnitude difference between the square of the pulse width and oscillation period easily overcomes the fact that the quantum noise is significantly larger than the thermal noise (Eq. 2.3). The end result is that femtosecond lasers have a timing-jitter improvement of greater than two orders of magnitude relative to electronic oscillators (Eq. 2.4). This creates the potential of sampling 20 GHz analog signals at a resolution of 10 ENOB.

$$\frac{d}{dt} < \Delta t_{RF}^2 > T_0^2 \cdot \frac{2}{E_{\text{mode}}} \frac{kT}{t_{car}}$$

2.1

$$\frac{d}{dt} < \Delta t_{ML}^2 > \sim \tau^2 \cdot \frac{2}{E_{pulse}} \frac{\hbar \omega_c}{\tau_{cav}}$$

2.2

$$\hbar\omega_c \sim 50kT$$

$$\frac{d}{dt} < \Delta t_{ML}^2 > 10^2 * \frac{d}{dt} < \Delta t_{RF}^2 > 2.4$$

**Fig. 2.2:** Proposed electronic-photonic ultra-fast analog-to-digital converter capable of >8 ENOB for a 20 GHz input signals. Key photonic components include a low-jitter femtosecond laser, broadband modulator and filter bank.

In order to take advantaged of the low jitter of a femtosecond laser the analog signal must be processed with photonics before being digitized by electronic ADCs. Fig. 2.2 shows a proposed electronic-photonic ultra-fast ADC that takes advantage of the low timing jitter of a femtosecond laser, WDM architecture, and the high resolution of "slower" electronic ADCs, to sample a 20 GHz signal at >8 ENOB. This system starts with a mode-locked femtosecond laser emitting broadband optical pulses at a 2 GHz repetition rate. This broadband pulse then travels through a dispersive fiber that stretches the frequency spectrum in time. The spectrum then travels through a Mach-Zehnder

modulator where the input voltage (V<sub>RF</sub>) is the 20 GHz analog signal to be sampled. The modulator will imprint the analog signal as an amplitude modulation on the broadband spectrum, effectively converting the analog signal from the time domain to the frequency domain. The spectrum is then demultiplexed into N channels using a bank of microring-resonator filters with precisely spaced resonant frequencies. Each channel is then incident onto a photodetector converting the optical signal into an electrical signal. The electrical signals from the photodetectors are then digitized in parallel by "slower" high-resolution electronic ADCs. The demultiplexing of the signal allows for each frequency to be processed electronically in parallel, therefore the electronic ADCs only need to be as fast as the repetition rate of the laser (2 GHz) not the frequency of the signal (20 GHz). An added benefit of this system is that the complementary output of the modulator can also be demultiplexed and digitized to cancel nonlinearities in the system. The total sampling speed of the system is the repetition rate of the femtosecond laser multiplied by the number of channels in the filter bank.

#### 2.1.2 Many-Core Processor-to-DRAM Networks

The new trend for increasing the performance of processors is to increase the number of cores. In order to maintain the pace of processor performance increase dictated by Moore's Law, these multi-core processors will soon become many-core processors, where the number of cores will be in the hundreds to thousands. One of the greatest problems facing many-core systems is that as the number of cores increases there is a corresponding increase in the memory bandwidth requirements. Without this

Chapter 2 Background

increase in bandwidth the increase in number of cores will not result in improved application performance. The ideal solution to this problem must provide the increased memory bandwidth with reasonable power consumption and packaging costs.

One proposed solution is to use monolithic silicon photonic to create an electrooptic global crossbar. Fig. 2.3 shows the schematic of a theoretical system containing

256 cores, 16 DRAM modules, and 16 group electro-optic crossbars. The system takes

advantage of dense WDM, allowing single waveguides to carry up 128 signals utilizing

64 wavelengths of light it each direction. As the number of cores increases it is necessary

to increase the number of wavelengths to achieve functional scaling, keeping the

photonic footprint minimal. To rout a signal from a specific core to the desired DRAM

module a network of microring resonator filter banks is used. Microring resonators are

**Fig. 2.3:** Schematic of a proposed manycore-to-DRAM network consisting of 256 cores, 16 DRAM modules, and 16 group opto-crossbars. Each ring in the left image represents a bank of 16 second-order microring-resonator filters.

also used as modulators in this system to encode the bit signals onto each wavelength of light individually. The figure of merit, energy per bit, for this system is ~250 fJ/bit about a 20X improvement over electronic-only systems [3].

#### 2.2 MICRORING RESONATOR OPTICAL FILTERS

As is evident in the two examples of EPICs described above, microring resonators are essential photonic components. In addition to filtering, it is possible to make switches, narrowband modulators, delay lines, and slow-light structures out of microring resonators. In many ways improving the performance of microring resonators is as essential to the future of integrated photonics as improvements in the transistor were, and still are, to integrated electronics. Also, similarly to the transistor, material properties and fabrication methods for microring resonators need to continuously improve to keep up with the need for higher performance in increasingly demanding applications.

#### 2.2.1 General Operation

The theory for microring resonator filters was first developed in 1969, but it was not until the late 1990s that advances in fabrication methods made these devices feasible [19,20]. A single microring resonator coupled to two waveguides,  $W_1$  and  $W_2$ , is depicted in Fig. 2.4a, with multiple signals carried by different wavelengths traveling through  $W_1$ . These wavelengths will evanescently couple to the nearby microring with to  $W_2$ , transferring the signal to  $W_2$ . This is how a microring resonator can filter out a

Chapter 2 Background

Fig. 2.4: (a) Top-view diagram of a single microring acting as a drop filter. (b) Simulated transmission response of a single microring filter.

coupling strength  $\kappa_1$ . Each time a wavelength evanescently couples from a waveguide to a microring its relative phase is shifted by 90 degrees. Therefore, for wavelengths,  $\lambda_n$ , that satisfies the resonant condition in Eq. 2.5, the light will be 180 degrees out of phase with respect to the light in  $W_1$  when evanescently coupling back into  $W_1$ , resulting in deconstructive interference. This results in the coupling to the microring being enhanced for  $\lambda_n$  and suppressed for all other wavelengths. The signal carried by  $\lambda_n$  is thus transferred from  $W_1$  to the microring. Once in the microring,  $\lambda_n$  will evanescently couple

signal carried on  $W_1$  and transfer it to  $W_2$ . The operation of the microring resonator is, of course, time reversible; hence a signal carried by  $\lambda_n$  on  $W_2$  can be added to the signals traveling in  $W_1$ . This is how a microring resonator can be used as an optical add-drop filter.

$$m^*\lambda_n = 2\pi R^* n_{eff}$$

2.5

The frequency-transmission function for a single microring resonator is shown in Fig. 2.4b. The key parameters of the transmission response are the 3 dB bandwidth  $(\Delta \lambda_{3db})$ , quality factor (Q), free spectral range (FSR), finesse, drop loss, and roll-off.  $\Delta \lambda_{3db}$  is the full-width half maximum of the transmission response and is dependent on the coupling coefficients (k) between the microring and the waveguides. The Q of a microring is a measure of the filters selectivity, where  $Q=\lambda/\Delta\lambda_{3db}$ , and is an inverse sum of the internal and external Qs. The external Q is a measure of the power loss due to evanescent coupling to external photonic structures such as waveguides or other microrings. The internal Q is a measure of the power loss to internal factors such as material absorption, radiation scattering losses, and bending loss. The internal Q sets a lower limit on the achievable bandwidth of the transmission response. The FSR is defined as the spectral range between adjacent resonant frequencies of the same microring filter. This range typically defines the maximum usable frequency spectrum for the photonic systems. The FSR is typically increased by reducing the microring radius but can also be increased artificially through the Vernier effect or by using twopoint coupling to suppress some of the resonances [21,22]. The finesse of a filter is defined by the FSR/  $\Delta\lambda_{3db}$  and is another way to measure the selectivity of the filter. The

Chapter 2 Background

drop-loss is a measure of how much of the incoming signal at the resonant frequency is not transferred to the drop waveguide. For most applications it is desirable for the drop loss to be < 3 dB. Roll-off is a measure of how quickly the transmission response decays outside the 3 dB bandwidth. The roll-off can be increased by increasing the order of the filter, i.e. coupling multiple microrings in series. Fig. 2.5a shows the schematic of a second-order filter consisting of two series-coupled microrings. Fig. 2.5b illustrates the increase in roll-off of the transmission response that is obtained when the filter order is increased.

**Fig. 2.5:** (a) schematic of a second-order microring filter. (b) Simulated transmission response of first-, second, and third-order microring-resonator filters all with the same bandwidth, demonstrating the increase in role-off as filter order is increased.

#### 2.2.2 Material Selection and Fabrication Challenges

To improve the performance of microring-resonator filters it is desirable to move to higher-index-contrast materials while keeping propagation loss minimal. Early microrings-resonators were fabricated using doped glass, providing very low index contrast, and limiting the bending radius to hundreds of microns [23]. Moving to higher index contrast allows for smaller bending radii without excess bending loss. This has a two-fold benefit of increasing the FSR of the microring and reducing the overall footprint of the device. It has been shown that in silicon-on-insulator it is possible to fabricated microrings filters that have a radius of only 1.5  $\mu$ m, and a FSR of over 6 THz, without incurring a prohibitive amount of bending loss [13].

As one moves to higher-index-contrast material systems to improve filter performance the fabrication challenges increase dramatically. Propagation loss due to scattering from sidewall roughness scales with the index contrast squared. Therefore, to maintain the same drop loss when switching to higher index contrast the sidewall roughness must be significantly reduced. Also the resonant frequency sensitivity due to small dimensional changes in the average microring waveguide width and height increases substantially with index contrast. For example, for a microring resonator filter with Si as the core and SiO<sub>2</sub> as the cladding, and using the nominal waveguide cross section of 220 nm X 400 nm, the resonant frequency shifts approximately 100 GHz for every 1 nm change in average microring width. In addition to these increased sensitivities, the higher confinement of HIC materials systems means that the evanescent field of the optical mode does not extend very far from the waveguide core. Therefore, to achieve significant coupling to the microring resonator the gap between the waveguide and the microring must be a few hundreds of nanometers, or less. All of these factors mean that moving to higher index contrast results in the need for the development of fabrication methods that are optimized for the specific needs of photonic structures.

### Chapter 3

### **Fabrication of Microring-Resonators**

#### 3.1 INTRODUCTION

The challenges in fabricating integrated photonics devices are often very different than those of electronic circuits; however, people often try to make use of the same techniques for both. This approach has a number of limitations. For integrated photonics to be successful new fabrication techniques must be developed. Microring-resonator filters are a prime example on how the fabrication requirements differ substantially from those of integrated electronic circuits. For example, one of the important fabrication challenges of a transistor is scaling the size to make it faster, cheaper and consume less power. Today the transistor gate length is ~20 nm but it can vary by as much as 10% from transistor to transistor on the same chip, this is not a problem for electronics [2]. On the other hand, all of the features of microring resonators are larger than 20 nm, generally much larger than 100 nm, but they require dimensional control of 2% or better, and dimensional precision on the tens of picometer scale. A second example is that electronics are laid out using so-called Manhattan geometries, and current optical-lithography tools exploit this fact with "resolution-enhancement techniques" such as dipole and quadrupole illumination [24]. In contrast, microrings and many other photonic structures rely on smoothly varying, curved structures, and many of the resolution-enhancement techniques used for Manhattan geometries sacrifice the quality of curved and off-axis features. These are just two of the many differences in the challenges for fabricating integrated photonics compared to integrated electronics.

To overcome these challenges each step of the fabrication process has been optimized for the fabrication of microring-resonator filters while still utilizing some of the same tools that have been developed primarily for the semiconductor industry. During the experiments, two different types of filters were fabricated one using siliconrich silicon nitride ( $SiN_x$ ) (n=2.19 @ 1550 nm) and the other using crystalline silicon (n=3.52 @ 1550 nm) as the core material. Scanning-electron-beam lithography (SEBL) with an optimized writing strategy was used to define the features in an electron-beam resist. The rest of the process optimizations included electron-beam resist choice, exposure dose, etch mask material, and etching recipes.

# 3.2 SILICON-RICH SILICON NITRIDE FILTERS

Silicon-rich silicon nitride ( $SiN_x$ ) is also commonly known as low-stress nitride and is widely used in the fabrication of membrane-based and MEMS devices. The reason that it is chosen as the core material for these experiments over stoichiometric silicon nitride ( $Si_3N_4$ ) is two fold. First, stoichiometric  $Si_3N_4$  deposited using low-pressure chemical-vapor deposition (LPCVD) is highly stressed, limiting its maximum thickness to ~300 nm. This combined with its lower index of refraction (n=1.98 @ 1550 nm) limits the achievable FSR to ~1 THz, making it unsuitable for most EPIC systems.  $Si_3N_4$  made

using plasma-enhanced chemical-vapor deposition (PECVD), where the stress can be controlled allowing for thicker films and slightly larger FSR, contains a large amount of N-H bonds that cause significant optical absorption around 1520 nm. These problems are not present in SiN<sub>x</sub> because it is produced using LPCVD at high temperature with a very slow deposition rate (~1nm/min), allowing all N-H bonds to anneal out during deposition. Its stoichiometery is controlled to minimize internal stress, which enables thicker films to

Fig 3.1: (a) Top-view scanning-electron micrograph of fabricated air-clad  $SiN_x$  filter design. (b) Designed and measured transmission response of air-clad filter. (c) Top-view scanning-electron micrograph of fabricated oxide-clad  $SiN_x$  filter design before cladding. (d) Designed and measured transmission response of oxide-clad filter.

be grown. When combined with its higher index of refraction of 2.19 at 1550 nm FSRs greater than 2 THz can be achieved.

Fig. 3.1 shows two different SiN<sub>x</sub> filters as well as their designed and measured transmission responses. These designs were created by Milos Popovic and Anatoly Khilo using rigorous numerical eigenmode and 3D finite-difference time-domain (FDTD) simulations [25]. The first filter design is a second-order air-clad microring-resonator filter with a designed FSR of 2.5 THz and a 3 dB bandwidth of 50 GHz. The second design is a second-order oxide-clad microring-resonator filters with a designed FSR of 2.0 THz and 3 dB bandwidth of 25 GHz. The reason for using second-order microring resonator filters is further discussed in Chapter 6.

The filter designs assume a propagation loss of 7.5 dB/cm, which was calculated by measuring the transmitted powers through so-called "paperclip" structures of different lengths, as explained in Appendix A. The designed and measured transmission responses agree very well for the air-clad design, indicating that the actual fabricated dimensions and propagation loss are very close to the design. The measured transmission response of oxide-clad filter, on the other hand, does not match perfectly with the design. The measured response has both a wider 3 dB bandwidth and a larger drop loss than expected. This combination of differences can only be explained by a larger propagation loss than expected. The SiN<sub>x</sub> films used for the two fabrications were deposited by the same tool but over 3 years apart. Although the stress of the deposited SiN<sub>x</sub> is measured often to confirm low-stress, the optical properties are not monitored and are found to change significantly over long periods of time, as observed here.

#### 3.2.1 $SiN_x$ Filter Fabrication with PMMA

Poly(methyl methacrylate) (PMMA) was chosen as the electron-beam resist for the fabrication of SiN<sub>x</sub> microring resonators because of its high contrast and process reliability. The fabrication process shown in Fig. 3.2 starts by growing a 3 μm-thick thermal-oxide layer on a silicon wafer. Next 400 nm of SiN<sub>x</sub> is deposited using LPCVD at a temperature of 700°C. The low deposition rate, ~1 nm/min, of the nitride combined with the high processing temperature results in a nitride film that does not contain any Si-

Fig. 3.2: Basic fabrication process for  $SiN_x$  filters, using PMMA and lift-off. A scanning-electron micrograph of a fabricated waveguide cross-section is shown in the bottom right image

H and N-H bonds. Next 200 nm of PMMA is spun on the wafer using a spin speed of 4500 rpm and baked in a convection oven at 180°C for 1 hr. Then a 60 nm-thick layer of AquaSAVE, a conducting polymer made by Mitsubishi Rayon, is spun on and baked on a hotplate for 1 min at 90°C. When properly grounded, this conductive layer eliminates charging during SEBL, which can cause beam-placement errors. The SEBL step was performed using a Raith 150 system operating at an accelerating voltage of 30 keV. The exposure dose used was 285  $\mu\text{C/cm}^2$  and 333  $\mu\text{C/cm}^2$  for the air-clad and oxide-clad designs, respectively. After exposure the AquaSAVE was removed with a rinse in deionized (DI) water. The PMMA was developed by immersing in a solution of 2 parts isopropyl alcohol (IPA) and 1 part methyl isobutyl ketone at 21°C for 60s, followed by immersion in an IPA bath for 60s. The sample was then thoroughly rinsed with IPA and blow dried with a N<sub>2</sub> gun. Next, a 40 nm-thick film of nickel was evaporated on the developed PMMA pattern. Using N-methyl-2-pyrrolidone at 80°C, the remaining PMMA was removed, lifting-off the unwanted nickel and forming a nickel hardmask of the desired pattern. The nickel pattern was then transferred into the SiN<sub>x</sub> using a reactive-ion-etching (RIE) process with a CHF<sub>3</sub>-O<sub>2</sub> gas mixture, optimized to give smooth vertical sidewalls. For the air-clad design a second RIE step was performed, using CHF<sub>3</sub> gas only, to etch an additional 200 nm into the SiO<sub>2</sub> undercladding layer. After etching, the nickel hardmask was removed using Transene TFB nickel etchant. The samples were then cleaned with a mixture of 5 parts DI water, 1 part H<sub>2</sub>O<sub>2</sub> and 1 part NH<sub>4</sub>OH at 80°C for 20 min. The oxide-clad design was then clad with 2.0 μm of HSQ using an optimized annealing process described in Chapter 7.

### 3.2.2 Reactive-Ion-Etching Optimization

One of the critical characteristics of microring resonators is that they require rigorously vertical sidewalls. This is especially important in the coupling-gap region for two reasons. One is that slanted sidewalls will affect the evanescent-coupling coefficient, changing the bandwidth of the filter. The second reason is that the slanted sidewalls can cause polarization mixing to occur. The microring filter designs are highly polarization dependent, and any mixing of polarization states at the coupling region will greatly reduce performance. Therefore, it is important to make the sidewalls as vertical as possible; this can be done by optimizing the RIE process.

To achieve highly vertical sidewalls during RIE, two things are desirable: high selectivity between the masking material and the material to be etched, and the formation of a sidewall passivation layer. Since a Ni hardmask is used for this RIE process the selectivity between the  $SiN_x$  and the mask is extremely high, ~40:1. It is also possible to form a passivation layer on the  $SiN_x$  surface by adding hydrogen into the etch recipe. This is done by using CHF<sub>3</sub> gas. Although the passivation layer forms on all surface of the  $SiN_x$ , ion bombardment helps to selectively remove it from horizontal surfaces, leaving it only on vertical surfaces, i.e. the sidewalls. However, if the sidewall passivation layer grows during the etch or is removed by the etch the resulting sidewall profile will slant out or in, respectively. By controlling the amount of  $O_2$  in the RIE process it is possible to control the growth rate of the sidewall passivation layer. If too little  $O_2$  is used the sidewall passivation layer will grow during the etch, resulting in the sidewall profile to slant outward (Fig. 3.3a). Alternatively, if too much  $O_2$  is added, the

Fig 3.3: Sidewall profile of  $SiN_x$  in the gap area for different RIE recipes: (a) outward sloping sidewalls from too little  $O_2$ , (b) near vertical sidewall for optimal  $O_2$  concentration, and (c) inward sloping/keyhole profile sidewalls for too much  $O_2$ .

sidewall passivation layer will be removed as soon as it develops, resulting in a sidewall profile that slants inward, forming a keyhole profile in the gap region (Fig. 3.3c). If the correct ratio of CHF<sub>3</sub> and O<sub>2</sub> is selected it is possible to achieve a steady state thickness, resulting in vertical sidewalls. For this process it was found that a ratio of 3.5:1 CHF<sub>3</sub>:O<sub>2</sub> resulted in nearly vertical sidewalls (Fig. 3.3b).

## 3.3 SILICON FILTERS

In addition to  $SiN_x$ , microring-resonator filters were also fabricated using crystalline Si as the core material. There are advantages and disadvantages to using Si over  $SiN_x$ . The main advantage is that Si exhibits very low loss from optical absorption at the

wavelengths of interest. Being a stoichiometric crystalline material it has well known and repeatable optical properties. The  $SiN_x$  material, on the other hand, is not stoichiometric or crystalline, and since the deposition parameters are optimized for low tensile stress, its optical properties, including absorption and refractive index, can vary significantly from batch to batch. Another advantage of Si is that it has a higher index of refraction, allowing for smaller radii and denser integration. However, with the increased refractive index comes an increased sensitivity to dimensional changes and sidewall roughness making fabrication much more challenging.

To partially overcome the problems associated with the higher index of Si, we use a filter design having a low-aspect-ratio waveguide cross-section. This low-aspect-ratio waveguide lessens the frequency sensitivity of the microring to changes in waveguide width at the price of an increased sensitivity to the height. This is an acceptable trade-off since the height can be controlled and measured very accurately through oxidative thinning and ellipsometer measurements. Another benefit of this low-aspect-ratio waveguide is that the propagation loss is less sensitive to sidewall roughness. The designed and measured transmission responses for this improved Si filter are shown in Fig. 3.4.

For this filter design the propagation loss in the Si was assumed to be 3 dB/cm. The drop loss of the measured response is lower than the design, indicating, that the actual propagation loss is less than expected. By measuring the Q of a weakly-coupled, large-radius microring resonator the propagation loss was calculated to be ~2.5 dB/cm (see Appendix A). The overall shape of the filter response agrees very well with the

**Fig. 3.4:** (a) Top-view scanning-electron micrograph of Si filter design before overcladding with HSQ. Arrows on the left indicated the gap dimensions. (b) Designed and measured transmission response of Si filter.

design indicating a high level of dimensional accuracy. The oscillations seen in the measured thru and drop responses are a Fabry-Perot effect due to reflections off the waveguide end facets, not a characteristic of the filter.

#### 3.3.1 Silicide Formation

The first attempt at fabricating Si filters used the same fabrication process developed for the SiN<sub>x</sub> filters with a slightly different CHF<sub>3</sub>:O<sub>2</sub> gas ratio. The fabrication process visually appeared to work, but when the devices were tested the loss was measured to be very high ~70 dB/cm. This very large loss is an order of magnitude higher than what would be expected from sidewall roughness alone, measured to have a variance of 3.0 nm<sup>2</sup>. One possible explanation for this loss would be if NiSi<sub>x</sub> was forming from a reaction between the Ni hardmask and the Si. This was thought to be

highly unlikely since there was a 40 nm-thick barrier layer of thermal SiO<sub>2</sub> between the Ni and the Si (Fig. 3.5). At the highest processing temperature used when the Ni was on the wafer, ~150°C, the Ni would be expected to diffuse less than an angstrom into the SiO<sub>2</sub> barrier layer. Also it is important to note that this highest processing temperature is

**Fig. 3.5:** Cross-section diagram of Si waveguide after RIE showing the SiO<sub>2</sub> diffusion barrier between the Ni hardmask and Si waveguide.

still below the formation temperature of NiSi<sub>x</sub>. Nevertheless, it was decided that the loss must be coming from using a Ni hardmask. To further test this theory various metals were used as a hardmask and the propagation loss and sidewall roughness measured. From Table 3.1 it is seen that the propagation loss decreased as the silicidation temperature of the hardmask metal increased, further supporting the idea of silicide formation from the hardmask. Table 3.1 also shows that there is no correlation between the measured propagation loss and the sidewall roughness for the various metals, confirming that another loss mechanism is dominate. To verify the formation of silicide, a cross-section of the waveguide that had been formed using a Pd hardmask was prepared for scanning-transmission electron microscope (STEM) analysis. The Pd sample was

chosen since it had both the highest loss and lowest sidewall roughness. The cross-section STEM micrograph of the waveguide is shown in Fig. 3.6(a) with boxes displaying different areas that were analyzed by energy-dispersive x-ray spectrometry (EDS). The EDS spectra for each sample point are shown in Fig. 3.6(b).

These spectra confirm the presence of Pd in the Si waveguide 1-2 nm from the sidewall, but not at 8-9 nm from the sidewall. The presence of the Pd confirmed that the metal hardmask was contaminating the Si waveguide, resulting in the excess loss. However, the location of the Pd only on the sidewalls showed that the Pd was not diffusing though the SiO<sub>2</sub> barrier layer. A probable explanation is that the Pd was sputtered from the mask and deposited on the sidewall with enough energy to form a silicide. The metals with higher silicidation-formation temperatures are also sputtered, but do not have enough energy to bond to the sidewall and are later removed at the same time as the hardmask. Although some metals did not appear to form a silicide; these metals all produced very rough edges making them non-ideal for photonics. As a result of this investigation, we changed the process from using PMMA with a lift-off step to using HSQ (a negative tone inorganic electron-beam resist) as the resist and mask material.

**Table 3.1 Measured Results for Different Metallic Hardmasks**

| Metal hard mask                                    | Ni  | Pd  | Co  | Cr  | Fe-Ti <sup>c</sup> | Fe  |

|----------------------------------------------------|-----|-----|-----|-----|--------------------|-----|

| Silicide formation temperature (°C)                | 200 | 200 | 270 | 400 | 350 (Ti)           | 400 |

| Roughness variance <sup>a</sup> (nm <sup>2</sup> ) | 3.0 | 2.8 | 4.8 | 7.7 | 3.1                | 4.2 |

| Propagation loss <sup>b</sup> (dB/cm)              | ~70 | >70 | >65 | <15 | <15                | <15 |

<sup>&</sup>lt;sup>a</sup> Results for nonoptimized lift-off.

<sup>&</sup>lt;sup>b</sup> Loss for Ni sample measured on ring resonator. Loss for other samples measured on straight waveguides.

<sup>&</sup>lt;sup>c</sup> Fe-Ti refers to a 5 nm Ti cap on top of 45 nm of Fe to prevent corrosion of Fe during lift-off.

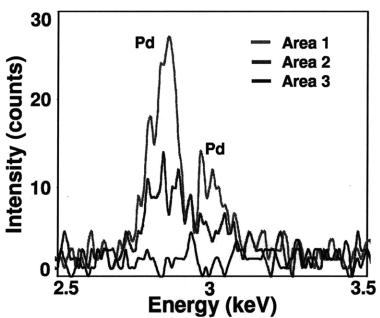

**Fig. 3.6:** (a) scanning-transmission-electron micrograph of top corner of Si waveguide (whole waveguide shown in inset). Highlighted areas are locations where energy-dispersive x-ray spectrometry was performed. (b) EDS spectrum for corresponding points showing the location of Pd contamination.

# 3.3.2 Si Filter Fabrication with HSQ

The fabrication process shown in Fig 3.7 begins with a SOI wafer having a 3  $\mu$ m-thick buried-oxide layer and a 220 nm-thick Si-device layer. The device layer was

thinned to 105 nm using thermal oxidation followed by a hydrofluoric-acid (HF) dip to remove the oxide. The exact thickness was measured with an ellipsometer. Next, the wafer was spin coated with a 65 nm-thick layer of HSQ, a negative electron-beam resist, and baked at 90°C for 60s on a hotplate (HSQ was developed as a spin-on glass; once baked it resembles SiO<sub>2</sub>). Unlike the SiN<sub>x</sub> fabrication process, there is no need for a conduction layer since the sheet resistance,  $10\text{--}30^{\Omega}/_{\square}$ , of the SOI wafer is sufficient to prevent the build up of charge during SEBL. The HSQ was exposed with the same SEBL system and accelerating voltage used previously for PMMA. The exposure dose for HSQ was 1500  $\mu$ C/cm<sup>2</sup>, significantly larger than what is used for PMMA. The exposed HSQ

Fig. 3.7: Basic fabrication process for Si filters using HSQ resist and HBr etching. Cross-section scanning-electron micrograph of fabricated waveguide is shown in the bottom right image.

was developed for 2 min. in a 25% solution of tetramethylammonium hydroxide (TMAH) and then rinsed with DI water. The HSQ pattern was then transferred to the Si layer using RIE with HBr gas. The selectivity between the Si and HSQ mask was measured to be 11:1 for this etch. The remaining HSQ mask was removed using an SC-1 clean [26] followed by a 4 min dip in 0.125% solution of HF. Lastly, the fabricated Si devices were overclad with 1 μm of HSQ and annealed for 1 hr at 400°C in an O<sub>2</sub> ambient.

### 3.4 EXPOSURE OPTIMIZATION

The most critical step in the fabrication of the SiN<sub>x</sub> and Si microring-resonator filters is the SEBL exposure. There are many variables that can be controlled in the SEBL process, including: electron dose, dimensional biasing, and writing strategy. For photonic devices it is important to optimize the exposure dose and e-beam resist to minimize line-edge roughness. This roughness will be transferred to the device sidewalls during further processing, resulting in increased propagation loss. Since the exposure dose is optimized for roughness, not dimensional accuracy, biasing must be used to achieve accurate dimensions. Also of great concern is pattern fidelity, i.e., how closely the fabricated microring represents the imputed circular pattern. Errors in the pattern fidelity can occur due to deflection errors, beam blanker timing errors, and intrafield distortion of the write field. By employing an optimized writing strategy it is possible to minimize these errors.

### 3.4.1 Roughness Minimization

For microring resonators, as well as almost all other integrated-photonic devices, it is very important to minimize sidewall roughness in order to minimize scattering losses. Sidewall roughness arises primarily from the line-edge roughness (LER) of the etching mask, which in turn depends on the SEBL exposure either indirectly, when using PMMA and a lift-off, or directly, when using HSQ.

For the optimization of the dose for the SiN<sub>x</sub> designs, using PMMA resist, a series of electron-beam doses were used to expose the filter design and nearby waveguides. The resist was developed, Ni deposited and a lift-off performed. The Ni hardmasks formed for each dose were then imaged with a scanning-electron microscope (SEM). Each imaged pattern, examples of which are shown in Fig 3.8, fall into one of five categories: not cleared, under exposed, optimal dose, over exposed and fused gap. In the not-cleared regime the dose is so low that after development there is still a thin layer of PMMA at the bottom of the exposed feature. In this case when the metal is evaporated there is no way for it to make contact with the substrate, so the entire defined feature is removed during lift-off. In the under-exposed regime, where the resist has been cleared over most of the feature except for small footings at the edges, these footings get covered with a thin layer of metal that is connected to the metal layer at the bottom of the trench. During lift-off the PMMA footing is removed by the solvent but the thin layer of metal remains attached to the mask. This thin layer will either fold over on top of the hardmask or fold down onto the SiN<sub>x</sub>. This layer acts as a etch mask during at least a portion of the

Fig. 3.8: Scanning-electron micrographs of Ni on  $SiN_x$  after lift-off for various exposure doses. (a) An under-exposed sample results in a thin coating of metal on the resist sidewalls that remains after lift-off. (b) Optimal exposure dose resulting in minimal sidewall roughness. (c) An over-exposed sample resulting in a thin secondary Ni line at the edges. (d) Zoom-in of an over-exposed sample clearly showing the double line.

etch process until it is completely sputtered away, adding to the sidewall roughness. With an optimally exposed dose the PMMA sidewalls are completely vertical or have a very slight undercut. In this case no metal is deposited on the PMMA sidewalls, resulting in a hardmask that has the same roughness as the PMMA resist. As one increases the dose even further the over exposed regime is entered. In this regime the PMMA profile has a significant undercut of a few nanometers. During evaporation the metal that hits the  $SiN_x$  surface has enough surface mobility to diffuse into this undercut area. This

creates a secondary thin mask that is seen in the SEM image as a faint double line (Fig. 3.8d). This thin secondary hardmask will sputter away during the etch process, once again increasing the sidewall roughness. If the dose is increased even further the coupling gap between the waveguide and the microring will fuse due to proximity effects, ruining the filter. The range of doses that fall between the under-exposed and over-exposed regimes makes up the exposure window. For PMMA, this window is quite large, †/-20%. Using the optimal dose the sidewall roughness of the SiN<sub>x</sub> microrings and waveguides is measured to have a variance of ~3.0 nm<sup>2</sup>,

For the Si-based photonic devices, fabricated using HSQ resist, another range of doses were tested. Once again the results could be divided into five regimes: incomplete crosslinking, under exposed, optimum dose, over exposed and fused gaps (Fig. 3.9). When the crosslinking is incomplete the HSQ is unable to withstand the developer. The under exposed regime is characterized by moderately rough edges. The optimal dose has

Fig. 3.9: Top-view scanning-electron micrographs of HSQ on Si after development for various exposure doses. (a) An under-exposed sample results in slightly rough sidewalls. (b) Optimal exposure dose resulting in minimal sidewall roughness. (c) An over-exposed sample resulting in a large footing and roughness

extremely smooth edges with a measured roughness variance of 1.8 nm<sup>2</sup>. As the dose is increased into the over exposed regime a significant footing develops at the bottom of the HSQ features. This footing has an extremely high roughness as seen in Fig 3.9c. Once again if the dose is increased too much the coupling gap between the ring and waveguide will fuse. Although the sidewall roughness at the optimal dose achievable with HSQ is lower than for PMMA, the exposure window is also smaller, \*/-8%, but still acceptable.

## 3.4.2 Absolute Dimensional Control and Pattern Fidelity

Since the exposure dose is optimized to reduce sidewall roughness, not for replicating absolute dimension of the design, it is important to pre-bias all of the dimensions so that they are correct at the end of fabrication. This places a high level of importance on how well one can measure the dimensions of the straight (bus) waveguide width, the microring waveguide, and the coupling gaps. Typically, measurements performed using an SEM can obtain a measurement accuracy of only 5%, which, for the near-micron-size features of the microring resonators, is substantial. In an SEBL system one can calibrate the deflection of the electron-beam to the movement of the interferometric stage. This can theoretically improve the accuracy of SEM measurements to below 1 nm, but in practice the accuracy is limited to ~5 nm due mechanical vibrations. Using this method, all of the critical features of each microring-filter design were measured after a test fabrication run and then biased appropriately in the final layout to achieve the correct dimensions. After biasing, the critical dimensions are no more than 6 nm off from the design as seen in Table 3.2.

**Table 3.2 Dimensional Accuracy of Filter Parameters**

|                     | SiN <sub>x</sub> filter, air clad |          | SiN <sub>x</sub> filter, oxide clad |      |          | Si filter, oxide clad |      |          |       |

|---------------------|-----------------------------------|----------|-------------------------------------|------|----------|-----------------------|------|----------|-------|

|                     | Bias                              | Measured | Error                               | Bias | Measured | Error                 | Bias | Measured | Error |

| Ring width (nm)     | -30                               | 897      | -3                                  | -36  | 802      | +2                    | -72  | 602      | +2    |

| Bus width (nm)      | -30                               | 700      | 0                                   | -42  | 602      | +2                    | -72  | 501      | +1    |

| Gap, bus-ring (nm)  | 0                                 | 166      | +4                                  | 0    | 508      | -2                    | 0    | 340      | -2    |

| Gap, ring-ring (nm) | -6                                | 394      | +4                                  | -12  | 926      | -4                    | -6   | 703      | -5    |

In addition to making sure that the absolute dimensions of the microring are accurate it is also important to make sure that the overall shape of the microring filter is correct. This has two key components, one is that the overall shape of the microring be as close to circular as possible, and second is that both microrings in the same filter be identical or at least have identical resonant frequencies. To ensure circular shape of the microring it is important to optimize the SEBL writing strategy. This was first done by Tymon Barwicz and is outlined in detail in his thesis [27]. I feel it is important to briefly explain it again here because of how critical it is to the fabrication of high quality microring-resonator filters.

The first optimization is the scan speed. In a vector scan SEBL system a beam blanker controls when the beam is on and off. The beam will be blanked and driven to a point near the starting point of the vector to be scanned. Once the beam position reaches the starting point of the vector it is unblanked and scanned continuously to the end point, exposing the resist along the vector. When the beam has reached the ending point the blanker is reactivated halting the exposure of the resist. With this method any timing error in the blanking and unblanking of the beam will result in a positional error in the exposure. By slowing down the writing speed the same timing error in the beam blanker

will result in a smaller positional error in the exposed feature. There are multiple ways to decrease the scan speed in the Raith 150 system, including decreasing the beam current (smaller aperture) and increasing the spacing between vector scans.

The second optimization is the scan algorithm. In the Raith 150 it is possible to expose a given feature using an area, a point or a line scan. When using an area scan to expose a microring the pattern generator of the Raith 150 will split up the microring shape into a series of boxes and write each one using a raster scan. This results in the majority of the beginnings and endings of each scan, where most placement errors take place, to be located at the edges of the microring, the place of most concern. The point scan method, where the beam exposes the ring on a point by point basis is not practical since there is a finite settling time before and after each point. Given that each ring contains approximately 1 million points this quickly adds up. The line scan is ideal for circular structures because it allows one to have both the beginning and ending of each scan inside the exposed pattern, thereby decreasing the effect of beam-placement errors on the microring shape. By writing a group of concentric circles using these line scans it is possible to exposes a circle with a desired width. Also, by randomizing the beginning

**Fig. 3.10:** Schematic demonstrating the optimum SEBL writing strategy for a microring resonator.

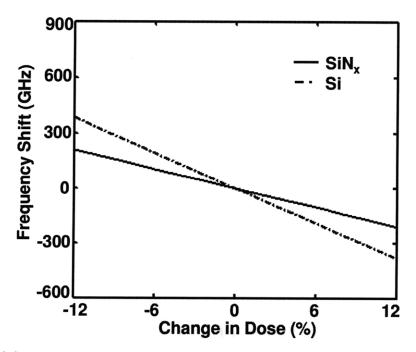

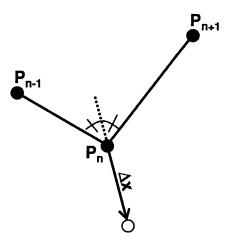

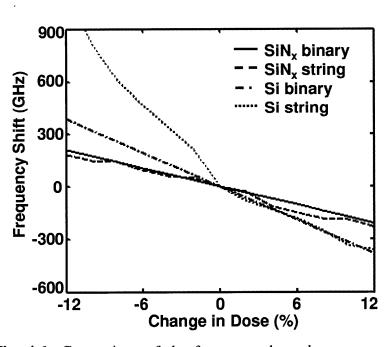

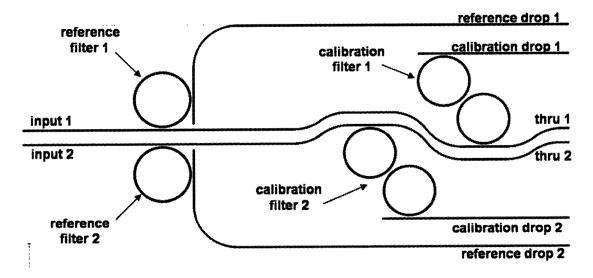

and ending points of the exposed concentric circles it is possible to distribute the deviation in the effective dose due to placement errors over the circumference of the microring, lessening their overall effect. This ideal writing strategy for the microring is sketched in Fig. 3.10, where the dots represent the starting and stopping points of each circular scan.