## An Energy Efficient AES Engine with DPA-Resistance

by

Hye Won Chung

B.S. in Electrical Engineering and Computer Science Korea Advanced Institute of Science and Technology, 2007

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

September 2009

© Massachusetts Institute of Technology 2009. All rights reserved.

## ARCHIVES

Author .... Department of Electrical Engineering and Computer Science September 4, 2009 Certified by ...... Anantha P. Chandrakasan Joseph F. and Nancy P. Keithley Professor of Electrical Engineering Thesis Supervisor Accepted by ..... Accepted by ..... Arthur C. Smith Chairman, Department Committee on Graduate Students

| M/ | ASSACHUSETTS INSTITUT<br>OF TECHNOLOGY | Ē |

|----|----------------------------------------|---|

|    | SEP 3 0 2009                           |   |

|    | LIBRARIES                              |   |

$\mathbf{2}$

#### An Energy Efficient AES Engine with DPA-Resistance

by

#### Hye Won Chung

Submitted to the Department of Electrical Engineering and Computer Science on September 4, 2009, in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering and Computer Science

#### Abstract

The advent of portable electronics which transmit and receive sensitive data via wireless communication have led to interest in the design of energy-efficient security engines. The hardware implementation of cryptographic algorithms, however, leaks side-channel information about the operations they process. Differential Power Analysis (DPA) is one of the most powerful attacks to disclose secret key of the engine.

This thesis proposes an energy efficient AES-128 engine which is resilient to DPA attacks. A proposed design adopts extensive parallelism and voltage scaling to simultaneously achieve energy efficiency and throughput requirement. Optimized 128-bit architecture and 16 S-boxes placed in the encryption datapath allow the parallel operation of 16 bytes of encryption data at supply voltages in the subthreshold region while maintaining more than tens of Mbps throughput rate. The energy efficient AES core, which does not incorporate techniques to mitigate DPA attack, can operate at 0.35V with 54.12pJ/encrypt. and 64.6Mbps.

Before developing countermeasures against DPA, a previously suggested DPA attack methodology in [1] is studied and modified to disclose secret key of our system. The transition power of register is estimated by using the byte-oriented reverse algorithm of AES with the knowledge of a ciphertext and a guess of a secret key. Correlation between the power estimate and the power measurement discloses 12 key bytes (among 16) within 20K encryption runs.

A newly proposed AES architecture which balances the Hamming weight of register input can protect the system from DPA attacks. The secured core has been subjected to 100K encryptions,  $33 \times$  more than the number of runs at which attack can disclose a secret key of the unprotected core, but none of its secret key have yet been disclosed. When running the encryption core at 0.4V and 10MHz, power increases by  $2 \times$  compared to the unprotected core. Maximum throughput at 1.0Vis reduced by 2/3 for protected core compared with the unprotected core. This IC performance overhead comes at the cost of the increased security.

Thesis Supervisor: Anantha P. Chandrakasan Title: Joseph F. and Nancy P. Keithley Professor of Electrical Engineering

## Acknowledgments

First, I would like to thank my research advisor, Professor Anantha Chandrakasan, who led me into this exciting research project on security processor design. I really appreciate that he gave me much freedom to develop this project in an interesting direction, and always provided me invaluable insights and inspirations which guided into fruitful outcomes. Thanks to his patience and support, I have been able to enjoy my work and to learn the way of thinking and conducting research in this area.

The past two years at MIT was really great time since I could work with the brilliant and interactive Ananthagroup members. I would like to thank Joyce who has been a wonderful mentor since the beginning of my graduate year. She answered all my questions about CAD tools and design flows, and gave me invaluable comments on my work. Special thanks to Masood, Vivienne, Daniel, Patrick and Payam for all their help in the struggle to tame the CAD tools, to Bonnie and Yildiz for their wonderful jobs as social chairs (I will miss the homemade brownies!), to Marcus and Courtney for getting through the first two years together with helping each other, and to Margaret for making all the paper work run smoothly. Many thanks to all current and former members of Ananthagroup.

My life would have been less colorful without my wonderful friends. Shin Young, thanks for listening my daily rants, and sharing exciting experiences at our new hometown, in Boston. Jessie, thanks for being there for the good times and the bad. Hwajung, we've known each other for more than 10 years! I've been so fortunate to share my dreams and thoughts with such a good friend like you for a long time. Oshanis, thanks for constant reminders to exercise more. Thanks to my KAIST friends for always being on my side. I would also like to thank Korean EECS at MIT for all their helps and advices throughout my life here.

I am grateful to Pastor Dae Sung Choi and his wife Young Mi Choi for their pray and support.

Finally, I would like to thank my parents, Ki Gon Chung and Seung Eem Baek, and my sister, Hye Jin Chung for their constant support and love to me.

# Contents

| 1        | Introduction |         |                                                              |    |  |  |

|----------|--------------|---------|--------------------------------------------------------------|----|--|--|

|          | 1.1          | Advar   | aced Encryption Standard                                     | 16 |  |  |

|          |              | 1.1.1   | Algorithm Specifications                                     | 16 |  |  |

|          |              | 1.1.2   | Area, Delay, and Power Characteristics of Implementations of |    |  |  |

|          |              |         | S-box                                                        | 19 |  |  |

|          | 1.2          | Differe | ential Power Analysis                                        | 20 |  |  |

|          |              | 1.2.1   | DPA Attack Methodology                                       | 21 |  |  |

|          |              | 1.2.2   | Previous Works to Defeat DPA Attacks                         | 23 |  |  |

|          | 1.3          | Thesis  | Contribution and Organization                                | 25 |  |  |

| <b>2</b> | Des          | ign of  | an Energy Efficient AES Engine                               | 27 |  |  |

|          | 2.1          | AES I   | Engine Specifications for Energy-Constrained Applications    | 28 |  |  |

|          | 2.2          | Minim   | nizing Energy Consumption                                    | 29 |  |  |

|          |              | 2.2.1   | Minimum Energy Point                                         | 30 |  |  |

|          |              | 2.2.2   | Parallelism and Subthreshold Operation                       | 32 |  |  |

|          | 2.3          | Propo   | sed Architecture                                             | 35 |  |  |

|          |              | 2.3.1   | Previous Works                                               | 36 |  |  |

|          |              | 2.3.2   | Architecture Optimizations                                   | 39 |  |  |

|          |              | 2.3.3   | Block Optimizations                                          | 41 |  |  |

|          | 2.4          | IC Per  | rformance Simulation Results                                 | 42 |  |  |

| 3        | DP.          | A Resi  | stance Test                                                  | 47 |  |  |

|          | 3.1          | DPA A   | Attack Methodology                                           | 47 |  |  |

|   |               | 3.1.1 Previous work for DPA attack                              | 48 |

|---|---------------|-----------------------------------------------------------------|----|

|   |               | 3.1.2 Modification in Power Estimation                          | 50 |

|   | 3.2           | DPA Attack Measurements and Results                             | 54 |

|   |               |                                                                 |    |

| 4 | $\mathbf{AE}$ | S Engine with Resistance to DPA Attacks                         | 59 |

|   | 4.1           | Idea Behind the Proposed DPA Protection Techniques              | 60 |

|   | 4.2           | Architecture of AES Engine with DPA-Resistance                  | 61 |

|   | 4.3           | DPA Attack Measurements and Results                             | 63 |

|   | 4.4           | IC Performance Comparison between Protected and Unprotected AES |    |

|   |               | Engines                                                         | 64 |

| 5 | Cor           | nclusion                                                        | 69 |

# List of Figures

| 1-1 | State array representation of input and output $[2]$                       | 17 |

|-----|----------------------------------------------------------------------------|----|

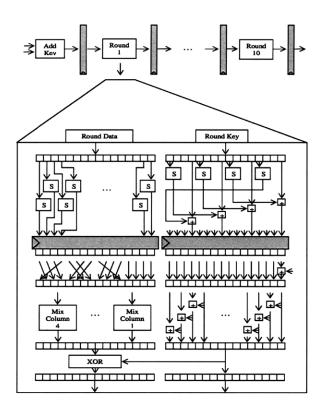

| 1-2 | Block Diagram of the Advanced Encryption Standard (AES) algorithm          | 18 |

| 1-3 | Current reference (at the top) and three DPA traces - the first trace      |    |

|     | with correct key guess and following two traces with incorrect guesses [3] | 23 |

| 2-1 | Model (lines) versus simulation (makers) of FIR filter show the mini-      |    |

|     | mum energy operation point and the contribution from dynamic and           |    |

|     | leakage energy. Inset shows $I_{leak}$ and $T_D$ effect on $E_L$ [4]       | 32 |

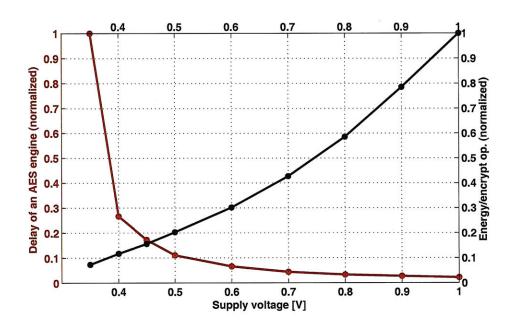

| 2-2 | Normalized delay (red line) and energy (black line) of a S-box with        |    |

|     | respect to supply voltage                                                  | 34 |

| 2-3 | Architecture of 8-bit AES module [5]                                       | 37 |

| 2-4 | Maximizing throughput of AES with inner and outer round pipelining         |    |

|     | [6]                                                                        | 39 |

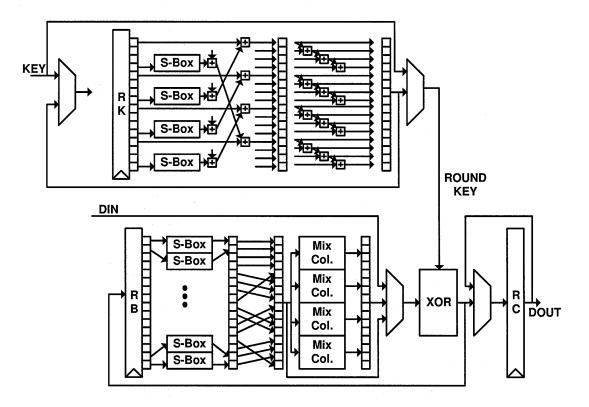

| 2-5 | Parallel architecture of AES hardware [1]- There exits two datapaths.      |    |

|     | One is for round key generation (top), and the other is for round trans-   |    |

|     | formation of encrypting data (bottom).                                     | 40 |

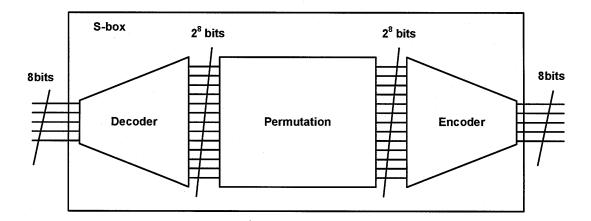

| 2-6 | Diagram of the S-box with the decoder, permutation, and encoder            |    |

|     | block [7]                                                                  | 42 |

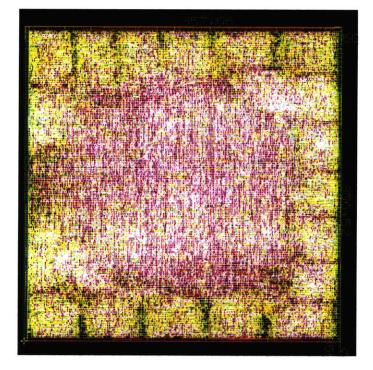

| 2-7 | Layout of energy-efficient AES engine                                      | 43 |

| 2-8 | Normalized delay (red line) and energy (black line) of the AES engine      |    |

|     | with respect to supply voltage.                                            | 44 |

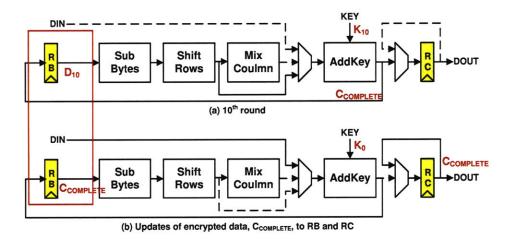

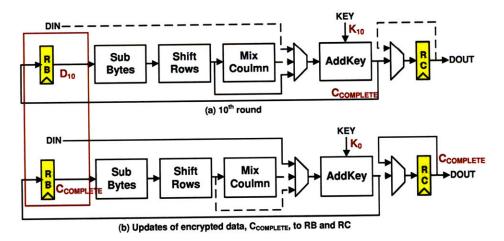

| 3-1 | AES core [1]: round 10 (top); and round 10+1 (bottom). Encryption          |    |

|     | data flows through the solid lines at each round                           | 48 |

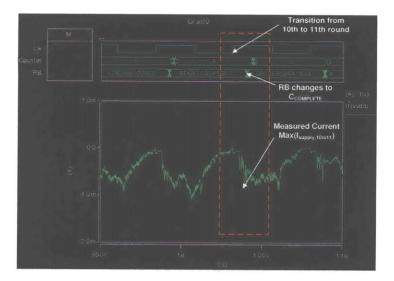

| 3-2 | Logic transition of CLK, Counter, RB out signals (top) and transient measurement of core supply current (bottom) near $10^{th}$ to $11^{th}$ round                                                                                                                                                                                                                                                                                                                                        |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | transition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51 |

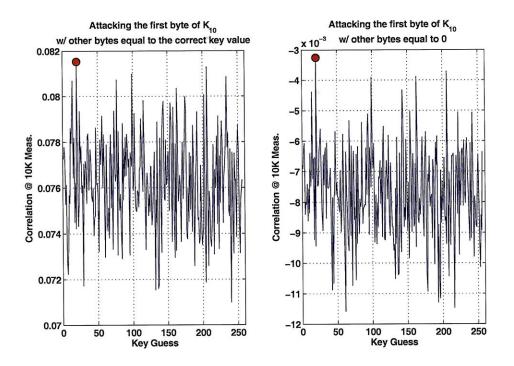

| 3-3 | Correlation coefficients vs. 256 key guess of $K_{10}[0]$ at 10K encryption<br>runs. $(K_{10}[1]K_{10}[15])$ is set to correct key values (left), and is set<br>to $(00)$ (right). Depending on the assumption of $(K_{10}[1]K_{10}[15])$ ,<br>correlation has the different bias. The red marker in the graphs shows<br>the correct key $K_{10}[0]$ of AES engine                                                                                                                        | 52 |

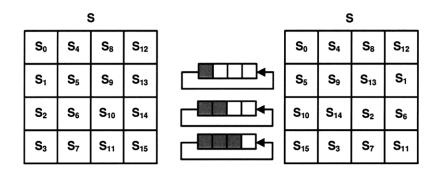

| 3-4 | ShiftRow operation of AES algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 53 |

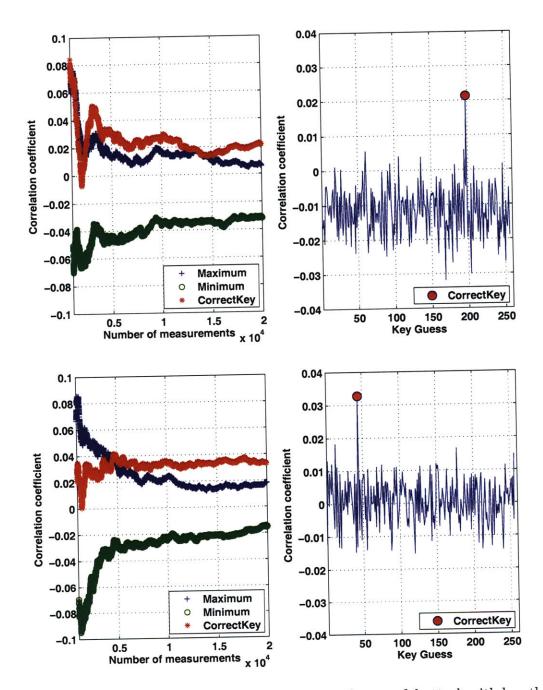

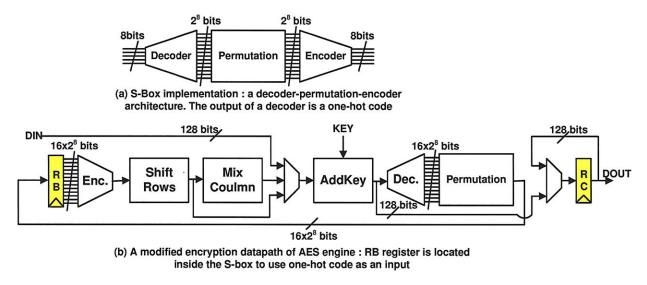

| 3-5 | Cracking the secret key. Two examples of successful attack with less than 5K encryption runs (top: $16^{th}$ byte, bottom: $14^{th}$ byte of secret key). Correlation coefficients as a function of encryption runs (left): Blue for max. correlation among 255 wrong keys, Green for min. correlation among 255 wrong keys, and Red for the correct key. Correlation coefficients for 256 possible key guesses at $20K$ runs (right): Red marker is the correct key                      | 56 |

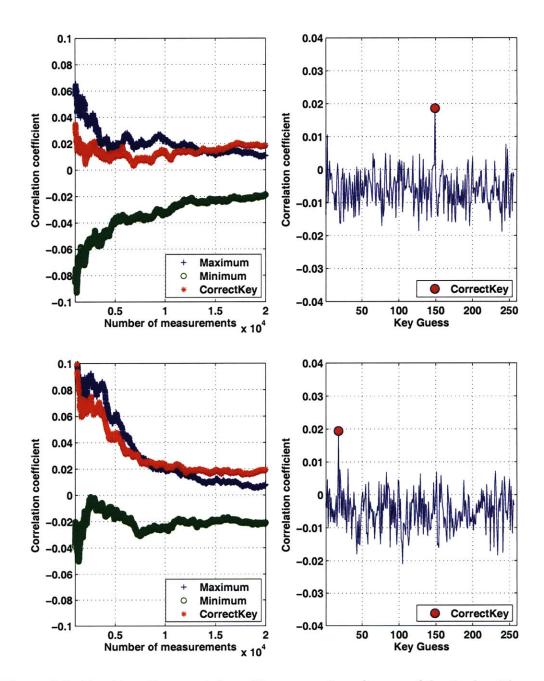

| 3-6 | Cracking the secret key. Two examples of successful attack with more<br>than 10K encryption runs (top: $6^{th}$ byte, bottom: $2^{nd}$ byte of secret<br>key). Correlation coefficients as a function of encryption runs (left):<br>Blue for max. correlation among 255 wrong keys, Green for min. cor-<br>relation among 255 wrong keys, and Red for the correct key. Correla-<br>tion coefficients for 256 possible key guesses at $20K$ runs (right): Red<br>marker is the correct key | 57 |

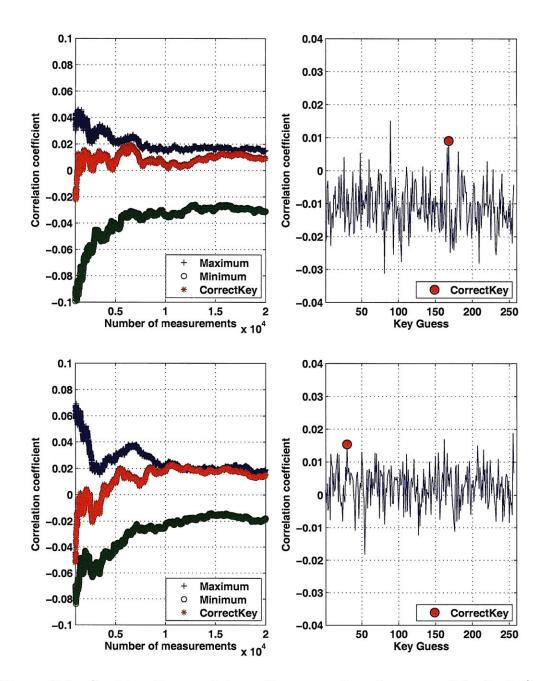

| 3-7 | Cracking the secret key. Two examples of unsuccessful attack (top: $11^{th}$ byte, bottom: $3^{rd}$ byte of secret key). Correlation coefficients as a function of encryption runs (left): Blue for max. correlation among 255 wrong keys, Green for min. correlation among 255 wrong keys, and Red for the correct key. Correlation coefficients for 256 possible key guesses at $20K$ runs (right): Red marker is the correct key                                                       | 58 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |

| 4-1 | AES core: round 10 (top); and round $10+1$ (bottom) [1] $\ldots \ldots \ldots 6$                      |    |  |  |  |

|-----|-------------------------------------------------------------------------------------------------------|----|--|--|--|

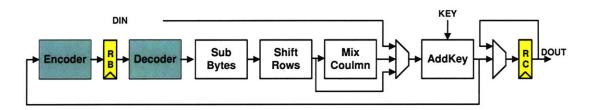

| 4-2 | RB register is located between encoder and decoder. Encoder masks                                     |    |  |  |  |

|     | the encryption data to have a fixed Hamming weight, and decoder                                       |    |  |  |  |

|     | recovers data to the original format                                                                  | 61 |  |  |  |

| 4-3 | A secure AES architecture with resistant to DPA                                                       | 62 |  |  |  |

| 4-4 | Cracking the secret key. Two examples of unsuccessful attacks with                                    |    |  |  |  |

|     | more than 10M encryption runs (top: $16^{th}$ byte, bottom: $12^{th}$ byte of                         |    |  |  |  |

|     | secret key). Correlation coefficients as a function of encryption runs                                |    |  |  |  |

|     | (left): Blue for max. correlation among 255 wrong keys, Green for min.                                |    |  |  |  |

|     | correlation among 255 wrong keys, and Red for the correct key. Cor-                                   |    |  |  |  |

|     | relation coefficients for 256 possible key guesses at $10M$ runs (right):                             |    |  |  |  |

|     | Red marker is the correct key $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 65 |  |  |  |

| 4-5 | Layout of the DPA-protected AES core.                                                                 | 66 |  |  |  |

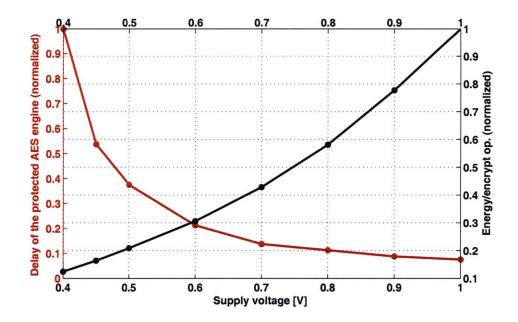

| 4-6 | Normalized delay (red line) and energy (black line) of the protected                                  |    |  |  |  |

|     | AES engine with respect to supply voltage $\ldots \ldots \ldots \ldots \ldots$                        | 67 |  |  |  |

|     |                                                                                                       |    |  |  |  |

# List of Tables

| 1.1 | Area and power trade-off between 3 different S-box implementations    |    |

|-----|-----------------------------------------------------------------------|----|

|     | [11]                                                                  | 20 |

| 2.1 | Comparison of energy consumption for different degrees of parallelism |    |

|     | all of which satisfy the same throughput requirement                  | 35 |

| 2.2 | Performance comparison of different ASIC AES implementations          | 45 |

| 3.1 | DPA Measurement Results                                               | 55 |

| 4.1 | IC Performance comparison between the unprotected and protected       |    |

|     | AES engines.                                                          | 68 |

## Chapter 1

# Introduction

Emerging mobile and biomedical devices, capable of connecting to the global network via wireless communication, are susceptible to tampering and eavesdropping because wireless network utilizes air itself as the transmission medium. Because of the security concerns, wireless mobile devices need to incorporate cryptographic primitives such as data encryption and user/message authentication. Since energy is highly limited in battery-operated devices, the cryptographic engine should be designed for minimum energy operation. Compared to software-based solutions, dedicated hardware implementations of cryptographic algorithms can be made very energy efficient, thereby making them suitable for energy-constrained applications [8].

However, security hardware is vulnerable to side-channel attacks. In cryptography, side-channel attack is any attack based on information gained from the physical implementation of a cryptosystem, rather than brute force or theoretical weaknesses in the algorithms. For example, power consumption, delay, or EM radiation can provide an extra source of information which can be exploited to break the system and to uncover secret key stored in the system. Differential Power Analysis (DPA) attack [3] is one of the most effective attacks because the switching power of digital CMOS gates provides attackers with important information about the secret key. There have been efforts to design a secure cryptographic core which defeats DPA attacks by masking the current signature of a system. The increased security is achieved at the cost of power, area, and/or performance overhead. For energy-constrained devices, however, design techniques for DPA-protection should satisfy not only the security specification but also stringent energy constraints. Therefore, most of the previously suggested DPA-protection techniques without specific concern for energy consumption overhead cannot be adopted for energy-limited applications.

The objective of this research is to design a secure 128-bit Advanced Encryption Standard (AES) engine which operates with utmost energy-efficiency while protecting secret key against DPA attack. There are several requirements that a batteryoperated AES engine should satisfy. Before delineating the specifications and ideas for an energy-efficient AES engine, the encryption algorithm of AES will be studied first, and then the DPA attack methodology will be explored to understand how attackers can get the critical information about secret key from the power measurement.

## 1.1 Advanced Encryption Standard

In cryptography, Advanced Encryption Standard (AES) [2] is an encryption standard adopted by U.S. government. The AES algorithm is a symmetric block cipher that can encrypt (encipher) and decrypt (decipher) information. The AES is one of the most popular algorithms in symmetric key cryptography because it is relatively fast to compute and easy to implement, but still secure enough. As of 2006, the only successful attacks against AES implementation have been side-channel attacks.

#### 1.1.1 Algorithm Specifications

The AES encryption algorithm is a block cipher that converts 128-bit plaintext to the same length of ciphertext by using cryptographic keys of 128, 192, or 256 bits. At the start of cipher, input is copied to the state array of 4 by 4 bytes as shown in Figure 1-1. After mathematical transformation of the data, the final value of the state is copied out as an encrypted data.

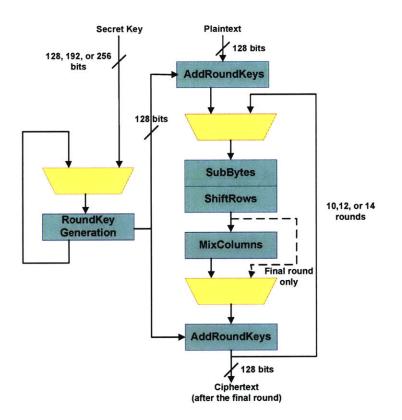

Figure 1-2 briefly describes the encryption process. After an initial round key addition, the state array is transformed by implementing a round function repeatedly for 10, 12, or 14 times depending on the key lengths of 128, 192, 256 bits respec-

|                 | Input bytes     |                  |                  | <br>State array  |                  |                  | _                | Output bytes |                  |                  |                   |                   |

|-----------------|-----------------|------------------|------------------|------------------|------------------|------------------|------------------|--------------|------------------|------------------|-------------------|-------------------|

| in₀             | in₄             | in <sub>8</sub>  | in <sub>12</sub> | S <sub>0,0</sub> | S <sub>0,1</sub> | S <sub>0,2</sub> | S <sub>0,3</sub> |              | outo             | out <sub>4</sub> | out <sub>8</sub>  | out <sub>12</sub> |

| in <sub>1</sub> | in₅             | in <sub>9</sub>  | in <sub>13</sub> | S <sub>1,0</sub> | S <sub>1,1</sub> | S <sub>1,2</sub> | S <sub>1,3</sub> |              | out <sub>1</sub> | out <sub>5</sub> | out9              | out <sub>13</sub> |

| in <sub>2</sub> | in <sub>6</sub> | in <sub>10</sub> | in <sub>14</sub> | S <sub>2,0</sub> | S <sub>2,1</sub> | S <sub>2,2</sub> | S <sub>2,3</sub> |              | out <sub>2</sub> | out <sub>6</sub> | out <sub>10</sub> | out <sub>14</sub> |

| in <sub>3</sub> | in <sub>7</sub> | in <sub>11</sub> | in <sub>15</sub> | S <sub>3,0</sub> | S <sub>3,1</sub> | S <sub>3,2</sub> | S <sub>3,3</sub> |              | out <sub>3</sub> | out <sub>7</sub> | out <sub>11</sub> | out <sub>15</sub> |

Figure 1-1: State array representation of input and output [2]

tively. All the rounds are identical with the exception of the final round, which does not include MixColumns operation as shown in Figure 1-2. A round function includes 4 sub-transformations : SubBytes, ShiftRows, MixColumns, and AddRound-Key. Round key is generated by a feedback operation of the RoundKeyGeneration block and added to the state array at AddRoundKey block.

The operations performed during a round transformation are described in the following.

• SubByte transformation is a non-linear byte substitution that operates independently on each byte of the State. The byte substitution (S-box) is constructed by composing two transformations, multiplicative inverse in the finite field  $GF(2^8)$ and the following affine transformation over GF(2).

$$\begin{bmatrix} b_0'\\ b_1'\\ b_2'\\ b_2'\\ b_3'\\ b_4'\\ b_5'\\ b_6'\\ b_7' \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 & 0 & 1 & 1 & 1 & 1 \\ 1 & 1 & 0 & 0 & 0 & 1 & 1 & 1 \\ 1 & 1 & 1 & 1 & 0 & 0 & 0 & 1 & 1 \\ 1 & 1 & 1 & 1 & 1 & 0 & 0 & 0 & 1 \\ 1 & 1 & 1 & 1 & 1 & 0 & 0 & 0 & 1 \\ 0 & 1 & 1 & 1 & 1 & 1 & 0 & 0 & 0 \\ 0 & 0 & 1 & 1 & 1 & 1 & 1 & 0 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 1 & 0 \\ 0 & 0 & 0 & 1 & 1 & 1 & 1 & 1 & 0 \\ \end{bmatrix} \begin{bmatrix} b_0\\ b_1\\ b_2\\ b_3\\ b_4\\ b_5\\ b_6\\ b_7 \end{bmatrix} + \begin{bmatrix} 1\\ 1\\ 0\\ 0\\ 1\\ 1\\ 0 \end{bmatrix}$$

(1.1)

where  $b_i$  and  $b_i^{'}$  are the  $i^{th}$  bit of a byte before and after the affine transformation

Figure 1-2: Block Diagram of the Advanced Encryption Standard (AES) algorithm

respectively.

- In the ShiftRow transformation, the bytes are cyclically shifted over different numbers of bytes depending on the row number. The first row is not shifted, and the second, third and forth row are cyclically shifted by 1, 2, and 3 bytes respectively.

- MixColumn transformation operates on the State column-by-column. Each column is multiplied modulo  $x^4 + 1$  with a constant polynomial  $a(x) = \{03\}x^3 + \{01\}x^2 + \{01\}x + \{02\}$  over  $GF(2^8)$  where  $\{ab\}$  is the hexadecimal notation.

- In the AddRoundKey transformation, a Round Key is added to the State by a simple bitwise XOR operation.

After the final round operation, the State is copied to the output (ciphertext) as shown in Figure 1-1 and the encryption process is finished.

## 1.1.2 Area, Delay, and Power Characteristics of Implementations of S-box

Cryptographic substitution boxes (S-boxes) are an integral part of modern block ciphers. SubBytes transformation which is defined by S-box introduces non-linearity to the AES algorithm to resist linear cryptanalysis. The S-box is a costly and performance-critical building block of the AES algorithm. S-box lies on the critical path of the round-key scheduler as well as the round datapath so that it limits the maximum clock frequency. Moreover, the S-box also impacts area and power consumption of the AES hardware. There exists several ways to implement the S-box operation by using look-up table [9], calculating block [10], or decoder-permutationencoder block [7]. The diverse implementations of S-box allow a wide range of tradeoffs among timing, silicon area and power consumption, and make it possible to design AES engines suitable for different applications with varying specifications.

In [11], silicon area, critical path delay, and power consumption characteristics are analyzed and compared for the most common standard-cell designs of the AES S-box. Different implementations of AES S-box can be grouped into three basic categories: look-up implementations, calculating implementations, and decoderpermutation-encoder implementations. Look-up table is the simplest and the most straightforward way to implement the SubBytes transformation. It ignores the algebraic structure of the S-box which includes an inversion in  $GF(2^8)$  and the following affine transformation, but just maps the input-output relationship which is realized to a straightforward Boolean equation. Hence, the synthesizer has a degree of freedom for optimizing the circuit, which allows a short critical path at the expense of silicon area. In contrast to the look-up table implementation, calculating implementations use algebraic properties of the SubBytes algorithm. The inversion in  $\mathrm{GF}(2^8)$  is realized by decomposing the finite field into the sub-fields of  $\mathrm{GF}(2^4)$  and  $\mathrm{GF}(2^2)$  to reduce the complexity of the inversion calculation. This implementation method allows a very area-efficient design which is suitable for area-constrained applications. However, in this design, it is hard to optimize the critical path compared to the LUT implementation. The last implementation method of S-box, decoder-permutation-encoder block, ignores the algebraic structure of the substitution and simply implements the Boolean equation for the input-output relation as like the LUT implementation. However, it uses a specific structure (decoder-permutation-encoder) and power-saving coding techniques to reduce the signal activity, and is therefore suitable for low power applications. From several synthesis results of the S-box designs in [11], we can find that the most power-efficient design for S-box is the decoder-permutation-encoder block suggested by Bertoni in [7].

Table 1.1 shows area and power trade-offs between 3 different S-box implementations which are synthesized for the same target delay of 5ns with the same  $0.25\mu m$ process technology. Calculating block [10] is synthesized with the smallest size, but it consumes the largest power among the 3 implementations. Decoder-permutationencoder [7] achieves the most power efficient implementation of S-box, which consumes only 15% and 27% power compared to other 2 designs, respectively.

Table 1.1: Area and power trade-off between 3 different S-box implementations [11].

|                  | Calculating [10] | LUT [9] | DecPermEnc. [7] |

|------------------|------------------|---------|-----------------|

| Area(Gates)      | 496              | 1352    | 1399            |

| Power( $\mu W$ ) | 1.78             | 0.97    | 0.27            |

### **1.2** Differential Power Analysis

The hardware implementation of AES algorithm leaks information about the operations being processed. Therefore, even though the cryptographic algorithm is mathematically strong, secret key of the cryptographic engine can be discovered from the leaked information of the encryption process such as delay, power or electromagnetic emanations. Power analysis is one of the most common side-channel attacks because of its simplicity and effectiveness. Two kinds of power analysis, Simple Power Analysis (SPA) and Differential Power Analysis (DPA), are introduced by P. Kocher, J. Jaffe, and B. Jun in [3]. Simple Power Analysis (SPA) involves visual interpretation of power traces, or graphs of electrical activity over time. Power consumption varies depending on the different operations, thereby making it possible for attackers to distinguish which instructions are processed and sometimes even to find out the secret keys from which the order of operations are determined. However, avoiding procedures that use secret intermediates or keys for conditional branch will mask many SPA characteristics. Moreover, the magnitude of variations in power consumption is small so that SPA does not yield key materials for most (but not all) of the hard-wired hardware implementations.

Differential Power Analysis (DPA) is a more advanced form of power analysis which can allow attackers to compute the secret intermediate values by statistically analyzing power consumption measurements collected from the multiple cryptographic operations. When the cryptographic hardware performs operations using secret keys, the attack exploits varying power bias and statistically extract the secret key from measurements, which contain too much noise to be analyzed using SPA. Therefore, DPA is a much stronger attack compared to SPA. We will look further into the methodology of DPA and some countermeasures against DPA attacks.

#### 1.2.1 DPA Attack Methodology

The DPA attack is conducted by monitoring the operations that leak information about secret keys in their power consumption. Attackers have access to ciphertext C(final version of the encrypted data) and guess a secret key  $K_S$  in the set of key space to calculate a secret intermediate value L of which Hamming weight is correlated to the power consumption. By finding out the value L which gives the highest correlation with the measured power consumption, the actual secret key  $K_S$  can be disclosed to attackers.

For AES-128 algorithm, the input value to the final round  $(10^{th} \text{ round})$  can be chosen as a secret intermediate value L since the value can be calculated in a reverse algorithmic way with the known ciphertext C and a guessed secret key  $K_S$ . Moreover, the value is highly correlated to the power consumption during the  $10^{th}$  round operation. Therefore, once the real value of L is disclosed from correlation attacks, secret key  $K_S$  can also be known to the attackers.

The DPA selection function  $D(C, b, K_{10})$  is defined as computing the  $b^{th}$  bit of intermediate value L where attackers observe the ciphertext C and guess a  $10^{th}$  round key,  $K_{10}$ . The secret key  $K_S$  can be calculated in a reverse way when the  $10^{th}$  round key  $K_{10}$  is found.

To implement the DPA attack, an attacker first observes m encryption operations and captures power traces  $T_{1...m}[1...k]$  containing k samples each. Attackers also records the ciphertexts  $C_{1...m}$ . DPA analysis uses power measurements and selection function  $D(C, b, K_{10})$  to determine whether a key block guess  $K_{10}$  is correct or not. The following k-sample differential trace  $\Delta_D[j], j = 1...k$  calculates difference between the average of the power traces for which  $D(C, b, K_{10})$  is one and the power traces for which  $D(C, b, K_{10})$  is zero [3].

$$\Delta_D[j] = \frac{\sum_{i=1}^m D(C_i, b, K_{10}) T_i[j]}{\sum_{i=1}^m D(C_i, b, K_{10})} - \frac{\sum_{i=1}^m (1 - D(C_i, b, K_{10})) T_i[j]}{\sum_{i=1}^m (1 - D(C_i, b, K_{10}))}$$

(1.2)

, where  $j = 1 \dots k$ .

If  $K_{10}$  is an incorrect guess, the bit computed using D will differ from the actual target for about half of the ciphertexts  $C_i$ . The selection function  $D(C, b, K_{10})$  is effectively uncorrelated to what was actually computed by the target device. Therefore, the difference between the power averages for which  $D(C, b, K_{10})$  is 1 and that for which  $D(C, b, K_{10})$  is 0 approaches to zero as the number of sample traces goes to infinity.

However, if  $K_{10}$  is a correct guess, the computed value for  $D(C, b, K_{10})$  will equal to the actual value with probability 1. Therefore, the selection function is correlated to the value of the bit manipulated in the  $10^{th}$  round and  $\Delta_D[j], j = 1 \dots k$  function gives the spikes where the effect of the target bit appears on the power consumption.

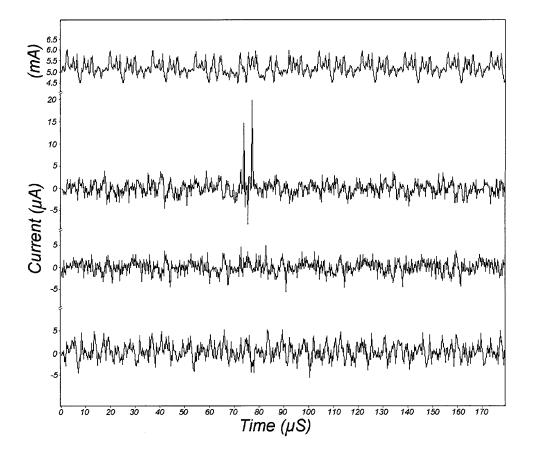

Figure 1-3 shows the reference current trace (top) averaged over  $m = 10^3$  encryptions and three differential traces  $\Delta_D[j], j = 1 \dots k$  (bottom) for different key guesses. The first differential trace is produced using a correct secret key and the others are

Figure 1-3: Current reference (at the top) and three DPA traces - the first trace with correct key guess and following two traces with incorrect guesses [3]

calculated using incorrect secret keys. We can clearly distinguish the correct key guess with spikes in the differential trace. Even though the differential traces are averaged over  $10^3$ , there still exists a modest amount of noise as shown in the traces.

#### **1.2.2** Previous Works to Defeat DPA Attacks

Techniques to prevent DPA have been suggested and demonstrated at different design levels including algorithm, circuit, logic gate, routing, and system. Even though the details of the ideas are all different, the techniques for DPA protection fall roughly into two categories.

The first approach uses randomization to introduce noise into power consumption measurements. In [12], current trace is scrambled with a randomized clock gating. The AES engine suggested in [12] incorporates two functionally identical units, and one unit is designed to be more power-efficient than the other. With the randomized clock gating scheme, one and only one of the two units operates at each time. Therefore, the power trace is scrambled, and it makes attackers hard to extract enough information to discover the secret key from power measurements. In [13], Dynamic Voltage and Frequency Scaling (DVFS) scheduler with the previously programmed voltage-frequency pairs is incorporated to randomize the power consumption of a system. However, the value of supply voltage can easily be discovered to attackers by observing the operating frequency of the system. Hence, this technique cannot adequately protect the system from DPA attack. In [14], supply voltage is dynamically scaled with a fixed operating frequency to add some noise in power consumption traces. Even though this idea improves DPA immunity due to the added noise in power trace, none of the power and performance characteristics can be optimized in this system, which is undesirable especially for performance-critical or resourceconstrained applications. Unfortunately, all the previously introduced noise-adding techniques moderately reduces the signal-to-noise ratio in power traces. Therefore, these techniques can increase the number of samples required for the disclosure of secret key, but after attackers gather large numbers of samples, the secret key can still be disclosed.

The second approach tries to reduce correlation between secret key and current trace observed at power supply by balancing Hamming Weights and state transitions or by shielding the core logic from power supply at certain period of time. In [1], signal activity is balanced by incorporating dual-rail logic and completely balanced interconnect with specific routing techniques. The method raises the number of measurements to disclosure significantly, but it incurs a 3x area, 4x power and 4x performance overhead. In [15], [16], and [17], the digital AES engine is isolated from the power supply with use of charge-pump circuits or a local switched-capacitor current equalizer. This approach also can make DPA attacks less feasible by increasing MTD by  $2500 \times$ , but it adds overhead in power consumption by 33%, and reduces maximum throughput by half [16]. It is because there should be periodical charging

and discharging phases in this system. At discharging phase, the capacitor is discharged to a known voltage before it is recharged in order to equalize the amount of charge provided by the external power supply, which prevents attackers from getting information about the amount of charge supplied to the core logic.

DPA-protection techniques always incur trade-offs between security (DPA-immunity) and overhead in power, performance, and area. This thesis aims to design a secure AES engine that accommodates both DPA-protection and low energy consumption with wise trade-offs among important specifications of the system.

## **1.3** Thesis Contribution and Organization

This thesis focuses on developing an energy-efficient AES engine which is resilient to DPA attack. DPA performs a statistical analysis of supply-current measurements and samples of ciphertext to disclose the secret key which consists of 16 bytes. It is a very effective attack for AES algorithm since each byte of a key can be attacked independently, which makes DPA search space to be only  $16 \times 2^8$ . Therefore, the countermeasures of DPA attack should be adopted for secure storage or transmission of private data in portable electronics. Furthermore, to make AES engine suitable for energy-constrained applications, the stringent power budget should be taken into account along with other constraints as well as DPA-resistance.

This thesis proposes the DPA-immune design of an AES engine which maintains energy-efficiency. In Chapter 2, we outline the performance and power constraints of portable mobile and biomedical devices where AES engine will be integrated, and present architecture/logic design techniques to achieve AES engines operating down to power levels of microwatts. An energy efficient architecture will be described and a number of block-design optimizations will be performed to minimize energy consumption per encryption operation. DPA-immunity will not be considered at this phase of design. Simulation results will show that the proposed design meets performance and power constraints of encryption systems suitable for energy-constrained devices.

Chapter 3 will describe the methodology of DPA attacks. A model of the current

consumption will be built for each possible key guess by using knowledge of the AES algorithm and ciphertext. The correlation between the model and the measured power will be calculated to disclose the secret key. The AES system designed in Chapter 2 will be attacked by the proposed DPA methodology and it will show how fast DPA analysis can discover the key from an AES engine which does not incorporate DPA-protection design.

Chapter 4 proposes a new design of an AES engine which defeats DPA in a power-efficient manner. DPA-resistant architecture and block optimizations will be described. The DPA attack will be conducted for this system and the results will be compared with those of the unprotected AES design. The area/performance overhead will also be discussed.

Chapter 5 describes the contribution of the thesis, and studies possible future research directions.

٠

## Chapter 2

# Design of an Energy Efficient AES Engine

The major advantage of AES algorithm is its ability of efficient implementation on various platforms including 8-bit microprocessors, 32-bit processors, or dedicated ASIC hardware. Hardware implementations of AES algorithm focus on different optimization goals such as maximum throughput for networking implementations, power efficiency for radio-powered or energy-harvested devices, and area efficiency for resource-constrained applications like RFID tags. Most of the previous works stress throughput optimization with no energy budget constraints. However, for AES engine to be adopted for mobile or implanted devices, the design goal should be changed to achieve minimum energy operation of the system.

In this chapter, performance and power constraints of an AES engine will be analyzed to integrate the system within biomedical or mobile devices. We will explore the opportunities to optimize the system at the architecture and logic levels. In the course of architecture/block optimization, previous work in literature will be examined to study how the performance/power requirements are met and traded off with varying specifications. Then, an energy-efficient AES engine which incorporates maximum parallelism with voltage scaling will be proposed and described. IC performance results of the system from Nanosim simulation will be provided and compared with those of the state-of-the-art AES engines at the end of the chapter.

# 2.1 AES Engine Specifications for Energy-Constrained Applications

The efficiency of hardware implementations of AES algorithm allows the use of AES in diverse applications ranging from high-speed networks to passively-powered smart cards. According to the fields of applications, the design specifications and efficient implementations of AES engines can differ greatly. For networking applications, throughput rates in the Gigabit range should be achieved for the first priority. However, in passively-powered or battery-powered electronics, energy is highly limited so that the main design goal is to minimize energy consumption to achieve long enough operation with the same battery. In this work, we consider the design of an AES engine to be integrated in biomedical or mobile devices which are powered by battery or energy-harvester. Therefore, the stringent energy constraints dominate architectural and implementation decisions throughout the design of the AES engine.

Portable devices can receive energy from battery and/or energy harvester. For nonimplanted systems, batteries can be recharged or replaced, but, for the user's benefit, as infrequently as possible. If a portable biomedical device incorporates a low-power general purpose processor, which consumes approximately 10mW, current battery technology would accommodate approximately 3 days of operation. Alternatively, dedicated solutions, employing specialized low-power design techniques, consumes only about  $8\mu W$ , achieving more than 10 years of operation with the same battery [18]. Therefore, dedicated low power solutions are indispensable for batteryoperated portable electronics.

For implanted systems, however, batteries cannot be easily removed without surgery, and hence alternate wireless energy harvesting approaches must be considered. To supply energy to implanted devices, wireless electromagnetic energy transfer is an effective and commercially proven techniques. However, near-field wireless energy transfer still requires an explicit power transmitter. Alternatively, emerging approaches which exploit true ambient energy do not require any external source because they have the source of energy inherently as part of the system. For example, system which harvests vibrational energy from the user's movement can generate approximately  $5\mu W$  on average [19]. The ultimate goal of our system is to operate by the energy derived from an energy-scavenging circuitry, which could deliver up to tens of microwatts. Thus, the power consumption of the AES engine should be constrained to be below tens of microwatts.

Required throughput range of AES implementations varies considerably depending on the applications. For optical networks, throughput range of tens of Gigabit per second (Gbps) should be achieved, while throughput range of tens to hundreds of Megabit per second (Mbps) is sufficient for secure data transmission at mobile devices. For sensor networks or implanted biomedical devices, an even lower throughput range can support real-time signal transmission since the period of signal sensing is on the order of few seconds. Therefore, the required throughput range of an AES engine is maximally hundreds of Mbps.

From these specifications, it is evident that new methodologies should be found for the design of an energy efficient AES engine with the system-level throughput constraints which are modest as they may be, but which must be met. Fortunately, scaling of device feature sizes, along with the development of high-density and lowparasitic packaging, make it possible to use the increased capability of CMOS gates to achieve the stringent specifications of low-power digital systems [20]. The following sections will suggest low-power techniques and architectural modifications to achieve an energy efficient AES engine with the acceptable throughput range.

## 2.2 Minimizing Energy Consumption

Low power operation of a system has become a major optimization goal of today's VLSI design. However, low power techniques do not necessarily result in a reduced energy consumption per operation. For example, a serial implementation of a processor can decrease the mean power consumption, but energy consumption is not reduced from this technique. Furthermore, if the serialized system runs at the maximum supply voltage to meet the throughput requirement, it degrades energy-efficiency

compared to the parallelized system running at lower supply voltages. Therefore, the difference between power consumption and energy consumption should be considered in adopting adequate techniques for energy-efficient system design.

This section will analyze the power and energy consumption of a digital system and show the existance of minimum energy point. Also, we will discuss how parallelism, combined with voltage scaling, can simultaneously achieve performance requirement and energy efficient operation.

#### 2.2.1 Minimum Energy Point

The dominant source of power in digital circuits is consumed during logic transitions when charge must be transferred from the supply voltage,  $V_{DD}$ , to the physical capacitance of a signal carrying circuit node,  $C_L$ . The power is called dynamic power,  $P_{DYN}$ , and is given by  $\alpha C_L V_{DD}^2 f_{clk}$ , where  $\alpha$  is the activity factor and  $f_{clk}$  is the operating frequency. For low power operation, each factor in this equation should be minimized. Architectural and algorithmic techniques have been developed and widely used to reduce switching power by minimizing switching factor,  $\alpha$ . For example, balancing logic delays from timing-path inputs can avoid glitching and reduce the activity factor. The attempt to reduce  $C_L$  by placing less gates on the die also results in the reduced power consumption. However, it might increase the number of clock cycles needed for the completion of operation. Therefore, in the respect of energy consumption, it might not be beneficial. Lowering supply voltage,  $V_{DD}$ , reduces power consumption significantly because the power consumption is a quadratic function of  $V_{DD}$ . Operating frequency,  $f_{clk}$ , can be decreased for reduction of power, but it directly deteriorates the throughput of the system. Therefore, trade-off between power and throughput should be considered and the design methodologies to accommodate both specifications have to be considered.

The total energy consumption of AES engine is broken down into dynamic energy and leakage energy. Dynamic energy is modeled as

$$E_{DYN} = \alpha N C_L V_{DD}^2 \tag{2.1}$$

where  $\alpha$  is the activity factor, N is the number of clock cycles,  $C_L$  is the switched capacitance of the circuit, and  $V_{DD}$  is the supply voltage.

The leakage energy,  $E_{leakage}$ , is given by

$$E_{L} = V_{DD}I_{LEAK}T_{D}$$

=  $V_{DD}I_{S}e^{\frac{-V_{th}}{nV_{T}}}(1 - e^{\frac{-V_{ds}}{V_{T}}})T_{D}$  (2.2)

where  $I_S$  is a technology-dependent scaling parameter,  $V_{ds}$  is the drain-to-source voltage,  $V_{th}$  is the threshold voltage,  $V_T$  is the thermal voltage, n is related to the subthreshold slope, and  $T_D$  is the latency of computation [21].

Therefore, the total energy per operation can be modeled by

$$E_{T} = E_{DYN} + E_{L}$$

=  $\alpha N C_{L} V_{DD}^{2} + V_{DD} I_{S} e^{\frac{-V_{th}}{nV_{T}}} (1 - e^{\frac{-V_{ds}}{V_{T}}}) T_{D}$  (2.3)

As shown in Equation 2.3, reducing the supply voltage yields significant energy savings. However, lowering  $V_{DD}$  increases the latency of computation,  $T_D$ , linearly in the saturation region, and exponentially in the subthreshold region because it lowers output currents available to switch the circuit node capacitances [4]. Since leakage energy,  $E_L$ , is proportional to  $T_D$ , lowering  $V_{DD}$  starts to increase the leakage energy after the effect of  $T_D$  overwhelms the reduced  $V_{DD}$  in Equation 2.2. Since the dynamic energy and the leakage energy scale in an opposite manner with  $V_{DD}$  in subthreshold region, there exists a minimum operation point where the energy consumption of a system is minimized.

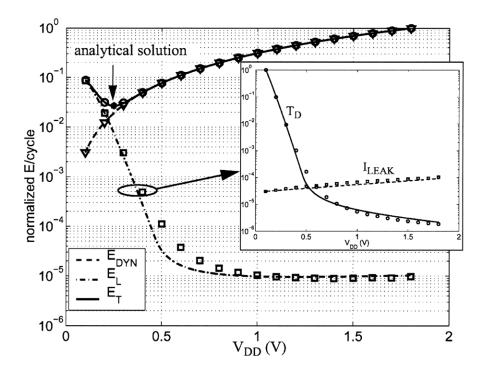

B. Calhoun solved equations for total energy to provide an analytical solution for the optimum supply voltage, and compared it with the simulation results of FIR filter in [4]. Figure 2-1 shows the existance of minimum energy point for the FIR filter in the subthreshold region. The exponential increase of latency,  $T_D$ , makes leakage energy increase exponentially in subthreshold region. The opposing trend of  $E_{DYN}$ and  $E_{leakage}$  results in the minimum energy point.

Figure 2-1: Model (lines) versus simulation (makers) of FIR filter show the minimum energy operation point and the contribution from dynamic and leakage energy. Inset shows  $I_{leak}$  and  $T_D$  effect on  $E_L$  [4].

#### 2.2.2 Parallelism and Subthreshold Operation

The previous analysis of energy consumption shows that reducing the supply voltage yields significant energy savings but comes at the cost of reduced performance. In energy-stringent applications such as biomedical devices, the reduced performance that comes with voltage scaling is often acceptable because the accompanying energy savings are so stringent [22]. However, in some real-time applications, system-level throughput constraints, modest as they may be, must be met. For an AES engine, tens to hundreds of *Mbps* throughput rate should be achieved for data encryption and transmission. In such cases, parallelism, combined with voltage scaling, can be employed to simultaneously achieve the required performance and energy efficiency [20].

The AES algorithm processes 128-bit (16 bytes) of data to get the same length

of ciphertext. Since the minimum unit for calculation of AES algorithm is a byte, 8-bit, 32-bit, and 128-bit platforms are all suitable for hardware implementation of AES. S-box is a non-linear byte substitution block that operates independently on each byte of the State. Depending on the bus size of datapath, the number of Sboxes placed in the datapath can range from 1 for 8-bit processor to 16 for 128-bit processor. The number of S-boxes placed in a system affects performance, area, and power consumption of the AES engine significantly since it has the longest delay within the critical path, and it is the largest and power-dominant building block of AES hardware. If maximally 16 S-boxes are located in an AES engine, then the substitution operation is conducted for all the 16 bytes concurrently, and each S-box can operate at a frequency reduced by a factor of 16, while maintaining the almost same overall performance as the system which has only one S-box to process 16-bytes of State. The reduced frequency per block enables voltage scaling and improved energy efficiency.

To see delay and energy consumption characteristics of a S-box with respect to supply voltages, a low-power S-box design suggested in [7] was implemented in a 90nm CMOS process with low threshold devices. Nanosim simulations were performed to determine the maximum frequency and energy per operation at various supply voltages. Figure 2-2 shows the results of these simulations for a S-box. The red curve shows the normalized delay of a S-box and the black curve shows the normalized energy consumption of a S-box with respect to supply voltage. Delay of a S-box increases exponentially as CMOS starts to operate in the subthreshold region. However, the effect of leakage energy on total energy consumption is not significant for this block because a S-box consists of only 839 gates, and thus the increase of total energy in deep-subthreshold region as in Figure 2-1 does not occur here. Therefore, for a S-box, minimum energy point coincides with the minimum operating voltage at which the system can still function well.

From the simulation results of a S-box, it was known that operating at the minimum energy point of 0.35V rather than at the maximum  $V_{DD}$  of 1V reduces the energy per operation by 91.15%.

Figure 2-2: Normalized delay (red line) and energy (black line) of a S-box with respect to supply voltage.

To run a S-box at low supply voltage in an energy efficient way while achieving hundreds of *Mbps* throughput requirement of AES engine, S-box should be parallelized in an AES engine. From the synthesized results, we estimated that the delay of S-box is about 46.25% of the critical path delay in encryption datpath of AES engine. Since the synthesized result does not include any parasitics which might increase the delay of critical path, we assumed that the delay of S-box occupies about one third of critical path delay. Table 2.1 shows energy consumption for substitution operation of 16 bytes with respect to the degree of parallelism which is represented as the number of S-boxes in system, *N*. For efficient use of hardware, it is desirable that the number of S-boxes (*N*) placed in an AES engine be a multiple of a word size, 4bytes, i.e., 4,8 or 16. The throughput requirement of AES engine is assumed to be 300Mbps, and the supply voltage is set to satisfy the throughput requirement with the given numbers of S-boxes in a system. From the energy consumption comparison in Table 2.1, it is shown that 16 S-boxes are needed to simultaneously achieve 300Mbpsthroughput and the minimum energy consumption requirements. This analysis will be used in the architectural optimization of AES engine which will be discussed in the next section.

| Ν  | Throughput | Delay of a S-box | $V_{DD}$ | Energy/16 substitutions |

|----|------------|------------------|----------|-------------------------|

|    | [Mbps)]    | [ns]             | [V]      | $[10^{-13}J/16op.]$     |

| 4  | 300        | 3.56             | 0.6      | 2.49                    |

| 8  | 300        | 7.11             | 0.5      | 1.70                    |

| 16 | 300        | 14.22            | 0.4      | 1.01                    |

Table 2.1: Comparison of energy consumption for different degrees of parallelism all of which satisfy the same throughput requirement.

## 2.3 Proposed Architecture

The chosen architecture of a chip design mainly determines the properties of an implementation including power consumption and performance. For a system which is powered by battery or energy-harvester, the stringent energy constraints dominate architectural decisions. Since most operations of AES are byte or word-oriented, they can be executed efficiently on 8-bit, 32-bit, 64-bit, or any word size processors. 128-bit architecture offers the greatest degree of parallelism to increase concurrency of AES computations, and it allows energy-efficient operation while satisfying the throughput requirement.

The AES algorithm encrypts 128-bit blocks of plaintext by repeatedly applying similar round transformations for 10, 12, or 14 times depending on the length of secret keys. Therefore, most AES hardware implementations have one round realized in hardware which is reused to compute all the iterations. To increase throughput of the system, some implementations even unroll the ten iterations of the round transformation and insert pipeline registers between the round transformations. Unfortunately, for modes of operations which have feedback such as CBC mode, pipelining and/or loop unrolling techniques cannot be used as methods for improving throughput. It is because encryption of a plaintext cannot start until processing of the previous text is completed for these modes of operations. This section will provide previous works of AES hardware implementations and analyze each system with respect to throughput and power consumption characteristics. We will propose a maximally parallelized AES architecture to satisfy energy efficiency as well as throughput requirement, and will optimize the main calculating block to save power consumption of the system further.

#### 2.3.1 Previous Works

The previous hardware implementations of AES algorithm can be categorized into two types depending on the design principles and applications. The first type of implementation is a lightweight design for RFID devices or sensor networks, and the second type of implementation aims for high-speed operation. The lightweight implementation requires low die size and low power consumption while data throughput is of minor importance. In contrast, high-speed implementations optimize system for high data throughput while the required hardware resources and the power consumption are of minor importance. Our design goal of AES engine does not fit perfectly into both of the implementations, but partially coincides with both. Our goal is to design an AES engine suitable for energy-constrained applications such as battery-operated medical devices, but still meet throughput requirements of hundreds of Megabits. Therefore, we will delve into previous works to study how the specifications are traded off with each other, and then we will propose an energy efficient architecture that accommodates the throughput requirement.

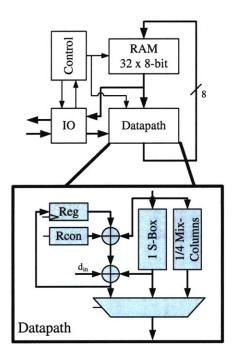

For lightweight implementations, design methodologies should be adopted to minimize the number of CMOS gates and to reduce the mean power consumption of a system, since the targeted applications like RFID tags only can support thousands of gates complexity and few  $\mu W$  of power. Therefore, the main design techniques for lightweight implementations aim to realize minimum number of calculating blocks in a system and to try to reuse the block repeatedly by serializing encryption operation and finding out the sub-operation which needs the same calculating block. An example of the lightweight implementation is provided in [5]. In this design, an 8-bit architecture of AES is implemented and only one S-box is realized in the datapath. The main parts of the AES are the controller, the RAM, the datapath, and the IO module as shown in Figure 2-3. The encryption operation and the key generation are all serialized in order to make it possible to conduct the operations with the given 8-bit datapath. The controller which is realized as a finite-state machine sequences the ten rounds of operations which consists of the sub-operations including SubBytes, ShiftRows, MixColumns, AddRoundKey. Totally, 1032 clock cycles are needed for this architecture to complete the one encryption including the IO operations. This design is optimized for resource-constrained applications so that it consists of only 3400 gates and consumes only  $4.5\mu W$ . However, it can support only upto 9.9Mbps throughput rate. Moreover, the reduction of power consumption does not necessarily result in the reduction of energy consumption. It is because this design reduces the mean power by serializing the required calculations. As a result, it needs more than thousands of clock cycles to complete one encryption and the large number of clock cycles deteriorates the throughput and energy efficiency of the system.

Figure 2-3: Architecture of 8-bit AES module [5]

Next example of an AES implementation requires data rates in the Gigabit range

for network applications. For these applications, parallelism, pipelining and loop unrolling are said to be the concepts which increase the performance of a system per second.

$$Throughput = \frac{Block\_size}{Latency}$$

$$Latency = \frac{T_{clk} \cdot \#Rounds\_per\_block \cdot \#Pipelined\_stages}{\#Utilized\_stages}$$

(2.4)

Equation 2.4 describes how the throughput of a circuit depends on the block size and latency. Due to the fixed block size of 128 bits in the AES algorithm, latency should be minimized for highest data throughput according to Equation 2.4.  $T_{clk}$  is the clock period of the circuit and it depends on the longest critical path through the system. The value  $\#Rounds\_per\_block$  is the number of rounds required to calculate one block of data. #Pipelined\_stages stands for the number of pipeline stages in the architecture, and  $\#Utilized\_stages$  is the number of pipeline stages which can be used concurrently. Therefore, from this equation, it should be noticed that  $T_{clk}$ should be minimized by cutting the longest critical path with pipeline registers, and all the pipeline stages should be utilized in order to maximize throughput of the system. Figure 2-4 shows a fully pipelined and fully parallelized AES processor which achieves tens of Gbps [6]. In this design, all 10 rounds are unrolled and pipelined to increase the throughput of the system. Moreover, in each round, one more pipeline register divides the critical path of encryption datapath and round key datapath. Since each pipeline stage is designed with 128-bit architecture, all the 128-bit block of data can be processed concurrently in each stage.

However, it has to be noticed that loop unrolling and pipelining techniques can improve the throughput of a system for limited modes of operations. The recommended modes of operation for a symmetric key encryption are defined by NIST [23]. For applications which demand higher level of security, it is needed to incorporate modes of operations which have feedback, for example Cipher Block Chaining (CBC) and Output Feedback (OFB). In these feedback modes, pipelining and/or loop unrolling cannot be used as methods for improving throughput, because only one round

Figure 2-4: Maximizing throughput of AES with inner and outer round pipelining [6]

is active at a time and the pipeline never stay filled. Since the targeting modes of operation in our system also include feedback operation, pipeline cannot be adopted for architectural solution for high throughput requirement.

#### 2.3.2 Architecture Optimizations

From the analysis of previous works for AES hardware implementations, it is found that a 128-bit architecture with parallel realization of 16 S-boxes is optimal to achieve high throughput requirement and energy efficiency simultaneously. Concurrent calculation of 16 bytes of data makes it possible to run each block at lower frequency compared to a non-parallelized architecture, and it allows to lower the supply voltage. Therefore, parallelism with voltage scaling results in energy-efficient operation while satisfying throughput requirement. Pipelining can also be used to increase throughput requirement in an energy-efficient manner, but feedback modes of operation prevents efficient use of pipelining.

Figure 2-5: Parallel architecture of AES hardware [1]- There exits two datapaths. One is for round key generation (top), and the other is for round transformation of encrypting data (bottom).

Figure 2-5 shows an energy efficient implementation of an AES engine suggested in [1], which realizes one round of the AES-128 encryption algorithm. For AES-128, the key length and the input size are the same as 128 bits, and a round transformation is repeated 10 times. The architecture of one round implementation contains two different datapaths, the encryption datapath and the key scheduling datapath. To reduce the storage requirements, the round key is generated by on-the-fly key scheduling, not by using specialized RAM memory which should store 11 128-bit round keys.

The encryption datapath contains four sequential sub-operations of a round transformation, including SubBytes, ShiftRows, MixColumns, and AddRoundKeys. The substitution (S-box) step is a non linear operation which consists of multiplicative inverse in Galois field of  $GF(2^8)$  and the followed affine transformation. This is the most costly sub-operation of each round in the respects of delay, power and area. Therefore, optimizing the critical path and/or developing a power-efficient algorithm for S-box can improve the power/performance characteristics of AES engine significantly. For 128-bit architecture, ShiftRows is performed just by rewiring so that it consumes only a small amount of power due to interconnect capacitance. In the Mix-Column block, the bytes of each column are mixed together by multiplying the round data with a fixed polynomial modulo  $x^4 + 1$ . The MixColumn is implemented using a chain of XORs to minimize delay of this unit. For KeyAddition, the round data is simply XOR-ed with the round key, which is generated from the key scheduling datapath.

The key scheduling datapath consists of substitution operation of a word, and followed by a sequence of XOR operations. It is important to match the critical path delay of the key scheduling datapath and that of the encryption datapath from Substitution to MixColumn operation in order to reduce glitches at round key addition.

In this 128-bit architecture, only 10 clock cycles are needed to complete the encryption of one block data. To increase throughput of the system further, critical path of S-box should be minimized. We will deal with this topic at the next section.

#### 2.3.3 Block Optimizations

As discussed previously, design of a S-box affects characteristics of AES engine significantly because delay, power, and area of a S-box dominate performance characteristics of main datapaths in an AES engine. Moreover, the effect of S-box is magnified especially for the fully parallelized architecture of Figure 2-5, since the number of S-boxes placed in this architecture is 20 times more that that of non-parallelized architecture shown in Figure 2-3.

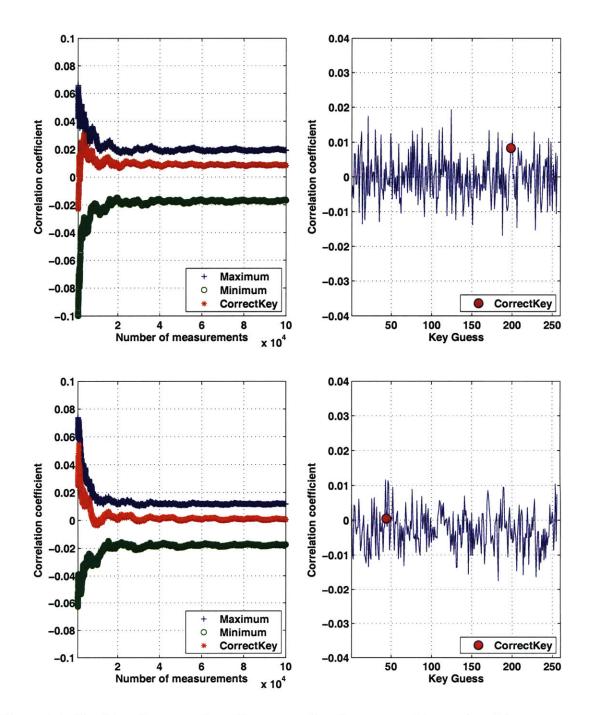

From the area, delay, and power analysis of diverse S-box implementations in [11], the S-box architecture suggested in [7] is the most power-efficient and comparably fast implementation. The overall idea for this implementation is depicted in Figure 2-6. First, the 8-bit input of an S-box grows to  $2^8$ -bit through a one-hot decoder. It expands the 8-bit input to a group of  $2^8$  bits output among which the legal combi-

Figure 2-6: Diagram of the S-box with the decoder, permutation, and encoder block [7]

nations of values are only those with a single high (1) bit and all the others of low (0). This decoding technique is called as One-hot coding. Therefore, the location of the only one high bit (among  $2^8$  bits) indicates what the input data to S-box is. At the permutation block, the one and only one active line will change place inside the string of  $2^8$  bits to generate an adequate output value for substitution operation, and then the  $2^8$  bits are re-mapped to 8-bit binary data at the encoder block. Since one and only one line is active for any input data, and since the permutation block rearranges bits just by rewiring, this implementations. Moreover, the critical path delay of this design is as short as that of LUT implementations. Therefore, we decide to use this design of S-box for our AES engine as shown in Figure 2-5.

### 2.4 IC Performance Simulation Results

The silicon implementation of an AES engine described in this chapter was realized using a 90nm CMOS standard-cell library from IBM. The circuit was described and verified in Verilog on register transfer level, and it is synthesized using the Synopsys Design Compiler. Placement and Routing were done with Astro from Synopsys. Continuous testing and verification eliminated errors during the design steps. Back-end verification ensured manufacturability. These tests consisted of static timing analysis, power simulations, LVS and DRC. After place and route, verification of the correct functionality was done in the Nanosim environment. The region of operation regarding supply voltage and clock frequency was evaluated using Nanosim simulations.

Figure 2-7: Layout of energy-efficient AES engine

Figure 2-7 shows the final layout of AES engine described in this chapter. The core needs a silicon area of  $0.13mm^2(=0.36mm \times 0.36mm)$  on a  $90\mu m$  CMOS, which includes 20854 gates. This number is much bigger than the result from synthesis. The difference in the layout complexity is due to the clock tree, filler cells and other layout overhead. The largest part of the circuit is the combinational logic of 16 S-boxes in encryption datapath. It consumes about 47% of the chip. The controller including the finite-state machine is the second largest portion of the circuit, which consumes 11% of the chip, and flip-flop based registers occupies 10% of the total silicon area.

Nanosim simulation of the extracted AES netlist indicates correct functionality until 0.35V. R/C parasitics extracted from the layout of AES are included in simulations to improve accuracy of power/delay measurements. At 0.35V of supply voltage, a clock frequency of 5.6MHz is reached. At the maximum supply voltage of 1V, the maximum clock frequency of 250MHz is reached. In our design, the encryption of one 128-bit data block requires 11 clock cycles including I/O operations. Therefore, the maximum achievable throughput rate is 2.9Gbps at 1V, and is 64.6Mbps at 0.35V.

Figure 2-8: Normalized delay (red line) and energy (black line) of the AES engine with respect to supply voltage.

Figure 2-8 shows the normalized delay and energy consumption per encryption operation of the AES engine with respect to supply voltage. Here, the minimum energy point coincides with the minimum operation voltage as in S-box implementation. The increase of energy consumption in deep subthreshold as in Figure 2-1 cannot be observed for energy curve of AES engine. It is because the switching activity of signal nodes is very high for encryption operation. The large  $\alpha$  factor in Equation 2.1 makes active energy still dominate total energy in deep subthreshold regions even though leakage energy grows fast due to the exponential increase of delay of a circuit. The switching activity,  $\alpha$ , can be calculated by dividing the total number of node toggles in simulation with the total number of cycles multiplied by the total number of nodes in the circuit as shown in Equation 2.5.

$$\alpha = \frac{\# node\_toggles}{\# cycles \times total \# of\_nodes}$$

(2.5)

The calculated  $\alpha$  for the encryption engine was 0.33. From the simulation results of AES engine, it was known that operating at the minimum energy point of 0.35V rather than at the maximum  $V_{DD}$  of 1V reduces the energy per operation by 92.74%.

| AES-128         | Tech.     | $V_{DD}$ | CLK      | Throughput | Power  | CLK cycles | Energy/op. |

|-----------------|-----------|----------|----------|------------|--------|------------|------------|

| Version         | $[\mu m]$ | [V]      | Per.[ns] | [Mbps]     | [mW]   | /encrypt.  | [pJ]       |

| Verbauwhede[24] | 0.18      | 1.8      | 8        | 1600       | 56     | 11         | 4923       |

| Satoh[25]       | 0.13      | 1.5      | 1.1      | 11600      | 1920   | 11         | 23234      |

| Feldhofer[5]    | 0.35      | 1.5      | 12.5     | 9.9        | 0.0045 | 1032       | 58.05      |

| Our work        | 0.09      | 1        | 4        | 2900       | 17     | 11         | 747.12     |

|                 | 0.09      | 0.35     | 180      | 64.6       | 0.027  | 11         | 54.12      |

Table 2.2: Performance comparison of different ASIC AES implementations.

Table 2.2 shows a performance comparison of the presented work with ASIC AES-128 implementations in [24], [25], and [5]. Many FPGA implementations of AES have also been reported, but it is not straightforward to compare FPGA designs with our ASIC design since design costs and characteristics are very different. The design goal of the first two implementations in Table 2.2, [24] and [25], is to achieve high data throughput upto *Gbps* range. In contrarst, Feldhofer [5] designed an AES engine which is suitable for RFID tags with low power and low die size. Technology and supply voltage are all different for the four designs in Table 2.2, which makes it hard to compare the performance and energy-efficiency in a fair way. However, we can still analyze and compare the different trade-offs between throughput and energy or power, depending on the design goals and implementation characteristics of each design.

Except Felhofer [5], which uses 8-bit architecture, all the AES designs adopt 128bit architecture to satisfy the high throughput requirement. Satoh [25] used Binary Decision Diagram (BDD) S-Box architecture which is optimized for minimum critical path delay, and thus, it could achieve the highest throughput among the previously reported ASIC implementations of AES. However, it consumes more than 1W of power. Verbauwhede [24] succeeded in achieving the high throughput of a few Gbps with much less power compared to Satoh [25]. Our design which runs at the maximum voltage of 1V exceeds the throughput of Verbauwhede [24], only with 30% of power compared to Verbauwhede's design [24]. Feldhofer [5] consumes the least power among the designs presented in Table 2.2. However, the serialized architecture of this design requires more than thousand clock cycles to complete one encryption, so that low power consumption from the design techniques does not result in low energy consumption per encryption operation. Compared to Feldhofer [5], our design which runs at 0.35V achieves  $6.5 \times$  improved throughput with 7% less energy per encryption operation. Therefore, our system which adopts parallelism with voltage scaling satisfies both the high throughput and energy efficiency simultaneously.

In summary, this chapter proposed a fully parallelized architecture of AES-128 engine. Parallelism, combined with voltage scaling, makes it possible to achieve energy efficiency as well as throughput requirements. IC performance results of the proposed engine showed that it can achieve 64.4Mbps with only 54.12pJ/encrypt. at 0.35V, which makes the system suitable for energy-constrained applications. The proposed AES engine is, however, prone to DPA attacks since it does not incorporate any countermeasures against DPA. The next chapter will show how DPA attack can disclose secret key of the system.

## Chapter 3

### **DPA** Resistance Test

A differential power analysis attack on the AES core can be performed using a correlation attack on the the transient signature of the core IC power supply. To attack our system suggested in Chapter 2, we pick a transient time at which, the register in encryption datapath is updated to a known value, such as the ciphertext. By using the known ciphertext, we can estimate a switching power of the register at the transient time with a power model based on the AES algorithm and a guessed secret key. Correlation between this power model and the measured transient power can reveal the secret key after large number encryption runs by using the recorded data sets of ciphertext and the corresponding measured power.

In this chapter, DPA attack methodology will be provided in detail to find an effective power model and correlation function to discover the secret keys. The effectiveness of DPA attack will be shown with measurement results of the attack on the AES engine. The number of measurements to disclosure (MTD) would be a metric to indicate how the system is prone to DPA attacks.

#### 3.1 DPA Attack Methodology