# Scalable Reconfigurable Computing Leveraging

Latency-Insensitive Channels

by

Kermin Elliott Fleming, Jr.

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 2013

$\odot$  Massachusetts Institute of Technology 2013. All rights reserved.

|              |               |                |                                  | 2                  |

|--------------|---------------|----------------|----------------------------------|--------------------|

| Author       |               |                | 6                                | .)                 |

|              |               | Electrical Eng | ineering and                     | Computer Science   |

|              |               |                | •                                | January 14, 2013   |

| Certified by | • • • • • • • |                |                                  |                    |

| J            |               | Ą              | - <                              | Arvind             |

|              | Professor,    | Electrical Eng | ineering and                     | Computer Science   |

|              |               |                |                                  | Thesis Supervisor  |

| Certified by |               | +              | ··· <del>· · · ·</del> · · · · · |                    |

|              |               |                |                                  | Joel S. Emer       |

|              | Professor,    | Electrical Eng | ineering and                     | Computer Science   |

|              |               | <i>(</i> )     |                                  | Thesis Supervisor  |

| Accepted by  | ·             |                | ייאן. דיט . דייק . דיי           | -y •u              |

|              |               |                | $\mathcal{L}_{\mathrm{es}}$      | He A. Kolodziejski |

|              | Chairman, I   | Department Co  | mmittee on (                     | Graduate Students  |

# Scalable Reconfigurable Computing Leveraging Latency-Insensitive Channels

by

Kermin Elliott Fleming, Jr.

Submitted to the Department of Electrical Engineering and Computer Science on January 14, 2013, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### Abstract

Traditionally, FPGAs have been confined to the limited role of small, low-volume ASIC replacements and as circuit emulators. However, continued Moore's law scaling has given FPGAs new life as accelerators for applications that map well to fine-grained parallel substrates. Examples of such applications include processor modelling, compression, and digital signal processing.

Although FPGAs continue to increase in size, some interesting designs still fail to fit in to a single FPGA. Many tools exist that partition RTL descriptions across FPGAs. Unfortunately, existing tools have low performance due to the inefficiency of maintaining the cycle-by-cycle behavior of RTL among discrete FPGAs. These tools are unsuitable for use in FPGA program acceleration, as the purpose of an accelerator is to make applications run faster.

This thesis presents *latency-insensitive channels*, a language-level mechanism by which programmers express points in their their design at which the cycle-by-cycle behavior of the design may be modified by the compiler. By decoupling the timing of portions of the RTL from the high-level function of the program, designs may be mapped to multiple FPGAs without suffering the performance degradation observed in existing tools. This thesis demonstrates, using a diverse set of large designs, that FPGA programs described in terms of latency-insensitive channels obtain significant gains in design feasibility, compilation time, and run-time when mapped to multiple FPGAs.

Thesis Supervisor: Arvind

Title: Professor, Electrical Engineering and Computer Science

Thesis Supervisor: Joel S. Emer

Title: Professor, Electrical Engineering and Computer Science

#### Acknowledgments

Finishing this doctoral thesis is the major, and perhaps the last, milestone of my academic career. Completing a work of this size gives the author pause to reflect on the path taken and the people encountered along it. First and foremost, I would like to thank my advisors Arvind and Joel Emer for providing me with a truly complete education. Through their guidance I have evolved from an undergraduate with limited technical expertise to a young researcher, a transformation to which the following pages will bear witness. Graduate school is a time of technical development and learning; however, it is also a time of personal growth. I thank Arvind and, to a lesser extent, Joel for providing me with many opportunities to travel overseas and explore the world. These opportunities have given me an international education through experience, and as a result, I have become a more complete human being.

This thesis is the culmination of a long collaboration with Joel Emer and the members of VSSAD: Michael Adler, Angshuman Parashar, and Michael Pellauer. In the many summers that we spent together at the Intel facility in Hudson, we created the LEAP FPGA operating system, which helped guide the development of critical portions of this thesis. I would like to thank Joel in particular for training my thinking towards solving some of the general problems facing reconfigurable logic.

My early days at MIT were spent working on Airblue in association with Man Cheuk Ng, Mythili Vutukuru, Sam Gross, and Hari Balakrishnan, of MIT, in association with Jamey Hicks and John Ankorn of Nokia Research Center Cambridge on the Airblue wireless research platform. I would like to especially thank Jamey, from whom I first learned how to develop hardware from a software perspective, and John who, presciently, suggested that Airblue only be an example in my thesis. Chun-chieh Lin, with whom I developed the H.264 implementation presented in this thesis, was also influential in steering me towards thinking about latency-insensitive design as a hardware design methodology.

Graduate school is a long journey with many ups and downs. My parents, Ike and Debbie, and my sister Kimberly have been supportive during my long tenure at MIT. The many care packages that they sent were helpful in getting through, quite literally, the long night of graduate school. I would also like to thank Nadan Cho, who has made the last few years brighter and happier than they would otherwise have been. I also thank my good friends Isaac Dekine, Chris Valerezno, Bryan Murawski, and Meg Hyland for providing many many entertainments and transportation to some poor graduate student.

Finally, to my reader, thank you. May you gain as much knowledge in reading this thesis as I gained in writing it.

Kermin Fleming, October 17th, 2012

# Contents

| 1 | Intr | oduction                                                        | 13         |

|---|------|-----------------------------------------------------------------|------------|

|   | 1.1  | Thesis Organization                                             | 17         |

|   | 1.2  | Thesis Contributions                                            | 18         |

| 2 | Mo   | del of Computation                                              | <b>2</b> 0 |

|   | 2.1  | A Model Of Computation for Multiple FPGAs                       | 21         |

|   | 2.2  | Compilation and Execution of Latency-Insensitive Modules        | 25         |

|   | 2.3  | Accessing Resources Across FPGAs                                | 26         |

| 3 | Rel  | ated Work                                                       | 28         |

|   | 3.1  | Existing Multiple FPGA Compilers                                | 28         |

|   | 3.2  | Latency-Insensitive Design                                      | 31         |

|   | 3.3  | The LEAP FPGA Operating System                                  | 35         |

| 4 | Mu   | ltiple FPGA Compilation                                         | 38         |

|   | 4.1  | Compiler Overview                                               | 39         |

|   | 4.2  | Inputs to the LIM Compiler                                      | 43         |

|   |      | 4.2.1 Soft Connections: Describing Latency-Insensitive Channels | 43         |

|   |      | 4.2.2 Describing Multiple FPGA Execution Environments           | 46         |

|   |      | 4.2.3 FPGA Mapping File                                         | 50         |

|   | 4.3  | Compiler Implementation                                         | 50         |

|   |      | 4.3.1 LIM Graph Construction                                    | 51         |

|   |      | 4.2.0 Madala Disamont                                           | 53         |

|   |      | 4.3.3   | Network Synthesis                                      | 54  |

|---|------|---------|--------------------------------------------------------|-----|

|   |      | 4.3.4   | RTL Generation                                         | 60  |

|   | 4.4  | Interfa | acing to the Bluespec Compiler                         | 62  |

|   | 4.5  | Concl   | usion                                                  | 64  |

| 5 | Rou  | ıter Aı | rchitecture                                            | 65  |

|   | 5.1  | Correc  | ct Latency Insensitive Networks                        | 66  |

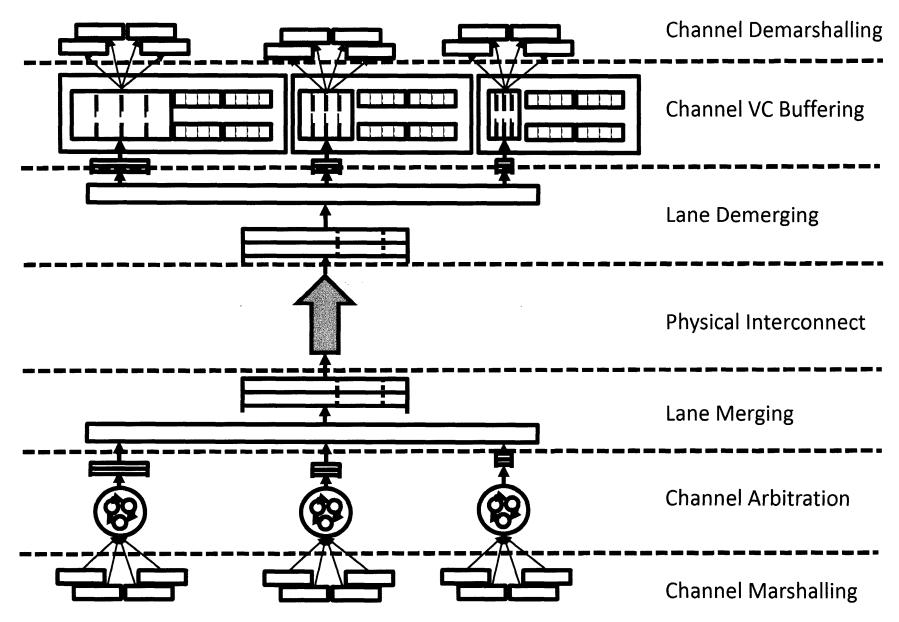

|   | 5.2  | Chanr   | nel Marshalling                                        | 70  |

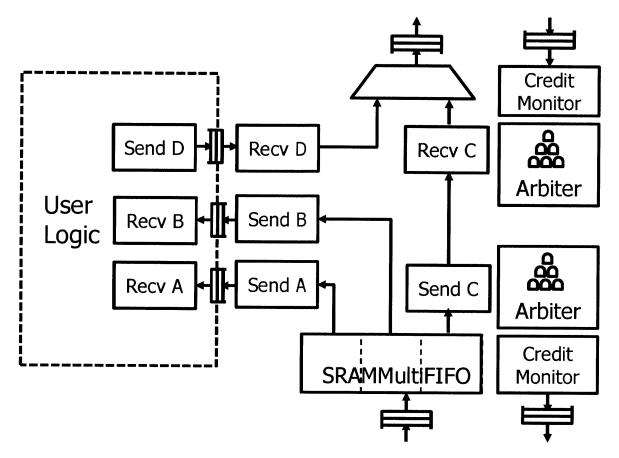

|   | 5.3  | Efficie | nt Virtual Channel Buffering: the SRAMMultiFIFO        | 71  |

|   | 5.4  | Routin  | ng In Parallel: Multiple Lane Routers                  | 75  |

|   | 5.5  | Physic  | cal Interconnect                                       | 81  |

|   | 5.6  | Route   | r Instrumentation                                      | 82  |

| 6 | Con  | npiler  | Optimizations                                          | 83  |

|   | 6.1  | Loops   | : A Micro-kernel for Optimization Evaluation           | 85  |

|   | 6.2  | Lane-S  | Sizing and Channel-Allocation                          | 86  |

|   |      | 6.2.1   | Complexity of Lane-Sizing and Channel-Allocation       | 86  |

|   |      | 6.2.2   | Channel-Allocation and Lane-Sizing in the LIM Compiler | 88  |

|   |      | 6.2.3   | Performance Results                                    | 92  |

|   | 6.3  | Chann   | nel Compression                                        | 96  |

|   |      | 6.3.1   | Tagged Unions                                          | 98  |

|   |      | 6.3.2   | User-specified Compression                             | 100 |

|   |      | 6.3.3   | Performance Results                                    | 102 |

|   | 6.4  | Conclu  | asion                                                  | 107 |

| 7 | Plat | form l  | Resources                                              | 108 |

|   | 7.1  | Latence | ey Insensitive Platform Interfaces                     | 109 |

|   | 7.2  | An Ab   | estraction for Memory                                  | 111 |

|   | 7.3  | Service | es on a Single FPGA: the Scratchpad Memory Hierarchy   | 114 |

|   |      | 7.3.1   | Programming Interface                                  | 114 |

|   |      | 732     | A Basic Scratchnad Implementation                      | 115 |

|    |      | 7.3.3   | Synthesizing a Cache Hierarchy                 | 117 |

|----|------|---------|------------------------------------------------|-----|

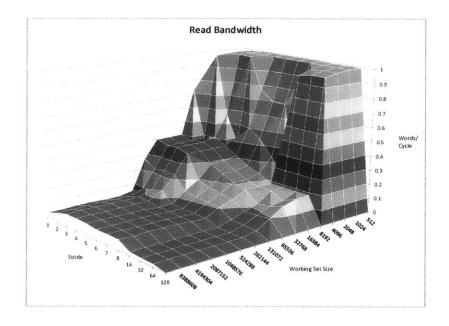

|    |      | 7.3.4   | Performance                                    | 119 |

|    | 7.4  | Scaling | g Services to Multiple FPGAs                   | 120 |

|    |      | 7.4.1   | Multiple Distributed Services                  | 123 |

|    |      | 7.4.2   | Performance                                    | 125 |

|    | 7.5  | Multip  | ole FPGA Platforms                             | 129 |

|    |      | 7.5.1   | Nallatech ACP Module                           | 130 |

|    |      | 7.5.2   | XUPV5                                          | 131 |

|    |      | 7.5.3   | Multiple FPGA Simulator                        | 131 |

| 8  | Airb | olue    |                                                | 135 |

|    | 8.1  | Anato   | my of an OFDM Pipeline                         | 138 |

|    |      | 8.1.1   | Transmitter Pipeline                           | 138 |

|    |      | 8.1.2   | Receiver Pipeline                              | 141 |

|    | 8.2  | Spinal  | Codes                                          | 142 |

|    | 8.3  | WiLIS   | S: High-speed Simulation of Wireless Pipelines | 150 |

|    |      | 8.3.1   | Airblue on Multiple FPGAs                      | 155 |

| 9  | HAs  | $\sin$  |                                                | 156 |

|    | 9.1  | Anato   | my of HAsim                                    | 159 |

|    |      | 9.1.1   | Timing Partition                               | 162 |

|    |      | 9.1.2   | Functional Partition                           | 163 |

|    | 9.2  | Scalin  | g HAsim: 128 Core Models                       | 164 |

|    |      | 9.2.1   | HAsim on Multiple FPGAs                        | 168 |

| 10 | H.20 | 64      |                                                | 170 |

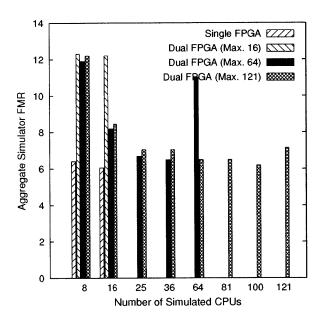

|    | 10.1 | Anato   | my of H.264                                    | 172 |

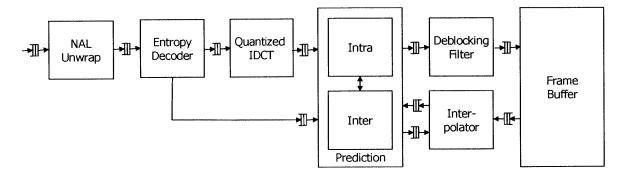

|    | 10.2 | H.264   | Memory Architecture                            | 175 |

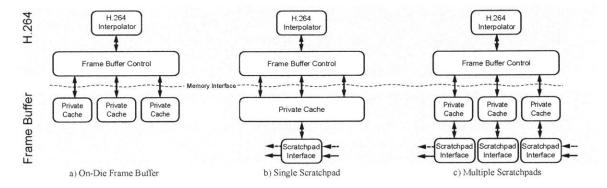

|    | 10.3 | H.264   | on Multiple FPGAs                              | 179 |

| 11 | Con  | clusio  | n                                              | 183 |

|    | 11.1 | Future  | e Work                                         | 185 |

|    |      |         |                                                |     |

# List of Figures

| 2-1  | A latency-insensitive program and its partitioning to two FPGAs      | 22 |

|------|----------------------------------------------------------------------|----|

| 4-1  | Latency-insensitive module (LIM) compiler flow                       | 40 |

| 4-2  | Sample Soft Connections ring declaration                             | 46 |

| 4-3  | Soft Connections syntax example                                      | 47 |

| 4-4  | A sample FPGA environment with two FPGA platforms                    | 48 |

| 4-5  | A sample FPGA mapping file                                           | 50 |

| 4-6  | A sample LIM graph                                                   | 52 |

| 4-7  | A sample module placement                                            | 53 |

| 4-8  | A full multiple FPGA program implementation                          | 54 |

| 4-9  | Ordering of ring-stops can be sub-optimal                            | 57 |

| 4-10 | An example of channel routing across FPGAs                           | 58 |

| 4-11 | An example of two-pass Bluespec compilation                          | 61 |

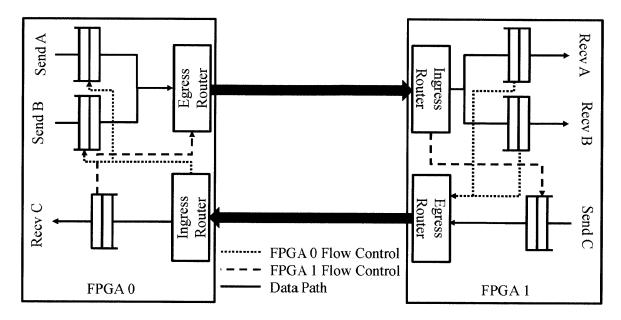

| 5-1  | Logical Architecture of inter-FPGA channels                          | 66 |

| 5-2  | A complete inter-FPGA router                                         | 67 |

| 5-3  | Inter-FPGA router with user logic                                    | 68 |

| 5-4  | A deadlock arising from a data dependence in a shared resource       | 69 |

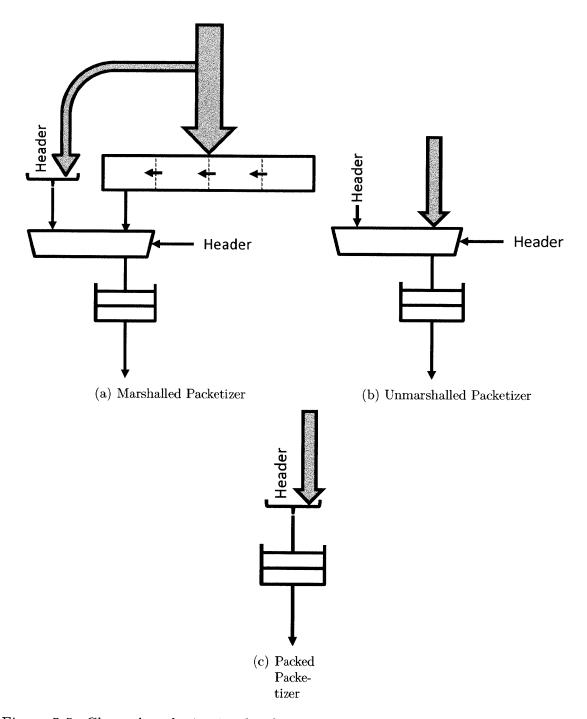

| 5-5  | Channel packetization hardware                                       | 72 |

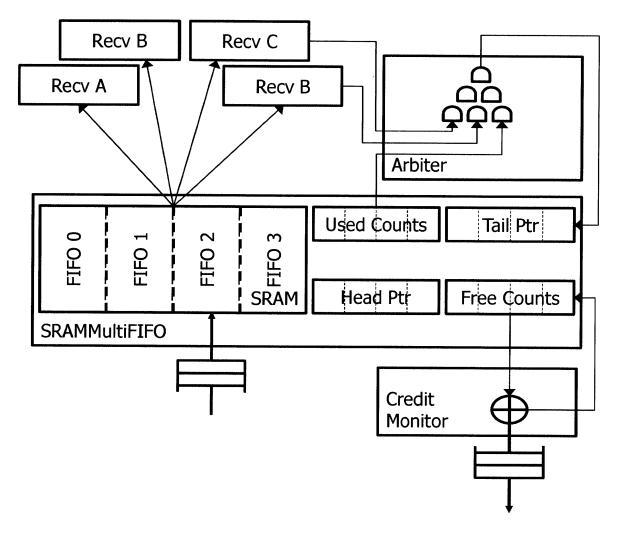

| 5-6  | Router microarchitecture, with SRAMMultiFIFO                         | 74 |

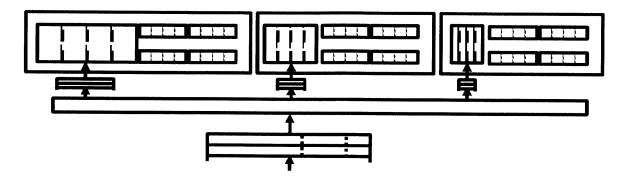

| 5-7  | De-merger microarchitecture.                                         | 76 |

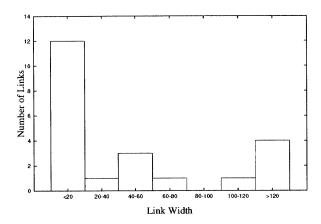

| 5-8  | Widths of inter-FPGA channels in a two-FPGA partitioning of HAsim.   | 77 |

| 5-9  | Activity of inter-FPGA channels in a two-FPGA partitioning of HAsim. | 78 |

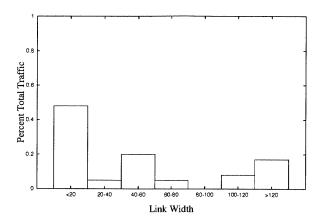

| 5-10 | A cumulative distribution of the channel traffic loads in HAsim. HAsim |     |

|------|------------------------------------------------------------------------|-----|

|      | is dominated by a handful of heavily loaded channels                   | 79  |

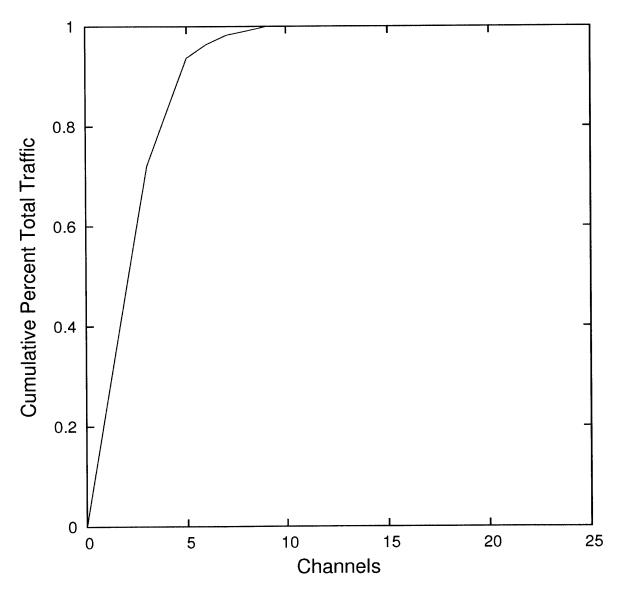

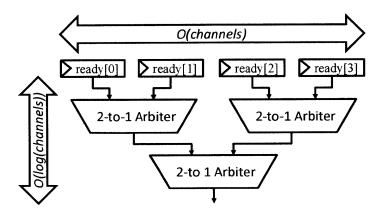

| 5-11 | Routers structures scale in a log-linear fashion                       | 81  |

| 6-1  | Inter-FPGA loop test                                                   | 85  |

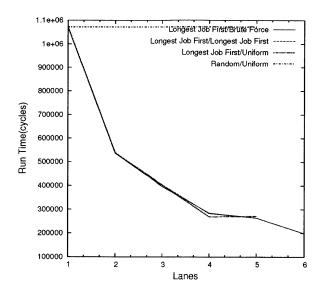

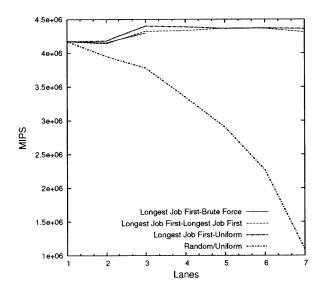

| 6-2  | Loops Test performance with optimized routers                          | 92  |

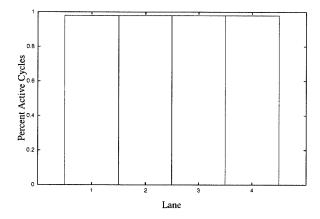

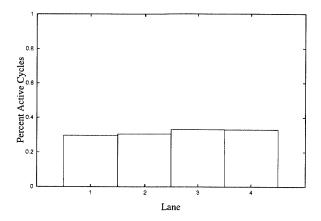

| 6-3  | Router lane loadings for Loops Test                                    | 92  |

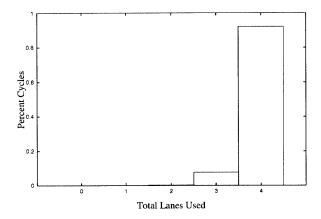

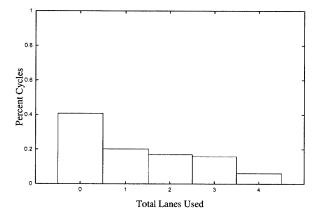

| 6-4  | Router lane parallelism for Loops Test                                 | 93  |

| 6-5  | HAsim performance with optimized routers                               | 93  |

| 6-6  | Router lane loadings for Hasim                                         | 94  |

| 6-7  | Router lane parallelism for HAsim                                      | 94  |

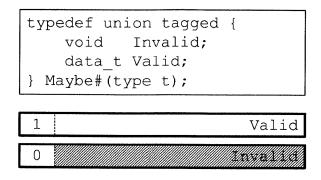

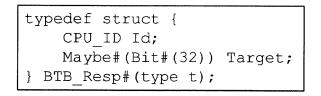

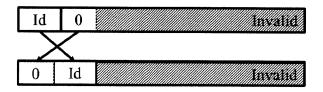

| 6-8  | Syntax and bit representation for Maybe type                           | 98  |

| 6-9  | An automatically generated compression scheme for the Maybe type.      |     |

|      | The Maybe is transformed into two separate latency-insensitive chan-   |     |

|      | nels, the tag and body. The body channel is only enqueued if the tag   |     |

|      | is Valid. The two channels tie in to the inter-FPGA router just like   |     |

|      | any other channels                                                     | 99  |

| 6-10 | Automatic compiler modification of user types                          | 100 |

| 6-11 | Interfaces for compression modules                                     | 102 |

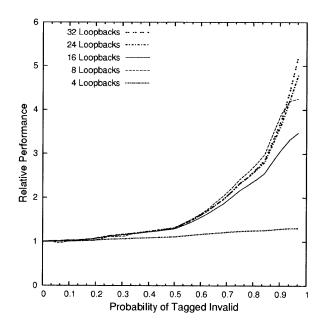

| 6-12 | Loops test performance with channel compression                        | 104 |

| 6-13 | Performance overhead of compression schemes                            | 104 |

| 6-14 | Router optimization composes with channel compression schemes          | 105 |

| 6-15 | HAsim performance with channel compression, but without router op-     |     |

|      | timizations                                                            | 106 |

| 7-1  | A general memory interface for hardware designs                        | 112 |

| 7-2  | A scalable memory hierarchy.                                           | 113 |

| 7-3  | Instantiating Local Scratchpads                                        | 115 |

| 7-4  | A degenerate memory hierarchy with no central cache                    | 116 |

| 7-5  | A memory hierarchy with central cache.                                 | 118 |

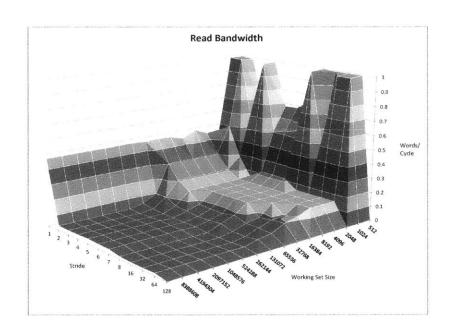

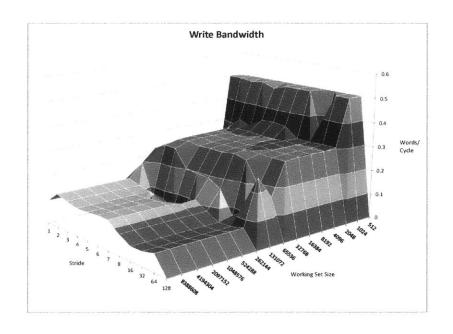

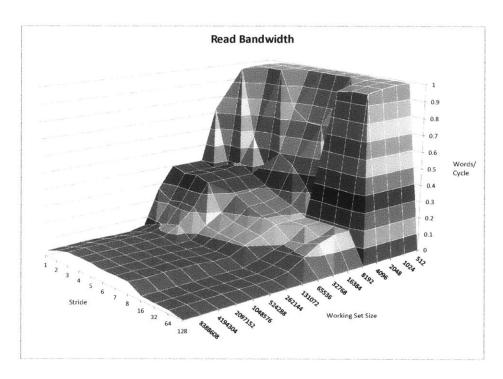

| 7-6  | A example of scratchpad read bandwidth                                 | 120 |

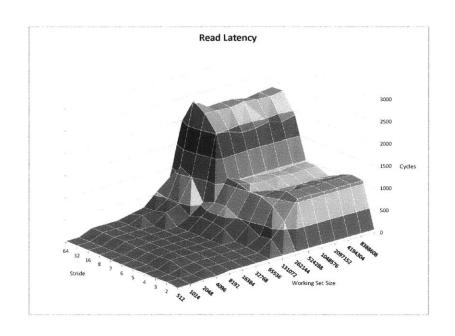

| 7-7  | A example of scratchpad read latency                                  | 121 |

|------|-----------------------------------------------------------------------|-----|

| 7-8  | A example of scratchpad write bandwidth                               | 121 |

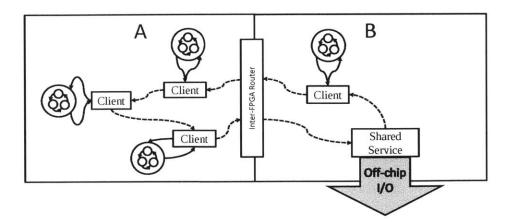

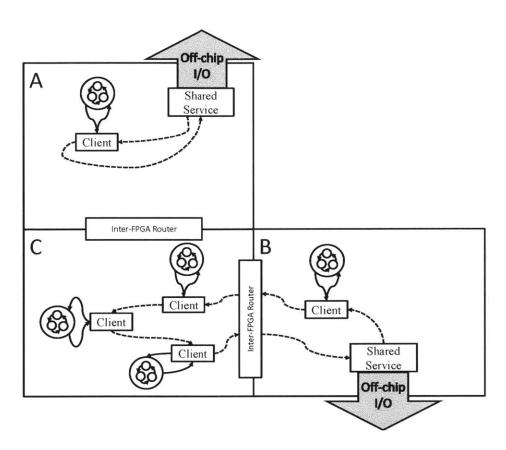

| 7-9  | A distributed service                                                 | 123 |

| 7-10 | An asymmetric distributed service                                     | 126 |

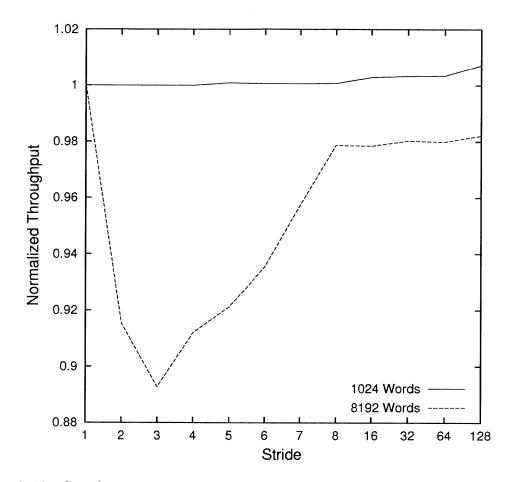

| 7-11 | Scratchpad performance in a multiple FPGA environment                 | 127 |

| 7-12 | Remote scratchpad performance in a multiple FPGA environment          | 127 |

| 7-13 | Simultaneous scratchpad performance                                   | 128 |

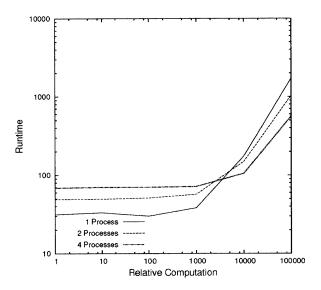

| 7-14 | Parallel simulation performance for loops kernel                      | 133 |

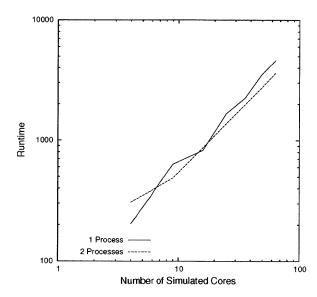

| 7-15 | Parallel simulation performance for HAsim                             | 134 |

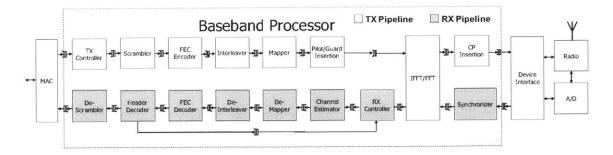

| 8-1  | An Airblue 802.11g-compatible transceiver                             | 137 |

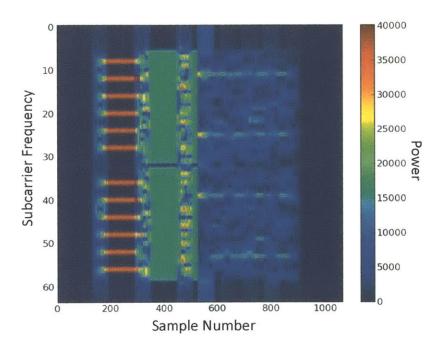

| 8-2  | The power spectrum of an 802.11g packet                               | 139 |

| 8-3  | Symbols produced by spinal encoder                                    | 142 |

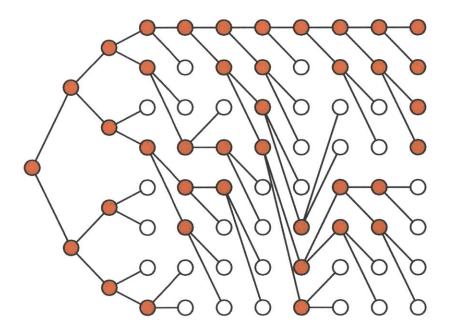

| 8-4  | Spinal code beam search                                               | 143 |

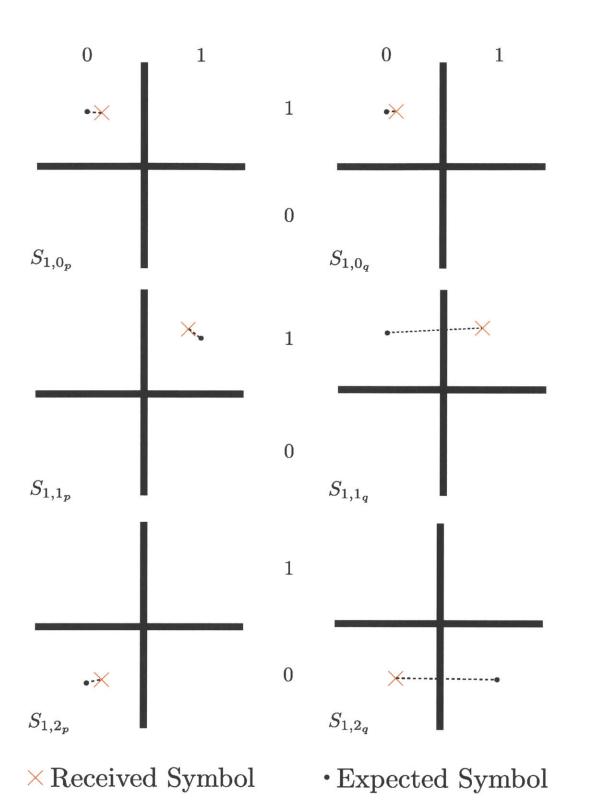

| 8-5  | An example spinal decoding                                            | 145 |

| 8-6  | A comparison of spinal decoder                                        | 147 |

| 8-7  | A spinal transceiver partitioned among two FPGAs                      | 149 |

| 8-8  | Spinal code validation test                                           | 149 |

| 8-9  | Components required to validate a BER estimator in a co-simulation    |     |

|      | environment                                                           | 151 |

| 8-10 | BER estimation simulator, partitioned across two FPGAs                | 152 |

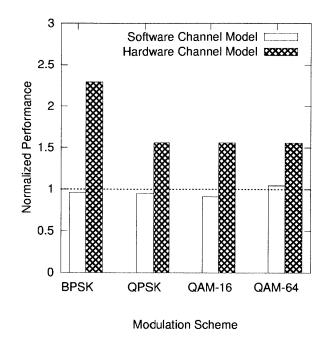

| 8-11 | Performance results for SoftPHY partitioned simulation                | 154 |

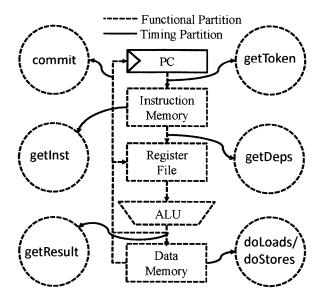

| 9-1  | HAsim partitioned processor simulator                                 | 159 |

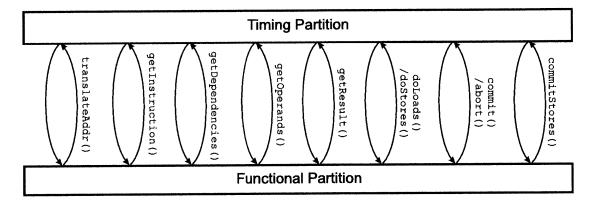

| 9-2  | HAsim un-pipelined processor timing model                             | 162 |

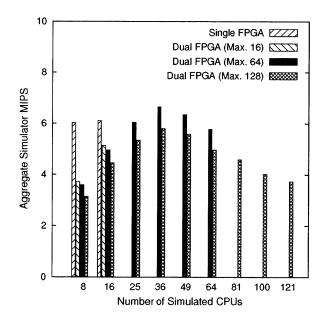

| 9-3  | HAsim simulator performance                                           | 166 |

| 9-4  | HAsim simulator FMR                                                   | 167 |

| 10-1 | An H.264 decoder                                                      | 171 |

| 10-2 | H.264 memory architectures                                            | 175 |

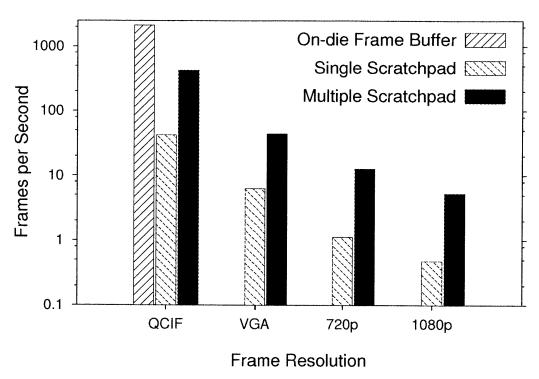

| 10-3 | H.264 frame-rates for different memory architectures and resolutions. | 180 |

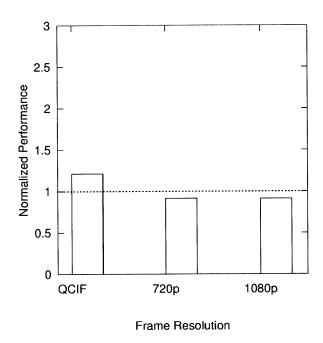

| 10-4 | H 264 performance  | e on multiple FPGA         | ۱ ۵        |      |   |      |  |   | 1    | 81    |

|------|--------------------|----------------------------|------------|------|---|------|--|---|------|-------|

| 10-4 | $\Pi.204$ Denomand | e on munipie ra G <i>r</i> | <i>1</i> 5 | <br> | • | <br> |  | • | <br> | . O . |

# List of Tables

| 5.1  | Synthesis and performance metrics for various router architectures | 75  |

|------|--------------------------------------------------------------------|-----|

| 5.2  | Synthesis metrics for various router configurations                | 81  |

| 7.1  | Performance metrics for FPGA systems                               | 130 |

| 8.1  | WiLIS simulation speeds of different rates                         | 153 |

| 8.2  | Synthesis metrics for WiLIS implementations                        | 154 |

| 9.1  | HAsim Model Configuration                                          | 165 |

| 9.2  | Synthesis metrics for HAsim implementations                        | 168 |

| 10.1 | H.264 bandwidth requirements                                       | 175 |

| 10.2 | H.264 memory architecture performance at QCIF resolution           | 178 |

| 10.3 | H.264 memory architecture performance at 720p resolution           | 178 |

| 10.4 | Synthesis results for various H.264 memory hierarchies             | 179 |

| 10.5 | Synthesis metrics for various implementations of H.264             | 182 |

## Chapter 1

### Introduction

Field-programmable gate arrays (FPGAs) were originally intended to provide a replacement for ASICs in small or low-volume designs. However, as FPGAs have grown in both size and capability, they have matured from their original role to become algorithmic computation platforms in their own right. Indeed, many recent academic and industrial research projects [17] [39] [9] [47] have targeted FPGAs, without the intention of producing, or even emulating an ASIC. Rather than trying to precisely emulate some circuit, the design goal for these programs is purely functional, that is, to produce the answer to a problem of interest as quickly as possible. These projects target FPGAs to take advantage of the performance benefits offered by the FPGA over general purpose processors. As Moore's law continues to offer greater numbers of transistors and general-purpose processor performance fails to scale along with it, it is likely that FPGAs will enjoy even greater penetration into the domain of general computation.

Unlike general purpose processors, which have a theoretically unlimited capacity to describe programs, FPGA programs must fit within the physical resources offered by the FPGA. As a result of this area limitation, some interesting programs may not fit into a single FPGA. If a program cannot fit onto a given FPGA, the programmer is faced with a handful of choices. The programmer may use a larger single FPGA or refine the program to reduce area, neither of which may be possible. A third possibility is to partition the program among multiple FPGAs. This option is typically

feasible from an implementation perspective, but often has serious drawbacks. Manual partitioning may obtain high performance, but requires time-consuming design effort – the programmer must modify the design such that it may be partitioned, develop inter-FPGA communications hardware, and generally take on tasks that are as or more difficult than writing the original program. Tool-based partitioning [67] [3] [54], while automatic, may suffer severe performance degradations of more than an order of magnitude. Neither of these options is attractive.

The crux of the multiple FPGA problem lies in the way that hardware systems are described: modern register-transfer languages (RTLs) do not adequately convey highlevel properties of hardware programs to the compiler, precluding significant compiler assistance. For example, large RTL systems are frequently described in a latencyinsensitive style [13] [17] [39], which is amenable to multiple FPGA implementation. Latency-insensitive designs are typically implemented with concrete RTL FIFOs between modules, such that the timing of data transportation in these inter-module FIFOs does not impact the functional correctness of the modules or, in aggregate, of the entire program. If a compiler could understand the high-level behavior of such a program, then multiple FPGA partitioning would be straightforward: inter-module latency-insensitive FIFOs could be stretched across FPGA boundaries while intrinsically preserving the functional correctness of the design. However, current RTLs obfuscate this high-level behavior. In general, RTL compilers cannot decide when it is safe to modify the cycle-over-cycle behavior of a program. As a result, compilers devolve to preserving the cycle-over-cycle behavior of the RTL as a correctness criterion and limit themselves to the optimization of combinational logic.

To attack the multiple FPGA problem, this thesis introduces a new language-level construct: the latency-insensitive channel. Latency-insensitive channels have operational behavior similar to FIFOs, but may have dynamically variable latency and buffering. Latency-insensitive channels thus allow the programmer to directly describe points in a program where the compiler *may* choose to alter the timing behavior of the system. In particular, the compiler may choose any physical implementation of the latency insensitive channel to meet compilation goals, including mapping a

program to multiple FPGAs.

Programs described using latency-insensitive channels have a natural decomposition into latency-insensitive modules, entities that communicate only by way of latency-insensitive channels. Once decomposed, mapping the program to multiple FPGAs is conceptually straightforward, since the implementation of all inter-module communications channels is left to the latency-insensitive module (LIM) compiler. The compiler places modules on to a set of FPGAs coupled by some physical interconnect. The compiler then synthesizes a program-specific, inter-module communications network on top of the physical FPGA interconnect. The structures of this synthesized network, including program-specific interconnect multiplexors, marshalling structures, and arbitration logic, are optimized for the latency-insensitive channels and behavior of the compiled program. The automatic synthesis of this network represents a significant design-effort savings over a manually produced inter-FPGA network: whereas the LIM compiler can automatically regenerate a network in response to changes in the user program, for example the introduction of a new inter-FPGA channel, a hand-design network would require significant re-engineering.

Latency-insensitive channels give a natural partitioning of hardware programs across multiple FPGAs. However, real designs must also make use of external resources, such as memory. Moreover, good use of FPGA platform resources is essential to high-quality multiple-FPGA implementation. Performance gains in parallel computing come from making use of more resources, including memory, to accomplish a task in parallel. The performance gain due to these increased computational resources can be significant: for some truly parallel workloads, super-linear performance gains can be obtained. When hardware programs scale to multiple FPGAs, they also gain access to more resources – ranging from look-up-tables (LUTs) in the FPGA fabric to extra external DRAM banks. These resources must be leveraged to improve the performance of multiple-FPGA implementations. For example, increasing the size of the memory caches inside the program to utilize extra fabric resources. However, traditional RTL compilers are not generally able to make such design modifications, particularly when doing so implies a perturbation in the cycle behavior of the original

#### RTL.

By raising the level of abstraction available to the programmer above the level of RTL and explicitly decoupling resource interfaces from program RTL, programs partitioned across multiple FPGAs can automatically make use of the extra resources available across platforms. This thesis will describe a scalable, transparent mechanism based on latency-insensitive channels which provides automatic, programmer-oblivious access to resources. As in the case of parallel software running on a multi-core processor, granting access to these additional resources can dramatically accelerate FPGA programs; as in software, super-linear speed-ups in real-world applications are possible and will be demonstrated in this thesis.

Scaling designs across multiple FPGAs has traditionally been viewed as a difficult, time- and performance-consuming task. This thesis will demonstrate not only that multiple FPGA implementations can be generated automatically, by way of minor modifications to existing hardware programs, but that these multiple FPGA implementations can be superior to single FPGA implementations across several performance metrics. Thus, the work presented in this thesis provides four potential benefits to hardware designs:

- Wall-clock runtime of the program can decrease, due to improved clock frequency and increased access to FPGA resources.

- Programs can be scaled to handle larger problem sizes, again due to increased access to resources.

- Synthesis times are reduced both by the smaller size of design partitions and the opportunity for parallel synthesis.

- Partial recompilation is available in earnest because only those FPGAs that host modified modules need to be rebuilt.

Different programs experience different combinations of these salutary effects.

#### 1.1 Thesis Organization

The thesis commences in Chapter 2.1 with a discussion of the properties that hardware systems need to have in order to permit automatic multiple FPGA implementation. This description of a model of computation for multiple FPGAs is followed by a discussion of prior work related to the thesis in Chapter 3.

After the discussion of these preliminaries, the thesis proceeds to the exposition of the LIM compiler, an automated tool capable of mapping latency-insensitive modules onto environments consisting of multiple FPGAs. Chapter 4 describes the operation and flow of the LIM compiler. The key activity of this compiler is synthesizing a communications network between the latency-insensitive modules, including support for channels that cross FPGA boundaries. To be practically useful, the network must not only provide high-bandwidth and low-latency communication, but also it must impose a low area overhead in terms of FPGA resource usage. Chapter 5 describes an efficient router architecture for inter-FPGA communications.

Efficient, high-performance networking hardware is essential to quality multiple-FPGA synthesis. However, the *parameterization* of this hardware is equally important. The compiler plays a major role in parameterizing the inter-FPGA network hardware for each application. Chapter 6 discusses program analysis techniques and compiler optimizations that are applied during compilation to improve network throughput. This chapter will also discuss mechanisms for program instrumentation and *feedback-driven* optimization.

Multiple FPGA programs are not comprised solely of latency-insensitive modules: like software programs, they must interface to memory and I/O devices. Chapter 7 describes the abstraction of these device-specific interfaces, which do not conform to the latency-insensitive model of computation.

The thesis concludes with the evaluation of multiple-FPGA implementations of several large latency-insensitive designs. Many hardware designs can be couched in the latency-insensitive model of computation, and the designs described in these chapters demonstrate both the utility of the latency-insensitive paradigm and the prac-

tem hardware implementations drawn from recent academic and industrial research: Chapter 8 describes Airblue, a set of libraries for implementing wireless baseband transceivers, including an implementation of 802.11g; Chapter 9 describes HASim [47], a framework for building cycle-accurate multi-processor simulators, which, on multiple FPGAs, can scale to hundreds of cores; and Chapter 10 describes H.264 a high-performance video compression scheme. These chapters may be omitted if the reader is interested only in understanding the implementation of the LIM compiler.

It is important to note, in reading about these applications, that all of them were written targeting a single FPGA, long before the conception of the compiler presented in this thesis. The multiple FPGA implementations presented in this thesis use the same, unmodified source as single FPGA implementations, with the exception of minor re-parameterizations where relevant. Although I helped to implement Airblue and H.264 at MIT, HAsim was primarily developed at Intel.

All three of these examples experience some benefits when implemented on multiple FPGAs. Both HAsim and Airblue scale to implement larger programs, while all three applications enjoy faster throughput for some test cases when mapped to multiple FPGAs. For Airblue, throughput improvement is super-linear, in some cases. All three examples enjoy both faster compilation and faster incremental recompilation.

Finally, the thesis describes some planned extensions to the LIM compiler and concludes in Chapter 11.

#### 1.2 Thesis Contributions

By providing new, abstract language-level constructs that allow the programmers to express the intrinsic behavior of their hardware programs, this thesis will demonstrate not only that existing hardware programs have properties that admit of multiple FPGA partitioning, but also that by explicitly exposing these properties, high-quality multiple FPGA implementations can be produced automatically. The following list summarizes the contributions of this thesis:

- The formulation and application of a model of computation for designs with explicit latency-insensitive channels (Chapter 2.1).

- A compiler mapping designs with explicit latency-insensitive channels to multiple FPGAs (Chapter 4).

- An area-efficient, high-performance network architecture for latency insensitive channels (Chapter 5).

- Optimizations for inter-FPGA networks (Chapter 6).

- Techniques for providing automatic and scalable access to resources, such as memory, across multiple FPGAs (Chapter 7).

- Numerous large hardware designs obtained through application of the compiler (Chapters 8, 9, and 10).

## Chapter 2

# Model of Computation

Traditional RTL has a strong structural correspondence to the physical reality of a hardware system. Designs are described in terms of registers, wires, logic gates, memory, and clocks. Even though system behavior can be complex, the semantic model of synchronous RTL is simple: at each clock cycle, values are read from register, some combinational computation occurs, and the results are written back to register. Compilers of RTL descriptions must honor these semantics: they must be cycle-accurate, that is, they must guarantee a bijective mapping between the cycle-overcycle behavior of the original RTL and whatever implementation that they produce.

Synchronous systems described using RTL synthesize well, in the sense that language-level constructs have a strong correspondence to the synthesized hardware produced by a physical compiler. Moreover, the designer has tight control over the design and tool flow, even until the final cell-level realization of the system. However, the cycle-accurate model of computation and tight design control come at a cost: they severely constrain the freedom of the compiler to alter the design. In RTL-based designs, increasing the latency of even one FIFO by one cycle can break a design, while inserting a new pipeline stage can represent a major engineering effort. In general, RTL compilers cannot infer that making these sorts of cross-cycle-timing modifications will preserve cycle-accuracy or functional correctness, even if the modifications, in fact, do preserve the functional correctness of the design. Since the compiler cannot prove that modifications will maintain cycle-accuracy, it cannot assist the program-

mer beyond combinational optimization.

The difficulty in automatic reasoning about when it is safe to modify the cycleover-cycle behavior of any part of an RTL design is the direct cause of low performance in existing multiple FPGA partitioning schemes. Since existing tools cannot reason about design behavior as communicated through RTL, they must pay the enormous cost of maintaining cycle accuracy across multiple FPGAs. Typically, an order of magnitude in wall clock performance is lost, even if the design, at the high level, could be well-partitioned across FPGAs by a human.

In the past, when gates were few and dear, the level of implementation control available in RTL was necessary. However, modern FPGAs offer enormous implementation capacity. As the usage of FPGAs shifts to algorithm acceleration from circuit emulation, the value in automating the design process becomes even more clear: real performance gains occur at the algorithm level. Design automation, even at the cost of slightly suboptimal performance, is essential to free the designer to focus on the high-level aspects of program behavior, as opposed to the low-level details of RTL.

#### 2.1 A Model Of Computation for Multiple FPGAs

This thesis seeks to raise the level of abstraction available to hardware programmers above traditional RTL, in an effort to simplify the scaling of fine-grained parallel programs to multiple FPGAs. To achieve this goal, the thesis introduces a novel, language-level means of communicating information about design behavior: the *latency-insensitive channel*. The latency-insensitive channel has operating behavior and interface similar to the RTL FIFOs commonly used in hardware design—either a simple enqueue or dequeue operation, depending on the endpoint. However, unlike the RTL FIFO, which has fixed buffering, fixed latency, and a fully specified behavior, the latency-insensitive channel makes only two basic guarantees. First, the channel guarantees FIFO delivery of messages. Second, the channel guarantees that at least one message can be in flight at any point in time. These properties imply that the channel may have dynamically-variable transport latency and arbitrary, but

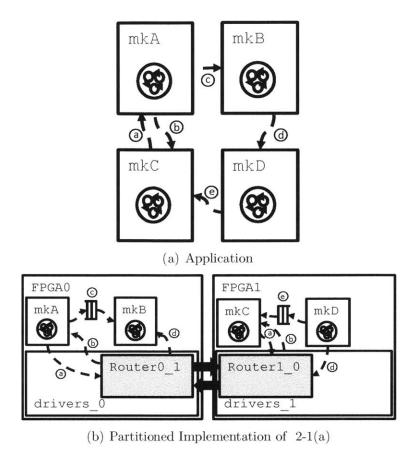

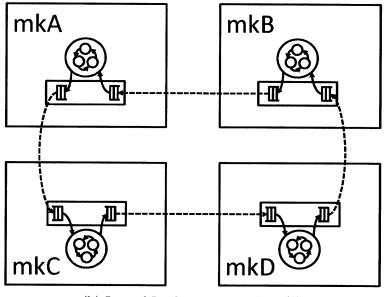

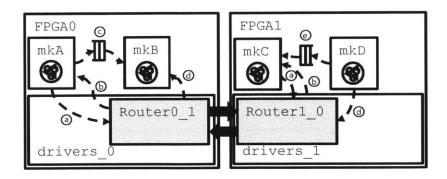

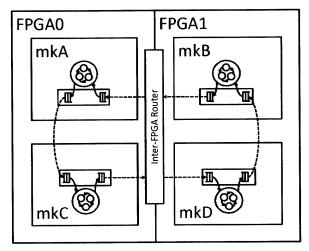

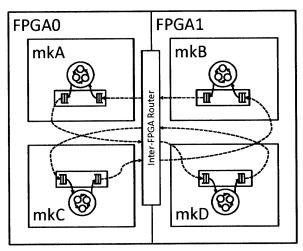

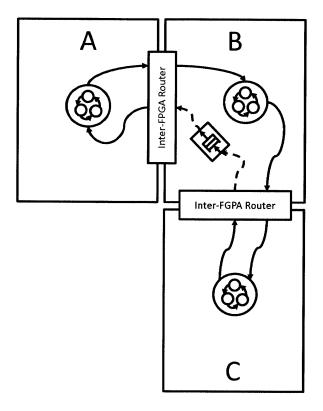

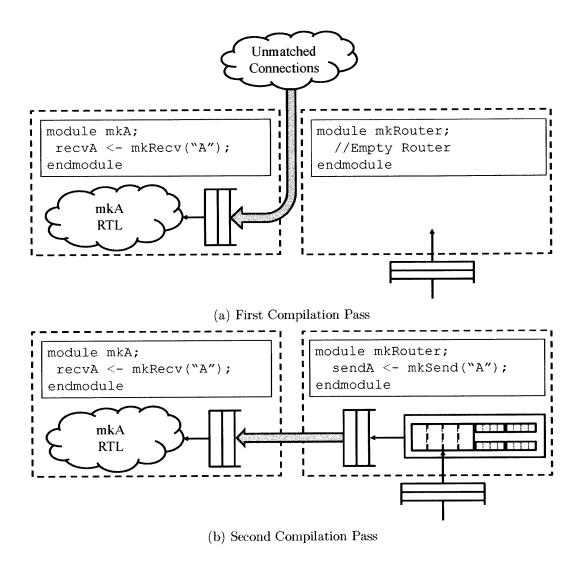

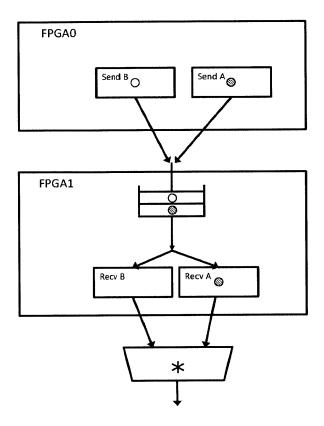

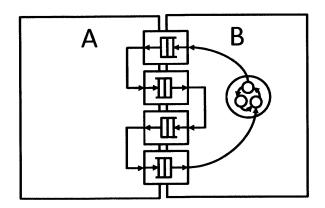

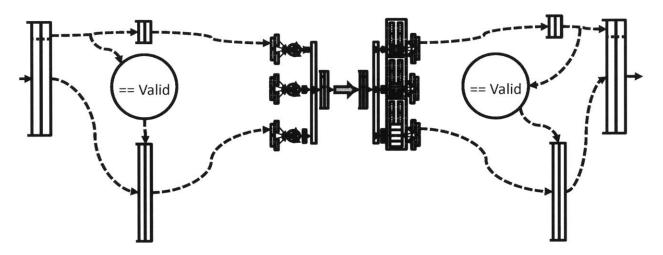

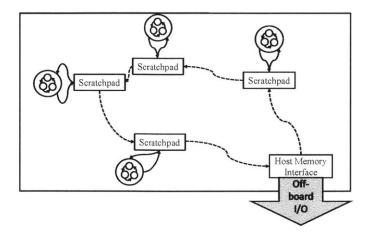

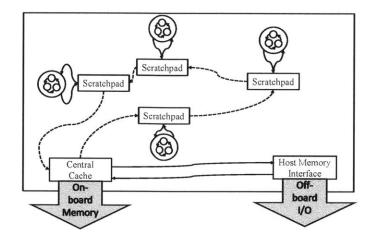

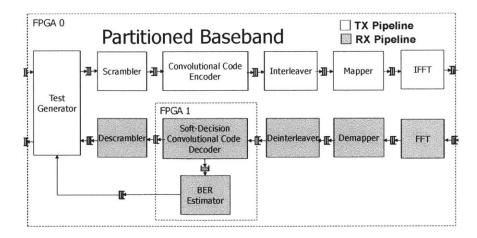

Figure 2-1: A sample program comprised of four modules and its mapping to an environment consisting of two FPGA platforms. Latency-insensitive channels between modules located on the same platform may be connected by a simple FIFO, while latency-insensitive channels that transit platforms are communicate via a service provided by the platform runtime. The platform drivers may also provide other services, for example, memory, which can also be accessed by latency-insensitive channels.

non-zero, buffering. When a programmer instantiates a latency-insensitive channel, they assert that these variations do not impact the functional correctness of their design.

The latency-insensitive channel abstraction gives the compiler great freedom in choosing the physical implementation of the channel. For example, the compiler may choose to implement the channel using a fixed-buffer, fixed-latency RTL FIFO. Alternatively, the compiler is free to choose a more complex implementation, including implementations in which the endpoints of the latency-insensitive channel are physically far apart. This freedom of choice permits the compiler to automatically map designs described in terms of latency-insensitive channels to multiple FPGAs,

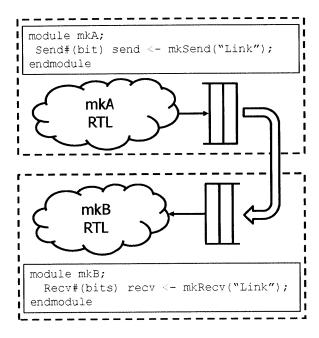

as shown in Figure 2-1. This thesis will use the syntax of Soft Connections [43], presented in Section 4.2.1, to denote latency-insensitive channels. Soft Connections simply designate to the compiler the endpoints of the latency-insensitive channels.

Latency-insensitive channels give great freedom to the compiler writer to transform hardware designs. However, if the use of latency-insensitive channels overly burdens the program writer, they are of little practical value. This thesis will show, via program examples, that the task of inserting latency-insensitive channels into a design does not significantly increase program complexity. Indeed, hardware designers frequently use FIFOs with latency-insensitive properties, but programming languages communicating these properties and compilers capable of leveraging these properties do not exist. Subsequent chapters will explore several large hardware programs which were originally expressed in RTL, but in a latency-insensitive style. As such, many of the hardware FIFOs in these designs were actually programmer-specified physical bindings of latency-insensitive channels. Thus, trivial textual substitution is sufficient to lift these physical FIFOs into the latency-insensitive channel abstraction, permitting the automatic mapping of these designs to multiple FPGAs. In practice, the design automation benefits obtained by using explicit latency-insensitive channels far outweigh the minimal programmer effort to explicitly demarcate latency-insensitive channels.

Once a program is expressed in terms of latency-insensitive channels, compiling that program to multiple FPGAs requires partitioning the program into latency-insensitive modules, modules that communicate only by way of latency-insensitive channels. In this thesis, programs are expressly constrained to be composed of latency-insensitive modules. Internally, modules may have whatever behavior the programmer sees fit, provided that the internal implementation honors the potential variability of the latency-insensitive interface. For example, once data has been obtained from an interface channel, it might pass through a traditional latency-sensitive hardware pipeline. Alternatively, although this thesis will consider only hardware latency-insensitive modules, modules could be implemented in software running on an FPGA-based soft-core, or even on an attached general-purpose processor. Module

internals do not matter; rather, it is the latency-insensitive interface that is fundamental.

The latency-insensitive channel formulation presented in this thesis is related to the burgeoning field of latency-insensitive, or elastic, design [7] [13] [40]. Work in this field, which will be discussed in detail in Section 3, can be grouped into two areas, latency insensitive design as a methodology and as a formalism for producing latency-insensitive implementations of arbitrary RTL. As a design methodology, latency insensitive design benefits programs in several ways, including lowered design times and simplified design-space exploration. This thesis treats latency-insensitive design primarily as a design methodology, but differs from previous works in that it provides explicit primitives which permit users to communicate information about latency-insensitive points in the design to the compiler.

Latency-insensitive design also exists as a formalism [6] [8] [61] for converting arbitrary latency-sensitive RTLs, which are referred to as synchronous state machines (SSMs) in the relevant literature, into latency-insensitive physical implementations. The main requirement of these transforms is that they preserve cycle-accuracy, such that the exact behavior of the original RTL implementation may be resolved. In contrast, the latency-insensitive channels formulated in this thesis are not required to preserve cycle-accuracy and may change design behavior at the cycle level to meet compilation goals, including mapping a program across multiple FPGAs. Latency-insensitive channels, as formulated in this thesis, are a programming abstraction for communication between points in a program, just as threads are a programming abstraction for parallel computation. The burden of reasoning about correctness, which has stymied previous, cycle-accurate tools, is pushed to the programmer, and the programmer must determine whether a particular point in the program can use a latency-insensitive channel safely.

# 2.2 Compilation and Execution of Latency-Insensitive Modules

Once a program has been formulated in terms of latency-insensitive modules, it must be mapped onto an environment for execution. An environment is an aggregation of platforms, each of which can execute latency-insensitive modules, joined together by an interconnect capable of carrying latency-insensitive channels. Depending on the underlying implementation of the particular module, it may be mapped to a variety of platforms for execution. For example, software modules can be executed on a general purpose processor or perhaps a soft-core on an FPGA. Hardware modules can be mapped to an FPGA or, if no FPGA is available or for simulation purposes, hardware modules may be executed on a general purpose CPU inside of a hardware simulator, as will be demonstrated in Chapter 7.

Platforms are subject to a handful of simple requirements, primarily related to inter-platform connectivity. Each platform in the environment must be linked by a pair of bi-direction, FIFO channels to at least one other platform. These interplatform channels must have guaranteed, in-order delivery. An environment, then, is a strongly-connected network of platforms.

Given a program comprised of latency-insensitive modules and an execution environment, the goal of a latency-insensitive module (LIM) compiler is to map the modules of the program on to the platforms of the environment. The first step in this mapping is to place specific modules on to specific platforms. Modules are treated as indivisible by the compiler, and only whole module placements are possible. Once this placement is known, the next task of the compiler is to synthesize an intermodule communication network, that is to choose a *physical* implementation for each latency-insensitive channel in the program. A significant contribution of this thesis is the automatic generation of an area efficient, high-speed, inter-FPGA network connecting latency-insensitive modules. This thesis also presents several automatic and user-directed optimizations which improve the performance of the generated network.

#### 2.3 Accessing Resources Across FPGAs

Real programs, both in hardware and in software, must make use of external devices. In software, dealing with physical devices, at least at a high level, can be straightforward. Software programs have general, well-defined, and highly-developed interfaces to devices, and interfaces such as sockets, virtual memory, and file systems are all relatively easy to use, to the point of being accessible to novice programmers. Moreover, these interfaces are stable across many machines, even those with radically different underlying physical hardware, permitting programs to be ported between machines, often with very little programmer intervention.

In contrast, device interfaces on the FPGA remain primitive. Programmers aiming to run programs on FPGAs must manually manufacture interfaces to raw, complex physical devices, and they must develop these interfaces for each FPGA platform they wish to use, even though the usage of physical devices is the approximately the same across many designs. These design issues represent a significant engineering effort and are only exacerbated by multiple FPGAs.

To illustrate the magnitude of the platform-interface problem, consider a design that has been fully debugged in simulation, but must be ported to an FPGA for evaluation. Porting the design to an FPGA requires bringing up various physical interfaces such as memory, clocks, and high-speed I/O and incorporating them into the existing design. These devices typically have non-trivial interfaces. Small errors, such as timing mismatches between the physical and simulation devices, are easy to make. Although trivial in scope, these errors can be extremely difficult to debug due to the limited visibility into and the lack of high-level debugging tools available for the FPGA. Without high-level debugging tools, finding errors in physical device interface logic degenerates to using an oscilloscope or, at a coarser grain, physical LEDs on the target board. These practical difficulties in FPGA use have limited the adoption of FPGAs as a general computation infrastructure.

A second issue with FPGA design, even when targeting single FPGAs, is design portability. Physical devices are inherently *platform-specific* and their interfaces are

fundamentally unportable. Moreover, if the programmer is not careful, any piece of user code touching these physical interfaces can inherit their unportability. This issue is particularly serious in latency-sensitive designs, in which circuits may well evolve, during the FPGA porting stage, to depend on particular device timings. These limitations have made it difficult to move designs from one FPGA platform to another, resulting in designs with limited re-usability and short life-spans.

Although design portability is an issue in single FPGA implementation, in multiple FPGA implementations, the problem of portability is a first-order concern. To use multiple FPGAs in any serious way, most, if not all, of a user design must be mappable to all of the FPGAs in a multiple FPGA system. However, as noted previously, any portion of the design that depends on a specific external resource, must be mapped to a specific FPGA. If enough parts of the user design are tightly coupled to specific FPGA resources, then multiple FPGAs are of limited use.

The solution to the physical interface problem and the platform portability problem is the same: latency-insensitive device abstraction. Just as in software, each FPGA platform provides a library of abstract, latency-insensitive interfaces to the physical devices available on that particular platform. Programs written using these abstract interfaces are insulated from behavioral and timing details of the underlying physical device. Both off-chip SRAM and off-chip DRAM can be captured using the same interface, and a program using this interface can alternatively use either SRAM or DRAM, depending on the platform, without a need for program modification. Because all platforms provide the same abstract interface, programs using these interfaces are portable.

In a multiple FPGA partitioning, each FPGA platform may have an instance of an external device, and a goal of a multiple FPGA compiler is to allow a program to make automatic use of these new resources across FPGAs. Abstract resource interfaces also provide a solution to the resource scaling problem. Once resource interfaces are expressed in an abstract manner, the compiler can be made aware of these resources and assist in scaling resources usage automatically, underneath of the abstraction layer.

## Chapter 3

### Related Work

This thesis presents a compiler that leverages explicit, language-level latency-insensitive channels to automatically produce multiple FPGA implementations. Much of the work in the thesis is novel, but it draws clear inspiration from prior research in the fields of FPGA operating systems, multiple-FPGA compilation, and latency-insensitive design.

The chapter begins with two sections discussing existing work conceptually related to the thesis: multiple FPGA compilation in Section 3.1 and latency-insensitive computing in Section 3.2. Both of these fields are relatively new, though latency-insensitive computing shares many theoretical ideas with the much earlier dataflow computing. This thesis represents a synthesis of ideas from both fields. Section 3.3 outlines the LEAP FPGA operating system, a general framework for supporting the use of external devices in single FPGA implementations. This thesis builds directly on the ideas of LEAP, extending it to support multiple FPGAs.

#### 3.1 Existing Multiple FPGA Compilers

Due to their generality and the incumbent overhead thereof, FPGAs cannot typically emulate the computational capacity realizable on a contemporary ASIC, and several FPGAs are required to emulate larger, next-generation ASIC designs. To solve this circuit emulation problem, multiple FPGA compilers appeared shortly after the in-

vention of the FPGA, and there exist a number of commercially available tools [26] [29] capable of emulating RTL designs using multiple FPGAs. Because these tools are intended for verification, they are required to maintain the cycle accurate behavior of all signals in the original RTL design. Existing partitioning tools are differentiated by whether they provide dedicated [67] or multiplexed [3] [27] chip-to-chip wires, but both styles of multiple-FPGA emulation incur significant performance degradation due to the maintenance of cycle accuracy.

Dedicated-wire partitioning tools resemble extended versions of traditional placeand-route tools, and include inter-FPGA link delays in the circuit-level timing equations for the determination of setup and hold times. The result is that the design

clocks are greatly slowed, since the delays of chip-to-chip wires are much longer than

on-chip delays. However, dedicated-wire partitioners produce board-level wires that

have a physical meaning, a property which may be useful in certain debugging regimes.

Dedicated-wire partitioners represent a true transliteration of the original RTL: no

effort is made at optimizing data transportation at FPGA boundaries. As a result, inter-chip data transportation may be extremely inefficient in terms of goodput,

due to the slow clock and the transportation of unused data. Another drawback of

dedicated-wire partitioning style is difficulty in timing closure: one FPGA failing to

make timing can require the repartitioning and recompilation of the entire design.

Multiplexed-wire or virtual-wire [3] partitioners differ from dedicated-wire partitioners in that inter-FPGA communication is abstracted from the emulation of the RTL design. Multiplexed-wire partitioners operate by first running a single clock cycle of the partitioned design on each FPGA, then propagating the resulting values across multiplexed inter-device links. When this inter-FPGA data exchange is complete and all FPGAs are synchronized, each FPGA steps another clock cycle and the process repeats. As with dedicated-wire partitioners, multiplexed-wire partitioners incur performance overhead due to the maintenance of the cycle accuracy. This overhead is manifest in the need to freeze the emulation clock while transporting data between FPGAs and in the need to synchronize FPGAs at the end of each time step. As a result, these partitioning tools do not typically exhibit high

performance, achieving cycle-accurate operating speeds of a few megahertz [55] [59]. Despite their drawbacks, multiplexed-wire partitioners represent a significant advance over dedicated-wire partitioning tools both because they permit more wires to cross between FPGAs and because they largely avoid the timing closure problems of the dedicated wire partitioners.

TIERS [54] offers an interesting optimization for multiplexed-wire partitioners: clock-skew-based pipelining. In the basic multiplexed-wire implementation, all FP-GAs operate on the same global clock cycle. However, this need not be the case: FPGAs can operate out of lock-step, provided that their inputs for a given cycle are available. In this manner, global synchronization can be obviated in favor of a distributed, data-flow style synchronization, improving overall emulation throughput. Similar pipelining effects are exploited in HAsim, described in Chapter 9.

Multiple FPGA compilation remains popular in industry, particularly in the context of emulating processors for the purpose of verification. IBM [2] has recently constructed a multiple FPGA platform for verifying a recent Bluegene processor. Intel [53] has also implemented a cycle-accurate version of its Nehalem core across a network of FPGAs for verification purposes. The IBM TwinStar system opts for full-system emulation of the original RTL, while the Intel Nehalem implementation admitted of some FPGA-friendly RTL modifications at the sub-cycle level. Both of these systems have dozens of FPGAs and run at effective speeds in the megahertz range.

This thesis presents an approach that is fundamentally different from existing tools and methodologies for multiple FPGA emulation: the compiler presented in this thesis is not required to maintain the cycle behavior or any relationship to the cycle behavior of an unpartitioned, single FPGA design. Latency-insensitive channels allow designers to explicitly annotate locations in designs at which it is safe to change cycle-by-cycle behavior of the design. As a result, partitions across these channels are free to run independently of one-another and operate on data as soon as it becomes available. Designs partitioned in this manner can take advantage of the natural pipeline parallelism inherent in hardware designs at a much finer grain than existing

optimized partitioners, such as TIERS [54]. Furthermore, the approach presented in this thesis enjoys an inter-FPGA bandwidth advantage over existing partitioners because only useful data is transported between FPGAs because only explicitly enqueued latency-insensitive channels are permitted to cross between FPGAs.

#### 3.2 Latency-Insensitive Design

Research into latency-insensitive design is divided into two areas: latency-insensitive design as design methodology and latency-insensitive design as a formal methodology for implementing arbitrary RTL designs. The former treatment places emphasis on the development time gains derived from latency-insensitive implementations, while the former works typically seek to convert existing RTL, referred to in the literature as synchronous sequential machines (SSMs), into a latency-insensitive representation of the SSM, thereby obtaining some useful property, such as timing closure.

As a methodology [13] [17] [39], latency-insensitive design has a number of advantages over traditional RTL implementation styles. Latency-insensitive design facilitates both modular refinement and architectural exploration. Latency-insensitive modules are easier to substitute for one another because changing the timing of a module in a latency-insensitive design does not impact the functional behavior of the other modules. For this reason, latency-insensitive design also facilitates module reuse. These properties stand in contrast to typical RTL implementations in which changing the cycle-over-cycle behavior of a single component of a design, for example, by inserting a pipeline stage, can precipitate a cascade of changes through the design, constraining exploration and preventing meaningful design reuse at the fine grain. Because latency-insensitive modules are isolated from one another in terms of timing behavior, development of a latency-insensitive design can be partitioned among many design teams.

Latency-insensitive design is related to the classical Khan process networks (KPN) [33] model of distributed computation. KPNs are comprised of sequential processes connected by unbounded FIFO queues. Writes to the queues are always non-blocking,

while reads are blocking. The latency-insensitive channel model of computation differs subtlety from KPNs, in that latency-insensitive channels have non-blocking reads, but this difference has enormous theoretical impact. The implication of non-blocking reads is that latency-insensitive modules are fully general, and may have any internal implementation, hardware or software. However, in exchange for this generality, useful properties of KPNs, including determinism, are not guaranteed for latency-insensitive channel-based designs.

The circuit design literature discusses a form of latency-insensitive design, called globally asynchronous, locally synchronous (GALS) design [57]. As the scale of integration and clock frequency increases, routing clock across an entire chip becomes power-inefficient and complicates timing closure. GALS arose as a solution to the problem of clock distribution in synchronous circuits. Effectively, GALS designs are partitioned into several clock islands, which communicate by way of an asynchronous, latency-insensitive network. In some formulations, clock islands may be gated when they are idle to conserve power. Most exploration into GALS has focused on on physical, circuit-level issues as opposed to models of computation.

Latency-insensitive channels subsume GALS: one possible physical implementation of a latency-insensitive channel is a synchronizer crossing between two differently-clocked modules. The compiler presented in this thesis is capable of recognizing that the endpoints of a latency-insensitive channel reside in different clock domains and will automatically instantiate the necessary domain-crossing logic. Moreover, it should be possible to extend this functionality to automate the generation of clock islands.

Although this thesis advocates the direct description of programs in terms of latency-insensitive channels, there are other ways in which such designs may arise: formal methodologies [6] [8] [61] for transforming arbitrary RTLs (SSMs) into latency-insensitive implementations. Transformation from an SSM to a latency-insensitive implementation is achieved by programmatically introducing new control circuitry and FIFO interconnects between partitions of the original SSM in a way that maintains the cycle-accurate behavior of the original SSM.

Originally [6], latency-insensitive transform techniques were proposed to aide in

timing closure for ASIC designs. By decoupling the cycle behavior of the original SSM from the physical circuit clock, these techniques permit the introduction, for example, of extra registered buffer stations, which, in the context of SoC designs, can dramatically improve overall system timing by eliminating long wire paths.

Latency-insensitive transformation tools are also applicable to FPGA-based designs. Recently [35] and [25] have applied latency-insensitive transformation techniques to aide in the FPGA timing closure and resource optimization problems. Here, the latency-insensitive transformation permits those portions of the original design that do not map well to FPGAs, for example content-addressable-memories, to be replaced either with multiple-cycle latency-insensitive implementations that do map well to FPGAs or with equivalent software implementations. In both applications of the latency-insensitive transformation, the number of physical cycles necessary to complete an operation increases relative to the original SSM, potentially reducing performance. However, clock frequency increases in the latency-insensitive implementation may counter some of this performance degradation. Latency-insensitive transforms may also be applied to produce multiple-FPGA mappings. In this respect, modern latency-insensitive transforms may be considered as the extremely refined successors of the original multiple FPGA partitioning tools, which obtained latency-insensitive designs through coarse clock manipulation.

Carloni [6] [7] appears to be the first to attempt the automatic transformation of arbitrary SSMs to latency-insensitive implementations. This approach takes a set of wire-connected SSMs and introduces wrappers to convert the SSMs into a latency-insensitive network consisting of wrapped SSMs connected by FIFO-like relay stations. The main requirement of this transform is that the SSMs be patient, that is that they may be stalled via external signal, a form of distributed flow control. However, as noted previously in this chapter, it is difficult to automatically discover whether an SSM is patient. Should an SSM not be patient, patience can be coerced through clock-gating.

Cortadella, Kinishevsky et. al. [8] [10] and Vijayaraghavan and Arvind [61] generalize the work of Carloni by presenting full-system transformations for trans-

lating arbitrary synchronous RTLs into latency-insensitive implementations through the introduction of latency-insensitive primitives. These latency-insensitive primitives replace primitive elements, such as gates and registers, of the original SSM and are connected using a latency-insensitive communication protocol. Cortadella et. al. introduce a latency-insensitive construction based around transparent latches and circuit handshaking, while Vijayaraghavan advocates the use of a protocol based on bounded FIFOS. Cortadella, Kinishevsky et. al. further refine [11] the latency-insensitive transformation to use dataflow-style data speculation, thereby improving throughput.

Attempts have also been made at manual conversion of SSMs to latency-insensitive designs. Pellauer et al. [45] provide a set of constructs, called A-Ports, that resolve the timing of processor models to FPGA timing, with the goal of resolving the cycle-accurate behavior of the modelled processor. Programmers insert A-Ports to track the timing of specific signals and events in their modelled processor, while other signals in the model implementation remain untracked. Although A-Ports are not an automatic transformation, they offer greater potential performance since parts of the processor model which are not of interest may run independent of the A-port scheme. A-Ports themselves use the latency-insensitive channels advocated by this thesis as an internal communications mechanism.

The above transformational techniques all maintain some notion of the original cycle behavior of the base SSM. The model of computation presented in this thesis, in Chapter 2.1, expressly allows the compiler to modify the cycle behavior of the original design, disregarding the bijective-mapping requirement of existing cycle-accurate latency-insensitive transformations, in exchange for increased performance. In the context of multiple FPGAs, there are powerful technical motivations to discard this requirement: inter-FPGA links have long latencies, which can only be hidden by effective pipelining. The approach presented in this thesis can take advantage of the natural, pipelined behavior of hardware designs, even in the context of systems with high degrees of inter-FPGA feedback, while cycle-preserving transformations generally cannot.

Although the compiler presented in this thesis provides no inherent guarantees relating to cycle-accuracy, it can be readily composed with cycle-preserving transformation tools, should the cycle-accuracy of some signals be required. Indeed, one of the example codes presented in this thesis, HAsim (Chapter 9), uses the A-Ports technique. In association with these transform tools, the compiler presented in this thesis can be used to verify any synchronous design, including those designs written in a latency-sensitive style. However, there is no free lunch: as the number of cycle-accurate signals increases, multiple FPGA implementations derived from latency-insensitive channels will degrade in performance until they reach parity with traditional cycle-accurate multiple FPGA partitioning tools. Conversely, the closer a latency-insensitive channel-based multiple FPGA implementation is to pure data flow, the faster it will be.

#### 3.3 The LEAP FPGA Operating System

This thesis leverages the LEAP [42] FPGA operating system and extends it to support multiple FPGAs. LEAP was developed to speed the implementation of FPGA-based systems and to ease the burden of migration between FPGA platforms by providing abstract, latency-insensitive channel-based device interfaces, between FPGA programs and FPGA platforms. Since all LEAP designs use the same interfaces, interfaces need be implemented only once per FPGA platform. Conversely, because physical interfaces are held constant across platforms, all LEAP programs can run on all LEAP-supported FPGA platforms. This second property of LEAP platforms is essential to the automatic implementation of latency-insensitive programs across multiple FPGAs.

In the LEAP virtualization framework, physical devices, such as memory, expose scalable, abstract, latency-insensitive request-response interfaces to the programmer. An example of a standard interface provided by LEAP is memory, which will be given a detailed treatment in Chapter 7. In LEAP, user-level designs interface to memory by means of a simple read-request, read-response, write interface [1]. Designs may

instantiate as many of these memory interfaces as the choose. At compile time, LEAP instantiates a set of caches and marshalling logic for each exposed user memory and ties these to the specific physical memory attached to the target platform.

In addition to memory, LEAP provides other generally useful device libraries and services to the FPGA programmer. The remote request-response protocol, RRR [41], is an automated mechanism for connecting FPGA programs to software running on a host PC. LEAP also provides an implementation of the Unix Standard I/O library, including an FPGA-based implementation of printf. LEAP also provides a single-FPGA implementation of Soft Connections [43], a syntax for describing both named, latency-insensitive point-to-point channels and named, latency-insensitive rings, which permit multiple ring stops to share a form of broadcast communication. The LIM compiler adopts Soft Connections, described in full in Section 4.2.1, as a syntax for latency-insensitive channels.

LEAP originally targeted single FPGA implementation. However, the platform abstraction advocated by LEAP can be scaled to implementations that span multiple FPGAs. Often, simple services or those with low performance requirements can be implemented directly on multiple FPGAs, without modifying the original LEAP source. On a single FPGA, LEAP device interfaces and services are typically implemented using Soft Connection point-to-point links or Soft Connection rings. Since the LIM compiler treats Soft Connections as the fundamental unit of communication between FPGAs, it can automatically scale some existing single-FPGA LEAP services to a multiple-FPGA implementation. For example, the LEAP STDIO library uses a ring to provide printf services to the user design. Scaling this service to more FPGAs requires only that the STDIO rings be able to span multiple FPGAs.

A good multiple-FPGA operating system will go beyond simply providing services on each FPGA. Rather, it will automatically claim and expose to the program any new resources that become available as a result of adding FPGA platforms to the system. In multi-core processors, threads mapped to different cores make use of not only the additional processor, but also additional cache resources. As in a multiprocessor, each FPGA typically has its own set of local resources, for example a memory interface. To

provide similar functionality in the context of multiple-FPGAs, performance critical services, such as memory, require a multiple-FPGA specific extension of the LEAP OS. Chapter 7 will present a mechanism by which these resources may be made available to user programs automatically, without requiring program modification.

# Chapter 4

# Multiple FPGA Compilation

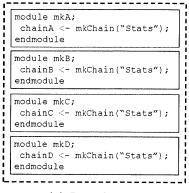

Abstractly, the LIM compiler operates on the latency-insensitive modules and channels described in Chapter 2.1. However, all compilers must have a concrete syntax to operate on. The designs described in Chapters 8, 9, and 10 were written in Bluespec System Verilog [4], a commercially available high-level synthesis language. To support these designs, the LIM compiler operates on Bluespec System Verilog. The internal RTL representation of the latency-insensitive modules handled by the LIM compiler is simply Bluespec<sup>1</sup>, while latency-insensitive channels are denoted using the Soft Connections [43] syntax, an extension to the base Bluespec syntax, which will be described in Section 4.2.1. Thus, the current implementation of the LIM compiler is best viewed as an extension of Bluespec System Verilog and its compiler, though the compilation scheme presented in this chapter generalize to all hardware descriptions augmented with latency-insensitive channels.

Implementations produced by the LIM compiler execute on top of some environment comprised of one or more FPGAs. Producing such implementations requires detailed knowledge of the FPGA environment configuration and the physical capabilities of each FPGA, for example, the availability of memory resources. Section 4.2.2 details how this information is conveyed to the compiler. Section 4.3 describes in detail the implementation of the LIM compiler and its internal algorithms. The LIM

<sup>&</sup>lt;sup>1</sup>Bluespec, itself, supports a notion of modules, but these modules may have arbitrary, latency-sensitive interfaces. The latency-insensitive modules operated on by the LIM compiler have no direct syntactic representation in Bluespec.

compiler relies on Bluespec, a closed-source, commercial tool, as a subroutine. Section 4.4 describes the way in which the LIM compiler integrates Bluespec and the implementation issues that result from Bluespec's limited external interface.

## 4.1 Compiler Overview

The goal of the LIM compiler is to map a program comprised of latency-insensitive modules on to an environment comprised of multiple FPGAs. The chief property of latency-insensitive modules that permits this mapping is that their interfaces are comprised solely of latency-insensitive channels, the implementation of which may be chosen by the compiler without affecting the functional correctness of the original user program. Thus, communicating modules may reside on the same FPGA and communicate via a simple hardware FIFO or on two different FPGAs and communicate over some complex network interconnect.

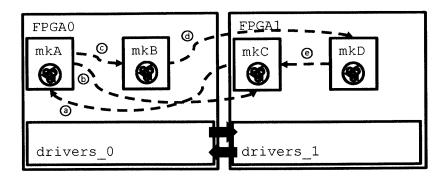

Conceptually, the LIM compiler takes user source, described in terms of RTL, Bluespec, augmented with latency-insensitive channels, Soft Connections, as input and produces a set of programming files for a target execution environment. Because the LIM compiler operates on a commercial language, in addition to its own algorithms, the LIM compiler must make heavy use of Bluespec as a subroutine. The LIM compiler relies on two passes of the Bluespec compiler. The first pass of the Bluespec compiler produces a kind of primitive intermediate representation of user program, upon which the LIM compiler operates. The LIM compiler then analyzes this program representation and synthesizes a new Bluespec program for each FPGA platform in the target execution environment. These generated platform programs consist of a stylized version of the latency-insensitive modules mapped to that platform combined with a synthesized network which provides a physical implementation of the latency-insensitive channels of those modules. The second pass of the Bluespec compiler produces Verilog implementations of programs produced by the LIM compiler, and this Verilog is compiled by an FPGA-vendor tool chain to produce a final implementation for each FPGA.

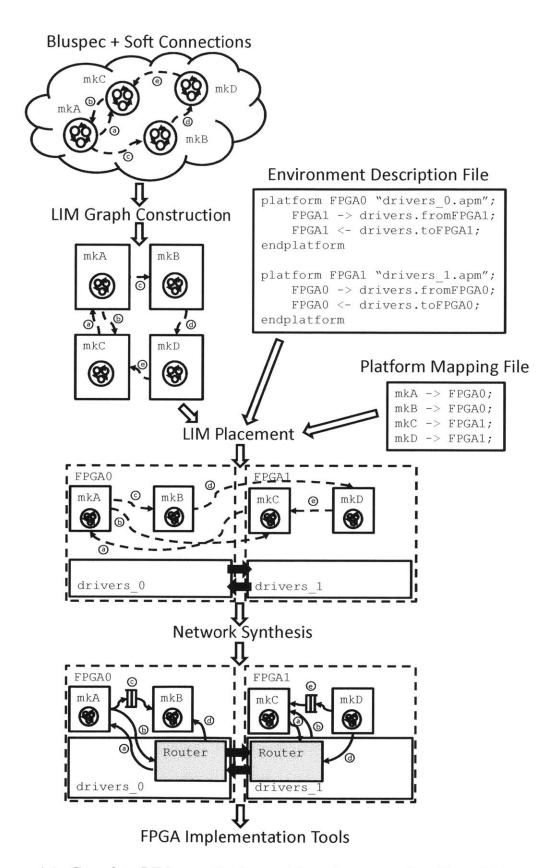

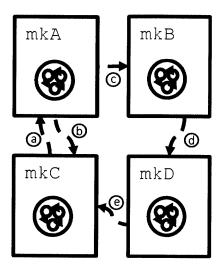

Figure 4-1: Complete LIM compiler flow, with syntax examples. Dotted lines represent logical connections, while elaborated connections are solid.

Figure 4-1 shows the flow of the LIM compiler along with its source inputs. The compiler is composed of three main phases, which occur sequentially after an initial parsing of the user program. These three phases are: the construction of graph representation of the latency-insensitive modules and channels of an input program; the mapping of that graph to a physical execution environment consisting of multiple FPGA platforms and their various physical resources; and the synthesis of a inter-module communications network for carrying data between latency-insensitive modules. At the end of these three phases, the LIM compiler produces a Bluespec program for each FPGA in the execution environment. The LIM compiler then proceeds to invoke Bluespec and the FPGA synthesis tool chain to produce a physical implementation.

#### Building a Latency Insensitive Module Graph

LIM compilation begins after an initial pass of the Bluespec compiler. This Bluespec invocation produces a set of log files, which can be parsed by the LIM compiler to produce a representation of the user program latency-insensitive modules and the latency-insensitive channels associated with each module. Once this data has been obtained from Bluespec, the LIM compiler builds a dataflow graph representation of the program: the LIM graph. In the LIM graph, edges correspond to the latency-insensitive channels, while vertices correspond to the synchronous RTL internals of the latency-insensitive modules. This graph will be processed by subsequent phases and eventually used to produce a physical implementation.

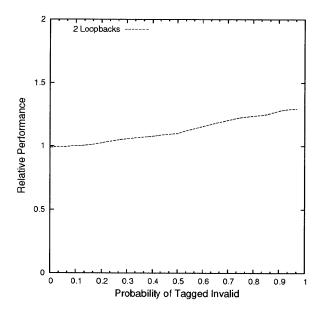

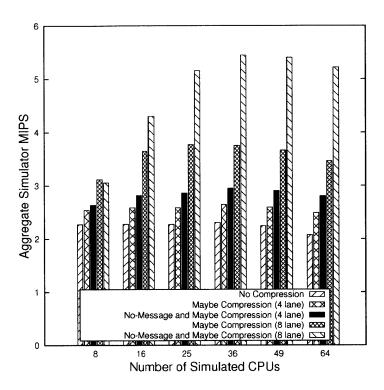

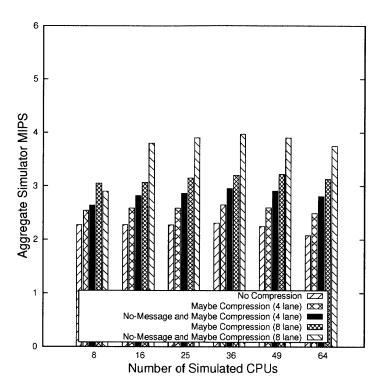

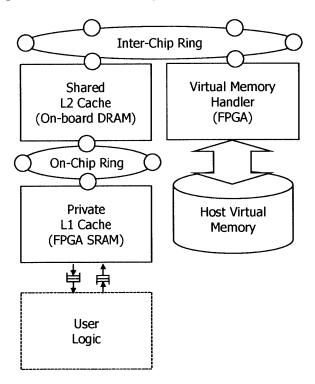

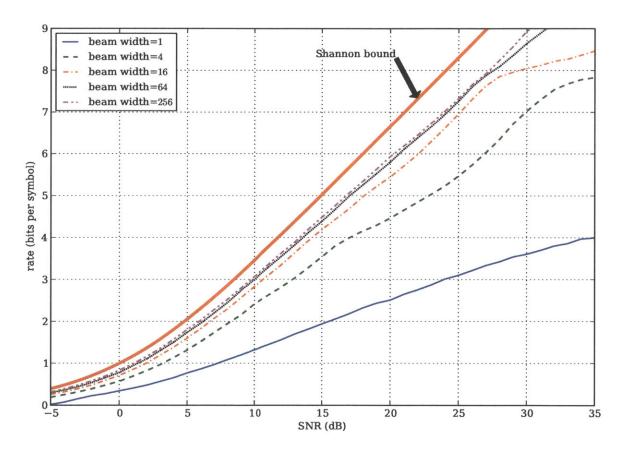

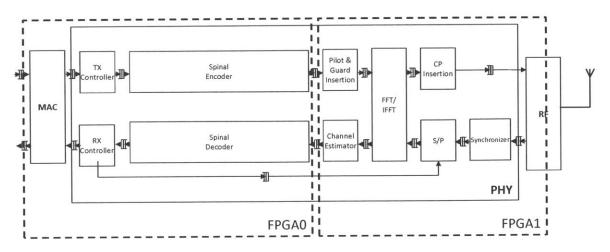

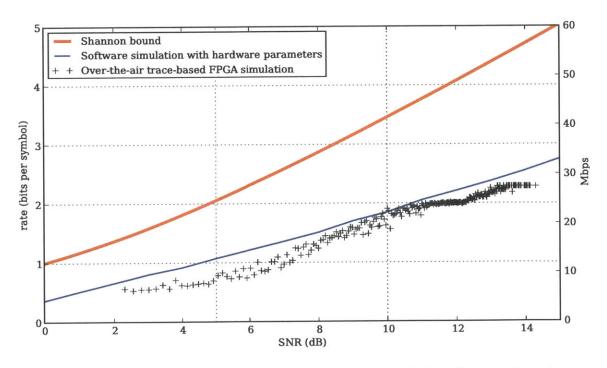

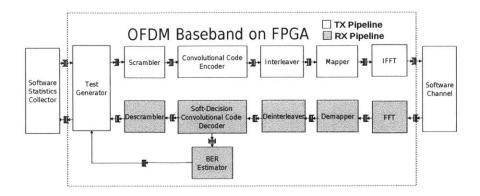

#### Mapping LIM Graph to Execution Environment