# Field Programmable Gate Arrays for Radar Front-End Digital Signal Processing

by

Tyler J. Moeller

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degrees of

Bachelor of Science in Electrical Engineering and Computer Science

and

Master of Engineering in Electrical Engineering and Computer Science

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

May 22, 1999

Copyright © 1999 Tyler J. Moeller. All Rights Reserved.

The author hereby grants to M.I.T. permission to reproduce and distribute publicly paper and electronic copies of this thesis and to grant others the right to do so.

|                | Author                                                                    |

|----------------|---------------------------------------------------------------------------|

|                | Department of Electrical Engineering and Computer Science<br>May 22, 1999 |

| ****           | Supervised by                                                             |

| visor<br>atory | Supervised by                                                             |

|                |                                                                           |

| visor          | Certified by                                                              |

| ience          | Assistant Professor, M.I.T. Laboratory for Computer Science               |

|                | Accepted by                                                               |

|                | Arthur C. Smith                                                           |

| neses          | Chairman, Department Committee on Graduate Theses                         |

## Field Programmable Gate Arrays for Radar Front-End Digital Signal Processing

by

Tyler J. Moeller

Submitted to the Department of Electrical Engineering and Computer Science

May 22, 1999

In Partial Fulfillment of the Requirements for the Degrees of Bachelor of Science in Electrical Engineering and Computer Science and Master of Engineering in Electrical Engineering and Computer Science

#### Abstract

As field programmable gate array (FPGA) technology has steadily improved, FPGAs have become viable alternatives to other technology implementations for high-speed classes of digital signal processing (DSP) applications. In particular, radar front-end signal processing, an application formerly dominated by custom very large scale integration (VLSI) chips, may now be a prime candidate for migration to FPGA technology. As this thesis demonstrates, current FPGA devices have the power and capacity to implement a FIR filter with the performance and specifications of an existing, in-system, front-end signal processing custom VLSI chip. A 512-tap, 18-bit FIR filter was built that could achieve sample rates of 7 MHz (with a clock rate of 117 MHz) using Xilinx Virtex FPGA technology, and was demonstrated through simulation and hardware implementation. Distributed arithmetic, bit-level systolic arrays, parallel multiplier/accumulator (MAC) cells, fast FIR algorithms, and frequency domain filtering were investigated to determine the most optimal structure for a FPGA FIR design, with distributed arithmetic resulting in the best performance. A custom VHDL cell-based layout tool was designed to improve the placement strategies of the Xilinx FPGA place and route tools, and improved the speed performance of the distributed arithmetic design by 37%.

Thesis Supervisors:

David R. Martinez Group Leader, Digital Radar Technology Group, MIT Lincoln Laboratory

Saman P. Amarasinghe Assistant Professor, MIT Laboratory for Computer Science

# Acknowledgments

I'd like to thank...

Dave Martinez for being interested in and for giving me a reconfigurable-computing project for my thesis, for supporting, encouraging, and funding my work, for encouraging me to submit a paper [MM99] to and participate in the 1999 Field-Programmable Custom Computing Machines Symposium, and for allowing me to co-author a paper for the *Journal of VLSI Signal Processing Systems* [MMT00]. My thesis work has been in an area that I find very interesting and think has a lot of promise for the future.

Saman Amarasinghe for being my thesis advisor at MIT. Your research interest in reconfigurable computing helped better my understanding of the subject and how it might apply to signal processing. I really appreciate your support, advice, and reading of my thesis in a short period of time.

Bill Song for being my mentor for three years, for trusting me and giving me a lot of freedom within unbelievable, mission-critical projects unusual for an intern to work on, for helping me with school and career decisions, and for teaching me a lot about working with cutting-edge technologies.

Mike Killoran for continuously and selflessly helping me with programming issues and design ideas, giving me moral support when I was stressed out, and being someone I could always turn to at Lincoln to bounce something off of or joke around with. Your FIR and other utility programs were a huge help.

Bob Ford at Lincoln and Brent Nelson at BYU for giving me the original idea for this thesis and providing support along the way; Ed McGettigan at Xilinx for providing me optimized Virtex multipliers and tirelessly giving me Virtex support directly from the applications group at Xilinx; Huy Nguyen for helping me with my MATLAB simulations and fixed-point noise analyses; Harry Levinson for endlessly helping me with my computer, and for installing all the software and hardware I needed.

Edith Gardner, Bob D'Ambra, and Jack Selfridge for putting up with me for three years and making my internship a lot of fun.

All my friends who made the past five years the best of my life. I don't know how I found you all, but thanks, and I will never forget you. We'll keep in touch.

My parents, who made MIT possible for me and never stopped supporting me or losing faith in me through thick and thin.

And Maggie. You've been there when I've been stressed or worried about this thesis, school, or anything. Thanks for always making me happy and being the one person I can *always* turn to. You've made the last year of my life incredible.

# **Table of Contents**

| 1 | Int | roduction                                              | 15        |

|---|-----|--------------------------------------------------------|-----------|

|   | 1.1 | Thesis Overview                                        | 15        |

|   | 1.2 | Contributions                                          | 16        |

|   | 1.3 | Outline of Thesis                                      | 17        |

| 2 | Ba  | ckground                                               | 19        |

|   | 2.1 | Radar Digital Signal Processing Development            | 19        |

|   | 2.2 | Reconfigurable Computing for Digital Signal Processing | 20        |

|   | 2.3 | FPGA Trends                                            | 23        |

|   | 2.4 | Radar Front-End Digital Signal Processing              | 25        |

| 3 | Cu  | stom VLSI Implementation                               | <b>27</b> |

|   | 3.1 | Overview                                               | 27        |

|   | 3.2 | Custom VLSI Architecture                               | 29        |

|   | 3.3 | Custom VLSI Noise Analysis                             | 30        |

| 4 | Pr  | oblem                                                  | <b>35</b> |

|   | 4.1 | FPGA Benefits to Radar Front-End Signal Processing     | 35        |

|   | 4.2 | Problem                                                | 36        |

| 5 | Xil | inx Virtex FPGA Technology                             | 39        |

|   | 5.1 | FPGA Selection                                         | 39        |

|   | 5.2 | Virtex Overview                                        | 39        |

|   | 5.3 | Computational Unit Implementation                      | 43        |

| 6 | Alg | gorithms and Techniques                                | <b>45</b> |

|   | 6.1 | Overview                                               | 45        |

|   | 62  | FIR Filtering                                          | 45        |

|   | 6.3 | Parallel Multipliers and Accumulators                  | <b>4</b> 5 |

|---|-----|--------------------------------------------------------|------------|

|   | 6.4 | Bit-Level Systolic Array                               | 50         |

|   | 6.5 | Distributed Arithmetic                                 | 53         |

|   | 6   | 3.5.1 Parallel Distributed Arithmetic                  | 60         |

|   | 6.6 | Fast FIR Algorithm                                     | 62         |

|   | 6.7 | Frequency Domain Filtering                             | 65         |

|   | 6   | 5.7.1 Pipelined FFT                                    | 68         |

|   | 6   | 5.7.2 FFT Convolution                                  | 70         |

|   | 6   | 3.7.3 Noise Analysis                                   | 71         |

| 7 | Im  | plementation                                           | <b>7</b> 3 |

|   | 7.1 | Verification                                           | 73         |

|   | 7.2 | Parallel Multipliers and Accumulators                  | 73         |

|   | 7.3 | Bit-Level Systolic Array                               | 75         |

|   | 7.4 | Distributed Arithmetic                                 | 77         |

|   | 7   | 7.4.1 Distributed Arithmetic Four-Tap Group            | 77         |

|   | 7   | 7.4.2 Linear Summer Network                            | <b>7</b> 9 |

|   | 7   | 7.4.3 Achieving 40 MHz Performance For 5 MHz Data Rate | 82         |

|   | 7.5 | Fast FIR Algorithm                                     | 83         |

|   | 7.6 | Frequency Domain Filtering                             | 86         |

| 8 | CE  | LL_MAKER Custom Layout Tool                            | 91         |

|   | 8.1 | Motivation                                             | 91         |

|   | 8.2 | Operation                                              | 93         |

|   | 8   | 2.2.1 RLOC Placement Constraints                       | 94         |

|   | 8   | 2.2. Parameter Passing                                 | 96         |

|   | 8   | 2.3 Generate statements                                | 97         |

| 8.2.4 Cm_expressions and Conditional Constraints | 98  |

|--------------------------------------------------|-----|

| 8.2.5 Output                                     | 99  |

| 8.2.6 CELL_MAKER Example                         | 99  |

| 8.3 CELL_MAKER on Linear Systolic DA Design      | 101 |

| 9 Results                                        | 105 |

| 9.1 Implementation Results                       | 105 |

| 9.2 Power Consumption                            | 107 |

| 10 Physical Implementation                       | 109 |

| 10.1 Annapolis Microsystems Starfire Board       | 109 |

| 10.2 Implementation                              | 109 |

| 11 Conclusions                                   | 111 |

| References                                       | 113 |

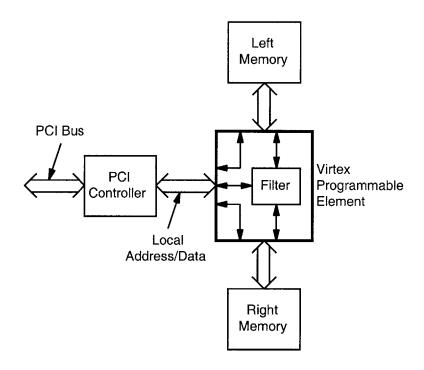

# **List of Figures**

| Figure 2.1: Growth in FPGA Performance Versus Process Geometry               | 24 |

|------------------------------------------------------------------------------|----|

| Figure 2.2: Growth of Computational Capability for Xilinx FPGAs              | 25 |

| Figure 2.3: Typical Radar Signal Processing Flow                             | 26 |

| Figure 2.4: Digital In-phase and Quadrature Sampling Architecture            | 26 |

| Figure 3.1: Custom VLSI Chip                                                 | 28 |

| Figure 3.2: Custom VLSI Chip Architecture                                    | 30 |

| Figure 3.3: Rounding Noise Approximation                                     | 31 |

| Figure 5.1: Block Diagram of Virtex CLB (Two Slices)                         | 41 |

| Figure 5.2: Virtex Block Diagram                                             | 42 |

| Figure 6.1: Direct Parallel Multiplier and Accumulator FIR Structure $\dots$ | 46 |

| Figure 6.2: Parallel MAC Filter With Summer Tree                             | 47 |

| Figure 6.3: Transposed Form Parallel MAC Filter                              | 48 |

| Figure 6.4: Direct Form Pipelined MAC Fir Filter                             | 49 |

| Figure 6.5: Eight Taps Per MAC FIR Filter                                    | 51 |

| Figure 6.6: Bit-Level Systolic Array                                         | 52 |

| Figure 6.7: Bit-Serial Multiplier                                            | 55 |

| Figure 6.8: Four MAC Filter Using Bit-Serial Multiplier                      | 56 |

| Figure 6.9: Serial Distributed Arithmetic FIR                                | 57 |

| Figure 6.10: Serial Distributed FIR Using LUT                                | 58 |

| Figure 6.11: 16-Tap Serial Distributed FIR                                   | 61 |

| Figure 6.12: 2-Bit Parallel Distributed Arithmetic FIR                       | 62 |

| Figure 6.13: Traditional Two-Parallel FIR Filter Implementation              | 64 |

| Figure 6.14: Two-Parallel FFA Implementation                                 | 65 |

| Figure 6.15: Four-Parallel FFA Implementation                                | 66 |

| Figure 6.16: Eight-Point Decimation-In-Frequency FFT 6              |

|---------------------------------------------------------------------|

| Figure 6.17: Decimation-In-Frequency Butterfly                      |

| Figure 6.18: Pipelined FFT Butterfly Module                         |

| Figure 6.19: Eight-Point Pipelined FFT Architecture Block Diagram 7 |

| Figure 7.1: 16-Tap Parallel MAC Unit                                |

| Figure 7.2: Four-Tap Group                                          |

| Figure 7.3: Linear Summer Network for SDA                           |

| Figure 8.1: Placed and Routed Linear Systolic DA Design             |

| Figure 8.2: CELL_MAKER Applied to Linear Systolic DA Design 10      |

| Figure 10.1: Starfire Board With Filter                             |

# **List of Tables**

| Table 6.1: Two Taps Per MAC FIR Filter Example         | 50  |

|--------------------------------------------------------|-----|

| Table 6.2: Contents of 4-Tap LUT                       | 58  |

| Table 7.1: Frequency Domain Filtering Output Precision | 87  |

| Table 9.1: Area and Performance Results                | 105 |

# Chapter 1

### Introduction

#### 1.1 Thesis Overview

As field programmable gate array (FPGA) technology has steadily improved, reconfigurable computing using FPGAs has become a viable alternative to other technology implementations, including custom very large scale integration (VLSI) devices and processor-based systems, for high-speed classes of digital signal processing (DSP). In particular, radar front-end signal processing, an application formerly dominated by custom VLSI chips, may now be a prime candidate for migration to FPGA technology.

To demonstrate the feasibility of using reconfigurable computing to implement radar front-end signal processing, FPGA-based DSP solutions meeting the specifications of an existing, in-system, radar front-end custom VLSI chip were investigated. These specifications required a 512-tap real finite impulse response (FIR) filter be built that could operate on 16-bit data and 18-bit coefficients while outputting results with 18-bits of precision with a sample rate of 5 MHz and a clock rate of 40 MHz. Two banks of coefficients were required so that one could be active while another was loaded in the background. The designs were implemented in the largest FPGA available today, the Xilinx Virtex XCV1000.

The designs considered included distributed arithmetic, bit-level systolic arrays, parallel multiplier/accumulator (MAC) cells, fast FIR algorithms, and frequency domain filtering. Implementations using distributed arithmetic,

parallel MAC cells, and fast FIR filtering were built and simulated. All of these designs met the custom VLSI chip's design specifications and exceeded its performance, with a distributed arithmetic design using linear-systolic cells having the best performance (7 MHz sample rate). An eight-tap distributed arithmetic design was implemented on an Annapolis Micro Systems Starfire reconfigurable-computing engine.

To improve upon a poor linear-systolic design placement strategy by the synthesis and FPGA tools, a custom VHDL placement tool, CELL\_MAKER, was built that could read VHDL, extract user placement constraints, and construct a placement strategy for the final FPGA. This tool improved the performance of the linear design by 37% due to layout alone.

This thesis demonstrates that current FPGA devices have the power and capacity to implement a FIR filter with the performance and specifications of an existing, in-system, front-end signal processing custom VLSI chip.

#### 1.2 Contributions

This thesis contributes new research or data in several areas:

- 1. A unique parallel MAC design using shift registers to store the inputs when multiple taps per MAC are computed instead of using RAM to store the multiplier outputs was constructed, simulated, and area and performance results were determined.

- 2. A distributed arithmetic design was built that did not require constant coefficients. Instead, it could operate on two banks of coefficients (one active, one loadable), and was built, simulated, and implemented in hardware. Two variations of this design, one using a tree approach for summing the individ-

ual cell's outputs together, and the other using a linear-systolic approach were built, and area and performance results were determined.

- 3. A new approach to reducing a parallel MAC design's area using fast FIR algorithms was developed. A filter using this approach was constructed, simulated, and area and performance results were determined.

- 4. Area figures for a pipelined radix-2 FFT-based filter in the frequency domain were calculated.

- 5. The performance limitations of the linear-systolic distributed arithmetic design (which should have been the fastest design) were determined to be due to the placement strategy of the design, as it was not placed in a linear-systolic fashion. A custom tool was built to solve this problem that could read user-inserted constraints in the design's VHDL code and generate a file with placement constraints for the Xilinx place and route tools to use. This tool improved the design's performance by 37%.

- 6. The power and performance in terms of billions of operations per second (GOPS) were calculated for the linear-systolic distributed arithmetic design.

#### 1.3 Outline of Thesis

Chapter 2 discusses the background for the research in this thesis, including reconfigurable computing for DSP using FPGAs, trends in FPGA development, and radar front-end signal processing. Chapter 3 gives an overview of a custom VLSI design built and used at MIT Lincoln Laboratory for a particular radar front-end signal processing system, including a description of its features, architecture, and an analysis of its output precision due to internal round-off noise. Chapter 4 discusses the problem this thesis investigated,

which was building a FPGA implementation to meet the specifications of the custom VLSI chip, and why a FPGA implementation would be beneficial. Chapter 5 gives an overview of the FPGA used in this thesis, the Xilinx Virtex. Chapter 6 provides a background on each of the algorithms or design techniques investigated for implementing a FPGA-based FIR filter, and Chapter 7 presents the particulars and implementations of each algorithm or technique as applied to the design problem discussed in Chapter 4 within a Virtex FPGA. Chapter 8 introduces the custom placement tool, its motivation, operation, and results as applied to the linear-systolic distributed arithmetic design. Chapter 9 summarizes the area and performance results for each implementation built in a Virtex FPGA, and calculates the power and GOPS for the best implementation (linear-systolic distributed arithmetic after using the custom placement tool). Chapter 10 discusses how an eight-tap version of the distributed arithmetic design was implemented in real hardware, and Chapter 11 presents the conclusions of this thesis.

# Chapter 2

# Background

#### 2.1 Radar Digital Signal Processing Development

Until recently, the first few stages of radar signal processing after an incoming radar signal was acquired were performed in the analog domain. As analog to digital converters (ADCs) have become faster in recent years, and digital hardware has become more capable, the trend has been to move the analog to digital converter closer to the radar antenna in the signal processing chain and perform more processing in the digital domain. Digital hardware offers more robust system stability, more flexibility in waveform and filter design, the ability to develop adaptive processing algorithms such as beamforming, adaptive nulling, or space-time adaptive processing that require fast changes in hardware configurations and system coefficients, and an easier upgrade path as digital electronics continue to advance. [MMT00]

As more and more front-end radar signal processing functions are moved into the digital domain, the signal processing requirements for the digital hardware executing them increases dramatically. This is due to fast ADC sampling rates, large numbers of sensor channels, and stringent requirements on filter designs. The computational demands range from tens to hundreds of billion operations per second (GOPS), as data throughputs often range in the hundreds of megabytes per second (MBytes/sec). Further restrictions on the digital hardware include size, weight, power, environment, and shock constraints as digital radar systems are fielded in platforms ranging from early

warning radars, unmanned air vehicles, fighters, and space-borne surveillance and targeting radars. [MMT00]

For the past several years, commercially available digital signal processors (DSPs) or reduced instruction set (RISC) microprocessors have not been able to meet the system requirements for front-end radar signal processing. However, this processing is often very regular, is highly parallel, and is usually independent of the data. Therefore, most implementations to date have used either commercially available, dedicated, computing engines or custom very large scale integrated-circuit (VLSI) designs. [MMT00, Hau98, BAK96]

One such custom VLSI design was recently fielded at MIT Lincoln Laboratory that is capable of operating at 100 GOPS. It has the ability to change banks of coefficients in a few milliseconds, and is channel parallel, meaning it can be scaled to many hundreds of GOPS as the number of radar input channels is increased. [MMT00, Gre96]

#### 2.2 Reconfigurable Computing for Digital Signal Processing

In the late 1980s and early 1990s, the conventional wisdom where hardware was fixed at design time and software contained the flexibility in a system was reexamined. The presence of chips (such as field programmable gate arrays, or FPGAs) that could adapt to the current demands of an application lead to the adoption of "generic" hardware, in which FPGAs, microcontrollers, and other reprogrammable parts could be combined together on a single board that could be reconfigured to serve many different applications. A computing device would not need to be as generic as a microprocessor, as reconfigurable elements could form special-purpose hardware to solve a specific problem, but

would be flexible enough to change that special-purpose function to another function upon demand. [Hau98, BAK96]

The ability of a system to change its functionality in hardware instead of in just software lead to the development of reconfigurable computing. Hardware was now able to become the medium for general-purpose computing, as it could adapt itself to compute algorithms normally handled by a processor. As the requirements for the algorithms changed, so could the hardware. Because the algorithms were being executed directly by hardware instead of by a computer that was fetching and decoding instructions sequentially, they would gain the performance boost inherent in being executed, in parallel, by processing units precisely designed for the algorithm. [Hau98, BAK96]

Currently, reconfigurable computing is a niche research field—it is not applicable for all applications. However, for applications characterized by deeply pipelined, highly parallel, and integer arithmetic processing, reconfigurable computing machines have shown performance improvements of an order of magnitude or more at a low cost. This is because current reconfigurable computing mediums are usually characterized by arrays of highly-replicated, pipelined, functional blocks. An algorithm that can be broken into many parallel tasks will map well into this architecture, especially if it is easily pipelined. A more complicated, irregular, structure will not map well into this architecture, as the number of unique functional units required to implement an irregular algorithm may surpass the capacity of even a large sized configurable computer. [Hau98, VH98]

A microprocessor achieves a variety of different functions temporally by executing multiple functions sequentially, during different cycles, while reconfigurable computing solutions achieve a variety of functions spatially by having different logic elements compute different functions. Therefore, microprocessors will execute irregular computations and complex data-flow manipulations better, while reconfigurable computing machines can be superior for data-parallel applications, where large amounts of data must be acted on in a similar manner. Some examples of tasks that are suitable for configurable computing include: image processing, pattern matching, target recognition, cryptography, filtering, convolution, FFTs, and some database tasks [Hau98, VH98].

FPGAs are a good medium for custom computing applications because of their highly-replicated regular structure of configurable logic combined with many pipeline registers that can be easily programmed to perform a series of parallel computing tasks. As FPGAs have grown in capacity, improved in performance, and decreased in cost, FPGA based custom computing machines have become an ideal medium for DSP applications. Several studies performed by Xilinx, researchers at BYU, Intel, and other institutions have shown that a single FPGA can outperform a DSP chip by an order of magnitude or more for pipelined, parallel DSP applications [ASR98, PH95, Gos96a, Xila, Kna95, VH98, Con96].

As FPGA technology has improved over the past several years, it may now be feasible to field a reconfigurable computing solution to the radar front-end signal processing problem instead of a custom VLSI solution. Such a solution would be more cost effective (typically FPGAs have a much lower cost per-part than custom chips due to non-recurring engineering costs and time-to-market factors for production runs of 100,000 to 400,000 units [Liu95]) and will

require less time and fewer resources for design, development, testing, and fielding than custom VLSI. In addition, because of the high demand and general purpose nature of FPGA devices, FPGA manufactures have the ability to reap the benefits of the latest reductions in lithography feature size, enabling FPGAs to take advantage of technologies that may not be available for custom VLSI for a significant period of time. Finally, the most significant benefit of using reconfigurable computing would be the ability of a system to adapt its configuration dynamically, in-system, a benefit previously only available to software running on slow microprocessor-based designs. [MM99]

There is a range of signal processing requirements (typically data throughputs exceeding gigabytes per second) for especially demanding applications which exceeds the maximum performance FPGAs can deliver, and for which custom VLSI devices are still the only viable solution. However, for many systems, FPGAs are becoming powerful enough to meet the system's signal processing demands and may be a better choice than a custom VLSI solution given the benefits of reconfigurable computing described above.

#### 2.3 FPGA Trends

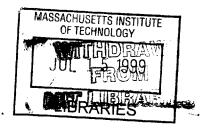

Shrinking process geometry and reduced supply voltages in FPGAs have resulted in enormous growth in terms of their computational capability and power efficiency [MMT00]. The growth in FPGA computational capability versus process geometry is shown in Figure 2.1. Curves are shown for FPGAs, the Motorola Power PC, and custom VLSI for comparison purposes. The data for the custom VLSI is based on several development efforts at MIT Lincoln Laboratory over the past several years [MMT00].

Figure 2.1: Growth in FPGA Performance Versus Process Geometry

Figure 2.1 shows that FPGAs offer an intermediate capability between that offered by programmable processors and custom VLSI. Presently, FPGAs are about an order of magnitude more capable than programmable processors, and an order of magnitude less capable than full custom VLSI. Furthermore, the gap between FPGAs and microprocessors is widening, as FPGA vendors use increased density to increase the number of logic cells, whereas microprocessor developers often use increased density for caches and reducing die size. [MMT00]

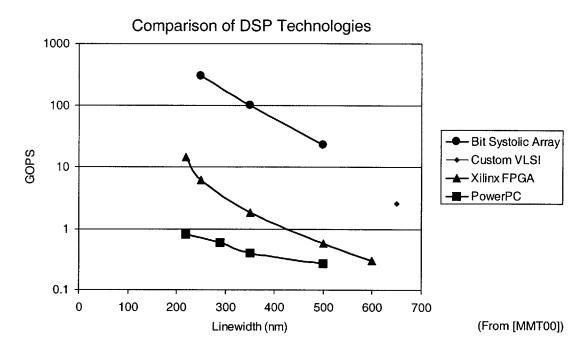

The growth in the computational capability of FPGAs for DSP applications as a function of time is shown in Figure 2.2 in billions of 16-bit arithmetic operations per second. Within the last 5 years, the computational capability of FPGAs have increased by an order of magnitude every two years. It is now feasible to explore the implementation of complex DSP systems using FPGAs as computational building blocks.

Figure 2.2: Growth of Computational Capability for Xilinx FPGAs

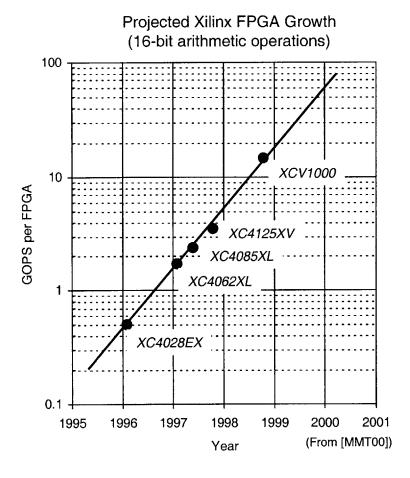

## 2.4 Radar Front-End Digital Signal Processing

A typical radar signal processing flow is illustrated in Figure 2.3. In this flow, the first stage of digital filtering is what is referred to in this thesis as frontend radar signal processing. This stage of filtering converts the data from real ADC samples to complex digital in-phase and quadrature (DIQ) samples, and is referred to as DIQ sampling [Sti98]. DIQ sampling is important to preserve the target's Doppler information. Although the remaining processing stages, Doppler filtering, adaptive nulling, and post-nulling processing, can be very demanding, it is the first stage of digital filtering that has the most stringent

processing requirements that have necessitated custom VLSI designs until now. The rest of the signal processing flow is described extensively in [War94].

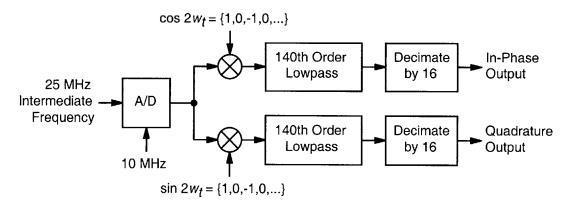

Figure 2.3: Typical Radar Signal Processing Flow

The DIQ filtering is designed to extract one sideband after ADC sampling, map the sideband to baseband, and remove any remaining spectrum images and DC offsets. The exact DIQ filter coefficients depend on the characteristics of the bandwidth present in the transmitted pulse, and are required to be dynamically alterable. The DIQ architecture for the custom VLSI design is shown in Figure 2.4, and is described in detail in [MMT00, Sti98, War94]. As the figure shows, the DIQ architecture requires two finite impulse response (FIR) filters followed by decimation. This design required a filter with 208 complex taps.

Figure 2.4: Digital In-phase and Quadrature Sampling Architecture

# Chapter 3

# **Custom VLSI Implementation**

#### 3.1 Overview

A custom VLSI implementation of the DIQ architecture in Figure 2.4 was begun in 1996 and finished in 1998 at MIT Lincoln Laboratory. It was concluded that no commercially available DSP or RISC processors or dedicated filtering chips would meet the processing requirements of the DIQ filtering stage, leaving a custom solution as the only alternative. The design that was chosen was a custom chip made up of a mix of standard cells and datapath multiply-accumulate (MAC) cells [Gre96]. The overall system consisted of several boards using these custom chips, and is described in detail in [MMT00].

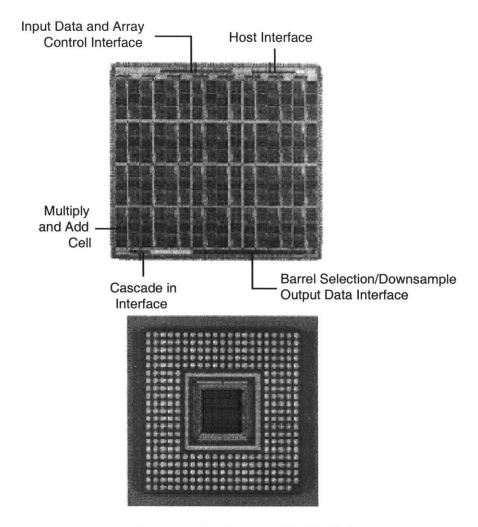

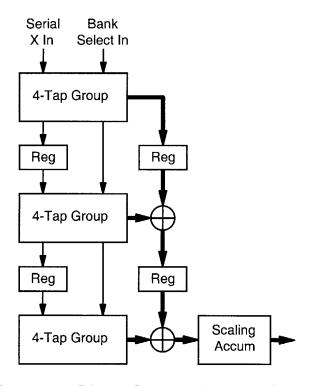

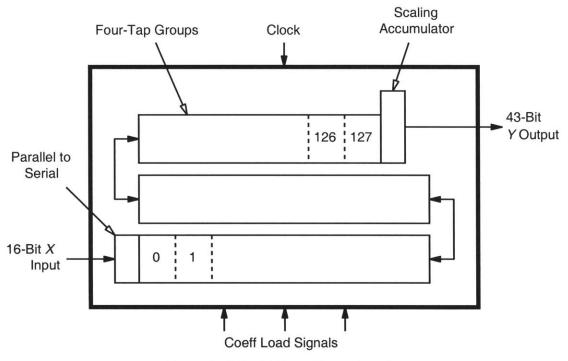

The custom VLSI chip, designed using 1996 process technology, is shown in Figure 3.1. The standard cells are used in the chip control interface, barrel bit selector, and downsampler. The datapath blocks form the MAC cells. There are a total of 64 MACs available on the chip. Depending on the input sample rate and mode, these MACs can be used either as 64, 128, or 256 complex taps, or as 128, 256, or 512 real taps. Since the chip was to compute the in-phase (I) and quadrature (Q) data from real ADC data, 32 MACs processed up to 128 real taps for the I samples and, in parallel, another 32 MACs up to 128 taps for the Q samples. [Gre96, MMT00]

For the specific technology demonstration discussed in Section 2.4, ADC samples arrive at 10 MHz. Samples alternate between the I computation and the Q computation. Thus, two sets of outputs are computed at 10 MHz (5 MHz

Figure 3.1: Custom VLSI Chip

for I and Q), each using 104 real taps. Since there are two real operations per tap (a multiply and an add), the total computation throughput for these parameters is 2.08 GOPS. These operations are performed on 18-bit sign extended data (from 14 bit ADC samples) using 18-bit coefficients. The resulting outputs (I and Q samples) are selected from the most significant 24 bits. [MMT00, Gre96]

The key features of this chip are: [MMT00, Gre96]

- 2.08 GOPS in DIQ mode

- 5.02 GOPS in 512-tap real mode

- 40 MHz operating frequency (tested to 44 MHz)

- 18-bit input data and coefficients; 24-bit output data

- 585 mil x 585 mil die size

- 1.5 million transistors

- 0.65 mm feature size

- CMOS using three-layer metal

- Designed for 4 watts power dissipation; measured 3.2 watts in operation

- DIQ mode throughput/power = 0.65 GOPS/W

- 512-tap real mode throughput/power = 1.57 GOPS/W

#### 3.2 Custom VLSI Architecture

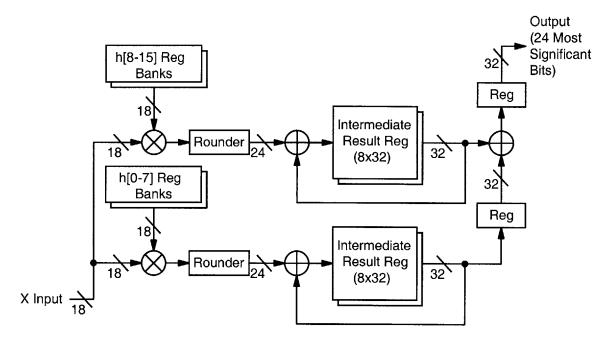

A block diagram of the custom VLSI chip's architecture is shown in Figure 3.2. As was discussed in Section 3.1, the custom VLSI chip consists of 64 MAC units. Each MAC unit contains a multiplier, accumulator and intermediate storage memory, and two banks of coefficient memory. The two banks of coefficient memory allows one set of coefficients to be active and is used by the multipliers while a new set can be loaded into the other coefficient bank. Once the new set has been loaded, it can now become active, allowing the chip to instantly change from one set of coefficients to another.

Each MAC, by using the accumulator and intermediate storage memory, is capable of forming the products of the current chip input and up to eight filter taps (i.e. eight coefficients). These products are accumulated together as required within the MAC, and then added to the other MACs' results when a new input is present. If the MACs are operating in their eight tap mode, they must run at a clock rate eight times the input sample rate so that all eight

taps' products are computed each time a new input arrives. In this mode, the 64 MACs can compute a 512-tap real filter, the mode used as a benchmark for a FPGA implementation (Chapter 4).

Figure 3.2: Custom VLSI Chip Architecture

## 3.3 Custom VLSI Noise Analysis

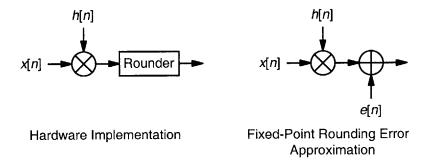

As shown in Figure 3.2, the multiplier in each MAC multiplies an 18-bit input by an 18-bit coefficient. This would produce a 36-bit output. However, to keep the logic downstream of the multiplier a reasonable size, the bit-width of the multiplier's output has been reduced to 24-bits by a rounder. The rest of the chip uses full-precision, i.e., each time a summation is performed (the only operation that occurs after the multiplication), the summation's output grows a bit to handle the one-bit word growth normal in addition. [Gre96, OS89]

Rounding is performed by adding the most significant bit (shifted right to bit position 0) of the bits to be removed to the bits that are to remain. For

example, when rounding the 36-bit multiplication output to 24 bits, the top 24-bits of the 36-bit output are kept and added to the 11th bit of the 36-bit output. Since each bit represents ½ the power of the bit to its left, adding the most significant bit of the part of a number to be rounded off to the bits on its left is the same as rounding the bits on its left up by one if the bits on the right are greater than 0.5, the typical method of rounding in math. However, since the rounded result is no longer exact (because bits were removed), noise is introduced. This noise can be approximated as additive noise added at the rounder with a mean of zero and a variance of ([OS89, OW75])

$$\sigma_e^2 = \frac{2^{-2B}}{12},\tag{3.1}$$

where *B* is the number of bits the result has been rounded to. The noise approximation is modeled simply as additive noise as shown in Figure 3.3. [OS89, OW75]

Figure 3.3: Rounding Noise Approximation

Examining Figure 3.2 with the rounders replaced with noise sources (as shown in Figure 3.3) shows that the noise sources will simply be added together. Since they are assumed to be independent, their means and variances can be summed, giving a total noise source for the 512-tap custom VLSI

chip filter with 24-bit rounded multiplier outputs a mean of zero and a variance of ([OS89, OW75])

$$\sigma_e^2 = \frac{512}{12} 2^{-2(24)} = 6.06 \times 10^{-13}.$$

(3.2)

With the chip's output variance computed, the number of bits required for a single rounder to achieve the variance in Equation (3.2) can be solved (i.e. if the custom VLSI chip had only one rounder at its output instead of 512 separate rounders):

$$B_{filter} = \frac{\log_2 \frac{1}{12} - \log_2 \sigma_e^2}{2} = \frac{\log_2 \frac{1}{12} - \log_2 6.06 \times 10^{-13}}{2} = 19.5 \text{ bits.}$$

(3.3)

This means that the final output of the custom VLSI chip is the same as if the filter had no rounding internally, and the output was rounded to 19.5 bits. Therefore, only the upper 19 bits of the chip's 24-bit output are exact; the extra bits in the chip's output data bus contain noise introduced by the rounding at each multiplier.

To experientially determine the chip's output precision, a fixed-point MAT-LAB simulation of the custom VLSI chip was built. The simulation performed 24-bit rounding at the output of each multiplier as described above, and compared this filtered output for a random set of data and coefficients with the ideal convolution of the data and coefficients. The difference of the ideal convolution's results and the rounding filter's results was equal to the noise introduced by rounding. The variance of this difference (the rounding noise variance) was then computed and used in Equation (3.3) to compute the number of valid bits output by the custom VLSI chip. This simulation indicated

that (with several different sets of random data and coefficients) the custom VLSI chip actually outputs 18 bits of valid data.

# Chapter 4

### **Problem**

#### 4.1 FPGA Benefits to Radar Front-End Signal Processing

As FPGA technologies become more capable, the same filtering operations currently implemented in custom VLSI devices can now be attempted to be implemented in a FPGA. a FPGA implementation would have several major benefits:

- 1. Reduction in design, manufacturing, and testing costs, time, and resources relative to custom VLSI designs.

- 2. Flexibility to implement different filtering functions using the same reprogrammable FPGA devices.

- 3. Ability to upgrade the design to higher ADC sampling rates by substituting more capable FPGA devices commensurate with the Moore's law progression in silicon technology (without requiring the new fabrication runs custom chips necessitate).

- 4. Wider vendor sources of FPGA technologies than available with custom VLSI designs.

The most limiting factor in permitting the use of FPGAs to date for the more advanced classes of DSP applications (in particular, radar front-end signal processing) is their inability to reach the required throughputs with high precision, which are on the order of several billion GOPS with at least 16-bits. Most high performance demonstrations to date are based on a few bits of precision. Therefore, this thesis attempts to demonstrate that FPGA technology

can implement filtering fast enough to allow the benefits of reconfigurable computing to be applied to radar front-end signal processing DSP functions.

#### 4.2 Problem

To demonstrate the current state of FPGA technology and its application to front-end signal processing, FPGA implementations meeting the design requirements of MIT Lincoln Laboratory's custom VLSI FIR chip discussed in Chapter 3 were created. The FPGA designs were required to:

- Perform 512-tap real FIR filtering

- Accept 16-bit data at a maximum input rate of 5 MHZ

- Operate with a maximum chip clock frequency of 40 MHz (eight times the input rate)

- Output data with the same precision as the custom VLSI chip (18-bits as described in Section 3.3)

- Use two swapable banks of 18-bit coefficients, one active and one loadable

- Have coefficient banks that must be able to be switched every 1 ms (i.e.

reloading all 512 coefficients must take place in less than 1 ms)

- Fit into the largest Xilinx FPGA available, the Virtex XCV1000.

The 512-tap real FIR filter specification was chosen as this is the mode in which the custom VLSI chip runs the most efficiently. Although the chip is used in-system in an in-phase and quadrature mode, the MACs are not fully utilized, so building an efficient FPGA design would not be a fair comparison. In the 512-tap design, each of the 64 custom VLSI MACs perform eight filter tap operations per input sample. The 512-tap design allows a direct perfor-

mance comparison between the two types of hardware. Once a FPGA design can meet the 512-tap real mode filtering requirements of the custom VLSI chip, it will easily be able to meet those of the DIQ mode, as moving to that mode simply changes the manner in which the internal filter results are summed together.

The maximum input rate in the design specifications for the custom VLSI chip operating in its 512-tap real FIR filter mode is 5 MHz. In this mode, the chip requires a clock rate eight times the sample rate since it is processing eight taps per input sample. Therefore, the maximum clock rate is 40 MHz, although the custom VLSI chip was tested to 44 MHz.

16-bit inputs were chosen as the custom VLSI chip is currently being used with an ADC with a 14-bit output, and it is unlikely the VLSI chip would operate with an ADC of more than 16-bits in the future. The only reason for having the custom VLSI chip designed to accommodate 18-bit input data was to facilitate word growth if several custom A1000 chips were used in a cascaded mode.

Two banks of coefficients were used in the custom VLSI chip, and are required for the FPGA so that one bank stores the active filter's coefficients while the other bank is being loaded with new coefficients. The banks may then be swapped by an external control so that the new coefficients may become instantly active.

Although the need to change coefficients could be viewed as an ideal application for reconfiguration, using swapable coefficient banks is more efficient. It has been proposed that the ability of a FPGA to be reconfigured in-system be used to implement a single filter with fixed coefficients that is reconfigured

when a coefficient switch is desired. The design requirements specify an instantaneous switch between the active coefficients and the new set of loaded coefficients, which prohibits using a single bank of coefficients that could be changed via the FPGA's reconfiguration ability. The filter would be inactive during the reconfiguration time, which is unacceptable.

One solution might be to have one filter operational while a second filter was being configured in the same chip. This would require the FPGA to have partial reconfiguration ability, and wouldn't save any space over two coefficient banks, because two filters would still have to be present in the chip during coefficient updates. In addition, the filter coefficients would have to be known in advance so that configurations using constant coefficients could be mapped, placed, and routed by the Xilinx software to be ready for loading into the FPGA. These configurations would then have to be stored off-chip to be recalled and loaded into the FPGA. In most applications, the filter responses are not known beforehand, so creating and storing every configuration for every set of possible coefficients is not feasible.

## Chapter 5

## Xilinx Virtex FPGA Technology

### 5.1 FPGA Selection

The Xilinx Virtex FPGA was chosen to implement the 512-tap FIR design because of several factors. At the time of this thesis, the Virtex XCV1000, with 1,124,022 gates, had the most capacity of any commercially available FPGA [Xil98b]. The Virtex series of FPGAs were also determined to be ideal for DSP applications as they had been designed with vector-based routing intended to carry large data busses within the chip instead of traditional FPGA routing schemes designed more for control logic [Xil98a]. In addition, PC-based reconfigurable computing boards from Annapolis Micro Systems, a company that MIT Lincoln Laboratory and DARPA are working with to develop reconfigurable computing solutions, are available with Virtex devices and could be used to implement solutions developed in this thesis in real hardware. Finally, prior Xilinx knowledge finalized the decision to use Xilinx Virtex FPGAs for this thesis.

### 5.2 Virtex Overview

FPGAs are similar to custom designed chips in that they implement specific circuitry for a particular function. The major difference is that a FPGA is configured by a bitstream instead of by being hardwired through fabrication at a factory. This means that a FPGA's internal circuitry may be altered an unlimited number of times.

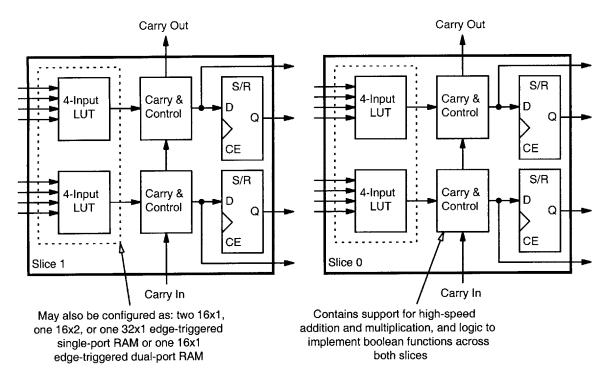

FPGAs may be classified as "coarse-grained" or "fine-grained," referring to the number and complexity of each basic logic element in the FPGA. Xilinx Virtex series chips are coarse-grained, and have logic units based on look-up tables (LUTs) and registers. The basic Virtex logic element is a Configurable Logic Block (CLB) slice. Two slices are present in each CLB. Each slice contains two 4-input, 1-output LUTs and two registers. The interconnections between these elements are configured by multiplexors controlled by SRAM cells programmed by a user's bitstream. The LUTs allow any function of five inputs, any two functions of four inputs, or some functions of up to nine inputs to be created within a CLB slice. The outputs of these functions may be registered, or the registers may be used independently of the LUTs. This structure allows a very powerful method of implementing arbitrary, complex digital logic. [Xil98a]

The Xilinx slices also have the ability to implement distributed memory instead of logic. Each 4-input LUT in a slice may be used to implement a 16x1 ROM or RAM, or the two LUTs may be combined together to create a 32x1 ROM or RAM or a 16x1 dual-port RAM. This allows each slice to trade logic resources for memory in order to maximize the resources available for a particular application. A block diagram of a Xilinx Virtex CLB showing both slices is illustrated in Figure 5.1. [Xil98a]

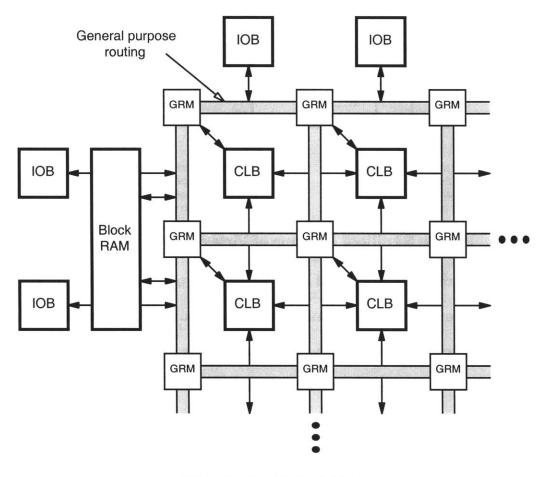

The CLBs in a Virtex FPGA are connected via programmable interconnect called the general purpose routing. This interconnect consists of differing length lines, some connecting adjacent CLBs together, while some span the entire length of the chip and others are designed for high fan-out signals such as clocks. The connections between the interconnect and the CLBS are con-

Figure 5.1: Block Diagram of Virtex CLB (Two Slices)

trolled by switch matrices called general routing matrices (GRMs). The programmable interconnect allows mappings that require local communication to be handled efficiently along with requirements for arbitrary, longer-distance, routing demands. In addition to the programmable interconnect, there are a few dedicated routing resources. One example is the carry-chains between CLBs that allow high-speed carry propagation through a series of slices, enabling high-speed adders and other arithmetic units to be designed in a chain of CLBs. Connections between the internal routing and the external world are made through Input/Output Blocks, or IOBs, which contain input/output registers and connect directly to a package pin. [Xil98a]

The Virtex FPGAs also include 4,096-bit block RAM units on the edges of the FPGA. These resources are ideal when large amounts of memory are required that would not use the small, distributed CLB-based memory efficiently. Finally, the Virtex also has advanced clock management resources built in, including a delay locked loop (DLL) that reduces clock skew and can divide (by up to 16) or multiply (by 2) external clocks for slower or faster internal clocking. Figure 5.2 shows a block diagram of a Virtex series chip. [Xil98a]

CLB = Configuable Logic Block GRM = General Routing Matrix IOB = Input/Output Block

Figure 5.2: Virtex Block Diagram

The highly replicated, register rich architecture of the Virtex makes it suitable for custom computing applications. Each slice can perform a two-bit computation or look-up, allowing a systolic structure of processors to be built out of the regular array of CLBs in a Virtex. There are cases when a finer grain

structure may be more efficient, as the CLB structure may not be the most efficient medium for very small systolic-cell based arithmetic (for example, the bit-level systolic FIR filter design investigated in this thesis).

The largest Virtex, the XCV1000, has 12,288 CLB slices and 131,072 block RAM bits [Xil98a].

### 5.3 Computational Unit Implementation

To illustrate the capacity of a slice, two commonly used DSP computational units, an adder and a multiplier, are presented with their area in terms of CLB slices.

The Virtex has dedicated fast-carry chain resources built into each CLB. Two adder bits can fit into a single slice so that a b-bit adder consumes  $\frac{b}{2}$  CLB slices. A 16-bit adder would require 8 slices. [Xil98a]

The Virtex also has dedicated multiplication resources so that two multiplication bits can fit into a single slice. An *a*-bit by *b*-bit multiplier requires approximately

$$\frac{b\log_2 b + (b-1)a}{2} \tag{5.1}$$

CLB slices. A 16x16-bit multiplier would require about 152 slices.

<sup>1.</sup> Based on an optimized multiplier built for Virtex by Xilinx.

## Chapter 6

# **Algorithms and Techniques**

#### 6.1 Overview

Several different algorithms or filtering techniques were investigated for implementing a FIR filter in a FPGA device. These included FIR filtering using parallel multipliers and accumulators, a bit-level systolic array, distributed arithmetic, fast FIR algorithms, and frequency domain filtering. The specifics of each are discussed in this chapter.

### 6.2 FIR Filtering

A FIR filter computes the discrete convolution of an input x[n] and a finitelength filter response h[n]. This convolution can be written as

$$y[n] = \sum_{k=0}^{N-1} h[k]x[n-k], \tag{6.1}$$

where N is the length of the filter response h[n], and is referred to as the number of taps in the filter.

## 6.3 Parallel Multipliers and Accumulators

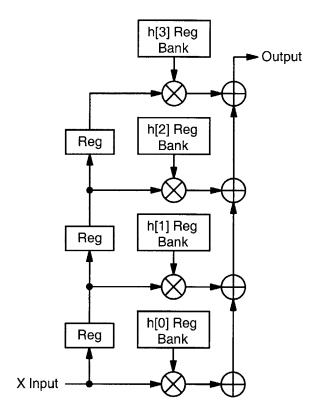

The most direct realization of a FIR filter is to calculate the output y[n] using parallel multipliers and accumulators (MACs). The parallel MAC structure is illustrated in Figure 6.1, and is derived directly from the FIR convolution in Equation (6.1) [OS89]. In this structure, each MAC computes the product of

the delayed input and the tap's active coefficient. The outputs from each multiplier are then accumulated together to produce the filter's output.

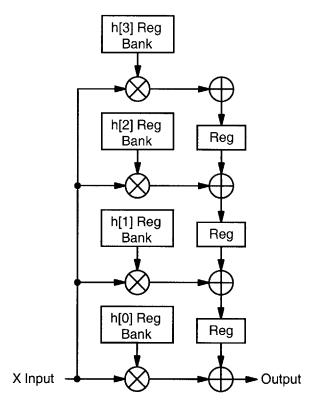

Figure 6.1: Direct Parallel Multiplier and Accumulator FIR Structure

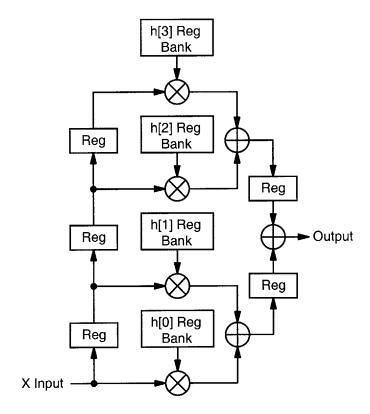

The structure in Figure 6.1 has long combinatorial delays through the accumulation chain, so the summer tree network shown in Figure 6.2 or the transposed form shown in Figure 6.3 are often used in actual FIR computational hardware. Both forms produce the same output, but can have their accumulation chains pipelined to increase performance. The benefit of the transposed form is that each MAC communicates only with adjacent MACs, as Figure 6.3 shows. This allows the MACs to be placed in a linear systolic fashion, where adjacent MACs are placed next to each other in a line so that each MAC only has routes to and from its nearest neighbors. This maximizes the performance of the design while minimizing its area. The tree network

requires long, complicated route lengths to the inputs of each stage of adders as the number of MACs that have been summed together for a given adder increases and the MACs grow farther apart. This prohibits a simple linear distribution of MAC cells and slows the design's performance due to the long routes.

Figure 6.2: Parallel MAC Filter With Summer Tree

One problem with the transposed form of the parallel MAC filter is that it requires a large fan-out on the X input signals, as they must connect to every MAC. To reduce this fan-out while maintaining pipelining in the accumulation chain and allowing the MACs to be placed in a linear systolic fashion, an additional stage of pipelining in both the inputs and outputs of each MAC can be introduced into the direct filter as shown in Figure 6.4.

Figure 6.3: Transposed Form Parallel MAC Filter

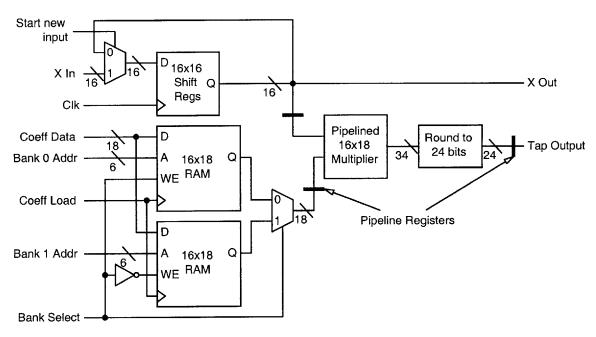

A frequent method used to decrease the area of a parallel MAC approach to FIR filtering is to increase the number of taps computed per MAC. This is the technique used in the custom VLSI chip [Gre96, MM99, MMT00]. One variation of this technique is shown in Figure 6.5. In this figure, a single multiplier is re-used eight times to compute the product of eight X values multiplied by eight coefficients for each input into the filter. An eight-word deep RAM stores the eight coefficients for the tap, and a seven-word long shift register stores the X values.

This architecture is similar to the one used in the custom VLSI chip (see Section 3.2 and Figure 3.2), except that shift registers have been used to store multiple input values for each MAC instead of RAM storing the multiplier's outputs. The result is the same except that storing multiple inputs per tap

Figure 6.4: Direct Form Pipelined MAC Fir Filter

requires less memory since the inputs are only 16-bits long versus the 24-bit multiplier outputs.

The shift registers are loaded with a new value at the beginning of each eight-clock cycle. The shift registers are then fed their outputs back into their inputs for the next seven clock cycles. This moves the input that was shifted into the register at the beginning of the eight clock cycles to the second shift register position at the beginning of the next eight clock cycles so that the next new value is loaded into the first position. After eight clock cycles, this input becomes the new value to the next MAC's shift registers. At the same time, the shift registers are arranged so that eight consecutive input values are sup-

plied to the multiplier to be multiplied by eight consecutive coefficient values.

These will be added together by the final accumulator shown in Figure 6.5.

The output of the first two MACs' shift registers and coefficient registers (i.e. the multiplier inputs) are shown in Table 6.1 for two-tap MACs. With eight-tap MACs, the movement of inputs through the shift registers produces the same effect with 64 multipliers as if 512 multipliers had been used with a clock rate equal to the sample rate.

|                | Mac 0        |                |      |        | Mac1  |                |      |        |                         |

|----------------|--------------|----------------|------|--------|-------|----------------|------|--------|-------------------------|

| Clock<br>Cycle | MAC<br>Input | Shift Register |      | Coeff  | MAC   | Shift Register |      | Coeff  | Chip                    |

|                |              | In             | Out  | Output | Input | In             | Out  | Output | Output                  |

| 0              | x[0]         | x[0]           |      | h[1]   |       |                |      | h[3]   | x[0]*h[0]               |

| 1              |              | x[0]           | x[0] | h[0]   |       |                |      | h[2]   |                         |

| 2              | x[1]         | x[1]           | x[0] | h[1]   |       |                |      | h[3]   | x[0]*h[1]+              |

| 3              |              | x[1]           | x[1] | h[0]   |       |                |      | h[2]   | x[1]*h[0]               |

| 4              | x[2]         | x[2]           | x[1] | h[1]   | x[0]  | x[0]           |      | h[3]   | x[0]*h[2]+              |

| 5              |              | x[2]           | x[2] | h[0]   |       | x[0]           | x[0] | h[2]   | x[1]*h[1]+<br>x[2]*h[0] |

Table 6.1: Two Taps Per MAC FIR Filter Example

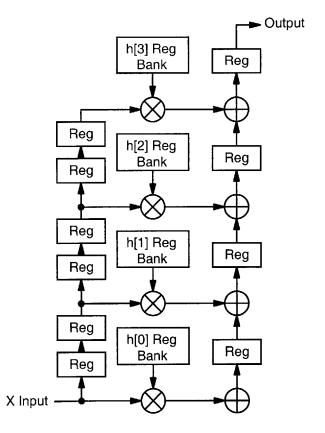

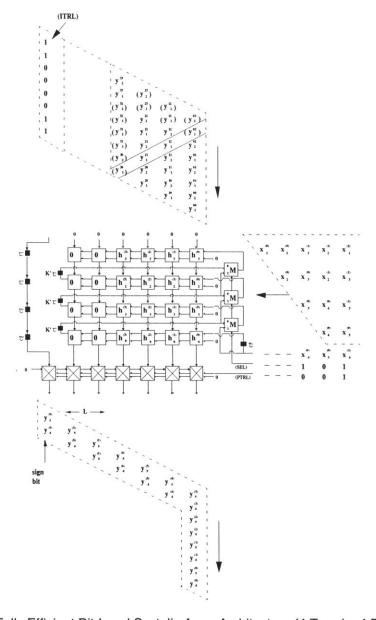

### 6.4 Bit-Level Systolic Array

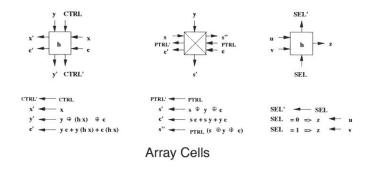

An approach which has proven to be a very efficient VLSI implementation at MIT Lincoln Laboratory [Son] is a fully-efficient bit-level systolic structure by Chin-Liang Wang [WWC88]. With this technique, single-bit processors compute each tap's multiplication partial products and accumulate tap outputs together in a systolic array. As inputs propagate through the array, filtered outputs are produced. The systolic nature of this approach lends itself well to

Figure 6.5: Eight Taps Per MAC FIR Filter

VLSI, and would be ideal for a FPGA if it was area-efficient, as it would limit the routing requirements in the FPGA to local connections between CLBs.

The configuration of this array and the logic required to implement each cell is shown in Figure 6.6. Since this technique did not turn out to be efficient in a FPGA architecture (see Section 7.3), the derivation if its structure will not be included here (see [Son, WWC88] for more information). It is presented to show the differences between architectures optimized for a FPGA's coarsegrained structure versus architectures optimized at the transistor level for a VLSI approach.

Fully Efficient Bit-Level Systolic Array Architecture (4 Taps by 4 Bits)

Figure 6.6: Bit-Level Systolic Array

### 6.5 Distributed Arithmetic

The following section describes DA, and is drawn from information presented in [MM99, Whi89, Gos96a, Gos95, Gos96b, New95, Xilb].

DA works by distributing the bit arithmetic of the sum-of-products (also called the vector dot product) used to calculate the FIR filter output given in Equation (6.1). This equation will be re-written as

$$y(n) = \sum_{k=0}^{N-1} A_k x_k(n), \tag{6.2}$$

where  $A_k = h[k]$ .

A FIR filter is typically implemented with some variation of Figure 6.1 or Figure 6.3, where a summation of the results of N multipliers each calculating an  $A_k x_k(n)$  product produce the output for a given n.

The number format used in the custom VLSI chip and in the FPGA design is 2's complement fractional fixed-point. In this format, the binary point is to the right of the most significant bit so that the most significant bit of a number represents -1, and each subsequent bit represents a power of  $\frac{1}{2}$ . Using this format, the variable  $x_k$  may be written as

$$x_k = -x_{k0} + \sum_{b=1}^{B-1} x_{kb} 2^{-b}, (6.3)$$

where  $x_{kb}$  is the bth bit of  $x_k$ , and B is the number of bits in the input variable.

Substituting Equation (6.3) into Equation (6.2) gives (n has been dropped, as we are only concerned with a single given output sample)

$$y = \sum_{k=0}^{N-1} A_k \left( -x_{k0} + \sum_{b=1}^{B-1} x_{kb} 2^{-b} \right), \tag{6.4}$$

which when rewritten, gives

$$y = -\sum_{k=0}^{N-1} x_{k0} A_k + \sum_{b=1}^{B-1} 2^{-b} \left( \sum_{k=0}^{N-1} x_{kb} A_k \right).$$

(6.5)

Explicitly writing out the summations results in the DA equation

$$y = -[(x_{00}A_0 + x_{10}A_1 + \dots + x_{(N-1)0}A_{N-1})] + [x_{01}A_0 + x_{11}A_1 + \dots + x_{(N-1)1}A_{N-1}]2^{-1}$$

$$\dots + [x_{0(B-1)}A_0 + x_{1(B-1)}A_1 + \dots + x_{(N-1)(B-1)}A_{N-1}]2^{B-1}.$$

(6.6)

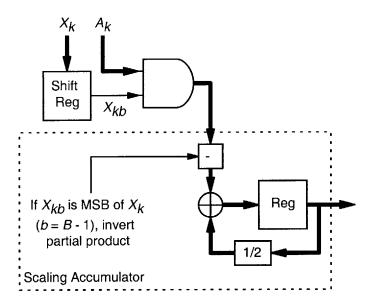

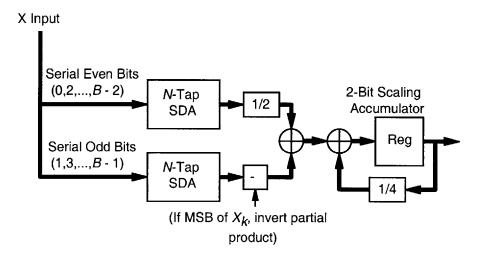

Each multiplication of a  $x_{kb}$  term and an  $A_k$  term is the product of a coefficient word with an input bit. This can be implemented by using an AND gate between each bit of the coefficient word and the input bit. Each scaling factor  $(2^{-i})$  can be implemented by shifting the data to be scaled right i bits. Equation (6.6) therefore becomes the summation of the scaled summation of a series of AND gates. This operation could be performed in parallel (as described in Section 6.3), or bit-serially, where each clock cycle a single bit from every  $x_k$  is multiplied by the corresponding  $A_k$ , forming one bracketed term in Equation (6.6). These partial products are then accumulated together with the appropriate scaling to produce a final multiplier output. An example of bit-serial multiplication for a single coefficient and input is shown in Figure 6.7.

Figure 6.7: Bit-Serial Multiplier

As Figure 6.7 illustrates, each clock cycle a single partial product consisting of one bit of the input  $x_k$  multiplied by the coefficient  $A_k$  is produced. This partial product is then added to an accumulating sum of partial products, which has been shifted right one bit (multiplied by  $\frac{1}{2}$ ). This operation produces the following result for a four-bit input (with each term in parenthesis being computed each clock cycle):

$$y_k = (((x_{k3}A_k)2^{-1} + x_{k2}A_k)2^{-1} + x_{k1}A_k)2^{-1} - x_{k0}A_k,$$

(6.7)

which when simplified, gives

$$y_k = x_{k3} A_k 2^{-3} + x_{k2} A_k 2^{-2} + x_{k1} A_k 2^{-1} - x_{k0} A_k,$$

(6.8)

and finally, results in the product of the input and the coefficient after four clock cycles:

$$y_k = x_k A_k. ag{6.9}$$

To maintain full-precision, the accumulator must be able to hold the entire multiplied result. The number of bits required is the number of bits in the input data + the number of bits in the coefficients.

The MAC structure in Figure 6.1 can be implemented with the bit-serial multiplier in Figure 6.7 as shown in Figure 6.8.

Figure 6.8: Four MAC Filter Using Bit-Serial Multiplier

In Figure 6.8, a parallel input to the FIR is converted into a serial stream of bits. Each clock cycle, one bit of the input is presented to the first scaling accumulator, and placed into a serial shift register for the next tap, so that each tap's input sample is presented to each scaling accumulator in a serial fashion. Each tap takes B clock cycle to produce a product, which are then summed together to produce an output sample. However, as the bracketed terms in Equation (6.6) show, the partial products computed by each AND

gate can be summed together first, then accumulated with scaling. In this method, one bracketed term in Equation (6.6) is computed each clock cycle, so *B* clock cycles are still required, yet each tap requires less hardware, since only one master scaling accumulator is now necessary. The new FIR structure is shown in Figure 6.9.

Figure 6.9: Serial Distributed Arithmetic FIR

To maintain full precision in this case, the scaling accumulator is now required to hold the number of bits in the input + the number of bits in the coefficients + the number of bits added due to word growth through the adder stages (1 bit per stage).

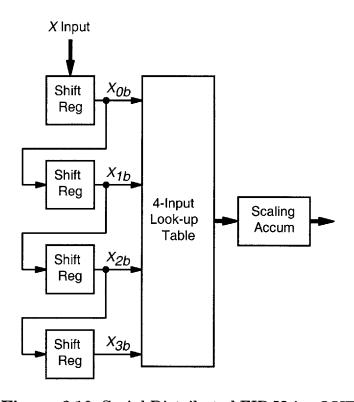

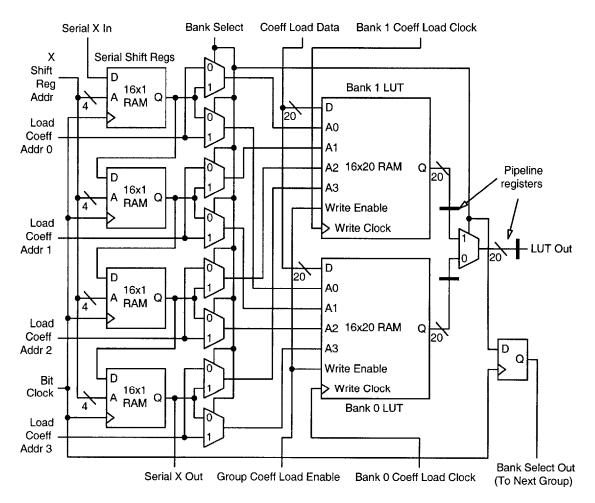

If the coefficients for the filter are constant, then the output of the summer tree depends solely on the single-bit inputs to each tap. With this being the case, the storage registers for the coefficients, the AND gates, and the summer tree can all be replaced by a single look-up-table addressed by the single-bit shift register outputs as shown in Figure 6.10.

Figure 6.10: Serial Distributed FIR Using LUT

With four taps as shown in Figure 6.10, a LUT with 16 entries is required. Each 4-bit address into the LUT can be thought of as being a sum of coefficients: if a particular address bit is high, then that address' sum should include the corresponding coefficient. Table 6.2 shows the 16 locations in the LUT, and what values they should hold.

| LUT Address                   | LUT Output |

|-------------------------------|------------|

| $x_{3b} x_{2b} x_{1b} x_{0b}$ | Sum        |

| 0000                          | 0          |

| 0 0 0 1                       | $A_0$      |

| 0010                          | $A_1$      |

Table 6.2: Contents of 4-Tap LUT

| LUT Address | LUT Output              |

|-------------|-------------------------|

| 0011        | $A_0 + A_1$             |

| 0 1 0 0     | $A_2$                   |

| 0101        | $A_0 + A_2$             |

| 0110        | $A_1 + A_2$             |

| 0 1 1 1     | $A_0 + A_1 + A_2$       |

| 1000        | $A_3$                   |

| 1001        | $A_0 + A_3$             |

| 1010        | $A_1 + A_3$             |

| 1011        | $A_0 + A_1 + A_3$       |

| 1100        | $A_2 + A_3$             |

| 1101        | $A_0 + A_2 + A_3$       |

| 1110        | $A_1 + A_2 + A_3$       |

| 1111        | $A_0 + A_1 + A_2 + A_3$ |

Table 6.2: Contents of 4-Tap LUT (Continued)

To keep the output of the LUT at full precision, the LUT should be two bits larger than the size of the coefficients to accommodate for word growth through the additions in Table 6.2.

The 16x1 RAM units within the Xilinx CLBs are ideal candidates for this sort of DA scheme. One bit of a single 4-input LUT can fit into one of these units with no unused logic.

For FIR filters larger than 4-taps, the filter can be broken into four tap groups, each constructed as shown in Figure 6.10. For example, a 16-tap FIR is shown in Figure 6.11. To eliminate overflow, each adder stage must grow by one bit, and the scaling accumulator must also grow accordingly in size (the

scaling accumulator could drop the lower bits in its accumulation if less precision is required).

Although larger LUTs could be used with less adders, LUTs larger than four inputs do not save space. For example, a five-input LUT would require 32-entries and take up two 16x1 RAM units (an entire slice). However, if these two 16x1 RAM units were used separately, they could each be addressed by four taps, allowing an entire slice to handle eight taps. The extra adder needed to sum the two four-input LUTs together would not significantly increase the area enough to justify a five-input LUT.

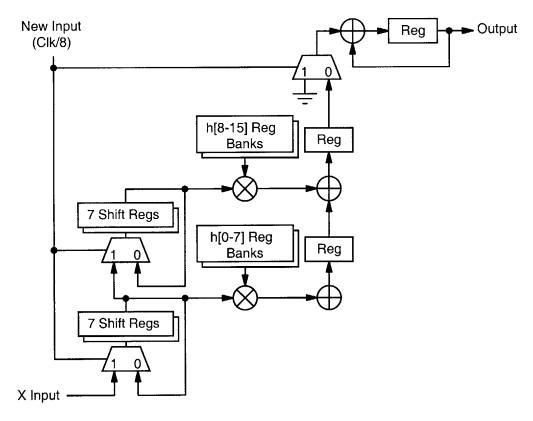

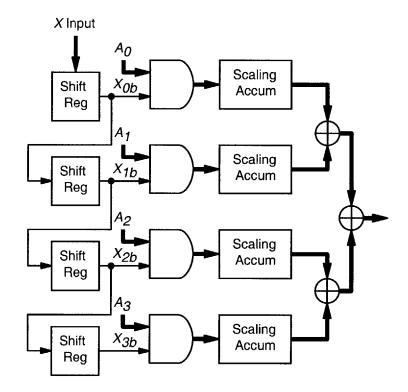

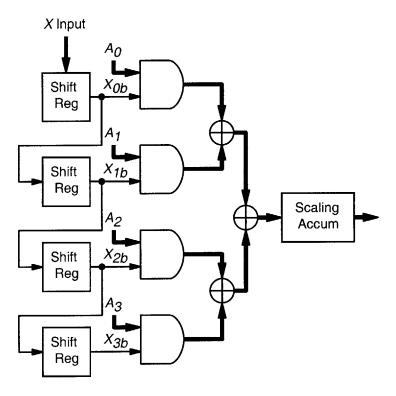

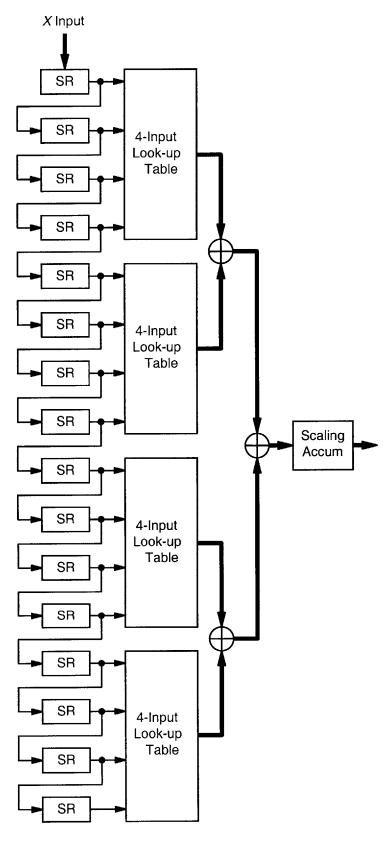

#### 6.5.1 Parallel Distributed Arithmetic

A benefit of distributed arithmetic is that it easily allows a trade-off to be made between the filter's area and performance. By doubling the filter's area, the filter's throughput or sample rate can be doubled without changing the clock rate that the individual filter components operate at. In the serial distributed arithmetic (SDA) designs discussed above, a clock rate B times the sample rate is required, as one clock cycle is needed to look up a partial product for each bit of x. However, by taking advantage of a feature inherent in the DA equation, Equation (6.6), fewer clock cycles can be required per input sample. Presently, one term in the equation has been computed per clock cycle. However, any number of terms can be computed per clock cycle (referred to as parallel distributed arithmetic, or PDA). For example, if two terms are computed per clock cycle, then  $\frac{B}{2}$  clock cycles are required to compute an output.

To compute two terms per clock cycle, two identical SDA FIR filters as described above must be constructed. Each filter will compute one term in Equation (6.6) so that two terms are computed per clock cycle. One filter will

Figure 6.11: 16-Tap Serial Distributed FIR

compute outputs for even input sample bits, and the other filter will compute outputs for odd input sample bits. For example, on the first clock cycle, the first filter will compute the output term associated with  $x_{k0}$  while the other filter computes the output term associated with  $x_{k1}$ . These outputs are then added together with the first filter's output (the bit 0 term) scaled by  $\frac{1}{2}$ , and then sent to the scaling accumulator. Each clock cycle, the scaling accumulator scales its registered accumulation by  $\frac{1}{4}$  to accommodate for the fact that it is handling two partial products per clock cycle instead of one. The 2-bit PDA approach requires twice as much area as the serial approach, but has twice the performance, and is illustrated in Figure 6.12.

Figure 6.12: 2-Bit Parallel Distributed Arithmetic FIR

### 6.6 Fast FIR Algorithm

The class of fast FIR algorithms (FFA) attempt to increase the parallelism of the FIR structure without a linear increase in area [PP97, CKJ<sup>+</sup>98]. Traditionally, to double the throughput of a FIR filter without increasing the clock rate of the filter itself, the filter area would have to be doubled.

Doubling the throughput of a FIR filter without changing its internal clock rate means that two outputs are to be calculated each clock cycle. These two outputs will be referred to as y[2j] and y[2j+1]. Producing two outputs per clock cycle would require two inputs per clock cycle as well, x[2j] and x[2j+1]. This leads to the following set of equations:

$$x_0[j] = x[2j]$$

$x_1[j] = x[2j+1]$

$y_0[j] = y[2j]$

$y_1[j] = y[2j+1],$

(6.10)

where  $x_0$  and  $y_0$  represent the even inputs and outputs, and  $x_1$  and  $y_1$  represent the odd inputs and outputs.

Two polyphase decompositions of the filter will be required, one containing the even samples of the original filter, the other the odd:

$$h_0[k] = h[2k]$$

$h_1[k] = h[2k+1],$  (6.11)

where h[n] is the original filter, k = 0, 1, ..., N/2-1, and N is the length of the original filter.

The above equations give the following z-transforms:

$$X = X_0 + X_1 z^{-1}$$

$$H = H_0 + H_1 z^{-1}$$

$$Y = Y_0 + Y_1 z^{-1},$$

(6.12)

which leads to the following two-parallel polyphase representation of the FIR filter:

$$Y = X \cdot H$$

$$= (X_0 + X_1 z^{-1})(H_0 + H_1 z^{-1})$$

$$= X_0 H_0 + (X_0 H_1 + X_1 H_0) z^{-1} + X_1 H_1 z^{-2}$$

$$Y_0 = X_0 H_0 + X_1 H_1 z^{-2}$$

$$Y_1 = X_0 X_1 + X_1 H_0.$$

(6.13)

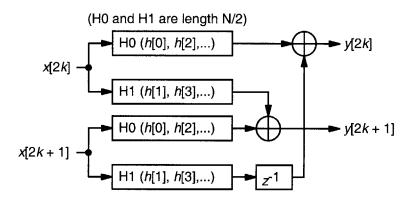

Equation (6.13) says that to double the throughput of the overall FIR filter h[n], two of each of the length  $\frac{N}{2}$  polyphase filters would be required as shown in Figure 6.13, resulting in an overall filter with twice as many taps as the original filter (four length  $\frac{N}{2}$  filters).

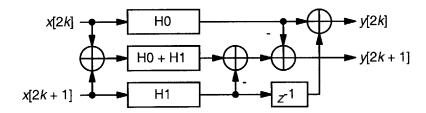

Figure 6.13: Traditional Two-Parallel FIR Filter Implementation

Two input samples are collected at a time and passed into the filter structure as illustrated in Figure 6.13, which produces two output samples. Each filter block shown in the figure is only running as fast as the original filter, however, so the throughput has been doubled. The FFA approach takes advantage of a rewriting of the polyphase equations derived from Equation (6.13):

$$Y = X_0 H_0 + (X_0 H_1 + X_1 H_0) z^{-1} + X_1 H_1 z^{-2}$$

$$= X_0 H_0 + [(X_0 + X_1)(H_0 + H_1) - X_0 H_0 - X_1 H_1] z^{-1} + X_1 H_1 z^{-2},$$

(6.14)

which implies that

$$Y_0 = X_0 H_0 + X_1 H_1 z^{-2}$$

$$Y_1 = (X_0 + X_1)(H_0 + H_1) - X_0 H_0 - X_1 H_1.$$

(6.15)

The structure that implements Equation (6.15) is shown in Figure 6.14 for the same overall filter inputs and outputs. This filter only requires 1.5 times as many taps as the original, non-parallel, filter, although the coefficients for the middle FIR element in the figure must be pre-computed before being loaded into the FIR element. This is not an issue for most applications, as such a computation can be performed external to the filter.

Figure 6.14: Two-Parallel FFA Implementation

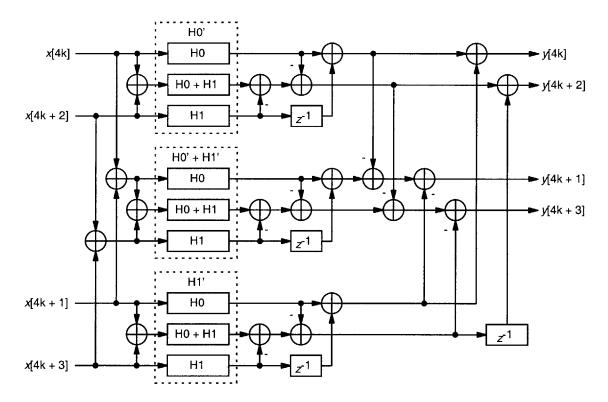

Each of the three filter blocks shown in Figure 6.14 may have the FFA algorithm applied to it, resulting in the filter shown in Figure 6.15. This filter can process four inputs and outputs per clock cycle, with an area increase of 2.25 times the original filter size versus four times for a normal polyphase implementation, as the four-parallel FFA requires  $9N_{16}$  taps instead of 16N taps. This process may be carried out recursively, increasing the throughput of the filter without a linear increase in area.

### 6.7 Frequency Domain Filtering

Instead of using convolution to calculate the output response for a FIR filter (as the techniques discussed above used), the filtering can be performed in the frequency domain. Convolution in the time domain is simply a multiplication

Figure 6.15: Four-Parallel FFA Implementation

operation in the frequency domain, so such an operation requires a transformation from the time domain into the frequency domain by a fast Fourier transform (FFT), a point multiplication of the input signal's spectrum by the filter's spectrum, and a transformation back into the time domain by an inverse fast Fourier transform (IFFT). The benefit of this technique is that it requires much less computational hardware than any of the approaches discussed so far using convolution. A FFT's computational requirements scales on the order of  $\log_2 N$  versus N for convolution approaches.

The FFT is derived from the discrete Fourier transform (DFT), which is used to transform discrete time waveforms into discrete frequency spectrums [OS89, GW75]. The DFT is defined by

$$X[k] = \sum_{n=0}^{N-1} x[n] W_N^{kn}, \tag{6.16}$$

where

$$W_N^z = e^{-j\frac{2\pi z}{N}}, (6.17)$$

x[n] is a complex data sample at time n, X[k] is a complex frequency sample at frequency  $\frac{k}{N}$ , and N is the number of frequency samples to calculate.  $W_N^z$  is sometimes referred to as a "twiddle factor." The DFT requires on the order of  $N^2$  computational requirements, so a more efficient method of computing the DFT is required. If N is an integer power of r, i.e.  $N = r^v$ , then an especially easy representation of the DFT appears, the radix-r FFT, where Equation (6.16) can be calculated iteratively in v stages:

$$a_{u,v}^{m} = \sum_{l=0}^{r-1} W_{r}^{-ul} a_{p,q}^{m-1}, \tag{6.18}$$

with

$$p = u \mod r^{m-1}$$

$$q = v + lC_m$$

$$C_m = \frac{N}{r^m}$$

$$a_{n,0}^0 = x[n],$$

(6.19)

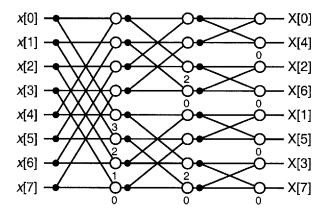

m=1...M,  $u=0...r^m-1$ , and  $v=0...C_m$  [GW75]. This is referred to as "decimation in frequency." For r=2, the algorithm is especially simple. At each stage, the algorithm passes through the entire array of N complex numbers, two at a time, generating a new array of N numbers. The basic numerical

computation operates on a pair of numbers at a time, and is referred to as a "butterfly." The decimation in frequency FFT structure is shown in Figure 6.16 for  $N=8=2^3$ , and a butterfly is shown in Figure 6.17. The numbers below each node in Figure 6.16 represent the z term in the twiddle factor  $W_N^z$  for that butterfly. A radix-4 FFT also exists, where four outputs are computed per butterfly for four inputs [OS89, GW75].

Figure 6.16: Eight-Point Decimation-In-Frequency FFT

Figure 6.17: Decimation-In-Frequency Butterfly

#### 6.7.1 Pipelined FFT

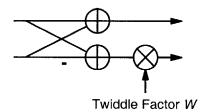

A nice feature of the FFT is that it can be easily pipelined by stage, as each stage needs only data from the proceeding stage. Each vertical grouping of butterflies in Figure 6.16 is referred to as a stage. Only one butterfly needs to be calculated in each stage at a time, although (to maximize the sample rate), each stage must have a butterfly calculated each clock cycle. Therefore, the

FFT can be built in a pipelined fashion, with each stage handled by a single pipelined butterfly.

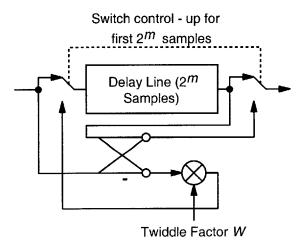

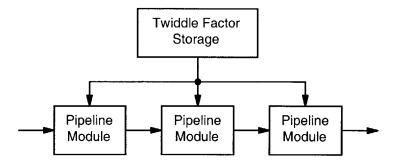

Each pipelined butterfly needs shift register storage  $2^m$  words long (where m is the stage number, with 0 being the right-most stage) to align its inputs and outputs correctly. For example, the first stage has butterflies that process inputs four samples apart in time. A shift register four words long is required to store the first four inputs, then output those four inputs to the top of that stage's butterfly as the next four inputs arrive at the bottom of the butterfly to compute the correct butterfly outputs. The top output of the butterfly are sent to the next stage while the bottom outputs are put into the shift register, which are then shifted out after the four butterflies have been computed. An example of a pipeline module is shown in Figure 6.18, and an eight-point pipelined FFT architecture is shown in Figure 6.19. [GW75]

Figure 6.18: Pipelined FFT Butterfly Module

The twiddle factors can be arranged so that they may be sent to all of the modules from a common memory if they are retrieved at the correct time, reducing memory requirements. [GW75]

Figure 6.19: Eight-Point Pipelined FFT Architecture Block Diagram

#### 6.7.2 FFT Convolution