# MODELING OF AND EXPERIMENTS CHARACTERIZING ELECTROMIGRATION-INDUCED FAILURES IN INTERCONNECTS

by

## VAIBHAV K. ANDLEIGH

B.S. Materials Science and Engineering Cornell University, 1995

Submitted to the Department of Materials Science and Engineering in Partial Fulfillment of the Requirements for the Degree of

DOCTOR OF PHILOSOPHY in ELECTRONIC MATERIALS at the

# MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 2001

© Massachusetts Institute of Technology, 2001 All Rights Reserved

| Signature of Author |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | Materials Science & Engineering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                     | May 4, 2001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Certified by        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| <del></del>         | Carl V. Thompson                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                     | Stavros State of Stavros Stavr |

|                     | Thesis Superviso                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                     | JUN 1 1 2202                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Accepted by         | and the same of th |

| Accepted by         | Harry L. Tulle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                     | Chairman, Departmental Committee on Graduate Studie                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# MODELING OF AND EXPERIMENTS CHARACTERIZING ELECTROMIGRATION-INDUCED FAILURES IN INTERCONNECTS

by

### VAIBHAV K. ANDLEIGH

Submitted to the Department of Materials Science & Engineering on May 4, 2001 in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electronic Materials

#### **ABSTRACT**

As interconnect linewidths continue to scale downward, a detailed knowledge of stress evolution and void growth processes enables a determination of the electromigration-induced failure times of these interconnects. This thesis provides this knowledge through the development of an electromigration simulation MIT/EmSim and through experiments.

The stress effect on diffusivity and alloying effects were incorporated into the MIT/EmSim model for Al-based interconnects, demonstrating Cu transport effects consistent with experiments by IBM. The void nucleation and growth process was modeled in long and short lines, and current density exponents for Black's equation determined for several failure conditions. Interconnects can also be immortal, either without void nucleation or by resistance saturation. This complex reliability behavior can be catalogued in the form of failure mechanism maps using simulation or analytical approximations, plotting failure or immortality mode as a function of current density and line length. To extend the MIT/EmSim model to Cu interconnects, experimental observation of void phenomenology and measurement of Cu-based electromigration parameters were performed using Cu/Ta interconnects specifically designed and fabricated at MIT. The knowledge gained from these experiments was used to develop an electromigration model for Cu, and incorporated into MIT/EmSim. Simulations comparing void growth in Al and Cu interconnects indicate that differences in failure times of these interconnects observed in accelerated tests may not necessarily be apparent at service conditions. A failure mechanism map constructed for damascene Cu demonstrates the absence of immortality by resistance saturation due to the shunt structure. Finally, proposed damascene designs eliminating the diffusion barrier at the studs may be expected to have an adverse effect on interconnect reliability due to the loss of short length effects.

The test structure developed in this thesis provides a simple means of testing the effects of new shunt and barrier layer technologies on the reliability of Cu-based interconnects. Through the use of the simulation, an accurate methodology for predicting the reliability of Al- and Cu-based interconnects in semiconductor chips has been developed. MIT/EmSim is now being used by Motorola and LSI Logic for evaluating interconnect reliability during the design of future Cu interconnects, and has also been used by numerous SRC-companies and universities through EmSim-Web for electromigration research.

Thesis Supervisor: Carl V. Thompson

Title: Stavros Salapatas Professor of Materials Science and Engineering

To My Parents and GrandParents,

Whose Direction and Support Led Me

To Complete This Degree

# **Acknowledgments**

My completion of this degree would not have been possible without significant contributions from my colleagues and friends.

I wish to thank Prof. Carl Thompson, whose guidance and support as my thesis advisor helped shape this research into a complete dissertation important to the semiconductor industry.

Additional members of my thesis committee, Prof. Suresh and Prof. Antoniadis, also provided valuable suggestions on improving the content of this thesis.

The research performed in this thesis was supported by the Semiconductor Research Corporation, and their support is appreciated. The experiments performed in this thesis could not have been completed without the aid of the staff and facilities of the Microsystems Technology Laboratories at MIT. In particular, Kurt Broderick and Vicky Diadiuk were very helpful in the development of my fabrication process.

My research group has also been very helpful during my research. Brett was a wonderful mentor. Dr. Fayad has always been a good friend and colleague, and I already miss our daily discussions. I have also cherished my friendship with Dr. Kobrinsky, and wish him the best in his future career aspirations. I am certain he will reach the top of his field, and will be rewarded with a very well-deserved cubicle. I also would like to thank Rob, Felix, Steve, Srikar, and Cody for their friendship and favors over the years. Now that Felix and I have graduated, I count on Zung to carry on the spirit of the Big Red.

My friends helped make my time at MIT more enjoyable. I've enjoyed having Jason and Matt as roommates, and wish them well in their future careers (and advise them to steer clear of those proximity mines!). I hope they come and visit me often after graduation, and Jason, don't forget the jelly-filled munchkins. Over the years, I have always looked forward to meeting with Jason, Mike, Kevin, Phil, Jeev, and Matt for our weekly discussions over a plate of General Gau's, and the occasional pitcher of mango. Certainly, our Kart bouts and movies added to the entertainment. I also wish to thank Mayank("the king"), Tom, Gianni, Sajan, and Chris, along with rest of Prof. Fitzgerald's group, for all the good times. Finally, I also wish to thank Dave, Katherine, Joanne, Li-li, Anton, Rajeev, Manish, Paul, and John for their years of close friendship and support. These friendships have always been very dear to me, and helped influence my decision to remain in Boston.

Most of all, I thank my family for their constant encouragement and support for as long as I can remember, and in particular, for their career guidance during my studies.

Finally, I am grateful to ACUNIA for providing me a very worthy opportunity, and to also thank them for their patience.

# **Table of Contents**

| L              | List of Figures |                                          | 9  |

|----------------|-----------------|------------------------------------------|----|

| List of Tables |                 | 14                                       |    |

| 1              | Intr            | oduction                                 | 15 |

|                | 1.1             | Interconnects & Interconnect Scaling     | 15 |

|                | 1.2             | Electromigration and EM-Induced Failure  | 19 |

|                | 1.3             | Electromigration Drift Experiments       | 20 |

|                | 1.4             | Electromigration in Interconnects        | 22 |

|                | 1.5             | Effects of Alloying and Microstructure   | 27 |

|                | 1.6             | Black's Equation                         | 38 |

|                | 1.7             | Summary                                  | 40 |

|                | 1.8             | Thesis Organization                      | 41 |

| 2              | Mod             | deling of Pure and Alloyed Interconnects | 43 |

|                | 2.1             | Introduction                             | 43 |

|                | 2.2             | Alloy Modeling                           | 44 |

|                | 2.3             | Alloy Effects in Homogeneous Structures  | 55 |

|                | 2.4             | Alloy Effects in Polygranular Clusters   | 58 |

|                | 2.5             | Conclusions                              | 61 |

| 3              | Voic            | d Nucleation & Growth in Long Lines      | 62 |

|                | 3.1             | Introduction                             | 62 |

|                | 3.2             | Modeling of Void Nucleation & Growth     | 63 |

|                | 3.3             | Void Evolution in Long Lines             | 65 |

|                | 3.4             | Scaling Test Data For Long Lines         | 67 |

|                | 3.5             | Conclusions                              | 71 |

| 4 | Void | d Nucleation & Growth in Short Lines    | 73  |

|---|------|-----------------------------------------|-----|

|   | 4.1  | Introduction                            | 73  |

|   | 4.2  | Resistance Saturation & Immortality     | 75  |

|   | 4.3  | Scaling Test Data For Short Lines       | 78  |

|   | 4.4  | Conclusions                             | 81  |

| 5 | Fail | ure Mechanism Maps                      | 83  |

|   | 5.1  | Introduction                            | 83  |

|   | 5.2  | Generation of Al Failure Mechanism Maps | 84  |

|   | 5.3  | Construction of Al-Cu Failure Map       | 92  |

|   | 5.4  | Analytical Construction of Failure Maps | 94  |

|   | 5.5  | Conclusions                             | 98  |

| 6 | Mea  | suring EM in Pure Cu Interconnects      | 100 |

|   | 6.1  | Introduction                            | 100 |

|   | 6.2  | Experimental                            | 104 |

|   | 6.3  | Characterization & Test Results         | 117 |

|   | 6.4  | Conclusions                             | 140 |

| 7 | Sim  | ulation of Pure Cu Interconnects        | 143 |

|   | 7.1  | Introduction                            | 143 |

|   | 7.2  | Model Parameters                        | 144 |

|   | 7.3  | Void Nucleation & Growth                | 144 |

|   | 7.4  | Current Density Scaling                 | 145 |

|   | 7.5  | Cu Failure Map                          | 149 |

|   | 7.6  | Future of Electromigration in Context   | 152 |

|   | 7.7  | Conclusions                             | 157 |

| 8.1 Summary       159         8.2 Future Research       164         Appendix A – MIT/EmSim Description and Source Code         A.1 MIT/EmSim Help Manual       168         A.2 MIT/EmSim Source Code       177         A.3 EmSim-Web Description       198         A.4 MIT/EmSim-ELM Extension Source Code       200         A.5 MIT/EmSim Verification Tools       217         Appendix B – Helper Applications       221         B.1 subline Code Generation Tool       221         B.2 Theracore Input Tool       232         B.3 find_tff Analysis Tool       238         B.4 vgline Analysis Tool       246         B.5 calc_res Analysis Tool       251         B.6 MIT/EmSim Movie-Making Utility       255         B.7 YearSecondCalc Utility       255         B.8 Mask-Layout Utility       261         Appendix C – Analytical Methodologies         C.1 Void Saturation Calculation       319         C.2 Grain Orientation Effects on Cu Reliability       321 | 8 Sum       | mary and Future Research                      | 159 |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------|-----|--|

| Appendix A – MIT/EmSim Description and Source Code  A.1 MIT/EmSim Help Manual A.2 MIT/EmSim Source Code A.3 EmSim-Web Description A.4 MIT/EmSim-ELM Extension Source Code A.5 MIT/EmSim-ELM Extension Source Code A.5 MIT/EmSim Verification Tools  217  Appendix B – Helper Applications B.1 subline Code Generation Tool B.2 Theracore Input Tool B.2 Theracore Input Tool B.3 find_ttf Analysis Tool B.4 vgline Analysis Tool B.5 calc_res Analysis Tool B.6 MIT/EmSim Movie-Making Utility B.7 YearSecondCalc Utility B.8 Mask-Layout Utility  255 B.8 Mask-Layout Utility  261  Appendix C – Analytical Methodologies C.1 Void Saturation Calculation C.2 Grain Orientation Effects on Cu Reliability  321                                                                                                                                                                                                                                                             | 8.1         | Summary                                       | 159 |  |

| A.1 MIT/EmSim Help Manual  A.2 MIT/EmSim Source Code  A.3 EmSim-Web Description  A.4 MIT/EmSim-ELM Extension Source Code  A.5 MIT/EmSim-ELM Extension Source Code  A.5 MIT/EmSim Verification Tools  217  Appendix B – Helper Applications  B.1 subline Code Generation Tool  B.2 Theracore Input Tool  B.3 find_ttf Analysis Tool  B.4 vgline Analysis Tool  B.5 calc_res Analysis Tool  B.6 MIT/EmSim Movie-Making Utility  255  B.7 YearSecondCalc Utility  255  B.8 Mask-Layout Utility  261  Appendix C – Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  321                                                                                                                                                                                                                                                                                                                                              | 8.2         | Future Research                               | 164 |  |

| A.1 MIT/EmSim Help Manual  A.2 MIT/EmSim Source Code  A.3 EmSim-Web Description  A.4 MIT/EmSim-ELM Extension Source Code  A.5 MIT/EmSim-ELM Extension Source Code  A.5 MIT/EmSim Verification Tools  217  Appendix B – Helper Applications  B.1 subline Code Generation Tool  B.2 Theracore Input Tool  B.3 find_ttf Analysis Tool  B.4 vgline Analysis Tool  B.5 calc_res Analysis Tool  B.6 MIT/EmSim Movie-Making Utility  255  B.7 YearSecondCalc Utility  255  B.8 Mask-Layout Utility  261  Appendix C – Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  321                                                                                                                                                                                                                                                                                                                                              |             |                                               |     |  |

| A.2 MIT/EmSim Source Code  A.3 EmSim-Web Description  A.4 MIT/EmSim-ELM Extension Source Code  A.5 MIT/EmSim Verification Tools  217  Appendix B – Helper Applications  B.1 subline Code Generation Tool  B.2 Theracore Input Tool  B.3 find_ttf Analysis Tool  B.4 vgline Analysis Tool  B.5 calc_res Analysis Tool  B.6 MIT/EmSim Movie-Making Utility  B.7 YearSecondCalc Utility  B.8 Mask-Layout Utility  Appendix C – Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  D.3 Code  200  201  221  221  221  222  238  238  246  251  255  251  261  255  261  276  287  298  298  209  200  200  200  200  200                                                                                                                                                                                                                                                                                               | Appen       | dix A – MIT/EmSim Description and Source Code | 168 |  |

| A.3 EmSim-Web Description A.4 MIT/EmSim-ELM Extension Source Code A.5 MIT/EmSim Verification Tools  217  Appendix B – Helper Applications B.1 subline Code Generation Tool 221 B.2 Theracore Input Tool 232 B.3 find_ttf Analysis Tool 238 B.4 vgline Analysis Tool 246 B.5 calc_res Analysis Tool 251 B.6 MIT/EmSim Movie-Making Utility 255 B.7 YearSecondCalc Utility 255 B.8 Mask-Layout Utility 261  Appendix C – Analytical Methodologies C.1 Void Saturation Calculation C.2 Grain Orientation Effects on Cu Reliability 321                                                                                                                                                                                                                                                                                                                                                                                                                                         | A.1         | MIT/EmSim Help Manual                         | 168 |  |

| A.4 MIT/EmSim-ELM Extension Source Code A.5 MIT/EmSim Verification Tools  217  Appendix B – Helper Applications B.1 subline Code Generation Tool 221 B.2 Theracore Input Tool 232 B.3 find_ttf Analysis Tool 238 B.4 vgline Analysis Tool 246 B.5 calc_res Analysis Tool 251 B.6 MIT/EmSim Movie-Making Utility 255 B.7 YearSecondCalc Utility 255 B.8 Mask-Layout Utility 261  Appendix C – Analytical Methodologies C.1 Void Saturation Calculation 319 C.2 Grain Orientation Effects on Cu Reliability 321                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A.2         | MIT/EmSim Source Code                         | 177 |  |

| A.5 MIT/EmSim Verification Tools  217  Appendix B – Helper Applications  B.1 subline Code Generation Tool  B.2 Theracore Input Tool  B.3 find_ttf Analysis Tool  B.4 vgline Analysis Tool  B.5 calc_res Analysis Tool  B.6 MIT/EmSim Movie-Making Utility  255  B.7 YearSecondCalc Utility  255  B.8 Mask-Layout Utility  261  Appendix C – Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | A.3         | EmSim-Web Description                         | 198 |  |

| Appendix B – Helper Applications  B.1 subline Code Generation Tool  B.2 Theracore Input Tool  B.3 find_ttf Analysis Tool  B.4 vgline Analysis Tool  B.5 calc_res Analysis Tool  B.6 MIT/EmSim Movie-Making Utility  B.7 YearSecondCalc Utility  B.8 Mask-Layout Utility  Appendix C – Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  221  221  221  221  221  221  232  238  238                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A.4         | MIT/EmSim-ELM Extension Source Code           | 200 |  |

| B.1 subline Code Generation Tool  B.2 Theracore Input Tool  B.3 find_ttf Analysis Tool  B.4 vgline Analysis Tool  B.5 calc_res Analysis Tool  B.6 MIT/EmSim Movie-Making Utility  B.7 YearSecondCalc Utility  B.8 Mask-Layout Utility  Appendix C - Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  221  232  233  246  247  258  248  249  259  250  251  251  255  251  255  251  255  251  255  251  255  251  255  251  255  251  255  251  255  257  261  270  281  291  292  293  294  295  295  295  296  297  297  298  298  298  298  298  298                                                                                                                                                                                                                                                                                                                                                         | A.5         | MIT/EmSim Verification Tools                  | 217 |  |

| B.1 subline Code Generation Tool  B.2 Theracore Input Tool  B.3 find_ttf Analysis Tool  B.4 vgline Analysis Tool  B.5 calc_res Analysis Tool  B.6 MIT/EmSim Movie-Making Utility  B.7 YearSecondCalc Utility  B.8 Mask-Layout Utility  Appendix C - Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  221  232  233  246  247  258  248  249  255  251  255  251  255  251  255  251  255  251  255  251  255  251  255  261  270  281  291  292  293  294  295  295  297  297  298  298  298  298  298  298                                                                                                                                                                                                                                                                                                                                                                                                      |             |                                               |     |  |

| B.2 Theracore Input Tool  B.3 find_ttf Analysis Tool  B.4 vgline Analysis Tool  B.5 calc_res Analysis Tool  B.6 MIT/EmSim Movie-Making Utility  B.7 YearSecondCalc Utility  B.8 Mask-Layout Utility  Appendix C - Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Appen       | dix B – Helper Applications                   | 221 |  |

| B.3 find_ttf Analysis Tool  B.4 vgline Analysis Tool  B.5 calc_res Analysis Tool  B.6 MIT/EmSim Movie-Making Utility  B.7 YearSecondCalc Utility  B.8 Mask-Layout Utility  Appendix C – Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  238  238  246  251  251  255  B.7 YearSecondCalc Utility  255  261  270  281  292  293  294  295  295  297  207  208  208  208  208  208  208  20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | B.1         | subline Code Generation Tool                  | 221 |  |

| B.4 vgline Analysis Tool  B.5 calc_res Analysis Tool  B.6 MIT/EmSim Movie-Making Utility  B.7 YearSecondCalc Utility  B.8 Mask-Layout Utility  Appendix C - Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  246  251  255  319  C.2 Grain Orientation Effects on Cu Reliability  321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | B.2         | Theracore Input Tool                          | 232 |  |

| B.5 calc_res Analysis Tool  B.6 MIT/EmSim Movie-Making Utility  B.7 YearSecondCalc Utility  B.8 Mask-Layout Utility  255  Appendix C - Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  251  255  319  C.2 Grain Orientation Effects on Cu Reliability  251  255  319  C.2 Grain Orientation Effects on Cu Reliability  251  255  319  261                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | B.3         | find_ttf Analysis Tool                        | 238 |  |

| B.6 MIT/EmSim Movie-Making Utility  B.7 YearSecondCalc Utility  255  B.8 Mask-Layout Utility  261  Appendix C – Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | B.4         | vgline Analysis Tool                          | 246 |  |

| B.7 YearSecondCalc Utility  B.8 Mask-Layout Utility  255  Appendix C – Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | B.5         | calc_res Analysis Tool                        | 251 |  |

| B.8 Mask-Layout Utility  261  Appendix C – Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | B.6         | MIT/EmSim Movie-Making Utility                | 255 |  |

| Appendix C – Analytical Methodologies  C.1 Void Saturation Calculation  C.2 Grain Orientation Effects on Cu Reliability  319  321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <b>B.</b> 7 | YearSecondCalc Utility                        | 255 |  |

| C.1 Void Saturation Calculation 319 C.2 Grain Orientation Effects on Cu Reliability 321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | B.8         | Mask-Layout Utility                           | 261 |  |

| C.1 Void Saturation Calculation 319 C.2 Grain Orientation Effects on Cu Reliability 321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             |                                               |     |  |

| C.2 Grain Orientation Effects on Cu Reliability  321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Appen       | dix C – Analytical Methodologies              | 319 |  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | C.1         | Void Saturation Calculation                   | 319 |  |

| Defenences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | C.2         | Grain Orientation Effects on Cu Reliability   | 321 |  |

| Keierences 222                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Refere      | References 326                                |     |  |

# List of Figures

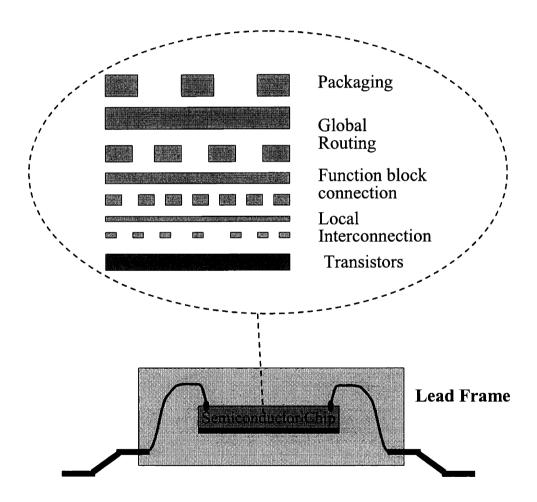

| 1-1  | The hierarchy of interconnect levels allow each metal level varying functionality. Once fabricated, semiconductor chips are placed in environmentally-protective packaging. [Based on Lin 98]                                                 | 16 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

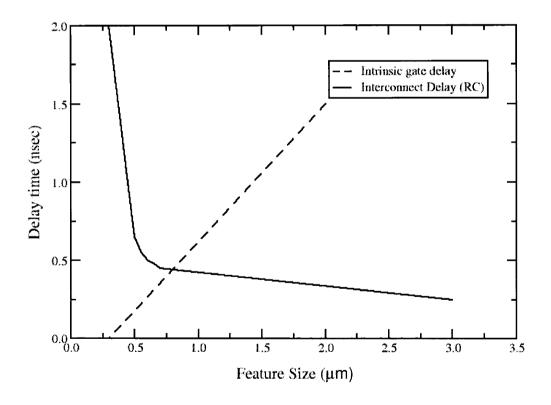

| 1-2  | As transistors and interconnects scale downward, signal transmission through interconnects becomes the major source of delay. [Lin 98]                                                                                                        | 18 |

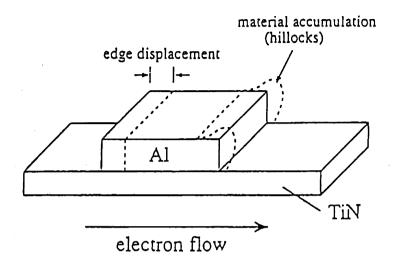

| 1-3  | The Blech drift structure is composed of Al strips deposited on TiN. Application of current results in the removal of Al at the cathode and the formation of hillocks at the anode. [Ble 76, courtesy of Kno <sub>2</sub> 97]                 | 21 |

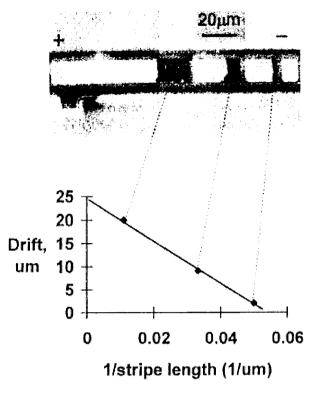

| 1-4  | Drift rate of four Al strips with varying lengths after application of 3.7E5 A/cm <sup>2</sup> .                                                                                                                                              | 22 |

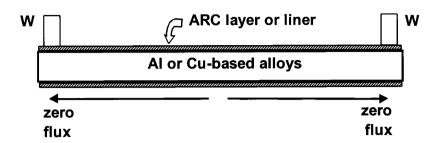

| 1-5  | Interconnect metal is surrounded by a conducting shunt material, with blocking boundaries at either end.                                                                                                                                      | 23 |

| 1-6  | The tensile stress at the cathode rises until the back-stress begins to suppress electromigration. At steady-state, the maximum stress is given by the expression in Eq. 1-2. The current density applied was 1.0 MA/cm <sup>2</sup> .        | 25 |

| 1-7  | An electromigration test of an Al-0.5wt%Cu interconnect results in void nucleation and growth until saturation. [From Fil 95]                                                                                                                 | 27 |

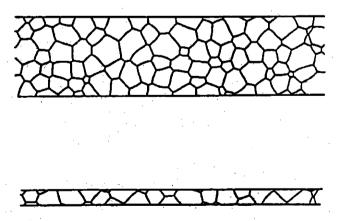

| 1-8  | Interconnects with varying linewidths and equivalent grain sizes can exhibit very different microstructures, leading to different bamboo and polygranular cluster length distributions.                                                       | 29 |

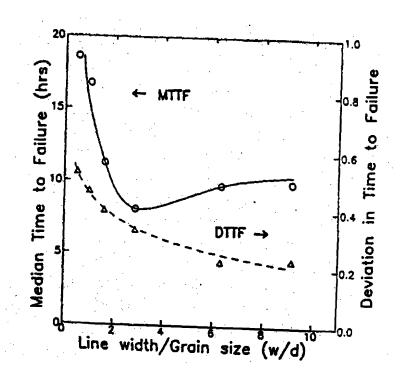

| 1-9  | This figure illustrates the complex dependence of median-time-to-failure (MTTF) of a population of interconnects as a function of linewidth-to-grain-size ratio.                                                                              | 30 |

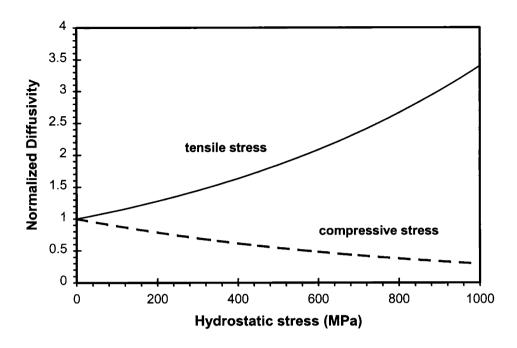

| 1-10 | A tensile stress enhances the diffusivity while a compressive stress reduces the diffusivity.                                                                                                                                                 | 31 |

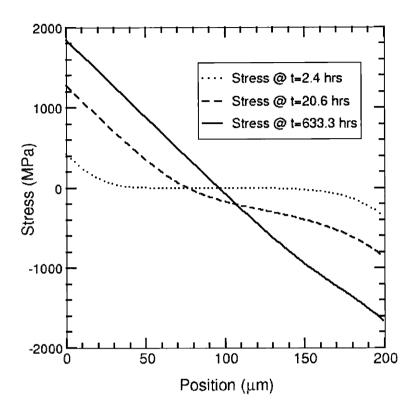

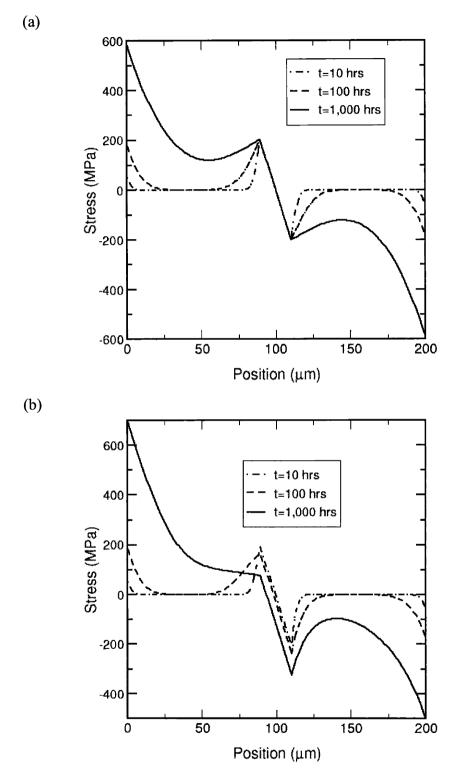

| 1-11 | Stress versus position for an interconnect with electrons proceeding to<br>the right for the case of (a) stress effect on diffusivity neglected and (b)<br>included. Including this effect results in a compressive stress twice as<br>large. | 32 |

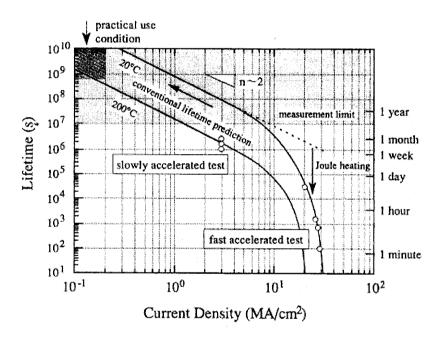

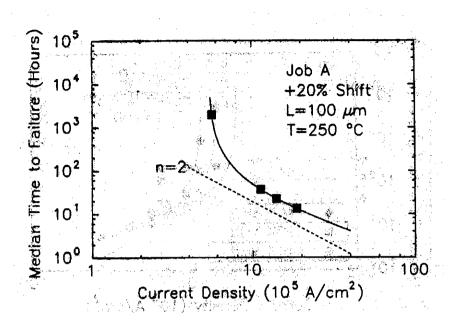

| 1-12 | Lifetime data measured at accelerated conditions is generally scaled to service conditions using Black's equation assuming n=2. At higher densities, Joule heating can significantly alter the interconnect lifetimes. [Courtesy of Kon 97] | 39 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1-13 | The failure times measured for a population of 100 µm long, Al-0.5 wt% Cu lines do not suggest a constant current density exponent. [Courtesy of Fil 95]                                                                                    | 40 |

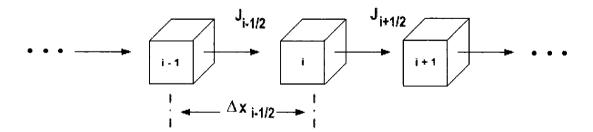

| 2-1  | Implementation involves dividing interconnect into a series of cells and calculating the flux between cells.                                                                                                                                | 45 |

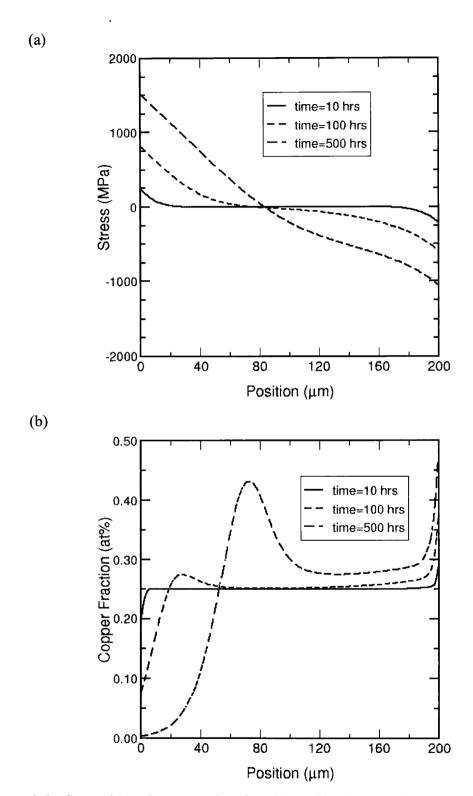

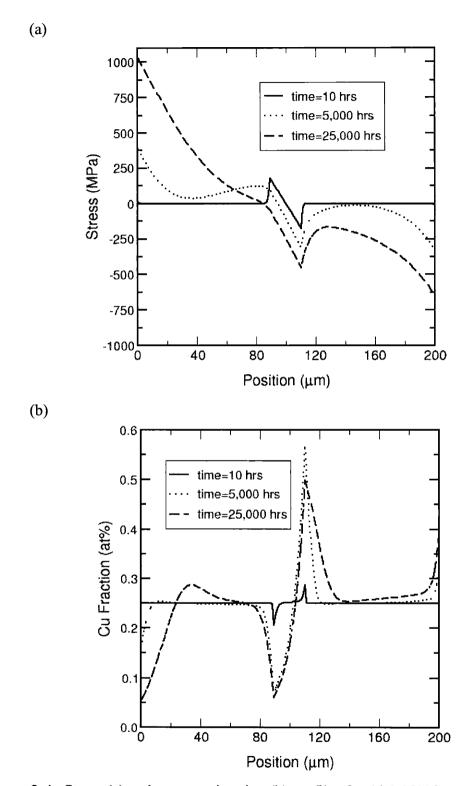

| 2-2  | Stress (a) and copper migration 9b) profiles for an Al-0.25% stud-to-stud line with all-bamboo microstructure at 1 MA/cm <sup>2</sup> .                                                                                                     | 57 |

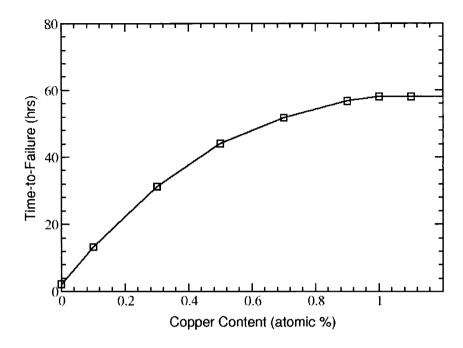

| 2-3  | Time-to-failure results for a 200 µm interconnect with varying Cu alloying content. Increasing Cu contents results in improved lifetimes.                                                                                                   | 58 |

| 2-4  | Stress (a) and copper migration (b) profiles for Al-0.25%Cu stud-to-stud lines with a 21 um polygranular cluster at the center of the line.                                                                                                 | 60 |

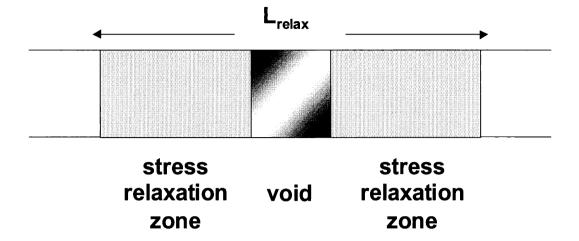

| 3-1  | The nucleation of a void results in the formation of a stress relaxation zone adjacent to the void.                                                                                                                                         | 64 |

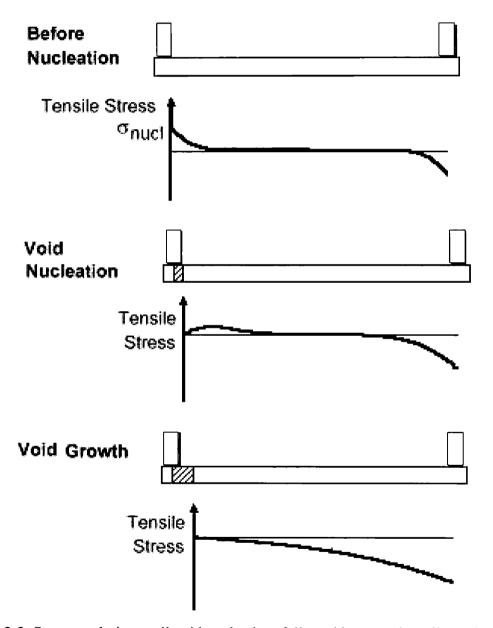

| 3-2  | Stress evolution until void nucleation, followed by growth until steady-state.                                                                                                                                                              | 66 |

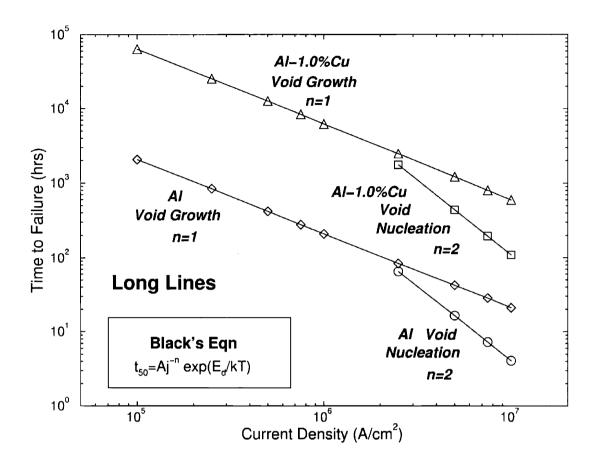

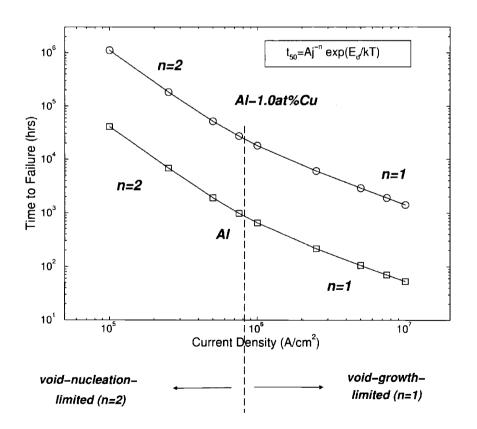

| 3-3  | The current density for void nucleation failure in Al and Al-Cu lines is n=2. The exponent for void growth failure is n=1 in Al and Al-Cu lines.                                                                                            | 69 |

| 3-4  | At high j, void-growth-limited failure is observed, resulting in an n=1 scaling exponent. At low j, failure is nucleation-limited, requiring an n=2 exponent.                                                                               | 70 |

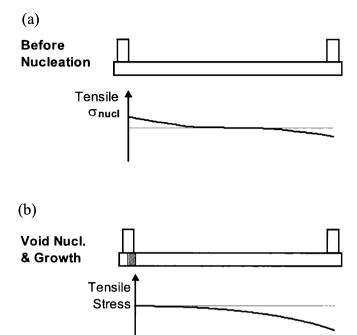

| 4-1  | Stress evolution (a) until void nucleation (b) followed by void growth until (c) a steady-state stress gradient develops.                                                                                                                   | 74 |

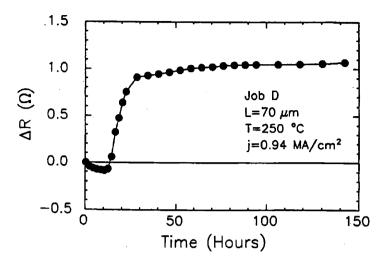

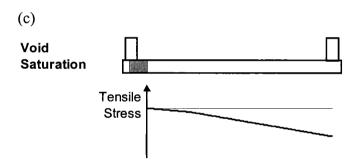

| 4-2  | After the incubation time, the void nucleates causing an increase in the line resistance. The void continues growing until void saturation is reached, resulting in no further increase in resistance.                                      | 78 |

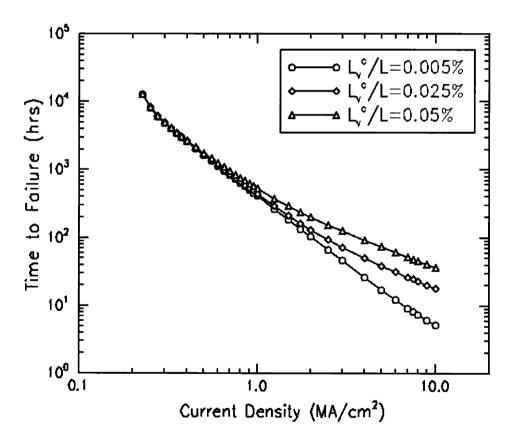

| 4-3  | Times-to-failure as a function of current density for several void length failure conditions.                                                                                                                                               | 80 |

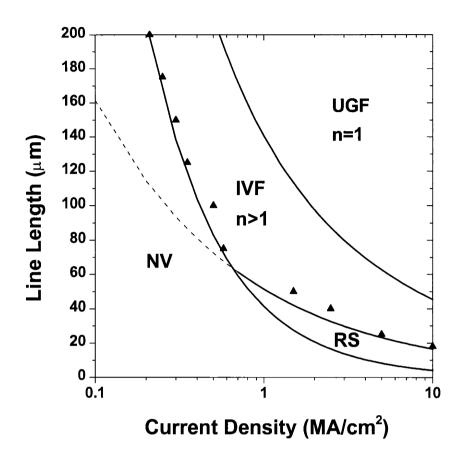

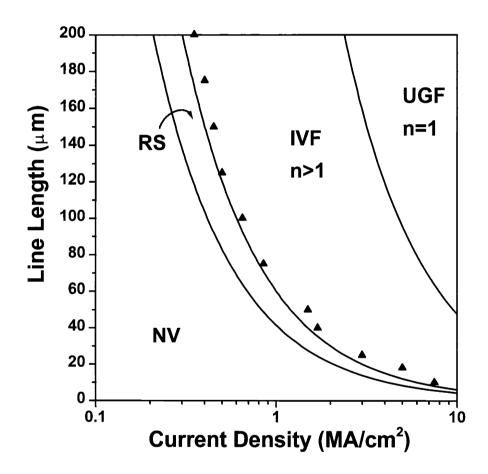

| 5-1 | A line length vs. current density failure mechanism map illustrating regions of immortality without void nucleation(NV), immortality due to void saturation (RS), failures with impeded void growth with n>1 (IVF), and unimpeded void growth-limited failures with n=1 (UGF) assuming a constant void failure length of 0.50 μm. | 85  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

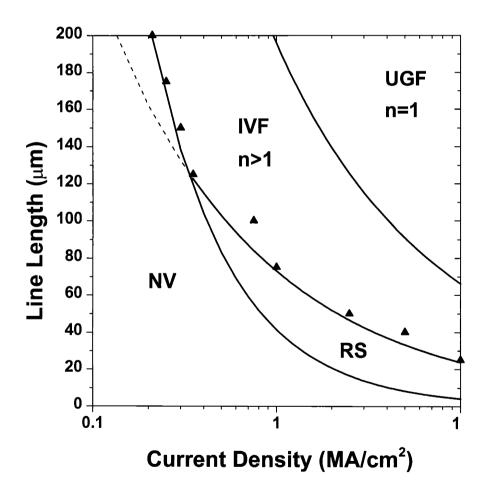

| 5-2 | Line length vs. current density failure mechanism map based on a void volume failure condition of $1.0~\mu m$ . Resistance saturation occurs at longer lines for this failure condition relative to the more conservative failure criterion in Fig. 5-1.                                                                          | 88  |

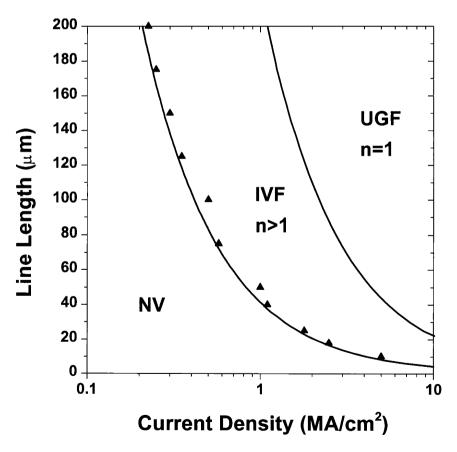

| 5-3 | Line length vs. current density failure mechanism map assuming a resistance failure condition of 25%. No void saturation region is present.                                                                                                                                                                                       | 89  |

| 5-4 | Line length vs. current density failure mechanism map assuming a resistance failure condition of 50%. A small void saturation region is present for all line lengths.                                                                                                                                                             | 91  |

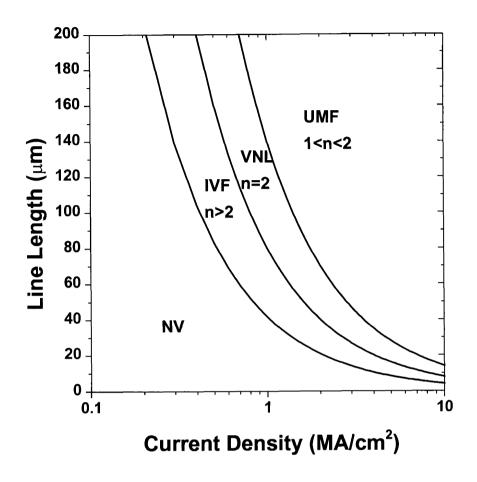

| 5-5 | Failure map assuming that a 1.0% resistance increase causes failure, illustrating regions of immortality without void nucleation (NV), impeded void failure (IVF), void-nucleation-limited failure (VNL), and unimpeded mixed failure (UMF).                                                                                      | 92  |

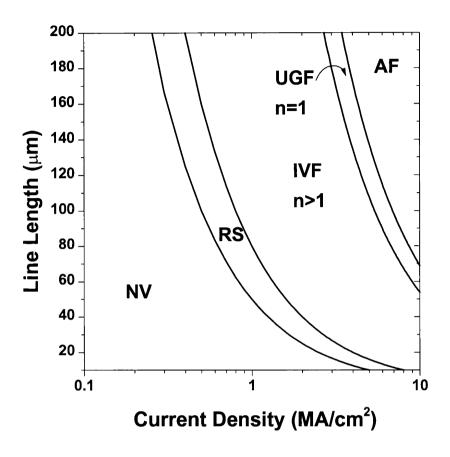

| 5-6 | Failure mechanism map for bamboo Al-0.5wt%Cu, assuming a resistance failure condition of 25%, constructed for a service temperature of 100°C. The corresponding map for bamboo pure Al is identical to this map. A regime for anode failure (AF) is indicated on this map.                                                        | 94  |

| 5-7 | Failure mechanism map assuming a constant-void-length failure condition of 0.5 $\mu$ m. Results from the use of the analytical model for the transition current density are shown as points on this plot, and indicate a good correlation with the simulation results.                                                            | 98  |

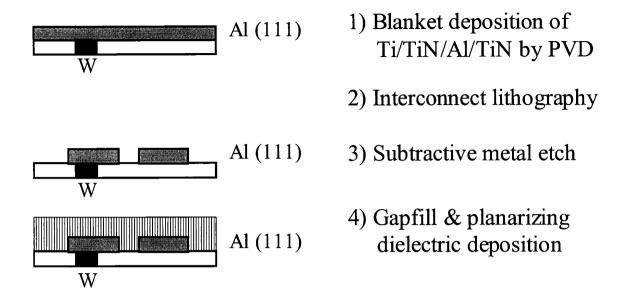

| 6-1 | Subtractive etch fabrication process for patterning Al-based interconnects. [Based on Gro 99]                                                                                                                                                                                                                                     | 101 |

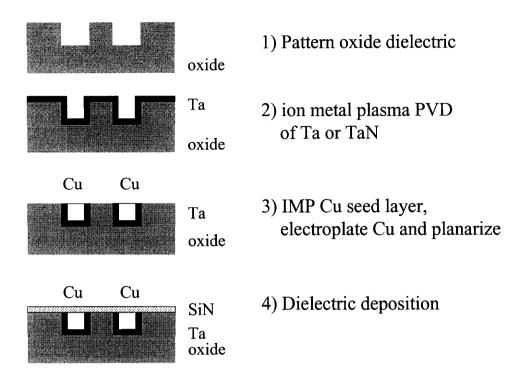

| 6-2 | Cu interconnects are fabricated by the damascene process, which requires the patterning of the dielectric followed by metal deposition and subsequent CMP.                                                                                                                                                                        | 102 |

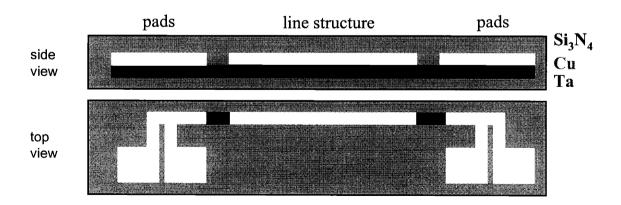

| 6-3 | Top and side view of probe pad interconnect structures. Cu is in white, Ta in black, and nitride in grey.                                                                                                                                                                                                                         | 105 |

| 6-4  | (b) and etch indicators are also shown.                                                                                                                                                                                                                                                                                                                                                                                                    | 106 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

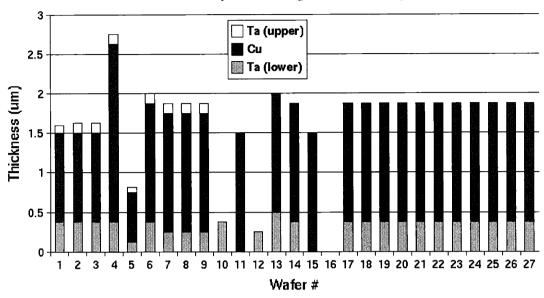

| 6-5  | Thicknesses of Cu / Ta films deposited by sputtering for all wafers fabricated.                                                                                                                                                                                                                                                                                                                                                            | 109 |

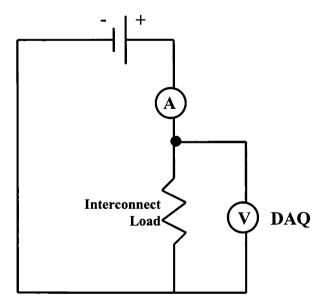

| 6-6  | Schematic of an electromigration test station.                                                                                                                                                                                                                                                                                                                                                                                             | 114 |

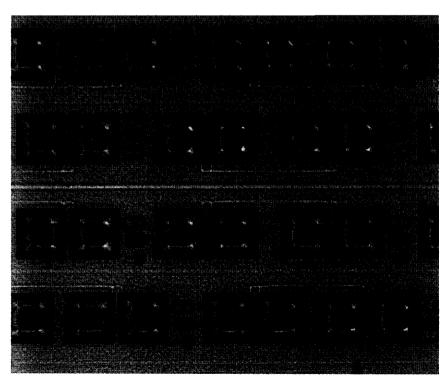

| 6-7  | Optical microscope image of several interconnects.                                                                                                                                                                                                                                                                                                                                                                                         | 118 |

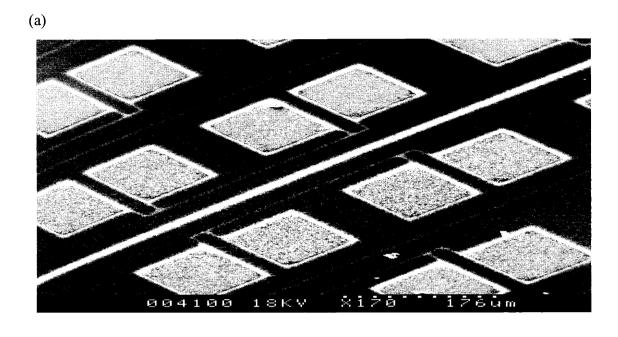

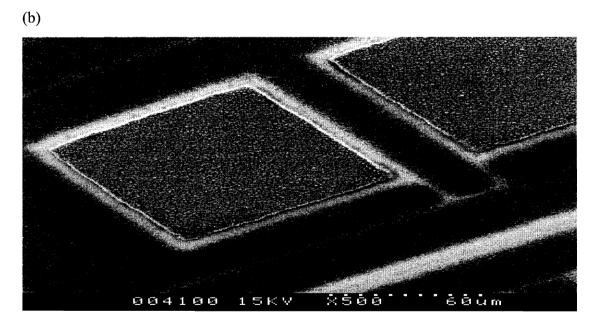

| 6-8  | SEM image of an interconnect structure (a). A close-up of the interconnect is shown in (b). The bright white fuzziness is presumably due to the Ta.                                                                                                                                                                                                                                                                                        | 119 |

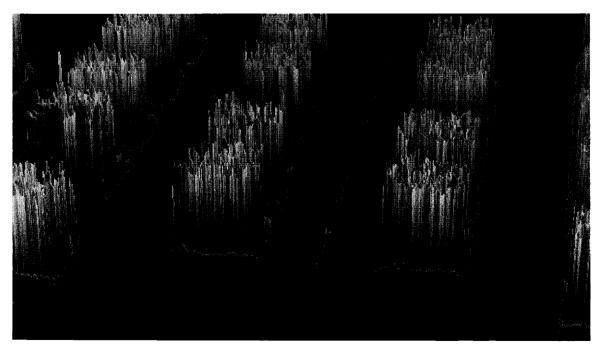

| 6-9  | Interferometric profilometry image of the interconnect test structure.                                                                                                                                                                                                                                                                                                                                                                     | 120 |

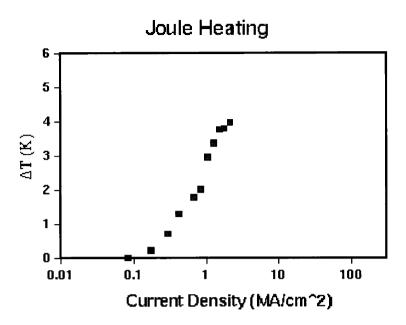

| 6-10 | Joule heating tests demonstrate that the temperature rise in the interconnects is not significant.                                                                                                                                                                                                                                                                                                                                         | 121 |

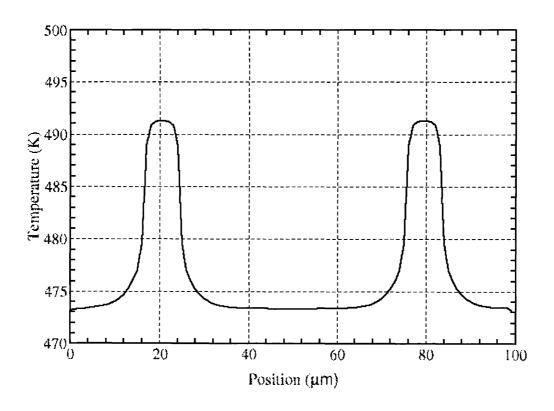

| 6-11 | Temperature profile of the fabricated based on joule heating simulations.                                                                                                                                                                                                                                                                                                                                                                  | 122 |

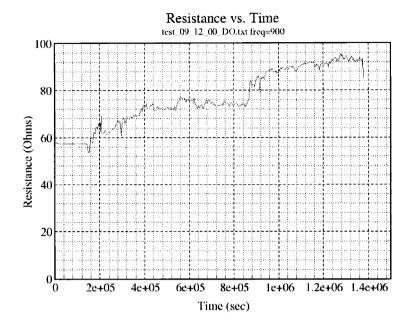

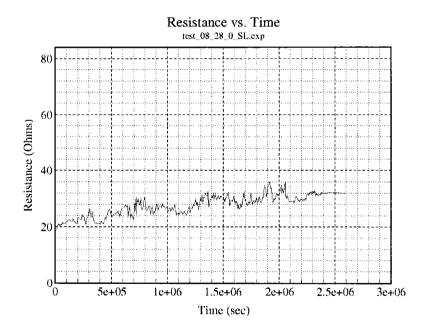

| 6-12 | Typical resistance curves (a,b) observed for resistance saturation in interconnects. The resistance remains constant until a void nucleates, after which it grows linearly until reaching resistance saturation.                                                                                                                                                                                                                           | 127 |

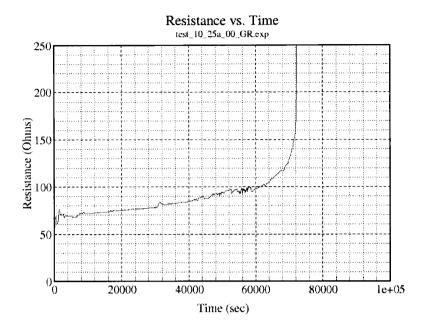

| 6-13 | Typical resistance profile for an interconnect with dielectric failure, leading to a steep increase in resistance.                                                                                                                                                                                                                                                                                                                         | 129 |

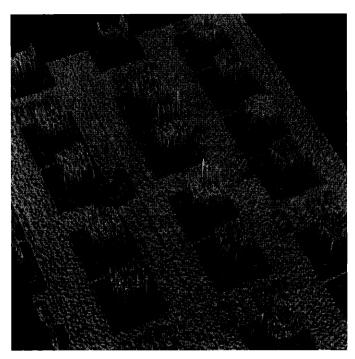

| 6-14 | Profilometer image of failed interconnect, illustrating the formation of a hillock after dielectric failure.                                                                                                                                                                                                                                                                                                                               | 130 |

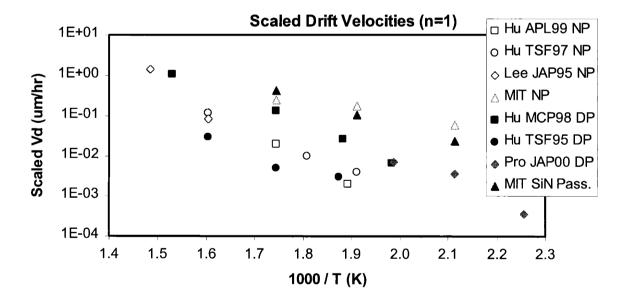

| 6-15 | Drift velocities for the Cu/Ta structure along with those reported for other Blech strips and damascene interconnects. Open data points represent unpassivated (NP) structures while closed data points represent passivated interconnects. Damascene structures are denoted by DP. Open and closed triangles represent the unpassivated and Si <sub>3</sub> N <sub>4</sub> passivated Cu/Ta structures, respectively, used in this study. | 136 |

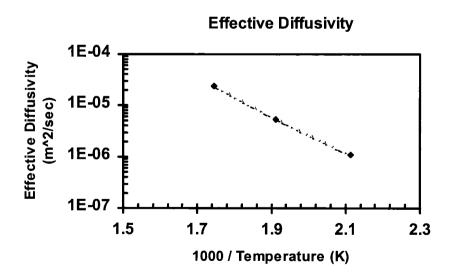

| 6-16 | Effective diffusivity plotted against the inverse of time yields the activation energy and the corresponding diffusivity coefficient.                                                                                                                                                                                                                                                                                                      | 137 |

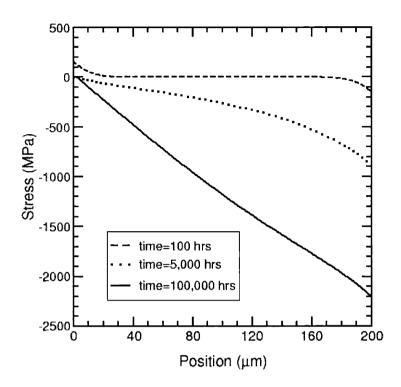

| 7-1 | After the initial development of a tensile and compressive stress (t=100 hrs), a void nucleates and grows (t=5,000 hrs) until void growth saturation is reached (t=100,000 hrs).                                                                                                                                                                                | 145 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

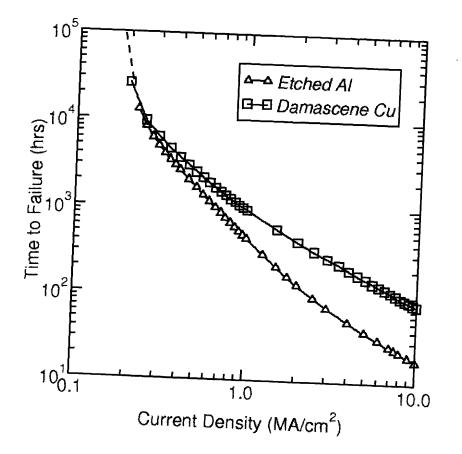

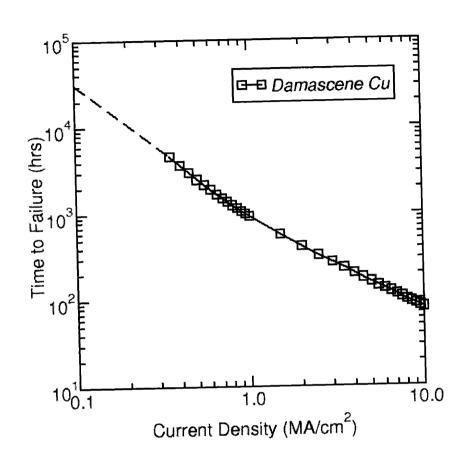

| 7-2 | Current density scaling behavior of Cu interconnects is compared to that of bamboo Al-based technologies. Al data is replotted from Fig. 4-3.                                                                                                                                                                                                                   | 147 |

| 7-3 | The reliability of Cu interconnects at low current densities is significantly reduced upon the removal of the $Si_3N_4$ diffusion barriers.                                                                                                                                                                                                                     | 149 |

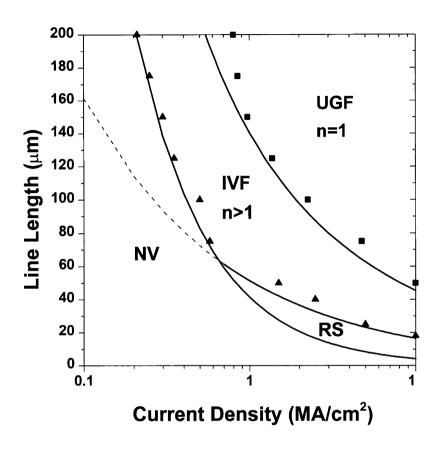

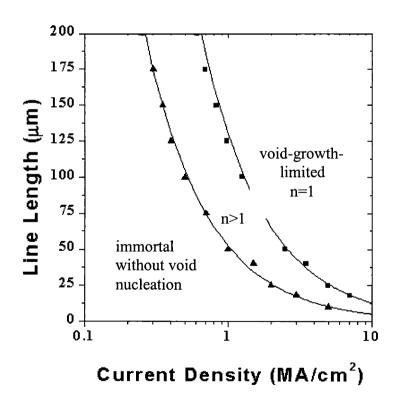

| 7-4 | Failure mechanism map of Cu interconnects assuming 25% resistance failure criterion. Data obtained by simulation is marked by data points, while analytical approximations are represented by solid lines.                                                                                                                                                      | 150 |

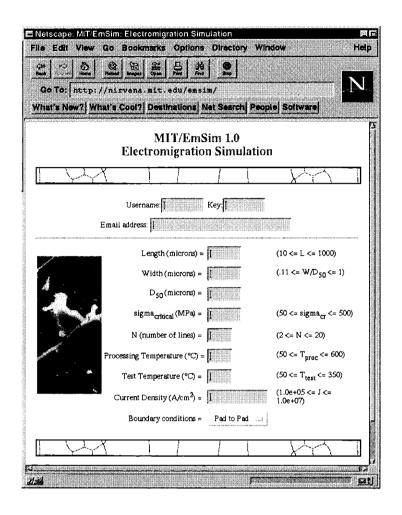

| A-1 | View of EmSim-Web data entry page.                                                                                                                                                                                                                                                                                                                              | 199 |

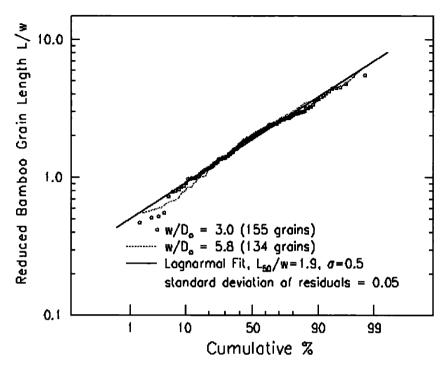

| C-1 | Lognormal plot of normalized bamboo grain length, L/w, distributions in bamboo structures resulting from post-patterning annealing of polygranular strips with different widths. The overlapping curves for different w/ $D_0$ show that the distribution of L/w is line-width-independent. Solid lines represent the best-fitting lognormal distribution.      | 322 |

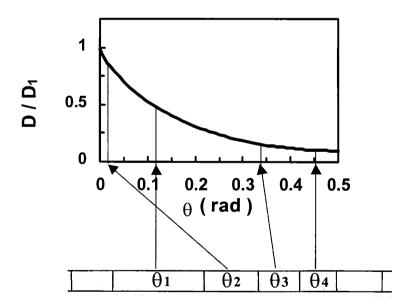

| C-2 | Distribution of interface diffusivities as a function of bamboo grain orientation. The grain orientation is assigned randomly, and the diffusivity for a given orientation $\theta$ is given by D=D <sub>fac</sub> (1+ A $\theta$ ln( $\theta$ ) - B $\theta$ ) where D <sub>fac</sub> = 2.2*10 <sup>-16</sup> m <sup>2</sup> /s at 392°C, A = 1.8, and B=0.55. | 323 |

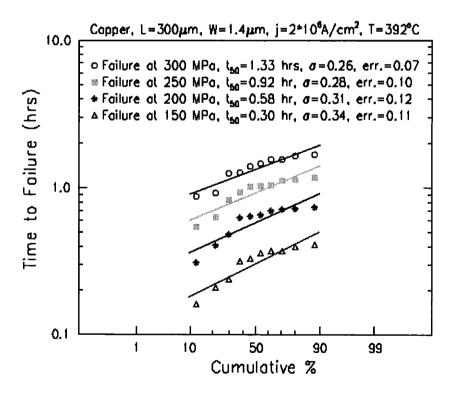

| C-3 | Lognormal plot showing the simulated variations in lifetimes resulting from interface diffusivity variations in lines with bamboo grain                                                                                                                                                                                                                         | 324 |

# **List of Tables**

| 5-I   | Legends Used in Failure Map Figures    | 86  |

|-------|----------------------------------------|-----|

| 6-I   | Comparison of (jL) Product Values      | 131 |

| 6-II  | Comparison of Average Nucleation Times | 132 |

| 6-III | Comparison of z* Values                | 133 |

| 6-IV  | Comparison of Drift Velocities         | 135 |

| 7-I   | Subset of SIA Technology Roadmap       | 153 |

# Chapter 1

## Introduction

The completion of this thesis comes at a time of great change in interconnect and process technology. For over forty years, aluminum and its alloys have served as the primary interconnect material for connecting transistors on semiconductor chips. Today, the industry is in the midst of a transformation to copper-based interconnects fabricated by the damascene process, requiring swift modeling and characterization of these new technologies for rapid adoption into manufacturing. This thesis serves to characterize the reliability of both Al and future Cu interconnect technologies through simulation and experiments.

# 1.1. Interconnects & Interconnect Scaling

A typical semiconductor chip consists of a high purity, singular orientation, planar silicon wafer on which transistor devices are fabricated, as illustrated in Figure 1-1. The processing associated with fabricating the active device (transistor) area is referred to as front-end processing. Above the transistors are several layers of metal interconnects separated by insulating dielectric material such as silica. The interconnects are connected to the transistors and other interconnects on the metal level immediately above or below by vias. The metal levels closest to the transistor (typically referred to as metal 1 for the first metal level, and metal 2 for the second metal level, and so on) are the smallest and