# High Mobility Strained Si/SiGe Heterostructure MOSFETs: Channel Engineering and Virtual Substrate Optimization

by

### Christopher W. Leitz

B.S. Materials Science and Engineering Pennsylvania State University, 1998

Submitted to the Department of Materials Science and Engineering in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy in Electronic Materials

at the Massachusetts Institute of Technology

June 2002

© 2002 Massachusetts Institute of Technology All rights reserved.

| Signature of Author:                                | Department of Materials Science and Engineering May 3, 2002                                                       |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| Certified by:                                       | Eugene A. Fitzgerald  Professor of Materials Science and Engineering  Thesis Supervisor                           |

| Accepted by:  MASSACHUSETTS INSTITUTE OF TECHNOLOGY | Harry L. Tuller Professor of Ceramics and Electronic Materials Chair, Departmental Committee on Graduate Students |

| JUN 1 7 2002                                        | ARCHIVES                                                                                                          |

LIBRARIES

## High Mobility Strained Si/SiGe Heterostructure MOSFETs: Channel Engineering and Virtual Substrate Optimization

by

#### Christopher W. Leitz

Submitted to the Department of Materials Science and Engineering on May 3, 2002 in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in Electronic Materials

#### **ABSTRACT**

High quality relaxed silicon-germanium graded buffers are an important platform for monolithic integration of high speed heterostructure field-effect transistors and III-V-based optoelectronics onto silicon substrates. In this thesis, dislocation dynamics in compositionally graded SiGe layers are explored and mobility enhancements in strained Si/SiGe metal-oxide-semiconductor field-effect transistors (MOSFETs) are evaluated. These results demonstrate the dramatic increases in microelectronics performance and functionality that can be obtained through use of the relaxed SiGe integration platform.

By extending and modifying a model for dislocation glide kinetics in graded buffers to SiGe/Si, a complete picture of strain relaxation in SiGe graded buffers emerges. To investigate dislocation glide kinetics in these structures, a series of identical samples graded to 30% Ge have been grown at temperatures between 650°C and 900°C on (001)-, (001) offcut 6° towards an in-plane <110>-, and (001) offcut 6° towards an in-plane <100>-oriented Si substrates. The evolution of field threading dislocation density (TDD) with growth temperature in the on-axis samples indicates that dislocation nucleation and glide kinetics together control dislocation density in graded buffers. The TDD of samples grown on offcut substrates exhibits a more complicated temperature dependence, due to their reduced tendency towards dislocation pile-up formation at low temperature and dislocation reduction reactions at high temperature. Finally, by evaluating field threading dislocation density and dislocation pile-up density in a wide variety of SiGe graded buffers, a correlation between dislocation pile-up formation and increases in field threading dislocation density emerges.

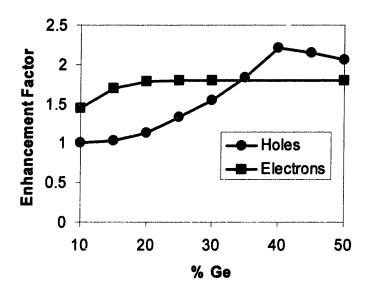

Record mobility strained Si p-MOSFETs have been fabricated on relaxed 40% Ge virtual substrates. Hole mobility enhancements saturate at virtual substrate compositions of 40% Ge and above, with mobility enhancements over twice that of co-processed bulk Si devices. In contrast, hole mobility in strained Si p-MOSFETs displays no strong dependence on strained layer thickness. These results indicate that strain is the primary variable in determining hole mobility in strained Si p-MOSFETs and that symmetric electron and hole mobility enhancements in strained Si MOSFETs can be obtained for virtual substrate compositions beyond 35% Ge.

The effect of alloy scattering on carrier mobility in tensile strained SiGe surface channel MOSFETs is measured directly for the first time. Electron mobility is degraded much more severely than hole mobility in these heterostructures, in agreement with theoretical predictions.

Dual channel heterostructures, which consist of the combination of buried compressively strained Si<sub>1-y</sub>Ge<sub>y</sub> buried channels and tensile strained Si surface channels, grown on relaxed Si<sub>1-x</sub>Ge<sub>x</sub> virtual substrates, are explored in detail for the first time. Hole mobilities exceeding 700 cm<sup>2</sup>/V-s have been achieved by combining tensile strained Si surface channels and compressively strained 80% Ge buried channels grown on relaxed 50% Ge virtual substrates. This layer sequence exhibits nearly symmetric electron and hole mobilities, both enhanced relative to bulk Si. Though channel composition plays a more important role than strain in determining hole mobility in dual channel heterostructures, significant hole mobility enhancements can be obtained even in low-Gecontent buried channels, despite the effects of alloy scattering. Finally, the best high-field hole mobility enhancements are obtained for structures with thin Si surface layers, whereby the hole is forced into the high mobility strained Si<sub>1-y</sub>Ge<sub>y</sub> buried channel. Overall, dual channel heterostructures display excellent promise for high mobility *n*- and *p*-MOSFETs and demonstrate the incredible performance improvements available through heterostructure MOSFET channel engineering.

Thesis Supervisor: Eugene A. Fitzgerald

Title: Professor of Materials Science and Engineering

# **Table of Contents**

| List of Figures                                                                          | 8   |

|------------------------------------------------------------------------------------------|-----|

| List of Tables                                                                           | 16  |

| Acknowledgements                                                                         | 17  |

| Chapter 1. Introduction and Background                                                   |     |

| 1.1. Motivation                                                                          | 22  |

| 1.2. The Relaxed SiGe Integration Platform                                               | 25  |

| 1.3. Lattice Mismatch and Critical Thickness                                             | 26  |

| 1.4. Active Slip Systems in SiGe/Si Heteroepitaxy                                        | 29  |

| 1.5. Comparing Dislocation Morphology in Low- and High-Mismat                            | ch  |

| Systems                                                                                  |     |

| 1.6. Compositionally Graded Buffers                                                      | 31  |

| 1.6.1. Evolution of Threading Dislocation Glide Density in Compositionally Graded Layers | ,   |

| 1.6.2. Barriers to Dislocation Glide in SiGe and III-V Materials                         |     |

| 1.6.3. Controlling Threading Dislocation Pile-Ups in Compositionally Grade SiGe Layers   | ded |

| 1.7. Device Integration on Relaxed SiGe Virtual Substrates                               | 41  |

| Chapter 2. High Mobility Strained Si and SiGe Field-Effect                               |     |

|                                                                                          | 42  |

| Transistors on Relaxed SiGe Virtual Substrates                                           |     |

| 2.1. Overview of Metal-Oxide-Semiconductor Field-Effect Transisto                        |     |

| Technology                                                                               |     |

| 2.1.1. Universal Mobility Curves for Si MOSFETs                                          |     |

| 2.1.2. Buried Channel MOSFETs                                                            |     |

| 2.2. Strained Si and SiGe Heterostructure FETs                                           |     |

| 2.2.1. Electronic Properties of SiGe Alloys                                              |     |

| 2.2.2. Effect of Strain on the Valence Band                                              |     |

| 2.2.3. Effect of Strain on the Conduction Band                                           |     |

| 2.2.5. Pseudomorphic SiGe p-Channel FETs                                                 |     |

| 2.2.6. SiGe p-Channel FETs on Relaxed SiGe Virtual Substrates                            |     |

| 2.2.7. Tensile Strained Si: Type II Band Alignment                                       |     |

| 2.2.8. Strained Si p-MOSFETs                                                             |     |

| 2.2.9. Strained Si n-MOSFETs                                                             |     |

| 2.2.10. SiGe Heterostructure FETs for CMOS Applications                                  |     |

| 2.3. Scope and Organization of Thesis                                                    | 68  |

| Chapter 3. SiGe Growth and Device Fabrication                                            | 70  |

| 3.1.         | Ultrahigh Vacuum Chemical Vapor Deposition                                           | 71         |

|--------------|--------------------------------------------------------------------------------------|------------|

| 3.1          | 1.1. Material Characterization                                                       | 76         |

| 3.2.         | Short Flow MOSFET Process                                                            | 82         |

|              | 2.1. Motivation for the Short Flow MOSFET                                            | 82         |

|              | 2.2. MOSFET Fabrication Process                                                      |            |

| 3.2          | 2.3. Carrier Mobility Extraction                                                     | 86         |

| Chapt        | ter 4. Dislocation Dynamics in Compositionally Grade                                 |            |

| 4.1          | Overview of Compositionally Graded SiGe Buffer Growth a                              | 85         |

| 4.1.         | Characterization                                                                     |            |

| 42           | Strain Relaxation Kinetics in Compositionally Graded SiGe                            |            |

|              | 2.1. Extracting Dislocation Glide Activation Energies in Samples Gro                 | own on     |

| 12           | On-Axis Substrates                                                                   |            |

|              | Exploring the Link Between Field Dislocations and Dislocat                           |            |

| 7.5.         | Pile-Ups                                                                             |            |

| 4.4.         | Application to Ge/SiGe/Si Virtual Substrates                                         |            |

|              | • •                                                                                  |            |

|              | ter 5. Surface Channel Strained Si p-MOSFETs                                         |            |

| 5.1.         |                                                                                      |            |

| <i>5</i> 0   |                                                                                      | III<br>112 |

| 5.2.         |                                                                                      |            |

| 5.3.         |                                                                                      |            |

|              | Alloy Scattering in Strained SiGe Surface Channels                                   |            |

| 5.4          | 1.1. Comparing Electron and Hole Mobility Degradation in Strained Alloy Channels     |            |

| 5.4          | 1.2. Evolution of Interface Quality with Alloy Channel Content                       |            |

|              | Strategies for Increased Carrier Confinement                                         |            |

|              | •                                                                                    |            |

| -            | er 6. Dual Channel Heterostructure MOSFETs                                           |            |

| 6.1.         | Overview of Dual Channel Heterostructure p-MOSFET Gro                                |            |

| 6.2.         | Effect of Channel Composition on Hole Mobility Enhancem                              | ents 137   |

| 6.3.         | Effect of Strain on Hole Mobility Enhancements                                       | 140        |

| 6.4.         | High Electron and Hole Mobility in Dual Channe Heterostru                            | ctures     |

|              |                                                                                      |            |

| 6.4.         | .1. Retaining High-Field Hole Mobility Enhancements in Dual Chan<br>Heterostructures |            |

| Chante       | er 7. Conclusions and Future Work                                                    |            |

|              | Cummon, of Evnorimental Work                                                         | 110        |

| 7.1.<br>7.2. | Summary of Experimental Work                                                         | 148<br>120 |

| 1.7.         | ATEAS FOR PURFUEL WORK AND PUBLIC PROSDECTS                                          | 150        |

| Appendix A. Analysis of Graded Buffers by | Triple-Axis X-Ray |

|-------------------------------------------|-------------------|

| Diffraction                               | 157               |

| Appendix B. Short Flow MOSFET Fabrication | on Sequence161    |

| Bibliography                              | 163               |

# **List of Figures**

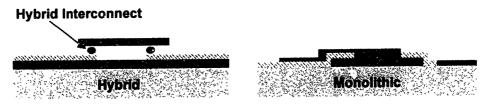

| Figure 1.1  | Schematic of hybrid versus monolithic integration techniques. The hybrid scheme (pictured on the left) involves integration of single components while the monolithic scheme (pictured on the right) utilizes film growth and/or wafer bonding and patterning to enable very-large-scale integration of dissimilar materials onto a common substrate                                                                                                                                               |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

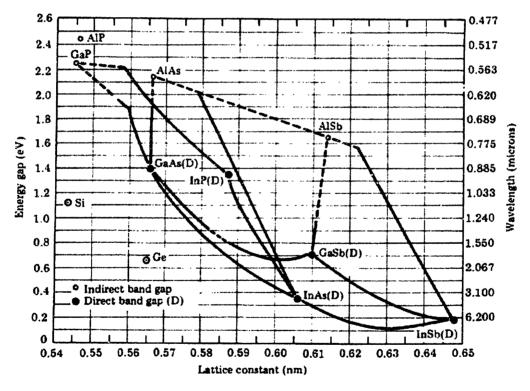

| Figure 1.2  | Bandgap versus lattice constant for common semiconductor materials. Figure adapted from Mayer and Lau. <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                |

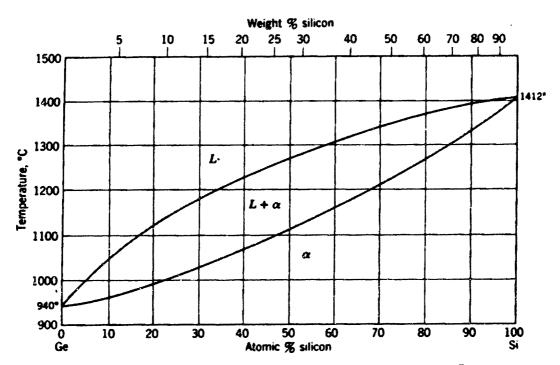

| Figure 1.3  | The Si-Ge Binary Phase Diagram, adapted from Gandhi. <sup>6</sup> Si and Ge are completely miscible, enabling SiGe films of arbitrary composition to be grown without phase segregation                                                                                                                                                                                                                                                                                                            |

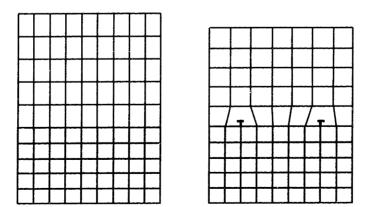

| Figure 1.4  | Schematic of pseudmorphic growth and the onset of dislocation formation in lattice-mismatched heteroepitaxy. Initially, the in-plane film lattice constant is constrained to that of the substrate, as shown on the left. Above a critical thickness, dislocation formation becomes energetically favorable and the film relaxes, as shown on the right                                                                                                                                            |

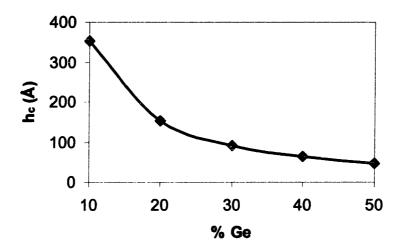

| Figure 1.5  | Critical thickness ( $h_c$ ) of Si <sub>1-x</sub> Ge <sub>x</sub> alloys on Si (001) versus Ge content ( $x$ ). Critical thickness drops rapidly with increasing lattice mismatch                                                                                                                                                                                                                                                                                                                  |

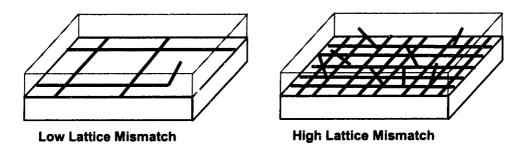

| Figure 1.6  | Illustration of dislocation morphology in low mismatch versus high mismatch systems. In low lattice mismatch films, relatively few mobile dislocations relieve mismatch strain. Under high lattice mismatch, a high density of mostly sessile dislocations nucleates at the film/substrate interface                                                                                                                                                                                               |

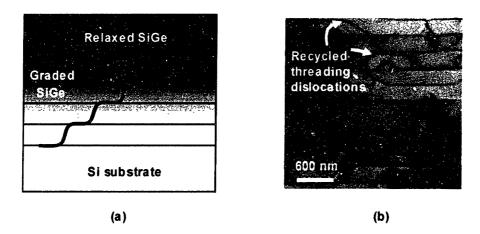

| Figure 1.7  | (a) Compositionally graded SiGe buffer schematic. A graded buffer consists of a series of step-graded, low mismatch interfaces. Each layer is relaxed to its intermediate lattice constant, and threading dislocations are recycled throughout the graded region. (b) Cross-sectional transmission electron micrograph of a compositionally graded SiGe region, showing threading dislocations being recycled as misfit dislocations throughout the graded region. Image courtesy of Thomas Langdo |

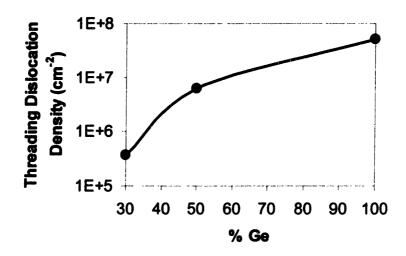

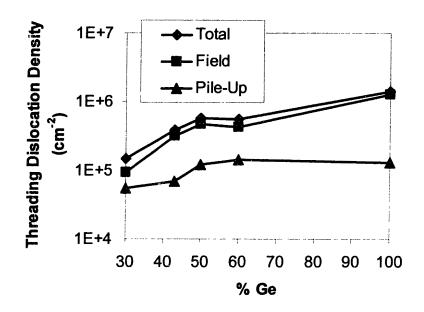

| Figure 1.8  | Overall threading dislocation density (a sum of the density of threading dislocations in the field and trapped in dislocation pile-ups) versus final Ge content for SiGe graded buffers grown at 750°C. Dislocation pile-ups cause an increase in overall threading dislocation density                                                                                                                                                                                                            |

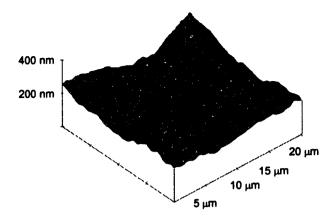

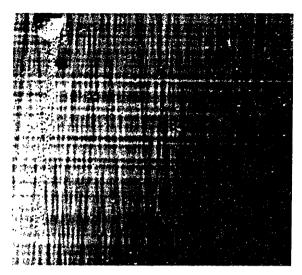

| Figure 1.9  | Atomic force microscopy image of the surface of a SiGe compositionally graded buffer showing the characteristic crosshatch surface morphology. In this case, the buffer has been graded to 50% Ge at a grading rate of 10% Ge/µm (2000 Å steps of 2% Ge)                                                                                                                                                                                                                                           |

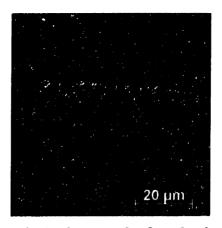

| Figure 1.10 | Plan-view optical micrograph of a selectively etched SiGe surface revealing widely spaced dislocations in the field and a large threading dislocation pile-up. Dislocations trapped in pile-ups cannot relieve                                                                                                                                                                                                                                                                                     |

|             | mismatch strain, forcing nucleation of additional dislocations in the field and causing an escalation in overall dislocation density                                                                                                                                                                                                                                                                              |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

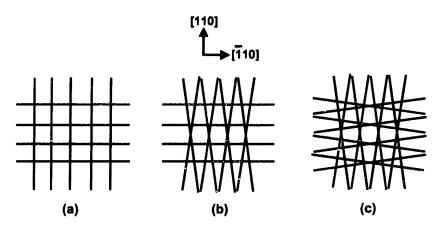

| Figure 1.11 | Schematic of cross-hatch morphology for SiGe graded buffers grown on (a) (001) Si substrates, (b) (001) Si substrates offcut 6° towards an inplane <110>, and (c) (001) Si substrates offcut 6° towards an in-plane <100>. For graded buffers deposited on offcut substrates, the probability that long parallel lines of misfit dislocations can form is reduced, leading to reduced dislocation pile-up density |

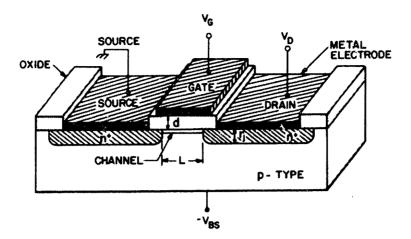

| Figure 2.1  | Cross-section of a typical metal-oxide-semiconductor field-effect transistor. Figure adapted from Sze. 36                                                                                                                                                                                                                                                                                                         |

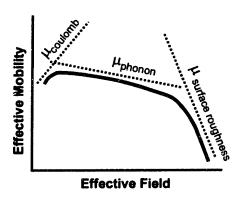

| Figure 2.2  | Universal electron and hole mobility relations for bulk Si MOSFETs. At low fields, carrier mobility is limited mainly by Coulomb scattering. At moderate vertical fields, carrier mobility is limited by phonon scattering. At high vertical fields, surface roughness scattering limits carrier mobility.                                                                                                        |

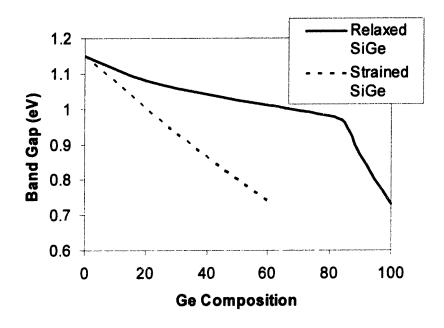

| Figure 2.3  | Bandgap of relaxed and compressively strained SiGe alloys versus Ge composition. In both cases, bandgap drops as Ge composition increases.                                                                                                                                                                                                                                                                        |

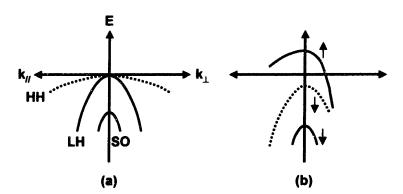

| Figure 2.4  | Valence band structure of (a) unstrained Si and (b) Si under biaxial tensile strain. Tensile strain lowers the energy of the heavy hole and spin-orbit subbands relative to the light hole subband and modifies the shape of the valence subbands.                                                                                                                                                                |

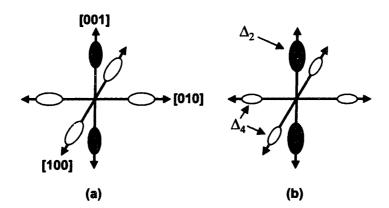

| Figure 2.5  | Conduction band structure of (a) unstrained Si and (b) Si under biaxial tensile strain                                                                                                                                                                                                                                                                                                                            |

| Figure 2.6  | Band alignments for strained $Si_{1-y}Ge_y$ /relaxed $Si_{1-x}Ge_x$ ( $x < y$ ), illustrating the type I band offset that emerges for compressively strained $Si_{1-y}Ge_y$ alloys on $Si_{1-x}Ge_x$                                                                                                                                                                                                              |

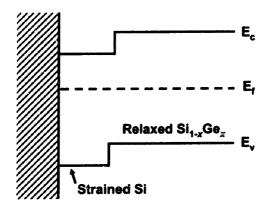

| Figure 2.7  | Band alignments for strained Si on relaxed Si <sub>1-x</sub> Ge <sub>x</sub> illustrating the type II band offset for these heterostructures                                                                                                                                                                                                                                                                      |

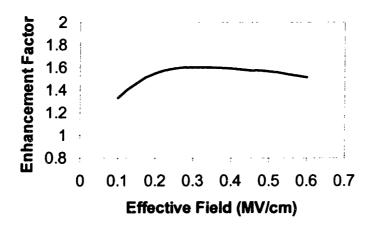

| Figure 2.8  | Hole mobility enhancement versus effective vertical field for a typical strained Si p-MOSFET. At low vertical fields, hole mobility is suppressed by parallel conduction through the relaxed SiGe virtual substrate. Hole mobility enhancements also decrease at high-fields, possibly from intervalley scattering                                                                                                |

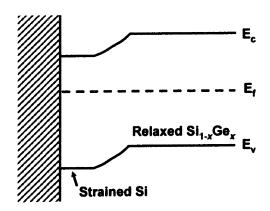

| Figure 2.9  | Band alignments for strained Si on relaxed SiGe using a gradeback layer at the interface. The gradeback smoothes the valence band discontinuity, allowing holes to populate the high mobility strained Si layer at low vertical fields                                                                                                                                                                            |

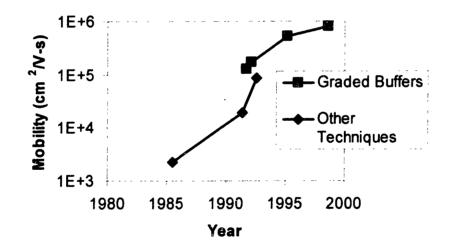

| Figure 2.10 | Evolution of record low temperature electron mobility in strained Si versus time. The introduction of the graded buffer technique resulted in a rapid increase in electron mobility. In chronological order, the record for electron mobility in strained Si grown without graded buffers was held by                                                                                                             |

|             | Abstreiter et al., <sup>77</sup> Ismail et al., <sup>86</sup> and Nelson et al., <sup>87</sup> while the record for electron mobility in strained Si grown on graded buffers was held by Mii et al., <sup>88</sup> Schäffler et al., <sup>89</sup> Ismail et al., <sup>90</sup> and Sugii et al. <sup>91</sup> Figure adapted from Schäffler. <sup>67</sup>                                                                                                                    |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

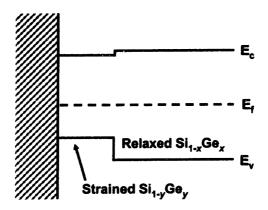

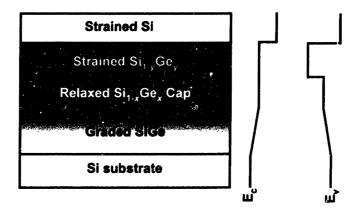

| Figure 2.11 | Schematic layer sequence and band alignments for dual channel heterostructures. Strained layer thicknesses have been exaggerated for clarity. The buried compressively strained Si <sub>1-y</sub> Ge <sub>y</sub> channel is a quantum well for holes while the surface strained Si channel is a quantum well for electrons. The conduction band offset between the relaxed Si <sub>1-x</sub> Ge <sub>x</sub> and the strained Si <sub>1-y</sub> Ge <sub>y</sub> is negligible |

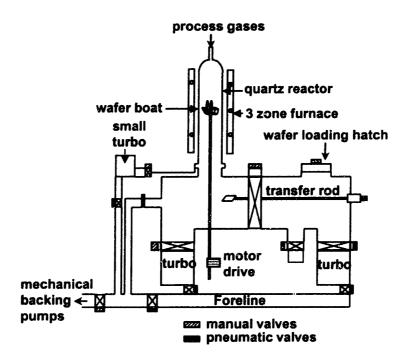

| Figure 3.1  | Schematic of the UHVCVD system used in this work                                                                                                                                                                                                                                                                                                                                                                                                                               |

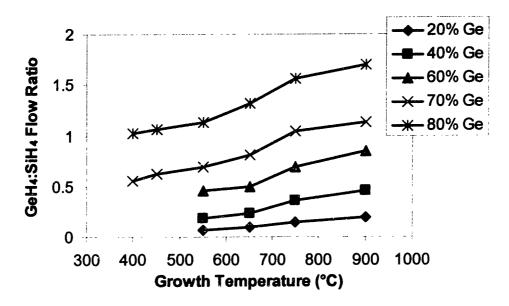

| Figure 3.2  | Experimentally determined ratio of GeH <sub>4</sub> :SiH <sub>4</sub> flow necessary to obtain a given Ge composition as a function of growth temperature for the UHVCVD system used in this study                                                                                                                                                                                                                                                                             |

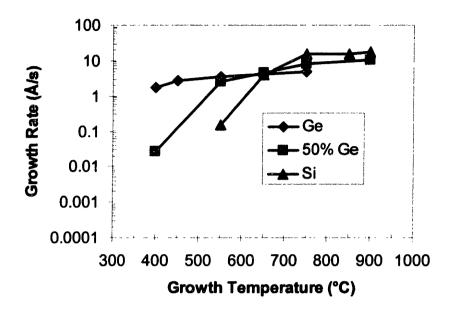

| Figure 3.3  | Growth rates of Si, Si <sub>0.5</sub> Ge <sub>0.5</sub> and Ge as a function of growth temperature in the UHVCVD used in this study. Growth rates fall rapidly at low temperature, where cracking of source gases becomes the rate-limiting step in crystal growth                                                                                                                                                                                                             |

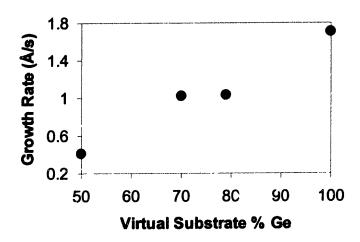

| Figure 3.4  | Growth rate of undoped Ge at 400°C as a function of virtual substrate Ge composition for the UHVCVD system used in this study. Growth rate increases rapidly as the crystal surface becomes more Ge-rich                                                                                                                                                                                                                                                                       |

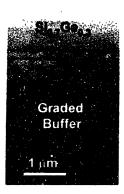

| Figure 3.5  | Cross-sectional TEM of a compositionally graded SiGe buffer graded to a final composition of 30% Ge                                                                                                                                                                                                                                                                                                                                                                            |

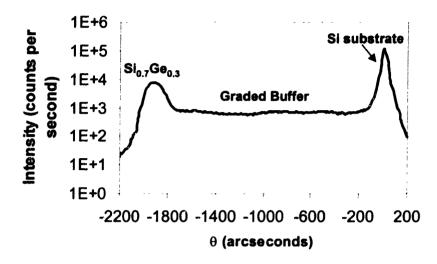

| Figure 3.6  | Example of an (004) $\theta/2\theta$ scan obtained from a compositionally graded SiGe buffer graded to a final Ge composition of 30%                                                                                                                                                                                                                                                                                                                                           |

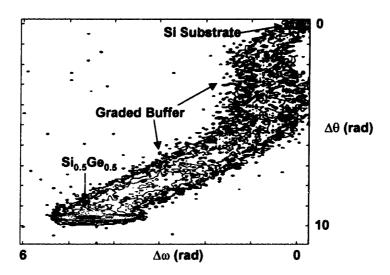

| Figure 3.7  | Example of an (004) reciprocal space map obtained from a compositionally graded SiGe buffer graded to a final Ge composition of 50%                                                                                                                                                                                                                                                                                                                                            |

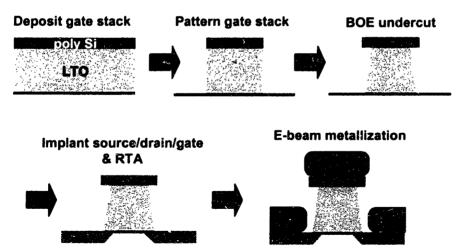

| Figure 3.8  | Short flow MOSFET process schematic. Since the geometry of metal deposition results in an electrically isolated source, gate, and drain, transistors can be fabricated in a single lithography step                                                                                                                                                                                                                                                                            |

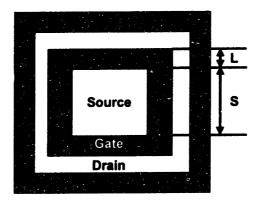

| Figure 3.9  | Top view of short flow MOSFET ring transistor with relevant device dimensions indicated                                                                                                                                                                                                                                                                                                                                                                                        |

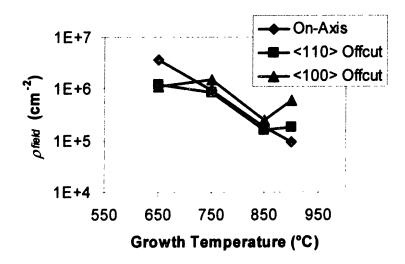

| Figure 4.1  | Field threading dislocation versus growth temperature for the three different substrate offcuts investigated. Generally, field threading dislocation density decreases with increasing growth temperature93                                                                                                                                                                                                                                                                    |

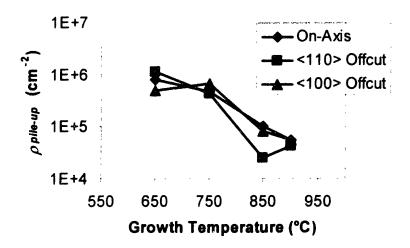

| Figure 4.2  | Total density of threading dislocations trapped in pile-ups versus growth temperature for the three different substrate offcuts investigated. Dislocation pile-up density decreases with increasing growth temperature.                                                                                                                                                                                                                                                        |

|             | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

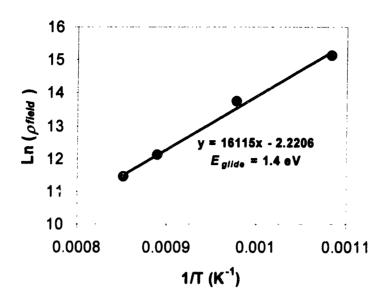

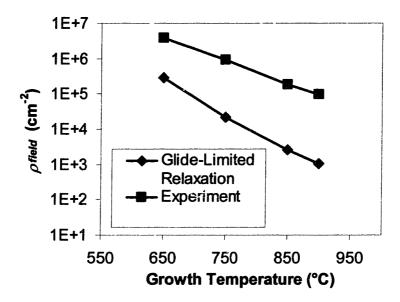

| Figure 4.3  | Fit of $\rho_{field}$ versus $1/T$ to obtain $E_{Glide}$ for on-axis glide kinetics samples. The extracted value of the activation energy for dislocation glide in this series is 1.4 eV                                                                                                                                                                         |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

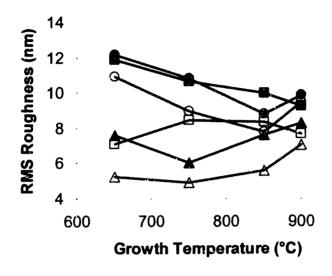

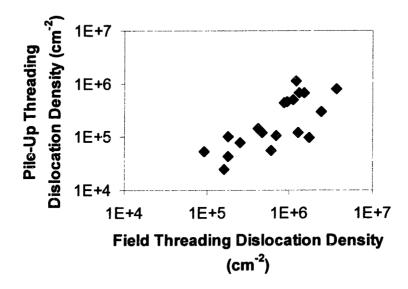

| Figure 4.4  | RMS roughness versus growth temperature for glide kinetics samples deposited on on-axis substrates (circles), substrates offcut towards a <110> (squares), and substrates offcut towards a <100> (triangles). Closed symbols are for 25 × 25 $\mu$ m scans, and open symbols are for 10 × 10 $\mu$ m scans.                                                      |

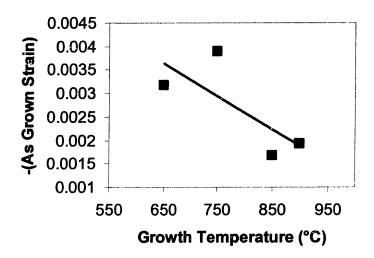

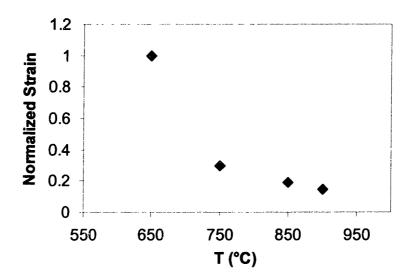

| Figure 4.5  | As-grown strain versus growth temperature for glide kinetics samples. As-grown strain drops with increasing growth temperature, possibly indicating that strain is accumulating during graded buffer growth at low temperature                                                                                                                                   |

| Figure 4.6  | Experimental and theoretical variation (taking $E_{glide}$ to be 2.25 eV) of field threading dislocation density for on-axis glide kinetics samples. The gap between the theoretical variation and experimental measurements reflects the influence of dislocation nucleation processes on field threading dislocation density.                                  |

| Figure 4.7  | Calculated variation of strain with growth temperature needed to account for the difference between theory and experiment. Strain needs to decrease with increasing growth temperature to account for this difference, a hypothesis supported by TAXRD measurements                                                                                              |

| Figure 4.8  | Field threading dislocation density versus pile-up density for selected SiGe samples. Field threading dislocation density and pile-up density increase concomitantly                                                                                                                                                                                             |

| Figure 4.9  | Defect density versus Ge content for selected SiGe samples. Both field threading dislocation density and dislocation pile-up density increase beyond 30% Ge                                                                                                                                                                                                      |

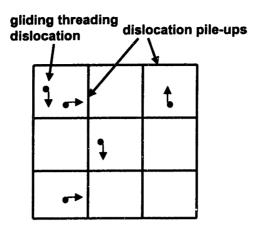

| Figure 4.10 | Plan-view of cellular structure emerging from dislocation pile-up formation. Dislocation pile-ups form boundaries that restrict gliding threading dislocation motion                                                                                                                                                                                             |

| Figure 4.11 | Etch-pit density photograph of a 60% Ge layer with a dislocation pile-up emerging from a particulate source                                                                                                                                                                                                                                                      |

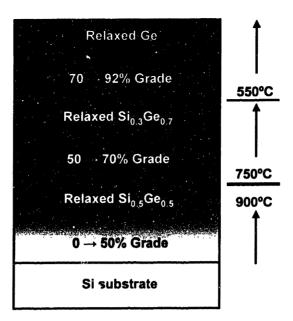

| Figure 4.12 | Optimized relaxed buffer sequence for Ge virtual substrates. Generally, layers are grown at the highest possible temperature. Maximum growth temperatures are limited mainly by gas-phase nucleation. The jump in composition between 92% Ge and Ge locks in compressive strain, which prevents cracking of the epilayer induced by thermal stress upon cooldown |

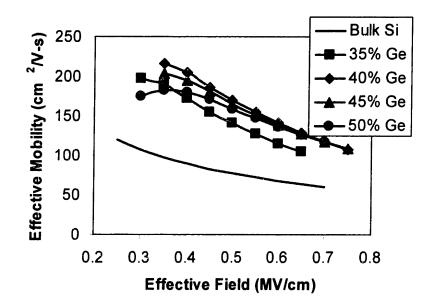

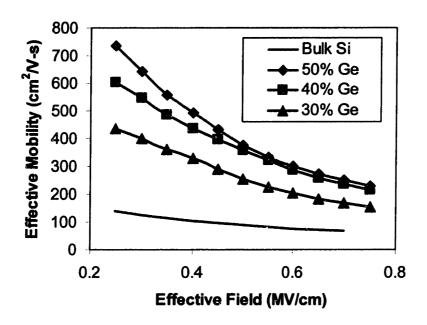

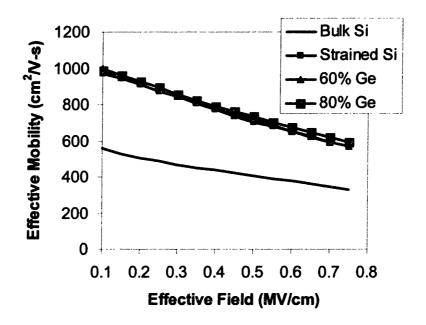

| Figure 5.1  | Effective hole mobility versus effective vertical field for strained Si p-MOSFETs grown on virtual substrate compositions between 35% Ge and 50% Ge. Low-field hole mobility increases between 35% Ge and 40% Ge, but falls slightly beyond this point                                                                                                           |

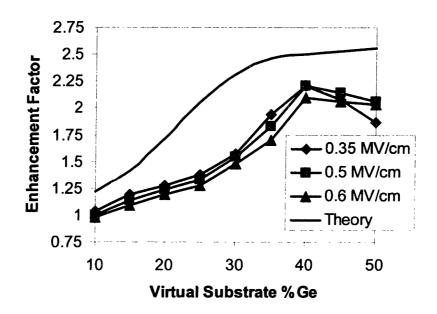

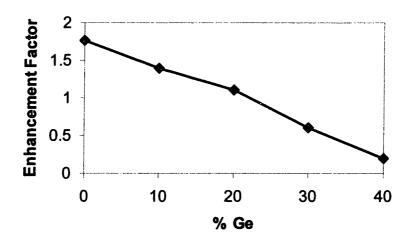

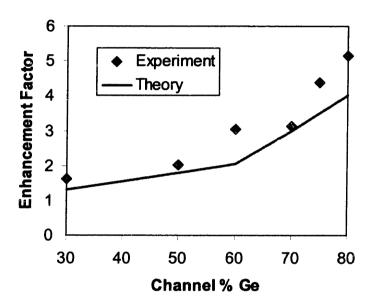

| Figure 5.2   | Hole mobility enhancement versus virtual substrate composition for strained Si p-MOSFETs, taken at the three vertical fields indicated Theoretical data is from Oberhuber et al. <sup>48</sup> while experimental data for virtual substrate compositions between 10% Ge and 30% Ge is from Currie et al. <sup>50</sup> The experimental data supports the theoretical conclusion that enhancements saturate at 40% Ge |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

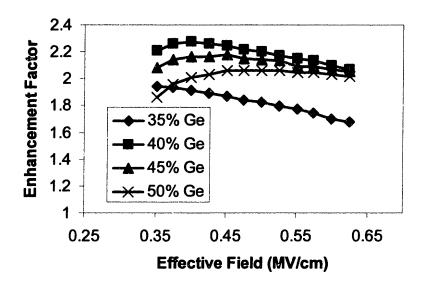

| Figure 5.3   | Hole mobility enhancement versus effective vertical field for strained Si per MOSFETs on different SiGe virtual substrate compositions. The rate of decrease of hole mobility enhancements with increasing effective field drops as strain increases                                                                                                                                                                   |

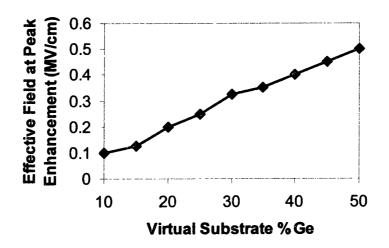

| Figure 5.4   | Vertical field at which peak hole mobility enhancement occurs in strained Si p-MOSFETs versus virtual substrate Ge composition. As strain increases, maximum enhancements occur at increasing vertical fields. Experimental data for virtual substrate compositions between 10% Ge and 30% Ge is from Currie et al. 50                                                                                                 |

| Figure 5.5   | Effective hole mobility versus effective vertical field for strained Si p-MOSFETs on 30% Ge virtual substrates with varying surface channel thicknesses                                                                                                                                                                                                                                                                |

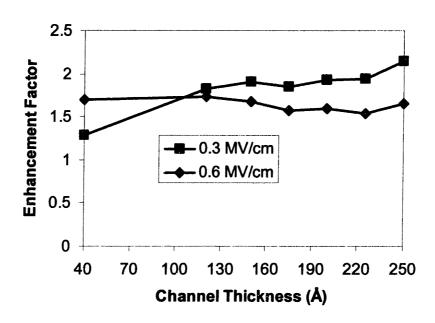

| Figure 5.6   | Hole mobility enhancement factor versus channel thickness in strained Si p-MOSFETs for two different effective vertical fields. At low vertical fields, thin channel exhibit the lowest hole mobility; however, hole mobility is independent of channel thickness at high vertical fields 119                                                                                                                          |

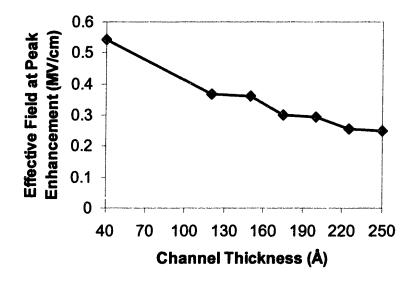

| Figure 5.7   | Effective vertical field at which hole peak mobility enhancement occurs in strained Si p-MOSFETs on 30% Ge virtual substrates versus channel thickness. As channel thickness increases, peak mobility enhancements occur at lower vertical fields                                                                                                                                                                      |

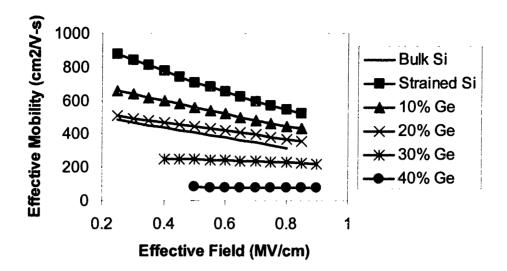

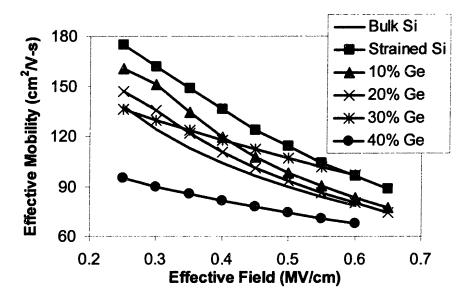

| Figure 5.8.  | Effective electron mobility versus effective vertical field for SiGe tensile strained alloy channel <i>n</i> -MOSFETs. Electron mobility drops sharply as alloy channel Ge composition increases                                                                                                                                                                                                                       |

| Figure 5.9.  | Effective electron mobility versus effective vertical field for SiGe tensile strained alloy channel $n$ -MOSFETs, presented on a logarithmic scale. The dependence of effective mobility on surface roughness scattering (labeled $\mu_{sr}$ ) and phonon/alloy scattering (labeled $\mu_{alloy/phonon}$ ) is also illustrated. 123                                                                                    |

| Figure 5.10. | Electron mobility enhancement factor measured at 0.5 MV/cm in SiGe tensile strained alloy channel <i>n</i> -MOSFETs versus channel alloy composition. Electron mobility enhancements drop sharply as Ge composition increases                                                                                                                                                                                          |

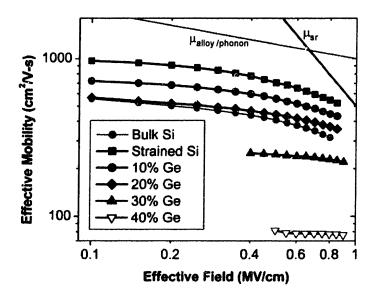

| Figure 5.11. | Effective hole mobility versus effective vertical field for SiGe tensile strained alloy channel p-MOSFETs. Low-field hole mobility drops slightly for all alloy compositions investigated compared to strained Si.                                                                                                                                                                                                     |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                        |

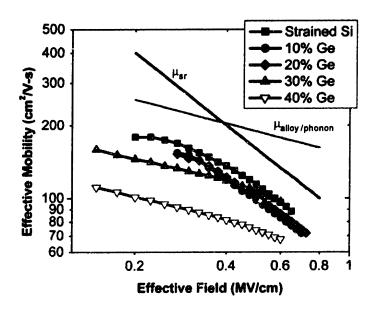

| Figure 5.12. | Effective hole mobility versus effective vertical field for SiGe tensile strained alloy channel $p$ -MOSFETs, presented on a logarithmic scale. The dependence of effective mobility on surface roughness scattering (labeled $\mu_{sr}$ ) and phonon/alloy scattering (labeled $\mu_{alloy/phonon}$ ) is also illustrated. 126                                                                                                                                                     |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 5.13. | Hole mobility enhancement factor (measured at 0.3 MV/cm) in SiGe tensile strained alloy channel p-MOSFETs versus channel composition. Hole mobility enhancements drop slightly for alloy channels up to 30% Ge, and sharply thereafter                                                                                                                                                                                                                                              |

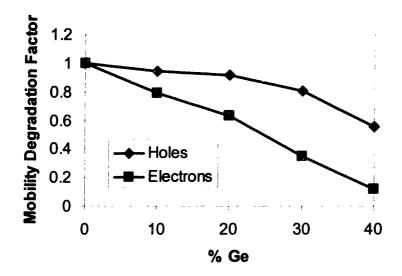

| Figure 5.14  | Comparison of electron and hole mobility degradation in SiGe tensile strained alloy channel MOSFETs (relative to strained Si) versus channel alloy composition. Mobilities were measured at 0.3 MV/cm (holes) and 0.5 MV/cm (electrons). Electron mobility is degraded much more severely by alloy scattering than hole mobility                                                                                                                                                    |

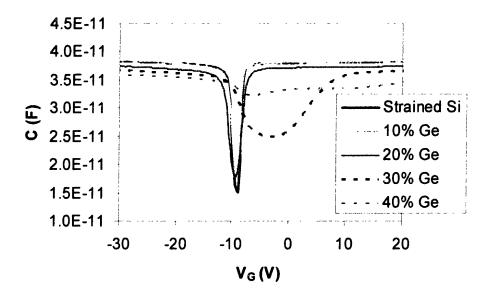

| Figure 5.15  | Capacitance-Voltage curves taken on alloy channel <i>n</i> -MOSFETs. The increasing full-width at half-maximum as channel composition increases results from increasing interface state density                                                                                                                                                                                                                                                                                     |

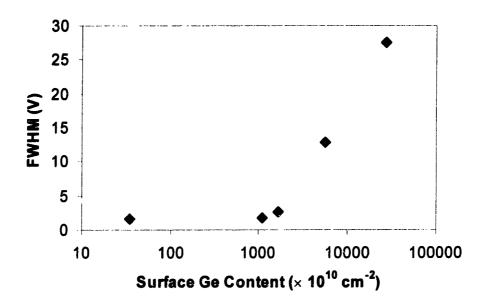

| Figure 5.16  | Full-width at half-maximum (FWHM) of Capacitance-Voltage curves for alloy channel <i>n</i> -MOSFETs versus surface concentration of Ge atoms in these heterostructures. FWHM increases rapidly beyond roughly 10 <sup>13</sup> Ge atoms cm <sup>-2</sup> , indicating that this concentration is sufficient to degrade interface state density                                                                                                                                      |

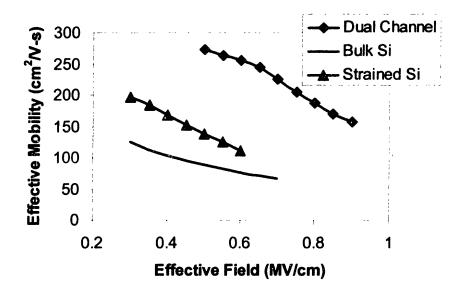

| Figure 5.17  | Effective hole mobility versus effective vertical field for two different dual channel heterostructures grown on 30% Ge virtual substrates. A control strained Si p-MOSFET is also shown. The heterostructure with the 60% Ge buried channel displays significant hole mobility enhancement over strained Si over the entire field range investigated                                                                                                                               |

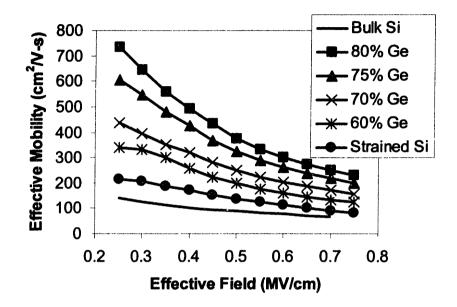

| Figure 6.1   | Effective hole mobility versus effective vertical field for dual channel heterostructures under constant strain $(y - x = 30\% \text{ Ge})$ compared to a strained Si p-MOSFET. All channel thicknesses in dual channel heterostructures are 85 Å. Hole mobility in dual channel heterostructures increases with buried channel Ge composition                                                                                                                                      |

| Figure 6.2   | Hole mobility enhancement factors over bulk Si (taken at vertical fields of 0.3 MV/cm) for different strained $Si_{1-y}Ge_y$ channel compositions. All channels except the 50% Ge point were grown on relaxed virtual substrates such that $y - x = 0.3$ ; the 50% Ge point was grown on a 30% Ge relaxed virtual substrate. The 30% Ge point was taken from Bouillon <i>et al.</i> Hole mobility enhancements are large even where alloy scattering is expected to be most severe. |

| Figure 6.3   | Effective hole mobility versus effective vertical field for dual channel heterostructures with 80% Ge buried channels on various composition $Si_1$ . $_xGe_x$ virtual substrates. Buried channel thickness is inversely proportional to strain. Hole mobility decreases as strain increases, indicating that                                                                                                                                                                       |

|            | channel thickness plays a more important role than strain in determining hole mobility enhancements in dual channel heterostructures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

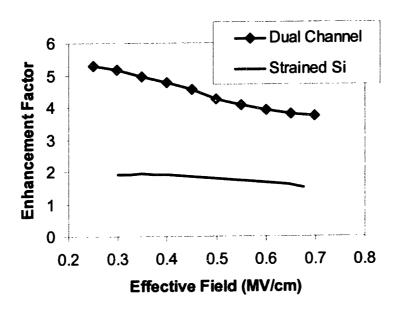

| Figure 6.4 | Hole mobility enhancement over bulk Si versus effective vertical field for a dual channel heterostructure featuring an 80% Ge buried channel on a relaxed 50% Ge virtual substrate. A strained Si p-MOSFET is also shown for comparison. Hole mobility enhancements in the dual channel heterostructure are above 3.65 over the entire effective field range 142                                                                                                                                                                                                                                                                                                                                            |

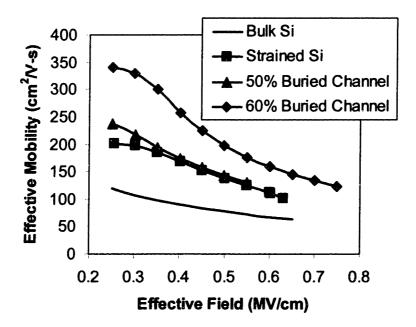

| Figure 6.5 | Effective electron mobility versus effective vertical field for two dual channel heterostructures and to strained Si. Electron mobility in dual channel heterostructures is identical to that of strained Si                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

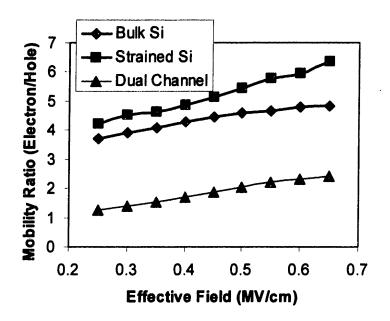

| Figure 6.6 | Ratio of electron mobility to hole mobility in the dual channel heterostructure shown in Figure 6.4 compared to both bulk Si and strained Si. In bulk Si, carrier mobilities are low and highly asymmetric. In strained Si, carrier mobilities are enhanced, but are still asymmetric. In dual channel heterostructures, carrier mobilities are nearly symmetric and both are enhanced relative to bulk Si                                                                                                                                                                                                                                                                                                  |

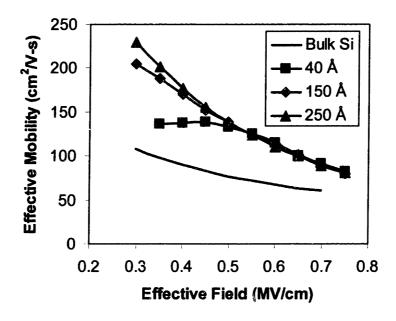

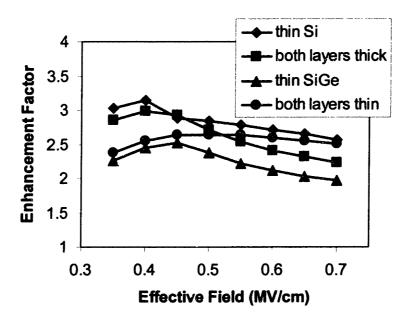

| Figure 6.7 | Hole mobility enhancement factors versus effective vertical field for different channel thicknesses in dual channel Si/Si <sub>0.4</sub> Ge <sub>0.6</sub> heterostructures on relaxed Si <sub>0.7</sub> Ge <sub>0.3</sub> virtual substrates. Thin channels are 40 Å while thick channels are 85 Å. Hole mobility enhancements are maintained at high vertical fields by minimizing the strained Si surface channel thickness. 145                                                                                                                                                                                                                                                                         |

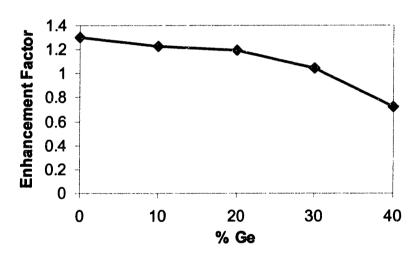

| Figure 7.1 | Electron and hole mobility enhancements in strained Si surface channel MOSFETs, taken at vertical fields of 0.6 MV/cm. Electron mobility enhancements saturate at 20% Ge, while hole mobility enhancements saturate at 40% Ge. Symmetric enhancements are obtained for strained Si MOSFETs on Si <sub>0.65</sub> Ge <sub>0.35</sub> virtual substrates. Experimental data for strained Si <i>n</i> -MOSFETs and <i>p</i> -MOSFETs between 10% Ge and 30% Ge was obtained from Currie <i>et al.</i> <sup>50</sup> Electron mobility enhancements in strained Si <i>n</i> -MOSFETs on Si <sub>0.5</sub> Ge <sub>0.5</sub> virtual substrates were obtained from measurements on dual channel heterostructures |

| Figure 7.2 | Cross section TEM image of a dual channel heterostructure incorporating a buried strained Ge channel and a strained Si surface channel on a relaxed 50% Ge virtual substrate. The buried Ge layer is extremely thin and has undulated severely.                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Figure 7.3 | Effective hole mobility versus effective vertical field for a dual channel heterostructure consisting of a buried undulated Ge channel and a strained Si surface channel on a relaxed 50% Ge virtual substrate, compared to strained Si and bulk Si p-MOSFETs. Despite having a very thin, undulated strained Ge layer, hole mobility in this dual channel heterostructure is still significantly higher than in strained Si                                                                                                                                                                                                                                                                                |

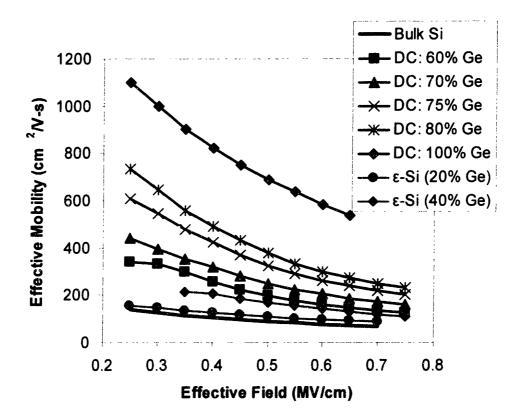

| Figure 7.4 | Comparison of effective hole mobility versus effective vertical field for strained Si (denoted ε-Si) and dual channel heterostructure (denoted DC; buried channel composition has been indicated) MOSFETs. Each curve                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# **List of Tables**

| Table 1.1 | Active slip systems for SiGe/Si(001) heteroepitaxy                                                                                                                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2.1 | Average electron and hole mobilities of common semiconductor materials.                                                                                                                                                       |

| Table 3.1 | Relevant dimensions of MOSFETs characterized in this work                                                                                                                                                                     |

| Table 5.1 | Concentration of Ge atoms at the surface of as-grown and processed alloy channel <i>n</i> -MOSFET heterostructures. In both cases, Ge concentration at the sample surface increases with increasing alloy channel content 130 |

### **Acknowledgements**

Wow, this part is fun. It's not just that graduate school, and its numerous frustrations, is nearly complete (though that helps). Anyone who knows me understands that I found graduate school immensely difficult at times. So I can only hope that I've been as good a friend and colleague to the people listed here as they've been to me, since I wouldn't be here without them.

Working for Gene Fitzgerald has been a privilege. Any success I've encountered in my work is in great part attributable to his incredible vision and dedication. I have enjoyed working with Gene and I valued the supportive environment that he fosters in his research group. I greatly appreciated having the independence to shape my own research project, which required a lot of trust on his part, and I've been fortunate to work for an advisor who truly cares about his students. I've constantly been inspired by his boundless enthusiasm towards technology, and the scary thing is that I'm starting to believe that he's been right all along. His dedication towards putting his group's work in a greater context has been an inspiration for me. I'll always be able to look back and reflect on how fortunate I was to have such a wonderful mentor in Gene.

Professor Dimitri Antoniadis has been a valued collaborator and has provided helpful advice throughout my time at MIT. I've enjoyed our numerous discussions, and the work in this thesis has benefited greatly from his input. Like Gene, Dimitri has also been an inspiring person to work with, and I'll never forget his selfless campaigning for me as I sought employment. As a collaborator, Dimitri consistently went out of his way to help me, and I consider myself fortunate to interact with such a great person and distinguished engineer.

I would also like to thank Professor Sam Allen for his input in shaping this thesis. I especially appreciate how he agreed to join my thesis committee on short notice and how he went out of his way to attend my final thesis defense under trying circumstances.

When I finally start working and assume the role of ex-student, I can only hope to enjoy the presence of my co-workers as much as I've enjoyed hanging around the various members of the Fitzgerald group. I have been consistently amazed at the intelligence, dedication, and enthusiasm of the group overall. But, even better, they also happen to be a great bunch of people with whom I was able to do research. The Fitzgerald group has really been more of a family than a group of colleagues, and I'll always look back fondly at the various personalities that I've encountered.

Arthur Pitera made my graduate career much easier and a heck of a lot more fun than it otherwise would have been. He's extraordinarily talented and has an amazing intuitive ability to fix anything. I really enjoyed working side-by-side with him on the UHVCVD. It's a poorly kept secret that Arthur is one of the most talented and valuable members of our lab group, even if he'd never admit it. Remember Arthur, we're all rooting for you. Hanging around with Arthur is always a lot of fun, even if he never wants to get coffee with me (MFP!) and can never tell me where the brown boats in TRL are. Arthur's been such a great friend to me—I already miss having him as a neighbor, and I'll really miss working with him.

Matt Currie has been a great collaborator and friend throughout the years. I was lucky enough to work side-by-side with him for years, and similarly fortunate to be able to continue his work. Matt paved the way for much of this research, and he was always

there to lend a helping hand and to help design experiments. At times, Matt was almost a co-advisor, and without him my work would not have progressed to the extent it has. Besides that, he's a great guy to hang around with, and I'll always appreciate his sense of humor and personality. He was always there to keep my difficulties in perspective and to make sure I was never taking myself too seriously.

Tom Langdo has also been a patient mentor and great friend. I owe nearly all my knowledge of vacuum systems and CVD to his guidance. More importantly, Tom gave me the confidence to try something, even if I failed miserably, a valuable approach in our lab. Tom also selflessly devoted himself to helping others in the group, including me on several occasions. I enjoyed lifting weights and generally hanging around with him (as well as expanding my vocabulary), and conferences without him would have never been so fun and...interesting.

I've benefited greatly from working with Larry Lee. I've really come to appreciate his many talents, be they in research or music. I owe much of Chapter 6 of this thesis to his dedication to understanding low-temperature growth in our CVD system and help in material characterization, for which I am very grateful. I really enjoyed our many discussions about research, music, or whatever we had in mind, and I discovered some great new music along the way.

Mayank Bulsara has been a great mentor and co-worker. If Mayank weren't such a cool person to work with, I may have never come to MIT in the first place. I witnessed Mayank's evolution from a graduate student to a successful entrepreneur, and I've been inspired by his constant growth. Someday, I'll look really cool when I mention that I knew him back in the day. Having talented people like Mayank around is what makes MIT a special place. Mayank is a hilarious guy, and I really like hanging around with him, even if he roots for all the wrong teams.

Gianni Taraschi was a great person to discuss research with; I've often been awed by his intelligence and understanding of science. He's a cool guy and always took the Canada jokes in stride.

I have immensely appreciated Charles Cheng's understanding of device physics and his willingness to take the time to help me. I always wonder how he manages to get so much work done. I've also enjoyed our many discussions about engineering and life in general.

Steve Ting was a good friend and a great person to have in the research group. I'll always be thankful that Steve took the time to talk to me when I was a first-year student here; without his kind words and sage advice, I may have jumped ship a long time ago.

Mike Groenert's presence really helped make the Fitzgerald group a fun place to work. We all were genuinely pleased when he finally had the success he deserved, a testament to how much we all like and respect him. Mike took his setbacks so well that I often felt guilty for thinking that I had it rough. I also enjoyed his affinity for fun and mischief.

We always knew the real Vicky Yang was lurking behind that quiet exterior. I've always admired how Vicky handles the stress of graduate school with grace and manages to keep difficulties in perspective. I also enjoyed hanging around with her, and I'm glad she's so tolerant of our noise and general mayhem.

I would like to thank Lisa McGill for taking the time to proofread my entire thesis. Her suggestions helped improve this document immensely. I also admire how she's been able to handle x-ray downtime and other um...impositions extremely well.

Andy Kim was a big influence in much of my early work and an extremely talented scientist. I'm glad I was able to bounce ideas off of him and that he took the time to shape much of the research in Chapter 4.

To Nate Quitoriano, we all wish you luck as heir to an entire lab. I'm sure with your intelligence and good humor that you'll do fine.

Similarly, all the best to Nava Ariel—she's got a tough job forging a path entirely her own, but she's definitely up to the task.

I'm grateful that Jessica Lai and Elissa Robbins were able to lend their assistance in the tedious task of EPD. They both helped me immensely along the way, and I wish them both the best.

Finally, I'm glad Anabela Afonso has been around to keep me in line and has tolerated our group's misbehavior. I really appreciated her help and patience throughout the years.

I admire everyone who works at MTL, since their job often seems an impossible and thankless task. In particular, I would like to thank Vicky Diadiuk for her support and good humor. MTL is lucky to have someone with her dedication and skills. Kurt Broderick, Paul Tierney, and Dan Adams were also particularly helpful and good-natured in the face of my occasional incompetence. I would also like to extend my gratitude to Bernard Alamariu, Jim Bishop, Gwen Donahue, Joe Walsh, Paudely Zamora, Paul McGrath, and Ron Stoute for their help at various times.

From my Penn State days, Darrell Schlom has been a great friend and mentor. I've always been inspired by his dedication to research and I'm glad that we've kept in touch through the years. Going back even further, I'm glad Raquel Almeida has always been a good friend of mine.

I can't really say enough good things about Rebecca Jacobstein, but here's a start. Through it all, she's been my biggest fan and a source of constant love and support. Rebecca has also been my best friend and an invisible co-author on everything I've written here. I never would have made it through grad school without her, and she always made the most trying of circumstances enjoyable. I really miss having her around; she would always patiently listen to my endless complaints about work and help me keep things in perspective. Her dedication to her work and her incredible intelligence have always been an inspiration to me. It's painfully obvious that life just wouldn't be nearly as fun without her, and I can hardly believe that I deserve someone as great as she is. This document is at least as much a testament to her dedication as it is to mine. To Rebecca: we finally made it. Thank you. I would also like to thank Jake and Nancy—the "in-laws"—for their support and friendship.

Finally, I've been blessed by a wonderful family. My parents are a constant source of inspiration and are my role models and my heroes. My mother and father have always lent their love and support, and they've stood behind me no matter which path I chose. I'll never be able to repay their devotion to my well-being and happiness (though I hope that chemistry set they bought me when I was five was worth it) but I'll always try to make them proud. Their selfless dedication to their children is incredible. Similarly, my brothers Tom, Sean, and Pat have always been supportive and tolerant of my general

weirdness. I was especially happy to take the vacation out west that Tom and I had talked about since college. Finally, I would like to thank my entire family for their constant encouragement through the years.

# **Chapter 1.** Introduction and Background

### 1.1. Motivation

The rapid increase in silicon-based CMOS speed and functionality, and the concomitant drop in cost per device over the past several decades, has been the result of aggressive scaling of chip components to ever smaller dimensions. This scaling results in improved metal-oxide-semiconductor field-effect transistor (MOSFET) performance and increased integration density and functionality. Consequently, this has allowed complementary MOSFET (CMOS) manufacturing to reach such economies of scale that there are now over 60 million transistors for every person on earth. However, through a convergence of various physical and economic factors, device scaling will eventually halt, putting an end to the incredible pace of CMOS performance advancements. As scaling approaches its inevitable end, interest in alternate high performance materials and technologies is intensifying. One approach to overcoming the limits of device scaling is to replace silicon microelectronics with a completely different technology. Another approach is to increase the performance and functionality of the silicon platform through integration of new materials onto Si substrates, while retaining compatibility with mainstream silicon device fabrication modules. Since the former approach is far less technologically mature than mainstream Si technology, and since there is immense economic pressure to utilize the existing multi-billion dollar Si fab infrastructure, for the foreseeable future the traditional Si scaling roadmap will be extended by integrating new high performance materials on the Si platform.

Before discussing the advantages over Si of alternate materials, it is important to emphasize the reasons for the ascension of Si to its current dominant status in the microelectronics industry. The importance of silicon's high quality native oxide (which

enables high quality MOS gate formation) and mechanical stability (which enables growth of large area substrates) cannot be overstated—without these attributes, modern microelectronics as we know it would not exist. However, Si has some inherently poor material properties that limit its device applications. First and foremost, Si has an indirect bandgap, which precludes efficient light emission. When compared to other common semiconductors, Si also has relatively low carrier mobilities, which is one factor which limits MOSFET speed. Similarly, hole mobility in bulk Si is over two times lower than electron mobility, which forces circuit designers to make *p*-MOSFETs larger than *n*-MOSFETs to obtain the same current drive. This takes up valuable chip real estate and decreases overall circuit speed. Integrating other semiconductor materials onto Si substrates offers the promise of overcoming these limitations while maintaining the inherent economic advantages of the Si platform.

There are two approaches to integration of dissimilar materials on the Si platform: hybrid and monolithic integration. These approaches are illustrated schematically in Figure 1.1 below.

Figure 1.1 Schematic of hybrid versus monolithic integration techniques. The hybrid scheme (pictured on the left) involves integration of single components while the monolithic scheme (pictured on the right) utilizes film growth and/or wafer bonding and patterning to enable very-large-scale integration of dissimilar materials onto a common substrate.

The hybrid approach generally involves bonding or soldering of discrete components onto Si chips, while the monolithic approach involves integration of dissimilar materials onto the wafer surface through either wafer bonding or thin film deposition. Since hybrid

integration involves picking and placing of individual components, it is inherently more costly and less reliable than monolithic integration. Furthermore, in practice hybrid integration is impossible for very large scale integrated (VLSI) systems, since the sheer number of discrete components is overwhelming. In contrast, monolithically integrated films are by definition self-aligned and compatible with standard VLSI processing techniques.

Figure 1.2 illustrates lattice constant versus bandgap for common semiconductor materials. Of particular interest for this work are the SiGe and AlGaAs alloys.

Figure 1.2 Bandgap versus lattice constant for common semiconductor materials.

Figure adapted from Mayer and Lau.<sup>2</sup>

As will be described below, the main barrier to monolithic integration of these materials on Si is the large lattice mismatch between the device material and the Si substrate.

### 1.2. The Relaxed SiGe Integration Platform

The silicon-germanium (SiGe) materials system possesses several attractive properties that make it a natural choice for extending the performance of the Si microelectronics platform.<sup>3,4</sup> High mobility strained Si and SiGe layers offer the potential for greatly increased MOSFET performance over bulk Si at the same gate length, while maintaining compatibility with mainstream CMOS processing. Ge-rich alloys are nearly lattice-matched to GaAs and AlAs, enabling integration of high quality III-V light emitting devices with SiGe-based CMOS. SiGe layers display excellent etch-stop properties,<sup>5,6</sup> making them attractive for microelectromechanical systems (MEMS) fabrication. Moreover, as the binary phase diagram in Figure 1.3 indicates, silicon and germanium are completely miscible over the entire composition range.

Figure 1.3 The Si-Ge Binary Phase Diagram, adapted from Gandhi. Si and Ge are completely miscible, enabling SiGe films of arbitrary composition to be grown without phase segregation.

While this makes bulk growth of compositionally uniform SiGe crystals difficult, it does mean that SiGe films grown on Si are immune to phase segregation. Finally, through the compositional grading technique discussed below, high quality SiGe layers of any composition can be grown upon Si substrates.

### 1.3. Lattice Mismatch and Critical Thickness

Accessing the improved functionality offered by silicon-germanium alloys requires relaxed films with a low defect density. However, because of the lattice mismatch between silicon (a = 5.431 Å) and germanium (a = 5.658 Å), direct deposition of SiGe onto a silicon substrate will not fulfill these requirements simultaneously. At small film thickness, the energy required for dislocations to be present and relieve mismatch strain is less than the strain energy accumulated in the film. As a result, the SiGe layer grows pseudomorphically, with an in-plane lattice constant equal to that of the Si substrate. At large film thickness, the strain energy in the film exceeds the energy necessary for dislocations to be present, leading to dislocation formation. This situation is depicted in Figure 1.4 below.

Figure 1.4 Schematic of pseudmorphic growth and the onset of dislocation formation in lattice-mismatched heteroepitaxy. Initially, the in-plane film lattice constant is constrained to that of the substrate, as shown on the left. Above a critical thickness, dislocation formation becomes energetically favorable and the film relaxes, as shown on the right.

The thickness at which it becomes thermodynamically favorable to nucleate misfit dislocations is termed the critical thickness. It is an *equilibrium* parameter; metastable structures that are dislocation-free well past the critical thickness can be grown at reduced temperatures (where dislocation nucleation is kinetically suppressed). The equilibrium critical thickness,  $h_c$ , for a lattice-mismatched layer is given by

$$h_c = \frac{D(1 - v \cos^2 \alpha)(b/b_{eff}) \left[ \ln \left( \frac{h_c}{b} \right) + 1 \right]}{2Yf}$$

where D is the average shear modulus at the interface,  $\nu$  is Poisson's ratio,  $\alpha$  is the angle between the dislocation line direction and Burgers vector b,  $b_{eff}$  is the interfacial component of the Burgers vector, h is the film thickness, Y is the Young's modulus of the film, and f is the mismatch between film and substrate. f

The lattice constant of a relaxed SiGe layer is given very nearly by Vegard's Law<sup>11,12</sup>

$$a_{SiGe} = a_{Si}(1-x) + a_{Ge}(x)$$

for a given Ge atomic fraction (x). The lattice constants for Si and Ge are 5.431 Å and 5.658 Å, respectively. By interpolating elastic constants, calculating mismatch for  $Si_{1-x}Ge_x$  layers grown on Si substrates, and assuming  $b_{eff} = \frac{a}{2}$  (discussed below), the equilibrium critical thickness for  $Si_{1-x}Ge_x$  layers grown on Si can be computed, as given in Figure 1.5 below. Note that for large Ge content (>15% Ge) the equilibrium critical thickness is on the order of only hundreds of angstroms (Å).

Figure 1.5 Critical thickness  $(h_c)$  of  $Si_{1-x}Ge_x$  alloys on Si (001) versus Ge content (x). Critical thickness drops rapidly with increasing lattice mismatch.

The exact mechanisms of dislocation nucleation are not well understood. 10

Theoretical calculations indicate that there is a large barrier to homogeneous dislocation nucleation, so the dominant dislocation nucleation paths in lattice-mismatched epitaxy are likely heterogeneous. A detailed discussion of possible dislocation nucleation mechanisms in mismatched epitaxy has been presented by Fitzgerald.<sup>10</sup>

In lattice-mismatched epitaxial systems, dislocations that glide along the heterointerface to relieve mismatch strain are termed misfit dislocations. However, since these dislocations cannot terminate in the crystal and must glide long distances to reach the wafer edge, they eventually bend upward and thread their way through the film to reach the film surface. These threading dislocations are in general deleterious for device applications; they scatter carriers, serve as non-radiative recombination centers in direct bandgap semiconductors, and are fast diffusion paths for dopants. Direct deposition of relaxed, highly lattice-mismatched layers (e.g. Ge on Si) results in large threading

dislocation densities ( $\sim 10^9$  -  $10^{11}$  cm<sup>-2</sup>) at the film surface that are too high for most practical applications.

## 1.4. Active Slip Systems in SiGe/Si Heteroepitaxy

The glissile slip system in diamond cubic semiconductors, such as Si, is {111}<10>, and a total of 24 unique slip systems (12 unique <110> Burgers vectors times 2 unique {111} planes per Burgers vector) are possible. However, for SiGe/Si(001) heteroepitaxy, not all of these slip systems will be active. For eight of these slip systems, Burgers vector and line direction are parallel, resulting in pure screw dislocations and no strain relief. Of the remaining 16 slip systems, only eight relieve compressive strain. These eight active slip systems are detailed in Table 1.1 below.

Table 1.1 Active slip systems for SiGe/Si(001) heteroepitaxy.

| Glide Plane | Burgers Vector |

|-------------|----------------|

| (111)       | ½a[101]        |

| (111)       | ½a [101]       |

| (111)       | ½a [101]       |

| (111)       | ½a [011]       |

| (111)       | ½a [101]       |

| (111)       | ½a [011]       |

| (111)       | ½a [101]       |

| (111)       | ½a [011]       |

When SiGe layers are deposited on Si substrates offcut from (001), the imbalance in resolved shear stress on active slip systems causes an imbalance in Burgers vector populations. This effect has implications on dislocation reduction reactions, discussed further in Section 4.2.2.

# 1.5. Comparing Dislocation Morphology in Lowand High-Mismatch Systems

In low-mismatch SiGe layers grown on Si(001), the majority of dislocations that nucleate are of the  $60^{\circ}$  variety (so named because of the angle between Burgers vector and line direction) with an in-plane Burgers vector ( $b_{eff}$ ) equal to  $\frac{a}{2}$ . These are mixed dislocations, with edge, screw, and tilt (*i.e.*, a misfit dislocation whose Burgers vector is parallel to the growth direction) components, and they can glide on  $\{111\}$  planes. However, non-edge components of  $60^{\circ}$  dislocations are in essence wasted, since they do not contribute to strain relief. In contrast, in highly mismatched SiGe layers, the majority of dislocations that nucleate are sessile ( $90^{\circ}$ ) pure edge dislocations.