# Making Handheld Devices Smaller: A Boost Converter that Uses Minimum Board Space

by

John G. Tilly

Submitted to the Department of Electrical Engineering and Computer Science

in partial fulfillment of the requirements for the degree of

Master of Engineering in Electrical Engineering and computer Science at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

May 2001 [June 2007]

© John G. Tilly, MMI. All rights reserved.

BARKER The author hereby grants to MIT permission to reproduce and distribute publicly paper and electronic copies of this thesis Magatimeters INSTITUTE OF TECHNOLOGY in whole or in part. JUL 11 2001 LIBRARIES Author..... Department of Electrical Engineering and Computer Science May 26, 2001 LTC Reader **Steve Pietkiewicz** 6-A Company Advisor Certified by... ...... ~ **Charles Sodini** Thesis Supervisor Accepted by Arthur C. Smith Chairman, Department Committee on Graduate Students

# Making Handheld Devices Smaller: A Boost Converter that Uses Minimum Board Space

by

John G. Tilly

Submitted to the Department of Electrical Engineering and Computer Science on May 26, 2001, in partial fulfillment of the requirements for the degree of Master of Engineering in Electrical Engineering and Computer Science

# Abstract

A method to decrease the board space of a boosting switching regulator is to increase the switching frequency. Specifications for a monolithic switching regulator operating at a nominal 10MHz switching frequency are described. The application circuit demonstrates efficiencies approaching 75%, operates with up to 200mA of switch current, and switches with current slew rates of 150mA per nanosecond. The high frequency of operation leads to some interesting test and measurement problems. In particular, measurement of the rise and fall times of the switch current requires custom board construction. Further increases in the switching speed lead to diminishing returns in board space.

Thesis Supervisor: Charles Sodini

# **Table of Contents**

| 1      | Introduction                        | 7  |

|--------|-------------------------------------|----|

| 1.1    | Handheld Devices                    | 7  |

| 1.2    | New Arrivals                        | 7  |

| 1.3    | About this Thesis                   | 8  |

| 1.4    | A Brief History of DC/DC conversion | 9  |

| 2      | Context                             | 11 |

| 2.1    | Scope                               | 11 |

| 2.2    | Approach                            |    |

| 2.3    | Prior Work                          | 14 |

| 2.4    | System and Specifications           | 16 |

| 2.4.1  | Brokaw Cell                         | 20 |

| 2.4.2  | Error Amplifier and Compensation    | 21 |

| 2.4.3  | Ramp Generator                      | 23 |

| 2.4.4  | Oscillator                          | 24 |

| 2.4.5  | SR Flip Flop                        | 25 |

| 2.4.6  | Driver                              | 25 |

| 2.4.7  | Switch                              | 25 |

| 2.4.8  | Current Sense Amplifier             | 25 |

| 2.4.9  | Shutdown                            | 26 |

| 2.4.10 | Current Limit                       | 26 |

| 3      | Design and Simulation               | 26 |

| 4      | The Switch and Driver Circuitry     | 31 |

| 4.1    | Transistor Modeling                 | 31 |

| 4.2    | Design Choices                      | 32 |

| 4.2.1 | Switch Size                                                  |

|-------|--------------------------------------------------------------|

| 4.2.2 | Quiescent Current                                            |

| 4.2.3 | Forcing Beta Current                                         |

| 4.2.4 | Dynamic Dissipation                                          |

| 4.2.5 | Modeling of External Components41                            |

| 5     | Testing                                                      |

| 5.1   | Measurement Techniques for High Frequency DC/DC converters43 |

| 5.1.1 | Switch Current                                               |

| 5.1.2 | Output Noise                                                 |

| 5.2   | Performance in the Application Circuits                      |

| 5.2.1 | Efficiency                                                   |

| 5.2.2 | Load Transient                                               |

| 5.3   | Specifications                                               |

| 5.4   | Speed Limits                                                 |

| 6     | Conclusion                                                   |

| 6.1   | Contributions                                                |

| 6.2   | Future Work                                                  |

| 6.3   | Acknowledgements                                             |

| Works | Cited                                                        |

| Appen | dix A69                                                      |

| Appen | dix B74                                                      |

# List of Figures

| 1-1:  | Synchronous Vibrating Power Supply                      | .10 |

|-------|---------------------------------------------------------|-----|

| 2-1:  | Typical Application for the Monolithic Boost Controller | .16 |

| 2-2:  | Block Diagram of the Monolithic Boost Controller        | .17 |

| 2-3:  | Linearized Model of the Brokaw Cell                     | .20 |

| 2-4:  | Linearized Model of the Error Amplifier                 | .21 |

| 2-5:  | Perturbation with Slope Compensation                    | .23 |

| 2-6:  | Perturbation without Slope Compensation                 | .24 |

| 3-1:  | Linearized Model of a Current Mode Boost Converter      | .29 |

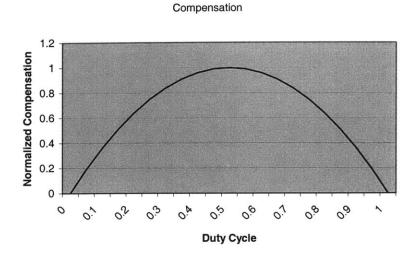

| 3-2:  | Theoretical Slope Compensation Curve                    | .30 |

| 4-1:  | Simplified Circuit Diagram of the Switch Driver         | .32 |

| 4-2:  | Equivalent Circuit Models of Energy Storage Elements    | .42 |

| 5-1:  | Die Photograph of the Integrated Circuit                | .43 |

| 5-2:  | Switch Current Measurement Board                        | .46 |

| 5-3:  | Switch Current Waveform                                 | .47 |

| 5-4:  | Switch Current Risetime                                 | .48 |

| 5-5:  | Switch Current Falltime                                 | .49 |

| 5-6:  | Filtered and Unfiltered Output Noise                    | .50 |

| 5-7:  | 3.3V to 5V Efficiency Curve                             | 51  |

| 5-8:  | 3.3V to 12V Efficiency Curve                            | .52 |

| 5-9:  | 5V to 12V Efficiency Curve                              | .52 |

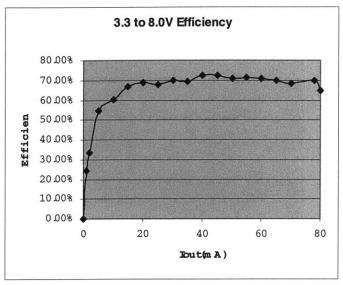

| 5-10: | 3.3V to 8V Efficiency Curve                             | 53  |

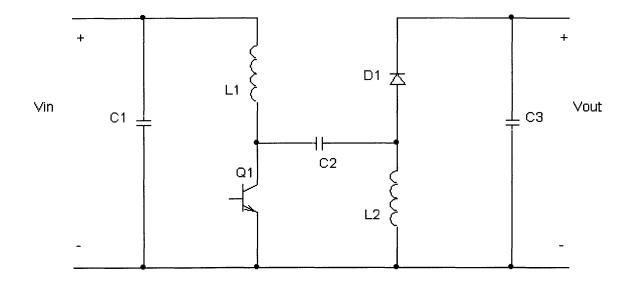

| 5-11: | Circuit Diagram of a SEPIC Converter                    | 54  |

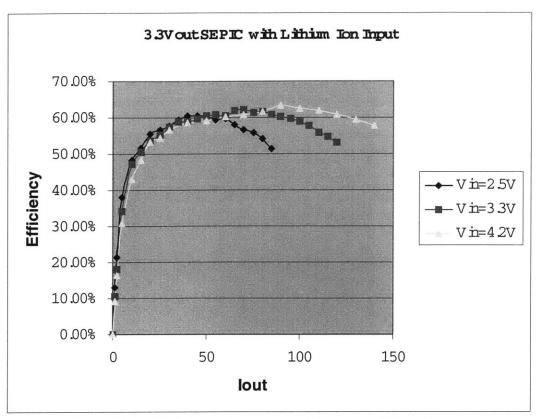

| 5-12: | Efficiency Curves for a 3.3V Output SEPIC Converter     | 55  |

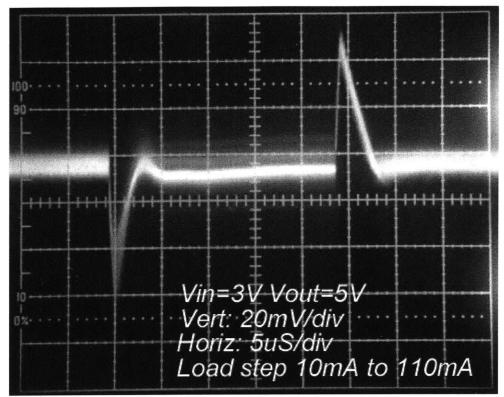

| 5-13: | Load Step Transient                                     | 56  |

|       |                                                         |     |

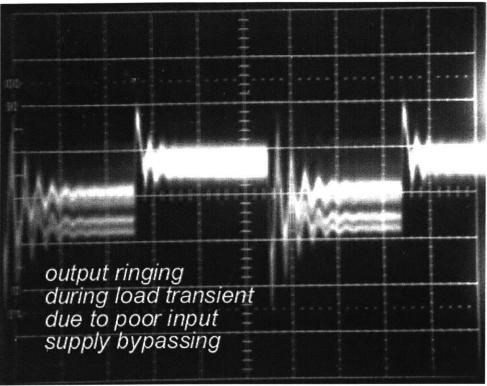

| 5-14: | Poorly Bypassed Load Step Transient                                   | 57 |

|-------|-----------------------------------------------------------------------|----|

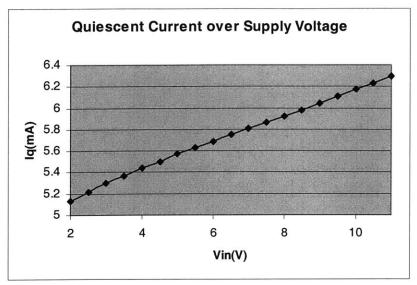

| 5-15: | Quiescent Current over Supply Voltage                                 | 58 |

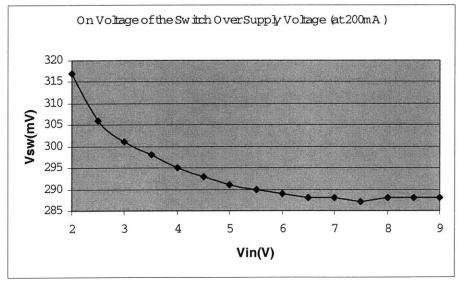

| 5-16: | On Voltage of the Switch over Supply Voltage                          | 58 |

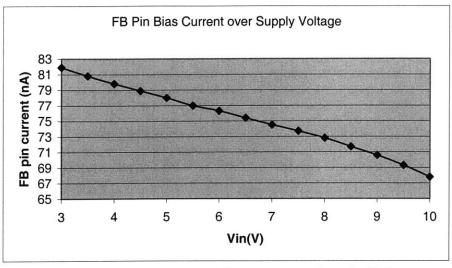

| 5-17: | FB Pin Bias Current over Supply Voltage                               | 59 |

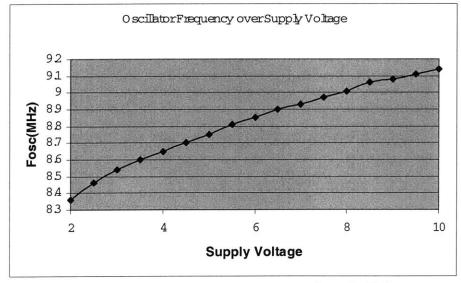

| 5-18: | Oscillator Frequency over Supply Voltage                              | 59 |

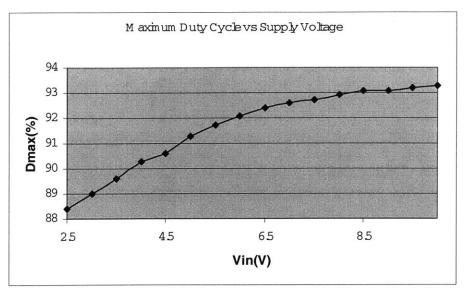

| 5-19: | Maximum Duty Cycle over Supply Voltage                                | 50 |

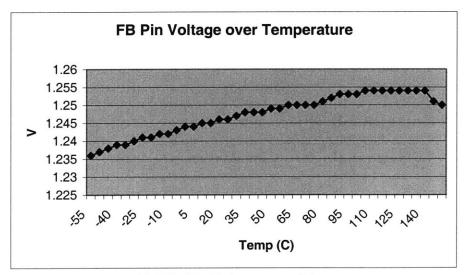

| 5-20: | FB pin Voltage over Temperature                                       | 50 |

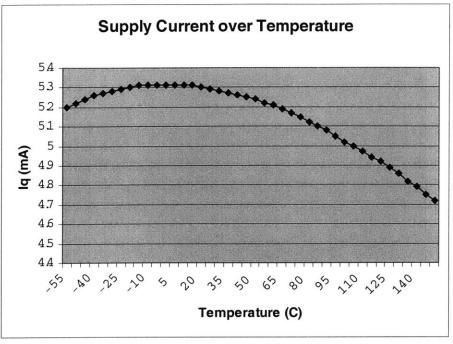

| 5-21: | Supply Current over Temperature                                       | 51 |

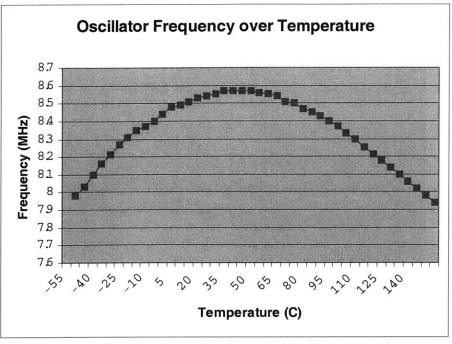

| 5-22: | Oscillator Frequency over Temperature                                 | 52 |

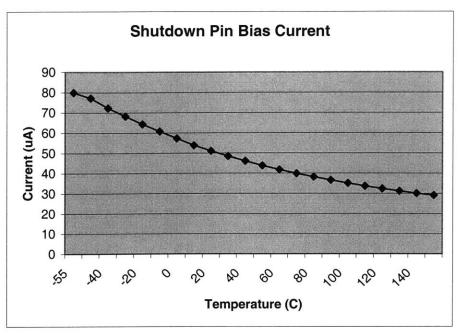

| 5-23: | Shutdown Pin Bias Current over Temperature                            | 53 |

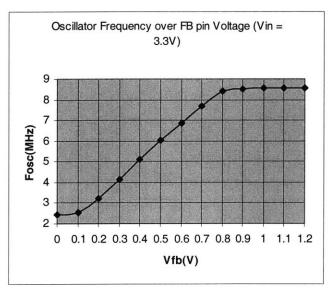

| 5-24: | Oscillator Frequency over FB Pin Voltage                              | 53 |

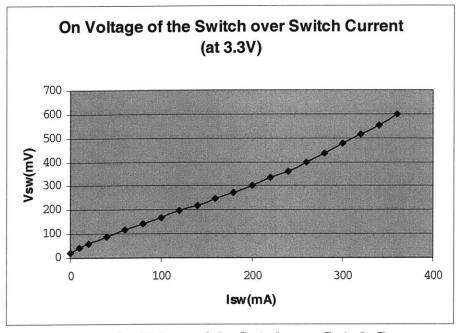

| 5-25: | On Voltage of the Switch over Switch Current                          | 54 |

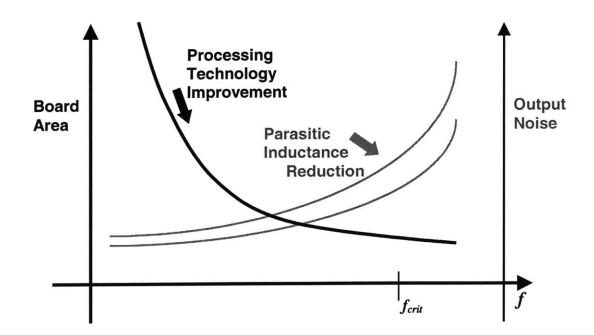

| 6-1:  | Qualitative Change in Board Area with Change in Switching Frequency 6 | 56 |

# List of Tables

| 2-1: | Electrical Characteristics of the Monolithic Boost Converter | . 19 |

|------|--------------------------------------------------------------|------|

| 2-2: | SR Flip-Flop Truth Table                                     | .25  |

| 2-3: | Shutdown Truth Table                                         | .26  |

| 4-1: | Temperature Ranges for Various Application Markets           | .36  |

# **1** Introduction

## 1.1 Handheld Devices

In the late 1950's an obscure Japanese company, Tokyo Tsushin Kogyo KK, revolutionized the electronics industry with a groundbreaking product offering: the transistorized radio.<sup>1</sup> The radios were an immediate success, and the newly renamed Sony Corporation<sup>2</sup> became an international leader in electronics. The company founders had the vision to tap into the undiscovered market for handheld devices [1]. Businesses worldwide mobilized to satiate the consumer hunger for portable electronics. Today there is a wide array of handheld products available, such as Discmans, MP3 players, cellular phones, personal organizers, and palmtop computers. Several companies serving the handheld market command capitalizations well above the fifty billion-dollar mark<sup>3</sup>, indicating that the handheld market is one of the most lucrative markets in business today.

### 1.2 New Arrivals

Amazing new handheld devices will arrive in the near future. There has been some hoopla in the news about electronic books, especially after Steven King's recent release of the ebook *Riding the Bullet*. A substantial amount of effort has gone into producing electronic paper and ink at Xerox PARC and several research universities. Products using electronic ink technology should be available to consumers before the end of the decade [2]. One step beyond

<sup>&</sup>lt;sup>1</sup> Texas Instruments released the first transistorized radio, which was also an immediate success. However, Texas Instruments only produced the radio as a marketing scheme for its transistors, and did not continue production after their first run of radios quickly sold out in the stores.

<sup>&</sup>lt;sup>2</sup> The founders of the minute Tokyo Tsushin Kogyo KK, decided to change the name to something that would be more attractive to the American consumer.

handheld computing will be wearable computing. There will be those who are so enthralled with connectivity that they would wear their computer wherever they go [3]. The current trend to make handheld devices smaller, cheaper, and more powerful should continue well into the future.

### 1.3 About this Thesis

One of the most interesting stories in the handheld market has been the evolution of the mobile phone. Mobile phones have been around for years, yet they have only recently become ubiquitous. Up until the late nineties, mobile phones were rarely found outside of executives' luxury sedans. Today, one out of every three people in America has a cell phone [4]. There are many reasons why they only recently became popular. The mobile phones of the eighties were pricey and service was even pricier. Unfortunately, you would get a lot of phone for your money. The phones were so big that they could barely fit in a briefcase. Now that mobile phones can fit in a pocket, people actually want to buy them.

Manufacturers of handheld devices will do whatever it takes to make their products smaller, because they know a smaller product will be more attractive to customers. To do this, they need to minimize the space consumed by the electronics. The power supply, in particular, can occupy a small but significant amount of the board area. The power supply is necessary because the batteries in a handheld device are rarely at the appropriate voltage for the microprocessor and other logic circuitry. For example, new batteries in the back of a Palm Pilot supply 3V. As the batteries drain, their voltage also drops, and can fall all the way to 0V if they are fully discharged. Most of the logic in the Palm Pilot needs 3.3V to work, however, so the battery voltage needs a boost. Manufacturers of handheld devices want the smallest possible

<sup>&</sup>lt;sup>3</sup> Sony has a market capitalization of 66 billion dollars and Nokia has a market capitalization of 212 billion dollars. To put this in perspective, Cisco, the corporation with the largest market capitalization, is valued at 301 billion dollars. All this information is from the end of the trading day on January 4<sup>th</sup>, 2001

boosting circuit for their product. Therefore, one of the most important goals for designers of boosting circuits is to make their circuit as small as possible.

This thesis involves the design, construction, and testing of an integrated circuit boost converter that occupies the smallest possible circuit board area. The printed circuit board area is dominated not by the integrated circuit itself, but by the external circuitry. The integrated circuit is only one of several components needed to boost the output voltage. There are also input and output capacitors, an inductor, and a diode. In particular, the inductor and the capacitors occupy the most significant amount of board space. The sizes of the inductor and the capacitors have an inverse relation to the switching frequency of the boost converter. Increasing the switching frequency of the regulator will therefore decrease the size of the total boost converter. The goal was to build a commercially viable converter with the highest possible switching frequency. This Masters thesis documents what was learned in the process of pushing today's switching power supply technology to its limits.

## 1.4 A Brief History of DC/DC conversion

There was a time when putting a radio into an automobile posed a significant technical challenge. Radios needed high voltage to operate, and the only voltage available in a car was the 6V battery. Galvin Manufacturing Corporation figured out that if they converted the 6V DC from the battery to the greater than 90V DC needed to electrify a vacuum tube, they could build a high quality and low cost audio amplifier and radio receiver. In order to get the 90V DC from 6V, they built the world's first commercial DC/DC switching converter, a synchronous vibrator power supply.

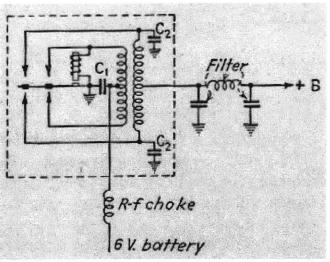

Figure 1-1: Synchronous Vibrator Power Supply [5]

To capture the idea of putting a radio in a motor car, the company gave the car radio product line the name Motorola. The car radio was so popular that the Galvin brothers soon changed their company name.

This great idea was only the beginning. Motorola's converter was noisy, bulky, inefficient, and prone to mechanical failure. The next big drive for improvements in power conversion came during the space race. Power supplies needed to be quiet, small, efficient, and extremely reliable, the exact opposite of their state at the time. Both industry and academics were supported through financial grants from the defense department to build the DC/DC converters needed to beat the USSR into space and to the moon. Further improvements came through continued support of the defense department, especially at the California Institute of Technology, where the modern control theory for switching regulators was developed [6]. Most the improvements since then have been driven by consumer-based demand for cheaper and smaller products.

# 2 Context

## 2.1 Scope

There are a few topics in DC/DC conversion where the author has the advantage of not only personal experience, but also expansive support from the staff of Linear Technology Corporation. These topics are investigated with the most amount of rigor.

Three areas in this thesis project are described in detail: the design of the switch, the performance of the application circuit, and measurement techniques. Although several months were spent designing the switching regulator, only a few facets of the design posed significant technical challenges. Monolithic<sup>4</sup> switching controllers have existed since the 1980's and it is doubtful that the design would garner academic interest [7].

The author does believe a 200mA switch that can operate at 10MHz with minimal power dissipation is a technically interesting creation. The design process is documented, focusing on the optimization of the switch. This process includes the choice of semiconductor technology and design driver circuitry.

The true test of the switch comes in the application circuit, when input to output efficiency is measured. The quality of the switch determines a majority of the efficiency loss in a power converter. The particularly important specifications will be the rise and fall times of the current in the switch, the on resistance of the switch, and the maximum output current of the switch.

Methods to perform measurements at high frequencies are dispersed in current literature. Any measurement techniques that were both nontrivial and important to characterizing the operation of the switching controller are carefully detailed. Some of the measurements pushed

<sup>&</sup>lt;sup>4</sup> Monolithic – A monolithic switching converter includes the switching controller and the switch all in one chip.

available instruments to the specified limits of reliable operation. The action of taking some of the necessary measurements also altered the performance of the circuit.<sup>5</sup> These shifts in performance are accounted for and analyzed.

Other subjects investigated may be of interest to the reader. In particular, some performance of the integrated controller suffered because of the high switching frequency. In addition, in the course of modeling the switch and external components, insights were gained as to what the maximum possible switching frequency for a commercial boost controller might be. The author predicts a maximum frequency with some reservations. Those who have predicted limits to human capability have been predictably wrong.<sup>6</sup>

## 2.2 Approach

There are many different ways to approach the design of an analog circuit. A researcher can program a circuit with analog hardware description language, design a circuit with computer tools such as SPICE<sup>7</sup>, hand design the circuit on paper, or breadboard a circuit on the bench. Each method has advantages and drawbacks in different applications. Analog hardware description language can be useful to those unfamiliar with analog design, but only if they need to meet low performance specifications. Computer tools such as SPICE are invaluable for the design of integrated circuits [8]. Designs based on SPICE simulations, however, should meet with practical experience as much as possible. Circuits that operate perfectly in SPICE simulations can fail miserably in the lab. For example, when the first design of the circuit was finished, and the simulated performance was acceptable, several staff members of the Linear

<sup>&</sup>lt;sup>5</sup> Heisenberg's Uncertainty Principle has a parallel in analog electronics. All analog measurements, by nature, will alter the performance of the circuit being measured.

<sup>&</sup>lt;sup>6</sup> "I confess that in 1901, I said to my brother Orville that man would not fly for fifty years... Ever since, I have distrusted myself and avoided all predictions." Wilbur Wright, 1908

<sup>&</sup>lt;sup>7</sup> Simulation Program with Integrated Circuit Emphasis

Technology Corporation examined the circuit. They discovered design flaws that would cause the circuit to have miserable performance, and realized that the SPICE simulations were overly optimistic.

The best way to measure the performance of discreet based designs is through bench verification. SPICE simulations will sometimes lie<sup>8</sup>; the bench will generally tell the truth. There are caveats to this statement, however, in the cases of high frequency or high accuracy measurement techniques. In these cases, SPICE simulations will often lie<sup>9</sup>, and without proper care, the bench will lie<sup>10</sup>. A project that necessitates high accuracy or high frequency measurement techniques should be approached with respect.

Hand calculating the performance of the circuit is also an invaluable exercise. Hand calculations will give the circuit designer a better understanding of his circuit, and therefore greatly aid him in both in troubleshooting and in improving performance. Every useful tool available was used in this design, including hand calculations, SPICE simulations, and thorough testing on the bench.

The best way to ensure this thesis would have timely relevance to the industrial community was to design the integrated circuit as if it would sell competitively in the open market. The power management integrated circuit market was 2.2 billion dollars in 1998, and continues to grow at a rapid pace [9]. Boost controllers comprise a significant portion of this

<sup>&</sup>lt;sup>8</sup> The term 'lying' in reference to design may be unfamiliar to the casual reader. A manufactured circuit may have electrical characteristics that differ from those indicated in SPICE simulations. When a SPICE simulation indicates electrical characteristics significantly different from the electrical characteristics of the manufactured silicon, this is considered 'lying'.

<sup>&</sup>lt;sup>9</sup> SPICE only gives results as accurate as the models it is given. If SPICE is given models that accurately predict the electrical characteristics of the transistors, and parasitics due to traces and packaging are taken into account, simulated performance should match well with measured performance.

<sup>&</sup>lt;sup>10</sup> Poor measurement techniques can also indicate electrical characteristics that deviate from the true electrical characteristics of the circuit under test.

market. Improving the performance of boost controllers allows companies to maintain or increase their market share of this segment, and should be a profitable venture.

### 2.3 Prior Work

It is easy for an engineer to be caught up in a novel design and forget about the outside world. In the outside world there may be other researchers doing similar or more impressive work. It is important for an engineer to be keenly aware of the latest developments in his area of research; else, he may suffer from irrelevance.

Most of the research in the academic world has focused on high power designs using MOS switches. The designs have focused mainly on overcoming the limitations of the MOS switches, which have significant amounts of both gate and output capacitance. Driving the circuits adds a significant loss term. Experimental versions of power converters have reported switching frequencies of up to 14MHz [10].

Nearly all of the experimental designs of switching converters either required expensive components or processing techniques, or were application specific, and were far from being useful in a commercial situation. In order to achieve high frequencies, the researchers designed in flaws that made their designs commercially impractical. Commercial products available today gave a better guide for the design.

The biggest push for high frequency conversion today appears to be in the market for step down DC/DC conversion. Several companies have developed step down switching controllers with very fast frequencies. Their choice of switching frequencies elucidates the problems with switching at even higher frequencies. Efficiency decreases significantly with the increase in

14

speed of the switcher, and at some point the efficiency becomes so poor the switcher is unusable. Currently available step down converters switch at frequencies of up to 2 MHz.<sup>11</sup>

There are other methods to boost voltages than using switching regulators. A popular alternative is to use a switched capacitor charge pump. Switched capacitor charge pumps provide an attractive solution because they avoid the use of inductors, and occupy a small amount of board space. Charge pump circuits also provide a simple solution to disconnect the input from the output. Unfortunately, they draw current from the input in impulses, which adds a significant noise to the input supply. The output of a switched capacitor charge pump is also noisy compared to a switching regulator, unless the output is pre-regulated with a linear regulator. Switched capacitor charge pumps with linear regulated outputs do provide low noise outputs, but are inefficient. In general, switching regulators can provide more current, in a smaller amount of space, and with lower noise, than switched capacitor charge pumps.

Increasing the switching frequency is not the only way to decrease the total board space used in a boost converter. Improved packaging techniques such as 'flip chip' result in smaller solutions. Other external components such as the feedback resistor or the Schottky diode can be integrated into the chip. This unfortunately results in less flexibility for the applications engineer. If the feedback resistors are integrated, one chip would only be able to do one output voltage. The Schottky diode can be integrated as a switch, but only in a complementary process. A circuit that used all of these ideas could be made very small, but would be application specific.

<sup>&</sup>lt;sup>11</sup> As demonstrated by the SEMTECH SC1144EVB.

# 2.4 System and Specifications

The integrated circuit is mounted in a five-pin SOT package. The typical application is boost conversion.

#### **Typical Application**

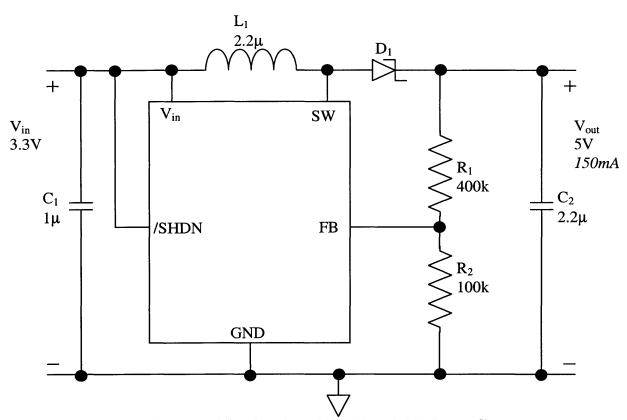

Figure 2-1: Typical Application of the Monolithic Boost Converter

The pin out in the typical application circuit corresponds to the numbered pins in Fig. 2-2. A boost converter works by switching inductor current between the output and ground. Inductor current, which corresponds to the input current, is only delivered to the output a fraction of each switching cycle. The fraction of the period the switch is on is called the duty ratio, and is often referred to simply as the letter D. The fraction of the switching cycle when inductor current is delivered to the output is therefore 1-D.

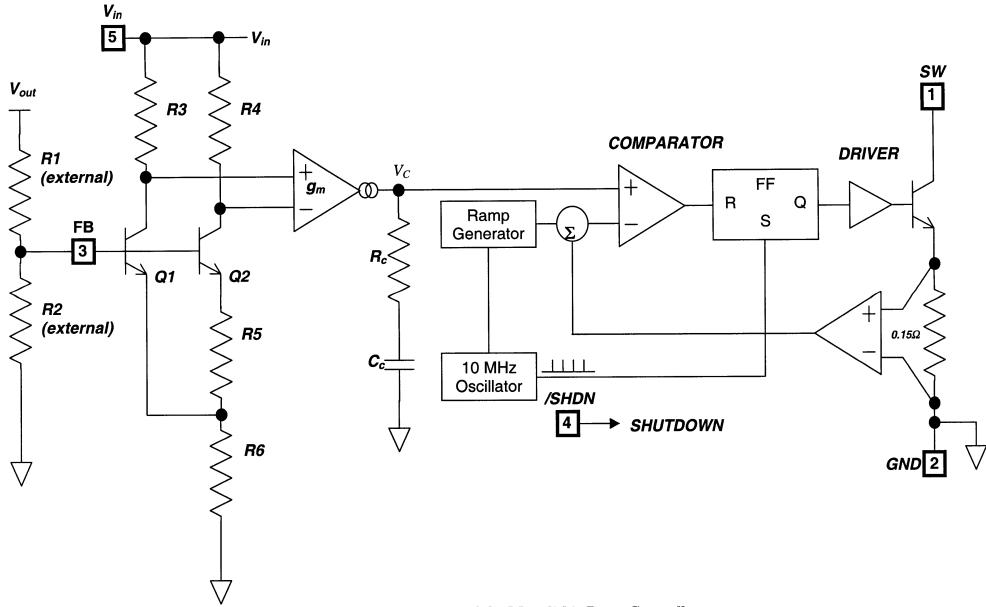

Figure 2-2: Block Diagram of the Monolithic Boost Controller

Since energy is conserved, the output voltage must be correspondingly greater than the input voltage:

$$V_{OUT} = \frac{V_{IN}}{1 - D}$$

The architecture and the circuit design were based on the LT1613. By careful observation of the typical application circuit and block diagram, one can identify the control loop and understand the operation of the circuit. Resistors R1 and R2 are selected so that  $V_{out} = 1.25V(1 + R_1/R_2)$ . When  $V_{out}$  falls, the voltage at the FB pin will decrease. This increases the current out of the error amplifier, which increases  $V_C$ , the threshold of the comparator. Each cycle, the switch turns on and drops a positive voltage across the inductor. The current ramps upwards and is sensed by the 0.15 Ohm resistor. The sense voltage is amplified and compared to  $V_C$ . When it rises to a higher potential than  $V_C$ , the flip-flop resets and the switch turns off. The output current will therefore increase with increasing voltages at  $V_C$ . Increased current leads to increased output voltage and closes the negative feedback loop.

If the load is decreased, the switch will turn on for a shorter period each cycle. At even lighter loads, the converter will skip cycles to maintain output regulation.

Although design changes were required to increase the LT1613's switching frequency from 1.4 MHz to 10 MHz, the architecture remains the same. Some of the LT1613's impressive specifications were relaxed in order to speed up the design process, since a limited time was available. In particular, the circuit operates only to 2.4V, but the LT1613 operates down to 1.1V. Designing circuits that work at low-level voltages is both challenging and time consuming.

| PARAMETER                     | CONDITIONS                                           |   | MIN _           | TYP  | MAX              | UNITS           |

|-------------------------------|------------------------------------------------------|---|-----------------|------|------------------|-----------------|

| Minimum Input Voltage         |                                                      |   |                 | 2.0  | 2.4              | V               |

| Quiescent Current             | $V_{SHDN} = 1.5V$ , Not Switching<br>$V_{SHDN} = 0V$ |   |                 | 4.7  | <b>6.1</b><br>50 | <b>mA</b><br>μA |

| Reference Voltage             | Measured at FB pin                                   | • | 1.21            | 1.24 | 1.27             | V<br>V          |

| FB Pin Bias Current           | $V_{FB} = 1.26V$                                     | • |                 | 150  |                  | nA              |

| Switching Frequency           |                                                      | • | 7               | 10   | 13               | MHz             |

| Maximum Switch Duty Cycle     |                                                      | • | <b>90</b><br>76 | 92   |                  | %               |

| Switch Current Limit          |                                                      | • | 220             | 350  |                  | A               |

| Switch V <sub>CESAT</sub>     | I <sub>SW</sub> = 150mA                              |   |                 | 200  | 240              | mV              |

| Switch Leakage Current        | Switch Off, $V_{SW} = 5V$                            | • |                 | 0.01 | 5                | μΑ              |

| SHDN Pin Current              | V <sub>SHDN</sub> = 1.5V                             |   |                 | 65   | 100              | μΑ              |

| Shutdown Threshold (SHDN pin) |                                                      |   |                 |      | 0.3              | V               |

| Startup Threshold (SHDN pin)  |                                                      | + | 0.9             |      | -                | V               |

ELECTRICAL CHARACTERISTICS The  $\bullet$  denotes specifications that apply over the full operating temperature range, otherwise specifications are at T<sub>4</sub> = 25°C. V<sub>PV</sub> = 3.3V. V<sub>SUDV</sub> = 3.3V. unless otherwise noted.

**Table 2-1: Electrical Characteristics of the Monolithic Boost Controller**

These specifications were derived from testing the manufactured integrated circuit. The ranges of operation were chosen to allow for a high yield under a large production run, and were determined using known process variations. A manufactured circuit should only deviate from the specified electrical characteristics if process parameters are out of bounds, and this would be caught immediately by automatic test equipment.

## 2.4.1 Brokaw Cell

The circuit diagram of a Brokaw cell is shown in Figure 2-2, and is formed by Q1, Q2, R3, R4, R5, and R6 [11]. Transistor Q2 is scaled so it has a larger emitter area than Q1. When the feedback loop is closed around the total circuit, the collector currents are forced to be equal. This sets up a  $PTAT^{12}$  voltage at the emitter of Q1. The voltage at the FB pin will be a sum of a  $V_{be}$ , which is  $CTAT^{13}$ , and a PTAT voltage. With appropriate scaling between R5 and R6, the voltage at the FB pin will be nearly independent of temperature.

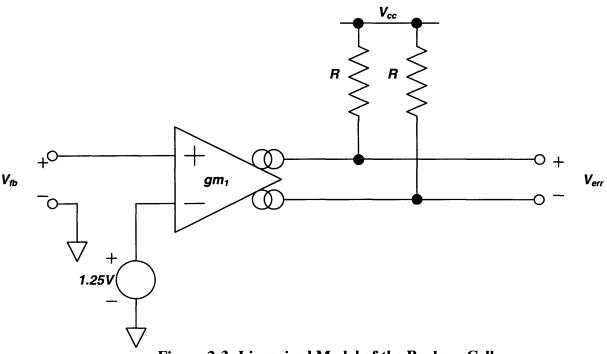

Figure 2-3: Linearized Model of the Brokaw Cell

A linearization of the Brokaw cell is shown in Figure 2-3. The Brokaw cell generates a differential output voltage that is proportional to the difference between the voltage at the FB pin and 1.25V. The input of the Brokaw cell is a high impedance, and the differential output is a

<sup>&</sup>lt;sup>12</sup> Proportional To Absolute Temperature

<sup>&</sup>lt;sup>13</sup> Conversely proportional To Absolute Temperature

lower impedance of 4.4k. The gain of this circuit is well below unity and has a marginal contribution to limiting the bandwidth of the feedback loop.

## 2.4.2 Error Amplifier and Compensation

The error amplifier generates an output current that is proportional to the difference in the voltages at its input. Both the input and the output are high impedances.

#### **Error Amplifier**

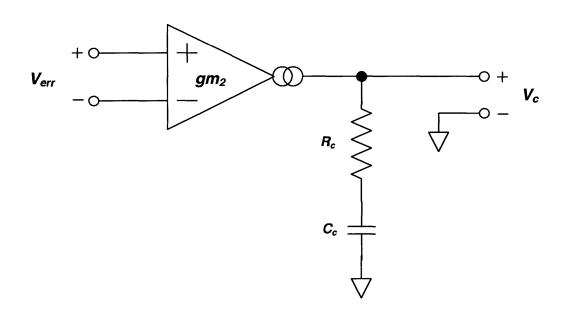

Figure 2-4: Linearized Model of the Error Amplifier

The compensation network provides both a pole and a zero. The pole is at a relatively low frequency, and the zero is at a higher frequency. The pole and zero are placed in locations to optimize transient response with a ceramic output capacitor. These components help determine the loop dynamics of the circuit. The transfer function of the circuit is calculated as follows:

$$\left|\frac{V_c}{V_{err}}\right| = gm_2 r_o \left|\left(R_c + \frac{1}{sC_c}\right) = \frac{gm_2 r_o \left(sC_c R_c + 1\right)}{sC_c \left(r_o + R_c\right) + 1}\right|$$

The formulas are more manageable with a few simplifications. The first is to express the pole time constant in terms of the zero time constant by a factor of  $\alpha$ . Lag type compensation is desired, so alpha must be greater than one. The lag compensation increases the open loop gain, but does contribute negative phase. This is acceptable because there is only ninety degrees of additional phase in the loop from the output capacitor, as long as the loop gain falls below unity well below the switching frequency of the converter [12].

$$T_{p} = \alpha T_{z}$$

$$H(s) = \frac{(T_{z}s+1)}{(\alpha T_{z}s+1)}$$

The phase of the transfer function over frequency is easily deduced from the transfer function:

$$\angle H(\varpi) = \tan^{-1}(T_z \varpi) - \tan^{-1}(\alpha T_z \varpi)$$

The frequency where the maximum phase dip due to the lag compensation is calculated by finding the zero crossings of the derivative:

$$\frac{d\angle H(\varpi)}{d\varpi} = \frac{T_z}{(T_z\varpi)^2 + 1} - \frac{\alpha T_z}{(\alpha T_z\varpi)^2 + 1} = 0$$

$$T_z^3 \varpi^2 (\alpha^2 - \alpha) - T_z (\alpha - 1) = 0$$

$$\varpi^2 = \frac{T_z (\alpha - 1)}{\alpha T_z^3 (\alpha - 1)}$$

$$\varpi = \frac{1}{T_z \sqrt{\alpha}}$$

The maximum phase dip therefore happens when the frequency is equal to the geometric mean of the two time constants:

$$\angle H\left(\boldsymbol{\varpi} = \frac{1}{T_z \sqrt{\alpha}}\right) = \tan^{-1}\left(\sqrt{\alpha}\right) - \tan^{-1}\left(1/\sqrt{\alpha}\right)$$

For acceptable transient performance of the circuit, a maximum of 135 degrees of phase at crossover is allowed. The output capacitor contributes 90 degrees of phase. This allows for another 45 degrees of phase contribution from the compensation network. An  $\alpha$  of six will lead to approximately 45 degrees of phase. An appropriate ratio between  $r_o$  and  $R_c$  can be determined:

$T_z = R_c C_c$

$\alpha T_z = C_c \left( R_o + R_c \right)$

$R_c \approx \frac{1}{5}r_o$

#### 2.4.3 Ramp Generator

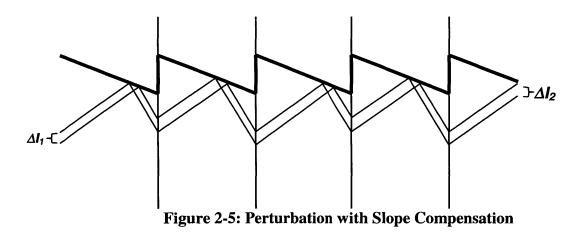

The ramp generator adds slope compensation to the current ramp created from the current sense amplifier. With slope compensation, a perturbation in the inductor current, such as  $\Delta I_1$ , remains small or disappears after several cycles. There is enough slope compensation to prevent subharmonic oscillations under all normal operating conditions.

Figure 2-6: Perturbation without Slope Compensation

Without slope compensation, a small perturbation in the inductor current, such as  $\Delta I_3$ , becomes increasingly larger, and the system is unstable for duty cycles greater than 0.5.

# 2.4.4 Oscillator

The oscillator is designed to operate at a nominal frequency of 10 MHz. The oscillator frequency will drift with supply and temperature variations. The oscillator should remain within plus or minus ten percent of nominal, under all operating conditions. One of the major advantages of fixed frequency control method is the predictable output frequency. If the switching frequency varies too much, the product will be unattractive to customers, because it can make the design of the application circuit difficult or impossible.

### 2.4.5 SR Flip Flop

| Input         |              |            | Output |            |  |

|---------------|--------------|------------|--------|------------|--|

| Present State | S            | R          | Q      | Next State |  |

| DON'T CARE    | $\uparrow$   | DON'T CARE | 0      | 0          |  |

| DON'T CARE    | 1            | DON'T CARE | 0      | 0          |  |

| DON'T CARE    | $\downarrow$ | 0          | 1      | 1          |  |

| DON'T CARE    | $\downarrow$ | 1          | 0      | 0          |  |

| 1             | 0            | 0          | 1      | 1          |  |

| 1             | 0            | $\uparrow$ | 0      | 0          |  |

| 0             | 0            | DON'T CARE | 0      | 0          |  |

Table 2-2: SR Flip-Flop Truth Table

## 2.4.6 Driver

The base drive requires more current than the digital logic can provide. The driver provides buffering between the output of the SR flip-flop and the switch. The driver is essentially a current booster, with anti-saturation circuitry for the switch.

#### 2.4.7 Switch

The switch is a large NPN bipolar transistor. The layout is optimized for minimal input and output capacitance and even current distribution. The switch and the rest of the circuit are designed on a two-micron complimentary bipolar process, which has forward transit frequency of up to 6 GHz. Using a high frequency bipolar process leads to a minimal output capacitance on the switch, so the switch can operate at a very high frequency with low loss. A sense resistor is closely coupled with the switch.

#### 2.4.8 Current Sense Amplifier

The current sense amplifier produces a voltage that is proportional to the difference in voltage across the two terminals of the sense resistor. This is called Kelvin sensing, and is the

most accurate way to measure voltage across a resistor. It is important to Kelvin sense the current sense resistor in a switching regulator, else significant errors can be introduced into the control loop.

#### 2.4.9 Shutdown

If the shutdown pin is high, the part will operate in a normal fashion. If the shutdown pin is pulled low, the part will go into a minimum current mode, and the total current to the part will drop below 50uA. This functionality enables the user to conserve battery power when output voltage regulation is not needed.

| SHDN                            | Mode             |  |

|---------------------------------|------------------|--|

| V <sub>/SHDN</sub> < 0.3V       | Shutdown         |  |

| $V_{\rm /SHDN} > 1.0V$          | Normal Operation |  |

| Table 2-3: Shutdown Truth Table |                  |  |

### 2.4.10 Current Limit

Any time the current in the switch exceeds a certain level, the switch will turn off. This will happen on a cycle-by-cycle basis. The current limit will trip at no less than 200mA. This is included to protect the integrated circuit from damage during overload. Unfortunately, a boost converter is inherently vulnerable to short circuits since there is only a diode from the output to the input. During a short circuit, the diode, and possibly the input supply will suffer damage, but the integrated circuit should survive.

# **3 Design and Simulation**

It is usually possible to take an existing schematic, make a few changes, and produce a better circuit. A circuit designer can do this without a good understanding of the circuitry

involved. Many excellent circuits designers hack<sup>14</sup> their circuits, getting superb results without ever getting out a calculator. A novice circuit designer would be better off cracking the books and developing a deep understanding of the circuits he is working on, and leave the hacking to the experts.

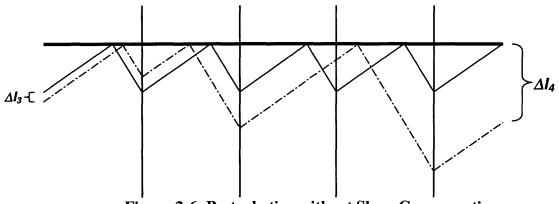

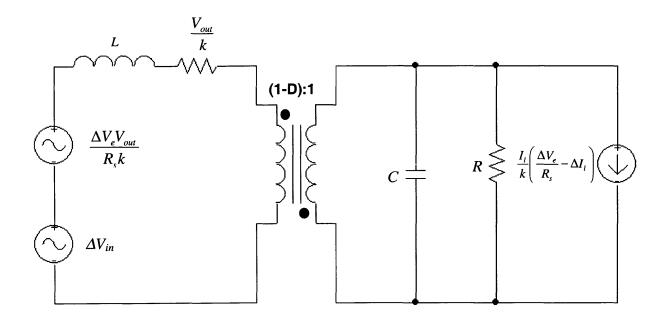

One of the best ways to understand analog circuits is to develop a linearized model of the circuit. The linearized model gives the designer a powerful tool to analyze the system. The designer can quickly iterate his design to provide the best performance possible. Researchers at the California Institute of Technology developed the first accurate linearized model of a buck, boost, and buck-boost converters [13]. Researchers at Unitrode developed a linearized model of the buck converter that is a more manageable than 'Cuk and Middlebrook's derivation [14]. The author derived a model for the boost converter in a similar fashion from the circuits described in Figure 2-1 and Figure 2-2. With this model in hand, intelligent design decisions for the loop and slope compensation were possible.

The derivation the linear model for a current mode boost converter starts with looking at the state space averaged equations for the inductor current and the output voltage:

$$\mathbf{\dot{I}}_{L} = \frac{V_{in}}{L}D - \frac{V_{out} - V_{in}}{L}(1 - D)$$

$$\mathbf{\dot{V}}_{out} = \frac{I_{L}}{C}(1 - D) - \frac{V_{out}}{CR}$$

An incremental change in the variables affects the change in inductor current:

$$\overset{\bullet}{\Delta} I_{L} = \frac{\Delta V_{in} D + \Delta D V_{in}}{L} - \left[ \frac{\Delta V_{out} - \Delta V_{in}}{L} (1 - D) + \frac{V_{in} - V_{out}}{L} \Delta D \right]$$

$$\Delta \overset{\bullet}{V}_{out} = (1 - D) \frac{\Delta I_{L}}{C} - \frac{\Delta V_{out}}{CR} - \Delta D \frac{I_{L}}{C}$$

The expression for the inductor current can be simplified:

$$\dot{\Delta}I_{L} = \left[\Delta V_{in} - \Delta V_{out}(1-D) + \Delta D V_{out}\right]/L$$

<sup>&</sup>lt;sup>14</sup> hack: designing circuits on gut instinct rather than hard and fast calculations

The control voltage for the current limit is related to the average current by the slope compensation, the sense resistor, the duty cycle, the period, the input voltage, the output voltage, and the inductor size:

$$I_L R_s = V_e - mDT - \frac{D^2 V_{in} TR_s}{2L} - \frac{(1-D)^2 (V_{out} - V_{in}) TR_s}{2L}$$

R<sub>s</sub> = resistance of the sense resistor (Ohms)

V<sub>e</sub> = output voltage of the error amplifier (Volts)

V<sub>in</sub> = input voltage to the boost converter (Volts)

V<sub>out</sub> = output voltage of the boost converter (Volts)

m = slope of the slope compensation ramp (Volts/second)

D = duty cycle of the converter (unitless)

L = inductance of the switching inductor (Henrys)

T = period of switcher (seconds)

The incremental change in inductor current with a change in the other variables is as follows:

$$\Delta I_{L} = \frac{\Delta V_{e}}{R_{s}} - \Delta DT \left( \frac{m}{R_{s}} + \frac{V_{in}D}{L} - \frac{(V_{out} - V_{in})(1 - D)}{2L} \right) - \frac{T}{2L} \left[ \Delta V_{in}D^{2} + (\Delta V_{out} - \Delta V_{in})(1 - D)^{2} \right]$$

The duty cycle changes with control voltage, inductor current, and input and output voltages:

$$\Delta D = \left[\frac{\Delta V_e}{R_s} - \frac{T}{2L} \left[\Delta V_{in} D^2 + \left(\Delta V_{out} - \Delta V_{in}\right)(1-D)^2\right] - \Delta I_L\right] / \left[\frac{Tm}{R_s}\right]$$

negligible

Simplifying further:

$$\Delta I_{L}^{\bullet} = \frac{1}{L} \left[ \Delta V_{in} - \Delta V_{out} (1 - D) + \frac{V_{out}}{k} \left( \frac{\Delta V_{e}}{R_{s}} - \Delta I_{L} \right) \right]$$

$$\Delta I_{L}^{\bullet} = \frac{\Delta V_{in}}{L} - \Delta V_{out} (1 - D) + \frac{\Delta V_{e} V_{out}}{L k R_{s}} - \frac{\Delta I_{L} V_{out}}{L k}$$

$$\Delta V_{out}^{\bullet} = (1 - D) \frac{\Delta I_{L}}{C} - \frac{\Delta V_{out}}{C R} - \frac{I_{L}}{C k} \left( \frac{\Delta V_{e}}{R_{s}} - \Delta I_{L} \right)$$

It is possible to draw a linearized circuit model based on these equations:

Figure 3-1: Linearized Model of Current Mode Boost Converter

The magnitude of k will largely determine the dynamics of the system. A smaller k will increase the magnitude of the damping resistance seen by the inductor and make the system look more like current source. If the inductor acts like a current source, the system will have first order dynamics.

If k is large, the system looks similar to that of a linearized circuit under duty cycle control. This makes intuitive sense, because the slope compensation is overwhelming the current sense ramp, and the circuit is operating like a voltage mode controller. The system will have a lightly damped pole pair due to the inductor and capacitor, which complicates the controller design.

Contrary to popular belief, a current mode boost controller with constant slope compensation is sensitive to changes in the input supply. It is easy to calculate the appropriate cycle-by-cycle waveform to give the boost converter ideal feed-forward characteristics.

$$I_{L}R_{s} = V_{e} - f(D) - \frac{(1-D)(V_{out} - V_{in})R_{s}}{2L}$$

29

The inductor current should only be dependent on the output voltage and the error voltage:

$$f(D) = \frac{(1-D)DV_{out}R_s}{2L}$$

But this curve looks like:

**Figure 3-2: Theoretical Slope Compensation Curve**

The loop will be unstable at duty cycles greater than 0.5. The inductor current will never be able to turn off at duty cycles greater than 0.5, and the system will not have the desired ideal feed-forward characteristics. Therefore, it is preferable to use simple slope compensation.

After hand analysis of the circuit was completed, the different blocks were simulated individually in SPICE and were checked over temperature and supply. Full chip simulations were not performed until all of the blocks were operating correctly, since full chip simulations take a much longer time to execute than simulations of the individual blocks. Load transients with a linearized model of the circuit were simulated before full chip simulations of load transients, which can take the better part of a day.

# **4 The Switch and Driver Circuitry**

The most important part of the switching regulator is the switch. The switch and switch driver circuitry were carefully modeled and designed. This attention to detail allows informed tradeoffs in its design, and permits accurate optimization of efficiency and duty cycle specifications. A solid understanding of the switch and its driver circuit is fundamental to optimizing the design.

# 4.1 Transistor Modeling

To get the most mileage both out of hand designs and SPICE simulations, one needs to start with accurate models. The author was lucky in this instance, since most of the work was already done. Several engineers of the Linear Technology Corporation devoted months to developing models of their transistors so simulations accurately matched the measured performance of the transistors in the process. This thesis would not have been possible without their labor.

## 4.2 Design Choices

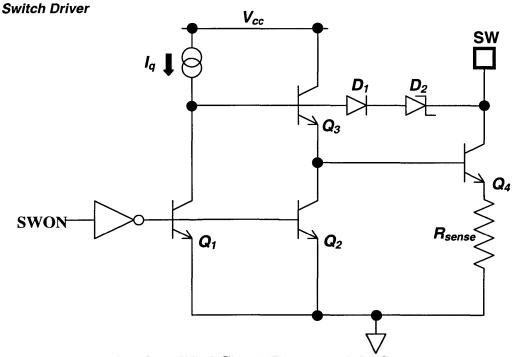

Figure 4-1: Simplified Circuit Diagram of the Switch Driver

The operation of the circuit is relatively simple.  $Q_4$  is a large area transistor and operates as the switch. When SWON goes high,  $Q_3$  turns on, and drives current into the base of the switch and it rapidly increases in current. Once the switch current is greater than the inductor current, the voltage on the switch decreases until the switch is saturated. The clamp diodes,  $D_1$  and  $D_2$ , are then forward biased and steal base current from  $Q_3$ , and reduces base current in the switch until the switch comes out of saturation. When SWON goes low,  $Q_2$  turns on and pulls charge out of the base of the switch. The switch turns off and the inductor then charges up the switch node until it is a diode drop above the output.

The topology of the switch driver circuit is decades old [15]. It is simply a Darlington configuration transistor with an active base pull-down. The drawback to the Darlington configuration is that it needs a significant supply voltage in order to run. To operate in the

forward active region, a switch in a Darlington configuration requires at least 2.1V of supply at – 55 degrees Celsius. If a switch needs to work with a lower supply voltage, it must be designed in a different configuration. Several important choices can be made in regards to the switch design. The first choice is the size of the switch. The optimal switch size will depend primarily on the output voltage and switch current of the target application. The second choice will be deciding the quiescent beta current, which will depend primarily on the maximum switch current. The third choice will be setting the saturation voltage of the switch. Some other considerations will be important in optimizing efficiency, such as the layout of the transistor, and size of the sense resistor.

#### 4.2.1Switch Size

The size of the switch is the most important design choice in the switching regulator. A large switch will have lousy efficiency at high output voltages, but can supply more current and has better efficiency at lower output voltages. The size of the switch determines several important specifications: maximum switch current, on resistance, and output capacitance. Increasing the maximum switch current is important because it will increase the usability of the part. The switch can be used in any applications that require less than the maximum switch current, but not in applications that require more. Therefore, a bigger switch is usually better.

A larger switch will also have a lower on resistance. Lowering the on resistance generally improves the efficiency of the converter. This is not always the case, however, since at high output voltages, the dominant source of loss will be the output capacitance of the switch, and a larger switch has a larger output capacitance. A simple hand calculation gives a basic idea of what the optimal switch size for an application is.

33

Bipolar transistor output capacitance [16]:

$$C_{cs} = \frac{k}{\sqrt{1 + v_{cs}}/\phi_{bs}}$$

k = zero bias capacitance per unit area (Farads per meter squared)  $C_{cs} = \text{collector to substrate capacitance of the transistor per unit area (Farads per meter squared)}$   $v_{cs} = \text{collector to substrate voltage of a transistor (Volts)}$  $\phi_{bs} = \text{built-in voltage of the collector substrate junction (Volts)}$

The collector resistance of a bipolar transistor is dependent on doping levels and layout.

Modern bipolar transistor design usually includes a highly doped buried layer that greatly

reduces the collector resistance. These doping levels are fixed by the process, so the designer can

only choose the transistor size to set the output resistance. Collector and emitter resistance is

directly proportional to transistor area.

Approximate power dissipation specifications for a bipolar transistor:

$$P_{diss} = A(fC_{cs}V_{out}^{2}) + \frac{1}{A}(r_{c} + r_{e})I_{sw}^{2}D + V_{ce}I_{sw}D + V_{in}I_{b}D$$

$$I_{sw} = \text{average current in the switch (Amps)}$$

$$V_{out} = \text{the output voltage of the switcher (Volts)}$$

$$V_{in} = \text{the supply voltage of the switcher (Volts)}$$

$$I_{b} = \text{the base current of the switch (Amps)}$$

$$D = \text{duty cycle of the switcher (unitless)}$$

$$R_{c} = \text{the collector resistance of a unit switching transistor (Ohms per meter squared)}$$

$$R_{e} = \text{the emitter resistance of a unit switching transistor (Volts)}$$

$$A = \text{the 'area' or number of unit transistors in the switch (meters squared)}$$

$$f = \text{the switching frequency of the converter (Hertz)}$$

Change in power dissipation dependent on a change in area:

$$\frac{dP_{diss}}{dA} = fC_{cs}V_{out}^{2} - \frac{1}{A^{2}}r_{c}I_{sw}^{2}D$$

Local maximum and minimum of this equation will be where

$$\frac{dP_{diss}}{dA} = 0$$

The positive root of this equation will be the area that gives the minimum power dissipation:

$$A^{2} = \frac{r_{c}I_{sw}^{2}D}{fC_{cs}V_{out}^{2}}$$

$$A = \frac{I_{sw}}{V_{out}}\sqrt{\frac{(r_{c}+r_{e})D}{fC_{cs}}}$$

Therefore, applications that require larger output voltages and less current will be more efficient with a smaller switch, whereas applications that require larger switch currents but smaller output voltages will be more efficient with a larger switch.

#### 4.2.2 Quiescent Current

Deciding the quiescent current for the Darlington is more complicated than would appear at first glance. The quiescent current determines the maximum current the switch can sink. The relationship between the quiescent current and the maximum switch current is proportional to the square of the forward current gain of the transistors. This means the choice for quiescent current is highly dependent on beta<sup>15</sup>. Beta, however, is highly dependent on process and temperature. There needs to be enough quiescent current to drive the switch even when the beta is low. The decision for the minimum operating temperature of the part will largely decide the maximum quiescent current specification.

As a case example, one can examine the performance of a discreet Darlington circuit. At room temperature and fixed collector current, the beta of the popular 2n2222 transistor varies from 100 to 300 from lot to lot. Two 2n2222 transistors operating in a Darlington connection will therefore have a current gain of as low as ten thousand or as high as ninety thousand, nearly an order of magnitude of difference. Over the military temperature range, beta can vary by over a

<sup>&</sup>lt;sup>15</sup> The DC forward current gain of the transistor will be referred to as beta or  $\beta$  for the remainder of this paper.

factor of four. This will result in over a 16:1 variation of current gain in a Darlington from 150 degrees Celsius to -55 degrees Celsius. With the worst case skew in process, the current gain of two Darlington connected transistors at high temperatures could be as much as 144 times as much as two Darlington connected transistors at low temperatures.

There are two options for designing the quiescent current source. It can be designed to be a constant current source, using a current so the switch will still work at the maximum switch current, minimum operating temperature, and worst-case beta due to process variation. The other option is to design a current source that tracks with temperature to only provide as much current as the Darlington needs. The current source can operate at much lower currents at room temperature than a static current source.

The maximum quiescent current drawn by the part is dependent on what the designer chooses as his minimum operating temperature. There are three basic temperature ranges: commercial, industrial, and military. The three temperature ranges vary from manufacturer to manufacturer, but the standard temperature ranges for the three are as follows:

| Application Market | Temperature Range (in degrees Celsius) |

|--------------------|----------------------------------------|

| Commercial         | 0 to 70                                |

| Industrial         | -40 to 85                              |

| Military           | -55 to 150                             |

Table 4-1: Temperature Ranges for Various Application Markets

For example, by looking for a maximum switch current of 500mA, one can determine what the maximum quiescent current for the switch will be for each of the temperature ranges.

$\beta$  (at room temperature) = 60 x = 2 (x is the exponent of the temperature coefficient of beta) T<sub>nom</sub> = 300 Kelvins (the temperature where the nominal beta was measured) I<sub>swmax</sub> = 500mA (the maximum operating current of the switch)

$$\beta = \beta_{nom} \left(\frac{T}{T_{nom}}\right)^{x}$$

$$I_{swmax} = I_{q} \beta_{nom}^{2} \left(\frac{T}{T_{nom}}\right)^{2x}$$

$$I_{q} = \frac{I_{swmax}}{\beta_{nom}^{2} (T/T_{nom})^{2x}}$$

Maximum commercial quiescent Darlington current:

$$I_q = \frac{500mA}{60^2 (273/300)^4} = 202uA$$

Maximum industrial quiescent Darlington current:

$$I_q = \frac{500mA}{60^2 (233/300)^4} = 382uA$$

Maximum military quiescent Darlington current:

$$I_q = \frac{500mA}{60^2 \left(218/300\right)^4} = 500uA$$

The example shows that the maximum quiescent current is largely dependent on the designer's choice of the minimum operating temperature.

#### 4.2.3 Forcing Beta Circuit

The design of the switch includes anti-saturation circuitry that limits the base current in the switch. The operating point of the circuitry can be chosen in order to optimize the performance and the efficiency of the switch. Richard Baker first addressed the performance problems associated with saturating bipolar transistors in a paper about digital logic [17]. He discovered that he could speed up the operation of bipolar transistor logic by keeping the transistors out of saturation. The physics behind saturation are now well understood. When a bipolar transistor is saturated, the base-collector diode is forward biased. The forward biasing of this transistor stores charge in the PN junction. That charge must be removed before the transistor can be turned off. Saturated bipolar transistors require approximately three times longer to turn off than a bipolar transistor held outside of saturation. The transistors must stay well out of saturation in order to maximize the switching speed of the bipolar transistors.

The switch anti-saturation circuitry also decreases power dissipation of the integrated circuit. The anti-saturation circuitry limits the base current, so that at lower current levels the base current drive is only as much as necessary.<sup>16</sup> Otherwise, the base current drive would be the same at all output current levels. The operating point of the switch can be chosen in order to optimize efficiency.

The Ebers-Moll model of the transistor gives an idea of the relation between the saturation voltage and the effective beta:

$$I_{c} = I_{s} \left( e^{V_{bc}/V_{th}} - 1 \right) - \frac{I_{s}}{\alpha_{r}} \left( e^{V_{bc}/V_{th}} - 1 \right)$$

Ebers-Moll Model of the Transistor when  $V_{be} \& V_{bc} > V_{th}$ :

$$I_c = I_s e^{V_{bc}/V_{th}} - \frac{I_s}{\alpha_r} e^{V_{bc}/V_{th}}$$

Simplification to find  $V_{ce}$  in terms of  $I_b$  and  $I_c$ :

$$I_{c} = I_{s}e^{V_{be}/V_{th}} \left(1 - \frac{1}{\alpha_{r}(\beta I_{b} - I_{c})}\right)$$

but Isexp(V<sub>be</sub>/V<sub>th</sub>) =  $\beta$ I<sub>b</sub> so:

$$\frac{1}{\alpha_r e^{V_{cc}/V_{th}}} = 1 - \frac{I_c}{\beta I_b}$$

$$\frac{\beta I_b}{\alpha_r(\beta I_b - I_c)} = e^{V_{cc}/V_{th}}$$

<sup>&</sup>lt;sup>16</sup> This is sometimes referred to as a forced beta circuit, because the transistor is forced to operate at a fixed current gain.

$$V_{ce} = V_{th} \ln \left( \frac{\beta I_b}{\alpha_r (\beta I_b - I_c)} \right)$$

It will be analytically easier to take the derivative in terms of  $I_b$ , and therefore easier to optimize  $I_b$ . Because of the earlier assumption that  $V_{be} \& V_{bc} > V_{th}$ , this new equation is only valid if  $\beta I_b < I_c$ .

In order to minimize power dissipation by changing  $I_b$ , the previously calculated power dissipation equation is needed:

$$P_{diss} = A(fC_{cs}V_{out}^{2}) + \frac{1}{A}(r_{c} + r_{e})I_{sw}^{2}D + V_{ce}I_{sw}D + V_{in}I_{b}D$$

$$\frac{dP_{diss}}{dI_{b}} = DI_{sw}V_{th}\left[\frac{\alpha_{r}(\beta I_{b} - I_{sw})}{\beta I_{b}}\right]\left[\frac{\alpha_{r}(\beta I_{b} - I_{sw})\beta - \beta^{2}\alpha_{r}I_{b}}{(\alpha_{r}\beta I_{b} - \alpha_{r}I_{sw})^{2}}\right] + DV_{in} = 0$$

$$\beta(\beta I_{b} - I_{sw}) - \beta^{2}I_{b} = -\frac{V_{in}}{I_{sw}V_{th}}\left[\beta I_{b}(\beta I_{b} - I_{sw})\right] = 0$$

$$I_{b}\left(\beta^{2} - \beta^{2} - \frac{V_{in}}{I_{sw}V_{th}}\beta I_{sw}\right) + I_{b}^{2}\frac{V_{in}}{I_{sw}V_{th}}\beta^{2} - I_{sw}\beta = 0$$

$$I_{b}^{2} - \frac{I_{sw}}{\beta}I_{b} - \frac{V_{th}I_{sw}^{2}}{V_{in}\beta} = 0$$

The positive root gives the minimum power dissipation:

$$I_{b} = \frac{I_{sw}}{2\beta} + \sqrt{\frac{I_{sw}^{2}}{4\beta^{2}} + \frac{V_{th}I_{sw}^{2}}{V_{in}\beta}}$$

The equation indicates that he optimal  $I_b$  is approximately  $I_{sw}/\beta$  unless  $V_{in}/V_{th} < 4\beta$ . This makes intuitive sense. The only time efficiency increases by letting the switch saturate further is if the input voltage is small, because the P=IV loss will be less significant.

#### 4.2.4 Dynamic Dissipation

Power is also dissipated in the switch during transitions. Analytically determining dynamic dissipation is tedious because it is dependent on higher order effects. Simplifying the calculations as much as possible makes the problem tractable, but still moderately accurate.

The dynamic dissipation of the switch at the full current load is a good test case. The inductor acts like a current source, whereas the switch makes transitions from full current to no

current. The voltage on the switch will make the transition from the output voltage to the switch saturation voltage when the switch current is more than the inductor current. This implies that when the switch is turning on, the voltage on the switch will remain the same until the switch current has risen almost to its maximum. When the switch turns off, however, the voltage on the switch is increasing as the current is decreasing. More power is dissipated in the switch during the transition when the switch is turning on. The dominant factor in determining the dynamic dissipation is the dissipation while the switch is turning on.

$V_{out} = \text{output voltage (Volts)}$   $I_{smax} = \text{maximum switch current (Amps)}$  f = switching frequency (Hertz)  $\frac{dI_{sw}}{dt} = \text{rate of change of the switch during turn on (Amps per second)}$  $P_{dyn} = \text{power dissipated current turn on of the switch (Watts)}$

$$P_{dyn} = \frac{V_{out}}{2} \left(\frac{dI_{sw}}{dt}\right)^{-1} (I_{s\max})^2 f$$

The power dissipated while the voltage on the switch node is rising or falling is almost entirely captured by the amount of capacitance on the switch node. The capacitance on the switch node is dominated by the capacitance on the Schottky diode. Different Schottky diodes can have different capacitances, so the choice of Schottky diodes can be an important factor in efficiency. Using a larger Schottky diode than is necessary can cost several percentage points in efficiency. The easiest, and probably the best way to optimize efficiency is to swap in several manufacturers Schottky diodes on the bench, and to see which diode gives the best performance. It is also possible to estimate the dynamic losses due to the Schottky diode capacitance by examining the manufacturer's specifications.

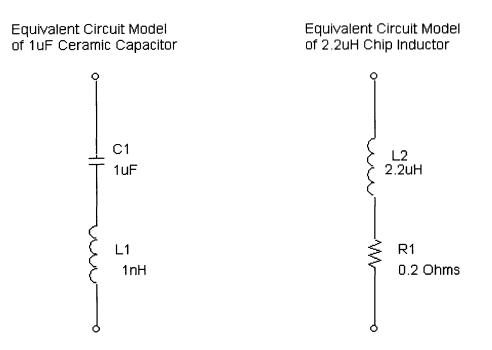

#### 4.2.5 Modeling of External Components

The previous discussion indicates the switch and the diode have less than ideal performance. The inductor and the capacitors also deviate from their expected performance. The inductor has a significant amount of resistance, which can be modeled as a series resistor. This resistance will lower the overall efficiency of the converter. The capacitance term in the inductor is usually small enough that it can be ignored. The output capacitor is ceramic, and has a nearly negligible amount of resistance and inductance. The series inductance in the capacitor is unfortunately still large enough to affect the performance of the circuit. The slew rates of the current through the capacitor are enough to excite the series inductance to a measurable voltage.  $L_{Cesl}$  = equivalent series inductance of the output capacitor (Henrys)  $\frac{dI_{sw}}{dt}$  = rate of change of current during switch transitions (Amps per second)  $V_{pip}$  = peak to peak voltage of the output noise (Volts)

$$V_{ptp} = 2L_{Cesl} \frac{dI_{sw}}{dt}$$

For example, an equivalent series inductance of 1nH and a switch current slew rate of 150mA/ns will lead to 350mV of peak to peak output noise.

Figure 4-2: Equivalent Circuit Models of Energy Storage Elements

# **5** Testing

Careful testing of the integrated circuit on the bench serves several purposes. The designer can gain a better familiarity with the operation of the circuit in a shorter time than with SPICE because many things are easier to test.<sup>17</sup> The manufactured circuit may deviate in performance from simulations, and those performance deviations provide a great opportunity to learn more about the integrated circuit. A careful evaluation on the bench helps avoid customer complaints and field failures.

<sup>&</sup>lt;sup>17</sup> A load step simulation in SPICE can take up to a day to simulate on a 700 MHz Pentium III, whereas a load step test on the bench can be set up and recorded within a couple minutes.

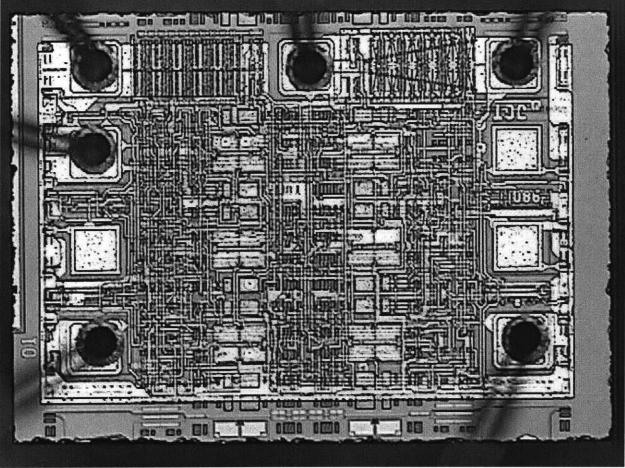

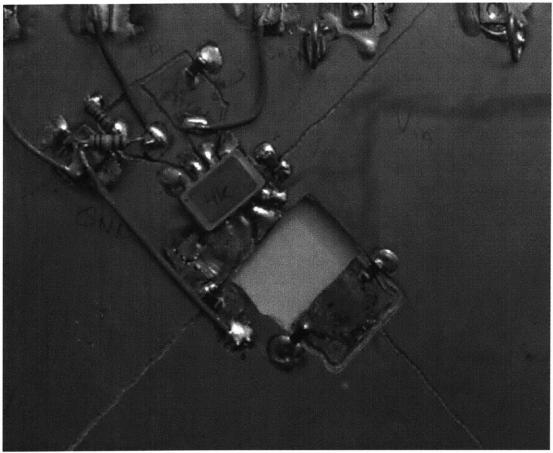

Figure 5-1: Die Photograph of the Integrated Circuit

# 5.1 Measurement Techniques for High Frequency DC/DC converters

As the frequency of operation of DC/DC converters increases, so will the sophistication of the measurement techniques required to characterize them. Several measurements of the converter required care and consideration. They are documented here.

# 5.1.1 Switch Current

The slew rate of the switch current significantly affects the performance of the circuit. Many people neglect to investigate this on the bench because it is not a simple measurement to take. This is not an excuse, however, especially because the measurement is usually straightforward. This project, however, required care in selecting instruments, and in board construction. The predicted current rise times were better than three nanoseconds. The author was only able to find one current probe that was capable of making such measurements. Using standard current probes would lead the engineer to think that his current rise times were far slower than they actually were. A simple calculation demonstrates the required probe bandwidth required to preserve the fidelity of a rise time measurement. Most 'scopes and probes are designed to have a Gaussian high frequency cutoff, but this can be approximated with a first order low pass filter.

$$H(s) = \frac{1}{\tau s + 1}$$

Using the Laplace transform, the step response in the time domain can be determined:

$$f(t) = u_{-1}(t)\left(1 - e^{-t/\tau}\right)$$

The 10% to 90% risetime of the filter can be determined using this equation.

$$f(t_{90\%}) = 0.9 = 1 - e^{-t_{90\%}/\tau}$$

$$t_{90\%} = \tau \ln 10$$

$$f(t_{10\%}) = 0.1 = 1 - e^{-t_{10\%}/\tau}$$

$$t_{10\%} = \tau \ln\left(\frac{10}{9}\right)$$

$$t_{10\% to 90\%} = t_{90\%} - t_{10\%} = \tau \ln 9$$

The risetime is therefore inversely related to the bandwidth or  $f_{-3dB}$  of the current probe:

$$f_{3dB} = \frac{1}{2\pi\tau} = \frac{\ln 9}{2\pi t_{10\%to90\%}}$$

$$t_{10\%to90\%} = \frac{\ln 9}{2\pi f_{3dB}} \approx \frac{0.35}{f_{3dB}}$$

In order to preserve the fidelity of a signal with a 2ns risetime, a current probe with at least 175MHz of bandwidth is required. The standard bench AC current probe from Tektronix, the P6022, has a high frequency bandwidth of 120MHz. Using this current probe leads to erroneous results. The Tektronix CT-1 has a bandwidth of 1GHz, however, and does the trick.

Board construction is also critical for this measurement. The inductance must be minimized in the switch current loop, so a custom board was built out of copper clad for this circuit. The current probe (not pictured) is placed through a hole drilled out of the center of the board, minimizing the loop through which the switch current must travel. Even this small loop adds enough inductance to corrupt the switch current waveform. A piece of copper tape (not pictured) was carefully threaded through the hole in the current probe and soldered to two ends of the board to bridge the contacts.

Figure 5-2: Switch Current Measurement Board

The rise and fall times should be faster than the 3ns that was measured, since the extra inductance added by the copper tape retarded the current slew rate. This measurement was taken when the part was forced into current limit. Switching regulators in equilibrium have a certain amount of phase jitter. The part is out of equilibrium when it is in current limit, and the phase jitter disappears. This gives a better look at the current edges and the rise and fall times.

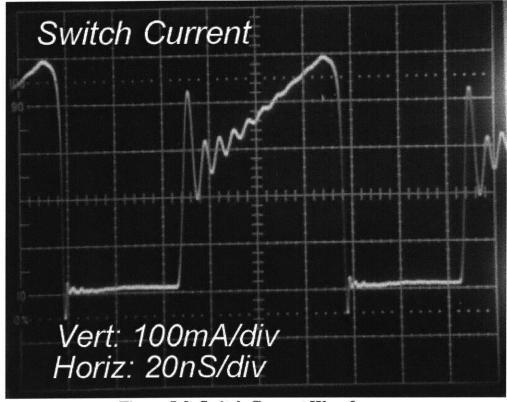

Figure 5-3: Switch Current Waveform

The switch current rings because of the added inductance from the current sensing loop. The switch current rise and fall times are fast enough that it is difficult to measure them merely by looking at the full cycle waveform. Zooming in on the rising and falling edge of the waveform shows better resolution.

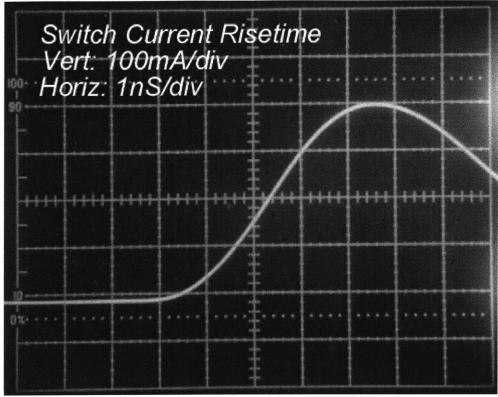

**Figure 5-4: Switch Current Risetime**

The switch current 10% to 90% risetime is better than 3ns, even with the added inductance from the current sensing loop.

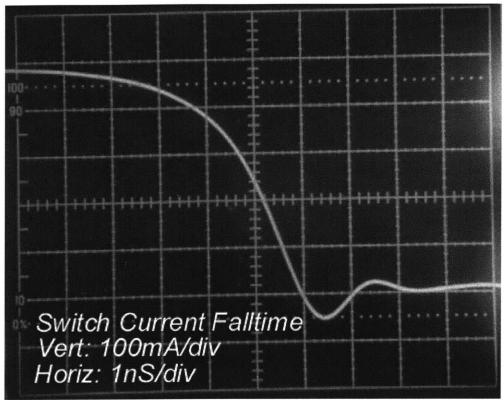

**Figure 5-5: Switch Current Falltime**

The switch current 90% to 10% falltime is also better than three nanoseconds. Knowing the rise and fall times of the switch current permits calculation of the dynamic dissipation.

# 5.1.2 Output Noise<sup>18</sup>

Getting an accurate look at the output noise of the converter takes a great deal of care. The high current and voltage slew rates of the converter generates radiated fields. These fields can corrupt test equipment without proper shielding. The signal also has very fast edges, so the measurement equipment must be able to detect very high frequency signals. The measuring device also must be properly terminated; otherwise, the signal will be corrupted due to transmission line effects.

<sup>&</sup>lt;sup>18</sup> The author refers to unwanted output signals as noise. The classic meaning of noise implies a signal lacking coherence, and is due to the natural properties of resistors and PN junctions, for example.

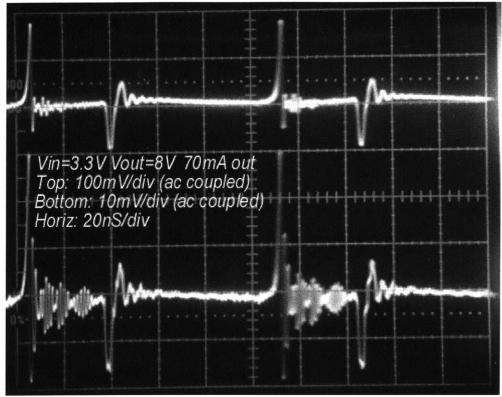

Figure 5-6: Top Trace – Output Noise, Bottom Trace – Filtered Output Noise. Note the change in scale. The scale for the top trace is 10x the scale of the bottom trace

The upper trace is a picture of the unfiltered output noise. The output noise is large, nearly 300mV peak to peak. This could prevent the converter from being usable in some applications. Slowing the current and voltage slew rates will decrease the output noise, but it will also decrease the efficiency because of the increased dynamic dissipation. There is an indirect relation between the efficiency of the converter and the output noise.

The output noise could also scare off potential customers, even though it should not be a problem in their application circuits. Since most of the output noise is due to high frequency content, it is an easy task to eliminate the noise. A small length of trace will have enough inductance that when connected to a capacitor it will form a second order filter. Since the boost converter is usually driving a microprocessor, there is often a second capacitor.<sup>19</sup> The lower

<sup>&</sup>lt;sup>19</sup> Most microprocessor manufacturers specify a required number of capacitors that must be closely coupled to the power pins.

'scope trace in the above picture of output noise is filtered by a small amount of board trace, and is greatly reduced in magnitude. Therefore, this high level of output noise should not pose any problems to the microprocessor.

The possibility that output noise violates any FCC regulations, or if output noise would cause any problems with a microprocessor warrants further investigation.

## 5.2 Performance in the Application Circuits

# 5.2.1 Efficiency

After the circuit was manufactured, a board was built and the performance was evaluated. The results were pleasing, because they were extremely close to simulations. Unfortunately, what was expected was not so spectacular. In particular, due to time constraints it was not possible to make the switch as large as was needed. The on resistance of the switch was rather large, on the order of two ohms, and led to efficiency that was underwhelming.

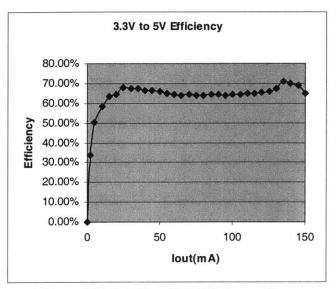

Figure 5-7: 3.3V to 5V Efficiency Curve

The efficiency is worse for lower output current because of the high quiescent current of the converter. For larger output currents, the losses are dominated by dissipation in the switch.

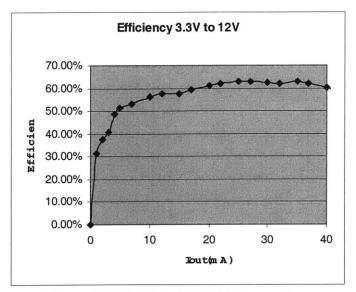

Figure 5-8: 3.3V to 12V Efficiency Curve

The efficiency is lower for the higher output voltage because the duty cycle of the converter is larger. Current is passing through the switch for a greater percentage of switching cycle, and more energy is lost in the on resistance of the switch. The converter delivers less output current because the switch current is proportionally higher for higher duty cycles. The converter is only rated for a certain amount of switch current. Once the switch current exceeds the current limit, the output falls out of regulation.

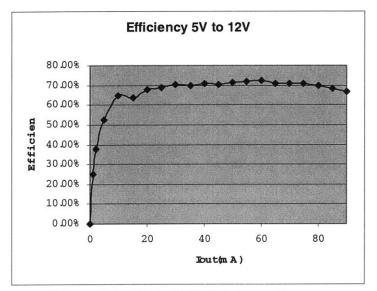

Figure 5-9: 5V to 12V Efficiency Curve

The efficiency and maximum output current is better for the 5V to 12V and 3.3V to 8V conversions because the converter is operating at a lower duty cycle.

Figure 5-10: 3.3V to 8.0V Efficiency Curve

An another common application for a monolithic boost converter is the SEPIC configuration. This allows output voltages above and below the input voltage. A SEPIC converter also provides short circuit protection, since there is no direct connection from the input to the output.

### Figure 5-11: Circuit Diagram of a SEPIC Converter

A typical application for the SEPIC converter is for use with a lithium-ion battery. The rated voltage for a lithium-ion battery can vary from as low as 2.5V to as high as 4.2V. If the desired output voltage is 3.3V, then the converter must be able to step up or step down the output voltage. The SEPIC converter is one of the few converter types that can do this.

Figure 5-12: Efficiency Curves for 3.3V output SEPIC converter

Unfortunately, the efficiency for a SEPIC converter is significantly lower than for its direct converter counterparts, since there is more resistance in the current path, and more energy is being dissipated in the greater amount of parasitic capacitance.

# 5.2.2 Load Transient

A critical test for the circuit is a load step. The circuit must be able to regulate the output voltage during a load transient. Figure 5-13 shows the change in output voltage when the load steps from a small load to a maximum load. The circuit regulates the output voltage and recovers quickly.

**Figure 5-13: Load Step Transient**

The step response illustrates the loop dynamics of the system. There is about a 20% overshoot. For a second order system a 20% overshot indicates fifty-five degrees of phase margin [14].

The change in the output voltage dependent on load is due to the change open loop gain of the circuit. The load resistance determines the open loop gain of the circuit, and a change in load resistance, such as a load step, will result in a small change in the output voltage. Since the open loop gain is large, the output voltage remains well within the specified bounds.

Testing the load transient provides ample opportunity to make a grievous testing error. The author initially tested the load transient on a circuit using a ceramic input capacitor. The resulting ringing on the input fed through to the output, and gives a waveform that appears as a poorly compensated loop. Replacing the ceramic input capacitor with tantalum capacitor increases the damping at the input. The load step transient then behaves as shown in Figure 5-13.

Figure 5-14: Poorly Bypassed Load Step Transient

# 5.3 Specifications

Most of the specifications were tested over the operating temperature ranges, and over the input voltage ranges. There were no surprises. The circuit performed similarly to SPICE simulations.

Figure 5-15: Quiescent Current over Supply Voltage

The quiescent current of the circuit increases with supply voltage. Although this is undesirable, not worrying about the supply dependence of the quiescent current allows simple circuit design.

Figure 5-16: On Voltage of the Switch over Supply Voltage

The change of the on voltage of the switch over supply voltage is due to the design of the switch driver circuitry and improves the efficiency of the converter at higher input voltages.

Figure 5-17: FB Pin Bias Current over Supply Voltage

The reason the FB pin bias current decreases with supply voltage is relatively

complicated. It is due to supply dependence of several of the circuits in the feedback network.

The change is quite small and should not affect the performance of the circuit in an application.

Figure 5-18: Oscillator Frequency over Supply Voltage

The bias current for the oscillator increases with voltage and increases the frequency of the oscillator. The change is relatively minor and should not affect the performance of the circuit in an application.

Figure 5-19: Maximum Duty Cycle over Supply Voltage

The greater quiescent current at higher voltages improves the speed of operation of the comparator and increases the maximum duty cycle. This is the exact opposite of what is desired, but ends up not mattering. The maximum voltage allowed on the switch is quite low, and the maximum duty cycle should not be a problem at any input voltage.

Figure 5-20: FB Pin Voltage over Temperature

The voltage at the FB pin remains relatively stable over temperature. The voltage could have a little more CTAT component to it. It remains within +/- 1% of nominal over the full temperature range.

Figure 5-21: Supply Current over Temperature

The quiescent current decreases at higher temperatures due to design. Since the beta of the driver transistors increase with temperature, they require less quiescent current. The current falls off at lower temperatures due to higher order effects of the devices in the integrated circuit.

Figure 5-22: Oscillator Frequency over Temperature

The frequency of the oscillator remains relatively stable over temperature. The temperature stays within +/- 4% of the nominal frequency.