# A Low-Power Reconfigurable Analog-to-Digital Converter

by

### **Kush Gulati**

B.E., Electronics and Communication Engineering, Delhi Institute of Technology, New Delhi (1993) M.S., Electrical Engineering and Computer Science, Vanderbilt University, Nashville (1995)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

### **Doctor of Philosophy**

at the

### **Massachusetts Institute of Technology**

June 2001

© 2001 Massachusetts Institute of Technology

| Signature of Author | Department of Electrical Engineering and Computer Science |

|---------------------|-----------------------------------------------------------|

|                     | April 25, 2001                                            |

| Certified by        |                                                           |

|                     | Hae-Seung (Harry) Lee                                     |

|                     | Professor of Electrical Engineering and Computer Science  |

|                     | Thesis Supervisor                                         |

|                     |                                                           |

| Accepted by         |                                                           |

|                     | Arthur C. Smith                                           |

|                     | Chair, Department Committee on SANTHUSE SUNSTRIVE         |

|                     | NOV 0 1 2001                                              |

|                     | BARKER                                                    |

**LIBRARIES**

### A Low-Power Reconfigurable Analog-to Digital Converter

by

#### **Kush Gulati**

Submitted to the Department of Electrical Engineering and Computer Science in August, 2001 in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

#### **ABSTRACT**

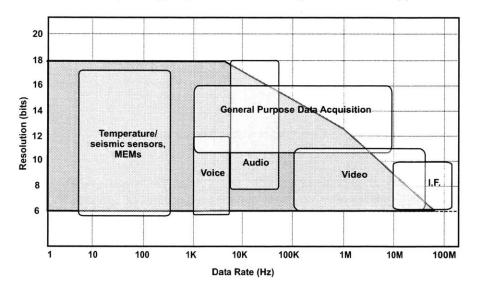

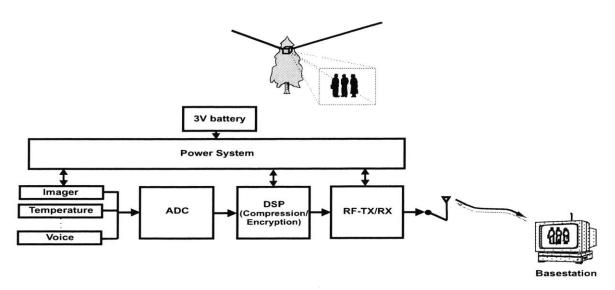

This thesis presents the concept, theory and design of a low power CMOS analog-to-digital converter that can digitize signals over a wide range of bandwidth and resolution with adaptive power consumption. The converter achieves the wide operating range by reconfiguring (1) its architecture between pipeline and delta-sigma modes (2) by varying its circuit parameters such as size of capacitors, length of pipeline, oversampling ratio, among others and (3) by varying the bias currents of the opamps in proportion with converter sampling frequency, accomplished through the use of a phase-locked loop. Target input signals for this ADC include high frequency and moderate resolution signals such as video and low I.F. in radio Receivers, low frequency and high resolution signals from seismic sensors and MEMs devices, and others that fall in between these extremes such as audio, voice and general purpose data-acquisition.

This converter also incorporates several power reducing features such as thermal noise limited design, global converter chopping in the pipeline mode, opamp scaling, opamp sharing between consecutive stages in the pipeline mode, an opamp chopping technique in the delta-sigma mode, and other design techniques. The opamp chopping technique achieves faster closed-loop settling time and lower thermal noise than conventional design.

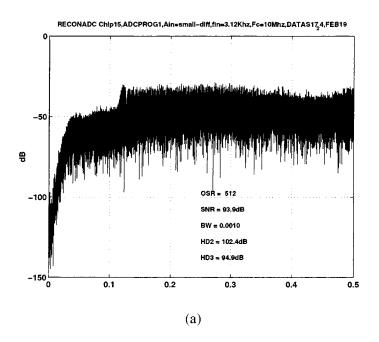

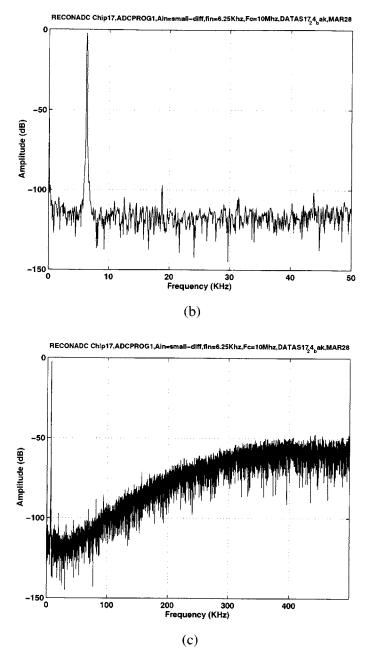

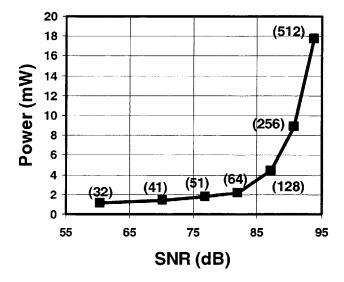

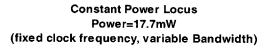

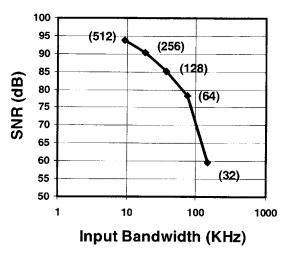

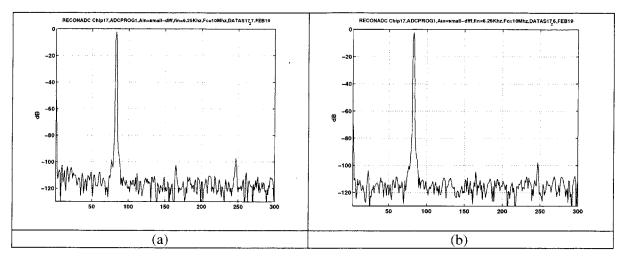

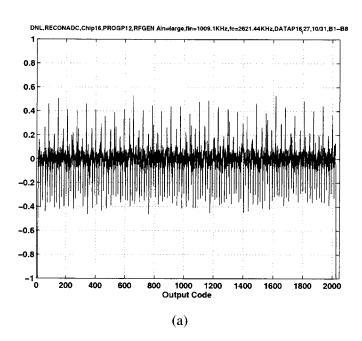

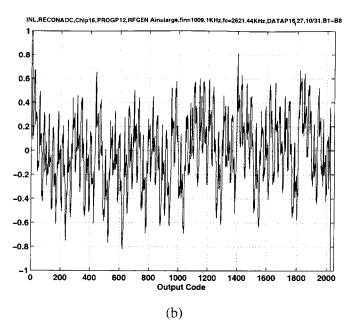

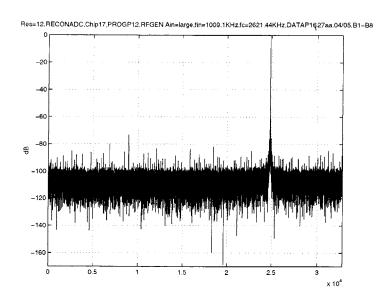

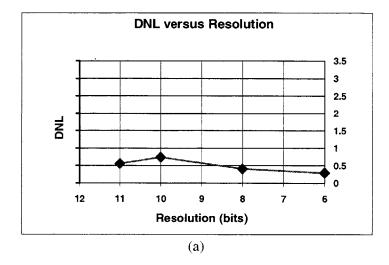

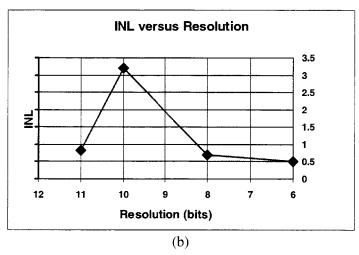

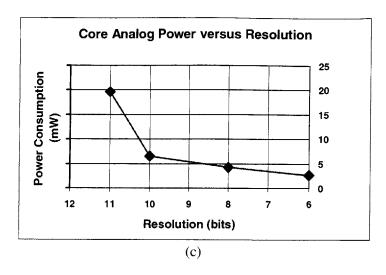

At a converter power supply at 3.3V, the converter achieves a bandwidth range of 0–10MHz over a resolution range of 6–16 bits, and parameter reconfiguration time of 12 clock cycles. Its PLL lock range is measured at 20KHz to 40MHz. In the delta-sigma mode, it achieves a maximum SNR of 94dB and second and third harmonic distortions of 102dB and 95dB, respectively at 10MHz clock frequency, 9.4KHz bandwidth, and 17.6mW power. In the pipeline mode, it achieves a maximum DNL and INL of +/-0.55LSBs and +/-0.82LSBs, respectively, at 11-bits of resolution, at a clock frequency of 2.6MHz and 1MHz tone with 24.6mW of power.

### Thesis Supervisor:

Hae-Seung (Harry) Lee Professor of Electrical Engineering and Computer Science

. 4

# Acknowledgements

At the end of my PhD program, I would like to recognize and acknowledge all those who offered me support during the last few years.

First and foremost, I would like to offer my sincerest gratitude to my advisor, Professor Hae-Seung Lee, for his sterling guidance through the duration of this project. His deep technical insight, technical know-how, creativity and practical bent of mind have benefited me personally and this project immensely. His belief that anything is possible with circuits has injected in me an enhanced sense of optimism in this area. I thank him for his patience and support during these years as we explored new circuit ideas. I also thank him for financial support throughout my program.

I also want to extend a special thank-you to Professor Charlie Sodini for always being a source of support and encouragement during the course of the low-power wireless sensor project and later. I really appreciate his belief in me through my Ph.D. His technical insights helped significantly in the evolution of this chip. I would also like to deeply thank Dr. Brian Brandt of Maxim Integrated Products for his advice, both technical and otherwise. It has been an honor to have been associated with him. I would like to thank both Professor Sodini and Dr. Brandt for having served on my thesis committee and their valuable feedback on this thesis. Professor Anantha Chandrakhasan of M.I.T. has also been a tremendous source of inspiration. I thank him for his strong support and encouragement in various forms.

Several people at Maxim Integrated products provided me assistance at different points in the execution of this chip. I especially thank Dr. Ted Tewksbury for providing me with the filters for testing the chip and other technical assistance, for connecting me up with other people at Maxim and for support and encouragement during my program. Dr. Andrew Karanicolas and Dr. Ben McCarrol of Maxim Integrated Products were also very helpful during the testing phase of the chip. I also thank John Newton of the Chelmsford division of Maxim for helpful advice towards the end of my program. In addition, I thank Dr. Paul Ferguson, Tom Barber, Dr. Jennifer Lloyd and Stacy Ho of Analog Devices, and D. Boisvert of National Semiconductor for their technical assistance. I also extend special thanks to Dr. Jim Goodman and Dr. Mike Perrott for help with a variety of issues – technical and otherwise.

Among my research group, I thank Ayman Shabra for being a great colleague and friend. I cherish the long circuit discussions we had late into the night. I am sure we will both look back at those times with nostalgia. Mark Peng has been a great person to work with. I have enjoyed working at close quarters with him and especially appreciate our discussions on circuit ideas. While I will always remember Mark Spaeth for his video games and apple computers, I will never forget the time when Mark helped me convert a Tektronix oscilloscope output to Tiff format after six hours of continuous work. Shortly before that, a Tektronix representative had told me it would take their best software person three days working continuously to do the same job! Mark Spaeth has been very helpful with several computer related issues. Andy Wang has been very good friend as well. I will remember the fun time we spent in Amsterdam. In addition, I thank Anh Pham, Tod Sepke, Lunal Khuon, John Fiorenza and Andrew Chen for making my time at the lab an enjoyable one. I will always look back fondly on all the dinners we went to. Also, I would like to thank Ginger Wang, Iliana Fujimori, Pablo Acosta, Don Hitko, Dan McMahill, and Susan Dacy, Andy Wei and Jim Fiorenza for contributing to the excitement at the MTL.

From my early years at MIT, many thanks go to Paul Yu and Vincent Peiris. They helped me tremendously as I adjusted to MIT. Thanks are also due to Jennifer Lloyd, David Martin and Jung-Wook Yang for several technical discussions that helped me immensely. Steve Decker, Joe Lutsky and Jeff

Gealow were helpful with Cadence and HSPICE. I also thank Siva Narendra for having been a good friend. Thanks are also due to Priti Naik for making my stay at MIT very enjoyable.

I extend my thanks to the computer staff at MTL who have helped me tremendously on numerous occasions. In specific I would like to thank Fletch (Myron Freeman), Mike Hobbs, Thomas Wingard, Thomas Lohman, and Ralph Nevins. Professor Boning has also extended a helping hand on computer related issues several times. I also thank Russ Cyr and Dr. Amit Sinha for helpful tips on the formatting of this document. Their time is appreciated.

Carolyn Zaccaria has provided superb administrative support to our group. I thank her for having been so kind and patient as I have searched for many a receipt after my conference trips. Debb Hodges-Pabón has also been extremely good about helping me at the various times I have needed her assistance. Marilyn Pierce and Monica Bell at the graduate student office have been amazingly helpful. I thank them too for having been very supportive on so many occasions. Thanks also go to Professor Arthur Smith for helping out on issues related to my Visa and completion of my Ph.D. Dean Daniel Ashbrook and Maria Brennan have been great people to work with at the International Students Office. MIT is indeed lucky to have such exceptional support staff.

I would like to also take this opportunity to thank Professor Lloyd W. Massengill of Vanderbilt University, Nashville, Tennessee. It was an honor being associated with his group during my Master's thesis. I thank him for recommending me to MIT. Another person I would like to thank is Professor David Allstot of the University of Washington, Seattle for helping me select a school for my Ph.D.

Among my friends, I would like to thank Mathew Varghese (MIT, 2001) for having been such a wonderful friend over since I came to Boston. Over these several years and many conversations (and heated debates) covering everything from MEMs and circuits to politics, start-ups and even god, we have learnt a lot and inspired each other. I thank his wife, Sharon Francis, for awesome dinners. I extend a special thanks to her for organizing a beautiful graduation party for me. Prerana Trehan, who I met only recently, has also been a great source of inspiration to me in the last few weeks of my program. I also thank Yihui Tang for having been a great friend. Sumit Roy and Deepa Iyer have been awesome friends since a long time and I cherish our friendship very much. Siddharth Dutta, Leifang Hu and Vivek Nadkarni have also been very good friends. My other friends I would like to thank are Nishi and Ashi Doshi, Smita Ghosh, Vaishali Joglekar, Ritwik Chatterjee, Bhavna Vasvani, Marie Kramer, and my housemates Natasha Bushueva and Arvind Subramanium for having made my life outside research very enjoyable.

My cousin Sanjay, his wife Maurine and their daughter Ilina deserve a special mention for having been my family away from home. They have inspired and influenced me in so many immeasurable ways – both material and otherwise. I thank them for the numerous vacations, dinners and parties they have invited me to, for the countless things I have borrowed from them, for helping me make hard decisions, and tremendous support and encouragement.

This thesis would not have happened had it not been for the love and support of my parents and sisters. I guess the 'science' stories that my dad used to tell me over dinner table when I was a kid did do something! My sisters, Abha and Priti have been great elder sisters, and have helped me find my way whenever I felt lost. I thank both my mother and father for having been an infinite source of inspiration; I also thank them for letting me choose my own career path. My family have influenced me in many wonderful ways; I dedicate this thesis to them.

This research was funded by DARPA under agreement DAAL-01-95-K-3526, fellowship from Maxim Integrated Products, Center for Integrated Circuits and Systems composed of the following companies:

Analog Devices, Compaq, IBM, Intersil, Lucent, Maxim Integrated Products, Multilink, National Semiconductor, Philips Research Co., Silicon Labs., Texas Instruments. The prototype reconfigurable converter was fabricated by TSMC.

# **Dedication**

To my family

# **Biography**

Kush Gulati was born in Nagpur, India in 1971. He received the B.E. degree in Electronics and Communication Engineering from Delhi Institute of Technology (now known as the Netaji Subhas Institute of Technology), Delhi, India in 1993 and M.S. degree in Electrical and Computer Engineering in 1995 from Vanderbilt University, Nashville, TN.

Between 1993 and 1995, he worked on circuit techniques for minimizing susceptibility of DRAMs to alpha particles and cosmic ions.

Since September, 1995 he has been with the M.I.T. Microsystems Technology Laboratories, working towards his Ph.D. in the area of analog circuit design. His current research interests include low-power, high-performance analog integrated circuit design.

# **Contents**

| 1 | INTRODUCTION                                            | 23 |

|---|---------------------------------------------------------|----|

| 2 | CONVENTIONAL CONVERTER DESIGN                           | 27 |

|   | 2.1 PIPELINE CONVERTER                                  | 27 |

|   | 2.1.1 Operation and Architecture                        |    |

|   | 2.1.2 Circuit Implementation.                           |    |

|   | 2.1.3 Non-idealities in Pipeline Converters             |    |

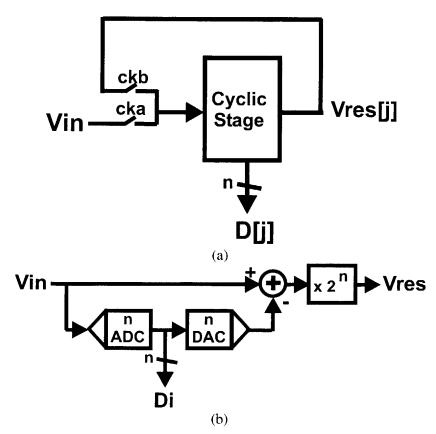

|   | 2.2 CYCLIC CONVERTER.                                   |    |

|   | 2.2.1 Operation and Architecture                        | 30 |

|   | 2.2.2 Circuit Implementation and Non-idealities         | 32 |

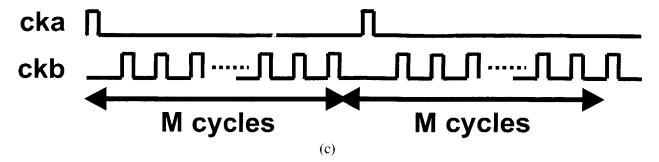

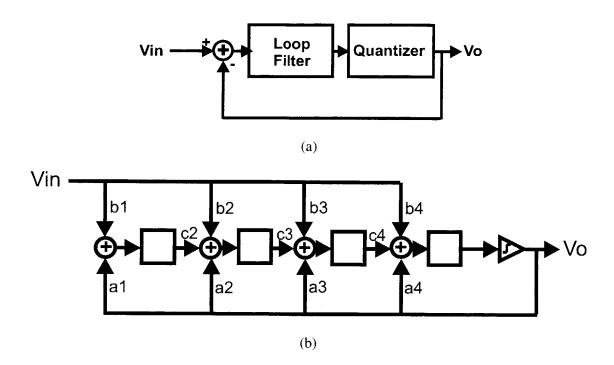

|   | 2.3 DELTA-SIGMA CONVERTER                               |    |

|   | 2.3.1 Operation and Architecture                        |    |

|   | 2.3.2 Circuit Implementation                            | 33 |

|   | 2.3.3 Non-idealities in Delta-Sigma Converters          |    |

| 3 | CONCEPT OF PROPOSED ADC                                 | 35 |

|   | 3.1 RECONFIGURATION METHODOLOGY                         |    |

|   | 3.2 SELECTION OF ARCHITECTURAL MODES                    | 35 |

| 4 | SYSTEM LEVEL ARCHITECTURE                               |    |

| 4 | 4.1 System Level Description of Converter               | 37 |

| 4 | 4.2 DESCRIPTION OF DATA CONVERTER BLOCK                 | 38 |

| 4 | 4.3 PIPELINE MODE ARCHITECTURE                          | 30 |

|   | 4.3.1 Offset Compensation in the Pipeline Mode          | 30 |

|   | 4.3.2 Opamp Scaling in the Pipeline Mode                | 40 |

|   | 4.3.3 Opamp Sharing in the Pipeline Mode                | 41 |

| 4 | 4.4 DELTA-SIGMA MODE ARCHITECTURE                       | 41 |

|   | 4.4.1 Offset Compensation in the Delta-Sigma Mode       | 42 |

|   | 4.4.2 Opamp Scaling in the Delta-Sigma Mode             | 42 |

| 4 | 4.5 PARAMETER RECONFIGURATION                           | 45 |

|   | 4.5.1 Parameter Reconfiguration in the Pipeline Mode    | 45 |

|   | 4.5.2 Parameter Reconfiguration in the Delta-Sigma Mode | 47 |

| 4 | 4.6 Summary                                             | 48 |

| 5 | ADC CIRCUIT IMPLEMENTATION                              | 49 |

| 4 | 5.1 Introduction                                        | 49 |

| 5 | 5.2 INTERACTION OF PRIMARY BLOCKS                       | 49 |

| 5 | 5.3 Main Reconfiguring Logic                            | 50 |

| 5 | 5.4 CLOCK GENERATOR                                     | 52 |

|   | 5.4.1 Non-overlapping two phase Clock generator         | 53 |

|   | 5.4.2 Digitally Tunable Multi-phase Clock generator     | 54 |

|   | 5.4.3 Clock Buffers                                     | 54 |

| 5 | 5.5 CONVERTER CORE                                      | 54 |

|   | 5.5.1 General Description of the Converter Core         | 54 |

|   | 5.5.2 Operational Amplifier Topology                    | 56 |

|   | 5.5.3 Switched-Capacitor Network                        | 61 |

|   | 5.5.4 Block Reconfiguration Logic                       | 67 |

|   | 5.5.5 Decision Block                                    |    |

|   | 5.5.6 Output Conditioning Block                         |    |

| 5 | 5.6 OUTPUT SIGNAL PROCESSING AND INTERFACE              | 72 |

|   | 5.6.1 Spatial Alignment of Digital Data                 |    |

| 5.6.2          | 1 0 0                                                              |     |

|----------------|--------------------------------------------------------------------|-----|

| 5.6.3          | 1 0                                                                |     |

| 5.7            | TESTING CONSIDERATIONS                                             | 74  |

|                | MIXED SIGNAL ISSUES                                                |     |

| 5.9            | SUMMARY                                                            | 7€  |

| 6 BAN          | DWIDTH RECONFIGURATION/PLL DESIGN                                  | 77  |

|                | Introduction                                                       |     |

| 6.2            | PRINCIPLE OF OPERATION OF PLL                                      | 78  |

| 6.2.1          |                                                                    | 78  |

| 6.2.2          | ,, , , , , , , , , , , , , , , , , , ,                             | 79  |

|                | VOLTAGE CONTROLLED OSCILLATOR THEORY AND DESIGN                    | 79  |

| 6.4            | PLL CIRCUIT IMPLEMENTATION                                         |     |

| 6.4.1          | - · r - · · · - · · · · · · · · · · · ·                            |     |

| 6.4.2          | 0                                                                  | 92  |

| 6.4.3          | 1                                                                  |     |

| 6.4.4          |                                                                    |     |

| 6.4.5          | 0 1                                                                |     |

| 6.4.6          | 0                                                                  |     |

|                | PLL DYNAMICS                                                       |     |

| 6.6            | Summary                                                            | 103 |

| 7 TEST         | I SYSTEM AND EXPERIMENTAL CHARACTERIZATION                         | 105 |

|                |                                                                    |     |

| 7.1            | Introduction                                                       | 105 |

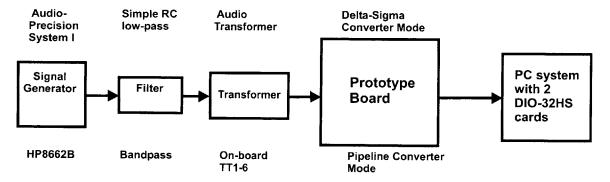

|                | TEST AND CHARACTERIZATION SYSTEM                                   |     |

| 7.2.1          |                                                                    | 105 |

| 7.2.2<br>7.2.3 | 71 0                                                               | 106 |

|                | 71 0 7                                                             | 109 |

|                | TEST AND CHARACTERIZATION EXPERIMENTS                              |     |

| 7.3.1<br>7.3.2 | Histogram Code Density Test                                        | 110 |

| 7.3.2          | Zero-input Test                                                    |     |

| 7.3.3<br>7.3.4 | FFT Test                                                           |     |

| 7.3.4          | Envelope Test                                                      |     |

|                | Signature Analysis EXPERIMENTAL RESULTS                            |     |

| 7.4.1          | Delta-Sigma Mode                                                   |     |

| 7.4.2          | Pipeline Mode                                                      |     |

| 7.4.3          | PLL Measurements                                                   |     |

| 7.4.4          | Comparison of the proposed converter to existing custom solutions. |     |

| 7.4.5          | Summary of Experimental Results                                    |     |

|                | FUTURE IMPROVEMENTS OF TEST SYSTEM                                 | 129 |

|                |                                                                    |     |

|                | CLUSIONS AND FUTURE WORK                                           |     |

| 8.1            | SUMMARY                                                            | 129 |

| 8.2 F          | FUTURE WORK FOR THE NEXT GENERATION RECONFIGURABLE CONVERTER       | 130 |

| 8.2.1          | Enhancements in the Delta-Sigma Mode                               | 130 |

| 8.2.2          | Enhancements in the Pipeline Mode                                  | 130 |

| 8.2.3          | Additional Architectures                                           | 130 |

| APPENDI        | X A: A HIGH-SWING CMOS TELESCOPIC OPERATIONAL AMPLIFIER            | 133 |

| A.1 I          | NTRODUCTION                                                        | 133 |

|                | IGH SWING OPERATIONAL AMPLIFIER                                    |     |

| A.2.1          | Importance of High Swing in Operational Amplifiers                 |     |

| A.2.2          | Methodology for Improved Swing                                     | 136 |

| A.2.3          | Regulated Cascode for Recovering Gain                              | 137 |

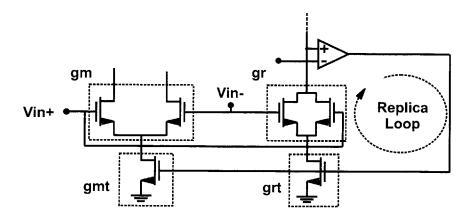

| A.2.4          | Concept of Replica-Tail Feedback Technique                         | 138 |

| A.3 IM              | IPLEMENTATION OF OPAMP                                              | 139       |

|---------------------|---------------------------------------------------------------------|-----------|

| A.3.1               | Circuit Description                                                 |           |

| A.3.2               | Optimization of Power Consumption and Area                          | 140       |

| A.3.3               | Effect of Mismatch                                                  | 141       |

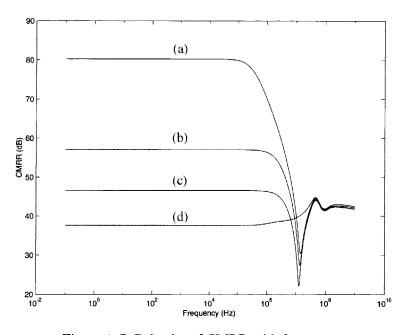

| A.3.4               | High Frequency Behavior of CMRR                                     |           |

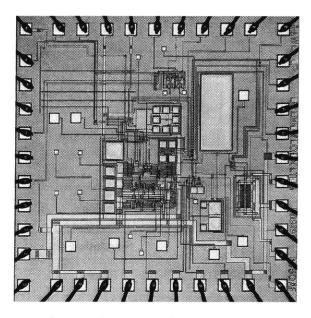

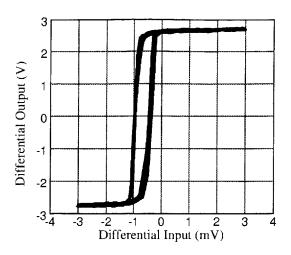

| A.4 Ex              | ØERIMENTAL RESULTS                                                  | 143       |

|                     | ONCLUSIONS                                                          |           |

| A.6 Aı              | PPENDIX                                                             | 147       |

| A.6.1               | Case A: Mismatch factor $\Delta = 0$                                | 150       |

| A.6.2               | Case B: Mismatch factor $\Delta >> \frac{1}{A_{loop}}$              |           |

| APPENDIX<br>MEASURE | B: SIGNATURE ANALYSIS – IDENTIFYING PIPELINE CONVERTER ER           | RORS FROM |

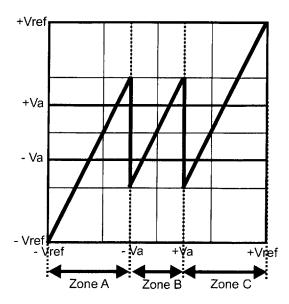

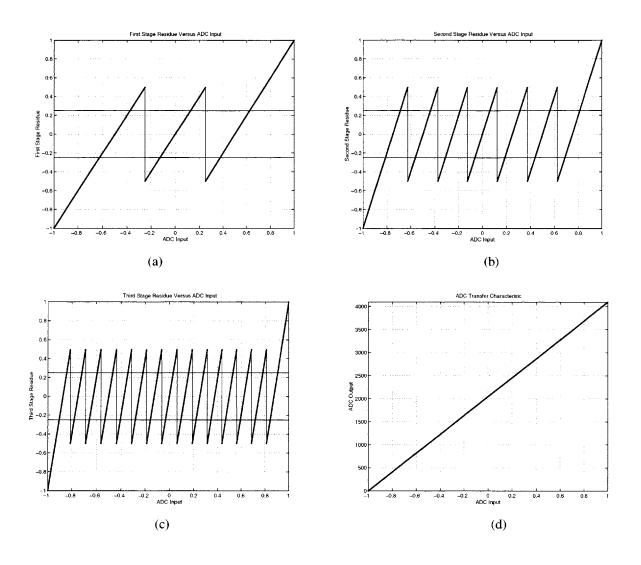

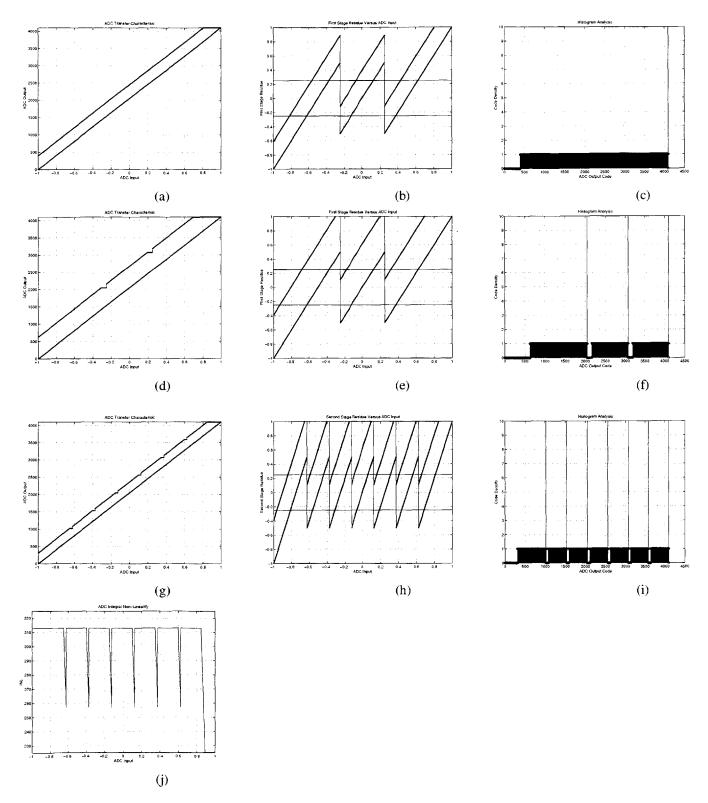

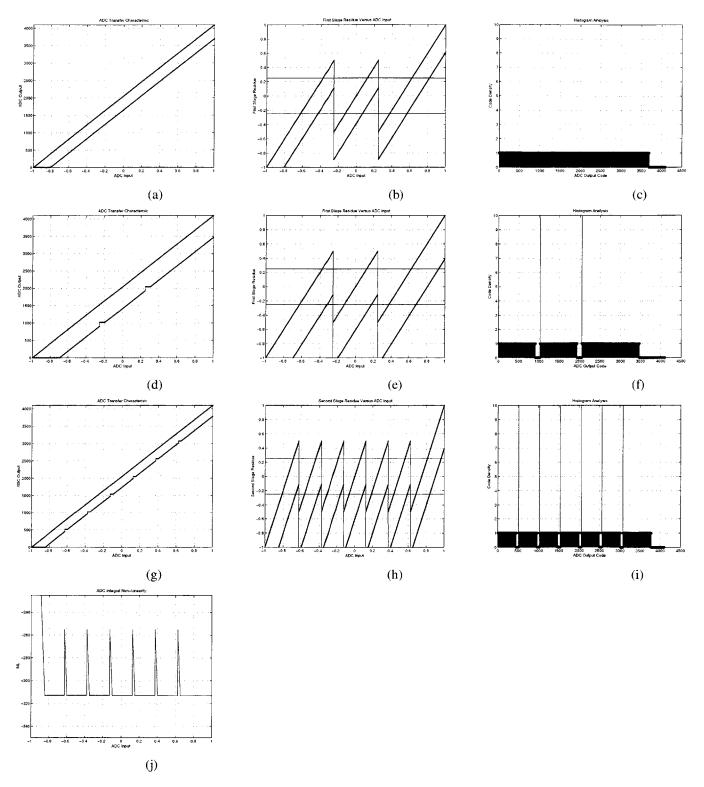

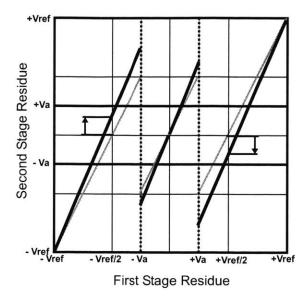

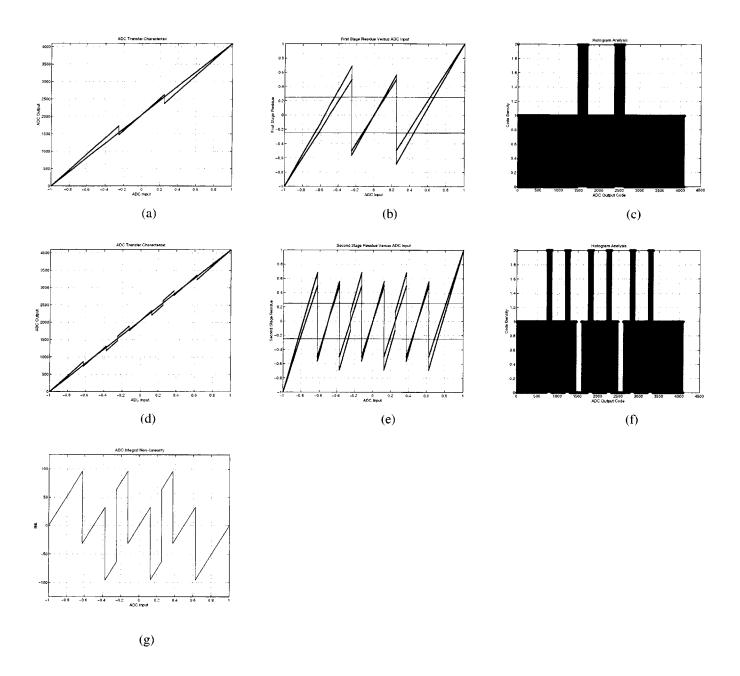

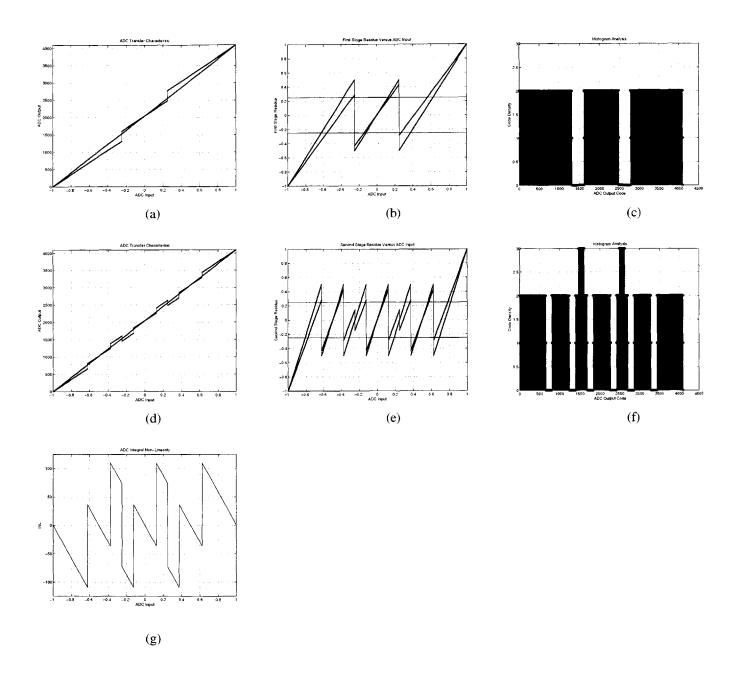

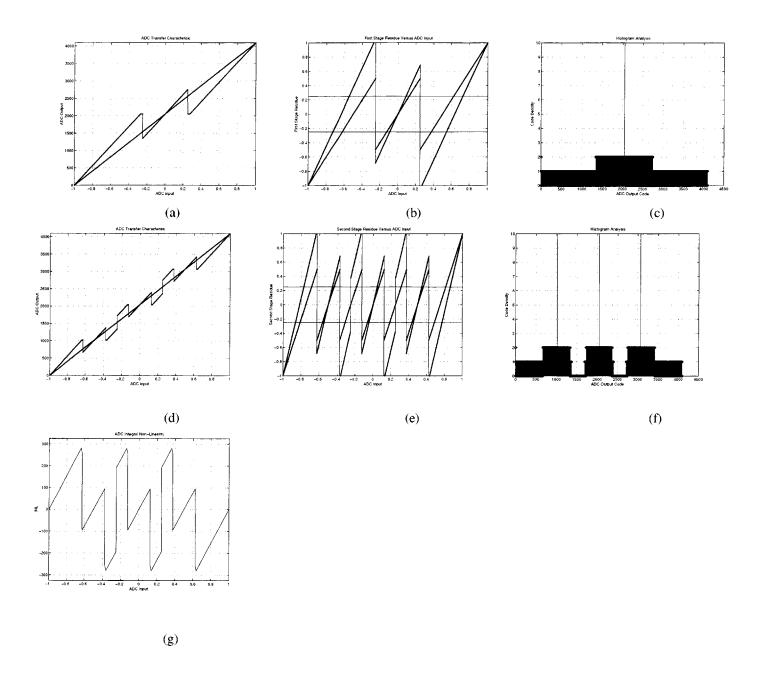

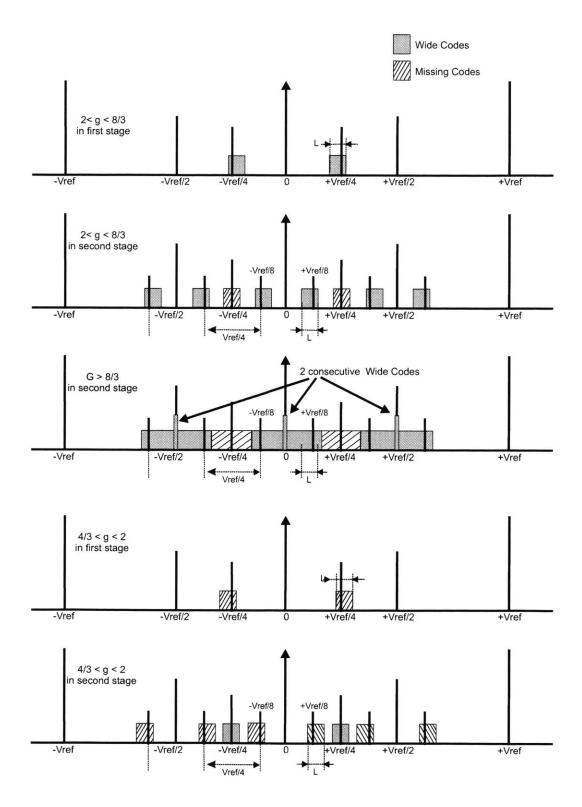

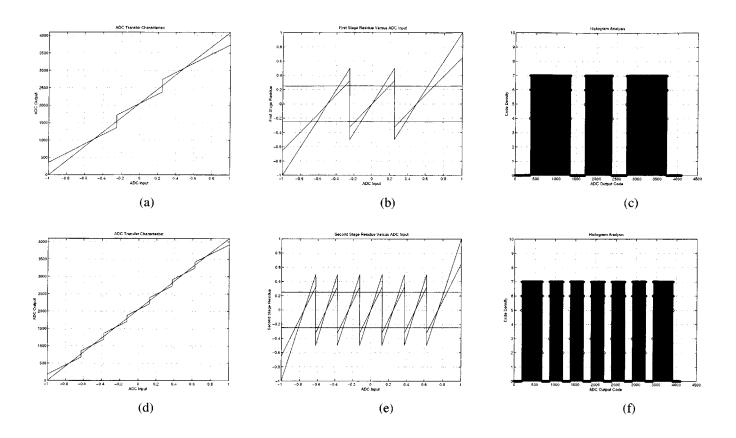

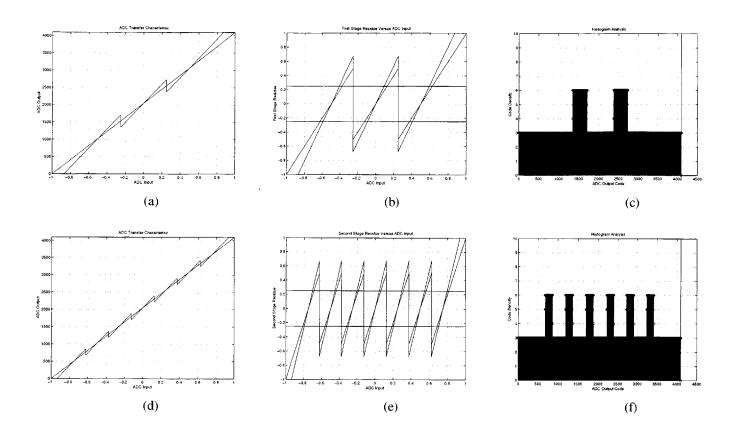

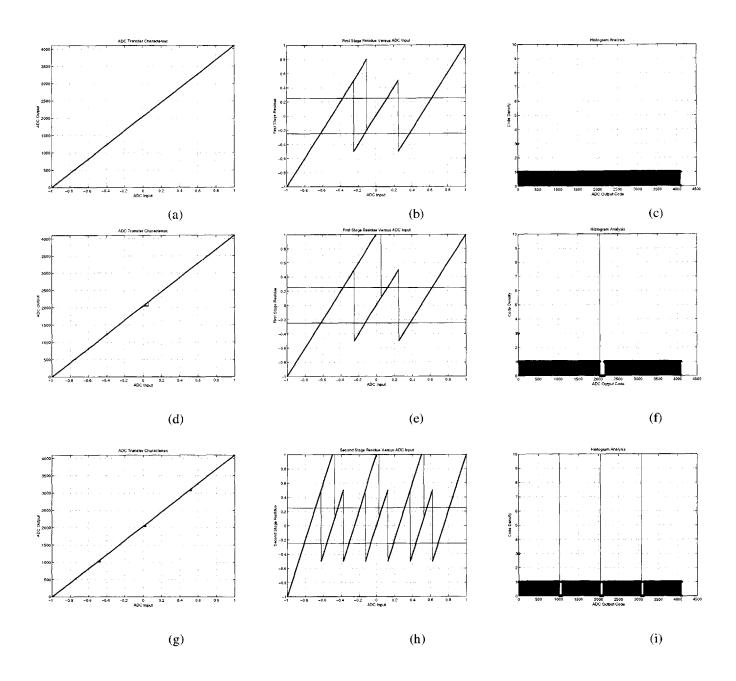

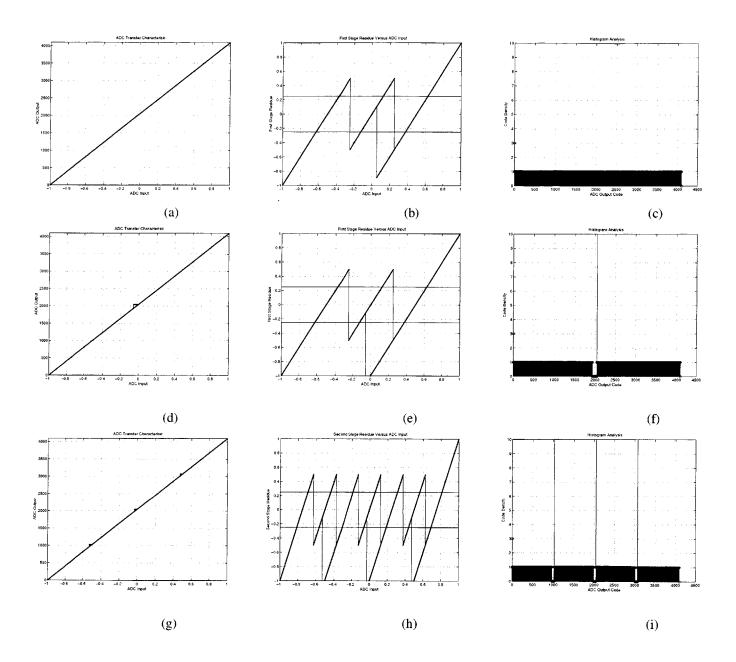

| B.1 Ar              | NALYSIS OF PIPELINE CONVERTER RESIDUE PLOTS                         | 151       |

| B.2 Er              | FECT OF IMPORTANT NON-IDEALITIES                                    | 155       |

| B.2.1               | Stage offset                                                        |           |

| B.2.2               | Stage Gain Error                                                    |           |

| B.2.3               | Stage Transition Shift                                              |           |

| B.2.4               | Non-linear variation of stage transfer characteristic               |           |

| APPENDIX            | C: TROUBLESHOOTING - MINIMIZING TESTING ARTIFACTS                   |           |

| APPENDIX            | D: TROUBLESHOOTING - MINIMIZING TEST SETUP NOISE                    | 191       |

| D.1 Ex              | TERNAL INTERFERENCE AND ITS MINIMIZATION                            | 191       |

| D.1.1               | Noise coupling in Audio Precision System-I                          |           |

| D.1.2               | Shielding                                                           | 193       |

| D.1.3               | The use of input transformer                                        | 193       |

| D.1.4               | Position of Computer CPU                                            | 193       |

| D.2 PR              | INTED CIRCUIT BOARD NOISE AND ITS MINIMIZATION                      | 193       |

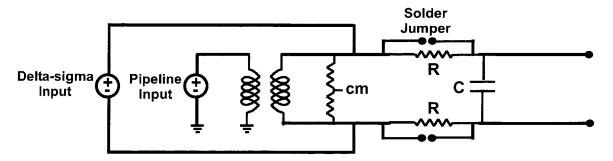

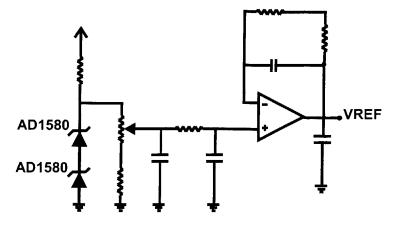

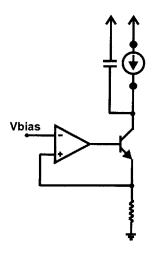

| D.2.1               | Noise on the input common-mode reference line of the line receivers |           |

| D.2.2               | Glitching noise on the converter outputs                            | 194       |

| APPENDIX            | E: EXACT SLEWING TIME EXPRESSION IN AN AMPLIFIER                    | 195       |

# **List of Figures**

| Figure 1-1: Application Space                                                                          | . 23       |

|--------------------------------------------------------------------------------------------------------|------------|

| Figure 1-2: Universal Wireless Sensor Illustration.                                                    | . 24       |

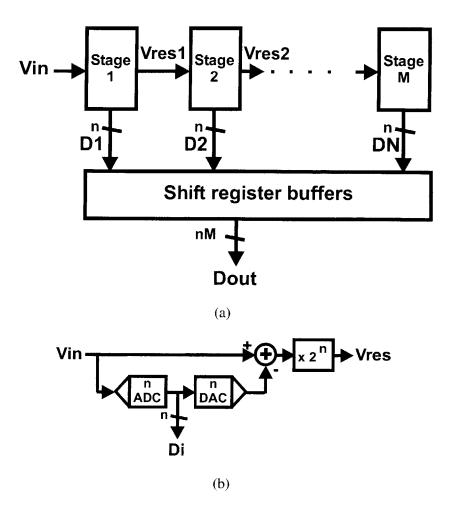

| Figure 2-1: Generalized pipeline architecture.                                                         | . 28       |

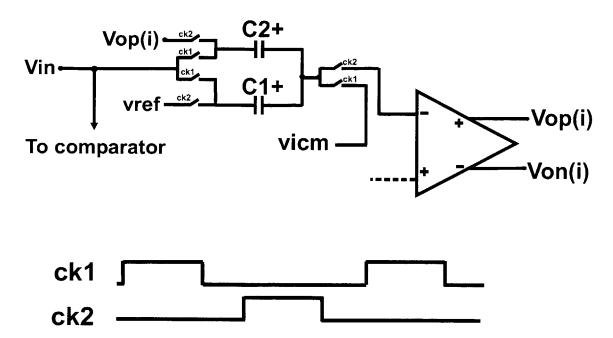

| Figure 2-2: Switched-capacitor implementation of a single stage of the pipeline architecture           |            |

| Figure 2-3: Residue plot of a single pipeline stage with digital error correction.                     |            |

| Figure 2-4: Architecture of n-bit/stage cyclic converter. (a) Top-level block diagram. (b) Stage block |            |

| diagram. (c) Clock scheme.                                                                             | . 32       |

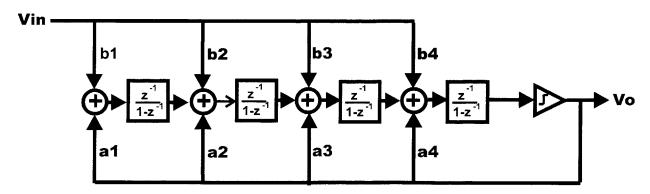

| Figure 2-5: Architecture of delta-sigma converter.                                                     |            |

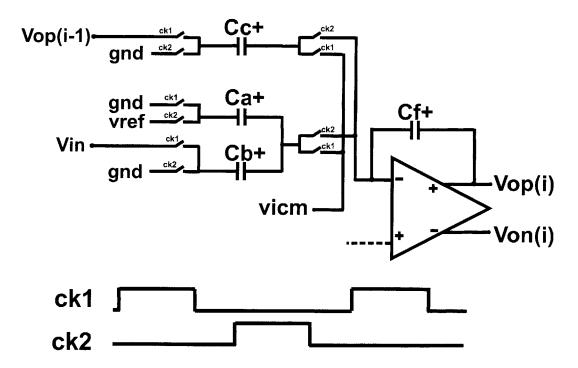

| Figure 2-6: Switched-capacitor circuit schematic of one stage of the delta-sigma converter             |            |

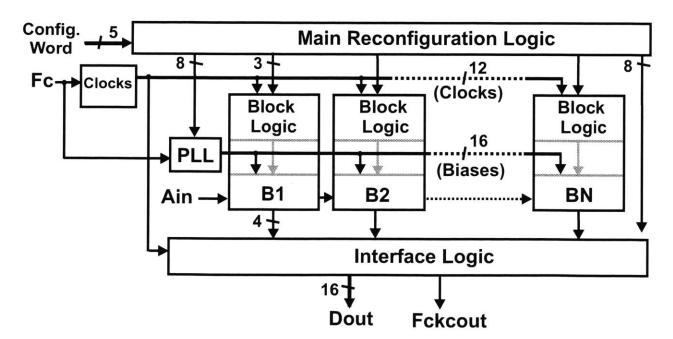

| Figure 4-1: Converter Architecture.                                                                    | . 31       |

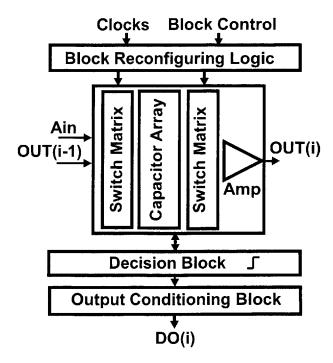

| Figure 4-2: Structure of basic building block.                                                         |            |

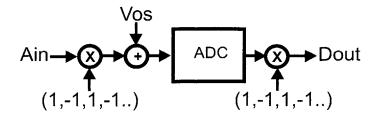

| Figure 4-3: Illustration of Global Chopping of ADC                                                     |            |

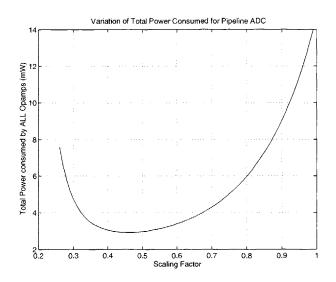

| Figure 4-4: Total ADC Analog Power Consumption versus Inter-stage scale factor.                        |            |

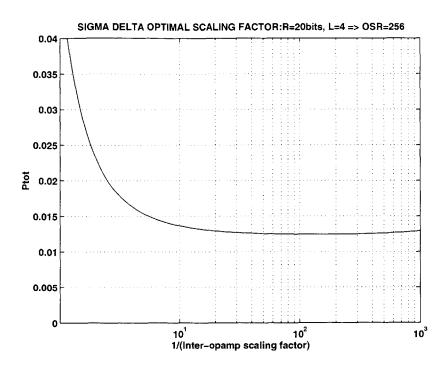

| Figure 4-5: Variation of total modulator power consumption with scale factor for an oversampling ratio |            |

| of 256                                                                                                 |            |

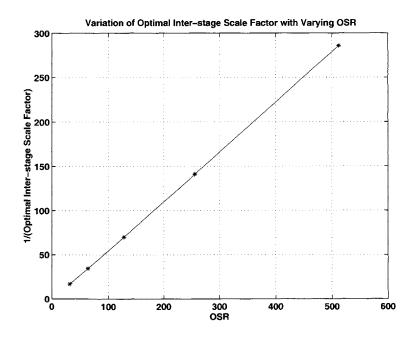

| Figure 4-6: Variation of optimal stage scale factor with oversampling ratio.                           |            |

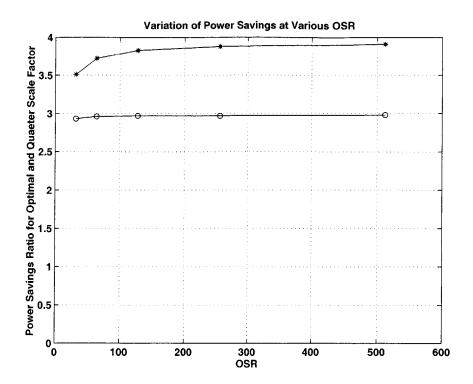

| Figure 4-7: Variation of power savings due to scaling at various oversampling ratio. The curve marked  |            |

| by asterix (*) corresponds to the ratio of the modulator power without any scaling applied to          |            |

| the minimum power that can be obtained when the stages are scaled by the optimal scale                 |            |

| factor (from Figure 4-6). The curve marked by circles (o) corresponds to the ratio of the              |            |

| modulator power without any scaling applied to the power obtained when the stages are                  |            |

| scaled by a fixed scaling factor of 0.25, as in this design.                                           | 44         |

| Figure 4-8: Architecture of converter in delta-sigma mode                                              | 44         |

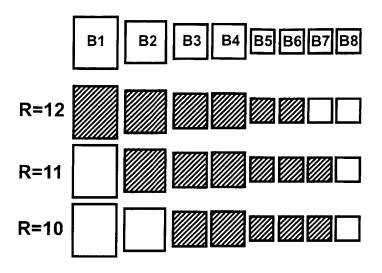

| Figure 4-9: Resolution Variation in Pipeline Mode                                                      |            |

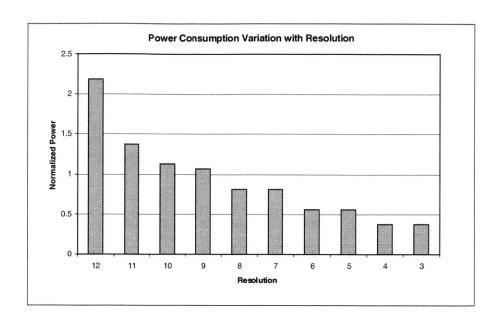

| Figure 4-10: Power Consumption Variation with changing resolution in the Pipeline Mode                 |            |

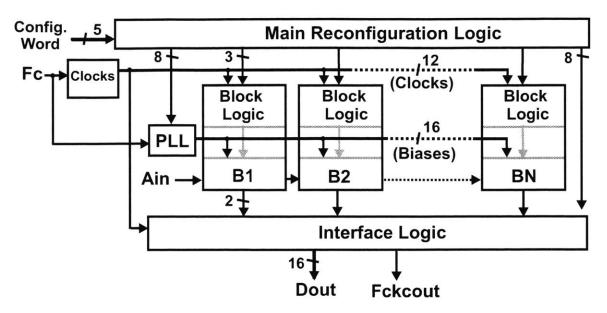

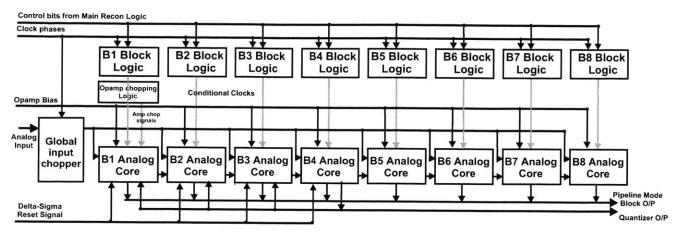

| Figure 5-1: ADC architecture.                                                                          | 50         |

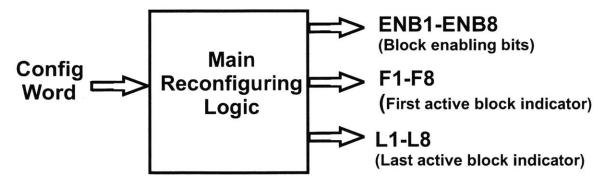

| Figure 5-2: Conceptual diagram of the main reconfiguring logic                                         |            |

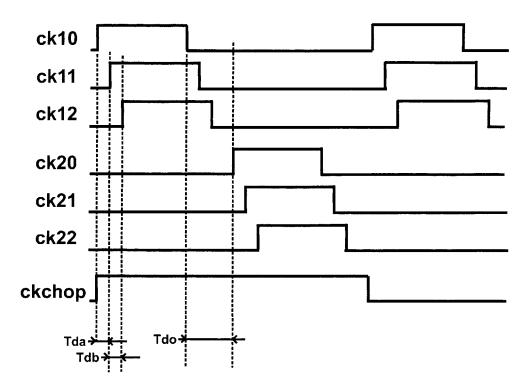

| Figure 5-3: Clock timing employed for converter.                                                       |            |

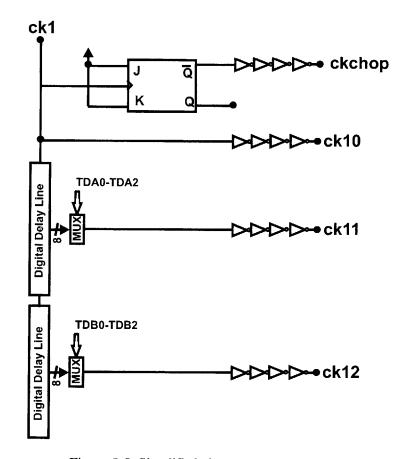

| Figure 5-4: Non-overlapping two-phase clock generator.                                                 | 52         |

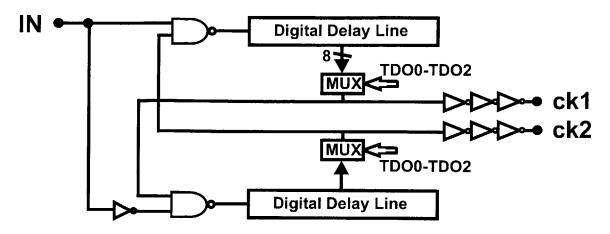

| Figure 5-5: Simplified phase generator module.                                                         | 53         |

| Figure 5-6: Block diagram of converter core.                                                           |            |

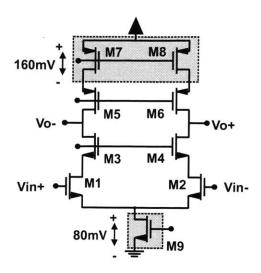

| Figure 5-7: Opamp used in blocks B1-B5. The opamps in blocks B6-B8 are topologically identical         |            |

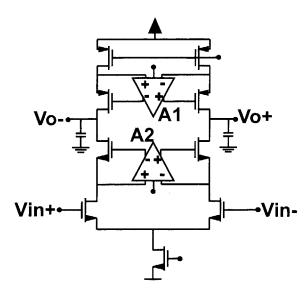

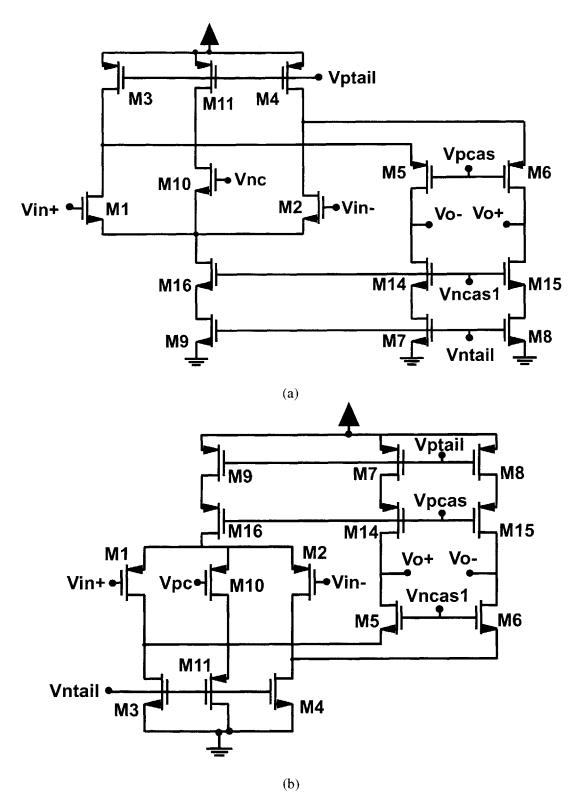

| without the gain enhancement amplifiers.                                                               | 56         |

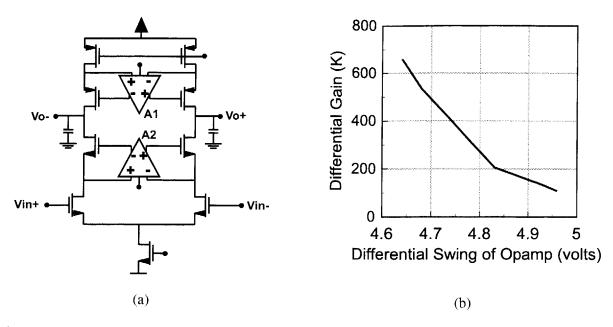

| Figure 5-8: (a) n-gain enhancement amplifier. (b) p-gain enhancement amplifier.                        |            |

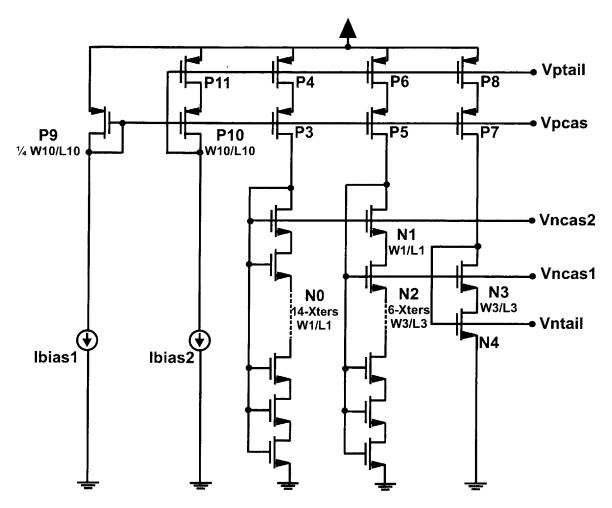

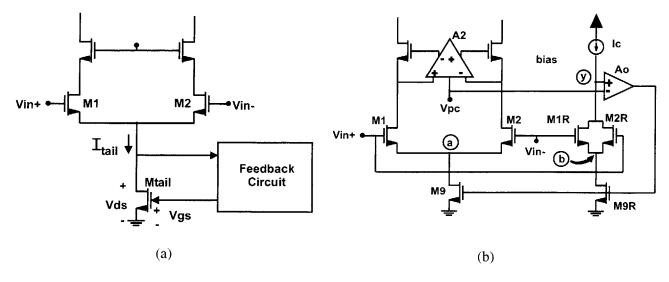

| Figure 5-9: Typical bias circuit employed for the amplifiers.                                          | . 58       |

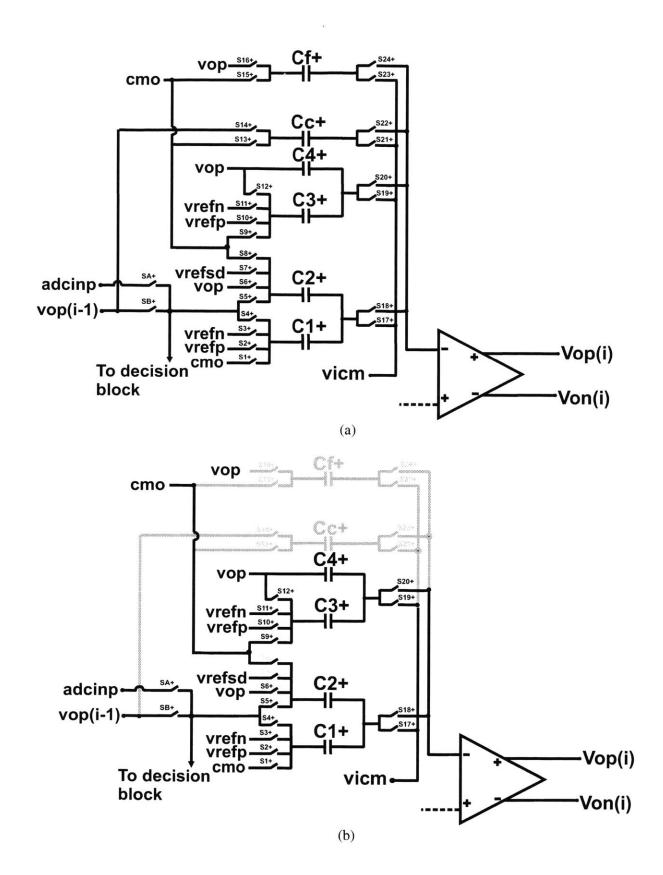

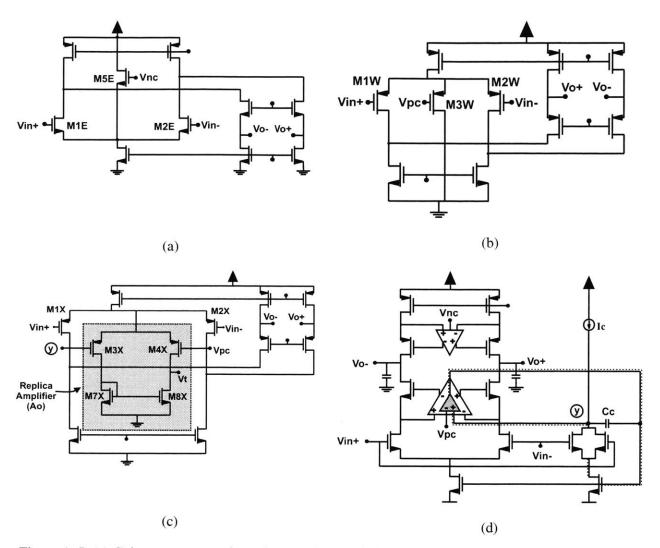

| Figure 5-10: Switched-capacitor core in basic building block. (a) All switches shown. (b) switched-    | . 50       |

| capacitor core in pipeline mode. (c) Switched-capacitor core in delta-sigma mode. (d)                  |            |

| Simplified structure of block in delta-sigma mode.                                                     | 63         |

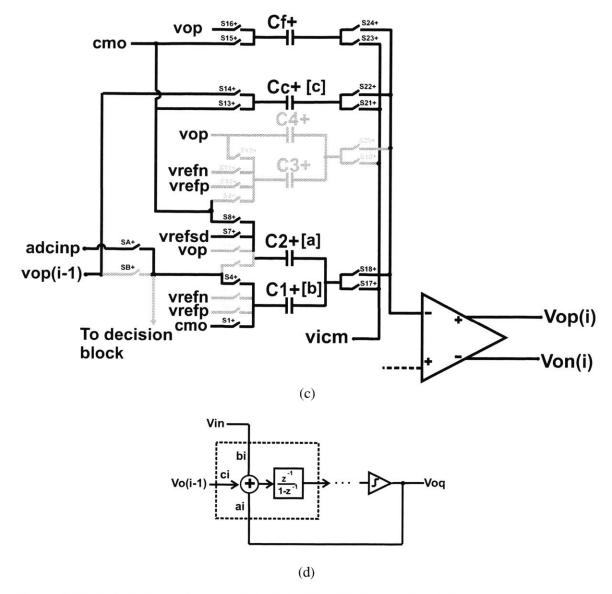

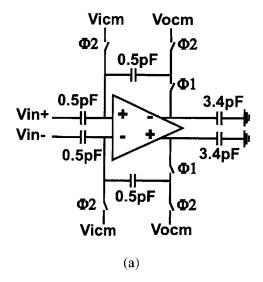

| Figure 5-11: Illustration of opamp chopping to minimize opamp offset and 1/f noise. (a) Conventional   | . 0.5      |

| opamp chopping scheme. (b) Proposed opamp-chopping mechanism.                                          | 67         |

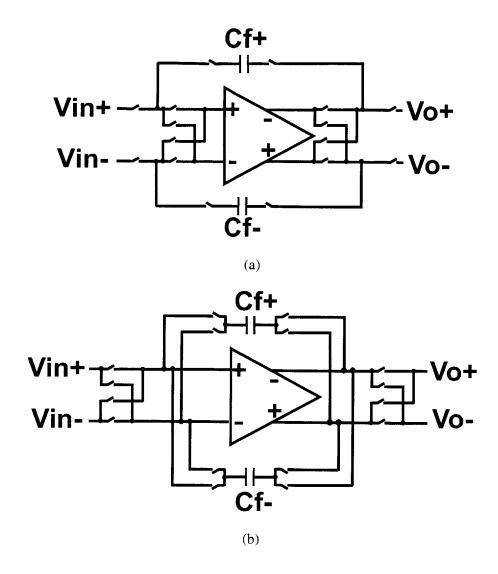

| Figure 5-12: Conceptual block diagram of the block reconfiguring logic                                 | . 69       |

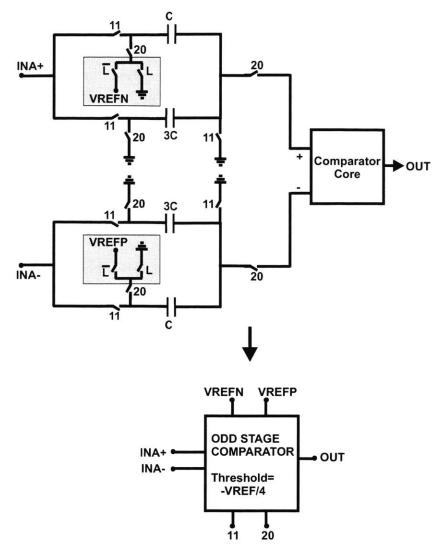

| Figure 5-13: Switched-capacitor circuit details of each comparator.                                    | . Ue       |

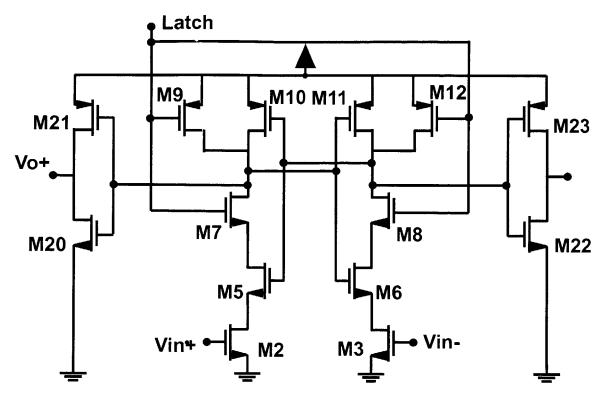

| Figure 5-14: Transistor-level circuit details of the latch employed in the comparator                  | . / C      |

| Figure 5-15: The block level diagram of the decision box in the basic building block                   | 71<br>71   |

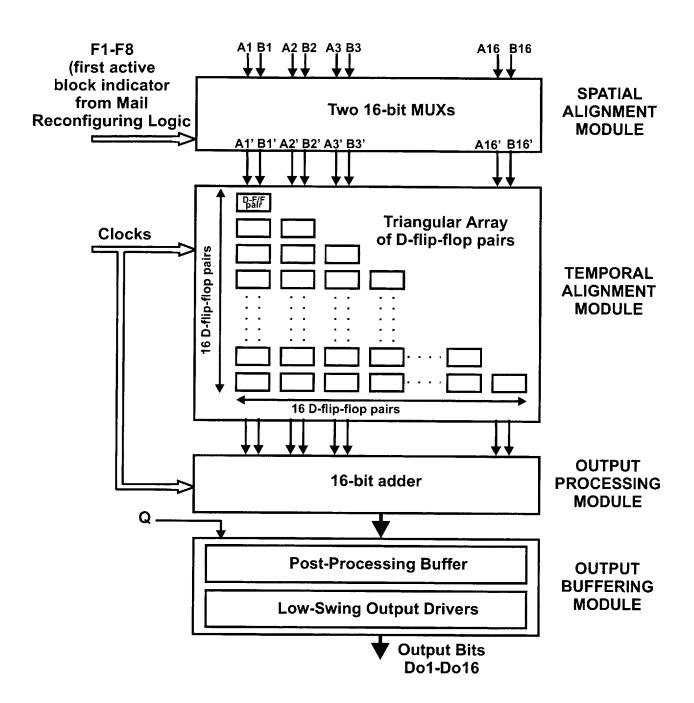

| Figure 5-16: Block level diagram of the output interface                                               | 72         |

| Figure 5-17: D-flip-flop employed for the spatial alignment buffers                                    | . 13<br>71 |

| - 2000 0 17. D Imprinop employed for the spatial anginnent buffers                                     | . 74       |

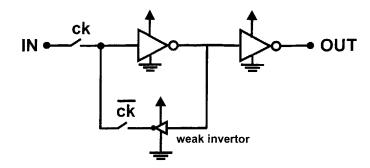

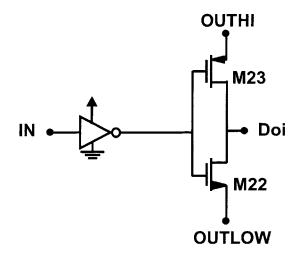

| Figure 5-18: Schematic of low-swing output driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

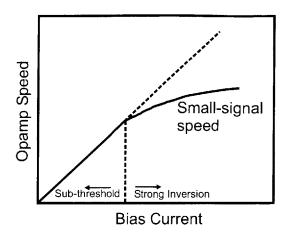

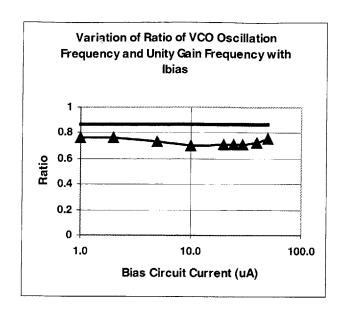

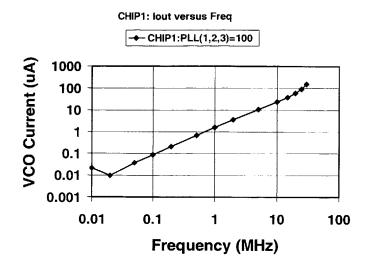

| Figure 6-1: Variation of opamp linear settling speed versus bias current flowing through opamp inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| The two regimes strong-inversion and sub-threshold refer to the regimes of the input devices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| of the opamp as bias current is varied                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

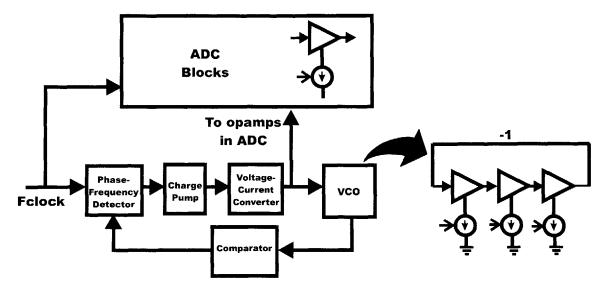

| Figure 6-2: Bandwidth reconfiguration with a phase-locked-loop                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

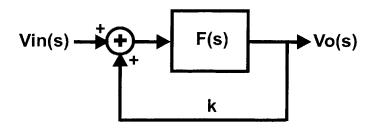

| Figure 6-3: Basic feedback model with loop gain $L(s)$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

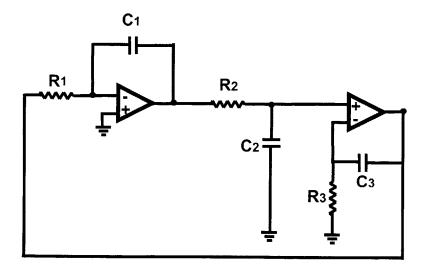

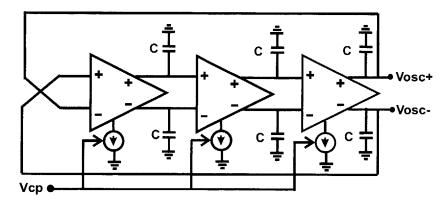

| Figure 6-4: Quadrature oscillator circuit schematic.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

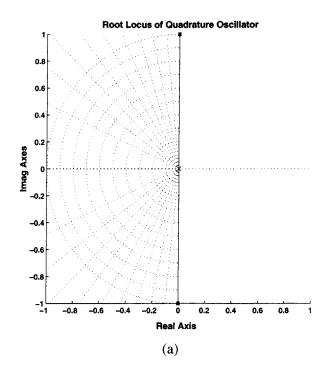

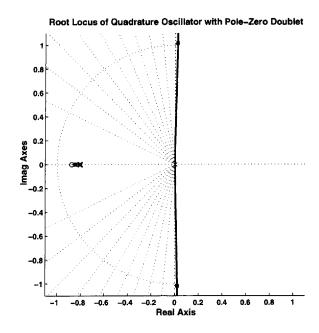

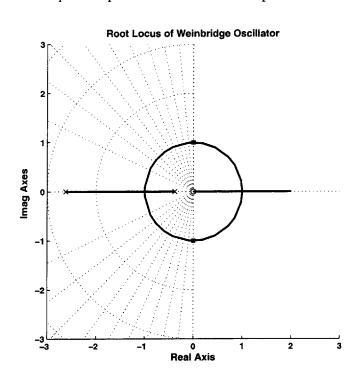

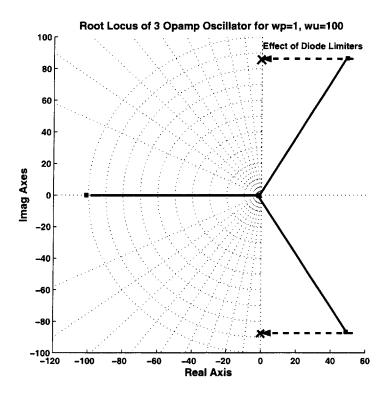

| Figure 6-5: Quadrature oscillator. (a) root-locus as feedback gain k is increased from zero to infinity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Location of poles when k is unity is represented by the squares. (b) Bode-plot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

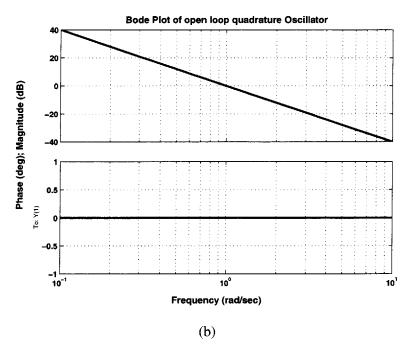

| Figure 6-6: Root-locus of quadrature oscillator with pole-zero doublet as feedback gain k is increased                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| from zero to infinity. The pole-zero doublet pushes the closed loop poles into the right-hand                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| plane. The small dark squares represent the location of the poles when k is unity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 6-7: Root-locus of the two-pole system with zero at DC.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

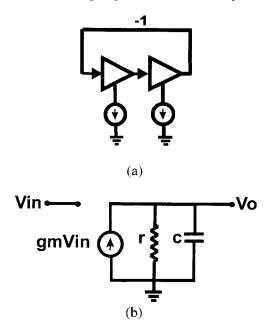

| Figure 6-8: (a) Conceptual diagram of two-opamp oscillator. (b) Model of each opamp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

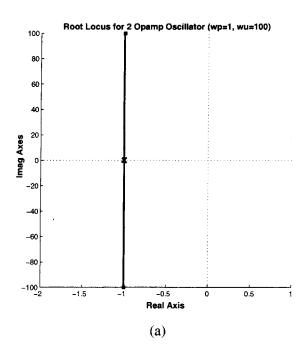

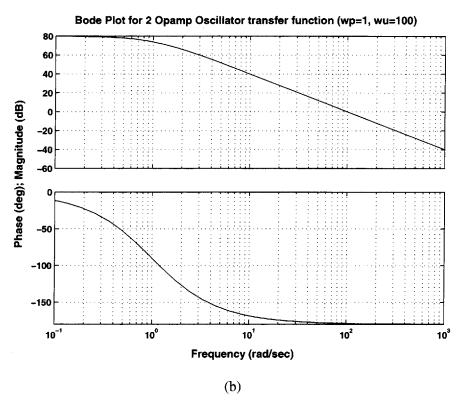

| Figure 6-9: Two-opamp oscillator. (a) root-locus as feedback gain k is increased from zero to infinity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Location of poles when k is unity is represented by the squares. (b) Bode-plot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

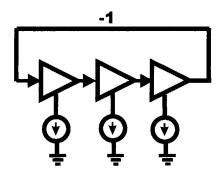

| Figure 6-10: Conceptual diagram of three-opamp oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

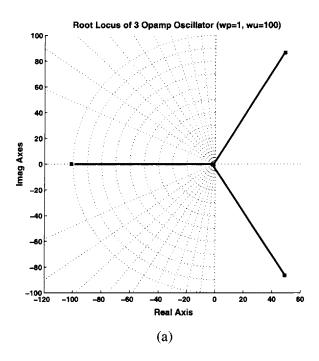

| Figure 6-11: Three-opamp oscillator. (a) root-locus as feedback gain k is increased from zero to infinity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Location of poles when k is unity is represented by the squares. (b) Bode-plot                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

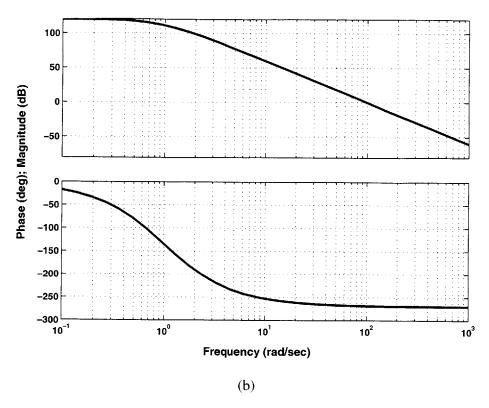

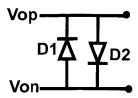

| Figure 6-12: Root-locus of three-opamp oscillator with dashed line showing trajectory of poles due to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

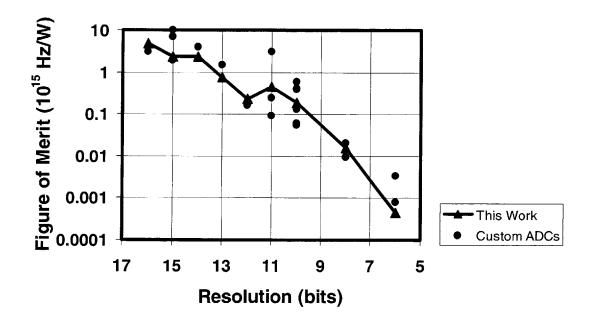

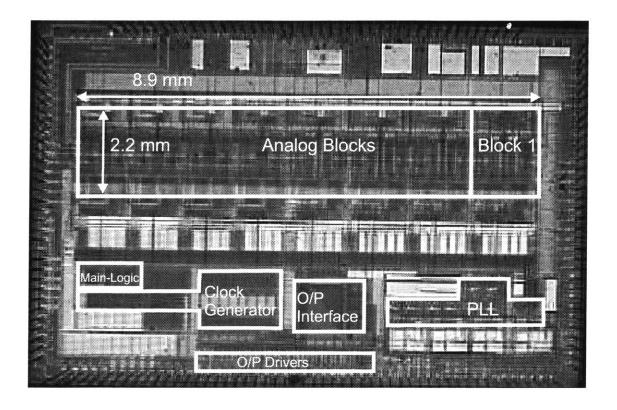

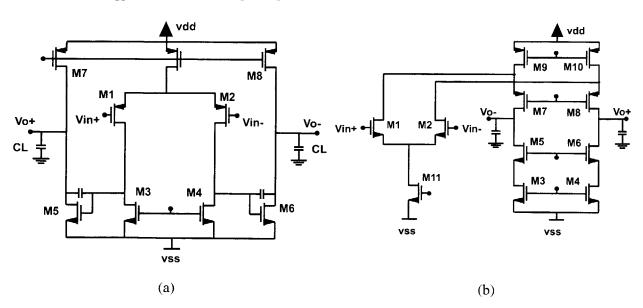

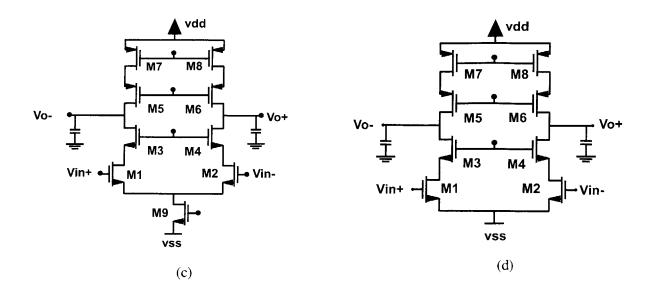

| diode limiting91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |