## A Low Noise, Low Power DC/DC Converter

## for Cell Phone Power Applications

by

Sauparna Das

Submitted to the Department of Electrical Engineering and Computer Science

in Partial Fulfillment of the Requirements for the Degrees of

Bachelor of Science in Electrical Science and Engineering

and Master of Engineering in Electrical Engineering and Computer Science

at the Massachusetts Institute of Technology

May 24, 2002 [الالمانية عندي 2002] Copyright © 2002 Sauparna Das. All rights reserved.

The author hereby grants to MIT permission to reproduce and distribute publicly paper and electronic copies of this thesis and grant others the right to do so.

| Author       | Department of Electrical Engineering and Comput<br>Ma | er Science<br>y 24, 2001 |

|--------------|-------------------------------------------------------|--------------------------|

| Certified by | Professor David J<br>M.I.T. Thesis                    |                          |

| Certified by | Thomas J.<br>VI-A Company Thesis                      |                          |

| Accepted by  | Arthu<br>Chairman, Department Committee on Gradu      | r C. Smith<br>ate Theses |

|              | BARKER                                                | USETTS INSTITUTE         |

|              | L                                                     | BRARIES                  |

## A Low Noise, Low Power DC/DC Converter for Cell Phone Power Applications

by

### Sauparna Das

Submitted to the Department of Electrical Engineering and Computer Science

May 24, 2002

In Partial Fulfillment of the Requirements for the Degrees of Bachelor of Science in Electrical Science and Engineering and Master of Engineering in Electrical Engineering and Computer Science at the Massachusetts Institute of Technology

### ABSTRACT

The goal is to design a low noise, low power DC/DC converter and controller IC to power an Analog Devices' digital signal processor that will run at 1.2 V from a 3.6 V battery and has a rated maximum current draw of 300mA. A switch-mode DC/DC converter is proposed as a possible way of efficiently stepping down the battery voltage to 1.2 V. The control chip is designed using Taiwan Semiconductor Manufacturing Corporation's 0.25  $\mu$ m CMOS process. Component selection issues for the power stage and input and output filters are discussed. Dynamic modeling of the DC/DC converter and feedback control design are also presented. A 1.5 MHz, synchronously rectified, current-mode controlled step-down converter was designed and simulated using Analog Devices' spice simulator ADICE.

Thesis Supervisor: David J. Perreault Title: Assistant Professor

Thesis Supervisor: Thomas J. Barber Jr. Title: Design Engineer, Analog Devices

## **Table of Contents**

| 1 | Introduction                                                      | 11  |

|---|-------------------------------------------------------------------|-----|

|   | 1.1 Power consumption in a cell phone                             | 11  |

|   | 1.2 Why use a DC/DC converter?                                    | 12  |

|   | 1.3 Organization                                                  | 14  |

| 2 | Buck Converter Design                                             | 15  |

|   | 2.1 Specifications for the buck converter                         |     |

|   | 2.2 Power Stage                                                   |     |

|   | 2.2.1 Pass transistor                                             |     |

|   | 2.2.2 Synchronous rectification                                   | 16  |

|   | 2.2.3 Losses in the power stage                                   |     |

|   | 2.3 Output Filter Design                                          |     |

|   | 2.3.1 Filter size requirements                                    |     |

|   | 2.3.2 Output filter inductor selection                            |     |

|   | 2.3.3 Output filter capacitor selection                           |     |

|   | 2.4 Input Filter Design                                           |     |

|   | 2.4.1 Overview                                                    |     |

|   | 2.4.2 Input filter size requirements                              |     |

|   | 2.4.3 Component selection                                         |     |

|   | 2.4.4 Input filter losses                                         |     |

|   | 2.5 Summary of buck converter design                              |     |

| 3 |                                                                   |     |

|   | 3.1 Dynamic model of Buck Converter                               |     |

|   | 3.2 Current-mode control                                          |     |

|   | 3.2.1 Current-mode operation                                      |     |

|   | 3.2.2 Ripple instability and slope compensation                   |     |

|   | 3.3 Closed loop model                                             |     |

|   | 3.4 Compensator Design                                            |     |

|   | 3.5 Input filter and closed loop stability                        |     |

|   | 3.5.1 Interaction between closed loop converter and input filter  |     |

|   | 3.5.2 Input impedance of a current-mode controlled buck converter |     |

|   | 3.5.3 Closed loop stability with an input filter                  |     |

| 4 |                                                                   |     |

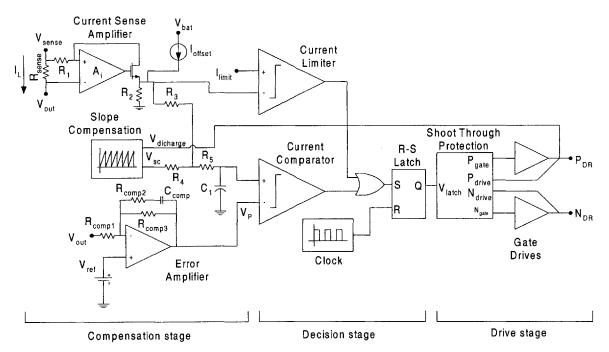

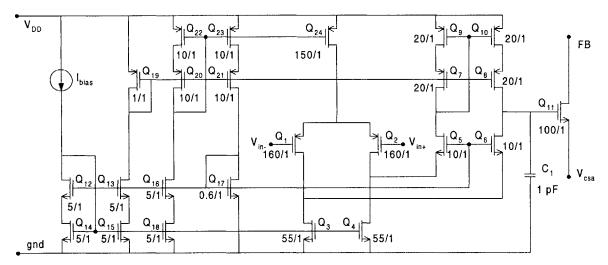

| - | 4.1 Overview of the control IC                                    |     |

|   | 4.2 Compensation stage                                            |     |

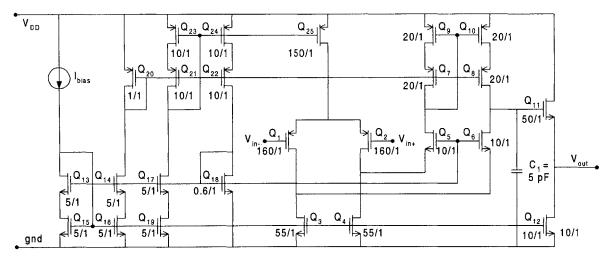

|   | 4.2.1 Error amplifier                                             |     |

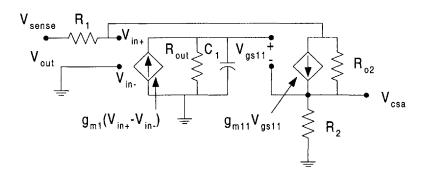

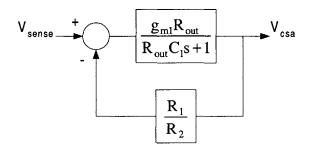

|   | 4.2.2 Current sense amplifier                                     |     |

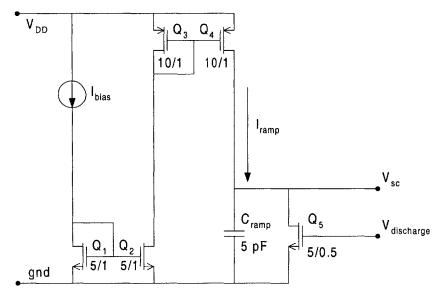

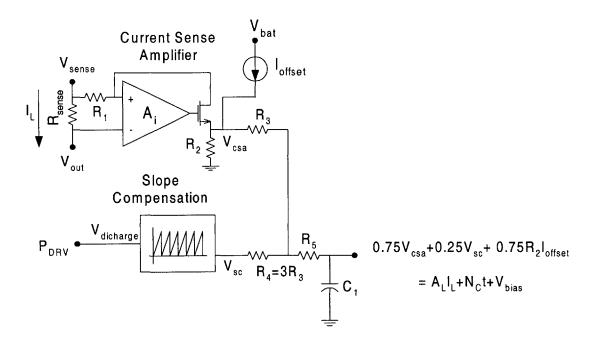

|   | 4.2.3 Slope compensation and voltage biasing                      |     |

|   | 4.3 Decision stage                                                |     |

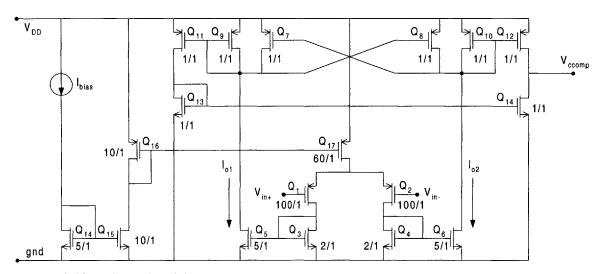

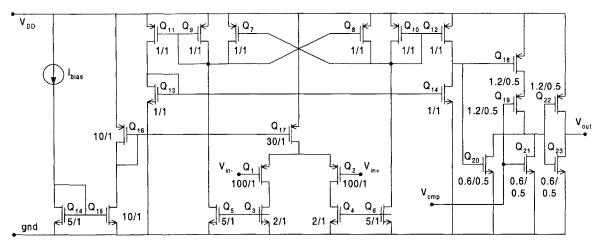

|   | 4.3.1 Current comparator                                          |     |

|   | 4.3.2 Current limiter                                             |     |

|   | 4.3.3 RS-latch                                                    |     |

|   | 4.4 Drive stage                                                   |     |

|   | 4.4.1 Drive stage circuits                                        |     |

|   | 4.4.2 Drive stage operation                                       |     |

|   | 4.5 Power consumption in the control IC                           |     |

| 5 |                                                                   |     |

| 5 | 5.1 Overview                                                      |     |

|   |                                                                   |     |

|   | 5.2 Output voltage response to step changes in output current     | 100 |

|    | 5.2.1 | Output voltage response for different output filter inductors   | 101 |

|----|-------|-----------------------------------------------------------------|-----|

|    | 5.2.2 | Output voltage response for different battery voltages          | 108 |

|    | 5.2.3 | Output voltage response over temperature and process variations | 110 |

|    | 5.2.4 | Output voltage response with variation in the compensator       |     |

|    | 5.3   | input filter performance                                        | 117 |

|    | 5.3.1 | Input current sourcing                                          | 117 |

|    | 5.3.2 | Input current ripple attenuation                                | 119 |

|    |       | Efficiency of the closed loop buck converter                    |     |

| 6  | Concl | usion                                                           | 123 |

| 7  | Refer | ences                                                           |     |

| 8  | Apper | ndix A: Losses in MOSFETs                                       |     |

|    | 8.1   | High side switching losses                                      |     |

|    | 8.2   | Low side switching losses                                       |     |

|    | 8.3   | Capacitive turn-on losses                                       |     |

|    | 8.4   | Gate drive losses                                               | 129 |

|    | 8.5   | Conduction Losses                                               |     |

| 9  |       | ndix B: Inductor loss testing                                   |     |

| 10 | ) Ap  | pendix C: MATLAB code                                           | 132 |

|    |       |                                                                 |     |

# List of Figures

| Figure 1-1: A buck converter employing a MOSFET switch and a free wheeling diode. The LC                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| filter attenuates the AC component of the square wave voltage $V_x$ to produce a DC voltage                                                                             |

| with a small ripple voltage                                                                                                                                             |

| Figure 1-2: Buck converter waveforms. A) The square wave voltage $V_x$ across the diode. B) DC                                                                          |

| component of the diode voltage. C) AC component of the diode voltage. D) The LC filter                                                                                  |

| attenuates the AC component, leaving a DC voltage with a small ripple at the output 13                                                                                  |

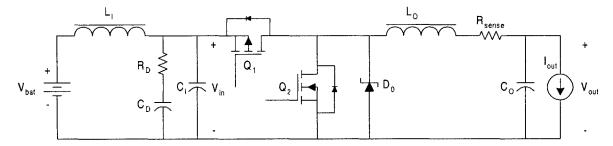

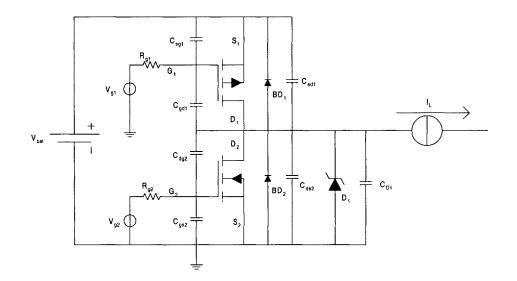

| Figure 2-1: Power stage for the buck converter using a PMOS pass transistor, NMOS                                                                                       |

| synchronous rectifier, and a schottky diode for free-wheeling conduction when both power                                                                                |

| MOSFETS are off                                                                                                                                                         |

| Figure 2-2: Capacitive turn-on loss in the PMOS pass device $(Q_1)$ . A) Power stage and inductor.                                                                      |

| The PMOS transistor is shown with its output capacitance across its drain and source. B)                                                                                |

| When the NMOS is conducting the PMOS device is off. The voltage across $r_{dsn}$ is very small                                                                          |

| (~ 100 mV) and $C_{out-p}$ charges up to $V_{in}$ . C) When the PMOS device turns on $C_{out-p}$                                                                        |

| discharges through the on-state resistance $r_{dsp}$ dissipating $\frac{1}{2}C_{out-p}V_{in}^2$ every cycle                                                             |

| Figure 2-3: Switching transition loss when the PMOS device turns off. A) Power stage and                                                                                |

| inductor. B) In order for the current through the PMOS device to go to zero the schottky                                                                                |

| diode must turn on and start to carry the inductor current. In order for this to happen the                                                                             |

| voltage across the PMOS device, $V_{sw}$ must rise to $V_{in}$ . Since $V_{in} = V_{sw} + V_{diode}$ , the schottky                                                     |

| diode turns on and starts to conduct once $V_{sw}$ equals $V_{in}$ and the voltage across the diode is                                                                  |

| zero. C) The total energy dissipated while the PMOS device switches off is $W_{diss} =$                                                                                 |

| $\frac{1}{2}V_{in}I_L\tau_{sw}$ . The power dissipated in a cycle is the switching frequency, f, times $W_{diss}$ . The                                                 |

| lower the input capacitance the shorter $\tau_{sw}$ is. A similar power loss occurs when the PMOS                                                                       |

| device turns on                                                                                                                                                         |

| Figure 2-4: Top: Si1555DL PMOS and NMOS gate drive losses. Bottom: Capacitive turn-on                                                                                   |

| losses in the Si1555DL PMOS and NMOS gate drive losses. Bottom: Capacitive turn-on<br>losses in the Si1555DL PMOS and NMOS transistors and the B0520WS schottky diode22 |

| •                                                                                                                                                                       |

| Figure 2-5: Top: Turn on and turn off switching losses for the Si1555DL PMOS pass transistor.<br>Bottom: Conduction loss in the Si1555DL PMOS and NMOS transistors23    |

| Figure 2-6: Power loss as a percentage of output power for Si1555DL, Si1303/4DL, and                                                                                    |

| Si3585DV transistors as output current is varied. The solid line at 25% corresponds to an                                                                               |

|                                                                                                                                                                         |

| 80% efficient converter and the solid line at 43% corresponds to a 70% efficiency converter.                                                                            |

|                                                                                                                                                                         |

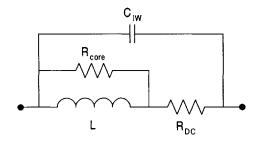

| Figure 2-7: Lumped parameter circuit model of a real inductor. $R_{DC}$ is the DC resistance in the                                                                     |

| windings. $C_{IW}$ is the inter-winding capacitance and $R_{core}$ is a nonlinear resistor that                                                                         |

| represents the energy lost aligning the magnetic domains in the inductor core                                                                                           |

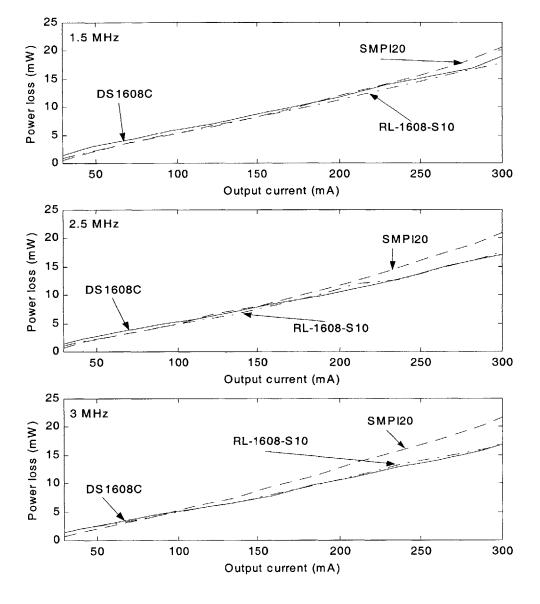

| Figure 2-8: Power loss vs. output current in the DS1608C, SMPI20 and RL-1608-S10 inductors                                                                              |

| at 1.5 MHz (top), 2.5 MHz (middle) and 3 MHz (bottom)                                                                                                                   |

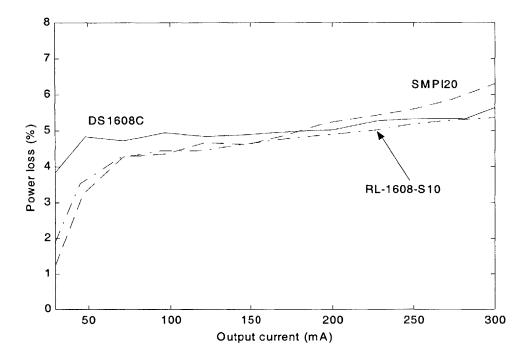

| Figure 2-9: Power loss as a percentage of output power vs. output current in the DS1608C,                                                                               |

| SMPI20 and 1608-S inductors at 1.5 MHz.                                                                                                                                 |

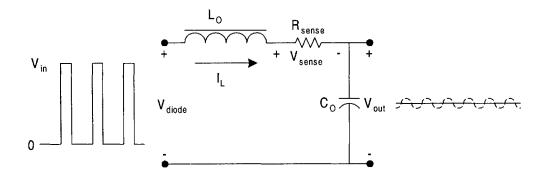

| Figure 2-10: The sense resistor, $R_{sense}$ , is placed in series with the output filter inductor, $L_0$ . It is                                                       |

| placed on the same side as the output filter capacitor, C <sub>0</sub> , to minimize noise due to the diode                                                             |

| voltage switching between 0 and V <sub>in</sub> rapidly                                                                                                                 |

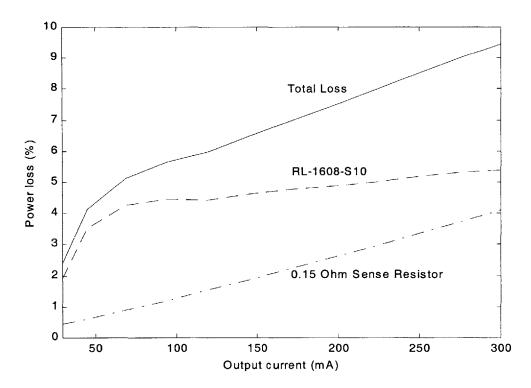

| Figure 2-11: Power loss, as a percentage of output power, in the 0.15 $\Omega$ sense resistor, the RL-                                                                  |

| 1608-S10 inductor and the total loss in the inductor-resistor pair                                                                                                      |

| Figure 2-12: Lumped parameter circuit model of a real capacitor. ESL is the equivalent series                                                                           |

| inductance and ESR is the equivalent series resistance of the capacitor leads. These parasitic                                                                          |

| elements make the capacitor look inductive or resistive at high frequencies                                                                                             |

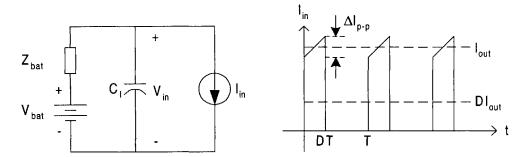

| Figure 2-13: The power stage is modeled as a current source that equals the inductor current when                                                                       |

| the pass transistor is on and equals zero when the pass transistor is off. The inductor current                                                                         |

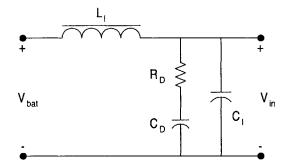

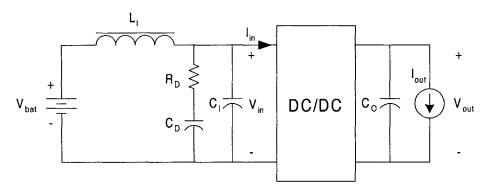

| Figu | parallel with the input capacitor, $C_1$<br>re 2-14: Second order input filter consisting of inductor $L_I$ and capacitor $C_I$ . $R_D$ and $C_D$ ma  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | up the damping leg that reduces the peaking at the resonance frequency of the LC filter                                                               |

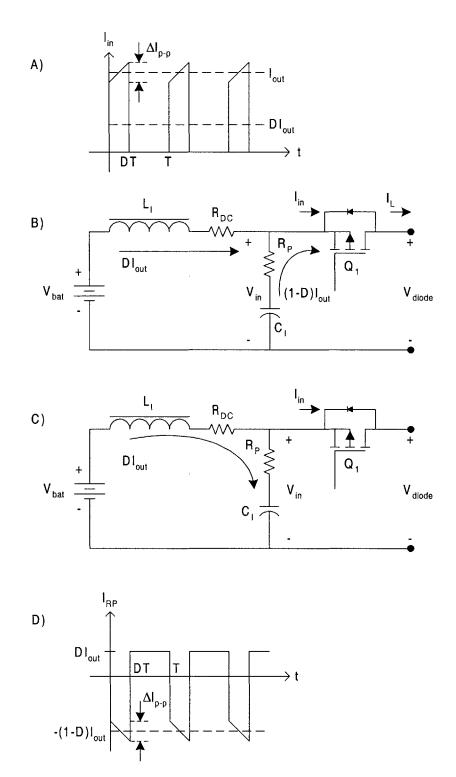

| Figu | re 2-15: A) Current into the power stage of the buck converter. B) When $Q_1$ is on, the curre                                                        |

|      | through L <sub>I</sub> , DI <sub>out</sub> , flows to the output filter inductor while C <sub>1</sub> sources an average current                      |

|      | $(1-D)I_{out}$ . C) When Q <sub>1</sub> is off, the current through L <sub>I</sub> flows into C <sub>I</sub> , recharging the capacit                 |

|      | D) Current through the resistor $R_P$ . $R_P$ is the resistance of the PCB trace from the $Q_1$ to $Q_2$                                              |

|      | The average current through $C_I$ , which equals the average current flowing through $R_P$ ,                                                          |

|      | zero so that average value of V <sub>in</sub> does not change                                                                                         |

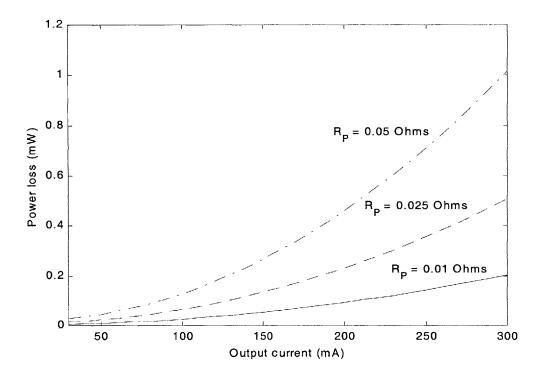

| Figu | re 2-16: Power dissipated in the trace resistance, $R_P$ , for $R_P$ equal to 10, 25 and 50 m $\Omega$ . Du                                           |

|      | ratio is 0.333 and $L_0$ is 4.7 $\mu$ H, making $\Delta I_{p-p}$ is 120 mA                                                                            |

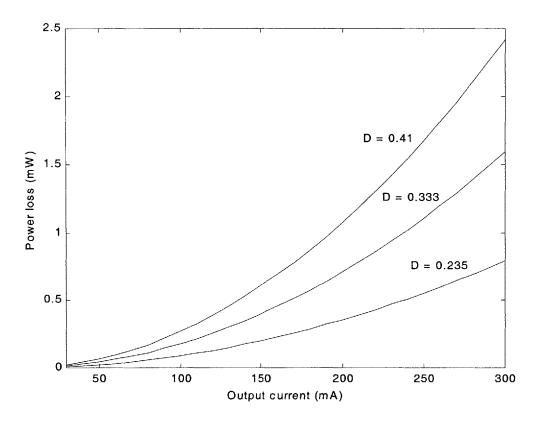

| Figu | re 2-17: Power dissipated in the DC resistance of the NLFC201614 input filter inductor t                                                              |

|      | different duty cycles. When battery is drained and the input voltage falls to 2.9 V, D w                                                              |

|      | equal 0.41. When the battery is fully charged at 3.6 V D will equal 0.333 and if a NiN                                                                |

|      | battery is charging the input voltage rises to 5.1 volts so that D is reduced to 0.235                                                                |

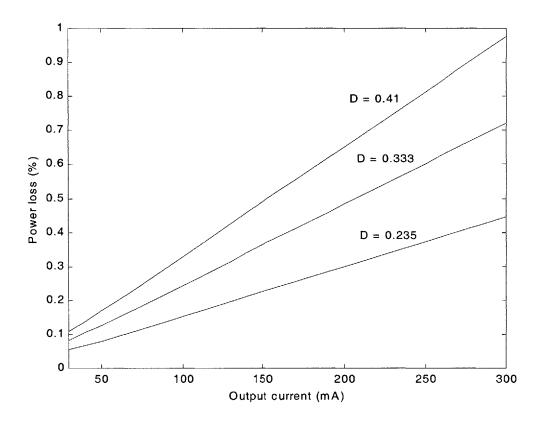

| Figu | re 2-18: Power loss as a percentage of output power for the input filter using t                                                                      |

|      | NLFC201614 inductor and an $R_P$ of 50 m $\Omega$ . The loss percentage is plotted at the nomin                                                       |

|      | duty cycle (0.333) and at the min (0.235) and max (0.41) duty cycle                                                                                   |

| Figu | re 2-19: Synchronously rectified buck converter with second order input filter. The DSP                                                               |

|      | modeled as the current source load Iout. The sense resistor Rsense is used for current limiti                                                         |

|      | and feedback control.                                                                                                                                 |

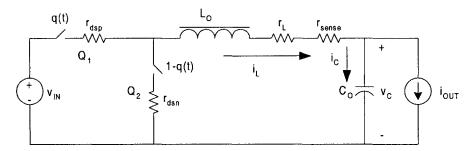

| Figu | re 3-1: Equivalent circuit of synchronous buck converter for state space modeling. The pow                                                            |

|      | MOSFETS are replaced by their respective on-state resistances and switching functions                                                                 |

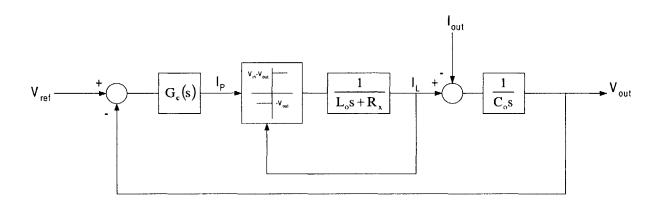

| Figi | re 3-2: Block diagram of a current mode controlled buck converter. The nonlinear block                                                                |

|      | the minor loop represents the switching MOSFETS, schottky diode and switching log                                                                     |

|      | circuitry. This block produces a voltage of $V_{in} - V_{out}$ across the inductor when the PMC                                                       |

|      | switch is on and a voltage of $-V_{out}$ when the NMOS is on                                                                                          |

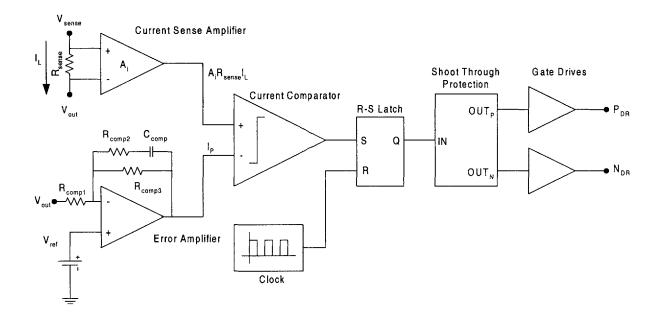

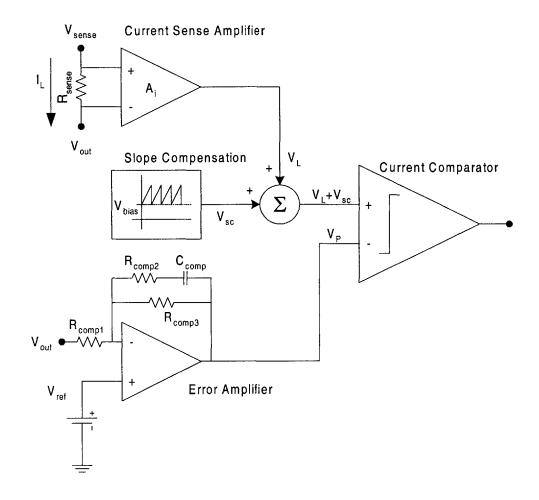

| Figi | re 3-3: Current-mode control architecture. The resistor-capacitor network across the en                                                               |

|      | amplifier implements $G_c(s)$ . The shoot through protection circuit prevents both pow                                                                |

|      | MOSFETs from turning on.                                                                                                                              |

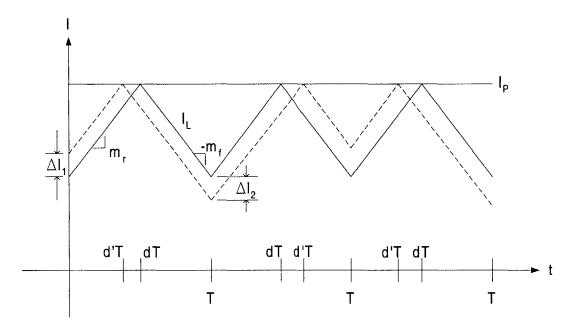

| Figu | re 3-4: Ripple instability in the inductor current of a current-mode controlled converter. T                                                          |

|      | duty cycle is 0.5 and therefore the perturbation, $\Delta I_1$ , in the inductor current is margina                                                   |

| Ein  | stable<br>re 3-5: Current-mode control with slope compensation $m_c$ . The perturbation $\Delta I_1$ dies out in                                      |

| Figi | periods due to the compensation                                                                                                                       |

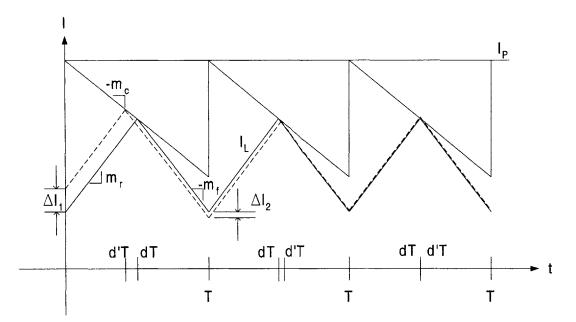

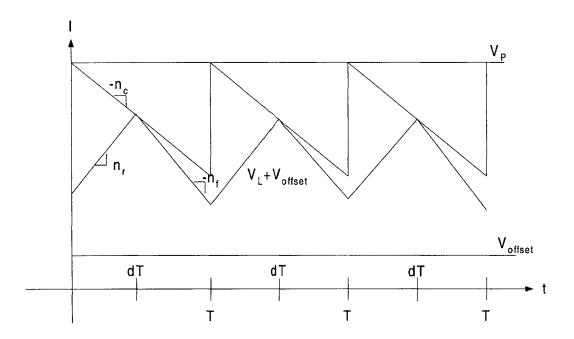

| Fim  | re 3-6: Inner control loop inductor current waveforms represented as voltages with t                                                                  |

| rigi | control IC                                                                                                                                            |

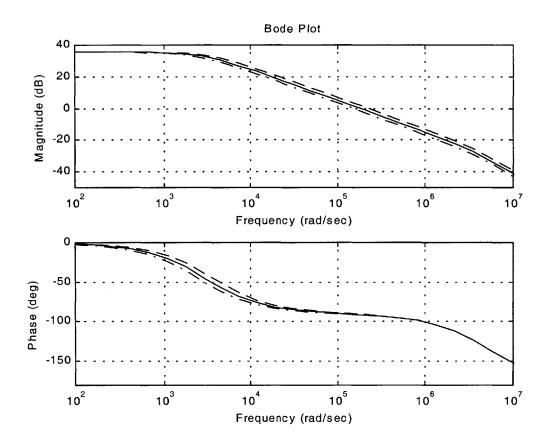

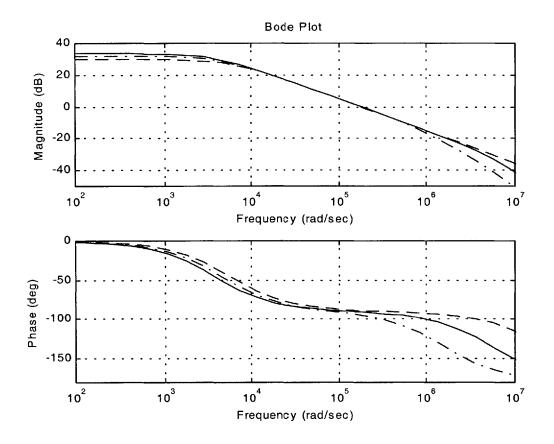

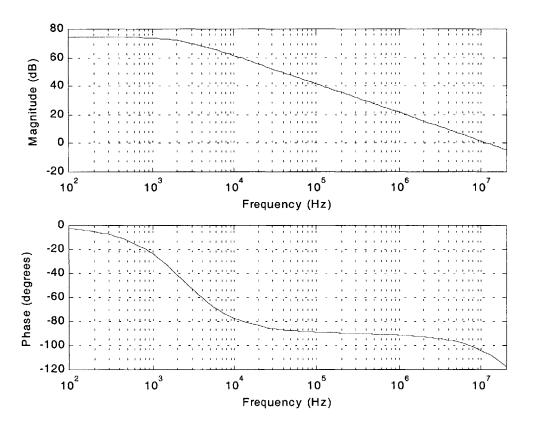

| Fim  | are 3-7: Bode plot of the transfer function from $v_p$ to $v_c$ for C <sub>o</sub> equal to 10 $\mu$ F (solid), 8                                     |

| rigi | (dashed) and 12 $\mu$ F (dashed-dot). The variation in C <sub>0</sub> due to its tolerance changes the ga                                             |

|      | bandwidth product of the transfer function.                                                                                                           |

| Fig  | are 3-8: Bode plot of transfer function from $v_p$ to $v_c$ for different combinations of $V_{IN}$ , $N_c$ a                                          |

| 1 15 | $L_{\rm O}$ . Solid line is $V_{\rm IN} = 3.6$ V, $N_{\rm C} = 9 \times 10^4$ V/s and $L_{\rm O} = 6.8$ µH. Dashed line is $V_{\rm IN} = 5.1$         |

|      | $N_{\rm C} = 5.6 \times 10^4$ V/s and $L_{\rm O} = 3.76 \mu$ H. Dashed-dot line is $V_{\rm IN} = 2.9$ V, $N_{\rm C} = 10^5$ V/s and $L_{\rm O}$       |

|      | $M_{\rm C} = 5.0 \times 10^{-10}$ V/s and $L_0^{-5.70}$ µH. Dashed-dot line is $v_{\rm IN} = 2.5^{-10}$ V, $M_{\rm C} = 10^{-10}$ V/s and $L_0^{-12}$ |

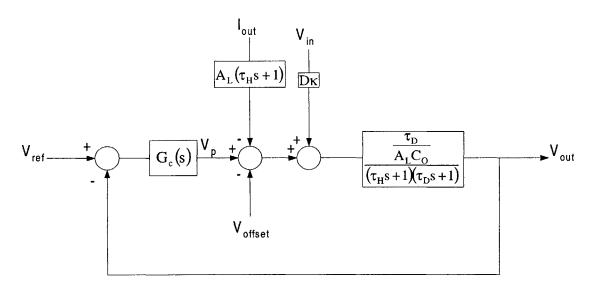

| Fio  | re 3-9: Closed loop block diagram of buck converter                                                                                                   |

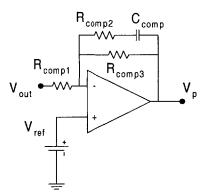

|      | re 3-10: Compensation section of current-mode control architecture                                                                                    |

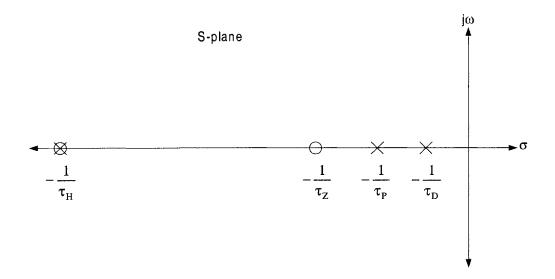

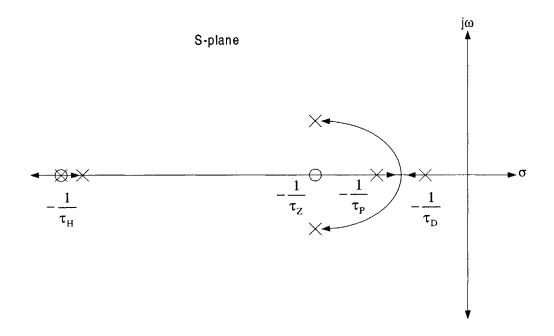

Figure 3-11: Pole and zero locations for  $\frac{v_{out}}{i_{out}}$  (s) and  $G_c(s)$  with the outer voltage loop open.

$\frac{v_{out}}{i_{out}}(s)$  has a dominant pole at  $s = -1/\tau_D$  and a pole-zero cancellation at  $s = -1/\tau_H$ . The pole

Figure 3-12: Root locus of  $\frac{v_{out}}{i_{out}}$  (s) when the outer voltage loop is closed. The dominant pole of

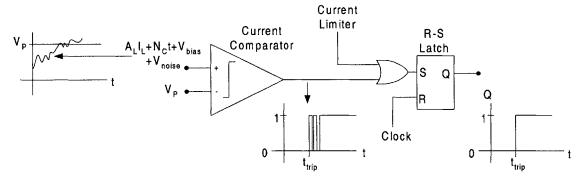

| Figure 4-14: Schematic of the current limiter and OR-gate. The current comparator is connected                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| to the $V_{cmp}$ terminal of the OR-gate                                                                                                                                                                          |

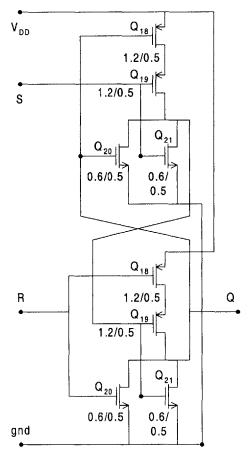

| Figure 4-15: Schematic of the RS-latch                                                                                                                                                                            |

| Figure 4-16: Once S sets Q to 1, Q stays at 1 even though the output of the comparator may swing                                                                                                                  |

| high and low due to noise at the input of the current comparator                                                                                                                                                  |

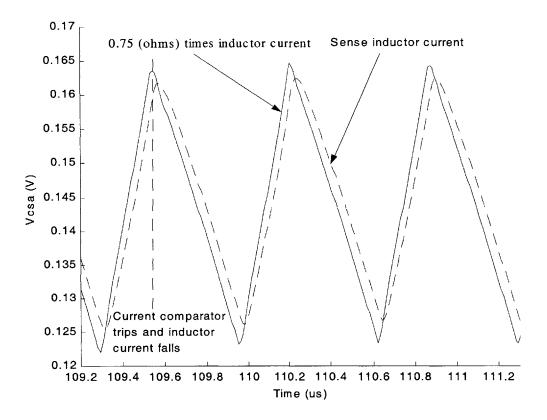

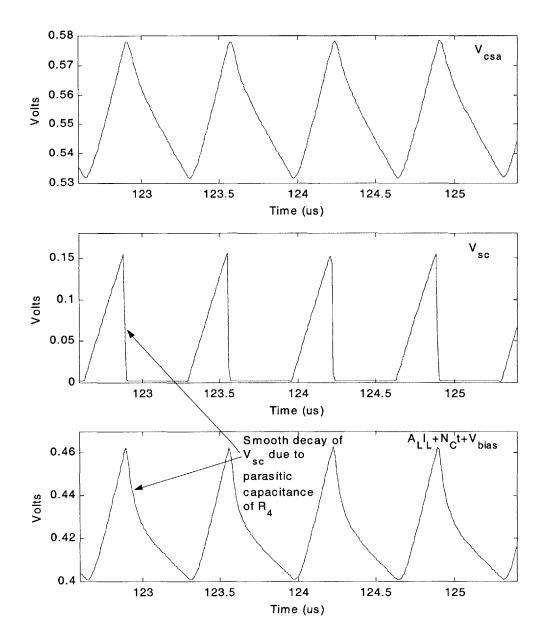

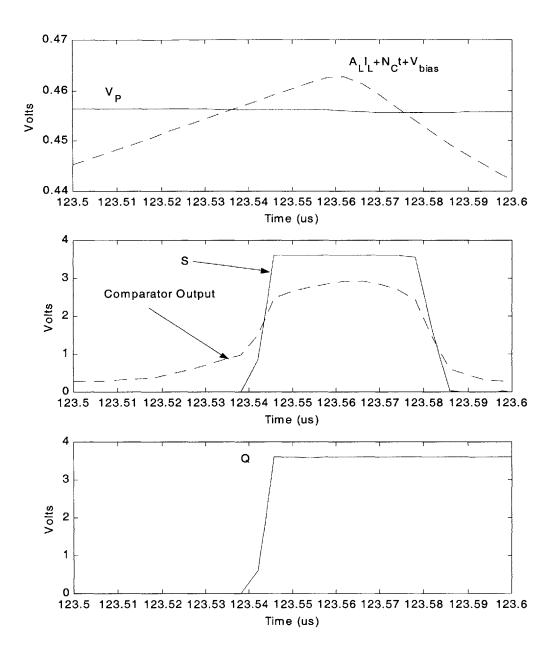

| Figure 4-17: ADICE simulation of the current comparator. When $A_L I_L + N_C t + V_{bias}$ exceeds $V_p$ , the                                                                                                    |

| current comparator trips high setting S to 1. S then sets Q to 1. The total delay from the                                                                                                                        |

| input of comparator to Q is only 9 ns. Notice that when $A_L I_L + N_C t + V_{bias}$ falls below $V_p$ and                                                                                                        |

| the comparator trips low, Q stays high and the pass transistor stays off letting the inductor                                                                                                                     |

| current decay until the end of the cycle                                                                                                                                                                          |

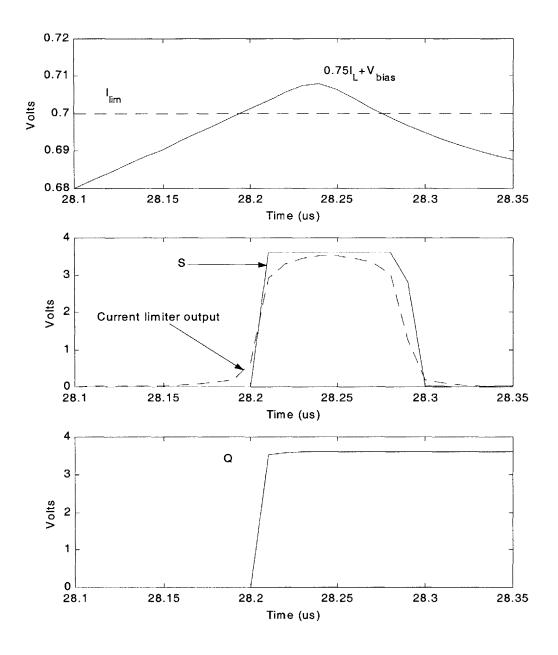

| Figure 4-18: ADICE simulation of the current limiter. When $0.75I_L+V_{bias}$ exceeds $I_{lim}$ , the current                                                                                                     |

| limiter trips high setting S to 1. S then sets Q to 1. The total delay from the input of                                                                                                                          |

| comparator to Q is only 16.6 ns. As in the case of the current comparator Q stays high even                                                                                                                       |

| when the comparator trips high and the inductor current decays until the end of the cycle90                                                                                                                       |

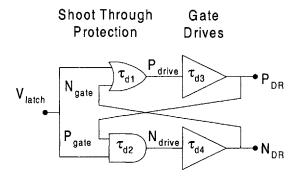

| Figure 4-19: The shoot-through protection circuit consists of an AND-gate and an OR-gate that                                                                                                                     |

| have one of their input tied to the output of the RS-latch at the terminal $V_{latch}$ . The output of                                                                                                            |

| the gate drives, P <sub>DR</sub> and N <sub>DR</sub> , are fed back to the terminals P <sub>gate</sub> and N <sub>gate</sub> , respectively, to                                                                   |

| prevent both power MOSFETs from turning on                                                                                                                                                                        |

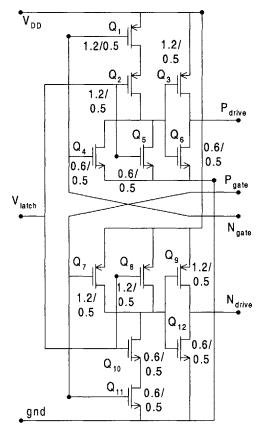

| Figure 4-20: Schematic of the shoot-through protection circuit                                                                                                                                                    |

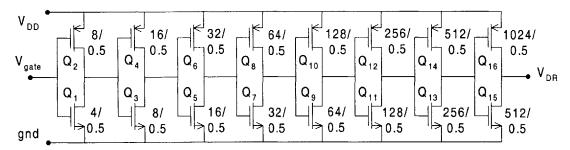

| Figure 4-21: Schematic of the gate drive. The cascade of increasing larger inverters reduces the                                                                                                                  |

| overall gate delay of the gate drive                                                                                                                                                                              |

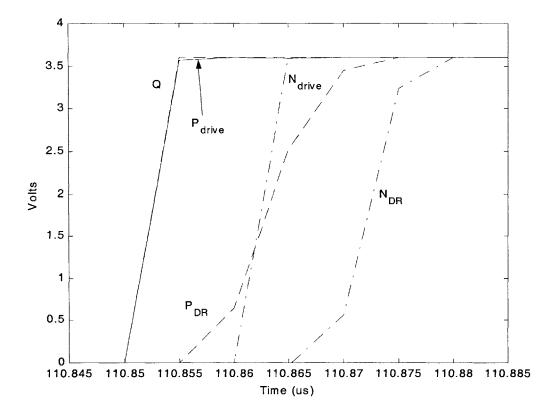

| Figure 4-22: Turn-on sequence for the buck converter in which the NMOS synchronous rectifier                                                                                                                      |

| turns off and the PMOS pass transistor turns on. There is a 16 ns delay from the time Q turns of $(D_{10}, D_{10})$                                                                                               |

| starts to go low to time the pass transistor starts to turn on ( $P_{DR}$ decreases to 2.6 V). The                                                                                                                |

| synchronous rectifier turns off ( $N_{DR}$ decreases to 0.9 V) 5 ns before the pass transistor starts                                                                                                             |

| to turn on                                                                                                                                                                                                        |

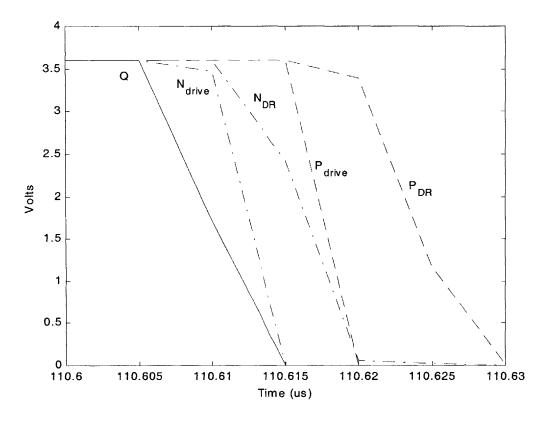

| Figure 4-23: Turn-off sequence for the buck converter in which the PMOS pass transistor turns                                                                                                                     |

| off and the NMOS synchronous rectifier turns on. There is a 21 ns delay from the time Q extents to go high to time the sumebronous rectifier starts to turn on $(N_{\rm ext})$ increases to $(0, 0, N_{\rm ext})$ |

| starts to go high to time the synchronous rectifier starts to turn on ( $N_{DR}$ increases to 0.9 V).                                                                                                             |

| The pass transistor turns off ( $P_{DR}$ increases to 2.6 V) 6 ns before the synchronous rectifier<br>starts to turn on Notice that N starts to go high after PDP starts to go high but received                  |

| starts to turn on. Notice that $N_{drive}$ starts to go high after PDR starts to go high but reaches $V_{bat}$ before $P_{DR}$ . This is because the $N_{drive}$ terminal is the output of an AND gate with very  |

| $v_{bat}$ before $r_{DR}$ . This is because the $N_{drive}$ terminal is the output of an AND gate with very small transistors that transition from low to high very rapidly. The $P_{drive}$ follows Q with       |

| almost no delay for the same reason. The OR-gate of the STP circuit consists of small                                                                                                                             |

| transistors that switch rapidly                                                                                                                                                                                   |

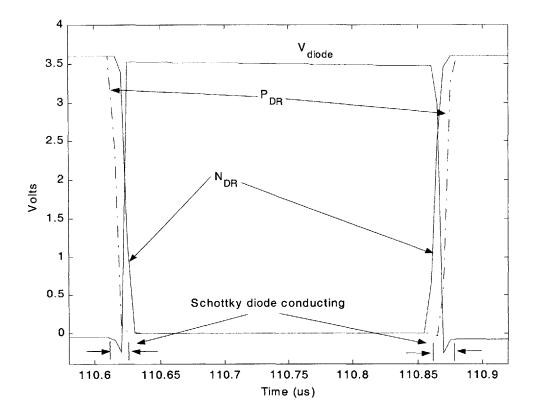

| Figure 4-24: Turn-on and turn-off sequence of the power MOSFETs and the corresponding                                                                                                                             |

| voltage across the schottky diode. The schottky diode turns on for a brief period of time                                                                                                                         |

| during the turn-on and turn-off sequences when both power MOSFETs are off. The forward                                                                                                                            |

| voltage drop is only 300 mV                                                                                                                                                                                       |

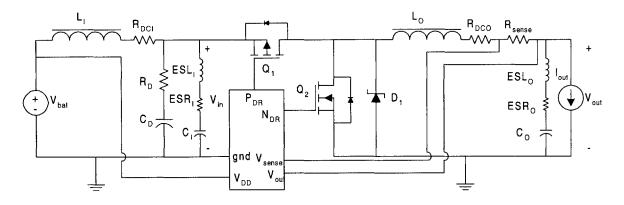

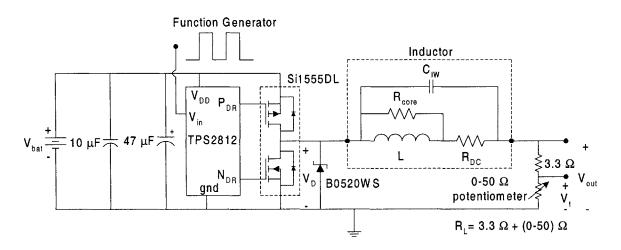

| Figure 5-1: Synchronous buck converter and control IC used in the ADICE simulations. The                                                                                                                          |

| input and output filter components are shown with their relevant parasitic elements                                                                                                                               |

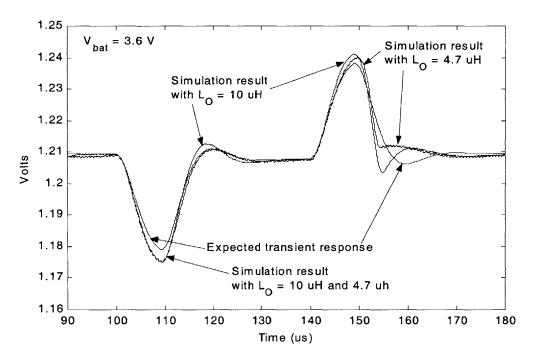

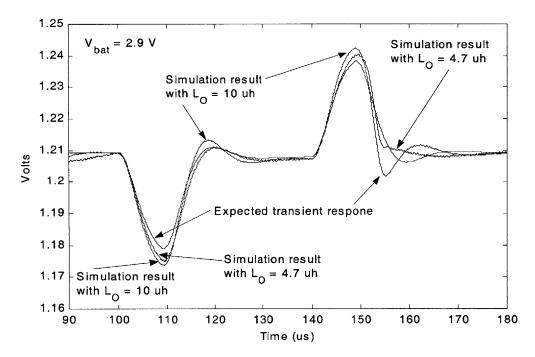

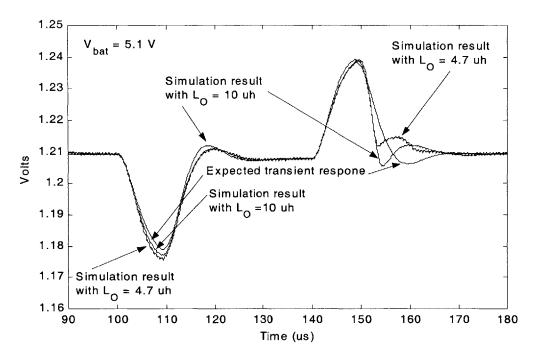

| Figure 5-2: Output voltage transient response for $L_0 = 4.7 \mu\text{H}$ and $10 \mu\text{H}$ and $V_{\text{bat}} = 3.6 \text{V}101$                                                                             |

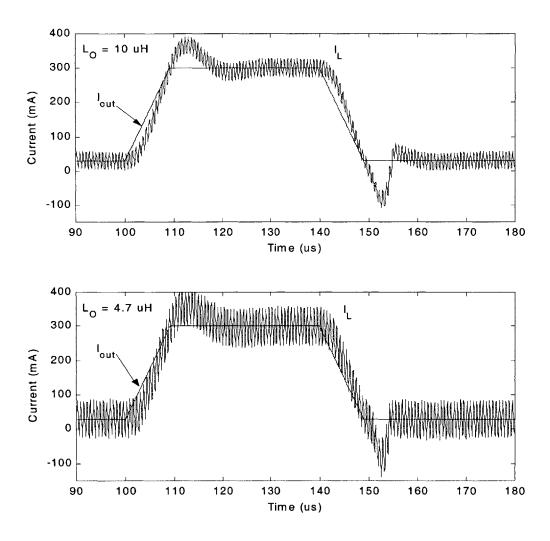

| Figure 5-3: Inductor current for $L_0 = 10 \ \mu\text{H}$ and 4.7 $\mu\text{H}$ during the step changes in $I_{out}$                                                                                              |

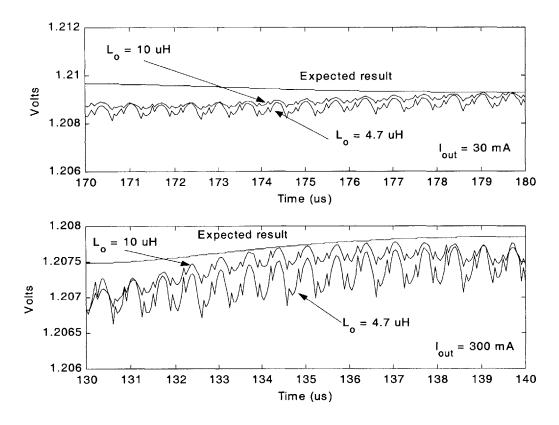

| Figure 5-4: Steady-steady output voltage for $I_{out} = 30$ mA and 300 mA                                                                                                                                         |

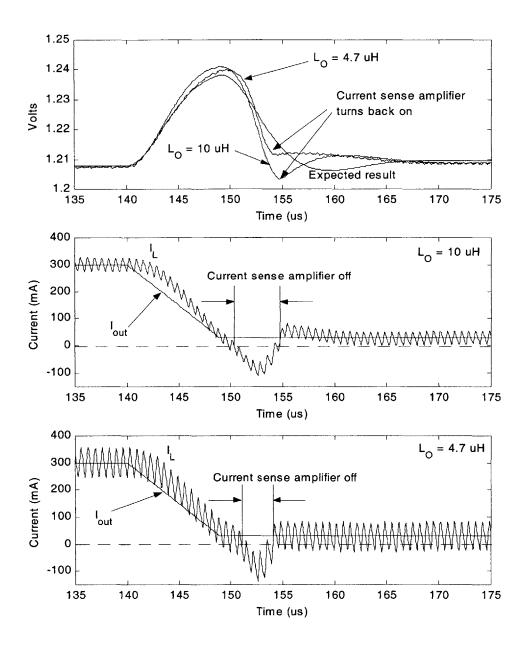

| Figure 5-5: Top: Output voltage response when $I_{out}$ steps down from 300 mA to 30 mA in 9 µsec.                                                                                                                |

| Middle: Inductor current in the converter with $L_0 = 10 \mu H$ during the step in $I_{out}$ . Bottom:                                                                                                            |

| Inductor current in the converter with $L_0 = 4.7 \mu\text{H}$ during the step in $I_{out}$ . Dottom. 106                                                                                                         |

| Figure 5-6: Output voltage transient response for $L_0 = 4.7 \mu\text{H}$ and 10 $\mu\text{H}$ and $V_{\text{bat}} = 2.9 \text{V}107$                                                                             |

| Figure 5-7: Output voltage transient response for $L_0 = 4.7 \mu\text{H}$ and 10 $\mu\text{H}$ and $V_{\text{bat}} = 5.1 \text{V}108$                                                                             |

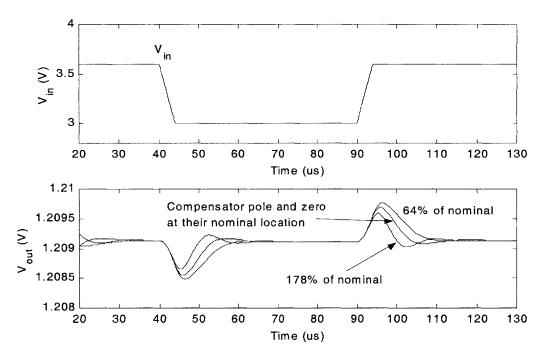

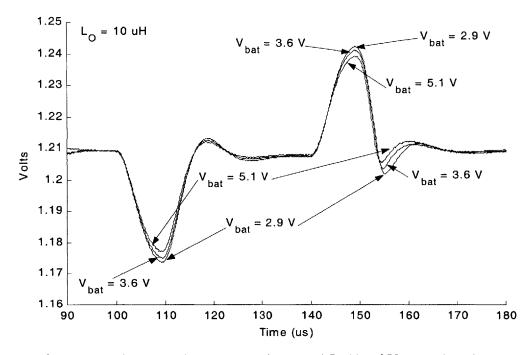

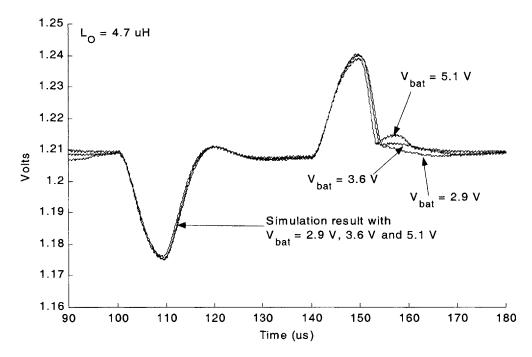

| Figure 5-8: Output voltage transient response for $L_0 = 4.7 \ \mu\text{H}$ and $V_{\text{bat}} = 2.9 \ \text{V}$ , 3.6 V and 5.1 V.                                                                              |

| $11gure 5 \text{ of output voltage transient response for } 20^{-1.7}  \mu\text{Trans } v_{\text{part}} = 2.5         $                                                                                           |

|                                                                                                                                                                                                                   |

| Figure 5-9: Output voltage transient response for $L_0 = 4.7 \mu H$ and 10 $\mu H$ and $V_{bat} = 5.1 V109$  |

|--------------------------------------------------------------------------------------------------------------|

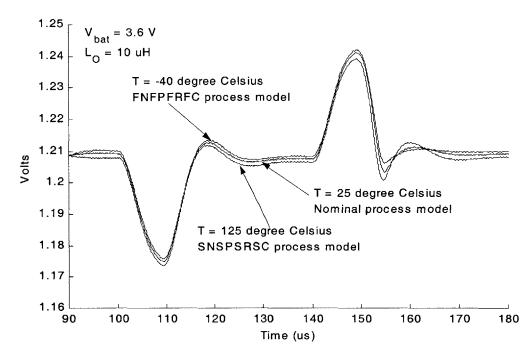

| Figure 5-10: Output voltage transient response at different process/temperature extremes with                |

| $V_{bat} = 3.6 \text{ V} \text{ and } L_0 = 10 \ \mu\text{H}112$                                             |

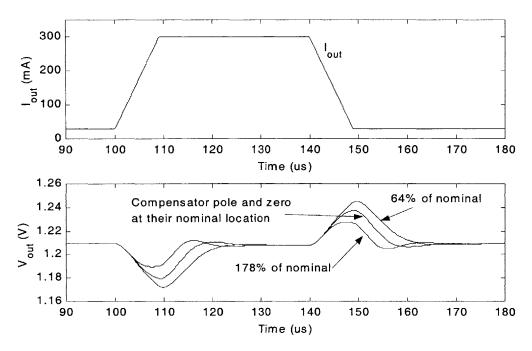

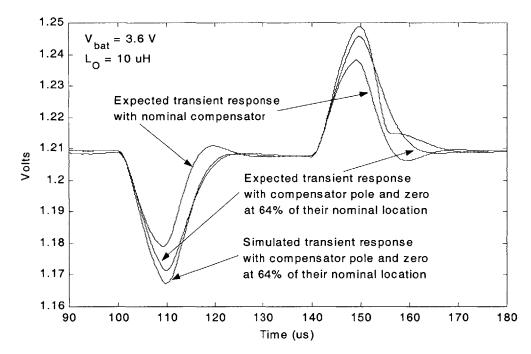

| Figure 5-11: Output voltage transient response with compensator pole and zero at 64% of their                |

| nominal value                                                                                                |

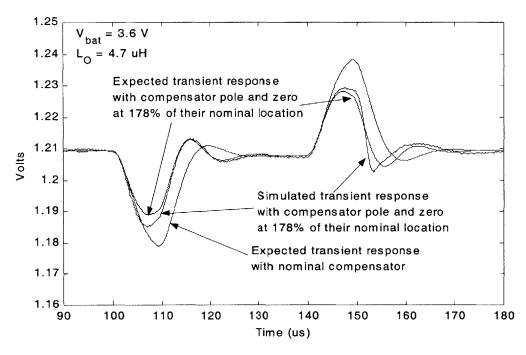

| Figure 5-12: Output voltage transient response with the compensator pole and zero at 178% of                 |

| their nominal location116                                                                                    |

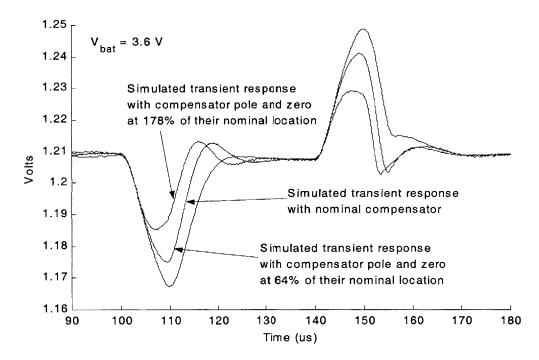

| Figure 5-13: Output voltage transient response across the range of the compensator pole and zero             |

| location116                                                                                                  |

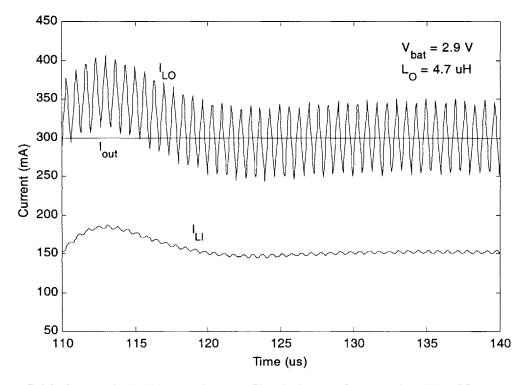

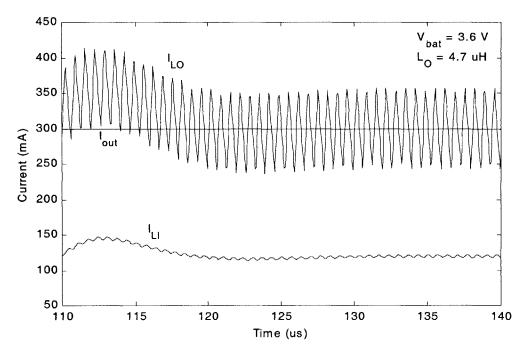

| Figure 5-14: Current in the input and output filter inductors for $L_0 = 4.7 \mu H$ and $V_{bat} = 2.9 V117$ |

| Figure 5-15: Current in the input and output filter inductors for $L_0 = 4.7 \mu H$ and $V_{bat} = 3.6 V118$ |

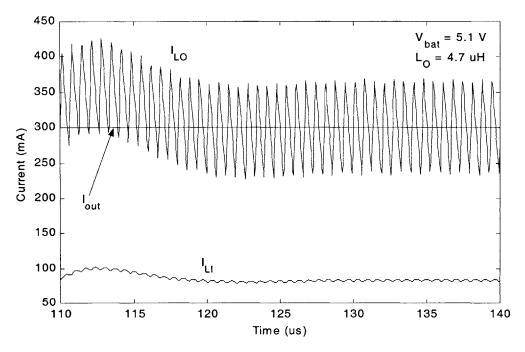

| Figure 5-16: Current in the input and output filter inductors for $L_0 = 4.7 \mu H$ and $V_{bat} = 5.1 V119$ |

| Figure 5-17: Ripple current in the input filter inductors for $L_0 = 4.7 \mu H$ and $V_{bat} = 5.1 V120$     |

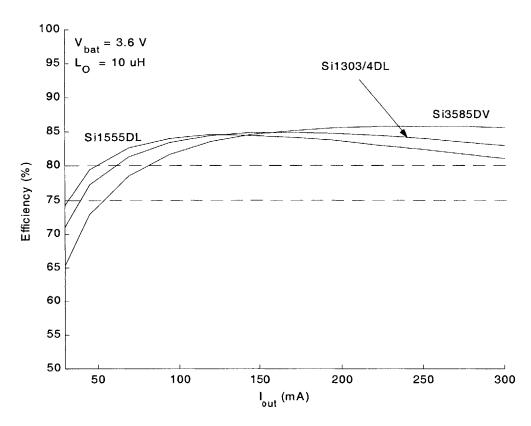

| Figure 5-18: Efficiency of the closed loop buck converter for different power MOSFETs taken                  |

| over the entire output current range121                                                                      |

| Figure 8-1: Loss model for voltage driven complementary MOSFET pairs in a synchronously                      |

| rectified buck converter126                                                                                  |

| Figure 9-1: Test setup for measure average inductor power loss                                               |

|                                                                                                              |

## List of Tables

| Table 2-1: Gate charge, capacitances and resistances of different power MOSFETs | 22  |

|---------------------------------------------------------------------------------|-----|

| Table 2-2: Surface mount power inductor characteristics                         |     |

| Table 2-3: Parasitic inductances due to package size of TDK ceramic capacitors  | 32  |

| Table 2-4: Input Filter Inductors                                               | 36  |

| Table 2-5: Input Filter performance for different component values              | 38  |

| Table 4-1: Transistor properties for TSMC's L46 CMOS process                    | 69  |

| Table 4-2: RS-latch logic                                                       | 88  |

| Table 4-3: Turn-on and Turn-off sequence for the power MOSFETs.                 | 94  |

| Table 4-4: Power consumption in the control IC.                                 | 98  |

| Table 5-1: Component Values used in ADICE simulations                           | 100 |

| Table 5-2: Peak efficiency and efficiency at minimum and maximum output current | 122 |

## **1** Introduction

### **1.1** Power consumption in a cell phone

Modern day cell phones use a digital signal processor (DSP) to process voice and data signals. DSPs are being fabricated using smaller and smaller process geometries in order to increase their transistor density and processing power. The smaller transistors have a lower maximum voltage rating and thus the supply voltage for DSPs continue to decrease. A cell phone also contains a power amplifier to amplify signals for transmission from the cell phone to the base station. The power amplifier typically requires a supply voltage greater than 3 V. In order to save space and reduce weight, a cell phone is typically powered with one 3.6 V lithium ion (Lilon) battery cell or three 1.2 V nickel metal-hydride (NiMH) battery cells. A linear regulator steps the 3.6 V battery voltage down to a lower voltage for the DSP. The efficiency of a linear regulator is approximately equal to its output voltage divide by its input voltage. The current Analog Devices (ADI) DSP runs at a supply voltage of 1.8 volts and uses up to 100 mA of current. In this case the regulator is only 50% efficient. This was satisfactory because the DSP typically draws less than 30 mA and thus the power lost in the regulator (< 54 mW) was acceptable. In addition, linear regulators take up little space on a printed circuit board (PCB) and produce little noise so do not interfere with sensitive RF and mixed-signal circuitry in the cell phone.

As supply voltages continue to decrease the amount of power lost in the regulator becomes unacceptable. The next generation ADI DSP can run at 1.2 V from a 3.6 V battery and has a rated maximum current draw of 300mA. The DSP is designed for data intensive applications (e.g. wireless internet) and will consume large amounts of current for longer periods of time. GSM cell phones transmit and receive voice and data information in 577 µsec blocks of time called slots. 8 slots are put together to create a frame. Standard voice only phones use 3 out of the 8 slots in a frame for transmitting and receiving data. In the future more data intensive schemes, such as GPRS or EDGE, can use up to 6 out of the 8 slots. The DSP in these cell phones can draw 300 mA of current during each of the 6 slots used and could draw close to 300 mA all the time. Thus the average current consumed during a frame can be more than 225 mA. If a linear regulator was used to power the DSP in this case, the efficiency would be only 33% and more than 560 mW would be lost in the regulator. This is not only a severe drain on the battery, but can also cause overheating of the cell phone.

## 1.2 Why use a DC/DC converter?

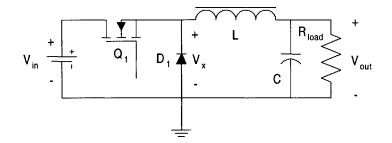

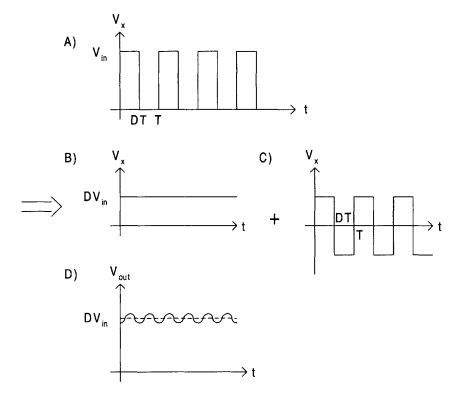

To step down the supply voltage for the DSP efficiently, a high frequency switch-mode DC/DC converter is proposed as a possible solution. The step-down converter, also known as a buck converter, uses a switch and a diode to produce a square wave voltage waveform across a filter network (Figure 1-1). The square wave can be thought of as having a DC component equal to the duty cycle, D, times the input voltage and a high frequency ripple component. The square wave is applied to a low pass LC filter which allows the DC component to pass, but attenuates the voltage ripple to an acceptable level (Figure 1-2). Ideally, the switches, inductor and capacitor do not dissipate any power and the converter is 100% efficient. However, real components dissipate power and thus the attainable efficiencies of DC/DC converters is less, typically around 70-90%.

While a DC/DC converter of this type is potentially very efficient, there are some important issues that must be resolved before it can be used on a cell phone. The primary concern is with noise generated from the switching power MOSFET. The sharp rise times of the square wave voltage pulses can lead to conducted and radiated electromagnetic interference (EMI). The noise from the converter can adversely effect the proper operation of the radio and other sensitive analog circuitry in the phone. This interference is not only at the switching frequency of the converter but also at harmonics that extend into the hundreds of MHz. The size of the converter is another important design constraint. Cell phones are small devices with very tightly packed circuit boards where space is at a premium. DC/DC converters can require large, bulky input and output filters that take up valuable space. In order to reduce the size of the filter components, the converter needs to be switched at very high frequencies (> 1MHz). However care must be taken so that capacitive losses in the power transistor and core losses in the inductor, which increase with switching frequency, do not severely degrade converter efficiency.

Figure 1-1: A buck converter employing a MOSFET switch and a free wheeling diode. The LC filter attenuates the AC component of the square wave voltage  $V_x$  to produce a DC voltage with a small ripple voltage.

**Figure 1-2:** Buck converter waveforms. A) The square wave voltage  $V_x$  across the diode. B) DC component of the diode voltage. C) AC component of the diode voltage. D) The LC filter attenuates the AC component, leaving a DC voltage with a small ripple at the output.

## 1.3 Organization

This thesis covers the design of a high frequency buck converter and an integrated circuit controller for the converter. Chapter 2 discusses the issues involved in designing the power stage, input filter and output filter for the buck converter. The emphasis is on the losses in real devices and the effects their parasitic components have on the design of high frequency switch-mode power supplies. The design of the feedback control system using the state-space averaged model of the buck converter is presented in chapter 3. The design of the control chip is discussed in chapter 4. The integrated circuit is design using TSMC 0.25 µm CMOS process. The overall function of the control chip is describes as well as detailed explanations of the analog and digital sub-blocks. Chapters 5 present the converter to be simulated and the simulation results. The simulation is done on Analog Devices' spice simulator ADICE.

## **2** Buck Converter Design

## 2.1 Specifications for the buck converter

The DC/DC converter, including its control circuitry, must run off a 3.6 volt Lilon or NiMH battery. The input voltage can range from 2.9 volts when the battery is almost drained to 4.2 volts when the Lilon battery is charging or 5.1 volts when the NiMH battery is charging. At the highest power setting, the power amplifier draws 1 amp from the battery for 177 µsec when the phone is transmitting data. This may cause the input voltage to drop by as much as 600 mV with a rise/fall time of 3.7-15 µsec. The converter must be able to maintain output voltage regulation in the presence of these input voltage pulses. The converter must produce an output voltage of 1.2 volts with less than 1% steady state error and no more than 5 mV of peak-to-peak voltage ripple. The converter must be able to supply 30 mA - 300 mA of output current and have less than a 5% overshoot and a 20 µsec settling time to a current load step of 30 mA - 300 mA in 9 µsec. The target efficiency of the converter is 70% with a minimum allowable efficiency of 50%. Typical ambient operating temperature is 25 °C, but the converter has to be able to operate between -40 °C and 85 °C.

A mixed-signal IC provides the D/A and A/D conversion necessary for the DSP to communicate with the radio. The D/A converter in the mixed-signal IC operates at 6.5 MHz with a bandwidth of ±100 kHz but is sensitive to noise in frequency bands centered at integer multiples of 6.5 MHz. This is because the frequency content of the digital signal is repeated every 6.5 MHz in the analog domain. Interference in these bands can mix down to DC during a transmission burst and degrade the outgoing signal. Two other frequencies that are very sensitive to noise are 13 MHz and 26 MHz. 13 MHz is the frequency of the system clock, and 26 MHz is the operating frequency of the receiver A/D converter (using the rising and falling edge of the system clock). In order to reduce interference, it is required that there be no switching noise within 500 kHz of 6.5, 13 and 26 MHz. Thus there can be no switching harmonic falling in the following frequency

bands: 6-7 MHz, 12.5-13.5 MHz and 25.5-26.5 MHz. Switching frequencies that satisfy this requirement are 1.5, 2.5 or 3 MHz.

The PCB trace from the battery to the converter is usually the largest radiator of EMI, basically acting like an antenna. In order to reduce EMI, an input filter may be used to reduce the input current ripple to an acceptable level. Input filters that reduce the input current ripple to 1, 5 and 10 mA when the converter draws maximum load current will be designed and evaluated.

## 2.2 Power Stage

### 2.2.1 Pass transistor

The buck converter of Figure 1-1 shows a NMOS device as the pass transistor. The pass device can be either an NMOS or PMOS transistor. An NMOS transistor has lower input, output and miller capacitance than a PMOS with the same on-state resistance. This is important for good efficiency at high frequency and low output power, where capacitive losses dominate. The drawback for NMOS devices is that they require a charge pump to produce sufficient gate to source voltage to turn on. This requires two external components: a schottky diode and capacitor. Unfortunately, the maximum voltage the control IC can withstand is 5 V. The NMOS device would have to be charged to  $2 \times V_{bat} = 7.2$  volts to properly turn on. The drive for PMOS transistors, on the other hand, can be ground referenced. Thus, a PMOS transistor will be used as the pass device.

### 2.2.2 Synchronous rectification

The loss due to diode forward voltage drop is too large for such a low voltage application. The power loss as a percentage of output power due to the forward voltage drop of the freewheeling diode is:

$$\frac{P_{diode}}{P_{out}} \approx \frac{(1-D)V_{diode}}{V_{out}}$$

(2-1)

For an output voltage of 1.2 V, duty cycle of 1/3 and a schottky diode with 0.4 V forward voltage drop, the diode power loss is 22% of output power. In order to achieve 70% efficiency,

$$\frac{P_{out}}{P_{out} + \sum Losses} \ge 0.7$$

(2-2)

This means that total losses must be less than 43% of output power at a given output current. The freewheeling diode contributes half of the total losses allowed.

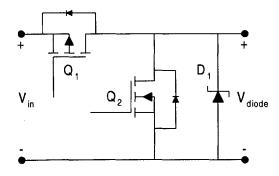

To remedy this, an NMOS power device is used in parallel with a schottky diode. The use of a MOSFET as a rectifying device in place of a freewheeling diode is known as synchronous rectification. The synchronous rectifier will be an NMOS transistor because it can be switched using a ground-referenced driver. However, using the MOSFET alone as a rectifier would also cause problems. If the NMOS rectifying device is turned on before the PMOS device is fully off, then power rail is shorted to ground (a shoot-through condition) creating a surge of current that can cause EMI and destroy the transistors. In order to prevent this the NMOS device is kept off while the PMOS device is turned off completely, letting the body diode of the NMOS device conduct and act like a freewheeling diode. Once the body diode is conducting full load current we can turn on the NMOS switch. We can then turn off the NMOS switch, let its body diode carry the output current and then turn on the PMOS switch. However, the reverse recovery loss in this body diode would be excessive and the reverse recovery time would be too long (30-50 ns) for such a fast switching converter. The body diode also has a high forward voltage, typically 0.8-1.2V. To prevent the body diode of the NMOS from conducting a schottky diode is added in parallel to act as a freewheeling diode between the turn on and turn off times of the power transistors. Low power schottky diodes typically have a forward voltage drop of 360 to 400 mV and a reverse recovery time of 10 ns.

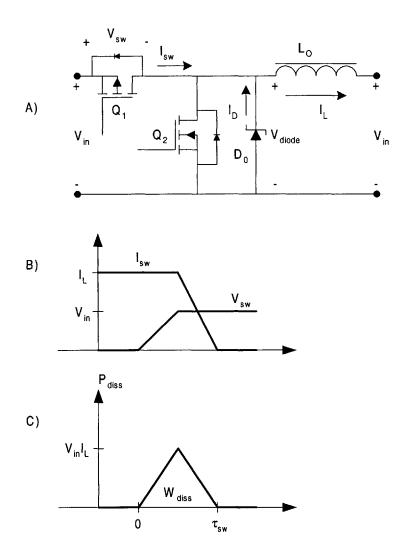

Figure 2-1: Power stage for the buck converter using a PMOS pass transistor, NMOS synchronous rectifier, and a schottky diode for free–wheeling conduction when both power MOSFETS are off.

#### 2.2.3 Losses in the power stage

In order to properly select the transistors for the power stage, the losses in the power MOSFETs must be analyzed. There are three main loss mechanisms in power MOSFETs: capacitive loss, switching transition loss and conduction loss.

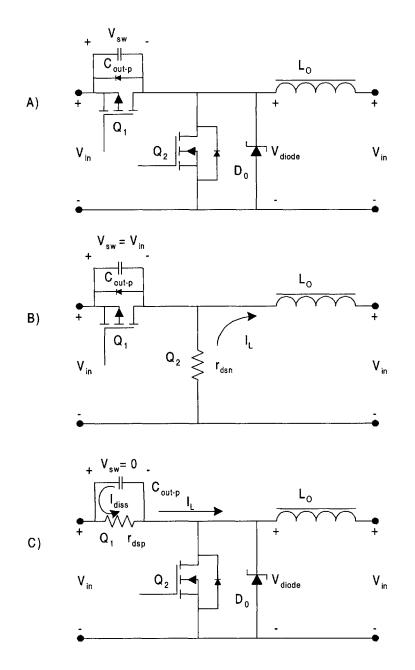

There are two types of capacitive loss, gate drive and capacitive turn-on loss. The gate drive loss is due charging and discharging the input capacitance of the power MOSFET. The total gate charge required to put a certain voltage across the gate and source is usually specified because the input capacitance is nonlinear [13]. Capacitive turn-on loss depends on the size of output capacitance. This capacitance is charged when the MOSFET turns off and is discharged when it is turned on (Figure 2-2). These losses are independent of the current through the MOSFET and depend only on switching frequency.

The switching transition losses are due to currents flowing through the MOSFET when their drain to source voltage rises and falls [9]. The smaller the input capacitance the less charge it takes to reach the turn-on gate voltage and the shorter the time in which there is current through the FET while a large voltage is across the drain and source (Figure 2-3). The power dissipated in the switching transition loss depends on frequency and current through the MOSFET. See Appendix A for a more detailed analysis of losses in MOSFETs.

**Figure 2-2:** Capacitive turn-on loss in the PMOS pass device (Q<sub>1</sub>). A) Power stage and inductor. The PMOS transistor is shown with its output capacitance across its drain and source. B) When the NMOS is conducting the PMOS device is off. The voltage across  $r_{dsn}$  is very small (~ 100 mV) and  $C_{out-p}$  charges up to  $V_{in}$ . C) When the PMOS device turns on  $C_{out-p}$  discharges through the on-state resistance  $r_{dsp}$  dissipating  $\frac{1}{2}C_{out-p}V_{in}^{-2}$  every cycle.

**Figure 2-3:** Switching transition loss when the PMOS device turns off. A) Power stage and inductor. B) In order for the current through the PMOS device to go to zero the schottky diode must turn on and start to carry the inductor current. In order for this to happen the voltage across the PMOS device,  $V_{sw}$  must rise to  $V_{in}$ . Since  $V_{in} = V_{sw} + V_{diode}$ , the schottky diode turns on and starts to conduct once  $V_{sw}$  equals  $V_{in}$  and the voltage across the diode is zero. C) The total energy dissipated while the PMOS device switches off is  $W_{diss} = \frac{1}{2}V_{in}I_L\tau_{sw}$ . The power dissipated in a cycle is the switching frequency, f, times  $W_{diss}$ . The lower the input capacitance the shorter  $\tau_{sw}$  is. A similar power loss occurs when the PMOS device turns on.

Conduction loss is the third major loss mechanism in the converter. It is proportional to the on-state resistance of the power MOSFET. The input and output capacitances are proportional to the conduction area of the MOSFET while the on-state resistance is inversely proportional to the conduction area. Thus, there is always a trade off between the two loss mechanisms when selecting MOSFETs. Since the converter's switching frequency is very high, the frequency dependent losses must be kept small. Thus, it is desirable to switch at the minimum allowed frequency of 1.5 MHz. Also, the converter is designed to carry low amounts of current (< 1A). Therefore, MOSFETS with small input capacitances (< 500 pF) and high on state resistances (>  $0.2\Omega$ ) will be used.

Vishay Siliconix Si1555DL, Si1303/4DL and Si3585DV are suitable complementary power MOSFETs. The Si1555DL contains PMOS and NMOS transistors in a SOT-363 package while the Si3585DV transistor pair comes in a TSOP-6 package. The Si1303DL and Si1304DL each come in a SOT-323 package. The B0520WS from Diodes Inc. and the ZHCS400 from Zetex are small surface mount schottky diodes that come in a SOD-323 package and are suited for low power, high frequency applications. Their forward voltage drops are 360 and 400 mV at 300 mA, respectively. These diodes have small junction capacitances (< 100 pF at 3.6 V reverse voltage), very small leakage currents and reverse recovery times of 10 ns.

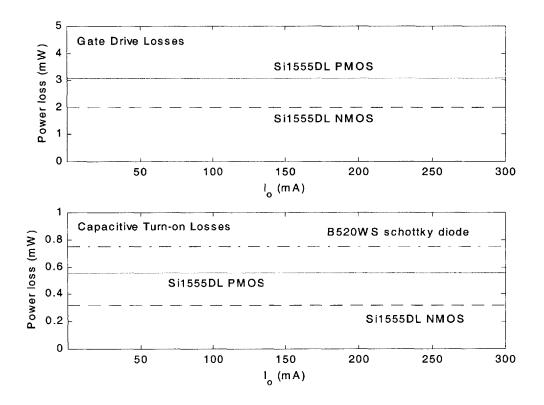

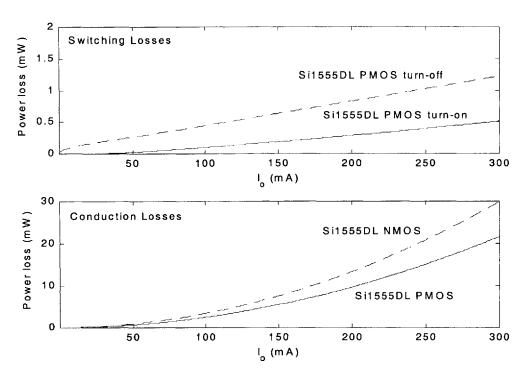

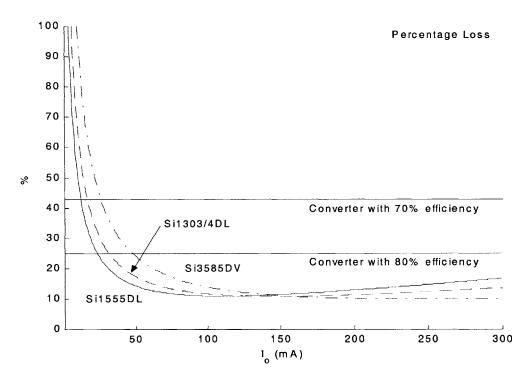

Table 2-1 compares the gate charge, input capacitance, output capacitance and on-state resistance of the three MOSFET pairs. The table shows the tradeoff between on-state resistance and input capacitance with the Si1555DL MOSFET pair having the smallest input capacitance and highest on-state resistance and the Si3585DV MOSFET pair having the largest input capacitance and lowest on-state resistance. Figures 2-4 and 2-5 show the various losses for the SI1555DL pair of transistors computed using the methods of Appendix A. Notice that the gate drive and capacitive turn on losses are independent of output current while both the switching transition and conduction losses increase with output current. Figure 2-6 compares the total losses in the power stage as a percentage of output power ( $1.2V \times I_{out}$ ) over an output current range of 3 to 300 mA. All three MOSFET pairs have a loss of 10% of output power at then 150 mA of output current. Below 150 mA, the Si1555DL, with its small capacitance, has the least amount of power loss while above 150 mA, the Si3585DV MOSFET pair, with its small on-state resistance has the least amount of power loss. Thus, it is possible to optimize the converter for operation at

high or low currents depending on the time averaged profile of the DSP current draw. Figure 2-6 also shows the maximum amount of power loss that the converter can have in order to be 70% and 80% efficient. If the loss in the input and output filters and the control circuitry are kept low, then it is feasible to design a converter with over 80% efficiency.

| MOSFET        | Gate Charge (nC)<br>@ $V_{ds} = V_{gs} = 3.6V$ | $\begin{array}{c} C_{in} \left( pF \right) \\ @ V_{ds} = 0 \end{array}$ | $\begin{array}{c} C_{out} \left( pF \right) \\ @ V_{ds} = 0 \end{array}$ | $\frac{R_{ds-on} (\Omega) @ 25^{\circ} C}{and V_{gs} = 3.6 V}$ |

|---------------|------------------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------------------------|

| Si1555DL PMOS | 2.05                                           | 154                                                                     | 100                                                                      | 0.67                                                           |

| Si1303DL PMOS | 2.7                                            | 230                                                                     | 150                                                                      | 0.45                                                           |

| Si3585DV PMOS | 4                                              | 432                                                                     | 243                                                                      | 0.28                                                           |

| Si1555DL NMOS | 1.33                                           | 84                                                                      | 64                                                                       | 0.47                                                           |

| Si1304DL NMOS | 1.722                                          | 183                                                                     | 183                                                                      | 0.355                                                          |

| Si3585DV NMOS | 2.9                                            | 250                                                                     | 175                                                                      | 0.16                                                           |

Table 2-1: Gate charge, capacitances and resistances of different power MOSFETs

Figure 2-4: Top: Si1555DL PMOS and NMOS gate drive losses. Bottom: Capacitive turn-on losses in the Si1555DL PMOS and NMOS transistors and the B0520WS schottky diode.

Figure 2-5: Top: Turn on and turn off switching losses for the Si1555DL PMOS pass transistor. Bottom: Conduction loss in the Si1555DL PMOS and NMOS transistors.

**Figure 2-6:** Power loss as a percentage of output power for Si1555DL, Si1303/4DL, and Si3585DV transistors as output current is varied. The solid line at 25% corresponds to an 80% efficient converter and the solid line at 43% corresponds to a 70% efficiency converter.

## 2.3 Output Filter Design

### **2.3.1** Filter size requirements

The output filter is a second order LC filter that is designed to attenuate the AC component of the square wave produced by the power stage while allowing the DC component pass through. The inductor integrates the square wave voltage into a triangular current waveform that has a DC current and a triangular current ripple. The magnitude of the current ripple is give by:

$$\Delta I_{p-p} = \frac{(1-D)TV_{out}}{L_0}$$

(2-3)

The DC current from the inductor flows directly into the load resistor to produce  $V_{out}$ . The ripple current will flow into the capacitor because at high frequency the capacitor has much lower impedance than the load resistor. The high frequency characteristics of the capacitor determine the peak-to-peak voltage ripple. The equivalent series resistance (ESR) and equivalent series inductance (ESL) of the capacitor dominate at high frequency. If the self-resonant frequency (SRF) of the capacitor is at least an order of magnitude above the switching frequency and the ESR is low, then the capacitor acts as a capacitive impedance and the ripple voltage produced by the ripple current though it is given by:

$$\Delta V_{p-p} = \frac{(1-D)T^2 V_{out}}{8LC}$$

(2-4)

If the capacitor looks resistive at the switching frequency and above (i.e. ESR dominates) then the peak-to-peak ripple voltage is given by:

$$\Delta V_{p-p} = \Delta I_{p-p} \times ESR \tag{2-5}$$

However, above 1 MHz, most large capacitors (>  $10 \,\mu\text{F}$ ) are dominated by their ESL. In this case the ripple voltage can be approximated by:

$$\Delta V_{p-p} \approx \Delta I_{p-p} \times \omega_{switch} \times ESL$$

(2-6)

The energy storage requirement of the capacitor is also important for determining its size. The energy stored in the output filter capacitor should be greater than that of the inductor. Suppose the buck converter is supplying maximum output current to the DSP. If the DSP suddenly goes into sleep mode or is turned off the output current goes to zero. The current in the inductor will flow into the capacitor increasing the output voltage. If the inductor dumps all its energy into the capacitor the output voltage should not increase significantly. For a 5% change in output voltage:

$$0.5LI_{peak}^{2} + 0.5CV_{out}^{2} = 0.5C(V_{out} + \Delta V_{out})^{2}$$

(2-7)

Simplifying and ignoring second order terms, the above equation reduces to:

$$LI_{peak}^{2} + CV_{out}^{2} \approx C \left( V_{out}^{2} + 2V_{out} \Delta V_{out} \right)$$

(2-8)

Since  $\Delta V_{out} = 5\%$  of  $V_{out}$ , the requirement for the output filter capacitor becomes:

$$C \ge 10L \left(\frac{I_{\text{peak}}}{V_{\text{Out}}}\right)^2$$

(2-9)

Since the switching frequency is 1.5 MHz or higher, small values of output filter capacitance and inductance can be used. The size of the inductor is determined by the amount of ripple current in the converter. Typically, the peak-to-peak ripple should be 20% to 40% of the peak output current or 60–120 mA for this design. For D = 1/3, T = 1/(1.5 MHz), this corresponds to inductor sizes of 8.8  $\mu$ H for a current ripple of 60 mA and 4.3  $\mu$ H for a 120 mA current ripple. Standard inductor values of 4.7, 6.8 and 10  $\mu$ H are suitable. For an output ripple voltage of 5 mV and using a 10  $\mu$ H inductor, the capacitor needs to be at least 0.89  $\mu$ F using Equation 2-4. If the capacitor looks resistive at 1.5 MHz then its ESR must be less than 94 m $\Omega$  (Equation 2-5) and if it looks inductive then its ESL must be less than 10 nH (Equation 2-6). However, in order to have enough energy storage, the capacitor value is larger than 7.56  $\mu$ F. Since the storage requirement for choosing the capacitor value is larger than the filter requirement any capacitor greater than 7.56  $\mu$ F will satisfy the filter requirement.

#### **2.3.2** Output filter inductor selection

There are three main issues in inductor selection. They are the self-resonance frequency, the current limit and the losses in the inductor. The first two parameters affect the physical size of the inductor while the third affects the efficiency of the buck converter.

The inductor should be chosen so that its self-resonance frequency (SRF) is at least an order of magnitude above the switching frequency. This is because the inductor integrates the square wave voltage produced by the power stage and a square wave can be reasonably approximated by its first ten harmonics. Beyond the SRF, the inductor's inter-winding capacitance dominates and acts as a short circuit at high frequency. This inter-winding capacitance is represented as a lumped capacitor across the terminals of the inductor (Figure 2-7). Typically, the larger the magnetic core of an inductor, the fewer number of windings it needs to achieve a given inductance. The fewer number of windings an inductor has, the smaller the overall inter-winding capacitance.

The current limit of an inductor specifies the current at which inductance drops by 20%. The inductance decreases because the inductor core is starting to saturate. It is critical that the sum of the ripple and DC output current not saturate the core. If the core saturates, the inductance will decrease dramatically and the ripple current will increase. This will lead to a higher output ripple voltage. Typically the inductor is chosen so that it can handle at least twice the output current without saturating the magnetic core. As in the case of the SRF, a larger magnetic core allows the inductor to store more flux without saturating and thus, handle more current.

Finally, the losses in the inductor must be analyzed. The resistance in the winding, represented as  $R_{DC}$  in Figure 2-7, should be kept small so that it does not contribute significant conduction loss. A good rule of thumb is that the power dissipated in  $R_{DC}$  should be less than 5% of output power at maximum output current. So at 300 mA, the output power is 360 mW. In order for conduction loss to be less than 5% of 360 mW, or 18 mW,  $R_{DC}$  should be less than 0.2  $\Omega$ .

**Figure 2-7:** Lumped parameter circuit model of a real inductor.  $R_{DC}$  is the DC resistance in the windings.  $C_{IW}$  is the inter-winding capacitance and  $R_{core}$  is a nonlinear resistor that represents the energy lost aligning the magnetic domains in the inductor core.

The loss in the inductor's magnetic core can be a significant source of loss at switching frequencies greater than 1 MHz. This loss is due to the energy required to realign the magnetic domains in the core as the current through the inductor changes. This energy is dissipated as heat and is represented as a nonlinear resistor,  $R_{core}$ , in parallel with the inductor in Figure 2-7. The core loss is dependent on the frequency and magnitude of the ripple current through the inductor. For a given core size, the larger the inductance the lower the loss. It is best to experimentally verify that losses from the core are small.

Surface mount power inductors should be used due to their small size, high SRF and large current handling capabilities. Table 2-2 shows the characteristic of 3 suitable 10  $\mu$ H surface mount inductors from Coilcraft, Wilco and Renco. The losses in these inductors were tested at 1.5, 2.5 and 3 MHz using the method described in Appendix B. The power loss as function of output current is shown in figures 2-8. Notice that the losses do not vary significantly with frequency. The core loss is proportional to frequency, so as the frequency goes up the core loss increases [12]. However, as the frequency increases the ripple current in the inductor decreases so that the overall loss slightly decreases. This will not be the case for all inductors so testing their losses is important.

| Inductor          | Value | DCR   | SRF   | I <sub>sat</sub> | Tolerance | Size (mm)     |

|-------------------|-------|-------|-------|------------------|-----------|---------------|

|                   | (µH)  | (Ω)   | (MHz) | (A)              |           | L×W×H         |

| Coilcraft DS1608C | 10    | 0.075 | 38    | 1                | ±20%      | 6.6×4.45×2.92 |

| Wilco SMPI20      | 10    | 0.08  | 23.5  | 1.02             | ±10%      | 4.5×3.96×4.29 |

| Renco RL-1608-S10 | 10    | 0.075 | 38    | 1                | ±20%      | 6.6×4.45×2.92 |

Table 2-2: Surface mount power inductor characteristics

Figure 2-8: Power loss vs. output current in the DS1608C, SMPI20 and RL-1608-S10 inductors at 1.5 MHz (top), 2.5 MHz (middle) and 3 MHz (bottom).

Figure 2-9: Power loss as a percentage of output power vs. output current in the DS1608C, SMPI20 and 1608-S inductors at 1.5 MHz.

Since the switching frequency of the converter is 1.5 MHz, Figure 2-9 shows the power loss as percentage of output power for the three 10  $\mu$ H as the output current varies from 30 to 300 mA. The loss percentage is relatively steady at about 5% from 30 to 300 mA. This is because the ripple current through the inductor is independent of output current.

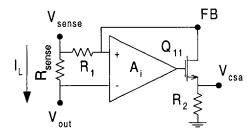

A sense resistor is often placed in series with the output filter inductor to sense the current through the inductor (Figure 2-10). Knowing the inductor current is important for overcurrent protection as well as enabling the use of current-mode control for regulating the buck converter's output voltage. Current-mode control will be discussed in Chapter 3. The sense resistor should be placed on the same side as the output filter capacitor. This is because the voltage across the diode is rapidly changing from 0 to  $V_{in}$ . Placing the sense resistor near the power stage would introduce noise in the current sense amplifier and prevent accurate sensing of the inductor current.

**Figure 2-10:** The sense resistor,  $R_{sense}$ , is placed in series with the output filter inductor,  $L_0$ . It is placed on the same side as the output filter capacitor,  $C_0$ , to minimize noise due to the diode voltage switching between 0 and  $V_{in}$  rapidly.

**Figure 2-11:** Power loss, as a percentage of output power, in the 0.15  $\Omega$  sense resistor, the RL-1608-S10 inductor and the total loss in the inductor-resistor pair.

The sense resistor should be small enough so that conduction losses due to it are small. Figure 2-11 shows the conduction loss as a percentage of output power for a 0.15  $\Omega$  sense resistor. It also shows the total loss percentage of the inductor-sense resistor combination for the RL-1608-S10 inductor. The sense resistor adds less than 1% of loss when output current is less than 100 mA and up to 4% at the maximum output current of 300 mA.

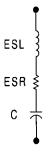

**Figure 2-12:** Lumped parameter circuit model of a real capacitor. ESL is the equivalent series inductance and ESR is the equivalent series resistance of the capacitor leads. These parasitic elements make the capacitor look inductive or resistive at high frequencies.

### 2.3.3 Output filter capacitor selection

For switching frequencies above 1 MHz, attention must be paid to ESR and ESL of filter capacitors. These parasitic elements limit the effectiveness of a capacitor at high frequencies and are shown in series with the capacitor in Figure 2-12. There are two possible choices of filter capacitors: tantalum electrolytic chip capacitors and multi-layer ceramic chip capacitors. Suppliers include Kemet, AVX and TDK and Taiyo Yuden.

Tantalum capacitors provide very large capacitances, typically 6.8 – 470  $\mu$ F, in EIA 3216-7343 sized packages. An EIA 7343 corresponds to a package that is 7.3 mm long and 4.3 mm wide. These capacitors look resistive above 100kHz and inductive above 5-10 MHz. Since the first few harmonics of the switching frequency (1.5, 3, 4.5 and 6 MHz) usually fall within the resistive impedance range the output ripple voltage can be approximated to be equal to the capacitors ESR times the peak-to-peak inductor ripple current. As calculated previously, the ESR must be less than 94 m $\Omega$  in order for the ripple voltage to be less than 5 mV. Tantalum capacitors with ESRs less than 94 m $\Omega$  come in EIA 7343 size packages and have capacitance values of 100 to 470  $\mu$ F.

Multi-layer ceramic caps are much smaller in size, coming in EIA 0603-1210 size packages. For ceramic capacitors, an EIA 1210 size package is 0.12 by .1 inches or 3.2 mm by 2.5 mm. Ceramic capacitors have capacitance values up to 47  $\mu$ F for an EIA 1210 package. X7R

or X5R dielectric materials should be used due to their good temperature stability. The X5R and X7R dielectrics have a  $\pm 15\%$  capacitance variation from -55 to +85 °C and -55 to +125 °C respectively. These capacitors have excellent high frequency characteristics and have very small parasitic resistances (< 10 m $\Omega$  for a 10  $\mu$ F capacitor). The conduction loss for a capacitor with an ESR of 10 m $\Omega$  and 120 mA of ripple current is only 12  $\mu$ W.

The ESL of ceramic capacitors dominates at high frequencies but is typically less then 1 nH. Table 2-3 shows the parasitic inductances due to different package sizes for TDK capacitors. For a given package size, the ESL varies with capacitor value. Notice that there is a difference between the ESL of an 0508 package and an 0805 package even though their volumes are the same. The ESL is proportional to the width of the package leads. An 0508 package has a width of 2 mm while a 0805 package has a width of 1.25 mm. This why the 0508 package has a much lower ESL. Thus is always preferable to use capacitor packages with wide leads to reduce ESL.

The main drawback of ceramic capacitors is that they do not have as high a capacitance as the tantalum capacitors. Fortunately, since we are switching at very high frequencies, large capacitance values are not needed. At least 7.56  $\mu$ F is required for energy storage. EIA 0805 (2 mm × 1.25 mm) size packages can have capacitance values of 10  $\mu$ F. Currently, EIA 0508 packages have at most 1  $\mu$ F. Multi-layer ceramic capacitors are the best choice due to their small size and small ESR and ESL.

| EIA Code | Package size, L× W× H (mm) | Parasitic Inductance (nH) |

|----------|----------------------------|---------------------------|

| 0306     | 0.81×1.6×0.9               | 0.3-0.35                  |

| 0508     | 1.25×2×1.3                 | 0.3                       |

| 0603     | 1.6×0.81×0.9               | 0.6-0.8                   |

| 0612     | 1.6×3.2×1.5                | 0.4                       |

| 0805     | 2×1.25×1.3                 | 0.6-0.9                   |

| 1206     | 3.2×1.6×1.5                | 1.1-1.4                   |

| 1210     | 3.2×2.5×1.7                | 1.1-1.2                   |

Table 2-3: Parasitic inductances due to package size of TDK ceramic capacitors

**Figure 2-13:** The power stage is modeled as a current source that equals the inductor current when the pass transistor is on and equals zero when the pass transistor is off. The inductor current rises from  $I_{out} - \frac{1}{2}\Delta I_{p-p}$  to  $I_{out} + \frac{1}{2}\Delta I_{p-p}$ . This current source sees the battery impedance in parallel with the input capacitor,  $C_{I}$ .

## 2.4 Input Filter Design

### 2.4.1 Overview

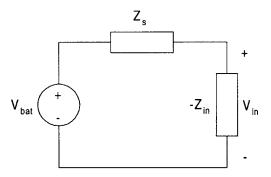

An input filter may be used to reduce the EMI generated from the power MOSFETS. The power stage of the buck converter can be modeled as a current source  $I_{in}$  that has a value of  $I_i$  when the pass transistor is on and 0 when the pass transistor is off (Figure 2-13). This square wave current has a DC value of  $DI_{out}$ . This current source sees the input filter capacitor and battery impedance in parallel. If the battery impedance is larger than the input capacitor impedance, then any ripple current through the battery can produce large voltage swings. These voltage swings will interfere with the supply rail of the cell phone. If the battery impedance is smaller than the input capacitor then most of the ripple current will flow through the PCB trace from the pass transistor to the battery. This trace will act as an antenna and radiate considerable amounts of EMI. This EMI will interfere with the radio and the D/A converter in the cell phone. As discussed is section 2.1, the D/A is sensitive to noise in frequency bands 200 kHz wide centered at multiples of 6.5 MHz. The EMI generated from the square wave current source,  $I_{in}$ , will have harmonics that fall into these bands. For instance, the 26<sup>th</sup> harmonic of  $I_{in}$  can cause interference at 39 MHz, which is the fourth multiple of 6.5 MHz.

Figure 2-14: Second order input filter consisting of inductor  $L_I$  and capacitor  $C_I$ .  $R_D$  and  $C_D$  make up the damping leg that reduces the peaking at the resonance frequency of the LC filter.