# Ge Photodetectors for Si Microphotonics

## Hsin-Chiao Luan

B. S. in Ceramic Engineering, Magna Cum Laude University of Washington, 1995

Submitted to the Department of Materials Science & Engineering in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February, 2001

| © Massachusetts Institute of Technology, 2001. All Rights Reserved.                                             |

|-----------------------------------------------------------------------------------------------------------------|

| Author  Department of Materials Science & Engineering  January 12, 2001                                         |

| Certified by Lionel Cooper Kimerling Thomas Lord Professor of Materials Science & Engineering Thesis Supervisor |

| Accepted by                                                                                                     |

MAY 1 4 2001

LIBRARIES

and the second of the second o

### **Ge Photodetectors for Si Microphotonics**

by

#### Hsin-Chiao Luan

Submitted to the Department of Materials Science & Engineering on January 12, 2001, in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### **ABSTRACT**

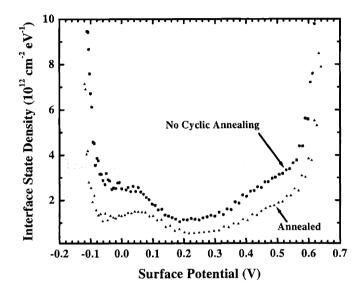

This thesis demonstrates the integration of pure Ge near-infrared photodetectors on Si. Ge epilayers were grown directly Si by on a two-step ultra-high-vacuum/chemical-vapor-deposition (UHV/CVD) process. This work conclusively proves that threading-dislocation densities in the Ge epilayers, measured both by plan-view transmission electron microscopy and etch-pit-density (EPD) counting, were reduced by cyclic thermal annealing. Additionally, Ge mesas with no threading dislocations as measured by EPD were also demonstrated. The removal of threading-dislocations can be attributed to the thermal stress induced dislocation glide and reactions. Using the annealed Ge epilayers grown on Si, p-i-n Ge photodetectors with maximum responsivities of 770 mA/W at 1.3 µm were fabricated. Finally, to allow the integration of Ge epilayers in Si microelectronic processing, the protection and passivation of Ge was investigated. The passivation was provided by the oxidation of Si epilayers grown on Ge. Capacitance-voltage characteristics of metal-oxide-semiconductor devices demonstrated the high quality of the passivation with the measured interface state density of 4 x  $10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup>.

Thesis Supervisor: Lionel Cooper Kimerling

Title: Thomas Lord Professor of Materials Science & Engineering

|  |  | , |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

### Acknowledgements

I would like to thank Professor Kimerling for his encouragement, guidance and inspiration. Kim is a wonderful thesis advisor. Working with Kim is always fun, challenging and rewarding. I am eternally grateful to him.

I would also like to thank Professor Jesus del Alamo for teaching the best device physics class. He has also provided invaluable advice throughout the last few years in our weekly SRC lunch meetings. I am deeply appreciative of that. I learned a lot about thinking like a materials scientist from taking Professor Sam Allen's class and reading his book. I also gained a lot of ideas about dislocations from talking to him. I would not have solved a lot of those dislocation problems without his help. I also need to express my appreciation to Professor Gene Fitzgerald. Gene is the kind of professor who spends a lot a time talking to students about any thing related to a student's life. He is always keen on research problems. I learned a lot about thinking critically from him.

Members of the EMAT group have enriched my life at MIT. Anu provided a lot of encouragement at times when my research went totally wrong. I would not have survived without our weekly conversation. I am also grateful for the huge amount of time she spend reviewing draft of this thesis. Jurgen gave me my first research problem that became the background of a lot of what I have included in this thesis. He gave me a heart warming wedding gift when Shingshing and I married each other on a cold New England winter day. I will always cherish that. Wada san shared a lot of his experience in semiconductor research with me. He took the role of my thesis advisor when Kim was not around. "Doo moo arigatoogozaimasu." My research is a continuation of Laura Giovane's thesis. I learned how to run our CVD from working with her and the need for growing Ge on Si came from the conclusion of her thesis. Over the last few years, we continued to work on several papers together. We have been a great team and I thank Laura for all her effort. I would also like to thank Desmond and Kidoo for being the most valuable research partners. Desmond, Kidoo and I started our PhD program in the same year. We have worked closely together on the Si microphotonics project and the result of our team is great. Desmond and Kidoo have brilliant plans for the future of Si microphotonics, and I wish them the best. Anand and Douglas have been my best buddies in the office. I have a lot of books and I have to confess that my books takes up too much space. I thank Anad and Douglas for all their understanding and constant encouragement. I would also like to thank Thomas Chen for his music and messages of life, Kevin for always being ready to lend a hand with experiments, Sajan for his French and Indian language lessons, Michal for sharing her life experiences on our trip to the Bell Labs, Xiaoman for getting me started with tripod polisher, Yutaka for sharing his TEM tricks, Kenichiro for his DLTS measurements, Nori for teaching me Kanseiben, Sang and Song for my first lesson in defects in semiconductors, Meghan and Jessica for helping with dislocation experiments, Pascal for sharing his knowledge in wafer bonding, Meyer for helping me learn about dislocations and wine, Mindy for helping me improve my writing skills and Ann for sharing her friendship.

My friends at the Universita degli Studi "Roma Tre" are the best research collaborators one can have. Lorenzo Colace, Gianlorenzo Masini, and Gaetano Assanto worked with me from 8AM to 8PM (sometimes 9PM) for two weeks on those Ge photdetectors. I learned so much from them. Working with them was like having my own personal tutors on optoelectronics. Beside helping me with measurement of photodetectors, they also demonstrated their technique at making the best home cooked Italian food. Without their hands-on demo, I would have never learned the art of Ragu sauce, Gelato, Spaghetti alla Carbonara, Prosciutto etc.... and that buffalo mozerella

A lot of good friends at MIT also provided a lot of help. Tom Langdo shared a lot of his experience with CVD with me. Our discussion about CVD is the key to fixing those challenging problems that kept we awake many nights. Vicky, Mat, Andy Kim, Mike all shared their knowledge about heteroepitaxy. Vab, Andy Wei and Keith gave me a lot of help. Minha, Chris, Stefan, Steve, Mat, Kidoo, and Tom are the best study group.

MTL and CMSE staff provided a lot of help. Mike Frongillo runs the best TEM lab. Vicky Diadiuk has always been supportive of my CVD project. Paul McGrath, Kurt Broderick, Joe DiMaria, Joe Walsh and Tom Takacs provided invaluable assistance at the most desperate times.

My undergraduate advisors gave me a lot of help. Professor Tom Pearsall taught my first class in optoelectronics. He took time to teach me how to use a curve tracer, a monochrometer and an MBE system while I was an undergraduate student. He helped me with graduate school applications by going through research papers published by professors at several universities and explaining the details to me. No undergraduate advisor could have been more helpful than Tom. Professor Mehmet Sarikaya spent his invaluable time teaching me some of those finer things about TEM. Professor Allen Miller trusted me and gave me admission to the MSE program at UW. Professor C. C. Lee at NTIT taught my first Intro to the MSE class. Without their willingnes to spend a little more time with me while I was an undergrad, I might have never found my way to MIT.

I would not have survived MIT without the help from my family. Martha, Betty, Peter, Henry, William, Bear, and Annie all have lent their hands at the hardest time. My parents gave me the opportunities to pursue my dream. They have supported my decision all the way. No words can described my gratitude to them. I would only hope the completion of this thesis would put more smiles on their faces. Finally, I would like to thank Shing-shing for her constant support and encouragement. This thesis is dedicated to her.

## **Table of Contents**

| 1 | Introdu   | ction                                                              | 17  |

|---|-----------|--------------------------------------------------------------------|-----|

|   | 1.1       | Motivation                                                         | 17  |

|   | 1.2       | Outline of thesis                                                  | 18  |

| 2 | Materia   | als selection and design considerations                            | 21  |

|   | 2.1       | Overview                                                           | 21  |

|   | 2.2       | Integration of near-infrared photodetectors on Si                  | 21  |

|   | 2.3       | Literature review                                                  | 23  |

|   | 2.4       | Requirements for photodetectors for Si microphotonics              | 29  |

|   | 2.5       | Materials selection                                                | 30  |

|   | 2.6       | Effect of threading-dislocations on the performance of photodiodes | 40  |

|   | 2.7       | Design of microphotonic photodiodes                                | 53  |

| 3 | Direct of | epitaxial growth of high quality Ge epilayers on Si                | 55  |

|   | 3.1       | Overview                                                           | 55  |

|   | 3.2       | Introduction                                                       | 55  |

|   | 3.3       | Experimental procedure                                             | 64  |

|   | 3.4       | Results and discussion                                             | 65  |

|   | 3.5       | Conclusion                                                         | 94  |

| 4 | Ge pho    | todetectors integrated on Si                                       | 95  |

|   | 4.1       | Overview and introduction                                          | 95  |

|   | 4.2       | Experimental procedure                                             | 95  |

|   | 4.3       | Results and discussion                                             | 100 |

|   | 4.4       | Conclusion                                                         | 120 |

| 5 | Passiva   | tion of Ge epilayer surface                                        | 123 |

|   | 5.1       | Overview                                                           | 123 |

|   | 5.2       | Introduction                                                       | 123 |

|   | 5.3       | Experimental procedure                                             | 125 |

|   | 5.4       | Results and discussion                                             | 127 |

|   | 5.5       | Conclusion                                                         | 134 |

| 6 | Summa     | ary and future work                                                | 135 |

| Bibliogra | aphy              | 143 |

|-----------|-------------------|-----|

| 6.2       | Future Work       | 135 |

| 6.1       | Summary of thesis | 135 |

## **List of Figures**

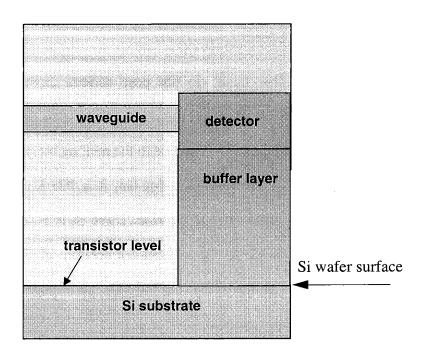

| Figure 1.1: A schematic of an application of Si microphotoinc technology: WDM                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------|

| photodetector receiver                                                                                                               |

| Figure 2.1: Integration challenge of photodetectors grown on a thick buffer-layer.                                                   |

| Depending on the thickness of the buffer layer, the photodetectors would typically be at                                             |

| least a few microns away from the transistor level. [5]                                                                              |

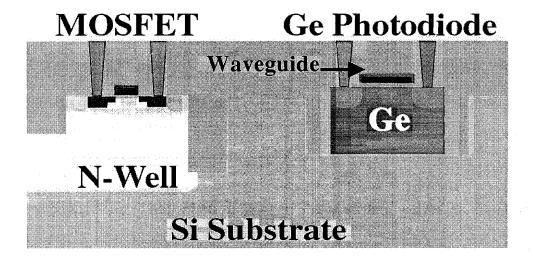

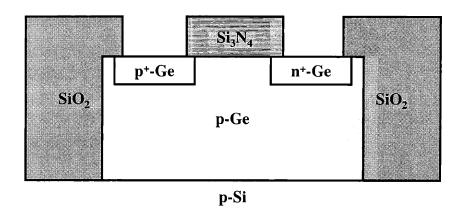

| Figure 2.2: A possible scheme for the integration of Ge photodetectors with Si MOSFETs                                               |

| and high dielectric contrast $\mathrm{Si}$ and $\mathrm{Si}_3\mathrm{N}_4$ waveguides. Selective area growth of $\mathrm{Ge}$ allows |

| the selective introduction of Ge into the Si substrate and therefore achieves large scale                                            |

| integration of microphotonic and microelectronic components33                                                                        |

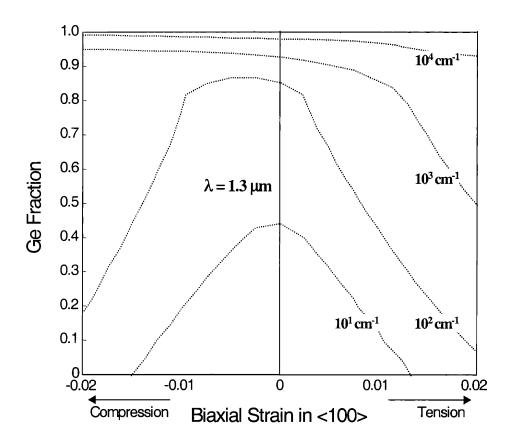

| Figure 2.3: Calculated absorption coefficient of SiGe as a function of strain and                                                    |

| composition at 1300 nm [5]                                                                                                           |

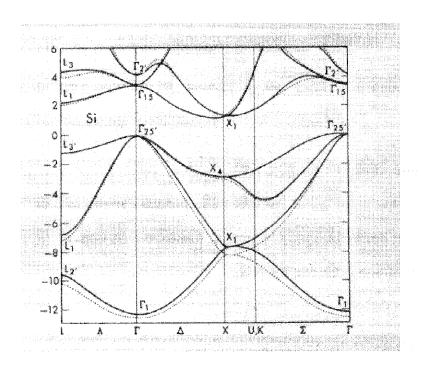

| Figure 2.4: Band structure of Si calculated by Chelikowsky and Cohen [224]36                                                         |

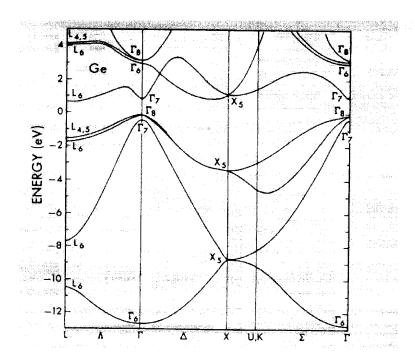

| Figure 2.5: Band structure of Ge calculated by Chelikowsky and Cohen [224]37                                                         |

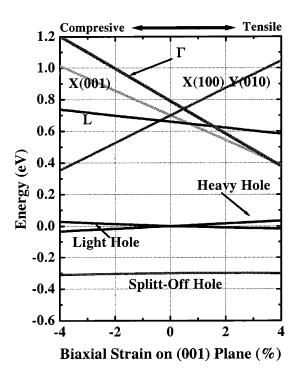

| Figure 2.6: The effect of biaxial strain on the band structure of Ge                                                                 |

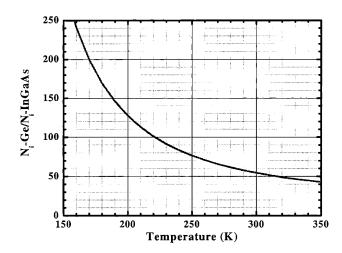

| Figure 2.7: The ratio of Ge intrinsic carrier concentration to the InGaAs intrinsic carrier                                          |

| concentration as a function of temperature45                                                                                         |

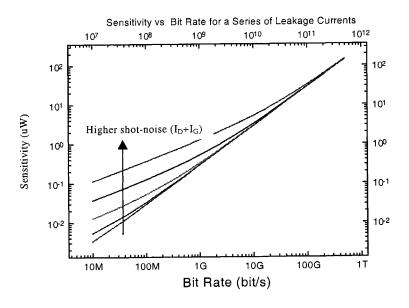

| Figure 2.8: Typical behavior of sensitivity versus bit-rate plot of a p-i-n receiver. At high                                        |

| bit-rate the contribution of shot-noise become less important                                                                        |

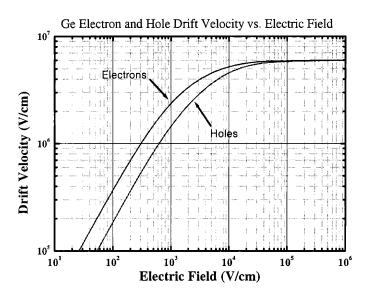

| Figure 2.9: Carrier drift velocity of electrons and holes in Ge calculated using equation                                            |

| 2.13                                                                                                                                 |

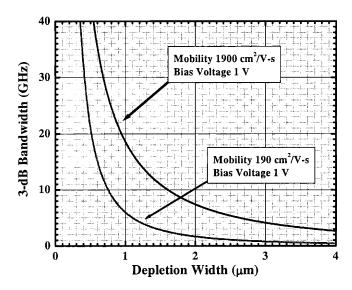

| Figure 2.10: 3-dB bandwidth of a p-i-n junction photodiode as a function of depletion                                                |

| width, mobility and bias voltage51                                                                                                   |

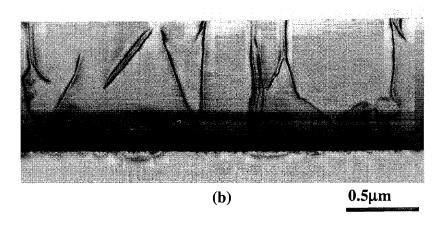

| Figure 3.1: (a) Plan-view TEM and (b) cross-sectional TEM pictures of Ge epilayers grown                                             |

| at 600°C67                                                                                                                           |

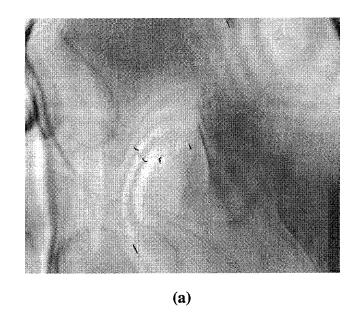

| Figure 3.2: a) Plan-view TEM and (b) cross-sectional TEM pictures of Ge epilayers grown                                              |

| at 600°C after annealing68                                                                                                           |

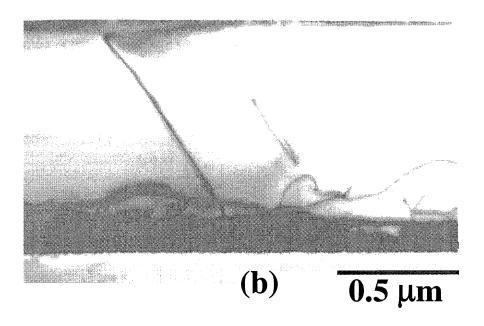

| Figure 3.3: Calculated normalized dislocation velocity in Ge epilayers grown on Si as a                                              |

| function of $T_L$ during cyclic annealing, assuming the system is relaxed at $T_H = 900$ °C. The                                     |

| calculated dislocation velocity has a peak at about $T_L = 830$ °C. An optimized cyclic                                                  |

|------------------------------------------------------------------------------------------------------------------------------------------|

| thermal annealing process should have a T <sub>L</sub> close this temperature71                                                          |

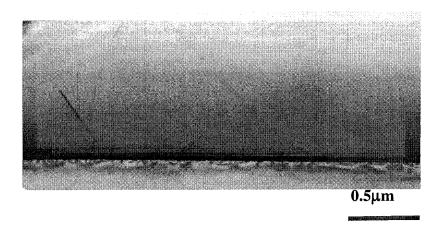

| Figure 3.4: Cross-sectional TEM picture of Ge epilayer grown on Si by two-step UHV                                                       |

| CVD process after cyclic thermal annealing between $T_H$ = 900°C and $T_L$ = 780°C72                                                     |

| Figure 3.5: Cross-sectional TEM pictures of Ge grown on Si at 600°C annealed in a rapid-                                                 |

| thermal annealing furnace for 60 seconds at (a) 650°C, (b) 750°C, (c) 850°C, and (d)                                                     |

| 930°C                                                                                                                                    |

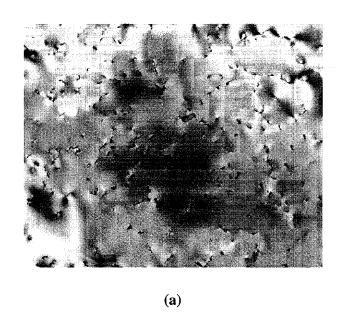

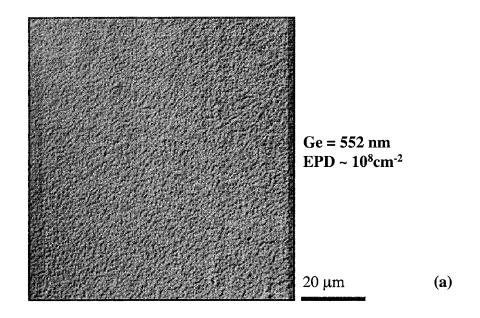

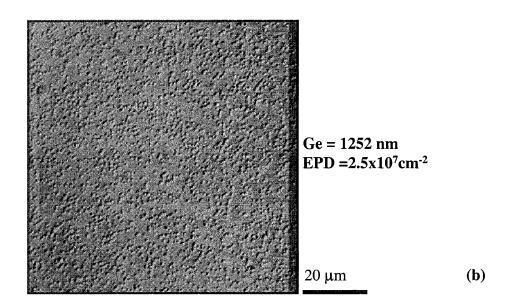

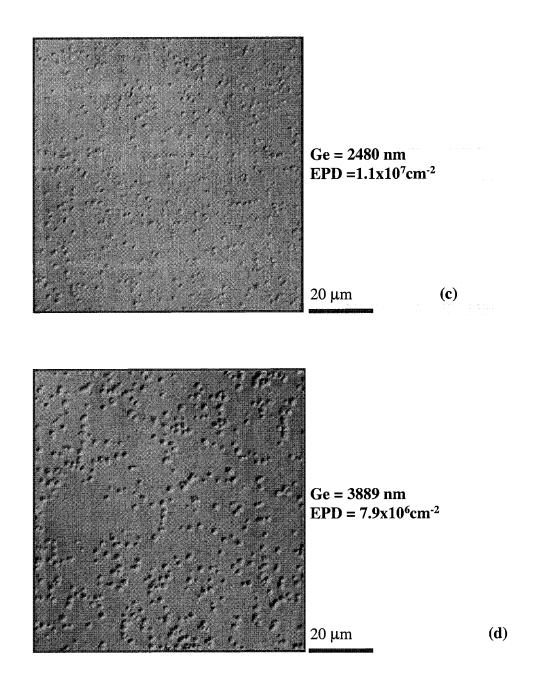

| Figure 3.6: EPD pictures of Ge epilayers grown on Si at 600°C after cyclic therma                                                        |

| annealing between $900^{\circ}\text{C}$ and $780^{\circ}\text{C}$ . (a) Thickness = $552 \text{ nm}$ , (b) Thickness = $1252 \text{ nm}$ |

| (c) Thickness = 2480 nm, (d) Thickness = 3889 nm                                                                                         |

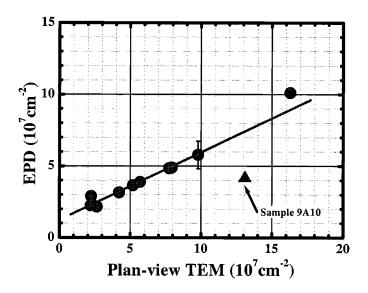

| Figure 3.7: Correlation between threading-dislocation densities measured by EPD and                                                      |

| plan-view TEM. The correlation between measurements by EPD and TEM is very good                                                          |

| except for the measurement of sample 9A1077                                                                                              |

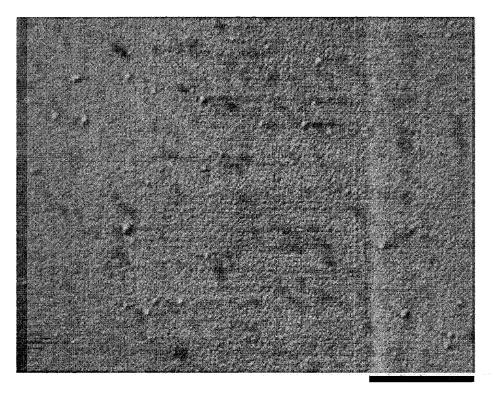

| Figure 3.8: Picture of sample 6A etched by the EPD etching solution. The picture is taken                                                |

| using an optical microscope79                                                                                                            |

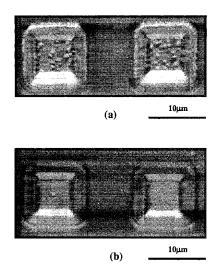

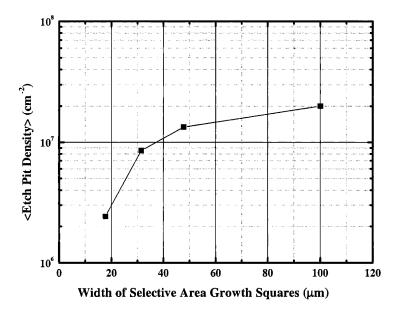

| Figure 3.9: EPD results of Ge selectively grown on patterned SiO <sub>2</sub> /Si wafers followed by                                     |

| annealing. (a) EPD picture of a sample annealed at 900°C for 10 min. (b) EPD picture of a                                                |

| sample cyclically annealed between 900°C and 100°C ten times81                                                                           |

| Figure 3.10: Average EPD vs. width of selective area growth squares81                                                                    |

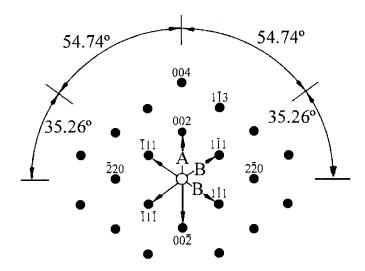

| Figure 3.11: Electron diffraction pattern for a diamond cubic structure when the [110] axis                                              |

| is aligned to the electron beam82                                                                                                        |

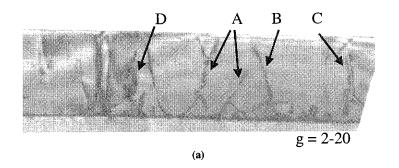

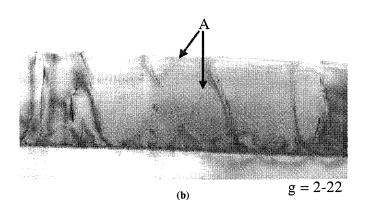

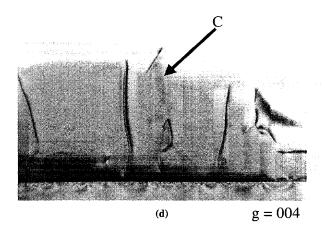

| Figure 3.12: Cross-sectional TEM pictures for the Burgers vector analysis of sample 6A                                                   |

| These pictures are two beam bright field images with five reflecting conditions: (a)                                                     |

| $g = [2\bar{2}0]$ , (b) $g = [2\bar{2}2]$ , (c) $g = [\bar{2}22]$ , (d) $g = [004]$ , (e) $g = [004]$ 85                                 |

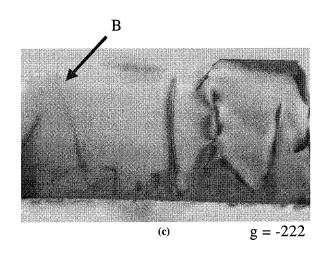

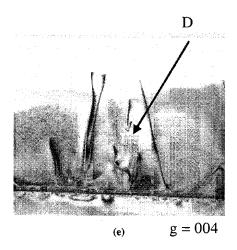

| Figure 3.13: Cross-sectional TEM pictures for the Burgers vector analysis of sample 6AC                                                  |

| These pictures are two beam bright field images with four reflecting conditions: (a)                                                     |

| $g = [2\bar{2}0]$ , (b) $g = [004]$ , (c) $g = [2\bar{2}2]$ , (d) $g = [2\bar{2}2]$ 86                                                   |

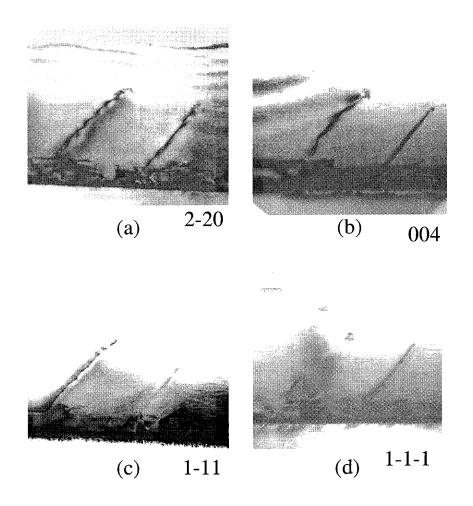

| Figure 3.14: Comparison of reaction kinetic model for threading-dislocation density                                                      |

| reduction to experimental data92                                                                                                         |

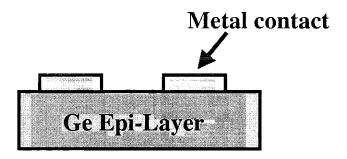

| Figure 4.1: Schematic of the MSM photodetectors97                                                                                        |

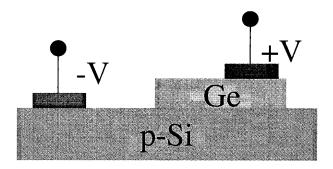

| Figure 4.2: Schematic of the mesa Ge/Si heterojunction photodetector97                                                                   |

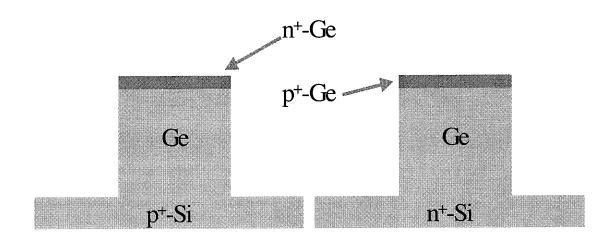

| Figure 4.3: Schematics of n-i-p Ge photodiode on p-Si substrate and p-i-n Ge on n-Si                     |

|----------------------------------------------------------------------------------------------------------|

| substrate98                                                                                              |

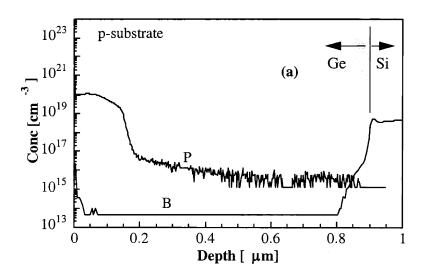

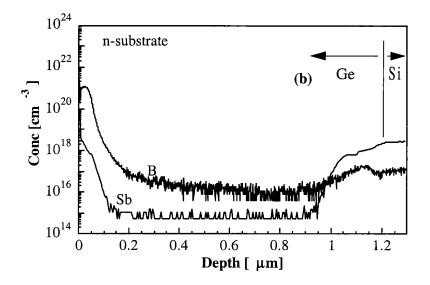

| Figure 4.4: SIMS profiles of (a) the Ge n-i-p diode (on p <sup>+</sup> Si substrate) and (b) the Ge p-i- |

| n diode (on n <sup>+</sup> Si substrate)99                                                               |

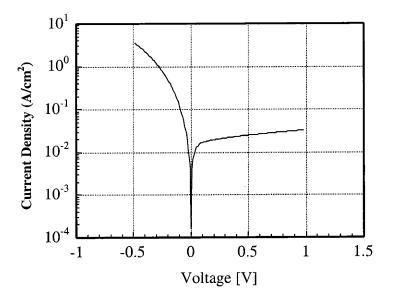

| Figure 4.5: Current-voltage characteristics (positive voltage on Ge) of mesa Ge/Si diodes                |

| made with Ge grown on p-Si treated by 20 post-growth thermal annealing cycles between                    |

| 900°C and 780°C100                                                                                       |

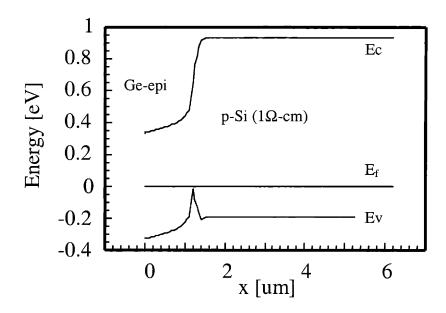

| Figure 4.6: Band-diagram of Ge/Si heterojunction diode grown on p-Si substrate101                        |

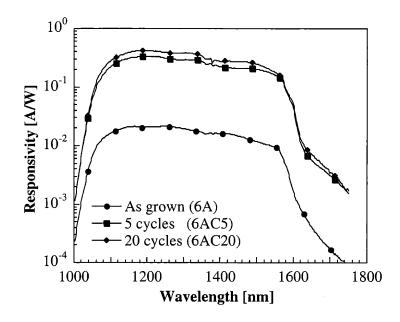

| Figure 4.7: Short circuit spectral responsivity of mesa heterojunction photodetectors made               |

| from Ge grown on Si treated with different post-growth annealing treatments. A                           |

| responsivity enhancement due to cyclic annealing is clearly demonstrated101                              |

| Figure 4.8: . Responsivity at 1300 nm versus applied bias voltage (positive voltage applied              |

| on Ge) of mesa heterojunction photodetectors made from Ge grown on Si treated with                       |

| different post-growth annealing. Annealed samples reach maximum responsivity at lower                    |

| bias voltages                                                                                            |

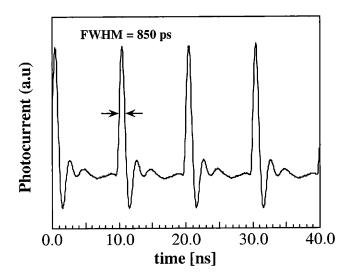

| Figure 4.9: Photocurrent response of a heterojunction photodetector made from Ge grown                   |

| on Si followed by 20 annealing cycles (6AC20)104                                                         |

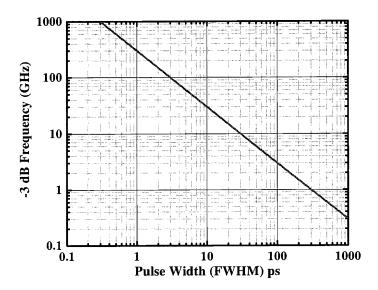

| Figure 4.10: The relationship between pulse width (FWHM) and -3dB frequency assuming                     |

| a hyperbolic secant <sup>2</sup> time dependence                                                         |

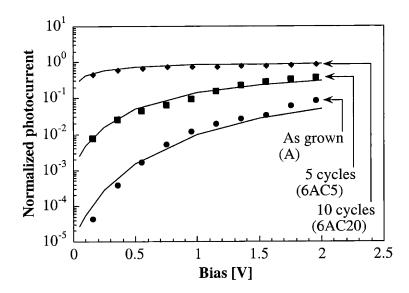

| Figure 4.11: Photocurrent response of MSM devices at 1300 nm versus applied bias                         |

| (symbols). The lines are fitted based on the Hecht model [193]. Cyclic thermal annealed                  |

| samples reach maximum responsivity at lower bias voltages                                                |

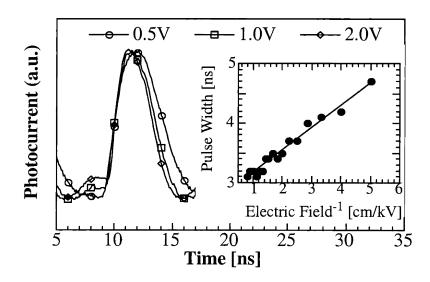

| Figure 4.12: Photocurrent response of MSM devices illuminated by 100 ps pulses at                        |

| $1.32\ \mu m.$ The photodiodes were fabricated from Ge grown on Si treated by 20 annealing               |

| cycles (6AC20). In the inset, the pulse width dependence on the inverse of the electric field            |

| is plotted: the symbols are experimental data, the solid line is a linear fit. An electron               |

| mobility of 3500 $\text{cm}^2/\text{V-s}$ was estimated from this experiment                             |

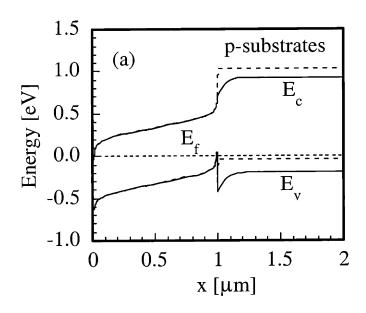

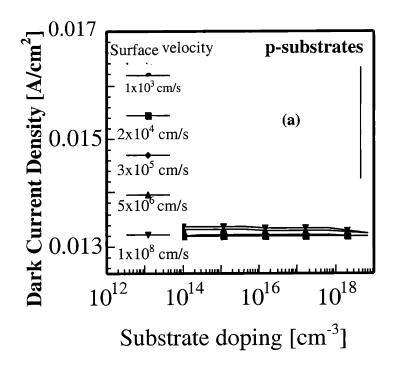

| Figure 4.13: Calculated equilibrium band diagram of Ge/Si p-i-n diodes for (a) n-i-p Ge                  |

| diode on p-Si substrates, and (b) p-i-n Ge diode on n-Si substrate. Continuous lines refer to            |

| calculated band diagram for substrates of resistivities of 1 $\Omega$ -cm. Dashed lines refer to         |

| calculated band diagram for substrates of resistivities of 0.01 $\Omega$ -cm110                          |

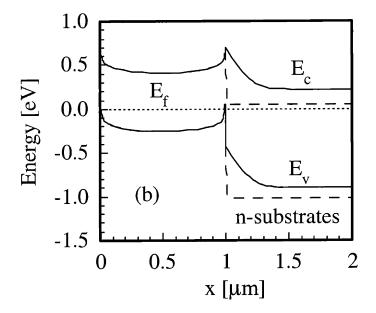

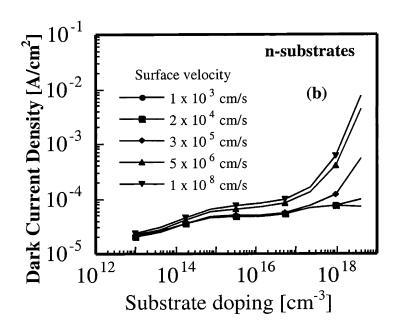

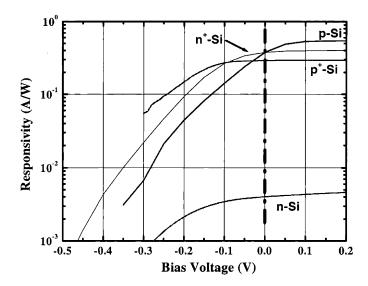

| Figure 4.14: Calculated reverse dark current densities for Ge/Si p-i-n diodes with different                                          |

|---------------------------------------------------------------------------------------------------------------------------------------|

| substrate doping type and density. Curves differ for the surface recombination velocity at                                            |

| the Si/Ge interface used in the calculations112                                                                                       |

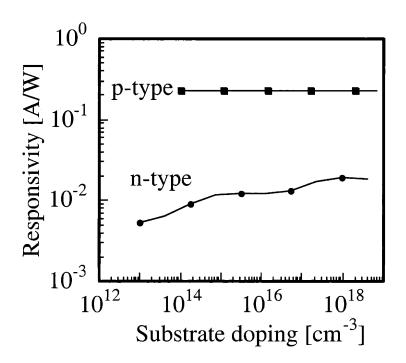

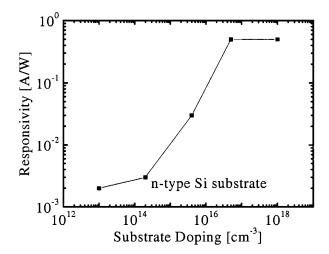

| Figure 4.15: Calculated 1300 nm responsivity of Ge/Si p-i-n diodes as a function of the                                               |

| substrate doping                                                                                                                      |

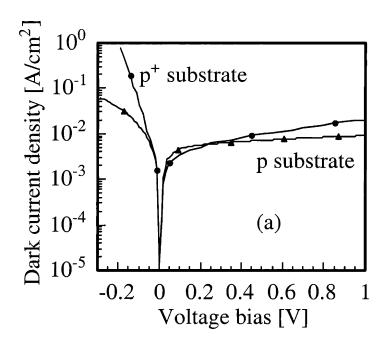

| Figure 4.16: Measured dark current versus voltage for mesa p-i-n Ge/Si diodes grown on:                                               |

| (a) p-Si and p <sup>+</sup> -Si substrates, (b) n-Si and n <sup>+</sup> -Si substrates. For the p <sup>+</sup> -Si case, the inferred |

| diode ideality factor is 1.2 and the saturation current density at 0 V is 2 mA/cm2. The                                               |

| reverse current at 1 V is 20 mA/cm2                                                                                                   |

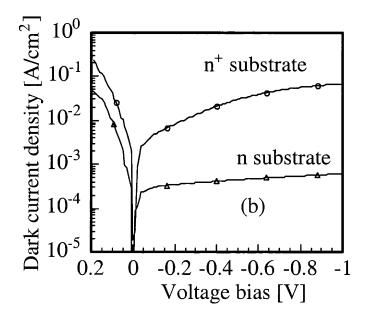

| Figure 4.17: Measured photocurrent-voltage characteristics of mesa p-i-n Ge/Si diodes at                                              |

| 1300 nm                                                                                                                               |

| Figure 4.18: Calculated 1300 nm responsivity of Ge/n-Si p-i-n diodes as a function of the                                             |

| substrate doping considering the diffusion of dopant from the n-Si substrate117                                                       |

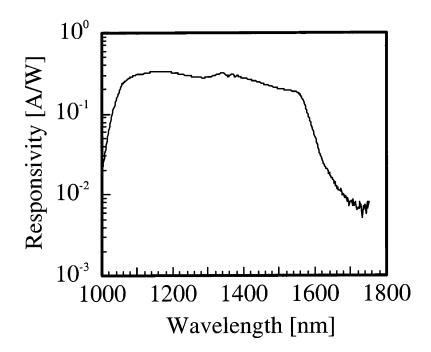

| Figure 4.19: Measured short circuit spectral responsivity of a mesa p-i-n Ge photodiode                                               |

| fabricated on p <sup>+</sup> -type Si                                                                                                 |

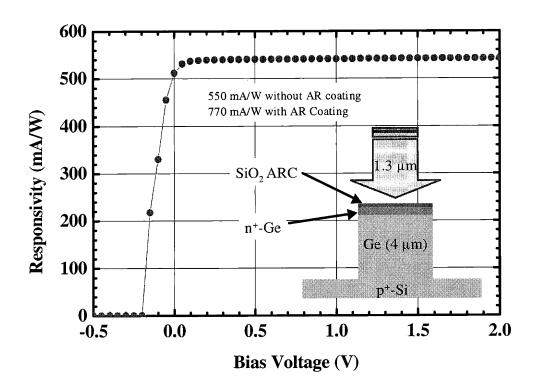

| Figure 4.20: Responsivity of n-i-p Ge (4 $\mu$ m) / p <sup>+</sup> -Si photodiode with and without SiO <sub>2</sub>                   |

| anti-reflection coating                                                                                                               |

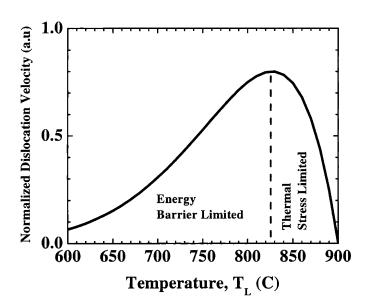

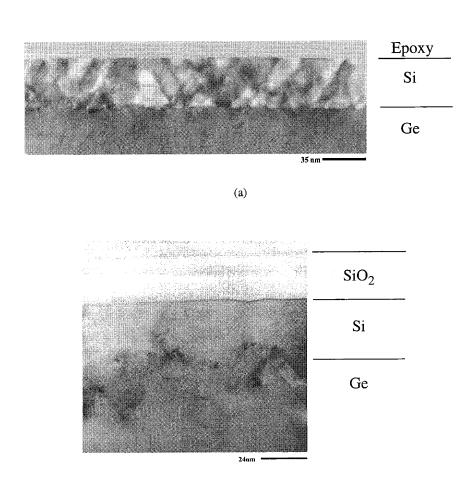

| Figure 5.1: (a) Cross sectional TEM micrograph of a Si epilayer grown on the Ge epilayer.                                             |

| (b) Cross sectional TEM micrograph of a Si epilayer grown on Ge, with SiO <sub>2</sub> grown by                                       |

| thermal oxidation as the topmost layer128                                                                                             |

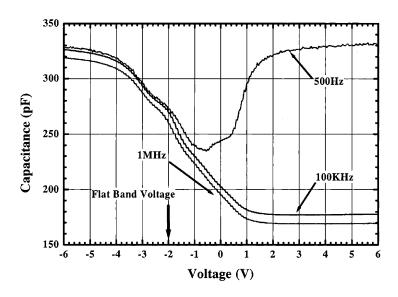

| Figure 5.2: Capacitance-voltage characteristics of SiO <sub>2</sub> /Si/Ge/p <sup>+</sup> -Si structure129                            |

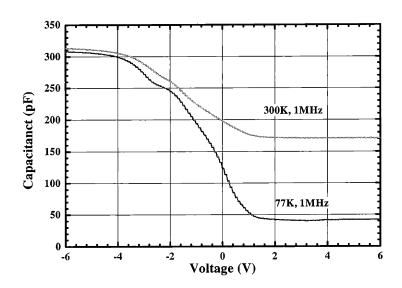

| Figure 5.3: High frequency C-V curve measured at 300K and 77K                                                                         |

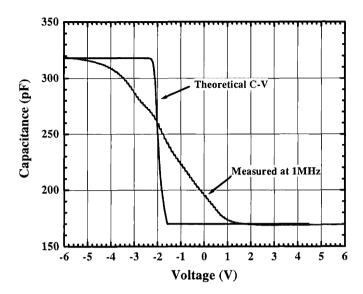

| Figure 5.4: Comparison of measured C-V curve (1 MHz) and calculated C-V curve131                                                      |

| Figure 5.5: Measured interface state density as a function of surface potential133                                                    |

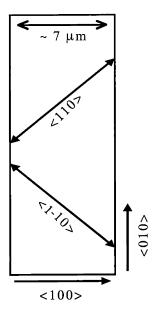

| Figure 6.1: Geometry for the reduction of threading-dislocations by gliding to mesa                                                   |

| sidewalls136                                                                                                                          |

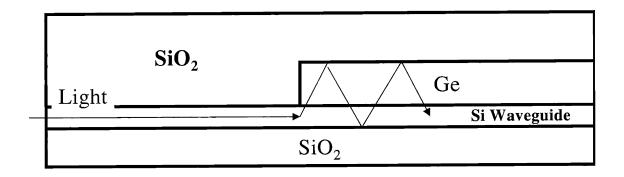

| Figure 6.2: Vertical coupling of Ge photodiode with Si waveguide. Ge photodiode is on top                                             |

| of the Si waveguide                                                                                                                   |

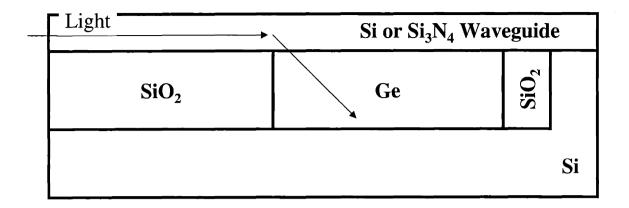

| Figure 6.3: Vertical coupling of a Ge photodiode with Si or Si <sub>3</sub> N <sub>4</sub> waveguide. Ge                              |

| photodiode is under the waveguide                                                                                                     |

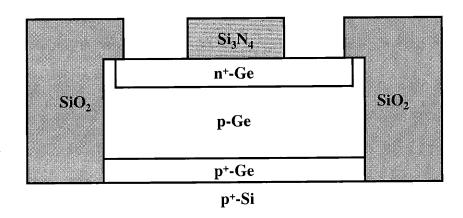

| Figure 6.4: Design of a vertical p-i-n Ge photodiode grown on Si integrated wit          | th a Si <sub>3</sub> N <sub>4</sub> |

|------------------------------------------------------------------------------------------|-------------------------------------|

| waveguide.                                                                               | 140                                 |

| Figure 6.5: Design of a lateral p-i-n Ge photodiode grown on Si integrated wit           | h a Si <sub>3</sub> N <sub>4</sub>  |

| waveguide.                                                                               | 141                                 |

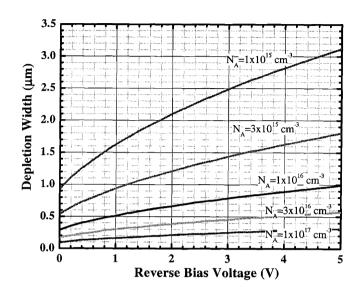

| Figure 6.6: Depletion width of an n <sup>+</sup> -p Ge diode as a function of voltage ar | nd doping                           |

| concentration                                                                            | 142                                 |

## **List of Tables**

| Table 3.1: Annealing parameters and characterization results of samples grown by two-step UHV/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 3.1: Annealing parameters and characterization results and 600°C 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CVD process with the first step at 350°C and the second step at 600°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| The second of samples grown by two-step of the second of samples grown by two-step of the second of two-step of the second of two-step of the second of two-step of two-step of the second of two-step |

| CVD process with the first step at 350°C and the second step at 900°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| CVD process with the first step at 350°C and the second step.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Table 3.3: Annealing parameters and characterization results of samples annealed at different TL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| The dialocation density decreases as TL approaches 830°C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Table 4.1: Annealing parameters and characterization results of samples used for making MSM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Table 4.1: Annealing parameters and characterization by two step LHV/CVD process with the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Table 4.1: Annealing parameters and orders and Ge/Si heterojunction detectors. Samples were grown by two-step UHV/CVD process with the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| first step at 350°C and the second step at 600°C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

## Chapter 1

### Introduction

#### 1.1 Motivation

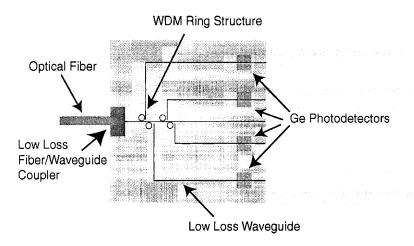

Si microphotonics [1], the optical analog to Si microelectronics, is the integration of optoelectronic components on Si substrates using process technologies that are compatible with Si microelectronic technology. Successful development of Si microphotonic technology can bring the advantage of optics to the Si platform and dramatically improve our information processing capability and deliver the benefit of optoelectronic technology at a much lower cost. Figure 1.1 shows an application of Si microphotonic technology: a wavelength-division-multiplexing (WDM) photodetector receiver. In this application, Si or  $Si_3N_4$  waveguides, waveguide ring-resonators, Ge photodetectors and Si microelectronics are all integrated on a Si chip. In more sophisticated applications, light emitters, and optical modulators can also be integrated on Si.

Figure 1.1: A schematic of an application of Si microphotoinc technology: WDM photodetector receiver.

Optical waveguides [4], optical modulators [3], photodetectors [5], light emitters [2], and optical amplifiers are the key components for Si microphotonic systems. This thesis investigates the integration of Ge p-n junction photodiodes on Si<sup>1</sup>. The goal is to develop processing technologies that allows the direct integration of high quality Ge epilayers on Si, and to provide an understanding of the materials properties for the design of integrated Ge photodiodes.

#### 1.2 Outline of thesis

In chapter 2, design issues related to the integration of near-infrared photodiodes on Si are discussed. Based on the consideration of the performance metrics of photodiodes and a discussion of the effect of threading-dislocations on the operation of photodiodes, Ge is selected as the most reasonable material for the integration of near-infrared photodiodes on Si for Si microphotonic applications.

Chapter 3 describes the direct epitaxial growth of Ge on Si. Based on a careful literature review, a two-step ultra-high-vacuum/chemical-vapor-deposition (UHV/CVD) process is designed for the growth of Ge epilayers directly on Si. The threading-dislocations in Ge epilayers are reduced by cyclic thermal-annealing process. The threading-dislocations in the as-grown and annealed Ge epilayers were studied extensively by transmission-electron-microscopy (TEM). Based on the TEM study, the mechanism for the reduction of threading dislocations in Ge epilayers is discussed.

<sup>1.</sup> Many devices can be used as photodetectors. This thesis focuses on the p-n junction photodiodes.

Chapter 4 describes the performance of Ge photodiodes integrated on Si. The beneficial effect of cyclic thermal-annealing on the electrical properties of Ge epilayers grown on Si is illustrated by the improved performance of metal-semiconductor-metal (MSM) Ge photodetectors and Ge/Si heterojunction photodiodes. Next, the properties of Ge p-i-n photodiodes are investigated and the role of misfit-dislocations at the Ge/Si interface is discussed. Finally, p-i-n Ge photodiodes made from Ge epilayers grown on Si with responsivity of 770 mA/W at 1300 nm is discussed.

Chapter 5 describes the development of a process technology for the passivation and protection of the Ge epilayer surface. Protection of Ge epilayer in Si wafer cleaning chemistry is provided by a thin-smooth Si epilayer grown on the Ge epilayer. Passivation for the Ge surface is provided by the oxidation of Si epilayer grown on Ge. Capacitance-voltage (C-V) characteristics of the metal-oxide-semiconductor (MOS) devices made this way demonstrate the good quality of the interface between the thermally grown silicon oxide and Ge.

Finally, Chapter 6summarizes this thesis work and concludes with suggestions for future development of Si microphotonic technology.

## Chapter 2

## Materials selection and design considerations

#### 2.1 Overview

This chapter first presents the reason for investigating the integration of near-infrared photodetectors on Si. A literature review of the work carried out in this field is then presented, followed by a justification for the selection of pure Ge as the material for integrating near-infrared photodiodes on Si. Finally, the effect of threading-dislocations on the operation of photodiodes is discussed leading to the conclusion that Ge photodiodes are the best short term solution for Si microphotonic receivers.

#### 2.2 Integration of near-infrared photodetectors on Si

Integration of optoelectronic devices on Si substrates has been an active research field for many years. There are several reasons: 1) Si substrates cost less and are mechanically stronger and thermally more conductive compared to InP and GaAs substrates. InP and GaAs substrates are currently used for making optoelectronic devices. If reliable and efficient LEDs, lasers and photodetectors can be made using Si wafers as substrates, the cost for these components can be reduced. 2) Si microelectronic technology provides the highest level of integration. Integration of optoelectronic devices with Si microelectronic devices can significantly improve the ability of integrated circuits (IC). Recent commercial developments in system on a chip (SOC), fiber to the home (FTTH), and fiber to the building (FTTB) concepts can all benefit from the successful development of Si based optoelectronic integrated circuit (OEIC) technology [6]. Application examples include fiber to the home receivers, on-chip optical clock distribution, and some high speed optical data transfer between Si chips.

Photodetectors and optical receivers are important components in optical networks. Photodetectors are not only used at the receiving end, they are also used as optical power monitoring devices. For networks operating in the first optical window of modern silica optical fibers (~850 nm), low cost Si detectors could be used. However, for operation in the second window (~1300 nm) and the third window (~1550 nm), InGaAs<sup>2</sup> or Ge photodiodes are needed [7]. The lattice constant of Ge and In<sub>0.53</sub>Ga<sub>0.47</sub>As are very different from that of Si. In<sub>0.53</sub>Ga<sub>0.47</sub>As and Ge photodiodes are therefore typically made on lattice matched substrates such as InP and Ge substrates. There are a lot of benefits to be gained if near-infrared photodiodes operating from 1300 nm to 1550 nm can be integrated on Si with Si microelectronics.

The integration of near-infrared photodiodes on Si has been pursued by several research mismatch between The key challenge is the lattice groups. lattice constant = 0.543 nm) and semiconductor materials that are sensitive to light in the range of 1300 nm to 1550 nm ( $In_{0.53}Ga_{0.47}As$  lattice constant = 0.587 nm; Ge lattice constant = 0.565 nm). This lattice mismatch causes two major problems when one deposits In<sub>0.53</sub>Ga<sub>0.47</sub>As or Ge epilayers on Si: (1) the introduction of high densities of misfit-dislocations and threading-dislocations in the epilayer, and (2) high surface roughness due to island growth. High surface roughness causes difficulties in process integration. High threading-dislocation densities can degrade device performance and compromise device reliability.

<sup>2.</sup> The International Union of Pure and Applied Chemistry (IUPAC) recommends the use of GaInAs instead of InGaAs. In this thesis, InGaAs is used because most papers and books use InGaAs. For the same reason, this thesis use units typically used in text books in semiconductors physics rather than SI units.

Misfit-dislocations are introduced to relax the lattice mismatch between the epilayer and the Si substrate and are typically confined to the interface between the epilayer and the Si substrate. If one makes devices (for example photodetectors) far away from the epi-substrate interface, problems associated with the misfit-dislocations can be avoided. Threading-dislocations are the by-product of the introduction of misfit-dislocations and do not relax lattice-mismatch strain. Threading-dislocations are left in the epilayers because dislocations cannot end in a crystal. Dislocations have to either form a loop or terminate at a free surface. Since the epilayer surface is always the nearest free surface to the epi-substrate interface, these threading-dislocations typically thread from the epi-substrate interface to the epilayer surface. Since devices are usually built close to the epilayer surface, these threading-dislocations cannot be easily avoided. Threading-dislocations can reduce carrier lifetime, carrier mobility and compromise device reliability. Discussion of the effect of threading-dislocations on the electrical properties of semiconductors is reviewed in section 2.6. To integrate high performance In<sub>0.53</sub>Ga<sub>0.47</sub>As or Ge near-infrared photodetectors on Si, it is necessary to solve problems related to threading-dislocations and surface roughness. Section 2.3 reviews works related to the integration of near-infrared photodetectors on Si.

#### 2.3 Literature review

Luryi and co-workers pioneered the integration of Ge photodetectors directly on Si by molecular-beam-epitaxy (MBE) [8]. To prevent island growth and minimize the effect of misfit-dislocations, they introduced a SiGe graded-buffer layer between the Ge epilayer and the Si substrate. Their transmission-electron-microscope (TEM) pictures revealed a high density (above 10<sup>9</sup> cm<sup>-2</sup>) of threading-dislocations in the Ge layer. These Ge/Si

photodetectors demonstrated a 40% external quantum-efficiency at a wavelength of 1450 nm and a dark current of 50 mA/cm². They did not report quantum efficiency at 1550 nm. Kastalsky, Luryi and co-workers later improved the materials quality by introducing a "glitche-grading" region between the Ge layer and the Si substrate [9]. The "glitche-grading" buffer was a combination of the graded-buffer layer and the "glitche" layer. The "glitche" region was a Ge(50 nm)/Si<sub>0.3</sub>Ge<sub>0.7</sub>(10 nm) superlattice. Their TEM measurement showed a reduction in threading-dislocation density to the 5x10<sup>7</sup> cm<sup>-2</sup> range. Their capacitance-voltage measurement showed a depletion width of about 0.15 μm. The measured leakage current density was 0.4 mA/cm² due to the reduced threading-dislocation density and the reduction in depletion width³.

To further reduce the leakage current density, Luryi and Pearsall suggested the use of strained-layer  $Si_{1-x}Ge_x/Si$  superlattice (SLS) as the active absorption layer in near-infrared photodetectors integrated on Si [10]. This idea is based on the bandgap calculations by People [11]. According to People's calculation, strained  $Si_{1-x}Ge_x$  alloys coherently grown on Si have a much smaller bandgap compared to relaxed  $Si_{1-x}Ge_x$  alloys [12]. This calculation was later experimentally verified by Lang and co-workers [13]. Using strained-layer  $Si_{1-x}Ge_x/Si$  superlattice with x > 0.35, materials with bandgap lower than 1300 nm and 1550 nm can be grown essentially dislocation free on Si. Strained-layer  $Si_{1-x}Ge_x/Si$  superlattice photoconductors [14], waveguide p-i-n photodiodes [15], and avalanche waveguide photodiodes [16] [17] with good photoresponse at 1300 nm were demonstrated. The photoresponse at 1550 nm was very low. The disadvantage of strained-layer  $Si_{1-x}Ge_x/Si$  superlattice material is its low absorption coefficient. With

<sup>3.</sup> Total leakage current due to carrier generation in the depletion region of a p-n junction is proportional to the depletion region width.

x = 0.6, the absorption coefficient is only about 21 cm<sup>-1</sup> at 1300 nm [16] [13]. Because of the low absorption coefficient, detectors made from strained-layer Si<sub>1-x</sub>Ge<sub>x</sub>/Si superlattice need a long absorption length to provide a reasonable quantum-efficiency. For example, with a 300  $\mu$ m long waveguide geometry and x = 0.6 an external quantum-efficiency of 10% at 1300 nm was measured [15]. The quantum efficiency at 1550 nm was about 2% and the measured leakage current density was 7 mA/cm<sup>2</sup>. Note that the leakage current density for strained-layer Si<sub>1-x</sub>Ge<sub>x</sub>/Si superlattice photodiodes is not much lower compared to that of Ge/Si photodiodes earlier reported by Kastalsky and Luryi. Etch-pit-density measurement of threading-dislocations revealed a density of about  $10^4\,\mathrm{cm}^{-2}$ . When strained-layer  $\mathrm{Si}_{0.5}\mathrm{Ge}_{0.5}\mathrm{/Si}$  superlattice photodiodes were measured at normal incidence, only 1% external quantum efficiency at 1300 nm was measured with a leakage current density of 60 mA/cm<sup>2</sup> at a reverse bias voltage of 7 V [18]. Strained-layer Si<sub>1-x</sub>Ge<sub>x</sub>/Si superlattice photodiodes were later integrated Si with rib waveguide [19] [20] [21] [22]. Other strained-layer Si<sub>1-x</sub>Ge<sub>x</sub>/Si superlattice based photodiodes have also been reported [23] [24] [25] [26] [27] [28] [29]. All of these photodiodes require a long waveguide geometry to achieve reasonable quantum efficiencies at 1300 nm and 1550 nm.

The limitation of strained-layer  $Si_{1-x}Ge_x/Si$  superlattice is the low absorption coefficient and the thickness of each strained-layer. The limitation on absorption coefficient can be solved by adding more Ge into the  $Si_{1-x}Ge_x$  layer. However adding more than 60% of Ge brings the critical-thickness below 10 nm. Although the use of strained-layer superlattice allows the growth of many pairs of strained- $Si_{1-x}Ge_x/Si$  on Si. The total critical-thickness of the strained-layer superlattice is still limited by the critical-thickness of the average concentration of the SiGe/Si superlattice layers. One way to solve these problems is to go

beyond the SiGe binary system and work with the SiGeC ternary system. The idea is that by adding elements (such as C) with lattice constant smaller than Si, the lattice mismatch between SiGe alloy and Si can be compensated [30]. Typically for every 1% of C added, lattice-mismatch due to about 8% of Ge can be compensated [31]. Normal incidence  $Si_{0.25}Ge_{0.6}C_{0.15}$  p-i-n photodiodes with 80 nm of active SiGeC layer have been reported [32]. The external quantum efficiency at 1.3  $\mu$ m was about 1% and the leakage current density was 7 mA/cm<sup>2</sup>. The threading-dislocation density was estimated to be below  $10^8$  cm<sup>-2</sup> and the absorption coefficient was 10 cm<sup>-1</sup> at 1550 nm and 340 cm<sup>-1</sup> at 1300 nm [33] [34].  $Ge_{1-x}C_x$  photodiodes have also been reported [35] [36]. The addition of C was found to reduce the leakage current and improve the ideality factor. With 590 nm of heavily doped p- $Ge_{0.902}C_{0.008}$  (2.7 x  $10^{18}$  cm<sup>-3</sup>) on n-Si ( $10^{14} \sim 10^{15}$  cm<sup>-3</sup>), the measured external quantum efficiency at 1300 nm was 2.2% and the leakage current density was 1.4 mA/cm<sup>2</sup>.

It is clear from the above review that SiGe strained-layer superlattice and SiGeC based photodiodes provide very little improvement from the Ge/Si approach first demonstrated by Luryi and Kastasky in terms of external quantum efficiency and leakage current. Although the use of SiGe strained-layer superlattice does reduce the threading-dislocation densities in the epilayers, the absorption coefficient is much lower. Also, the reduction in threading-dislocation density did not help reducing the leakage current density.

Another approach to the integration of near-infrared photodiodes on Si is the integration of InGaAs photodiodes on Si. InGaAs photodiodes made on InP are efficient, fast and of low leakage current [37] [70]. The challenge is the 8% lattice mismatch between In<sub>0.53</sub>Ga<sub>0.47</sub>As (lattice matched to InP with bandgap at 1650 nm) and Si that guaranteed a

high density of threading-dislocations in the InGaAs epilayer grown on Si. Despite this challenge, InGaAs epilayers have been grown on Si using various techniques and InGaAs photodiodes have been integrated on Si [38] [39] [40] [41] [42] [43]. For example, Razeghi and co-workers demonstrated InP/InGaAs(4 μm)/InP(1 μm)/GaAs(1 μm) p-n diffused-junction photodiodes on Si with 88% external quantum efficiency at 1300 nm and 92% external quantum efficiency at 1550 nm and a leakage current density of 1 mA/cm² at -1 V [38]. This performance is much better compared to that produced by the SiGe and SiGeC approach. The excellent quantum-efficiency can be understood in terms of InGaAs's high absorption-coefficient at 1300 nm and 1550 nm (>10<sup>4</sup> cm<sup>-1</sup>). The much lower leakage-current density compared to those of SiGe SLS photodiodes is probably due to the use of diffused junction rather than mesa structures. The threading-dislocation densities in InGaAs epilayers grown on Si are typically on the order of 10<sup>8</sup> cm<sup>-2</sup> range [43]. This might explain the much higher leakage current density compared to that of InGaAs photodetectors made on InP (typically in the range of 16 μA/cm<sup>2</sup>).

To completely eliminate threading-dislocations, InGaAs/InP structures can be bonded to Si substrates. The InP substrates can be etched by HCl, leaving behind InGaAs on Si. The final products are threading-dislocation free InGaAs/InP structures on Si: a perfect material for making near-infrared photodiodes on Si [44] [45] [46] [47] [48]. Near-infrared InGaAs photodiodes integrated on Si by wafer bonding typically have 100% quantum efficiency and leakage current density similar to that of InGaAs photodiodes grown on InP. Wafer bonding technique, however, still requires the handling of InP substrates. InP substrates are fragile and expensive compared to Si wafers. Wafer bonding, unlike selective area epitaxy, does not provide the possibility of selective introduction of InGaAs material on Si in designated small areas. The introduction of III-V

compound into a Si processing line is also an issue to be resolved. All the elements in InGaAs are dopants in Si. Cross contamination is an issue to be considered if III-V compound semiconductors are to be introduced into the Si processing line.

Another possible solution is to go back to the Ge/Si approach. Compared to SiGe and SiGeC, Ge has an absorption coefficient that is almost comparable to that of InGaAs in the range of 1300 nm to 1550 nm. Considering the fact that the commercial applications of SiGe BiCMOS technology have already been demonstrated, the intoduction of Ge into the Si processing technology raises less issues related to cross contamination. It is also well known that Ge can be grown selectively on patterned SiO<sub>2</sub>/Si substrates [49]. The key challenge is the epitaxial growth of flat-Ge epilayers on Si with low surface roughness and low threading-dislocation densities. Samavedam and co-workers have integrated Ge p-n junction photodiodes on thick (> 10 µm) optimized SiGe graded buffer-layers grown on Si [54] [55]. The optimized SiGe graded buffer-layer technology includes an intermediate chemo-mechanical-polishing (CMP) and regrowth step. High quality Ge film with threading-dislocation densities of  $2 \times 10^6 \, \text{cm}^{-2}$  was achieved on Si. The p-n junction was defined by in-situ doping and mesa etching. The mesa side-wall was passivated by a thin layer of PECVD SiO<sub>2</sub>. The measured external quantum efficiency was 12.6% at 1300 nm, the leakage current density was 0.22 mA/cm<sup>2</sup> at -1 V with a depletion region of 0.24 µm. Samavedam's work demonstrated that high quality Ge photodiodes can be integrated on Si if the threading-dislocation density is low and the mesa side-wall is passivated. The challenge of this graded-buffer technology is the integration of the 10 µm thick SiGe graded-buffer with the planar Si CMOS technology. If Ge of similar quality can be grown directly on Si, process integration of Ge photodiodes with Si CMOS technology would be much simpler.

Colace and co-workers demonstrated that Ge epilayers with low root-mean-square surface roughness (~ 0.5 nm) can be grown on Si using a two-step CVD process [51] [52] [53]. Colace and co-workers demonstrated metal-semiconductor-metal photodetectors with their Ge epilayers. The measured external quantum-efficiency was 12.6% at 1.3 µm. As will be discussed in Chapter 3, Ge epilayers grown on Si using this two-step process have a threading-dislocation density on the order of 10<sup>9</sup> cm<sup>-2</sup>. The threading-dislocation density, however, can be reduced to the mid 10<sup>6</sup> cm<sup>-2</sup> level by cyclic thermal-annealing [56] [57]. Selectively grown Ge mesas on Si with threading-dislocation after cyclic annealing were also demonstrated. Details will be discussed in Chapter 3. Applying this improved Ge epilayer on Si, Ge photodiodes with external quantum efficiency of 52% at 1.32 µm and 20% at 1.55 µm have been demonstrated with 1 µm of Ge [58] [59]. The leakage current density was 30 mA/cm<sup>2</sup>.

This section provided a short review of the integration of the near-infrared photodetectors on Si. Two conclusions can be drawn from this literature review: (1) Materials with high absorption coefficients are the key to high quantum efficiency. (2) Materials with the lowest threading-dislocation densities do not always make the best photodetectors. Surface passivation is also important. More details regarding these points will be discussed later in this thesis. The following section will first provide a discussion of the requirements for integrated photodetectors for Si microphotonics.

#### 2.4 Requirements for photodetectors for Si microphotonics

Si microphotonic technology is the integration of optoelectronic components on Si substrates using process technologies that are friendly to Si microelectronic technology.

An important feature of Si microphotonic technology is the use of high index contrast waveguide systems such as the Si/SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> (core/cladding) systems. The high optical confinement in these waveguide systems allows the fabrication of a high density of micron-size waveguide bends, waveguide splitters and wave-length-division (WDM) multiplexing filters on Si [4] [60]. Another important feature of Si microphotonic technology is the process compatibility with Si based microelectronic technology. These two features, the high integration density and Si process compatibility, ensure the large scale integration of microelectronic and microphotonic devices on Si.