# Commercialization of Microelectromechanical Systems (MEMS)

by

#### Alan M. Then

B.S., Ceramic Science and Engineering The Pennsylvania State University, 1987

M.S., Ceramic Science The Pennsylvania State University, 1990

Submitted to the Sloan School of Management in Partial Fulfillment of the Requirements for the Degree of

# Master of Science in Management of Technology at the Massachusetts Institute of Technology June 2001

© 2001 Alan M. Then. All rights reserved.

The author hereby grants to MIT permission to reproduce and to distribute publicly paper and electronic copies of this thesis document in whole or in part.

|                     | •                                               | ARCHIVES |

|---------------------|-------------------------------------------------|----------|

| Signature of Author |                                                 |          |

|                     | Alan M. Then                                    |          |

|                     | MIT Sloan School of Management                  |          |

|                     | Management of Technology Program                |          |

|                     | May 11, 2001                                    |          |

| Certified by        |                                                 |          |

| •                   | Henry Birdseye Weil                             |          |

|                     | Senior Lecturer, MIT Sloan School of Management |          |

|                     | Thesis Supervisor                               |          |

| Accepted by         | ~                                               |          |

|                     | David A Weber                                   |          |

|                     | Director, Management of Technology Program      |          |

# Commercialization of Microelectromechanical Systems (MEMS)

By

## Alan M. Then

Submitted to the Alfred P. Sloan School of Management on May 11, 2001 in partial fulfillment of the requirements for the Degree of Master of Science in the Management of Technology

#### **ABSRACT**

Microelectromechanical systems (MEMS), at their core are a set of technologies that employ the processes developed in the integrated circuit (IC) and semiconductor industries to construct electro- mechanical devices. In the case of Microopticelectromechanical systems (MOEMS), optical elements are also integrated into these devices.

MEMS technology holds the promise of significantly miniaturizing, reducing the cost of, and enhancing the performance of many sensors and actuators, evidence its widespread use in the manufacture of accelerometers, ink jet printer heads and various chemical gas sensors.

Despite its stellar success in these "killer-applications," MEMS technology has failed to realize the widespread success many had predicted for it. Nonetheless, this technology has recently been explored extensively for new electro-optics applications, specifically in telecommunications for dense wavelength division multiplexing (DWDM) and optical switching.

This thesis examines various models of dynamic technology adoption and explores how they apply to MEMS technology. Furthermore, by way of historical comparison to the development of application specific integrated circuit (ASIC), it will identify various developmental similarities. Finally, a unique model outlining the critical driving forces behind the adoption of MEMS technology will be constructed.

Thesis Advisor: Henry Birdseye Weil

Title: Senior Lecturer

#### **ACKNOWLEDGMENTS**

I wish to acknowledge the loving support of my family, without whom I would not have completed this endeavor. To my darling wife and parents, I owe an immeasurable debt of gratitude that I could never repay. To my wonderful son, thank you for reminding me of the power of a smile and a hug. To the faculty, staff and students of the Sloan school, particularly Henry Weil, I wish to thank one and all for sharing your thoughts and energies and for making this a joyful year of learning for me.

# **Table of Contents**

| Li  | st of | Tables                                                           | 5    |

|-----|-------|------------------------------------------------------------------|------|

| Li  | st of | Figures                                                          | 5    |

| 1   |       | roduction                                                        |      |

|     | 1.1   | Background                                                       | 6    |

|     | 1.2   | Purpose and Approach                                             | 7    |

| 2   | Lite  | erature Review                                                   | 7    |

| 4   | 2.1   | Diffusion and Innovation                                         | 7    |

| - 2 | 2.2   | Dynamic Models                                                   |      |

| 1   | 2.3   | Origins of Innovation in MEMS and Relevance                      | . 15 |

| - 2 | 2.4   | Conclusions                                                      | . 18 |

| 3   | ind   | lustry Review – Micro-Electro-Mechanical-Systems (MEMS)          | . 18 |

| ,   | 3.1   | Process Technologies                                             | . 23 |

|     | 3.1   | .1 Surface Micromachinning                                       | . 23 |

|     | 3.1   | .2 Bulk Micromachinning                                          | . 24 |

|     | 3.1   | .3 High-Aspect Ratio Micromachining                              | . 26 |

| ,   | 3.2   | MEMS Industry Architecture                                       |      |

|     | 3.3   | Case Review of Cronos and IntelliSense                           |      |

|     | 3.4   | Case Review of Accelerometers                                    |      |

| 4   |       | lustry Review – Application Specific Integrated Circuits (ASICs) | . 35 |

| 4   | 4.1   | Process Technologies                                             |      |

|     | 4.2   | ASIC Industry Architecture                                       | . 38 |

| 4   | 4.3   | Case Review of LSI Logic                                         | . 42 |

| 5   | Bu    | siness Model Description and Comparison                          | . 48 |

| ;   | 5.1   | Industry Comparisons                                             | . 48 |

|     | 5.2   | Market Pull                                                      | . 51 |

| ;   | 5.3   | Technology Push                                                  |      |

| 6   | Co    | nclusions                                                        | . 64 |

| 7   | Re    | ferences                                                         | 69   |

# **List of Tables**

| Table 3-1: Analysis and Forecast of the U.S. MEMS Market by Units in 1999 (in Millio  |    |

|---------------------------------------------------------------------------------------|----|

| of Dollars)                                                                           | 19 |

| Table 3-2: Analysis and Forecast of the U.S. MEMS Market by Percent in 1999 (in       |    |

| Millions of Dollars)                                                                  | 20 |

| Table 3-3: Analysis and Forecast of U.S. MEMS Market by Dollar in 1997 (in Million of | of |

| U.S. Dollars)                                                                         |    |

| Table 3-4: Market Segment and Companies Supported by DARPA                            | 22 |

| Table 3-5: Optical Switching Market Projections for North America and Europe          | 28 |

| Table 4-1: Changes in Market Share for the Four ASIC Architectures                    | 40 |

| Table 4-2: Attributes Affecting Customer Choices Among ASIC Technologies              | 41 |

| List of Figures                                                                       |    |

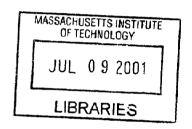

| Figure 3-1: Basic Process Formation of Polysilicon Cantilever Structure Via SSM       | 24 |

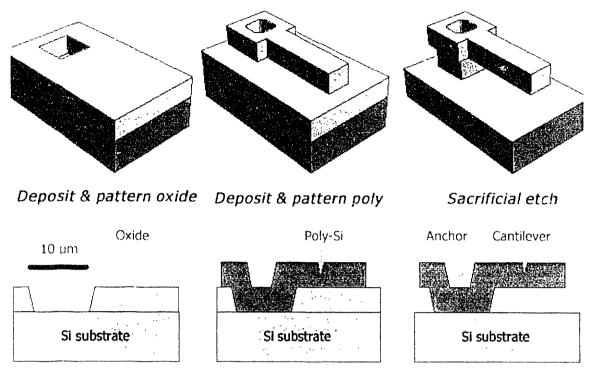

| Figure 3-2: Basic Surface Features Created Using BMM Via KOH Etching                  |    |

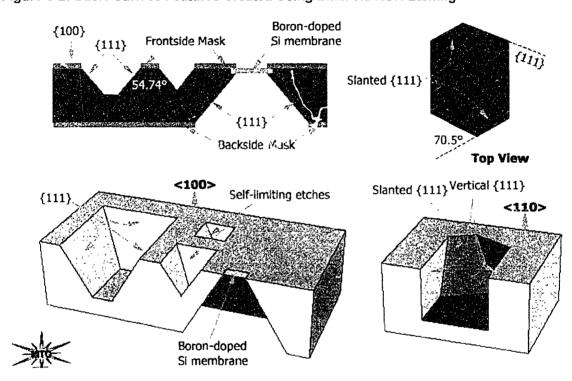

| Figure 3-3: Basic Methodology of LIGA                                                 | 27 |

| Figure 4-1: ASIC Architectural Family Tree                                            |    |

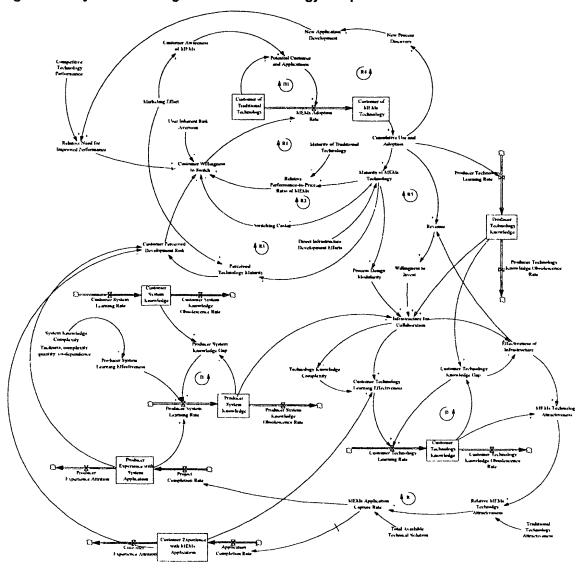

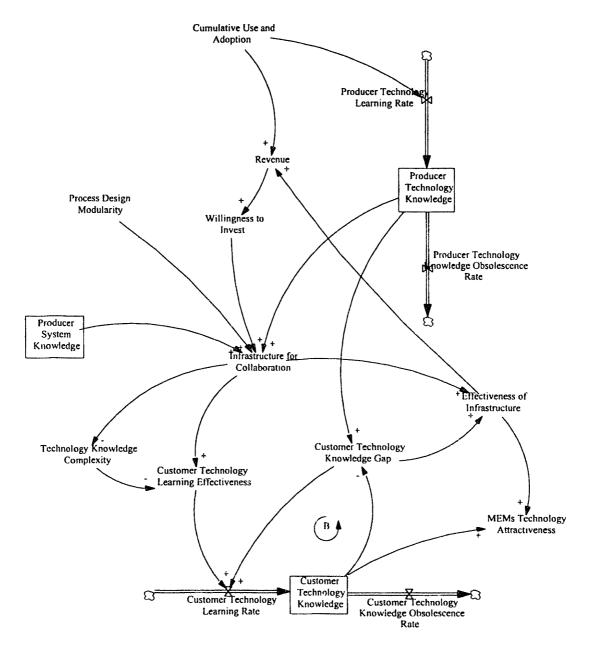

| Figure 5-1: System Thinking Model for Technology Adoption                             | 51 |

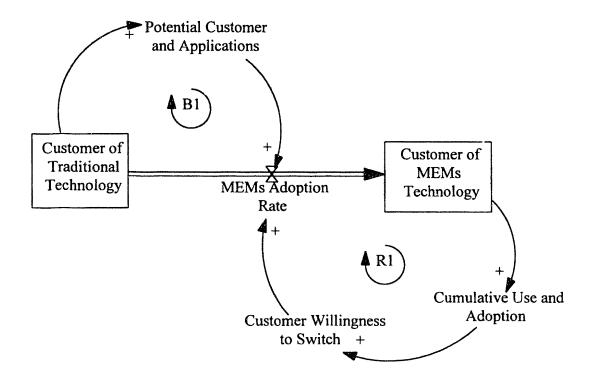

| Figure 5-2: Basic Adoption Cycle                                                      | 53 |

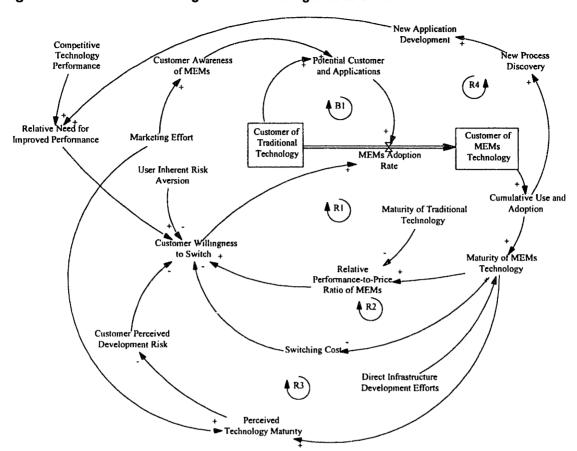

| Figure 5-3: Factors Influencing Customer Willingness to Switch                        | 54 |

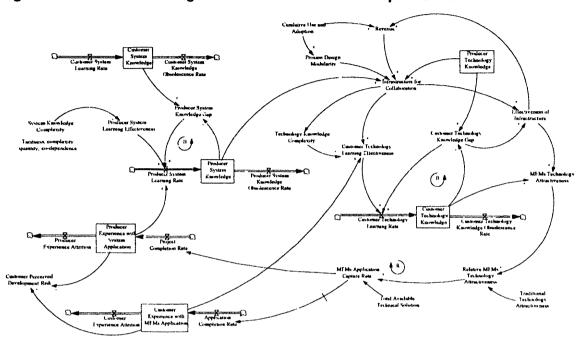

| Figure 5-4: Effects of Learning of Customer Perceived Development Risk                | 57 |

| Figure 5-5: Importance of Infrastructure for Collaboration                            | 59 |

### 1 Introduction

#### 1.1 Background

The rapid and effective commercialization of technical advances is critical to the success of high-technology industries. The process of commercialization of new technologies results from the complex interplay between the evolution of technical advancement and the ability of the firms, both within an industry and external to that industry, to recognize the value of those technologies. Furthermore, these firms must assemble the means and expertise to exploit the potential of these technologies to commercial ends. This ability to exploit the commercial potential of new technology is arguably the most important source of competitive advantage to all high technology companies. It is for this precise reason that the study of the diffusion of technology has been the subject of extensive research over the past several decades.

The study of the diffusion of innovation has attracted the interest of a wide variety of disciplines, including education and learning, organizational behavior, communications, marketing and sociology. In each field, there exists numerous theories that seek to explain how and what factors influence the adoption and diffusion of technology. Suffice to say here, many factors from all these fields influence technology diffusion and adoption. It is this complexity of interchange between many factors, coupled with the short- and long-term dynamics of these interactions, that make the field of system dynamics particularly well suited for the study of this topic.

Nonetheless, technology diffusion can be viewed as a special kind of communication in which the message is about a new idea. The very novelty of the idea gives the message a special characteristic, that of uncertainty. Uncertainty implies a lack of predictability. It is the goal of this thesis to examine this property of the process of adoption. Information is perhaps the most notable antidote to uncertainty. Thus, it is also the goal here to better define and

6

understand the dissemination of information and knowledge, and to examine the role of knowledge transfer as a driving force in the adoption of MEMS technology, and indeed any technology. More specifically, it is the dissemination of information throughout an "infrastructural value-chain" that represents a form of social change, without which adoption will be slowed.

## 1.2 Purpose and Approach

This thesis will seek answers to the questions: What factors shape the demand for new technology, specifically MEMS technology, and how can an organization shape those factors so as to improve its success in the marketplace? The investigation will begin with the basic model for technology adoption proposed by Lyneis<sup>1</sup> and will explore in some detail its three key concepts: 1) the availability of potential conversions, 2) the willingness to switch and 3) user need. The concept of user toolkits forwarded by von Hippel<sup>2</sup> will be examined in light of the Lyneis model. In addition, a recent working paper on industry disruption by Clay Christensen<sup>3</sup> will be considered.

The manner in which several companies have attempted to influence these various factors in the ASIC and MEMS industry will also be identified, particularly the willingness to switch on the part of potential customers. Moreover, the history of LSI Logic will be considered, and the approach it employed will be compared with the business strategies of Cronos and IntelliSense in the MEMS industry. Finally, several business strategies will be proposed for successfully introducing new MEMS-based products.

#### 2 Literature Review

#### 2.1 Diffusion and Innovation

One of the earliest works on the study of technology diffusion and adoption is the <u>Laws of Imitation</u> by the French sociologist Gabriel Trade in 1903<sup>4</sup>. In this book the first expression of the concept of "opinion leaders" and

"S-shape adoption patterns" were forwarded. While work counted in the area, it was in 1943 that a seminal study examining the adoption of hybrid seed corn by lowa farmers was published by Ryan and Gross<sup>5</sup> and the beginnings of a conceptual and mythological distinct area of research was forged. Rogers formalized this cross-disciplinary field of technology adoption in 1962 with the publishing of his book, <u>Diffusion of Innovations</u>. In 1995, Rogers revised and expanded his book with over one hundred generalizations.

Rogers defined the diffusion of technology as "the process by which innovations spreads to members of a social system." He described an innovation as being "any practice or object perceived as new by an individual." Based on this view, it is tempting to begin to apply an approach articulated in the system dynamics literature to describe adoptions of new products to MEMS, with perhaps the product being "knowledge." Rogers goes on to present a simple classification system scheme consisting of five conceptually distinct characteristics: 1) relative advantage, 2) compatibility with values, needs and past experiences of potential adaptors, 3) complexity of understanding and using innovation, 4) "trialability," i.e., the ability to use the innovation on a limited basis and 5) "observability," or the communicability of results. Rogers supports his findings with empirical studies, suggesting that each of these attributes can affect the rate of adoption, although it is clear that the relative importance of each is dependent on the particular context in which adoption takes place. Nonetheless, this framework suggests a broad series of causal loops that can form the basis from which to begin to generate a dynamic model.

Traditional adoption has been examined in the context of an individual's adoption of new products. Research has tended to look at those factors that differentiate the various classes of adaptors, which generally have been defined as: 1) risk-taking innovators, followed in order by 2) highly respected early adopters, 3) deliberate early majority, 4) the skeptical late majority, and the entrenched laggards.<sup>7</sup>

Alternatively, a model has also been forwarded that examines adoption as a problem-solving behavioral pattern in which individuals progress through a series of steps: 1) becoming aware of a problem, 2) recalling and gathering information about possible solutions, 3) evaluating alternative solutions, perhaps with limited attempts, 4) deciding on the appropriate solution and 5) evaluating the decision.<sup>8</sup> This is similar to the work 1971 of Robertson<sup>9</sup>, where he describes a conceptual model consisting of three fields: 1) the cognitive field consisting of problem perception, followed by awareness and understanding, 2) the attitude field consisting of attitude formation and legitimization and 3) the behavior field consisting of trial and adoption. Robertson points out that the process leading to adoption could be interrupted or cut short at any point. Other investigators eventually added a final stage to the Robertson model, that of confirmation, which determines the continued or discontinued use of a product. 10 Discontinuance occurred as a result of dissatisfaction with the innovation or by displacement by a newer technology. It is these models based on Robertson that are perhaps worth considering in the context of organizations as adaptors of new technology (not creators) and as the basis for a generic framework or series of causal loops for studying the adoption of new technology.

In more recent years, a number of investigators have developed frameworks that attempt to further characterize innovation along a number of dimensions, such as technological, economic and organizational. For example, Abernathy and Clark <sup>11</sup> list four types of innovation: 1) niche, 2) regular, 3) architectural and 4) revolutionary, which are distinguished along the dimension of "transilience". Transilience is defined as a measure of the impact of the innovation on the firm's competencies. This, in turn, measures the competitive advantage of the firm. Innovations that open up new markets, require new channels of distribution, or establish new relationships with customers (or forms of communication with customers) would all have greater transilience. Similarly, innovations that radically depart from established technologies that require new designs and manufacturing techniques are characterized by higher degrees of

technological transilience. Architectural innovations are disruptive along both dimensions (market and technology). Niche innovations are disruptive along market dimensions. Regular innovations build on existing markets and technologies. Revolutionary innovations make obsolete a company's (perhaps an industry's) technical skills and knowledge while preserving market connections.

Henderson and Clark<sup>12</sup> present a model that considers the impact not only on the components of a product, but also on the relationship among the components as well. In their model, radical innovations overturn the core design concepts of the components and the way they interact. They characterize incremental innovations as reinforcing design concepts and preserving the existing lineages among the components. Architectural innovation retains existing core designs, but at the same time, alters the relationship between the components. Modular innovation utilizes new components, but generally preserves the relationships among them or the configuration within the product. Both these frameworks view successful commercialization as being related in large measure to the ability of organizations to acquire and distribute new architectural knowledge.

Foster forwards another view of technological progress.<sup>13</sup> His model forwards the notion that successful firms are those that recognize the limits of existing technology. The concept revolves around a framework that empirically recognizes the occurrence of S-curves in technological progress. Foster applies his model by plotting various performance parameters against effort to further improve those parameters. Thus, as the rate of improvement in performance begins to decline, the technology is said to be reaching its natural limit. While the Foster model is consistent with historical data, it only accounts for endogenous factors and does not account for such exogenous factors as market and competitive forces. Similarly, Utterback<sup>14</sup> views the flattening of the S-curve as arising from the establishment of a dominant design for the technology or product that results from competition in the market among rival firms.

. 10

Christensen<sup>15</sup> has examined growth in the disk drive industry, and in so doing has developed the hypothesis that incumbent firms, while quite successful at fending off new entrants by utilizing sustaining innovations around existing technology, are generally unable to recognize disruptive technological changes. He categorizes many of these disruptive changes as architectural in nature, i.e., they involve new configurations of existing components within a product. It is by virtue of these disruptive innovations that companies are forced to shift to entirely new value networks, where their previous business practices might be unsustainable. More importantly, firms cannot rely on existing customers to decide whether to commercialize a new technology. Christensen intimates by way of example that typically these innovations perform more poorly than existing technologies along a set of criteria favored by existing customers, but fill the unique requirement of newcomer firms along differing dimensions of performance.

There are essentially two assertions to the Christensen model. The first is that there is a trajectory of performance improvement that customers can actually absorb or utilize over time. The second assertion is that there is a distinctly different trajectory of performance improvement that the innovators in an industry provide to their market. Christensen's studies reveal that the trajectory of technology is generally steeper than the abilities of customer to utilize the improvement. It is this difference between the trajectory of performance and customer need, which eventually opens the way for people serving lower-tiered markets to begin to attack customers in higher-tiered markets.

Similarly, Cooper and Schendel<sup>16</sup> found that typically new technologies were more expensive and under performed relative to established technologies, at least along the traditional dimensions of performance. They observed that newcomer firms often were the first to commercially introduce a new technology. Furthermore, while these frequently created new markets, success depended in large measure on initially capturing a niche market segment within an established market. The response of established firms to these new technologies varied, but

could be characterized as one of the following: 1) improving older technology, 2) avoiding directed competition by ceding market share or 3) participating in the new technology through some form of internal development.

Clearly, then, the degree to which an innovation or new technology is to be considered disruptive can be viewed along many dimensions (e.g. product performance and market needs primarily) and from various perspectives (e.g. existing users, new users, manufacturer and supply primarily). Is MEMS technology disruptive by the criterion established by these investigators? If so, how might its success be accessed in various markets? By all measures, the technology is disruptive in many industries; however, the success of MEMS technology will vary greatly, depending on the specific application, markets and incumbent technologies at play.

#### 2.2 Dynamic Models

There have appeared in recent years an increasing number of numerical models studying time series data related to the diffusion of innovation or first purchases. Much of this work has evolved from models built to examine the growth of population and the spread of infectious diseases. One of these models is SIR model developed by Kermack and McKendrick in 1927. The importance of this model was its second order nature and the ability of the disease to die-out, without always causing an epidemic. In addition, this allowed for the observation of the tipping-point. For any given system there is a critical combination of contact frequency, infectivity, and disease duration just great enough for the positive loop to dominate the negative loops. Below this point, the system is stable and on average people will recovery faster than new cases are generated. Beyond this point, the system becomes unstable and once the disease arrives it will spread uncontrollably, limited only by the remaining susceptible population. The SIR model also involved the concept of the herd immunity, i.e., once a sufficient population is infected the reproduction rate will fall below one and the disease will become dormant.

A second important model in the evolution of the study of diffusion is the logistic growth model. First published in 1838 by Francois Verhulst, it was reexamined by Richardson in1991. The dynamic model from which the logistic or S-shape curve is derived is a very simple one, consisting of only a single differential equation. It is based on the assumption that adoption takes place solely as a result of the imitation and word-of-mouth interaction between adopters and non-adaptors.

Bass introduced an important extension to the logistics growth model that allowed for the inclusion of more real world complexities in 1969.<sup>19</sup> It took the form:

$dN/dt = (a + b N_a) (N_p - N_a)$  where:  $N_a =$  the number of adaptors  $N_p =$  the number of potential adaptors a = the coefficient of innovation b = the coefficient of imitation

The Bass model was based on the notion that non-adopters can be persuaded to become adopters as a result of interactions either internally or externally to the network of adopters. If a = 0 in this equation, the logistics model is operation and all persuasion comes from internal sources. If b = 0, then the exponential model is in effect and all persuasion comes from external sources with no limit. Empirical best-fit testing of the model usually generate very small values for "a", reconfirming the basic usefulness of the logistics model.

The Bass model includes several simplifying assumptions that others have sought to relax in order to gain further insight and allow the model to be applied more generally and realistically. One method for this is to allow the internal and external coefficients to vary over time in response to changes in the intensity of marketing<sup>20,21</sup>. A second extension allows for the multiplicative effect of price reductions arising from the manufacture's increasing experience with the product. The cumulative number of adopters (N) is used as a proxy for this increased in experience.<sup>22</sup> A third extension considers the effect of sales of other products on sales of the new product. The nature of this effect is a function of whether the

two products are independent, complementary, contingent or substitutes<sup>23</sup>. The model has also been extended to allow the coefficients to depend on location, resulting in a time-space diffusion model.<sup>24</sup> Other extensions to the Bass model have also been proposed that, allow for a change in the number of potential adaptors (N<sub>p</sub>) through exogenous means, i.e., these changes occur independent of the adoption process itself (endogenously)<sup>25</sup> Models which allow for exogenous changes to potential adaptors, are generally based on a two-step process of learning consisting of awareness and acceptance.<sup>26</sup>

Sharif and Ramanathan in1982 proposed an extension to the Bass model of particular relevancy to the adoption of new technology.<sup>27</sup> In their model, various outcomes of the decision process are allowed, including adoption, rejection, re-adoption by rejecters, and permanent disapproval. This model is appropriate for analyzing multi-level technology substitution, a situation in which old, intermediate, and new products are simultaneously vying for market share.

Finally in a model proposed by J. Lyneis. 28 he lays out a basis for generally determining: 1) how much to invest in an existing technology vis-à-vis next generation of technology, 2) when to introduce a new generation of technology, 3) how much to spend on marketing and 4) how to price the new product. In the process of generating his general model Lyneis attempts to ensure that the formulation and output of the model produces results consistent with several existing forecasting and assessment techniques, including: 1) ability to generate S-curves to demonstrate technological progress, 2) cost experience curves and there influence on pricing strategy, 3) price performance trade-off curves, 4) diffusion or product life cycle deploying the concept of lead user to laggards (discussed previously) and 5) substitution curves developed consist with Fisher-Fry techniques. Lyneis accomplishes this by defining a matrix of three overreaching factors: 1) the user need, i.e., technology push vs. market pull; 2) market growth rate, i.e., the higher the growth rate the more new users there are relative to replacement users, and therefore the higher the willingness to switch to the new technology and 3) product lifetime vs. technology lifetime,

i.e., the shorter the technology lifetime relative to the product, the more critical will be the timing of technology adoption relative to the replacement cycle of the older technology.

#### 2.3 Origins of Innovation in MEMS and Relevance

MEMS owe their roots to the integrated circuit industry, which played an indispensable and inseparable role in creating the basic knowledge out of which grew the MEMS industry. MEMS technology began at the Sandia National Laboratories, in California, when the US government required a highly robust, mechanical system to act as locking-triggers for its nuclear arsenal.<sup>29</sup> It had been known for some time that electronic triggering devices were subject to disablement from larger electro-magnetic pulses (EMP) associated with nuclear explosions. The fear was that such an event, perhaps the result of a nuclear first strike, would render the US arsenal crippled and thus remove its deterrent effect. Thus, among other technologies, MEMS was born. There existed a substantial barrier to deploying this technology because of a lack of reliable data to support its use in such a critical application. Thus, efforts where made to find commercial applications whereby a large number of MEMS-based devices might be sold and tested in real world application, which would, in turn generate the data required in deploying the technology for military application.

To this day, Sandia National Laboratories remains one of the most advanced and encompassing MEMS development laboratories. But some have claim the origins of MEMS technology can instead be found at Draper Laboratories in Massachusetts<sup>30</sup>. An independent non-profit laboratory loosely affiliated with MIT, Draper conducts research and development on missile guidance systems for its primary customer, the US military. Some of the earliest work on MEMS accelerometers was conducted at Draper, which was related to the laboratory's missile guidance research. Nonetheless, as with many technologies, the US government's role was important and its motives were primarily defense-related.

Two of the most successful early commercial applications of MEMS technology were pressure- and acceleration-based sensors. One of the earliest applications of bulk micro-machined devices (BMD) was pressure sensors used in aerospace. The signficant reduction in weight offered by these devices was a critical driving force in their adoption, given that typically one-third of the cost of operating a commercial jet is associated with fuel consumption. Additionally, in the case of accelerometers, MEMS-based accelerometers have been adopted and have all but supplanted previously employed technologies for the sensing of crashes and the subsequent deployment of air bags. This compelling need for lightweight, low cost, highly reliable devices was created almost entirely by the government mandating the adoption of air bag technology for use in passenger cars.

As in the cases of these two products, it is important to note that initial adoption and deployment resulted from a compelling need for a unique technical or commercial solution, or indeed, a government mandate for a product. This is consistent with the findings of Utterback,<sup>33</sup> who reviewed a large number of retrospective studies and noted that market factors appear to be the primary influence on innovation, and play a critical factor in 60 to 80% of important innovation. Clearly then, as in the framework forwarded by Lyneis, a compelling performance-to-price ratio can be viewed as the strongest determinate in the adoption of MEMS technology. Indeed, today it is generally accepted that most innovation is driven by market demand, i.e., market pull innovation.

A second important observation of MEMs history is that the successful development of this technology resulted not internally to the commercializing companies, but in large part externally through the effort of Sandia National Laboratory and Draper Laboratories, followed by many universities. This is consistent with the findings of Myers and Marquis,<sup>34</sup> who in their extensive study of 157 historical cases of the commercialization of technology, found that 98 of these ideas were the result of information obtained from outside the firm. Similarly, Langrish<sup>35</sup> found that 102 of 158 key ideas instrumental in the

commercialization of 51 innovations came from outside the companies. Indeed, according to Utterback, <sup>36</sup> if the many innovation identified by firms as being commercially successful are studied, it can be concluded that a signficant number (23 to 33%) have been wholly adopted from other firms. If this premise is accepted as being valid, it is clear then that a central requirement for the commercialization of an innovation is some form of information sharing about both the technical dimension of the innovation and the system specific knowledge that could employ this innovation. This engenders the critical question, who are the originators of these ideas and how are they communicated into the firm that ultimately commercializes the innovation?

While there are many factors affecting the commercialization of innovations, seemly two consistently important factors remain paramount. One is the driving force described by Lyneis<sup>37</sup> as the price-to-performance ratio. The second is the capturing of information and the source of innovation.

Von Hippel<sup>38</sup> describes the sources of innovation in a number of industries and, in doing so, broadly categorizes these sources as lying distributed across the functional value chain of an industry. He identifies functional roles of organization as users, manufacturers, suppliers and others.

Von Hippel goes further and attempts to explain why these variations in the sources of innovations occur and how they can be predicted. His hypothesis is, "the analysis of temporary profits (economic rents) expected by potential innovators can by itself allow us to predict the functional source of innovation usefully often." Furthermore, von Hippel defines the innovator as "the individual or firm that first develops an innovation to a useful state, as proven by documented, useful output." Thus, the abilities of firms to protect and benefit from innovations will differ as a consequence of their functional role. For example, innovative users can protect process and process machinery innovations as trade secrets better than other types of innovators. In the case of an equipment manufacturer, the process of selling obviously requires persuasion based on the demonstration of technical competence and/or differentiating

features. Thus, innovations are more difficult to protect. In the case of an industry that is process intensive, the ability to protect innovation as trade secrets is far greater. The data presented are sufficiently compelling to suggest that methods of capturing this shared innovative are predicable useful and could provide a source of competitive advantage. Thus, stemming from von Hippel's work, it might be expected that in process intensive industries including MEMS and ASIC, which afford some measure of protection to innovation, sharing of innovation might be feasible and desirable in speeding the adoption of the technologies.

#### 2.4 Conclusions

The Lyneis<sup>39</sup> model will serve as the starting point for the examination of the MEMS industry. It incorporates many important dynamics forwarded by a number of authors discussed in this review. Additionally, it is possible to capture within its framework, the majority of important dynamics revealed in these studies examining both the ASIC and MEMS industries. In combination with this model, the concepts of "Toolkits for User Innovation" forwarded by von Hippel,<sup>40</sup> which are relevant to particular aspect of user design software in the MEMS and ASIC industries, will be applied.

# 3 Industry Review – Micro-Electro-Mechanical-Systems (MEMS)

Micro-electro-mecrianical-systems (MEMS) describe, at once, a technology, a methodology and a set of physical products. While a universal definition is lacking, MEMS products can be generally characterized as subsystems involving a number of micron-sized components and structures. Frequently, the structures are assumed to be active or moving; however, it has come to be accepted that they simply require a significant vertical dimension from the plane of the material on which they are formed, 41 i.e., they require a

significant three-dimensional nature to their form and/or function. As part of a high-level architecture, the structures enable a distinctive set of functionalities previously unobtainable with devices of this scale. They enable close integration of a variety of functions, typically sensing and actuation with computation and communication. This has led to the development of a large number of MEMS devices in both the commercial and military sectors. Table 3-1and Table 3-2 summarize the broad market segments and revenues that categorize the MEMS industry.<sup>42</sup> It is important to note that the reports on which these tables are based, exclude devices such as micro-fluidics, micro-optics and optical scanners because it is believed these devices lack "mechanical components," as discussed above. While this may not be entirely true and excludes some important categories of MEMS devices, the data provide a sense of how the market is believed to be evolving.

Table 3-1: Analysis and Forecast of the U.S. MEMS Market by Units in 1999 (in Millions of Dollars)

| Year        | Units  | Unit   | Average    | Price  | Revenues      | Revenue   |

|-------------|--------|--------|------------|--------|---------------|-----------|

|             |        | Growth | Units      | Growth | (\$ millions) | Growth    |

|             |        | (%)    | Price (\$) | (%)    |               | Rates (%) |

| 1995        | 35.51  | -      | 9.54       | -      | 338.91        | -         |

| 1996        | 46.56  | 31.1   | 8.78       | (8.0)  | 408.89        | 20.7      |

| 1997        | 58.77  | 26.2   | 8.05       | (8.3)  | 473 29        | 15.7      |

| 1998        | 71.99  | 22.5   | 7.48       | (7.1)  | 538.44        | 13 8      |

| 1999        | 87.18  | 21.1   | 7.05       | (5.7)  | 614.95        | 14.2      |

| 2000        | 102.90 | 18.0   | 6.76       | (4.1)  | 696.01        | 13.2      |

| 2001        | 118.83 | 15.5   | 6.56       | (3.0)  | 779.68        | 12.0      |

| 2002        | 136.27 | 14.7   | 6.45       | (1.7)  | 878.76        | 12.7      |

| 2003        | 155.63 | 14.2   | 6.31       | (2.1)  | 982.33        | 11.8      |

| 2004        | 173.38 | 11.4   | 6.16       | (2.4)  | 1068.20       | 8.7       |

| 2005        | 191.96 | 10.7   | 6.06       | (1.7)  | 1162.55       | 8.8       |

| CAGR (1998- |        |        |            |        |               |           |

| 2005)       |        | 15     |            | (3)    |               | 12        |

Source: Frost and Sullivan Report #5999-32, 1999.

Table 3-2: Analysis and Forecast of the U.S. MEMS Market by Percent in 1999 (in Millions of Dollars)

| Year | Automotive | Defense and | Industrial | Medical |

|------|------------|-------------|------------|---------|

|      | (%)        | Aerospace   | (%)        | (%)     |

|      |            | (%)         |            | . ,     |

| 1995 | 53.6       | 16.2        | 21.4       | 8.9     |

| 1996 | 57.6       | 14.9        | 18.8       | 8.7     |

| 1997 | 59.8       | 14.3        | 17.1       | 8.8     |

| 1998 | 61.0       | 14.3        | 15.8       | 9.0     |

| 1999 | 62.7       | 13.9        | 14.5       | 8.9     |

| 2000 | 63.9       | 13.9        | 13.4       | 8.8     |

| 2001 | 64.3       | 14.3        | 12.7       | 8.8     |

| 2002 | 64.7       | 15.0        | 12.0       | 8.3     |

| 2003 | 65.1       | 15.6        | 11.6       | 7.7     |

| 2004 | 65.0       | 16.1        | 11.6       | 7.3     |

| 2005 | 64.2       | 17.0        | 11.8       | 7.0     |

Source: Frost and Sullivan Report #5999-32, 1999.

It is instructive to compare these 1999 figures to a similar 1997 report summarized in Table 3-3<sup>43</sup>. While the earlier report clearly overestimates the market growth and actual revenues, it was generally accepted at the time that the potential for this technology was enormous, some even suggesting that these numbers were understated. However, as the market has played out, this enthusiasm has been tempered by the constraints of the technology.

Table 3-3: Analysis and Forecast of U.S. MEMS Market by Dollar in 1997 (in Million of U.S. Dollars)

| Year | Automotive | Medical | Information<br>Technology &<br>Industrial | Military and<br>Aerospace | Total   |

|------|------------|---------|-------------------------------------------|---------------------------|---------|

| 1994 | 255.7      | 129.5   | 438.3                                     | 49.1                      | 872.5   |

| 1995 | 298.0      | 146.1   | 459.0                                     | 54.8                      | 957.9   |

| 1996 | 355.0      | 164.4   | 492.8                                     | 62.2                      | 1,074.3 |

| 1997 | 419.0      | 187.0   | 527.0                                     | 71.6                      | 1,204.6 |

| 1998 | 491.5      | 216.7   | 575.0                                     | 79.6                      | 1,363.1 |

| 1999 | 562.0      | 245.7   | 645.9                                     | 95.8                      | 1,549.4 |

| 2000 | 645.7      | 291.3   | 733.3                                     | 110.7                     | 1781.0  |

| 2001 | 758.5      | 354.8   | 836.0                                     | 133.3                     | 2,082.5 |

| 2002 | 879.6      | 444.7   | 995.1                                     | 156.9                     | 2,476.3 |

| 2003 | 1,019      | 562.9   | 1,222                                     | 176.7                     | 2,980.4 |

| 2004 | 1,172      | 716.0   | 1,514                                     | 202.7                     | 3,604.5 |

| CAGR | 16%        | 21%     | 16%                                       | 16%                       | 17%     |

Sources: Frost &Sullivan Report#5549-16, 1997.

NB: (1) Data prior to 1997 is actual.

- (2) Airbag system and Manifold Absolute Pressure (MAP) sensors constitute 90% of the automotive MEMS sector.

- (3) In 1998, the market division was: inkjets 75.6%, displays 5.4%, and industrial 19%.

Today, the industry landscape has more than 50 companies active in the U.S. MEMS market. A large number of these are start-up companies from research laboratories or institutes either marketing a product or technology, or entering partnerships with industry participants.<sup>44</sup> Nonetheless, the majority of revenue for MEMS, remains generated from crash sensors and pressure sensors for medical and automotive use, and is dominated by large semiconductor/sensor firms such as Analog Devices, Motorola and HP. As will be seen latter, it is perhaps no accident that these major players are in the ASIC industry.

Today's major MEMS market applications include accelerometers (or inertial sensors), pressure sensors and ink jet printer cartages. These products require diverse technical and process capabilities, and it is this diversity that characterizes the MEMS industry. Table 3-4, which is taken from a presentation by the US Defense Advanced Research Projects Agency (DARPA), is an excellent characterization of the degree of diversity in the MEMS industry.<sup>45</sup>

Table 3-4: Market Segment and Companies Supported by DARPA

| Technology<br>Area                                   | Typical Devices/<br>Applications                                                                           | Companies.                                                                                                                                                                                                | Market<br>Baseline<br>(\$Millions) | Market 2003<br>(Est.)<br>(\$Millions) |

|------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------------|

| Inertial<br>Measurement                              | Accelerometers, Rate<br>Sensors, Vibration<br>Sensors                                                      | II, Sarcos, Boeing, ADI, EG&G IC<br>Sensors, AfriMi, Motorola, Delco,<br>Breed, Systron Donner, Honeywell,<br>Alfied Signals                                                                              | <b>\$</b> 350 <b>-\$</b> 540       | \$700-\$1400                          |

| Microfluidics and<br>Chemical Testing/<br>Processing | Gene Chip, Lab on Chip,<br>Chemical Sensors, Flow<br>Controllers, Micronozzles,<br>Microvalves             | cal Sensors, Flow ers, Micronozzles, Motomia, Lloydett Packard, Tl. Xerry                                                                                                                                 |                                    | \$3000-\$4450                         |

| Optical MEMS<br>(MOEMS)                              | Displays, Optical Switches,<br>Adaptive Optics                                                             | Tanner, SDL, GE, Samoff, Northrop-<br>Grumman Westinghouse, Interscience,<br>SRI, CoreTek, Lucent, Iridigm, Silicon<br>Light Machines, TI, MEMS Optical,<br>Honeywell                                     | \$25-\$40                          | \$450-\$950                           |

| Pressure<br>Measurement                              | Pressure Sensors for<br>Automotive, Medical, and<br>Industrial Applications                                | Goodyear, Delco, Motorola, Ford, EG&G IC<br>Sensors, Lucas NovaSensor, Siemons, Tt                                                                                                                        | \$390-\$760                        | <b>\$1</b> 100- <b>\$</b> 2150        |

| RF Technology                                        | RF switches, Filters,<br>Capacitors, Inductors,<br>Antennas, Phase Shifters,<br>Scanned Apertures          | Rockwell, Hughes, ADI, Raytheon TI.<br>Aether                                                                                                                                                             | (Essentially \$0<br>as of 1998)    | \$40-\$120                            |

| Othor                                                | Actuators, Microrolays,<br>Humidity Sensors, Data<br>Storege, Strain Sensors,<br>Microsatellite Components | Boeing, Experient TIP, Sarcos, Xerox,<br>Aerospaco, SRI, Hughes, AMM Lucas<br>Novasensor, Samoff, ADI, EG&G IC<br>Serisors, CP Clare, Siemens, ISSYS,<br>Honeywell, Northrop Grumman, IBM,<br>Kionix, TRW | \$510-\$1050                       | \$1230-\$2470                         |

Source: W. Tang, DARPA Micro System Technology Office, 2001.

Furthermore the consensus next killer-application, optical telecommunications components, will similarly have many unique technical and process requirements. Thus, unlike the ASICs market that will be discussed later, the MEMS market is far less homogenous and can be characterized as an assemblage of niche markets. Where unit volumes for some MEMS are substantial, running into the millions of units, production volumes are far more modest then in the ASICs industry. Competition in this market is based predominately on price and performance, together with company reputation for quality and on-time delivery.

## 3.1 Process Technologies

MEMS processing technologies have their roots in the integrated circuit (IC) industry, particularly in complimentary metal oxide semiconductor (CMOS) fabrication. Nonetheless, distinct mythologies have emerged over time with important technical distinctions. Within the context of MEMS, components and structures are generally formed via three process technologies:

- 1) surface micromachinning (SMM)

- 2) bulk micromachinning (BMM) and

- 3) high-aspect-ratio Micromachinning (HARM).

## 3.1.1 Surface Micromachinning

SMM most closely resembles that of CMOS processing. With SSM, thin film material layers are deposited on a wafer or substrate. Generally, the substrate is intended only as a supporting foundation. These deposited layers, which can be sacrificial or structural in nature, are generally composed of polysilicon (doped and un-doped) or silicon dioxide. These were well understood and characterized materials by the CMOS foundries that originally developed these techniques and thus their use was straightforward. Through a series of patterning via traditional optical photolithography, coupled with a number of processes of etching (wet and dry), structural elements can be formed and partially released from the substrate so as to allow mechanical actuation. Figure 3-1 depicts a simple illustration of a process to form a cantilever beam.

Figure 3-1: Basic Process Formation of Polysilicon Cantilever Structure Via SSM

Source W Tang, DARPA Micro System Technology Office, 2001

The primary advantage of SSM is its ability to readily integrate with electric circuitry. Recognizing this, the US Defense Advanced Research Projects. Agency (DARPA) supported the development of a standardized, cost-effective SSM fabrication process, known as MUMPs<sup>TM</sup> (multi-user-MEMS-process). This was supported primarily at the North Carolina Micromachining Center (NCMC), which evolved into Cronos, Inc (see Section 3.3).

The primary disadvantage of SSM is that thermal stress gradients and differences in thermal expansion among the deposited layers can generally cause instability and deformation in devices

# 3.12 Bulk Micromachinning

Bulk micromachinning (BMM) refers to the creation of features and structures directly in the wafer or substrate. Originally developed in the 1950 for the creation of silicon pressure sensors, it is a mature technology when

embodied in a silicon wafer. This methodology primarily revolves around the use of wet chemical agents that selectively etch silicon along specific crystallographic planes. Utilizing masking materials that are carefully aligned to various cryptographic planes and patterned as described above, these masks, which are resistant to the various chemical agents, allow for the selective formation of a number of distinct and useful features in the surface of the wafer (Figure 3-2).

Figure 3-2: Basic Surface Features Created Using BMM Via KOH Etching

Source: W. Tang, DARPA Micro System Technology Office, 2001.

BMM is extremely simply and inexpensive compared to many other micromachining techniques. It produces very stable devices, but it does suffer from very high material usage.

# 3.1.3 High-Aspect Ratio Micromachining

Many non-traditional and new process methodologies have evolved to meet the demand for devices with great vertical dimension relative to the substrate surface. Primary among these are LIGA (a German acronym for: lithography-electroplating-molding) and deep reactive ion etching (RIE).

LIGA is a process whereby a mold of a desired structure is "grown" or formed on a substrate. This is done in three steps. First, a metal substrate is coated with a thick layer of photoresist on which a mask is patterned and developed. To penetrate the thick photoresist, and thus achieve the desired large vertical dimension relative to the feature size (aspect ratio), high-energy synchrotron X-rays are used to transfer the mask image into the resist. Second, the patterned metal substrate is then formed into a mold by growing or forming a metal structure in the developed regions within the photoresist where the metal is then exposed to an electroplating bath. Finally, the mold is used to form structures via injection molding or embossing, usually with a polymer.

Figure 3-3: Basic Methodology of LIGA

Source W. Tang, DARPA Micro System Technology Office, 2001.

Despite its unique ability to form very high-aspect ratio parts, LIGA is severely limited because of the need to use x-rays. Thus, compromises such as SLIGA, which combine some feature of LIGA with other micromachining, have been developed.

Reactive ion etching (RIE) is a technique in which a low-pressure gasplasma is directed to the surface of a material. These highly reactive ions and/or charged particles remove material through a combination of physical and chemical action. By masking a substrate with a material that is selectively resistant to the impinging beam of reactive particles, vertical structures can be created in substrates. While commonly used in IC production for years, recent advances in material and equipment have allowed this technique to be used to create even deeper, high aspect-ratio structures. Unfortunately, this equipment is expensive and the rates at which material can be removed severely limits its application.

# 3.2 MEMS Industry Architecture

Today, many smaller companies operate within emerging and niche markets and offer custom MEMS application-specific manufacturing for a variety of industries. The most notable of these markets is in the telecommunication sector, which has seen industry giants such as Nortel, JDS Uniphase and Corning acquire in quick succession Cortek and Xros, Cronos, and IntelliSense, respectively. The combined acquisition price for these three moderately small companies – whose combined work forces were approximately 150 persons and combined revenues were \$15 million — was in excess of \$2.5 billion. These valuations were a reflection of the project growth of the optical switching and dense wavelength dispersion multiplexing (DWDM) markets. Table 3-5 summarizes the recent market projects for the optical switch market segment.

Table 3-5: Optical Switching Market Projections for North America and Europe

| Region           | 1999<br>(\$b) | 2000<br>(\$b) | 2001   | 2002<br>(\$b) | 2003<br>(\$b) | 2004<br>(\$b) | Annual<br>Growth |

|------------------|---------------|---------------|--------|---------------|---------------|---------------|------------------|

|                  |               |               | (\$b)  |               |               |               | Rate             |

| North<br>America | 104.6         | 431           | 1631.4 | 3544.7        | 6475.1        | 10372         | 212%             |

| Europe           | 47.2118       | 118           | 324.5  | 976.6         | 2685.5        | 4821.7        | 195%             |

Sources: Global Industry Analysts, Report #CF3-0319

With these acquisitions, much of the industry's open foundry capacity has become captive. Only Standard MEMS remains largely independent, with the remainder of capacity being in universities, laboratory environments and to a lesser extend excess capacity in captive houses. While these MEMS companies have each been purchased so as to ensure the role of their parents in the coming changes to the telecommunication components industry, an important business

model is evidenced in two of these recently purchased MEMS foundries, Cronos and IntelliSense (see section 3.3). As will be seen in the review of the ASIC industry, there is recognition on the part of these acquiring companies that the development of full-custom application specific MEMS is complicated and fraught with risk for both the customer and foundry. Indeed, this complication in development frequently leads to extended development periods characterized by significant design iterations. It is often impossible to separate the performance of a device from the process used to fabricate it, or indeed, the equipment on which the process was developed. This fundamental incompatibility between the development cycles for new MEMS devices and industry needs is one of the most important factors impeding the more rapid adoption of MEMS technology. The degree of linkage between process and device performance also distinguishes MEMS from ASIC, which have a far more modular architectural design and process independence.

Nonetheless, as in the early history of ASIC, there has been the emergence of a new business model exemplified by MEMGens that of the "fabless" foundry, meaning that the company own no fixed manufacturing assets. Also present is the emergence of independent design software tools by such companies as Coventar and MEMScAP. Indeed, another sign of the developing industry is the marketing of specialized equipment for the MEMS industry by large companies. Furthermore, there will result general over capacity as each group bets on its position in the market, much as in the case of accelerometers (section 3.4). This is particularly true in this market since appropriability will be somewhat difficult. This results from the breadth of design space and multitude of designs that might address a specific market need. Thus, it seems that the complimentary asset, namely manufacturing assets, will be the initial source of competition. However, as each firm's assets compete and are built assuming optimist market share projections, pressure will mount to achieve better capital utilization. Whether this over capacity will lead to rapid commoditization in other

MEMS application markets remains to be seen, but it seems likely, given the historical precedent in the semiconductor industry.

This phenomenon of rapid commoditization and overbuilding of capacity has been reviewed extensively by Van Bree<sup>46</sup> in the semiconductor industry at large. His study reveals that this behavior continues in a predicable cyclical fashion and is generally exacerbated by normal economic cycles.

#### 3.3 Case Review of Cronos and IntelliSense

Within the MEMS industry, it is instructive to briefly examine the business models of two notable companies that have achieved recent success. As noted, both Cronos and IntelliSense were recently acquired by JDS Uniphase and Corning, respectively. Unique to both of these companies is their use of design software as well as the degree to which they have employed process modularity to drive the adoption of MEMS.

Founded in1993 under the umbrella of The Micromachinning Center of North Carolina (MCNC),<sup>47</sup> the original mission of Cronos was to serve as an incubator and technology research center in semiconductor technology, particularly in the area of CMOS technology. Originally the company was to be supported by the state and federal government, but political fortunes favored a rival organization in Texas that grew to become SemiTech.

Recognizing the need for a new direction, the management team at NCMC quickly reoriented the organization into the MEMS arena. Based on the same premise as SemiTech, the initial funding was aimed at preserving and accelerating the US role in the emerging field of MEMS technology. To that end, the US Defense Advanced Research Projects Agency (DARPA) supported the development of a standardized, cost-effective SSM fabrication process MUMPs<sup>TM</sup> (multi-user-MEMS-process). MUMPs is a three-layer polysilicon surface micromachining process architecture. The design rules for the process are somewhat flexible within the defined terms of layer structure. These consist of a non-patternable silicon-nitride isolation layer, a polysilicon ground plane layer, two

structural polysilicon layers, two silicon dioxide release layers, and one metal layer used for electrical connectivity and/or reflectively enhancement.<sup>48</sup> In many ways this can be though of as an analogous "master-slice" when describing the gate array architecture used in the ASICs industry.

Cronos attributes much of its success in promoting the adoptions of MEMS technology to the MUMPs™ process. The firm reports that MUMPs™ has never been a moneymaker, but instead was particularly useful at pushing the technology into universities. Overall, there has been limited commercial use for the process as it was constructed beyond market development of brand name and future potential customers. Ultimately, more complex and proprietary designs tend to emerge for addressing commercial markets. Nonetheless, in Cronos' sale literature, it promotes they forward the MUMPs™ process as "the most affordable and accessible MEMS prototyping offering in the world."49 The process allows users to purchase a number of one-centimeter square die sites on a pre-scheduled production run. The user simply submits a design, and within 8 weeks, 15 unreleased chips (see section 3.1.1) for each die set purchased are delivered. Further distinguishing Cronos is its explicit reference and use of "MEMS components library based on proprietary actuation and process technology."50 It is highly likely that the evolution of this business model owns its origins to the initial involvement of Cronos in the CMOS industry, a notion supported in the firm's product literature.

"Leveraging MEMS' inherent qualities of miniscule size and robust reliability, Cronos has created a standardized manufacturing platform for MEMS processes and components consisting of simple building blocks that comprise an application-specific approach to MEMS. This approach streamlines MEMS devices into communications products, significantly reducing time-to-market for component and system manufacturers."

Sandia National Labs promotes its own development services and has it own "standard process." The laboratory promotes a formalized program, SAMPLES (Sandia Agile MEMS Prototyping, Layout Tools, Education, and

Services), an introductory short course on Sandia's Ultra-planar Multi-level MEMS Technology (SUMMiT V) and how to design real micromechanical systems in this five-layer process. Similar to MUMPs™, users can purchase space on wafer masks to have their designs fabricated using the SUMMiT V process.

Cronos recently announced a promotional agreement with Coventar, formerly Microcosm Technologies. Established in 1996, Coventar provides MEMS development software, although it attempted to broaden its value proposition by providing in their words:

". a comprehensive approach to MEMS-enabled product development. The Coventar solution combines robust design automation software, professional engineering services, an extensive network of manufacturing partnerships, and a proven methodology that enables companies to efficiently move products from concept to volume manufacturing." <sup>52</sup>

Coventar's initiative with Cronos, JumpStart™, couples Conventar's Catapult™ design tool with integrated layout generators for the Cronos' MUMPs™ and a reserved slot on a the fabrication run. With this tool, developers can "create, verify, and optimize a design using Microcosm's Catapult™ layout software, then seamlessly transfer the design to Cronos for fabrication according to their design specifications." As will be observed, not only does this strategy on the part of Conventar and Cronos borrow from IntelliSense, but it also echoes in many respects, the efforts of LSI Inc. and VLSI Inc. in the ASICs industry in earlier years (see section 4.3).

Fariborz Maseeh founded IntelliSense in 1991 "with the plan to become vertically integrated in design and manufacturing". He began as a consultant in the field of MEMS and over time "incorporated his experience and knowledge into a software tool" which, in turn, became the mainstay of the IntelliSense's business. <sup>54</sup> Today, the firm's software is widely used and recognized in the MEMS community. Nonetheless, IntelliSense expanded into the foundry

business and, having becoming a subsidiary of Corning, plans to further expand its fabrication capacity.

#### 3.4 Case Review of Accelerometers

The prototypical killer application that has characterized the emergence of MEMS technology into everyday life is the crash senor, or accelerometer. Robinson has reviewed the history of the development of the MEMS accelerometer for crash sensing and airbag deployment. Presented here is a brief synopsis of Robinson's review to highlight some of the key driving forces behind MEMS.

Prior to 1995, Breed Automotive (now Breed Technologies) dominated the automotive crash sensor market, supplying nearly 59% of all the crash sensors used in US made cars. These eletromechanical sensors where limited in their appeal to automakers for a number of reasons, primary among these was their cost, which was between \$15 to \$18 each, with three to five devices being required for each car. Also important was the sensors inability to discriminate between the severity of collisions, and between collisions and other types of impacts.

It was into this environment that the MEMS-based accelerometers were introduced. Unlike previous electro-mechanical switches, MEMS accelerometers converted acceleration into a proportional output voltage. Early work on these devices was conducted at the University of California, Berkeley, and at numerous smaller companies (IC Sensors, SemSym and NovaSensor). Recognizing the commercial applicability of these devices, large integrated circuit companies (Motorola and Analog Devices) quickly followed suit. These new devices addressed the major shortcomings of the electromechanical switches being employed at the time. Since the sensors were processed using silicon semiconductor-based batched processing, costs were significantly reduced. Furthermore, the ability of the devices to produce variable signal output allowed

the sensors to be coupled with signal processing ICs, which enabled a single point "smart " sensor capable of self-calibration, self-diagnoses and crash discrimination. These signficant economic and performance advantages led quickly to the universal adoption of MEMS accelerometers for crash sensing and air bag deployment. This unique combination of superior performance and price is perhaps the best definition of the so-called killer-applications.

The mere existence of a killer-application does not ensure that any specific company will be able to capture the value offered by the opportunity afforded. In this instance, the functional buying relationship and norms of the industry were such that automakers preferred to buy complete subsystems, rather than individual components. Thus, sensor manufactures were forced to partner with existing system integrators. In many ways, then, the development of the infrastructure and relationship to sell to automakers limited the ability of the sensor manufactures to capture much of the value chain, and necessitated carefully select partners who might bring these elements to the partnership. In essence, this industry-specific knowledge was in ways, equally important to the early adoption of MEMS based accelerometers in the design of automobiles.

The early manufacture of MEMS-based accelerometers can be categorized in one of two ways:

- Semiconductor companies that specialize in the production of microelectronic devices (e.g., Motorola, Analog Devices and EG&G) and

- 2) Integrated automobile component and system suppliers (e.g., Delco Electronics, Bosch and Siemens).

These groups each tried to leverage their primary strength. Two basic design architectures emerged: monolithic and hybrid. Analog Devices (AD) led the development of monolithic devices, which incorporated both the signal processing and mechanical structures onto the same silicon chip. It was hoped that this integration would enhance the device performance and lead to

manufacturing cost advantages. Packaging represents a significant portion of the device cost (about 25%) and, thus, the single chip approach represented a judgment that the added cost of integrating more processing into the chip (and thus yields) would be offset by gains on packaging costs.

Motorola leads the hybrid design, which separates the processing and mechanical elements onto two separate chips. Since device cost scale with silicon area, material cost tended to be higher for this approach. Furthermore, there are added costs in mating the two chips. However, this approach involves far less process complexity, and the device yields are expected to be higher. Moreover, companies with existing ASIC facilities (including AD and Motorola) could avoid duplicated capital costs that are inherent in building specialized integrated process facilities.

As the MEMS accelerometer industry evolved, it became clear that automobile makers would continue to foster strong rivalry among their suppliers and demand increasingly lower prices. Coupled with the need of the sensors manufacturers to maintain high utilization of their facilities in order to distribute fixed costs, margins plummeted and power shifted to system integrators. Indeed, Breed Technologies the manufacturer of the original electromechanical crash switch, responded quickly and moved to diversify and vertically integrate, purchasing AlliedSignal's safety restraint business and forming a joint venture with Siemens Automotive to sell complete safety restraints systems. Breed went so far as to backward integrate and purchased Vaisala Technologies in order to develop competencies in micromachined sensors.

# 4 Industry Review – Application Specific Integrated Circuits (ASICs)

The relatively short history of the application specific integrated circuit (ASIC) industry has been marked by volatility. There have been numerous mergers and exits, numerous new products and processes, and many new

methodologies. Few agree entirely on the precise definition of ASIC, with the term being applied to virtually every type of chip that was designed to perform a specific set of tasks. One way to define ASIC is by their intended use and the source of the design. This definition has been adopted for this thesis. ASICs are integrated circuits designed predominately by end-users, specifically for their proprietary application. For example, a maker of an automobile might specify an ASIC to perform some or all of the product specific electronic functions for engine control required in the design. In contrast, application-specific standard products (ASSP) are integrated circuits that have a specific narrow range of applications, but are developed for multiple users. The term "chip-set" is often used to refer to these devices. An example is ICs that incorporate a number of major functions for personal computers. In contrast to ASSP are standard integrated circuits with a function useful in a wide myriad of applications, e.g., memory chips.

Like many industries, customers remain the driving force behind the development of the ASICs industry. Although a few large, broad-based semiconductor companies dominate the market, the wide range of customer requirements has created market opportunities for hundreds of smaller suppliers. Nonetheless, customer adoption of this technology has been slower then predicted. Forecasts for industry growth during the mid-1980s predicted that ASICs would capture fully 50% of the total semiconductor market. However, by 1990, the number was only about 15%. The overall industry is substantial, with sales in 1994 of \$13.5 billion.<sup>56</sup>

From media reports, it might be concluded that the ASIC market is dominated by high-performance, 100,000+ gate devices. But this remains a small portion of the overall market. Nonetheless, it is these relative few applications that push the market in conjunction with the EDA (electronic design automation) tools that are used to design these high-end devices. It has been reported that the vast majority of electronic design engineers have never designed an ASIC and thus the expectation that system designers would naturally migrate to this technology has not come to pass. A great deal of time is

necessary to research, acquire and install trained people to successfully use these tools.<sup>57</sup>

Another signficant factor having an impact on the acceptance of ASIC is their perceived risk. Today, there is a 50% chance that an ASIC will be fully operational when first introduced. With the high development costs and long lead-time of many ASIC production methodologies, there is an understandable reluctance on the part of many to utilize ASIC designs.

These long lead times have had an interesting side effect, which reveals itself in the way computer aided engineering (CAE) tools are developing. Most software vendors tend to cater to the needs of their existing customers, the most experienced and knowledgeable ASIC designers. Thus, CAE designers are lead to ever increasing levels of sophistication and mature products, at least from the perspective of their existing users. Even so, adoption is inevitable, given the increasingly complex nature of electronics and the need for tailored electronics in such devices as cellular phones. However, this failure to recognize the needs of the potential new or more mainstream electrical engineers makes adoption far more difficult. As will be seen, this has created an opportunity for a different model.

## 4.1 Process Technologies

Integrated circuits are generally constructed on the surface of thin silicon wafers and processed through a series of steps that involve the deposition of various thin layers of semiconducting, insulating and metal layers. These layers are patterned with photo-resistance materials that are exposed to light and devolved much like a photograph. These patterns are then transferred into the deposited layer through various forms of chemical etching that preferentially attacks the deposited layer relative to the undeveloped photo resist, which acts to mask certain areas. The semiconductor and isolating materials serve to form such elements as resistors and capacitors, while the metal serves to interconnect these elements. The combination of these elements form transistors and are the basis of modern integrated circuits (ICs).

ICs can be produced with a variety of semiconductor technologies, including metal-oxide-semiconductor (CMOS) or bipolar. Components of like function are built differently in each of these technologies, and each technology is selected for various overall performance characteristics, such as power consumption or switching speed.

## 4.2 ASIC Industry Architecture

Once having decided to employ ASIC as a solution, there are a number of various solutions, or design architectures, that can be applied. This are summarized in the ASIC family tree shown in Figure 4-1:

Custom Semi-Custom

Cell Based Array-Based PDL

Figure 4-1: ASIC Architectural Family Tree

Sources: Adopted from Schroeter, 1992, Figure 2.2, p.10)

These architectures have evolved over time as a means of providing customized solutions, with significantly reduced time and cost. A key component of these architectures that reduces development time and costs is their enabling of less knowledgeable engineers to design integrated circuits without having to have extensive knowledge of the physical make-up and properties of the semiconductor devices themselves. The four basic architectures are:

- full-custom architecture,

and three semi-custom architectures namely;

- 2) cell-based,

- 3) array-based, and

- 4) programmable logic (PLD) architectures.

Full-custom designs are so called because their entire fabrication is unique to the particular ASIC chip under consideration. By comparison, semi-custom approaches use predefined cell structures that are layered on a prefabricated transistor grid. The degree to which the user can define interconnections and layout determines the specific semi-custom architecture.

In the full-custom architecture, each circuit element in the design (transistor, resistor, capacitor and interconnect) is drawn out and positioned in the circuit layout. This gives the maximum design flexibility because each circuit element can be optimized along a number of dimensions and the amount of silicon real estate that is consumed can be minimized. This approach is typically used when it is known that very high volume production will result. With this method, however, there are considerable development costs and time. Furthermore, because these designs are typically specific to the process constraints of a given fabricator (i.e. line widths and spacing), these designs are frequently not portable to other facilities. Thus, while full-custom encompasses the majority of ASIC production starts, it is the only ASIC architecture whose use is declining.<sup>58</sup>

Cell-based architecture offers a compromise between full-custom and array-based architectures. It uses predefined circuit elements called cells, but allows the user to vary the layout. Cells are pre-tested circuit modules that simplify design for the user, who no longer requires special knowledge of the internal transistor level design of the circuit element. The cells are generally stored in a library that is specific to the ASIC's vendor's process. The user simply selects and places the symbol of a desired circuit element in a circuit schematic, simulates the design, and then forwards the design to the vendors, who translates the circuit design into a physical layout design compatible with their process. Cell libraries continue to exhibit ever-greater complexity such that they permit integration of relatively high-level functions, e.g., core microprocessors, peripheral controllers, random-access memory (RAM), read-