### A Stereo Vision System with Automatic **Brightness Adaptation**

by

#### Keith G. Fife

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degrees of

Master of Engineering

and

Bachelor of Science in Electrical Engineering and Computer Science

at the

Massachusetts Institute of Technology

May 1999

State of Technology. All rights reserved.

| Signature of Author |                                                                         |        |

|---------------------|-------------------------------------------------------------------------|--------|

| S                   | Department of Electrical Engineering and Computer Science<br>7 May 1999 |        |

| Certified by        |                                                                         |        |

|                     | Charles G. Sodini, Ph.D.                                                |        |

|                     | Professor of Electrical Engineering                                     |        |

|                     | Thesis Supervisor                                                       |        |

|                     |                                                                         |        |

| Accepted by         | - CARCINE -                                                             |        |

| •                   | Arthur C. Smith, Ph.D.                                                  |        |

|                     | Professor of Electrical Engineering                                     |        |

|                     | MASSACHUSETTS INSTITUTE Graduate Officer                                |        |

|                     | OF TECHNOLOGY                                                           | CHIVES |

|                     | MASSACHUSETTS INSTITUTE OF TECHNOLOGY  NOV 0 9 1999                     |        |

|                     | I IDDADIES   1 100 0 1000                                               | •      |

LIBRARIES

#### A Stereo Vision System with Automatic Brightness Adaptation

by

#### Keith G. Fife

Submitted to the Department of Electrical Engineering and Computer Science on 7 May 1999 in partial fulfillment of the requirements for the degrees of Master of Engineering

Bachelor of Science in Electrical Engineering and Computer Science

#### **Abstract**

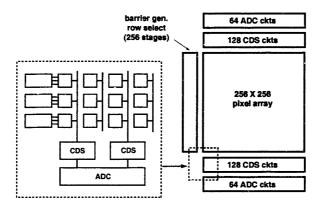

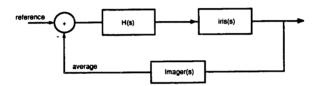

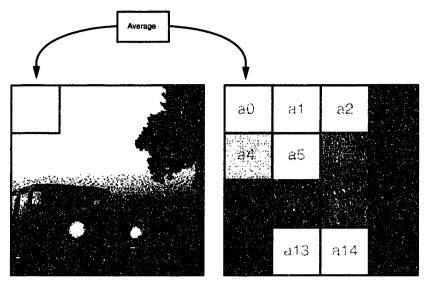

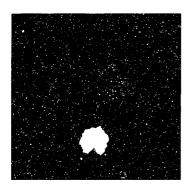

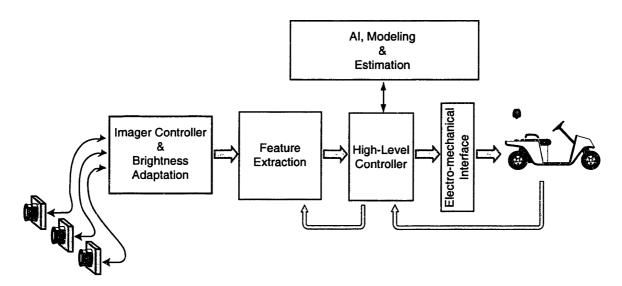

This thesis describes the development of an automatic brightness adaptive imaging system for use in stereo vision algorithms implemented for a variety of processing architectures. A  $256 \times 256$  array of wide dynamic range pixels with on-chip A/D converters provides the digital data path for a feedback network which controls the charge integration parameters at each pixel. The first goal of the project was to build a real-time demonstration of the imager with configurable compression functions. Secondly, electronic irising was employed by controlling the global charge integration time based on the average intensity of the image. In addition to electronic-irising, the imaging system employs a linear or a logarithmic compression scheme based on the image data. The controller fits the compression function to the image by comparing the average intensities of many different regions within the image. Finally, a 3-camera stereo-vision system was developed with data transfer to a PC through the PCI bus at 60fps. The imagers are synchronized and controlled based on the center imager's data which allows for consistent object correlation in stereo vision algorithms.

Thesis Supervisor: Charles G. Sodini Title: Professor of Electrical Engineering

# Acknowledgments

I am very grateful to the number of people who have contributed to the successful completion of my master's project.

First, I'd like to extend my gratitude to Professor Charles Sodini for providing me with this research opportunity. Throughout the project he exhibited trust in my judgment and confidence in my ability. I also thank Dr. Ichiro Masaki for his insight and judgment in this technical field.

Without the help of Zubair Talib I would not have been able to meet the deadline for the first stage of this project. He also helped me out with general computing issues and warmed me up to the idea of using PCs rather than UNIX Workstations when the proper tools fit better there. He also provided many useful tools such as perl programs and LATEX documents. Thanks to Lane Brooks for being the key player in developing the software for displaying the 3 real-time images on the PC.

I thank all of the students and staff in Professor Sodini's research group. Many thanks to Steven Decker for his help on the first stage of the project and in general for creating the CMOS imager chip upon which this thesis is based. Pablo Acosta-Serafini allowed me to move the lab into our office and lengthen my desk with the infamous desk extender. Jim MacArthur offered assistance and advice with design and general engineering problems. Many thanks are in order to Patricia Varley and Anne Hunter for their generous assistance in dealing with MIT administrative tasks.

Finally, I thank my family. In addition to all her support, and despite her busy schedule, my wife kindly proof-read my thesis. I also thank my Mom and Dad. It was they who encouraged me to explore my scientific interests while growing up. I'm very grateful for their constant support, encouragement, and money.

# Contents

| 1 | Inti | roduction                                                     | 15 |

|---|------|---------------------------------------------------------------|----|

|   | 1.1  | Imager Architecture                                           | 16 |

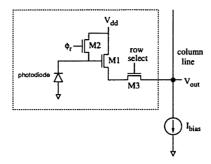

|   |      | 1.1.1 3 Transistor MOS pixel                                  | 16 |

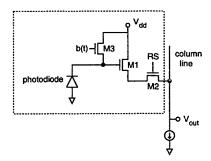

|   |      | 1.1.2 Wide-Dynamic Range MOS pixel                            | 17 |

|   | 1.2  | Imager System Requirements                                    | 18 |

|   | 1.3  | Automatic Brightness Adaptation                               | 18 |

|   | 1.4  | Project Description                                           | 19 |

|   | 1.5  | Thesis Organization                                           | 19 |

| 2 | Ima  | ager Architecture and Compression Functions                   | 21 |

|   | 2.1  | The Pixel Array                                               | 21 |

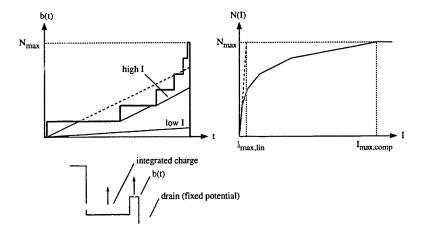

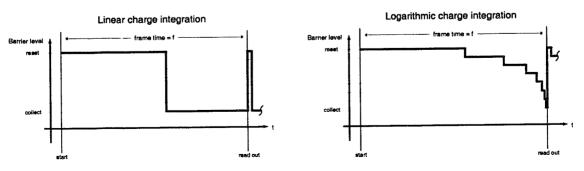

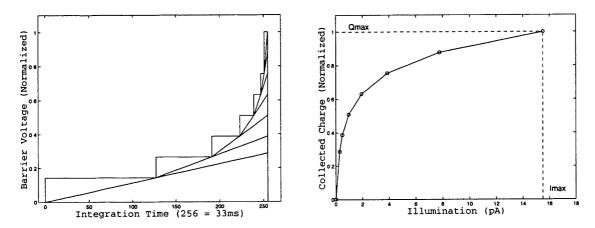

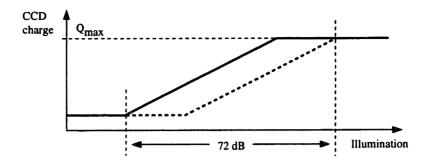

|   | 2.2  | The Compression Function                                      | 23 |

|   | 2.3  | Adjusting Global Integration Period                           | 26 |

|   | 2.4  | Compression Function Used for Automatic Brightness Adaptation | 27 |

| 3 | Alte | ernative Brightness Adaptive Schemes                          | 29 |

|   | 3.1  | Image Sensors with Extended Dynamic Range                     | 29 |

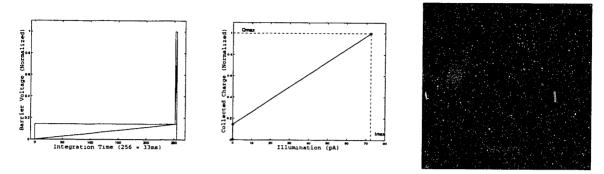

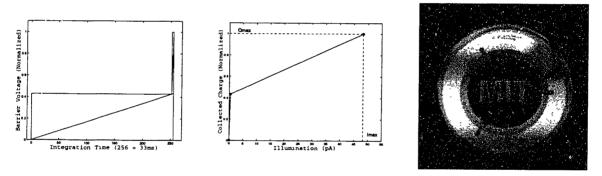

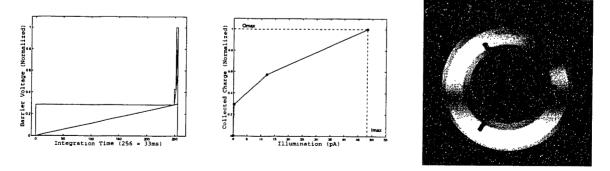

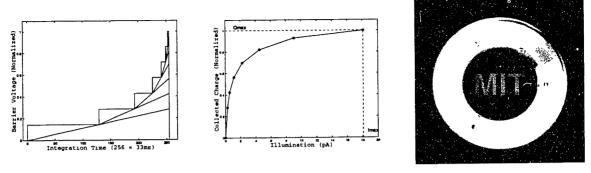

|   |      | 3.1.1 Multiple Integration Periods                            | 29 |

|   |      | 3.1.2 Non-Linear Pixels                                       | 32 |

|   | 3.2  | Techniques for Automatic Iris control                         | 32 |

|   |      | 3.2.1 Mechanical Irising                                      | 32 |

|   |      | 3.2.2 Electronic Irising                                      | 33 |

|   | 3.3  | Systematic Solutions for Intelligent Vehicles                 | 33 |

| 4 | Des  | ign                                                           | 35 |

|   | 4.1  | Overview                                                      | 35 |

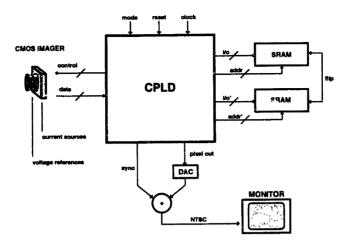

|   |      | 4.1.1 Real-Time Demonstration                                 | 35 |

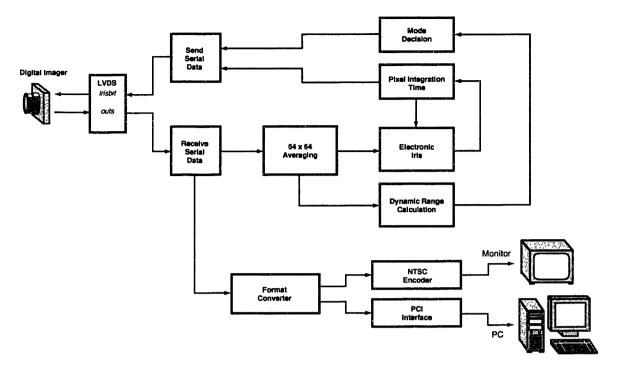

|   |      | 4.1.2 Digital Imager                                          | 35 |

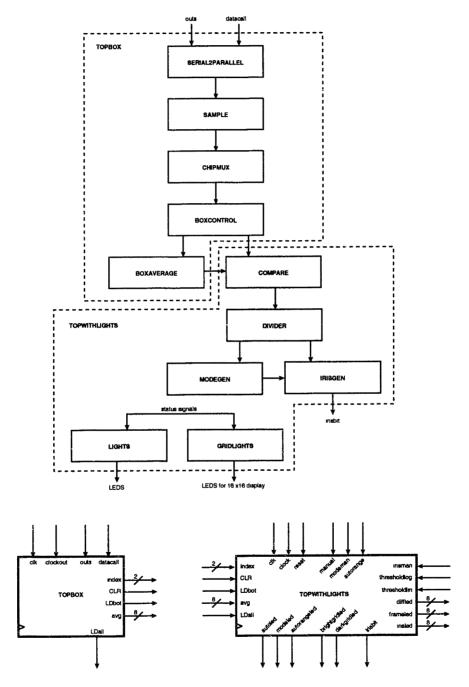

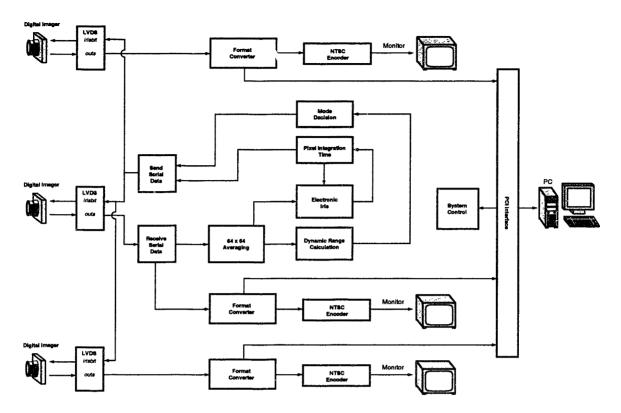

|   |      | 4.1.3 Automatic Brightness Adaption System                    | 36 |

|   |      | 4.1.4 PCI Interface                                           | 38 |

|   | 4.2  | Real-Time Camera Implementation                               | 39 |

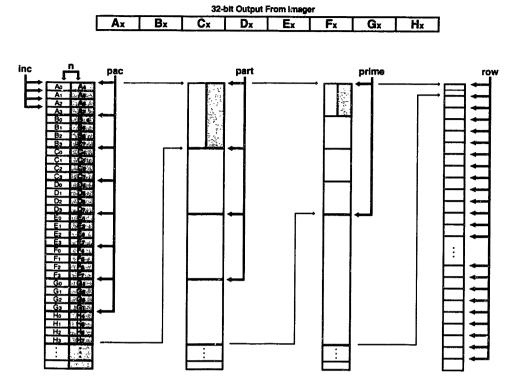

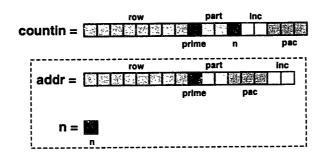

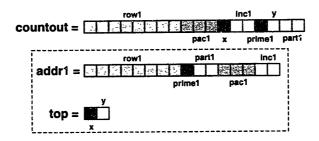

|   |      | 4.2.1 Format Converter                                        | 39 |

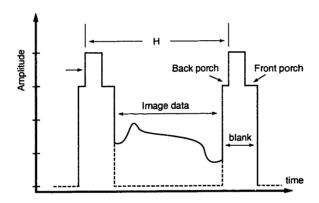

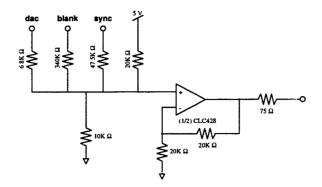

|   |      | 4.2.2 NTSC Encoder                                            | 42 |

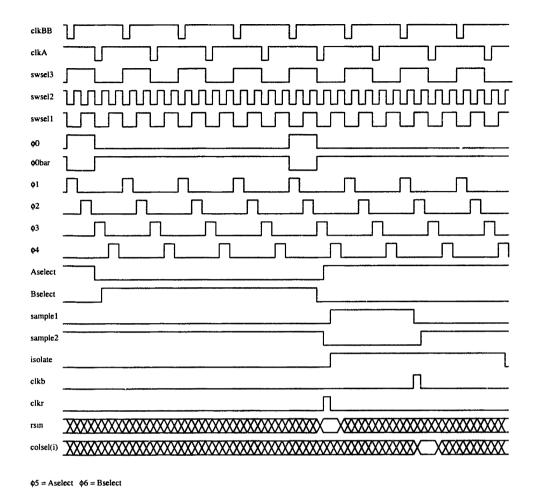

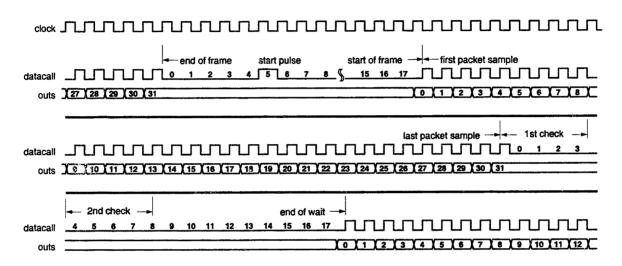

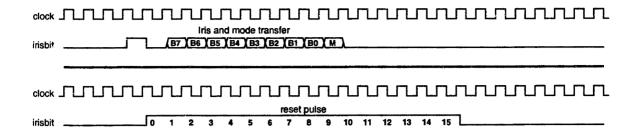

|   |      | 4.2.3 Imager Timing Signals                                   | 45 |

|   | 4.3  | Digital Imager Implementation                                 | 47 |

8 CONTENTS

|   | 4.4 $4.5$ |         | atic Brightness Adaptation Controller Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 49<br>53 |

|---|-----------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5 | Res       | ults    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 55       |

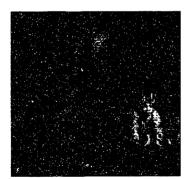

| • | 5.1       |         | me Imager Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 55       |

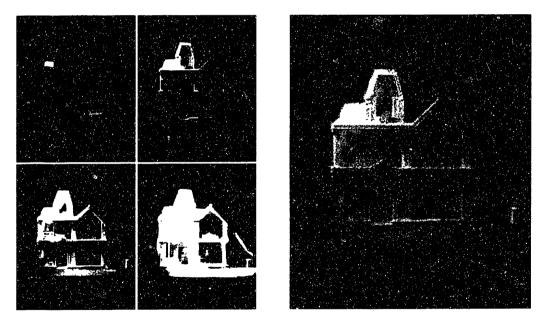

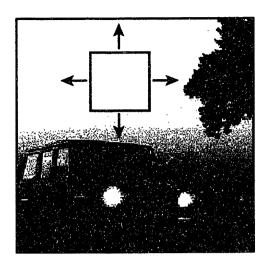

|   | 5.2       |         | atic Brightness Adaptation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 56       |

|   | 5.3       |         | terface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 59       |

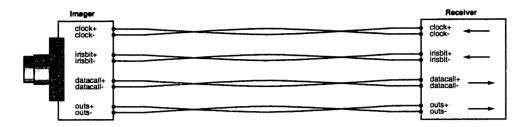

|   | 5.4       |         | era System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60       |

| 6 | Con       | clusior | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 63       |

| • | 6.1       |         | -<br>ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 63       |

|   | 6.2       |         | Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 63       |

|   | Refe      | erences | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 66       |

| A | Rea       | l-Time  | Imager Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 71       |

|   |           |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 71       |

|   |           | A.1.1   | Top Level VHDL - ims: vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71       |

|   |           | A.1.2   | Imager Timing and Barrier Function - image.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73       |

|   |           | A.1.3   | Top Level VHDL - format.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 76       |

|   |           | A.1.4   | Format Conversion - inout.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 78       |

|   |           | A.1.5   | NTSC encoder - ntsc.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 82       |

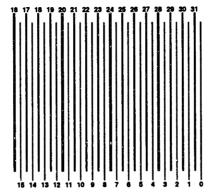

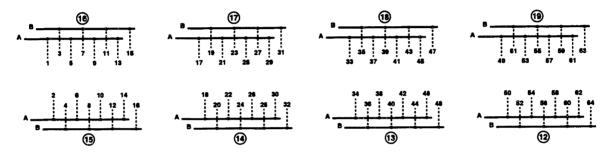

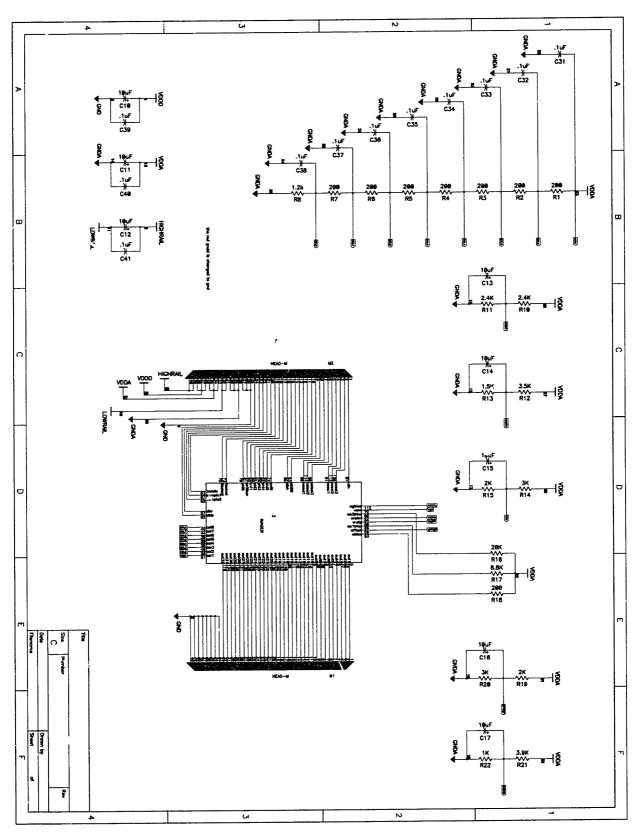

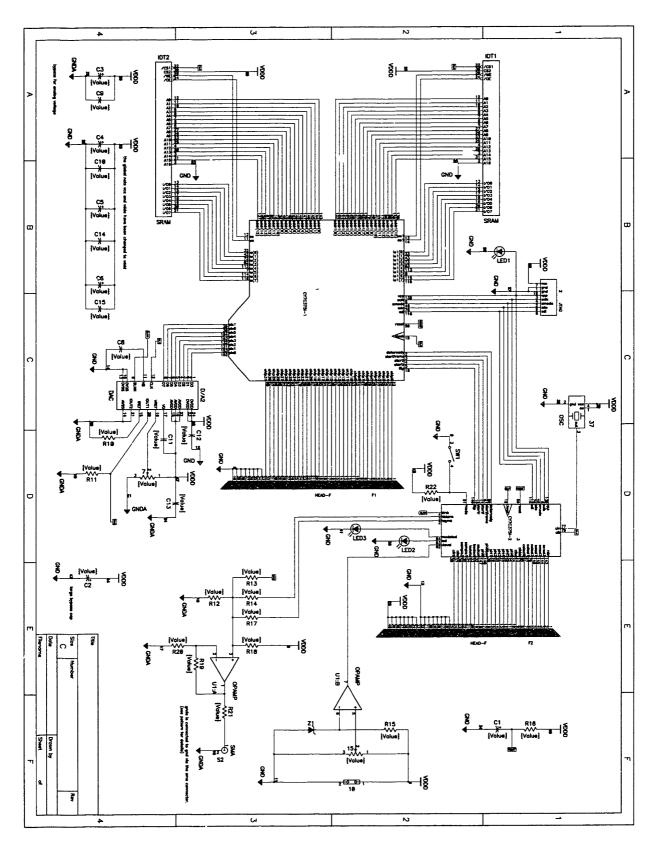

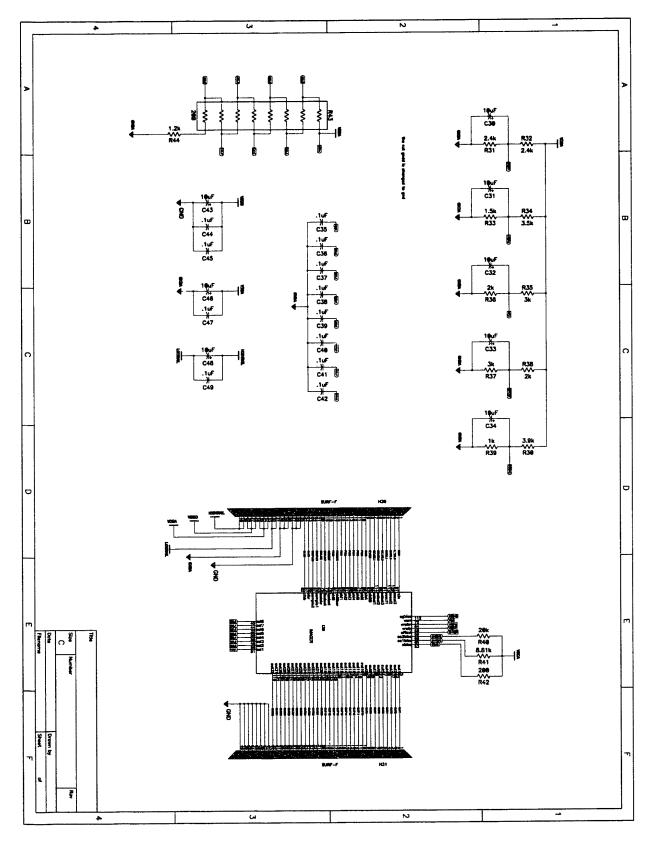

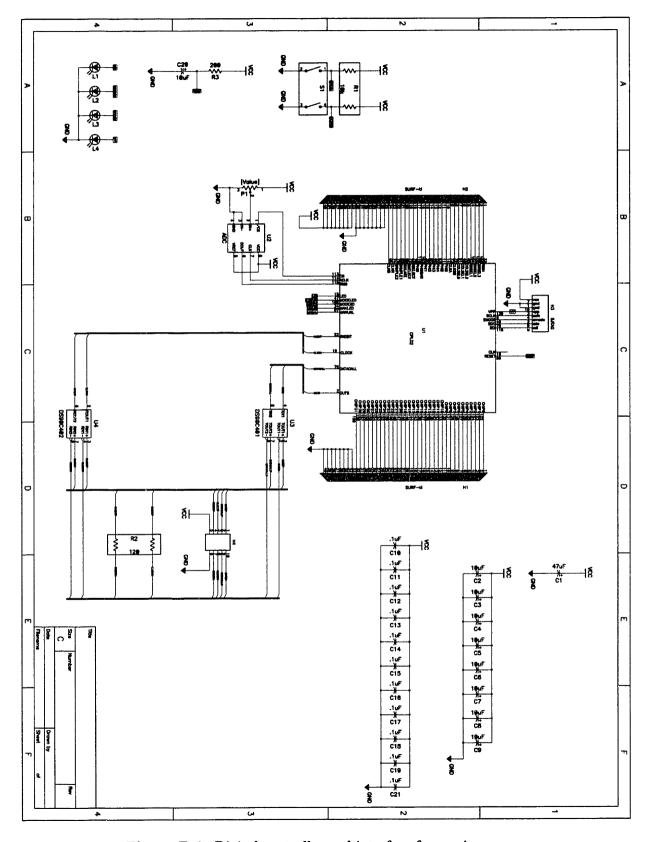

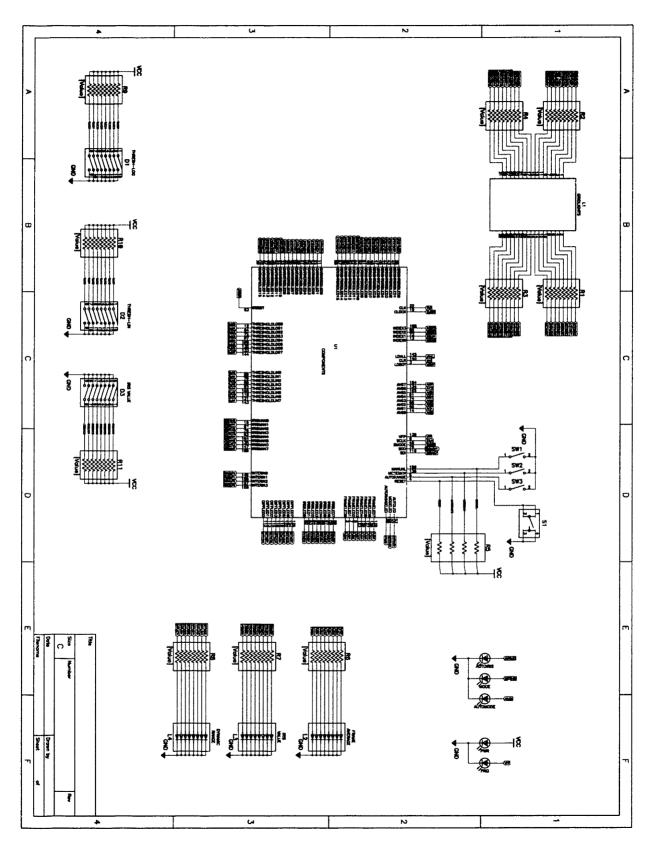

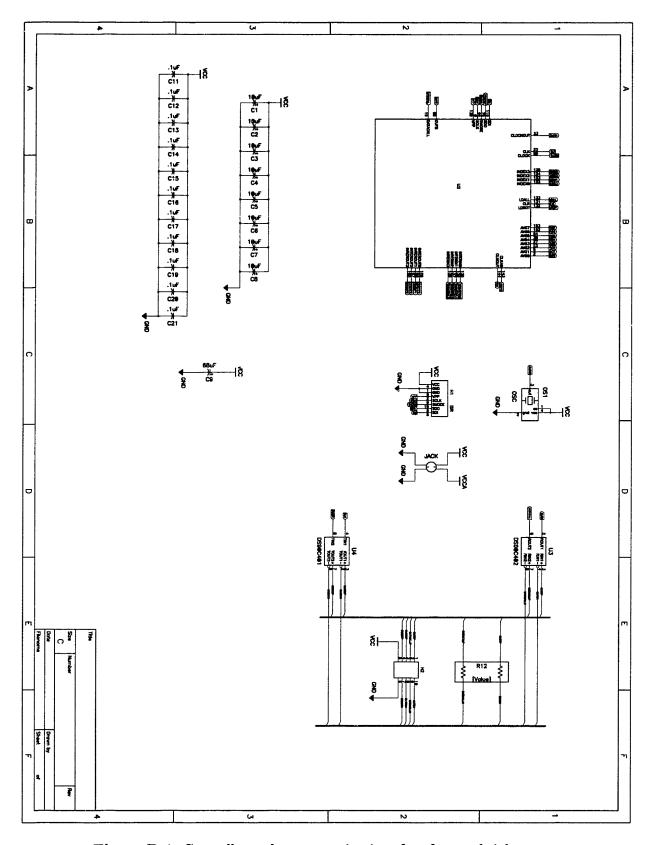

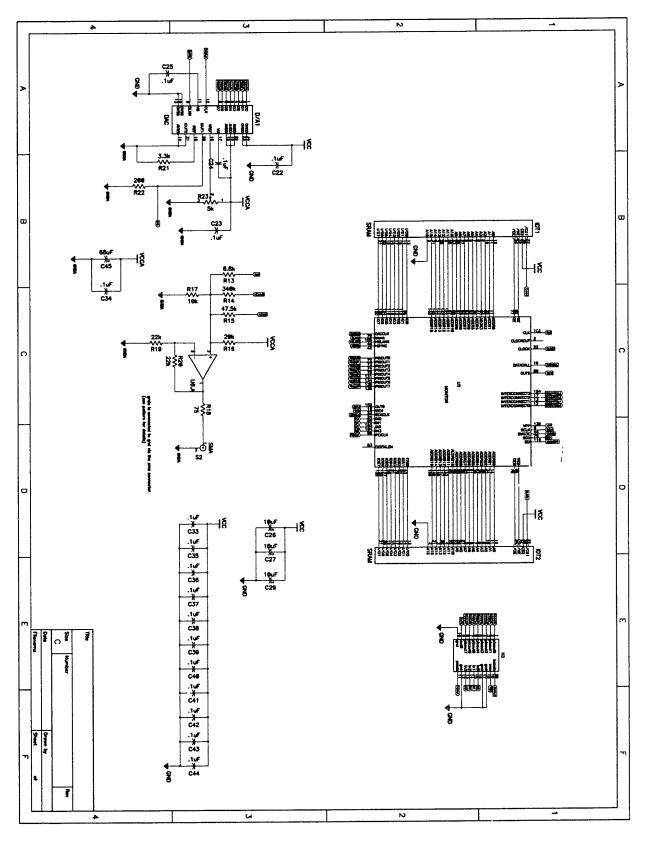

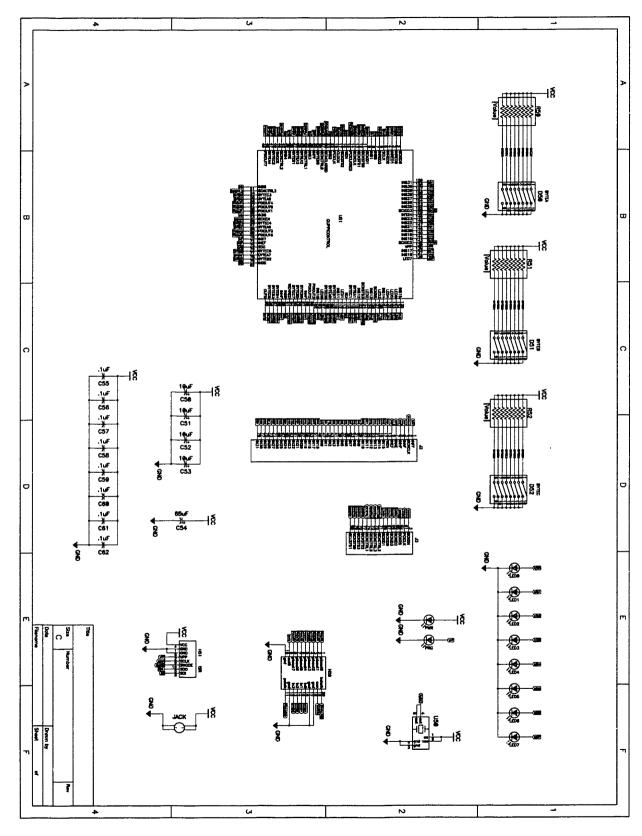

|   | A.2       | Schem   | atics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 83       |

| В | Aut       | omatic  | Brightness Adaptation Demonstration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 87       |

|   | B.1       | VHDL    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87       |

|   |           | B.1.1   | Top Level - imsync.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 88       |

|   |           | B.1.2   | Data Protocol and Barrier Generation - image.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 91       |

|   |           | B.1.3   | Package for all Digital Imager Signals - imagertiming.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 95       |

|   |           | B.1.4   | Top Level - topbox.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 97       |

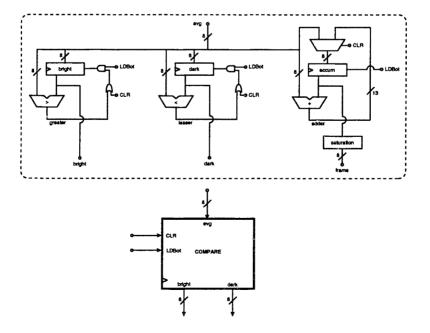

|   |           | B.1.5   | Controller for Arithmetic Functions - boxcontrol.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 100      |

|   |           | B.1.6   | Sychronous Sample - sample.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 101      |

|   |           | B.1.7   | Serial to Parallel Converter - serial2parallel.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 102      |

|   |           | B.1.8   | Selector - chipmux.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|   |           | B.1.9   | Dual of France State of the Sta |          |

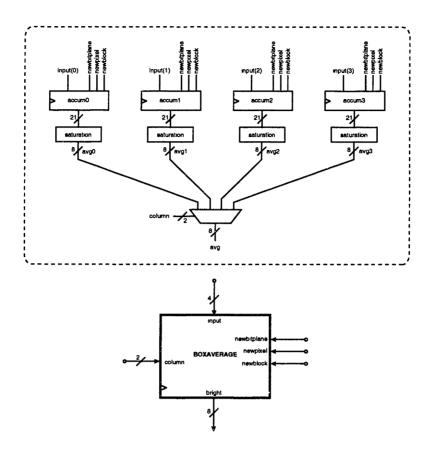

|   |           | B.1.10  | Generating Averages - boxaverage.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 105      |

|   |           | B.1.11  | Top Level - topwithlights.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 107      |

|   |           | B.1.12  | Output Signals - lights.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 110      |

|   |           |         | Next Level - topcomponents.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 111      |

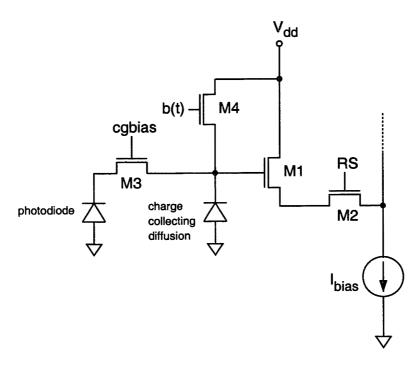

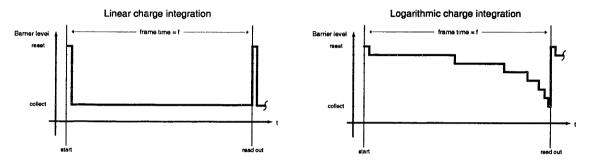

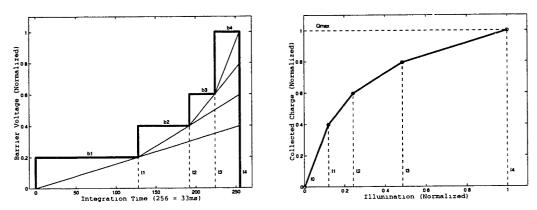

|   |           |         | LED display for Dynamic Range - gridlights.vhd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 113      |