## The System Architecture Concept in Axiomatic Design Theory: Hypotheses Generation & Case-study Validation

by

Tae-Sik Lee

B.S., Mechanical Engineering Seoul National University, 1997

Submitted to the Department of Mechanical Engineering in Partial Fulfillment of the Requirements for the Degree of

#### MASTER OF SCIENCE IN MECHANICAL ENGINEERING

at the

#### MASSACHUSETTS INSTITUTE OF TECHNOLOGY

May 1999

[June 1000]

© 1999 Massachusetts Institute of Technology All rights reserved

| Signature of Author | ARCHIVES                                                                                      |

|---------------------|-----------------------------------------------------------------------------------------------|

|                     | Department of Mechanical Engineering  May 7, 1999                                             |

| Certified by        |                                                                                               |

|                     | Nam P. Suh                                                                                    |

|                     | Ralph E & Eloise F Cross Professor & Mechanical Engineering Department Head Thesis Supervisor |

| Accepted by         |                                                                                               |

|                     | Ain A. Sonin                                                                                  |

| Ch                  | airman, Department Committee on Graduate Students                                             |

# The System Architecture Concept in Axiomatic Design Theory: Hypotheses Generation & Case-study Validation

by

#### Tae-Sik Lee

Submitted to the Department of Mechanical Engineering on Mr y 7, 1999 in Partial Fulfillment of the Requirements for the Degree of Master of Science in Mechanical Engineering

#### **ABSTRACT**

This thesis presents an investigation of a System Architecture (SA) as defined within Axiomatic Design (AD) theory. A system design is essentially the same as the design of simple products, when considered within the theory of Axiomatic Design. This correspondence enables the Axiomatic Design framework for a design process to be applicable to the design of systems. A list of hypotheses is presented to formalize the issues concerning system design using Axiomatic Design and the concept of System Architecture. The aim is to provide an understanding of the concept of System Architecture in Axiomatic Design for designers to design a system in a rational approach.

The hypotheses address three issues: system representation, system design, and the coordination of system elements. Fundamental concepts within Axiomatic Design support these hypotheses, and an industrial case study illustrates the validity of the hypotheses. The concept of System Architecture and system design using Axiomatic Design discussed in this thesis can contribute to the development of a rational approach to the design of a system.

Thesis Supervisor: Nam P. Suh

Title: Ralph E & Eloise F Cross Professor & Mechanical Engineering Department Head

|  |  | , |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

#### Acknowledgements

I would like to thank Professor Nam P. Suh for his vision and support throughout this research project. This thesis was possible because of his guidance and patience to give an opportunity to explore ideas. I would also like to thank Dr. Larry H. Oh of Silicon Valley Group, Inc. for his intellectual and moral support. My sincere thanks go to Derrick Tate for his invaluable suggestions and sound criticism.

I would like to thank all the members of the Axiomatic Design Group at MIT for their constant contribution to the current body of knowledge within Axiomatic Design. Deserving special mention are Jason Hintersteiner and Sunghee Do for the numerous inspiring discussions and general assistance throughout my time at MIT.

I am grateful to Silicon Valley Group, Inc. for funding this thesis work and offering an opportunity to validate the theory through an industrial application.

Most of all, I wish to thank my family for their unconditional support and constant encouragement through the years of education. Without their love, the task of completing this thesis would not have been as enjoyable as it has been.

## **TABLE OF CONTENTS**

| ABSTRACT                                           |            |

|----------------------------------------------------|------------|

| ACKNOWLEDGEMENTS                                   |            |

| <i>TABLE OF CONTENTS</i>                           |            |

| LIST OF FIGURES                                    |            |

| LIST OF TABLES                                     |            |

| 1. INTRODUCTION                                    |            |

|                                                    |            |

| 1.1 MOTIVATION                                     |            |

| 1.2 OBJECTIVES                                     |            |

| 1.3 RESEARCH METHOD                                |            |

| 1.4 THESIS OVERVIEW                                | 14         |

| 2 SYSTEM ARCHITECTURE                              |            |

| 2.1 SYSTEM ARCHITECTURE IN AXIOMATIC DESIGN        | 15         |

| 2.1.1 What is a 'System' and 'design of a system'  | 15         |

| 2.1.2 System architecture (SA)                     | 18         |

| 2.2 CREATION OF SYSTEM ARCHITECTURE                | 19         |

| 2.2.1 Design processes in Axiomatic Design         | 19         |

| 2.2.2 Elements of System Architecture              | 26         |

| 2.2.3 Representation of System Architecture        | 28         |

| 2.2.3.1 Tree Diagram                               | 28         |

| 2.2.3.2 Module-Junction Diagram                    |            |

| 2.2.3.3 Flow chart                                 |            |

| 2.3 SUMMARY                                        |            |

| 3 HYPOTHESES ON AXIOMATIC DESIGN AND SYSTEM ARCHIT | TECTURE 32 |

| 3.1 LIST OF HYPOTHESES                             | 32         |

| 3.2 ARGUMENT ON VALIDITY                           | 34         |

| 3.3 Test/validation strategy                       |            |

|                                                    |            |

| · · · · · · · · · · · · · · · · · · ·              |            |

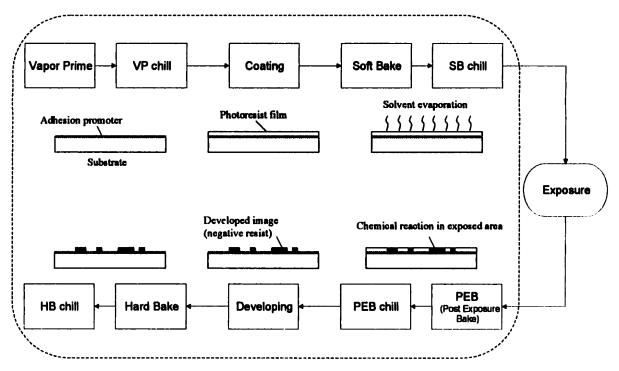

| 4.1 PHOTORESIST PROCESSING                         |            |

| 4.2 DECOMPOSITION FOR TRACK SYSTEM                 |            |

| 4.2.1 Background                                   |            |

| 4.2.2 Decomposition                                | 5 <i>2</i> |

| 4.2.2.1     | 1st Level                                                  | 53 |

|-------------|------------------------------------------------------------|----|

| 4.2.2.2     | 2 <sup>nd</sup> Level                                      | 57 |

|             | Check Design Decision consistency (Level 1 & Level 2)      |    |

|             | 3 <sup>rd</sup> Level                                      |    |

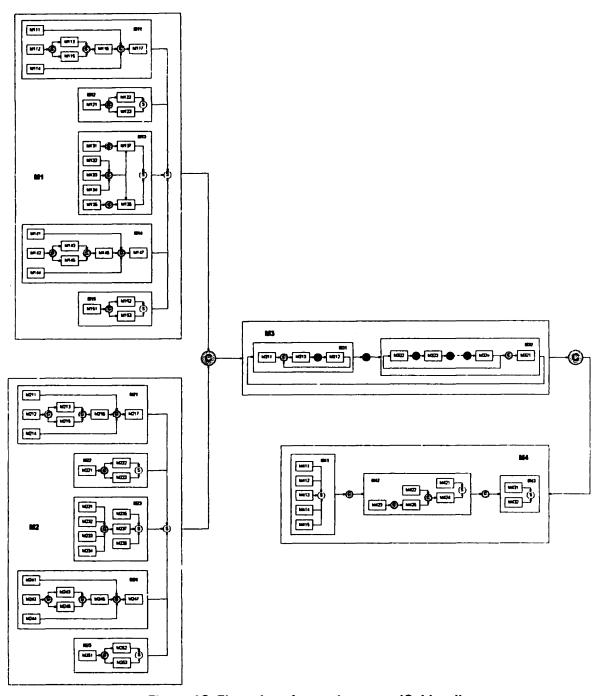

| 4.2.3 Gi    | raphical represent of System Architecture                  | 79 |

| 4.3 EXAMP   | LES AND RELATED HYPOTHESIS                                 | 80 |

| 4.3.1 Sy    | stem Diagnosis with SA – Diagnosis for wafer off-centering | 80 |

| 4.3.1.1     | Description of the problem                                 | 80 |

| 4.3.1.2     | Diagnosis procedure                                        | 80 |

|             | Conclusion                                                 |    |

| 4.3.2 Sy    | stem design from SA – synchronous algorithm                |    |

| 4.3.2.1     | Problem description                                        | 83 |

| 4.3.2.2     | Synchronous algorithm                                      | 84 |

| 4.3.2.3     | Conclusion                                                 | 86 |

| 5 CONCLU    | 'SIONS                                                     | 87 |

| 5.1 SYSTEM  | DESIGN USING THE CONCEPT OF SYSTEM ARCHITECTURE            | 87 |

| 5.2 APPLICA | ATION OF SYSTEM ARCHITECTURE                               | 87 |

| ∠ DEEEDE    | PAICE                                                      | 00 |

## **LIST OF FIGURES**

| Figure 1. Hierarchy of System Elements [12]                                                                            | <i>17</i> |

|------------------------------------------------------------------------------------------------------------------------|-----------|

| Figure 2. Synthesis of FRs                                                                                             |           |

| Figure 3. Synthesis of DPs                                                                                             | 22        |

| Figure 4. Tree diagram for a system                                                                                    |           |

| Figure 5. Illustration of Module-Junction diagram                                                                      | 29        |

| Figure 6. Junction Properties of the flow chart [18]                                                                   | 30        |

| Figure 7. Flow chart (1st and 2nd level)                                                                               | <i>30</i> |

| Figure 8 Design lead time                                                                                              | <i>33</i> |

| Figure 9 List of Hypotheses                                                                                            | 34        |

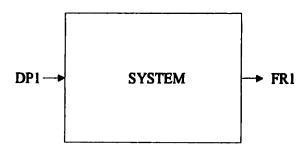

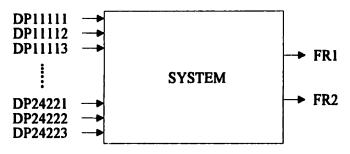

| Figure 10. Single level, One FR/One DP                                                                                 | 43        |

| Figure 11. Single level, multi FRs/DPs                                                                                 | 43        |

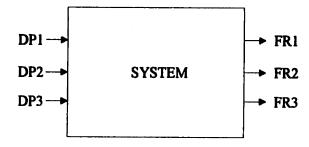

| Figure 12. Multilevel                                                                                                  | 44        |

| Figure 13. Identifying the cause of a problem [22]                                                                     |           |

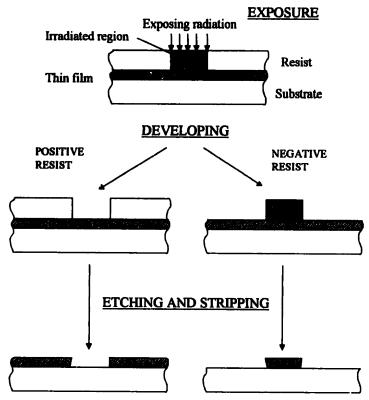

| Figure 14. Diagram showing the lithographic process [25]                                                               |           |

| Figure 15. Photoresist processes in Track system                                                                       |           |

| Figure 16. Flow chart for track system (3rd level)                                                                     |           |

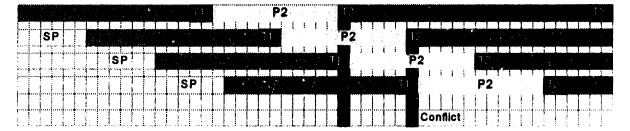

| Figure 17. Illustration of transport conflict                                                                          |           |

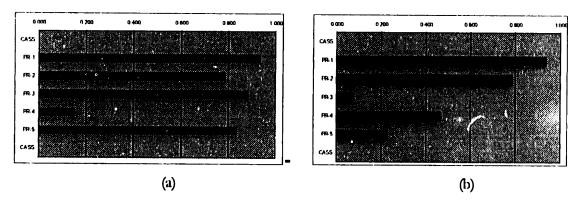

| Figure 18. (a) Location of transport requests, normalized by SP (b) Transports with no conflic with solved queue times | :1<br>85  |

## **LIST OF TABLES**

| Table 1. Definitions on system design terminology [12]       | 16 |

|--------------------------------------------------------------|----|

| Table 2. Ist/2nd level DM                                    | 26 |

| Table 3. Multi-level design matrix                           | 42 |

| Table 4. Generic FR / DP table                               |    |

| Table 5. Ist Level FR/DP                                     | 53 |

| Table 6. 2nd Level FR/DP - Coating process modules branch    | 57 |

| Table 7. 2nd Level FR/DP - Developing process modules branch | 61 |

| Table 8. 2nd Level FR/DP - system configuration branch       |    |

| Table 9. 2nd Level FR/DP - CCA branch                        | 65 |

| Table 10. Consistency checking matrix for 1st&2nd level      | 68 |

| Table 11. 3rd Level FR/DP - Spin coater branch               | 69 |

| Table ! 2. 3rd Level FR/DP - System layout branch            |    |

| Table 13. 3rd Level FR/DP - Operational controller branch    |    |

| Table 14 . FRs/DPs for Vapor Prime module branch             | 81 |

#### 1. Introduction

The role of design in product development and manufacturing has been widely appreciated in recent years. In product design research, it has long been said that the design determines 80% of manufacturing cost. In order to meet such industrial needs for competitiveness, extensive work has been done for the last 20 years in the area of product design [1-4]. As our interest moves toward systems design, more complex and larger scale design object, there arises a strong need for a rational methodology that addresses system design issues. The topic of systems design has not been explored enough to provide a formal theoretical framework for systems design, and as a consequence, system design has been practiced mostly based on heuristic or empirical lessons.[5, Ch.4] In Axiomatic Design theory, it is claimed that the Axiomatic Design approach for a simple product design is equally applicable to the design of complex systems. By following the Axiomatic Design processes, a designer/design group will be able to come up with a proper system design and generate a comprehensive roadmap for a system.

In this thesis, hypotheses for systems design, based on Axiomatic Design, are discussed in detail, and a case study is presented to illustrate the application of the hypotheses.

#### 1.1 Motivation

The ultimate goal of engineering design is system design. It not only requires solving specific engineering problems, but also coordinating every component's functionality to yield a final goal of the system. A variety of issues are involved in system design. A designer needs to make sure that each of the well-functioning components are integrated properly, so that they perform together to produce the system's objective. A design manager should also overcome the complexity in order to plan and execute a large number of design tasks. Most tasks related to system design have been done heuristically or empirically, because system design practice has lacked a formal framework. Furthermore, heuristic approaches emphasize qualitative guidelines, which can result in expensive and unpredictable after-built testing processes.

There is a need to create a rational approach for system design. Rational system design should be method-based and include system-level analysis, as opposed to the design practice based on heuristic lessons, solution-based approaches using building codes and handbooks, etc. Systems engineering has been accepted as a general problem-solving paradigm that divides the decision-making process into a series of stages [6]. These stages typically cover the activities in a design process: comprehensive problem identification; formalization of goals; generation of solution concepts; evaluation of concepts and selection of the best solution; and implementation. For example,

Templeman [7] identifies four fundamental questions to be answered during the system design process:

- 1. What are the goals that must be achieved?

- 2. How are the goals achieved, limited, and related to one another within each solution alternative?

- 3. How are solution alternatives assessed in terms of good and bad?

- 4. How can the best solution be identified?

Traditional systems engineering, however, does not provide explicit concepts and a formal strategy with which one can answer the above questions. In Axiomatic Design theory, the concepts of design domains, zigzagging between the domains, and the two design axioms are clearly presented, and those concepts provides formal and rational answers to the above questions. By offering designers a rational system design methodology, system design practice is improved.

#### 1.2 Objectives

Ulrich and Eppinger [8] propose three needs which a systematic design process can provide for a successful product development. A systematic design process provides 1) an explicit decision making method that is well understood by all team members, 2) a checklist to ensure that important steps are not forgotten, and 3) a natural documentation of the decisions made for future reference. The above needs are equally applicable to system design, since system design is an extension of product development.

The concept of System Architecture in Axiomatic Design theory satisfies these needs for rational and systematic system design. It is an efficient way of dealing with system design. It guides a designer through the system design process, helps with managing system design and the interrelationships of the components, and finally yields a well-organized document as well as the design itself.

The objective of this research is to elaborate the concept of System Architecture within Axiomatic Design theory. A theoretical review on the System Architecture concept is followed by a case study conducted to verify the concept and illustrate the application of the System Architecture.

#### 1.3 Research method

This section discusses the method for researching System Architecture, that was followed in this thesis. This concerns the start and progress of research in Axiomatic Design and System Architecture.

Axiomatic Design begins with two axioms, namely, the Independence Axiom and the Information Axiom. The axioms are stated in abstract language and provide generic guidelines for designers. Suh

developed a number of theorems and corollaries out of the axioms to facilitate their use. However, many people who try to apply Axiomatic Design to their own design projects say that it is difficult to apply Axiomatic Design to an actual problem. Why is it so difficult? Are there some straightforward steps? Answering these questions requires serious research activity. Case-studies have been considered as an effective means to learn Axiomatic Design, and various case-study works have been done by Suh and his colleagues. Still, there is a need for a clear definition/description for each concept used in Axiomatic Design, rules/steps to follow in the decomposition process, guidelines with which a designer can select a proper set of functional requirements, and so forth.

One can elaborate the concepts used in Axiomatic Design by answering every prospective question: e.g., why are functional requirements inherently independent of each other? How do functional requirement and design parameter differ? It is theoretical research to some extent, and requires intensive philosophical efforts. Developing rules/steps in decomposition process has been addressed recently by Tate[9]. The rules are developed through the observation of various design processes, and verified by large-scale case-studies. Writing guidelines for functional requirement selection is not simple. If they are stated in purely abstract terms, they are not likely to be readily useful. On the other hand, if they are biased toward specific fields or applications, they will not be applicable to problems in other disciplines. This conflict results from the peculiar nature of design research. Nordlund and Tate categorize the fundamental knowledge areas within design as the following[10].

- Designers,

- The design process,

- The design object,

- The relevant field(s), and

- Resources (such as time and morey).

The areas, which are connected by Axiomatic Design theory, are the design process and the design object. Specifically, the concepts relating to the process are domains and zigzagging, and the concepts relating to the design object are independence and information. It is noteworthy that Axiomatic Design itself does not cover the field where the individual design object belongs: specialized methodology will correspond to the relevant field. Thus, an individual theory in design discipline does not necessarily need to encompass all of the above five areas.

The issues discussed in this thesis fall into the category of concept definition/description within Axiomatic Design theory. Axiomatic Design theory claims that the practice of System Architecture improves the result of the design. Although the concept of System Architecture has been present in

Axiomatic Design since the early 1990s, little work has been done regarding System Architecture and application of it. The concept of System Architecture needs to be elaborated, and the methodology must be applied to actual system designs to verify the concept. As stated above, the System Architecture concept is defined and described by answering the expected questions. Those questions are formalized in terms of hypotheses. The hypotheses are also the statements the author believes to be true based on Axiomatic Design theory, regarding system design. Based on the fundamentals of Axiomatic Design theory, the author can argue that these hypotheses are reasonable. Then, they are tested through the case study.

The first phase of the research is to list a number of hypotheses regarding SA. Logical reasoning will be given for each of the hypotheses. The justified hypotheses, then, will be applied to an actual system design for the verification.

#### 1.4 Thesis overview

This thesis is structured in the following way: the concept of System Architecture is reviewed, issues related. System Architecture – in general, system design – are discussed, and finally a case study is presented. The following list summarizes the content of each chapter.

- Chapter 2 reviews the System Architecture concept, and discusses activities in the Axiomatic Design process from the perspective of system design.

- Chapter 3 presents a list of hypotheses concerning System Architecture. The hypotheses are

described based on Axiomatic Design theory and practices. At the end of the chapter, an

approach to test and validate the hypotheses is discussed.

- Chapter 4 provides a case study to illustrate system design based on System Architecture concept. A case study on photoresist processing system covers the practice of Axiomatic Design for a system design and verifies the hypotheses with detailed examples.

- Chapter 5 concludes the discussion presented in this thesis.

#### 2 System Architecture

#### 2.1 System Architecture in Axiomatic Design

A System Architecture (SA) is an integrated form of application of Axiomatic Design (AD) in the following ways: 1) it is created SA when the AD approach is applied to a design of a system, the ultimate goal of design, 2) it includes all the aspects of AD process, and 3) it provides structured information about a system based on the fundamental concepts of AD. The basic motivation of SA is that we want to design a system in a systematic manner as opposed to the more chaotic approach typically applied in system design.

All of the above statements will be thoroughly covered in this paper. Before starting the main discussion, a couple of keywords must be clarified so that readers understand the terminology used in this thesis. Unfortunately, misunderstanding of terminology is not uncommon in the design research community and frequently hinders researchers from communicating effectively.

#### 2.1.1 What is a 'System' and 'design of a system'

The very first term to be defined is a 'system'.' It is, indeed, very difficult to define precisely, and there are various definitions for a system. Among the various definitions is Suh's definition [11].

A system may be defined as an assemblage of sub-systems, hardware and software components, and people that is designed to perform a set of tasks to satisfy specified functional requirements and constraints.

Different definitions for system are also available from other researchers. One of the broad definitions of a system is as follows: a system is an integrated set of elements that accomplishes a defined objective [12]. Another definition is available: a system is a set of different elements which together produces a result which they could not achieve separately [13].

Although it is not easy to obtain a unique definition in formal language, it seems that most people intuitively know what a system means. Observing the above three different definitions, one can notice two essential concepts in common throughout those definitions. They are

- A large number of components are integrated to yield a system.

- A system has its ultimate goal(s) which is(are) achieved through the accomplishment of distributed functions.

<sup>&</sup>lt;sup>1</sup> It is reasonable to confine our interest within the area of design theory.

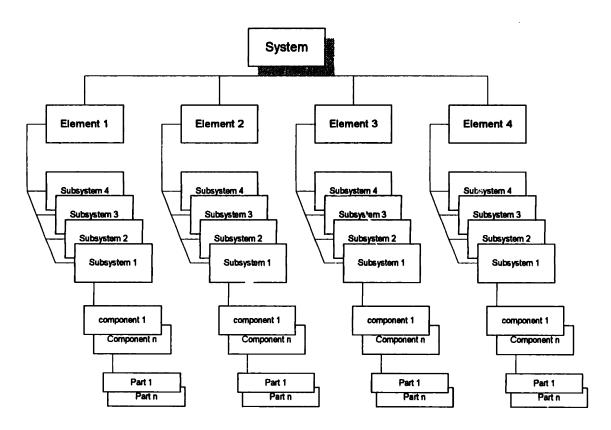

The above two statements are necessary conditions for the definition of a system. In addition to these conditions, it should be noted that whether an entity is system or not is determined in the context of a discussion. For example, a computer, which consists of main unit, monitor, keyboard, and a mouse, is a system in the context of computing machine design, but it is only a subsystem when we think of it as a part of Internet environment. Despite this relativity, agreeing to these two necessary conditions of the system definition, provide a sufficient basis to proceed with a discussion. We need to clarify the meaning of the terminology used in defining a 'system', e.g. component, subsystem, etc. INCOSE has good definitions regarding system design, and they are shown here to give a common understanding of the terminology used in this thesis. Table 1 shows a list of terminology definitions commonly used in systems engineering field. In Figure 1, the hierarchical nature of a system is illustrated using this terminology.

The result of a system design is a physical realization/entity that performs the ultimate functionality as initially intended. Although it may sound obvious, a system design is, therefore, the process through which a designer obtains the result: defining system's functionality, assigning elements to satisfy lower level functions, detailing them into subsystems, etc. The practice of system design is systemized with the help of the Axiomatic Design approach.

Fundamental concepts of Axiomatic Design can be summarized to three categories: design domains, mapping/zigzagging, and design axioms. Based on these concepts, the AD process – or the AD approach – is composed of several steps. The first step of the design process is to state Functional Requirements (FRs). Secondly, these FRs are mapped into the physical domain to yield Design Parameters (DPs). The third step is to examine the relationship between FRs and DPs and determine

| Tem                  | Definition                                                                                                                                                      |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Segment<br>(element) | A major product, service, or facility of the system, e.g., the aircraft element of an air transportation system                                                 |

| Subsystem            | Applied to apparatus which performs a cleanly separated function, such as communications, electronics, structures, or controls                                  |

| Assembly             | An integrated set of components and/or subassemblies that comprise a defined part of a subsystem, e.g., the fuel injection assembly of the propulsion subsystem |

| Subassembly          | An integrated set of components and/or parts that comprise a well-defined portion of an assembly                                                                |

| Component            | Comprised of multiple parts; a cleanly identified item                                                                                                          |

| Part                 | The lowest level of separately identifiable items                                                                                                               |

Table 1 . Definitions on system design terminology [12]

Figure 1 . Hierarchy of System Elements [12]

the design matrix. If the choice of DPs satisfies axiom 1, which is the Independence Axiom, these steps are repeated in the same manner to the next level of design. This is known as decomposition.

From the AD perspective, the design of a system is not fundamentally different from the design of simple mechanical products [11]. A system can be designed by following the AD approach described above, and all of the fundamental concepts of AD are applied to a system design. Therefore, all of the AD aspects are necessarily incorporated in system design activities, and the resultant is a System Architecture, hereafter called SA. If a system has only one or two layers of hierarchy, which is unlikely in any real case, a system design is not that different from the straightforward application of AD. However, as the scale of a system gets larger in terms of the level of the hierarchy and its span, it is not a trivial task to view the design object with a system perspective. SA, once created, can provide a whole view of a system.

One can raise the following question regarding the system design activity: how far shall a system designer reach in designing a system? When can a system designer say the system design is 'done?' Obviously, a system design doesn't have to focus on part level design: for example, a track system – pre/post photolithography processing system – designer may not be interested in selection of

bearings used in a robot carrier.<sup>2</sup> AD names the last module of the FR/DP hierarchy as a *leaf module*. In any kind of design, the design is said to be done when decomposition reaches to leaf module for every branch of the decomposition. Then, how do we know that the decomposition reaches a leaf module? What is a leaf module? Tate argues that if an operand of a sub-FR is different from that of parent-FR, design for that branch is done by assigning appropriate sub-DP [9, pp. 15-18]. In his logic, it is the FR that determines whether a module is a leaf or not. Yet, it is more intuitive to consider the DP as a key factor in determining an answer to this question. If a selected DP is something that already exists and either needs no re-design or needs no further decomposition for the purpose of system interaction investigation, then the module – FR/DP pair – is considered to be a leaf. The concept of a leaf module as an indicator for design completion can be applied to system design in the same way. Whether it be a component, subsystem, or even an element, once a designer specifies all the requirements and constraints enough to consider the design as a *local* design task, the system design can be said to be completed.

#### 2.1.2 System architecture (SA)

The concept of system architecture, in general, is receiving enormous attention in recent days, because many people recognize the lack of formal theoretical framework for complex systems [11, 14]. The term, system architecture can be named and defined in various ways. Ulrich defined 'product architecture' as the scheme by which the function of a product is allocated to physical components [15]. INCOSE defines 'system architecture' as the arrangement of elements and subsystems and the allocation of functions to them to meet system requirements. In the AD theory, system architecture is used to mean the structure by which each physical parameter interacts with each of system's functional requirements. It is the aggregation of all of design decisions during the AD process. Therefore, SA does imply not only the allocation of functions to system's (physical) components but also the interconnection between those functions and physical parameters. Tate also states that SA can be exploited as a tool for decision making in AD[9], which is the prominent value of the AD SA concept. Each of these definitions has its proper form with which the researcher can use the term "system architecture" in his research context. Ulrich's product architecture shares some common concepts with the AD SA. Ulrich's product architecture is defined as follows: 1) the arrangement of functional elements, 2) the mapping from functional elements to physical components, 3) the specification of the interfaces among interacting physical components. The differences are 1) Ulrich's product architecture is used in the context of the effect of a product's physical structure onto the manufacturing firm performance; 2) the meaning of the mapping process is relating functional

<sup>&</sup>lt;sup>2</sup> Detailed discussion on track system architecture is available in Chapter 4.

elements with physical components<sup>3</sup>. The concept of system architecture recognized by INCOSE does not capture the interaction between functional and physical elements. It seems that INCOSE's initiative is to focus more on the managerial aspect of system design. Throughout the thesis, by system architecture I will follow the definition used in AD theory, since it captures the most essential activity, making design decisions, when discussing the design of a system.

Potential applications of the system architecture are discussed by Suh [5], who lists some of the applications which are related to system design and operation. They are 1) diagnosis of system failure, 2) engineering change orders, 3) job assignment and management of a system development team, 4) distributed systems, 5) system design through assembly of modules, and 6) system consisting of hardware and software. In this thesis, these applications will be discussed in detail in terms of hypothesis verification.

#### 2.2 Creation of System Architecture

As stated in the previous section, creating SA is equivalent to the design a system, and an SA is created by following the AD processes. In this section, the AD processes will be discussed, and elements of SA will be described.

#### 2.2.1 Design processes in Axiomatic Design

#### • State FRs and Cs

After investigating the customers' needs, a designer – or group of designers – states FRs explicitly in solution neutral terms. The FRs should be the functions a design object has to perform. – The object could be a system/element/subsystem/component/part, e.g. a designer's task could be a part design or a system design. Thinking in the solution neutral environment guarantees the freedom in the subsequent step of the design, which is devising DPs. Stating FRs is a stage of problem definition, and it cannot be emphasized too strongly. Stating/selecting FRs is a totally subjective activity and there is no dependable criterion by which the set of FRs is determined to be 'good'. With the parent DP given, different designers may come up with different sets of sub FRs, depending on his/her own background knowledge and bias. Is there any kind of logical measure based on which one set of FRs is said to be "better" than the other? So far, the activity has depended almost only on the definition of FR: a minimum set of independent requirements that 'completely' characterizes the functional needs of the product in the functional domain. Accordingly, the only way to make the judgement is to examine – by

<sup>&</sup>lt;sup>3</sup> For example, following Ulrich's definition, a coke can may be categorized into integral architecture, which means one-to-many mapping from functions to components. On the contrary, from the AD perspective, a coke can is still one-to-one mapping from functional domain to physical domain with 'decoupled' interaction. In AD, physical component must not be confused with design parameter.

any means – whether the parent DP is completely realized and consequently the parent FR is satisfied. Recently, Tate discussed the idea of 'completeness' of the selected FRs and developed rules that could be a guide to FR selection.[9] A complete set of sub-FRs is defined as a set of sub-FRs that is sufficient for producing the parent-level FR, that also satisfies the parent-level Cs and the parent-level DM, and that describes the functions of parent-level DP.

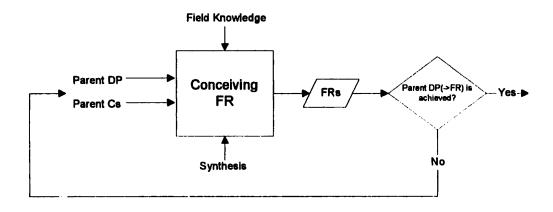

With this limited conceptual guideline, it is never an easy task to come up with the "right" set of FRs. It requires creativity and logical reasoning, and often involves quite a few iterations to conceive a proper set of FRs. The reason why iteration is needed is because verifying the correctness of FRs in current practice necessarily incorporates bottom-up characterization as opposed to top-down approach, a part of the main philosophy of AD. In spite of the ambiguity, a lot of designers seem to manage to get reasonable sets of FRs in terms of achieving parent level FRs. They tend to have more trouble stating FRs in solution neutral terms and keeping the number of FRs to a minimum. The process of conceiving FRs is illustrated in Figure 2. Since the question "is parent DP (→FR) achieved?" sometimes cannot be answered until the design is decomposed further, there will be another feedback loop departing from somewhere far downstream of the whole design process, which is also regarded as part of the iteration process.

The discussion of the above paragraphs is better understood with an example. The example shown here is adapted from the case study which is presented in section 4.2.

Below is an example of top level functional requirements. It is a list of FRs for the design of photoresist processing equipment.

FR1 = coat wafers with desired resist film

FR2 = develop exposed film

FR3 = process wafers at desired rate

FR4 = control the system functions

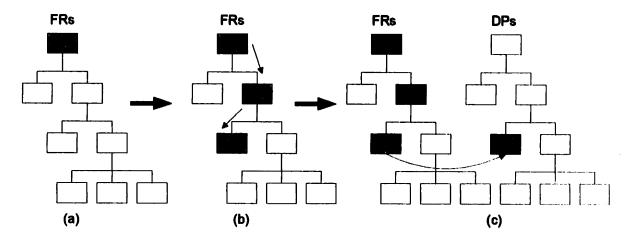

Figure 2. Synthesis of FRs

How were these 4 FRs obtained? At first, a designer looks at the parent FR and parent DP. In this case, the parent FR is "fabricate wafers before/after photolithography process." The parent DP to satisfy the FR is "track system", which is clustered to a photolithography system. Though the concept of "track system" at this level is not detailed at all, a designer has at a least rough picture of what it will look like. Besides the parent FR/DP, there are many system level constraints such as cost, footprint, throughput, safety, just to name a few. Those constraints have potential impacts on the design decisions, although the impacts are not directly expressed in FR statements. Given the parent FR/DP and constraints, a designer thinks about what type of functions the parent DP has to perform in order to achieve the parent FR and satisfy the constraints. Here comes a designer's process-knowledge and logical reasoning based on engineering science. In the example, four types of FRs are identified as a result of this thought process. They are the essential functions required for the track system.

As mentioned above, a different designer may come up with different set of FRs even with the same inputs, i.e. same parent FR/DP, and same set of constraints. Although two sets of sub-FRs are not identical, if the highest level FR, which is "fabricate wafers..." in this case, is eventually achieved, then both sets should carry the essential functional requirements somewhere in the FR hierarchy. By its definition of 'equivalent design', the difference is neglected after all4.

Now that we have FRs, the next step is to devise DPs that satisfy the FRs – this is known as the mapping process.

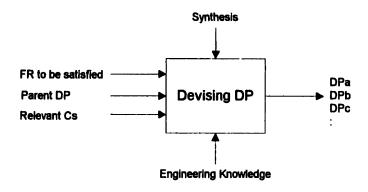

#### Devise DPs for each of FRs

Each FR must be mapped into the physical domain, which results in a set of DPs. When choosing DPs, we have the freedom to come up with any feasible idea only if they satisfy FRs subject to the related constraints. Thanks to this freedom, we may have several alternative DPs for a particular FR among which we can choose the best one. The mapping process is illustrated in Figure 3.

This mapping process, of course, requires quite an amount of knowledge and effort regarding the design object: e.g. material science, fluid dynamics, electromagnetics, etc. The more a designer has field knowledge, the higher chances he/she can come up with good design because he/she will have a better quality database for DPs. The typical notion for 'engineering design' refers to this mapping

<sup>&</sup>lt;sup>4</sup> Definition S1: Two designs are defined to be "equivalent" if they perform the same set of the highest level FRs within the bounds established by the same set of constraints, even though the mapping and decomposition process might have yielded designs that have substantially different lower level FRs and all DPs for each of these designs. Equivalent design doesn't mean that two 'equivalent design' will have the same quality and/or cost effectiveness. Equivalency just implies that two – or more – equivalent design all satisfy the highest level FR.

process: extensive research, creative thinking, physical synthesis, etc. A lot of misunderstandings about AD occur here because some people think that AD should be able to make this challenging process easy. It is similar to saying that a computer should solve all the problems if we just give the problems to a computer. What AD really does is to provide sound criteria for judgement on whether a certain choice of DP will make system work or not. The AD process requires a designer to come up with any feasible solution to an FR, and helps him with making the best choice out of his/her own database.

Conceiving a number of candidates for DP is still in the role of human designer. A design theory, including AD, can help the designer by leading him to the right way of thinking. As an example, among the design methodologies that help a designer in that way is TRIZ – The Theory of Inventive Problem Solving. It guides a designer to formulate the existing problem. It also tries to help a designer with his design task by providing detailed rules to various kinds of problems, which are known as 'algorithms' in TRIZ. These efforts are useful when a designer seeks a core understanding of the problem when the original design violates the design axioms, and those are consistent with AD. Although both AD and TRIZ are very useful at the problem definition stage and provide some help when conceiving a particular solution, those activities are still highly dependent on the synthetic ability of human beings.

An example of DPs is shown below. These DPs are mapped from the previous FR example.

DP1 = coating process modules

DP2 = developing process modules

DP3 = system configuration

DP4 = system control command

Figure 3. Synthesis of DPs

FR1 is 'coat wafers with desired resist film,' and the parent DP is 'track system.' Relevant constraints at this level of design are cost, throughput, process flexibility, serviceability, etc. Based on those inputs, DP1 is chosen to be 'coating process modules.' By choosing 'coating process modules' as DP1, the designer implies that the system needs a series of processes to perform resist film coating. With the information, a modular structure is adopted as a reasonable way to satisfy FR1 with specified constraints. In the same way, 'developing process modules' are selected as DP2. FR3 is 'process wafers at desired rate,' and the identified DP for the FR3 is 'system configuration.' DP4 is 'system control command' which will be the control software of the track system. The above set of DPs is abstract and has little information with them since they are at such a high level. All that is stated with DPs is that the system will have different modules to perform corresponding functions. It is acceptable because it gives the designer a conceptual direction for further design.

#### Determine Design Matrix

Once we have FRs and DPs, the next step is to examine their relationship by determining a design matrix. Design matrix is defined as:

$${FR1 \atop FR2} = [DM] {DP1 \atop DP2}$$

(2.1)

DM is 2×2 matrix in the above case, and it shows the relationship between FRs and DPs. That is, it shows whether DPi will affect FRj or not. Strictly writing,

$$\begin{cases}

\Delta FR1 \\

\Delta FR2

\end{cases} = \begin{bmatrix}

\frac{\partial FR1}{\partial DP1} & \frac{\partial FR1}{\partial DP2} \\

\frac{\partial FR2}{\partial DP1} & \frac{\partial FR2}{\partial DP2}

\end{bmatrix}

\begin{cases}

\Delta DP1 \\

\Delta DP2

\end{cases}$$

(2.2)

Based on the definition of DM, a typical question a designer asks when determining each element of design matrix, is:

Does DPj affect FRi?

The question is refined maintaining equivalence,

Does a change in DPj, consistent with fulfilling FRj, affect FRi?

οr

Does the choice of DPj affect the choice of DPi?

We can answer these criteria questions relatively easily when design reaches leaf level, where mathematical expressions may be available. Answering the question, which is equivalently defining

the relationship between FRs and DPs, is not a design decision at the leaf level, but a fact to be analyzed. On the contrary, at early stages of design, it may not be answered easily in the same way. The reason is that we have a relatively small amount of information about the chosen DP. The intellectual activity a designer performs when determining the design matrix at this level can be considered with two different point of views. First, it is more like a decision of design direction than solid analysis with concrete DP. What a designer is really doing is to conceptualize abstract design and impose a direction on later design. Therefore, the types of questions are changed to:

Shall DPj affect FRi?

Shall a change in DPj consistent with fulfilling FRj, affect FRi?

Shall the choice of DPj affect the choice of DPi?

In the ensuing design, a designer should be always well aware of the design direction imposed by the design of the previous level. Another way of viewing the process is that it involves the further detail of the DP, which is not yet decomposed, to some degree. If the answer to the question is 'yes,' it must have some supporting argument such as 'The aspect xx of DPj will affect FRi.' The aspect may come from the designer's reasoning toward a sort of decomposition of the DP. The latter argument implies that bottom-up thinking is necessary to determine the design matrix. In fact, the next step of design process, consistency checking, shows the bottom-up feedback characteristic in AD processes.

Returning to the example, a design equation is constructed as following:

$$\begin{cases}

FR1 \\

FR2 \\

FR3 \\

FR4

\end{cases} = \begin{bmatrix}

X & O & O & O \\

O & X & O & O \\

X & X & X & O \\

X & X & X & X

\end{bmatrix}

\begin{cases}

DP1 \\

DP2 \\

DP3 \\

DP4

\end{cases}$$

(2.3)

FR1/FR2 and DP1/DP2 have an uncoupled relationship. Since DP1 and DP2 are chosen to be modular with respect to each other, it is reasonable to proceed with the subsequent design in an uncoupled way. FR3 is 'process wafers at desired rate.' DM(3,1) and DM(3,2) are marked 'X' indicating that DP1 and DP2 will affect FR3. The modular structure of DP1 and DP2 and various detailed features which will be addressed in further decomposition will affect FR3 as design requirements or constraints so that DP3 has to be designed (decomposed) in a way that it accounts for these effects. DM(1,3) and DM(2,3) are 'O's since we do not want DP3 to affect FR1 and FR2. FR1 and FR2 are the most fundamental requirements for a track system, and no effect from other DPs is acceptable. One of the efforts to make DM(1,3) and DM(2,3) to be 'O' is presented in the case study section, which shows the algorithm preventing irregular delay time in transport. All of

DP1, DP2, and DP3 have some effects on FR4 in a sense that FR4 can be detailed only after DP1, DP2, and DP3 are characterized. Thus, DP4, 'system control command' will be designed last.

Once a DM is determined with given DPs, we have to examine the type of design: uncoupled, decoupled, or coupled. If the design is either uncoupled or decoupled, it is an acceptable design, and we can go to next level of design. But if the design is coupled, we have to revisit the choice of DPs and do something – change the DP that causes coupling or pose certain constraints on the DP so that it will not cause coupling. During the design at the high level such as one in the example, the design matrix is determined by our own decisions to some degree, and we explicitly decide not to have a coupled design. Maintaining the validity of high level decisions should be emphasized more than the decisions themselves. The feasibility of the decisions will be fully realized through further design decomposition.

#### Decision consistency checking

As mentioned above, maintaining former design decision has much importance. Therefore, there should be a systematic way to force a designer to take it into account. A multilevel design matrix has been used by a few [6, 16], and the author believes it is a good tool to view the decision consistency.

The basic motivation for a multi-evel design matrix originated from the investigation of off-diagonal terms in a design matrix. When one decomposes the design, the focus is normally on the diagonal elements in the design matrix. Little information is known about off-diagonal elements. In order to justify the decision on an off-diagonal element in the design matrix, one needs to examine the relationship between sublevel FRs and DPs. It is simply done by subdividing columns and rows into sublevel ones. For example<sup>5</sup>:

Suppose that the first level design equation is

$$\begin{cases}

FR1 \\

FR2

\end{cases} = [DM0] \begin{cases}

DP1 \\

DP2

\end{cases} = \begin{bmatrix}

X & O \\

X & X

\end{bmatrix} \begin{cases}

DP1 \\

DP2

\end{cases}$$

(2.4)

With the above DM0, we can say that DP1 affect FR2, and DP2 does not have any effect on FR1.

The second level design equations are

$$\begin{cases}

FR11 \\

FR12

\end{cases} = [DM1] \begin{cases}

DP11 \\

DP12

\end{cases} = \begin{bmatrix}

X & X \\

O & X

\end{bmatrix} \begin{cases}

DP11 \\

DP12

\end{cases} \tag{2.5}$$

<sup>&</sup>lt;sup>5</sup> The example given in this section is arbitrary one. A more detailed example for a track system is available in section 4.2.2.

$$\begin{cases}

FR21 \\

FR22 \\

FR23 \\

FR24

\end{cases} = [DM2] \begin{cases}

DP21 \\

DP22 \\

DP23 \\

DP24

\end{cases} = \begin{bmatrix}

X & O & O & O \\

O & X & O & O \\

X & X & X & O \\

X & O & O & X

\end{bmatrix} \begin{bmatrix}

DP21 \\

DP22 \\

DP23 \\

DP24

\end{bmatrix} \tag{2.6}$$

To examine whether the choice of sublevel DPs is consistent with higher level design decision, we construct multilevel design matrix which includes the first and second level design matrices as shown in Table 2.

| FR11 | Х     | x (S) (S) (e) |     |    |   | DP11         |      |

|------|-------|---------------|-----|----|---|--------------|------|

| FR12 | 0     | X             | Ho. | 60 |   | ##.<br>19.10 | DP12 |

| FR21 |       | Fot           | X   | 0  | 0 | 0            | DP21 |

| FR22 | Ta ji | To l          | 0   | X  | 0 | 0            | DP22 |

| FR23 |       | ie,           | X   | X  | X | 0            | DP23 |

| FR24 | 7,5   | 701           | X   | 0  | 0 | X            | DP24 |

Table 2. 1st/2nd level DM

The unshaded portion of the design matrix is DM1 and DM2, respectively. The emphasis here is on the shaded area. Filling the elements in the shaded area requires examination of the cross effects such as the effect of DP1x on FR2y. If any one of DP2x has strong effect on FR1y, then it will violate the earlier design decision. One should impose some constraints or specify conditions with which it will not happen. The superscripts in Table 2 indicate there are constraints that DP21 and DP22 must satisfy. If it is inevitable for a sub DP to have effect that leads to the violation of the former design decision, there are two options for a designer: choose new DP or revise the higher level DM. In the latter case, the higher level DM must be either uncoupled or decoupled matrix, otherwise, serious redesign from the 1<sup>st</sup> level needs to be done.

The steps illustrated above are repeated until a designer gets to the final stage of design. It is a continuous application of AD.

#### 2.2.2 Elements of System Architecture

System Architecture is created while we follow AD design processes. Consequently, the elements of SA include all the things we bring forward during AD activities.

Fundamental elements of SA are, needless to say, FRs, DPs and design matrices, and constraints. For the system design, they combine to form a large hierarchy, which is equivalently a set of design

decisions. As we saw in section 2.1.2, "design decision" is a keyword in describing SA in AD. In AD process, decisions are made at various stages of the design while affecting each other.

First of all, the selection of FRs is the most fundamental design decision. After a designer studies customer needs (CNs), he/she must make a decision which one should be mapped into functional domain and which ones should not. Since all of CNs are not likely to be mapped into top level FRs, the designer also has to decide an appropriate hierarchical level for mapping CNs. From the second level hierarchy, the upper level DPs give a boundary to a designer's scope in establishing FRs. In the narrowed-down design space, he/she selects minimum set of FRs. A minimum set of FRs is a set of FRs that is necessary and sufficient to describe the functionality of a parent DP. As mentioned in the previous section, section 2.2.1, defining FRs can be considered a subjective task, and involves design decisions.

Secondly, choosing a DP among alternatives is a design decision. The mapping process itself is not a decision making process: it is concept generation rather than decision making. Only when there is more than one option is the decision making activity involved.

Determining the design matrix is also a design decision. In the previous section, it was argued that at the high level of system design, determining design matrix elements is more like a decision on design direction. The high-level design matrix directly shows the designer's intention for the ensuing design. At lower-levels, the design matrices represent a physical analysis of FR/DP interactions. It determines the type of the design: uncoupled, decoupled or coupled. A coupled design matrix indicates that a designer should change the previous decision - choice of DPs or higher level design matrix.

The above set of design decisions is all incorporated in the SA. In other words, they are important elements of the SA. SA shows a clear picture of the whole set of design decisions using its appropriate forms, which are explained in the next section. Later on, when an alternative design decision is made, the decision will be substituted into the structure of the SA. To summarize, the essence of SA is its hierarchical structure of design decisions.

Documenting System Architecture is important. Documentation structure includes the essential elements – all of the design decisions. Therefore, it consists of FR/DP/design matrix/constraints table, description of FRs/DPs, justification of DM, and visual representation. A standard template to document SA has been developed in Axiomatic Design Group at MIT [17]. In the case study, an example SA documentation is presented.

#### 2.2.3 Representation of System Architecture

One of the critical factors in SA representation is how clearly and concisely a system can be represented or visualized. It should give an insight into a system with a quick look. It should also provide essential information in a concise format. There are three ways in AD to visualize SA: 1) Tree diagram, 2) Module-Junction Diagram, and 3) Flow chart.

#### 2.2.3.1 Tree Diagram

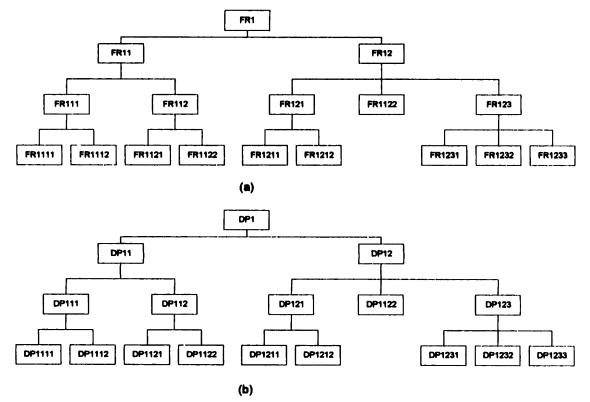

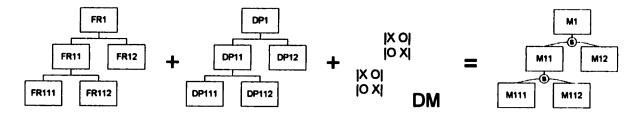

A tree diagram just shows the hierarchical structure of a system. It is has two types of tree structures one of which is for FRs and the other for DPs. Figure 4 shows the example of a tree diagram.

This representation is good for showing concisely the system's hierarchical structure of FRs and DPs. However, the tree diagram is nothing but a depiction of the hierarchical structure.

#### 2.2.3.2 Module-Junction Diagram

A Module-Junction diagram is created to represent SA more efficiently. It contains more information than a tree diagram. It indicates the type of each design matrix as well as the hierarchical structure of a system.

A module is, conceptually, equivalent to the row of the design matrix that yields the FR when it is provided with the input of its corresponding DP[11]. By its definition, a module represents the relationship between FR and related DP(s). In mathematical form,

$$Mi = \frac{\partial FRi}{\partial DP1} \frac{DP1}{DPi} + \frac{\partial FRi}{\partial DP2} \frac{DP2}{DPi} + \dots + \frac{\partial FRi}{\partial DPi} + \dots + \frac{\partial FRi}{\partial DPn} \frac{DPn}{DPi}$$

(2.7)

$$FRi = Mi \times DPi \tag{2.8}$$

where Mi is the module relating DPi with FRi.

In an uncoupled design matrix, a module is simply the diagonal element in DM. In a coupled case, it includes off-diagonal elements and DPs as well as diagonal elements. This is explained in more detail by Suh [11]. When we mention a module, we imply FR, DP, and their relationship as a whole. Therefore, the Module-Junction diagram is a combined representation of FR tree, DP tree, and DM.

A junction represents the type of each design matrix. A junction is a conceptual space where modules are combined. Each module is processed at a junction according to instructions given by the DM. There are 3 kinds of junctions: summing junctions (S), control junctions (C), and feedback junctions (F). They represent uncoupled, decoupled, and coupled design matrices respectively.

Figure 4. Tree diagram for a system (a) FR tree (b) DP tree

Figure 5. Illustration of Module-Junction diagram

A Module-Junction Diagram is based on the definition of module and junction. Basically, it is similar to a tree diagram. Additional features are

- Combination of FR tree and DP tree diagram

- Information on the type of design matrix

The Module-Junction diagram is good in a sense that it shows both the hierarchical structure and the type of design at each level – whether it is uncoupled, decoupled or coupled. In case of decoupled and coupled designs, knowing the detail of the design matrix, such as the sequence of design (operation), source of coupling, etc., is essential. Although we know the information by examining each DM, a representation scheme that visualizes the information is more advantageous. The next

section discusses another representation scheme, a flow chart, which satisfies the aforementioned need of visualization.

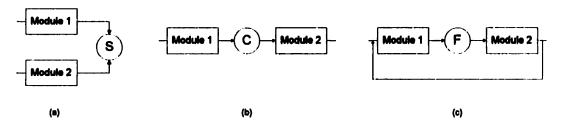

#### **2.2.3.3** Flow chart

The third way to represent SA is with a 'flow chart.' It is concise in its form and has explicit information from each design matrix: it shows the details of design matrices pictorially as well as the types of design matrices. The definition of module enables this simple representation of the SA in a form of the flow chart [11]. The Flow chart uses the symbolic expression of junctions in Figure 6.

Figure 6. Junction Properties of the flow chart: (a) Summing Junction (Uncoupled), (b) Control Junction (Decoupled), (c) Feedback Junction (Coupled) [18]

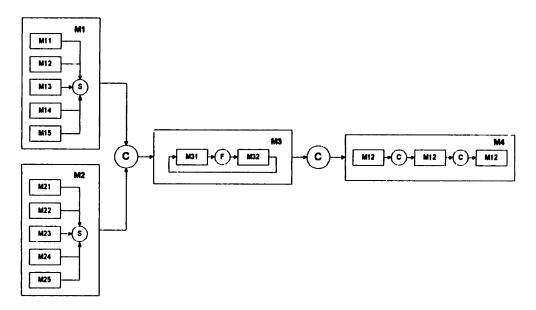

Figure 7 is an example of a flow chart, based on the one 1st level design matrix and four 2nd level design matrices. M<sub>i</sub> represents each module, and the flow chart clearly shows the structure of each design matrix. For example, we see from Figure 7 that the design matrix for FR1x/DP1x is diagonal matrix which means an uncoupled design. On the other hand, we see that the design matrix for FR4x/DP4x is a decoupled design, which represents a full-triangular matrix. Supposing that each design matrix is created properly, we can see the effects among components immediately with a flow chart, and we also get the right sequence to design the system.

Figure 7. Flow chart (1st and 2nd level)

#### 2.3 Summary

Chapter 2 discussed the topic of system design from the Axiomatic Design perspective. The author characterizes a system with two aspects: an integration of a large number of components and distributed functions to achieve the goals as a whole. Those characteristics imply that the fundamentals of system design are the same as the fundamentals of the design of simple mechanical products within the Axiomatic Design framework. System architecture is defined as the structure by which each physical parameter interacts with each of a system's functional requirements. The design processes in Axiomatic Design theory was reviewed to describe how to create a System Architecture - equivalently, how to design a system following the design processes in Axiomatic Design. The last two sub-sections, 2.2.2 and 2.2.3, explained the elements of a system architecture in terms of design decisions and representation schemes for the system architecture.

Chapter 3, based on the concepts presented in this chapter, discusses the system design and system architecture in more detail.

### 3 Hypotheses on Axiomatic Design and System Architecture

A list of hypotheses concerning SA is presented in this section. In section 4.1, the hypotheses are stated and described. Section 4.2 justifies the hypotheses based on AD theory and practices. Section 4.3 discusses how to test and validate the hypotheses with a practical application.

#### 3.1 List of hypotheses

In this section, a list of hypotheses is precented and described. The hypotheses listed here have a hierarchy. There are three high level hypotheses, the second and the third of which are directly adapted from Suh [11, Chapter 4.2].

#### A system (design of a system) is represented in SA

System Architecture incorporates the essential elements, which show the structure of a system created.

#### A system is designed using a top-down approach based on the fundamental concepts of AD

A designer starts system design by conceiving top level FRs/DPs and proceeds with the design through detailing them level by level. By doing so, he/she can complete the system design.

## • The complex relationships between various components of a system are coordinated and managed varing the SA

Most systems consist of a large number of various sub-components. In order to achieve the ultimate goal of a system, each component should be designed in a certain order and their interaction should be controlled properly. The SA contains necessary and sufficient information for this task.

The first hypothesis relates SA and system representation, the second is about SA and system design, and the third concerns SA and system management/control. The last two hypotheses are elaborated with lower levels hypotheses listed below:

#### A system is designed using a top-down approach based on the fundamental concepts of AD

The AD approach forces the designer to think in the right direction

By following the AD approach, a designer is kept on the right track, which should lead to a better design solution in less time.

This hypothesis can be refined further:

- Mapping & zigzagging is the right way to design and is always possible

Mapping & zigzagging, or equivalently decomposition, is required in order to do design properly, and it is possible regardless of the hierarchical level within the system.

- A designer can proceed with design given only a small amount of information at a high level

It is often the case with system design at high levels that DPs can not be defined precisely. Nevertheless, high level DPs can be decomposed into sub level FRs/DPs successfully.

- Design knowledge is captured in a structured way

Design knowledge includes a thorough understanding of the design objectives (FRs), physical methods (DPs) to achieve those objectives, relationships between them, constraints and instruction for physical implementation. These are captured and organized in the SA clearly.

• Concept of Concurrent engineering is necessarily incorporated in AD system design

Concurrent engineering has two essential characteristics: 1) it is a *concurrent* process, and 2) it is carried out by a multifunctional product development team [19]<sup>7</sup>. Following AD system design implies these types of activities.

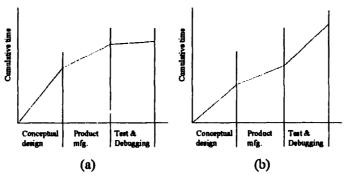

• Design lead time is decreased

Applying AD to complex system design has the benefit of shortened design lead time. This is illustrated in Figure 8.

Figure 8 Design lead time (a) AD process (b) typical design process

The complex relationships between various components of a system are coordinated and managed using the SA.

<sup>&</sup>lt;sup>6</sup> The term 'information' is used as general word. It is not related to the word 'information,' as defined by the Information Axiom.

• SA predicts the effects of the Engineering Change Orders

The meaning of ECO in a system is how many sub-components must be changed as a result of a change of certain component – or requirement. SA shows the effect of DP changes in the system and of FR changes.

• SA provides instructions for controlling the system

With the SA, one can easily obtain instructions regarding the sequence of system control.

SA is useful as a diagnostic tool for a system

SA can serve the task of diagnosis and be the basis of diagnostic tool development by indicating potential sources of the failure.

A full list of the hypotheses mentioned above is shown in Figure 9.

- A system (design of a system) is represented in SA

- A system is designed using a top-down approach based on the fundamental concepts of AD

- The AD approach forces the designer to think in the right direction

- Mapping & zigzagging is the right way to design and is always possible

- A designer can proceed with design given only a small amount of information at a high level

- Design knowledge is captured in structured way

- Concept of Concurrent engineering is necessarily incorporated in AD system design

- Design lead time is decreased

- The complex relationships between various components of a system are coordinated and managed using SA

- SA predicts the effects of the Engineering Change Orders

- SA provides instructions for controlling the system

- SA is useful as a diagnostic tool for a system

#### Figure 9 List of Hypotheses

#### 3.2 Argument on validity

In this section, the hypotheses presented are discussed based on AD theory and the nature of the SA.

<sup>&</sup>lt;sup>7</sup> Clausing refers this concept to 'basic concurrent engineering' to differentiate it from 'world-class concurrent engineering'.

#### A system (design of a system) is represented in SA

Suh describes the design process as four distinct activities: problem definition, creative process, analytical process and ultimate check[1]. During an original system design process that emphasizes problem definition and design solution synthesis, system representation corresponds to an aggregation of design decisions. Therefore, a system representation should include explicit delineation of functions and selected design concepts (physical domain) of the system. At the same time, it should clearly depict interrelationships between those components. A designer starts system design by stating fundamental FR(s) and then devises physical entities which will satisfy the FRs. Then, the design matrix is determined. These processes are repeated at the next level, which is known as decomposition. Along with the design processes, system representation is done in a form known as the System Architecture. SA covers all of these areas in its simple format as mentioned in section 2.2.2 and 2.2.3. Providing that a designer ends up with final design of a system through AD approach, the system built and SA should be identical. For improvement of an existing design, the analytic aspect dominates the design process. A designer is supposed to observe existing physical entities first, which are in the physical domain, and figure out which FRs are subject to each of the DPs. The focus is to organize FRs/DPs/design matrices to match the existing system. Out of an arbitrary<sup>8</sup> assemblage of physical entities, the designer has to construct a hierarchy of FRs and DPs. The resulting SA shows the structure of the existing system. Different aspects from the SA of an original design are that all the DPs are conjectured from existing physical entities and that we should not assume those are the right set of FRs since our basic motivation for analysis is to improve the existing design.

#### A system is designed using a top-down approach based on the fundamental concepts of AD

In designing a system, it is obvious that a reasonable designer will do his design in a hierarchical manner even though he is not aware of AD theory. According to Suh, that is because of the hierarchical nature of design objects. Suh indicates that the hierarchical nature of design objects justifies the top-down approach [1, p.4]. The design object of a system also has the hierarchical nature, and Figure 1 shows the physical hierarchy of a system. The top-down approach is one of the fundamental concepts in AD theory. Decisions are made in the order of importance by decomposing the problem into a hierarchy. Through the top-down process, upper-level design decisions propagate

<sup>&</sup>lt;sup>8</sup> The term 'arbitrarily' is used in the sense as follows:

Physical entities are integrated in ordered manner to achieve the overall goal, which is the top level functional requirement. However, in most cases of existing design, functional requirements at every level of a system are not clearly defined.

to lower-level design. It is exhibited by the facts: 1) previous choice of DP drives sub level FRs (zigzagging) and 2) the upper-level design matrix can lead to constraints that impact the choice of sub-level DPs. The top-down approach results in a hierarchical FR/DP structure, which is equivalent to a system's hierarchical structure. Therefore, considering the hierarchical nature of a system's functionality, the top-down approach is, in principle, the most rational way of designing a system.

It should be noted, however, that some of the activities during the top-down work flow need to be done in a bottom-up fashion. These are mentioned in section 2.2.1: verifying the correctness of FRs and determining design matrices. INCOSE describes this process as the combination of a top-down & bottom-up approach followed by compromise: "These (requirements and specifications of a system) are developed in a top-down/bottom-up fashion, with systems engineers defining what they want in a top-down fashion and subsystem engineers describing what they can provide in a bottom-up fashion". [12, p3] AD views the process as design limitations or constraints realized afterward, since AD wants to maximize a designer's freedom during the conceptual design stage.

#### • The AD approach forces the designer to think in the right direction

Following the AD approach means that a designer will proceed with a design through repeating a series of characteristic activities: 1) identify FRs in a solution-neutral environment, 2) devise DPs, 3) determine design matrices and make sure that the design axioms are satisfied, 4) check design consistency with respect to higher-level design decisions, and 5) repeat steps (1)-(4) at the next level. The 'right' direction in design thinking should lead a designer to better design solutions in less design time. The AD process will guide a designer toward this goal – better solution in less time. First of all, AD enables a designer to define the term, 'better.' It is one of AD's fundamental contributions to the area of design research. By elucidating the criteria of good design explicitly, AD directs a designer to the better design solution among the alternatives. Secondly, one of the claims in AD is that time/resource-consuming iteration process after the concept generation stage is reduced as a result of following the AD process: a system satisfying the two axioms is guaranteed to be working properly. The essential activities that contribute to those benefits include stating FRs, classification of uncoupled/decoupled/coupled designs, measuring information contents, and the decomposition process.

#### - Mapping & zigzagging is the right way to design and always possible.

Mapping and zigzagging are combined to complete the decomposition process, and decomposition is one of the crucial activities in design because of the hierarchical nature of the design object. Mapping and zigzagging are carried out between different domains and throughout all levels of the hierarchy.

Between the functional domain and physical domain, mapping and zigzagging are required: choose FRs, map them into DPs, select sub FRs, etc. It is the process of moving between 'what' and 'how,' which is the core of the design activity. There seems to be no doubt about it. Zigzagging, however, is not feasible between the customer domain and the functional domain because of the nature of customer domain. A designer does map between the two domains but does not zigzag between them. Customer Needs (CNs) are given from the customers, and a designer doesn't have freedom to define CNs. Sub-level CNs – if there is a hierarchical structure in CNs – are not driven by upper-level FRs. Defining sub-DPs based on parent FRs is the essence of zigzagging. Because of the lack of the characteristic, zigzagging is not performed between the two domains.

The hierarchical level of design does not affect applicability of mapping and zigzagging. Although it is possible to map and zigzag between domains regardless of the hierarchical level, there are some situations, especially at high-levels in a hierarchy, when it is difficult to devise solid (i.e. concrete or physically meaningful) DPs. In the example of automobile hood lock and release mechanism design [5, Chapter 2, p.58],

FR1 = Hold the pin in the locked position

FR2 = Release the pin from the lock position to an open position

After the mapping process, DPs are,

DP1 = Mechanical locking mechanism

DP2 = Release mechanism

DP1 and DP2 carry no detailed information about the mechanisms. Then, they are decomposed to,

FR11 = Locate the pin at the locked position

FR12 = Lock the pin

Again, the above two FRs are mapped into physical domain.

DP11 = A cam plate that provides dead stop position

DP12 = Rotating cam plate with a slot for the pin and a cam profile to engage a spring loaded ratchet mechanism (to keep the ratchet spring loaded against the cam surface)

Looking at the example, at the second level, we clearly see the mapping from FR11 to DP11 and from FR12 to DP12. On the other hand, one may say that the first mapping process,

from FR1 to DP1, is redundant and that one could decompose FR1 into FR11 and FR12. But, the process of going from FR1 to DP1 is not redundant because it implies its sub-FRs within itself: choosing DP1 is more or less equivalent to defining sub-FRs. If, for example, DP1 were 'magnetic locking mechanism', the subsequent design would yield different sub-FRs than FR11 and FR12. Therefore, mapping and, consequently zigzagging, have significance and are possible even at the high-levels of design hierarchy.

#### - A designer can proceed with design given only a small amount of information at the high level

In the original design process, a designer is likely to encounter situations in which he/she does not have enough knowledge to envision the rest of the design. However, a small amount of information does not necessarily mean an insufficient amount. In other words, at a high-level of a design hierarchy, the amount of essential information - knowledge - may be relatively smaller than that needed at the lower-level. The design activities related to concerned FR/DP are 1) determination of the design matrix at that level and 2) next level decomposition. The sequence of performing those activities in AD process is 1)-2). Activity 1) can be done without fully detailed information about the concerned DPs. In this activity, a designer imposes design direction for further decomposition in the absence of information on the details of the DPs. To impose design direction without constraints by lower-level DPs is another form of solution-neutral environment. Activity 2) requires enough information to figure out the next level functional requirements. By repeating these processes, the amount of information – design knowledge – will be increased to the amount needed to implement the final design.

#### Design knowledge is captured in a structured way

Design knowledge includes the design goals, physical methods to achieve those goals, relationships between them, and instructions for physical implementation.

Design objectives are explicitly stated in terms of FRs and their target value with tolerances. An FR is, by its definition, the requirement to be satisfied, and equivalently 'what' a designer wants to achieve. Starting from abstract FRs at high levels of design, it is detailed with continuing decomposition. The detailed FRs are itemized design objectives.

Physical methods to achieve these FRs are expressed in terms of DPs in the physical domain. Along with the detailing process for FRs, DPs are also specified in detail. A designer should try to come up with alternative DPs to yield a database of DPs for one FR. He/she will choose one DP as the best solution among them, and the rest of the database, which are alternative DPs, will facilitate any possible change of DPs later on.